Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

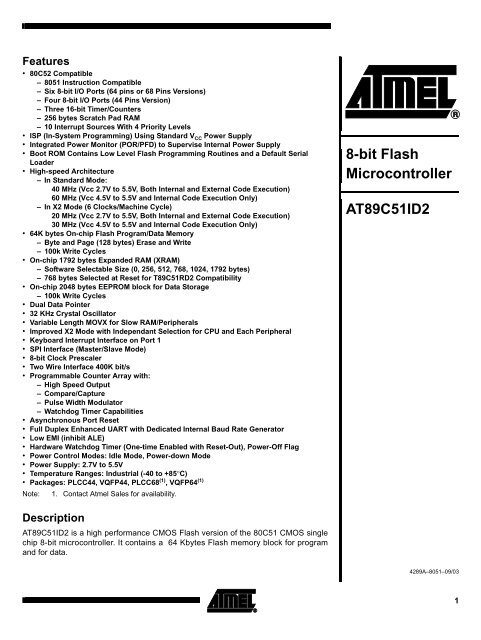

Features<br />

80C52 Compatible<br />

– 8051 Instruction Compatible<br />

– Six 8-bit I/O Ports (64 pins or 68 Pins Versions)<br />

– Four 8-bit I/O Ports (44 Pins Version)<br />

– Three 16-bit Timer/Counters<br />

– 256 bytes Scratch Pad RAM<br />

– 10 Interrupt Sources With 4 Priority Levels<br />

ISP (In-System Programming) Using Standard V CC Power Supply<br />

Integrated Power Monitor (POR/PFD) to Supervise Internal Power Supply<br />

Boot ROM Contains Low Level Flash Programming Routines and a Default Serial<br />

Loader<br />

High-speed Architecture<br />

– In Standard Mode:<br />

40 MHz (Vcc 2.7V to 5.5V, Both Internal and External Code Execution)<br />

60 MHz (Vcc 4.5V to 5.5V and Internal Code Execution Only)<br />

– In X2 Mode (6 Clocks/Machine Cycle)<br />

20 MHz (Vcc 2.7V to 5.5V, Both Internal and External Code Execution)<br />

30 MHz (Vcc 4.5V to 5.5V and Internal Code Execution Only)<br />

64K bytes On-chip Flash Program/<strong>Data</strong> Memory<br />

– Byte and Page (128 bytes) Erase and Write<br />

– 100k Write Cycles<br />

On-chip 1792 bytes Expanded RAM (XRAM)<br />

– Software Selectable Size (0, 256, 512, 768, 1024, 1792 bytes)<br />

– 768 bytes Selected at Reset for T89C51RD2 Compatibility<br />

On-chip 2048 bytes EEPROM block for <strong>Data</strong> Storage<br />

– 100k Write Cycles<br />

Dual <strong>Data</strong> Pointer<br />

32 KHz Crystal Oscillator<br />

Variable Length MOVX for Slow RAM/Peripherals<br />

Improved X2 Mode with Independant Selection for CPU and Each Peripheral<br />

Keyboard Interrupt Interface on Port 1<br />

SPI Interface (Master/Slave Mode)<br />

8-bit Clock Prescaler<br />

Two Wire Interface 400K bit/s<br />

Programmable Counter Array with:<br />

– High Speed Output<br />

–Compare/Capture<br />

– Pulse Width Modulator<br />

– Watchdog Timer Capabilities<br />

Asynchronous Port Reset<br />

Full Duplex Enhanced UART with Dedicated Internal Baud Rate Generator<br />

Low EMI (inhibit ALE)<br />

Hardware Watchdog Timer (One-time Enabled with Reset-Out), Power-Off Flag<br />

Power Control Modes: Idle Mode, Power-down Mode<br />

Power Supply: 2.7V to 5.5V<br />

Temperature Ranges: Industrial (-40 to +85°C)<br />

Packages: PLCC44, VQFP44, PLCC68 (1) , VQFP64 (1)<br />

Note: 1. Contact <strong>Atmel</strong> Sales for availability.<br />

Description<br />

<strong>AT89C51ID2</strong> is a high performance CMOS Flash version of the 80C51 CMOS single<br />

chip 8-bit microcontroller. It contains a 64 Kbytes Flash memory block for program<br />

and for data.<br />

8-bit Flash<br />

Microcontroller<br />

<strong>AT89C51ID2</strong><br />

4289A–8051–09/03<br />

1

2 <strong>AT89C51ID2</strong><br />

The 64 Kbytes Flash memory can be programmed either in parallel mode or in serial<br />

mode with the ISP capability or with software. The programming voltage is internally<br />

generated from the standard VCC pin.<br />

The <strong>AT89C51ID2</strong> retains all features of the <strong>Atmel</strong> 80C52 with 256 bytes of internal<br />

RAM, a 10-source 4-level interrupt controller and three timer/counters.<br />

In addition, the <strong>AT89C51ID2</strong> has a Programmable Counter Array, an XRAM of 1792<br />

bytes, a Hardware Watchdog Timer, SPI and Keyboard, a more versatile serial channel<br />

that facilitates multiprocessor communication (EUART) and a speed improvement<br />

mechanism (X2 mode).<br />

The fully static design of the <strong>AT89C51ID2</strong> allows to reduce system power consumption<br />

by bringing the clock frequency down to any value, even DC, without loss of data.<br />

The <strong>AT89C51ID2</strong> has 2 software-selectable modes of reduced activity and 8-bit clock<br />

prescaler for further reduction in power consumption. In the Idle mode the CPU is frozen<br />

while the peripherals and the interrupt system are still operating. In the power-down<br />

mode the RAM is saved and all other functions are inoperative.<br />

The added features of the <strong>AT89C51ID2</strong> make it more powerful for applications that need<br />

pulse width modulation, high speed I/O and counting capabilities such as alarms, motor<br />

control, corded phones, smart card readers.<br />

Table 1. Memory Size and I/O pins<br />

<strong>AT89C51ID2</strong> Flash (bytes) XRAM (bytes)<br />

TOTAL RAM<br />

(bytes) I/O<br />

PLCC44/VQFP44 64K 1792 2048 34<br />

PLCC68/VQFP64 (1)<br />

64K 1792 2048 50<br />

1. For PLCC68 and VQFP64 packages, please contact <strong>Atmel</strong> sales office for availability.<br />

4289A–8051–09/03

Block Diagram<br />

Figure 1. Block Diagram<br />

4289A–8051–09/03<br />

XTALA1<br />

XTALA2<br />

XTALB1(1)<br />

XTALB2<br />

ALE/ PROG<br />

PSEN<br />

EA<br />

RD<br />

WR<br />

(2)<br />

(2)<br />

CPU<br />

RESET<br />

RxD<br />

TxD<br />

EUART<br />

RAM<br />

256x8<br />

Timer 0 INT<br />

Timer 1 Ctrl<br />

T0<br />

T1<br />

C51<br />

CORE<br />

(2) (2) (2) (2)<br />

INT0<br />

INT1<br />

IB-bus<br />

VCC<br />

Vss<br />

(2) (2)<br />

(1) (1) (1) (1)<br />

Flash<br />

64Kx8<br />

XRAM<br />

1792 x 8<br />

PCA Timer2<br />

Watch<br />

Dog<br />

Keyboard<br />

POR<br />

PFD<br />

Port 0 Port 1Port 2 Port 3 Port4 Port 5<br />

P0<br />

P1<br />

P2<br />

(1): Alternate function of Port 1<br />

(2): Alternate function of Port 3<br />

(3): Alternate function of Port I2<br />

P3<br />

ECI<br />

P4<br />

PCA<br />

T2EX<br />

T2<br />

Keyboard<br />

Parallel I/O Ports &<br />

External Bus SPI<br />

TWI<br />

P5<br />

<strong>AT89C51ID2</strong><br />

(1)<br />

(3) (3) (1) (1)(1)(1)<br />

SDA<br />

SCL<br />

MISO<br />

MOSI<br />

SCK<br />

SS<br />

BOOT<br />

2K x8<br />

ROM<br />

E² DATA<br />

2K x 8<br />

Regulator<br />

POR / PFD<br />

3

SFR Mapping The Special Function Registers (SFRs) of the <strong>AT89C51ID2</strong> fall into the following<br />

categories:<br />

4 <strong>AT89C51ID2</strong><br />

C51 core registers: ACC, B, DPH, DPL, PSW, SP<br />

I/O port registers: P0, P1, P2, P3, PI2<br />

Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2,<br />

RCAP2L, RCAP2H<br />

Serial I/O port registers: SADDR, SADEN, SBUF, SCON<br />

PCA (Programmable Counter Array) registers: CCON, CCAPMx, CL, CH, CCAPxH,<br />

CCAPxL (x: 0 to 4)<br />

Power and clock control registers: PCON<br />

Hardware Watchdog Timer registers: WDTRST, WDTPRG<br />

Interrupt system registers: IE0, IPL0, IPH0, IE1, IPL1, IPH1<br />

Keyboard Interface registers: KBE, KBF, KBLS<br />

SPI registers: SPCON, SPSTR, SPDAT<br />

2-wire Interface registers: SSCON, SSCS, SSDAT, SSADR<br />

BRG (Baud Rate Generator ) registers: BRL, BDRCON<br />

Flash register: FCON<br />

Clock Prescaler register: CKRL<br />

32 kHz Sub Clock Oscillator registers: CKSEL, OSSCON<br />

Others: AUXR, AUXR1, CKCON0, CKCON1<br />

4289A–8051–09/03

Table 2. C51 Core SFRs<br />

4289A–8051–09/03<br />

<strong>AT89C51ID2</strong><br />

Mnemonic Add Name 7 6 5 4 3 2 1 0<br />

ACC E0h Accumulator<br />

B F0h B Register<br />

PSW D0h Program Status Word CY AC F0 RS1 RS0 OV F1 P<br />

SP 81h Stack Pointer<br />

DPL 82h <strong>Data</strong> Pointer Low byte<br />

DPH 83h <strong>Data</strong> Pointer High byte<br />

Table 3. System Management SFRs<br />

Mnemonic Add Name 7 6 5 4 3 2 1 0<br />

PCON 87h Power Control SMOD1 SMOD0 - POF GF1 GF0 PD IDL<br />

AUXR 8Eh Auxiliary Register 0 - - M0 XRS2 XRS1 XRS0<br />

AUXR1 A2h Auxiliary Register 1 - -<br />

ENBOO<br />

T<br />

EXTRA<br />

M<br />

AO<br />

- GF3 0 - DPS<br />

CKRL 97h Clock Reload Register - - - - - - - -<br />

CKSEL 85h Clock Selection Register - - - - - - - CKS<br />

OSCON 86h Oscillator Control Register - - - - - SCLKT0 OscBEn OscAEn<br />

Table 4. Interrupt SFRs<br />

Mnemonic Add Name 7 6 5 4 3 2 1 0<br />

IEN0 A8h Interrupt Enable Control 0 EA EC ET2 ES ET1 EX1 ET0 EX0<br />

IEN1 B1h Interrupt Enable Control 1 - - - - - ESPI EI2C EKBD<br />

IPH0 B7h Interrupt Priority Control High 0 - PPCH PT2H PSH PT1H PX1H PT0H PX0H<br />

IPL0 B8h Interrupt Priority Control Low 0 - PPCL PT2L PSL PT1L PX1L PT0L PX0L<br />

IPH1 B3h Interrupt Priority Control High 1 - - - - - SPIH IE2CH KBDH<br />

IPL1 B2h Interrupt Priority Control Low 1 - - - - - SPIL IE2CL KBDL<br />

5

Table 5. Port SFRs<br />

Mnemonic Add Name 7 6 5 4 3 2 1 0<br />

P0 80h 8-bit Port 0<br />

P1 90h 8-bit Port 1<br />

P2 A0h 8-bit Port 2<br />

P3 B0h 8-bit Port 3<br />

P4 C0h 8-bit Port 4<br />

P5 E8h 8-bit Port 5 - - - -<br />

Table 6. Flash and EEPROM <strong>Data</strong> Memory SFR<br />

Mnemonic Add Name 7 6 5 4 3 2 1 0<br />

FCON D1h Flash Control FPL3 FPL2 FPL1 FPL0 FPS FMOD1 FMOD0 FBUSY<br />

EECON EEPROM data Control<br />

Table 7. Timer SFRs<br />

Mnemonic Add Name 7 6 5 4 3 2 1 0<br />

TCON 88h Timer/Counter 0 and 1 Control TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0<br />

TMOD 89h Timer/Counter 0 and 1 Modes GATE1 C/T1# M11 M01 GATE0 C/T0# M10 M00<br />

TL0 8Ah Timer/Counter 0 Low Byte<br />

TH0 8Ch Timer/Counter 0 High Byte<br />

TL1 8Bh Timer/Counter 1 Low Byte<br />

TH1 8Dh Timer/Counter 1 High Byte<br />

WDTRST A6h WatchDog Timer Reset<br />

WDTPRG A7h WatchDog Timer Program - - - - - WTO2 WTO1 WTO0<br />

T2CON C8h Timer/Counter 2 control TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2# CP/RL2#<br />

T2MOD C9h Timer/Counter 2 Mode - - - - - - T2OE DCEN<br />

RCAP2H CBh<br />

RCAP2L CAh<br />

Timer/Counter 2 Reload/Capture<br />

High byte<br />

Timer/Counter 2 Reload/Capture<br />

Low byte<br />

TH2 CDh Timer/Counter 2 High Byte<br />

TL2 CCh Timer/Counter 2 Low Byte<br />

6 <strong>AT89C51ID2</strong><br />

4289A–8051–09/03

Table 8. PCA SFRs<br />

4289A–8051–09/03<br />

<strong>AT89C51ID2</strong><br />

Mnemo<br />

-nic Add Name 7 6 5 4 3 2 1 0<br />

CCON D8h PCA Timer/Counter Control CF CR - CCF4 CCF3 CCF2 CCF1 CCF0<br />

CMOD D9h PCA Timer/Counter Mode CIDL WDTE - - - CPS1 CPS0 ECF<br />

CL E9h PCA Timer/Counter Low byte<br />

CH F9h PCA Timer/Counter High byte<br />

CCAPM0<br />

CCAPM1<br />

CCAPM2<br />

CCAPM3<br />

CCAPM4<br />

DAh<br />

DBh<br />

DCh<br />

DDh<br />

DEh<br />

PCA Timer/Counter Mode 0<br />

PCA Timer/Counter Mode 1<br />

PCA Timer/Counter Mode 2<br />

PCA Timer/Counter Mode 3<br />

PCA Timer/Counter Mode 4<br />

-<br />

ECOM0<br />

ECOM1<br />

ECOM2<br />

ECOM3<br />

ECOM4<br />

CAPP0<br />

CAPP1<br />

CAPP2<br />

CAPP3<br />

CAPP4<br />

CAPN0<br />

CAPN1<br />

CAPN2<br />

CAPN3<br />

CAPN4<br />

CCAP0H FAh PCA Compare Capture Module 0 H CCAP0H7 CCAP0H6 CCAP0H5 CCAP0H4<br />

CCAP1H FBh PCA Compare Capture Module 1 H CCAP1H7 CCAP1H6 CCAP1H5 CCAP1H4<br />

CCAP2H FCh PCA Compare Capture Module 2 H CCAP2H7 CCAP2H6 CCAP2H5 CCAP2H4<br />

CCAP3H FDh PCA Compare Capture Module 3 H CCAP3H7 CCAP3H6 CCAP3H5 CCAP3H4<br />

CCAP4H FEh PCA Compare Capture Module 4 H CCAP4H7 CCAP4H6 CCAP4H5 CCAP4H4<br />

CCAP0L<br />

CCAP1L<br />

CCAP2L<br />

CCAP3L<br />

CCAP4L<br />

EAh<br />

EBh<br />

ECh<br />

EDh<br />

EEh<br />

PCA Compare Capture Module 0 L<br />

PCA Compare Capture Module 1 L<br />

PCA Compare Capture Module 2 L<br />

PCA Compare Capture Module 3 L<br />

PCA Compare Capture Module 4 L<br />

Table 9. Serial I/O Port SFRs<br />

CCAP0L7<br />

CCAP1L7<br />

CCAP2L7<br />

CCAP3L7<br />

CCAP4L7<br />

CCAP0L6<br />

CCAP1L6<br />

CCAP2L6<br />

CCAP3L6<br />

CCAP4L6<br />

CCAP0L5<br />

CCAP1L5<br />

CCAP2L5<br />

CCAP3L5<br />

CCAP4L5<br />

CCAP0L4<br />

CCAP1L4<br />

CCAP2L4<br />

CCAP3L4<br />

CCAP4L4<br />

MAT0<br />

MAT1<br />

MAT2<br />

MAT3<br />

MAT4<br />

CCAP0H3<br />

CCAP1H3<br />

CCAP2H3<br />

CCAP3H3<br />

CCAP4H3<br />

CCAP0L3<br />

CCAP1L3<br />

CCAP2L3<br />

CCAP3L3<br />

CCAP4L3<br />

TOG0<br />

TOG1<br />

TOG2<br />

TOG3<br />

TOG4<br />

CCAP0H2<br />

CCAP1H2<br />

CCAP2H2<br />

CCAP3H2<br />

CCAP4H2<br />

CCAP0L2<br />

CCAP1L2<br />

CCAP2L2<br />

CCAP3L2<br />

CCAP4L2<br />

PWM0<br />

PWM1<br />

PWM2<br />

PWM3<br />

PWM4<br />

CCAP0H1<br />

CCAP1H1<br />

CCAP2H1<br />

CCAP3H1<br />

CCAP4H1<br />

CCAP0L1<br />

CCAP1L1<br />

CCAP2L1<br />

CCAP3L1<br />

CCAP4L1<br />

Mnemonic Add Name 7 6 5 4 3 2 1 0<br />

ECCF0<br />

ECCF1<br />

ECCF2<br />

ECCF3<br />

ECCF4<br />

CCAP0H0<br />

CCAP1H0<br />

CCAP2H0<br />

CCAP3H0<br />

CCAP4H0<br />

CCAP0L0<br />

CCAP1L0<br />

CCAP2L0<br />

CCAP3L0<br />

CCAP4L0<br />

SCON 98h Serial Control FE/SM0 SM1 SM2 REN TB8 RB8 TI RI<br />

SBUF 99h Serial <strong>Data</strong> Buffer<br />

SADEN B9h Slave Address Mask<br />

SADDR A9h Slave Address<br />

BDRCON 9Bh Baud Rate Control BRR TBCK RBCK SPD SRC<br />

BRL 9Ah Baud Rate Reload<br />

Table 10. SPI Controller SFRs<br />

Mnemonic Add Name 7 6 5 4 3 2 1 0<br />

SPCON C3h SPI Control SPR2 SPEN SSDIS MSTR CPOL CPHA SPR1 SPR0<br />

SPSTA C4h SPI Status SPIF WCOL SSERR MODF - - - -<br />

SPDAT C5h SPI <strong>Data</strong> SPD7 SPD6 SPD5 SPD4 SPD3 SPD2 SPD1 SPD0<br />

7

Table 11. Two-Wire Interface Controller SFRs<br />

Mnemonic Add Name 7 6 5 4 3 2 1 0<br />

SSCON 93h Synchronous Serial control SSCR2 SSPE SSSTA SSSTO SSI SSAA SSCR1 SSCR0<br />

SSCS 94h Synchronous Serial Status SSC4 SSC3 SSC2 SSC1 SSC0 0 0 0<br />

SSDAT 95h Synchronous Serial <strong>Data</strong> SSD7 SSD6 SSD5 SSD4 SSD3 SSD2 SSD1 SSD0<br />

SSADR 96h Synchronous Serial Address SSA7 SSA6 SSA5 SSA4 SSA3 SSA2 SSA1 SSGC<br />

Table 12. Keyboard Interface SFRs<br />

Mnemonic Add Name 7 6 5 4 3 2 1 0<br />

KBLS 9Ch Keyboard Level Selector KBLS7 KBLS6 KBLS5 KBLS4 KBLS3 KBLS2 KBLS1 KBLS0<br />

KBE 9Dh Keyboard Input Enable KBE7 KBE6 KBE5 KBE4 KBE3 KBE2 KBE1 KBE0<br />

KBF 9Eh Keyboard Flag Register KBF7 KBF6 KBF5 KBF4 KBF3 KBF2 KBF1 KBF0<br />

8 <strong>AT89C51ID2</strong><br />

4289A–8051–09/03

Table 13. SFR Mapping<br />

F8h<br />

F0h<br />

E8h<br />

E0h<br />

D8h<br />

D0h<br />

C8h<br />

C0h<br />

B8h<br />

B0h<br />

A8h<br />

A0h<br />

98h<br />

90h<br />

88h<br />

80h<br />

4289A–8051–09/03<br />

Table below shows all SFRs with their address and their reset value.<br />

Bit<br />

addressable Non Bit addressable<br />

<strong>AT89C51ID2</strong><br />

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F<br />

PI2<br />

XXXX XX11<br />

B<br />

0000 0000<br />

P5 bit<br />

addressable<br />

1111 1111<br />

ACC<br />

0000 0000<br />

CCON<br />

00X0 0000<br />

PSW<br />

0000 0000<br />

T2CON<br />

0000 0000<br />

P4<br />

1111 1111<br />

IPL0<br />

X000 000<br />

P3<br />

1111 1111<br />

IEN0<br />

0000 0000<br />

P2<br />

1111 1111<br />

SCON<br />

0000 0000<br />

P1<br />

1111 1111<br />

TCON<br />

0000 0000<br />

P0<br />

1111 1111<br />

CH<br />

0000 0000<br />

CL<br />

0000 0000<br />

CMOD<br />

00XX X000<br />

FCON (1)<br />

XXXX 0000<br />

T2MOD<br />

XXXX XX00<br />

SADEN<br />

0000 0000<br />

IEN1<br />

XXXX X000<br />

SADDR<br />

0000 0000<br />

SBUF<br />

XXXX XXXX<br />

TMOD<br />

0000 0000<br />

SP<br />

0000 0111<br />

CCAP0H<br />

XXXX XXXX<br />

CCAP0L<br />

XXXX XXXX<br />

CCAPM0<br />

X000 0000<br />

EECON<br />

xxxx xx00<br />

RCAP2L<br />

0000 0000<br />

IPL1<br />

XXXX X000<br />

AUXR1<br />

XXXX X0X0<br />

BRL<br />

0000 0000<br />

TL0<br />

0000 0000<br />

DPL<br />

0000 0000<br />

CCAP1H<br />

XXXX XXXX<br />

CCAP1L<br />

XXXX XXXX<br />

CCAPM1<br />

X000 0000<br />

RCAP2H<br />

0000 0000<br />

SPCON<br />

0001 0100<br />

IPH1<br />

XXXX X111<br />

BDRCON<br />

XXX0 0000<br />

SSCON<br />

0000 0000<br />

TL1<br />

0000 0000<br />

DPH<br />

0000 0000<br />

CCAP2H<br />

XXXX XXXX<br />

CCAP2L<br />

XXXX XXXX<br />

CCAPM2<br />

X000 0000<br />

TL2<br />

0000 0000<br />

SPSTA<br />

0000 0000<br />

KBLS<br />

0000 0000<br />

SSCS<br />

1111 1000<br />

TH0<br />

0000 0000<br />

CCAP3H<br />

XXXX XXXX<br />

CCAP3L<br />

XXXX XXXX<br />

CCAPM3<br />

X000 0000<br />

TH2<br />

0000 0000<br />

SPDAT<br />

XXXX XXXX<br />

KBE<br />

0000 0000<br />

SSDAT<br />

1111 1111<br />

TH1<br />

0000 0000<br />

CKSEL<br />

XXXX XXX0<br />

CCAP4H<br />

XXXX XXXX<br />

CCAP4L<br />

XXXX XXXX<br />

CCAPM4<br />

X000 0000<br />

WDTRST<br />

XXXX XXXX<br />

KBF<br />

0000 0000<br />

SSADR<br />

1111 1110<br />

AUXR<br />

XX00 1000<br />

OSSCON<br />

XXXX X001<br />

P5 byte<br />

Addressable<br />

1111 1111<br />

IPH0<br />

X000 0000<br />

CKCON1<br />

XXXX XXX0<br />

WDTPRG<br />

XXXX X000<br />

CKRL<br />

1111 1111<br />

CKCON0<br />

0000 0000<br />

PCON<br />

00X1 0000<br />

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F<br />

Reserved<br />

FFh<br />

F7h<br />

EFh<br />

E7h<br />

DFh<br />

D7h<br />

CFh<br />

C7h<br />

BFh<br />

B7h<br />

AFh<br />

A7h<br />

9Fh<br />

97h<br />

8Fh<br />

87h<br />

9

Pin Configurations<br />

10 <strong>AT89C51ID2</strong><br />

P1.5/CEX2/MISO<br />

P1.6/CEX3/SCK<br />

P1.7/CEx4/MOSI<br />

RST<br />

P3.0/RxD<br />

PI2.1/SDA<br />

P3.1/TxD<br />

P3.2/INT0<br />

P3.3/INT1<br />

P3.4/T0<br />

P3.5/T1<br />

P1.4/CEX1<br />

P1.3/CEX0<br />

P1.2/ECI<br />

P1.1/T2EX/SS<br />

P1.0/T2/XTALB1<br />

XTALB2<br />

VCC<br />

P0.0/AD0<br />

P0.1/AD1<br />

P0.2/AD2<br />

P0.3/AD3<br />

6 5 4 3 2 1 44 43 42 41 40<br />

7<br />

39<br />

8<br />

38<br />

9<br />

37<br />

10<br />

36<br />

11<br />

12 <strong>AT89C51ID2</strong><br />

35<br />

34<br />

13 PLCC44<br />

33<br />

14<br />

32<br />

15<br />

31<br />

16<br />

30<br />

17<br />

29<br />

18 19 20 21 22 23 24 25 26 27 28<br />

P3.6/WR<br />

P3.7/RD<br />

XTAL2<br />

XTAL1<br />

VSS<br />

NIC*<br />

P2.0/A8<br />

P2.1/A9<br />

P2.2/A10<br />

P2.3/A11<br />

P2.4/A12<br />

P1.5/CEX2/MISO<br />

P1.6/CEX3/SCK<br />

P1.7/CEX4/MOSI<br />

RST<br />

P3.0/RxD<br />

PI2.1/SDA<br />

P3.1/TxD<br />

P3.2/INT0<br />

P3.3/INT1<br />

P3.4/T0<br />

P3.5/T1<br />

P0.4/AD4<br />

P0.5/AD5<br />

P0.6/AD6<br />

P0.7/AD7<br />

EA<br />

PI2.0/SCL<br />

ALE/PROG<br />

PSEN<br />

P2.7/A15<br />

P2.6/A14<br />

P2.5/A13<br />

P1.4/CEX1<br />

P1.3/CEX0<br />

P1.2/ECI<br />

P1.1/T2EX/SS<br />

P1.0/T2/XTALB1<br />

XTALB2<br />

VCC<br />

P0.0/AD0<br />

P0.1/AD1<br />

P0.2/AD2<br />

P0.3/AD3<br />

44 43 42 41 40 39 38 37 36 35 34<br />

1<br />

33<br />

2<br />

32<br />

3<br />

31<br />

4<br />

30<br />

5<br />

6<br />

7<br />

<strong>AT89C51ID2</strong><br />

VQFP44 1.4<br />

29<br />

28<br />

27<br />

8<br />

26<br />

9<br />

25<br />

10<br />

24<br />

11<br />

12 13 14 15 16 17 18 19 20 21 22<br />

23<br />

P3.6/WR<br />

P3.7/RD<br />

XTAL2<br />

XTAL1<br />

VSS<br />

NIC*<br />

P2.0/A8<br />

P2.1/A9<br />

P2.2/A10<br />

P2.3/A11<br />

P2.4/A12<br />

P0.4/AD4<br />

P0.5/AD5<br />

P0.6/AD6<br />

P0.7/AD7<br />

EA<br />

PI2.0/SCL<br />

ALE/PROG<br />

PSEN<br />

P2.7/A15<br />

P2.6/A14<br />

P2.5/A13<br />

4289A–8051–09/03

11<br />

<strong>AT89C51ID2</strong><br />

4289A–8051–09/03<br />

50<br />

49<br />

48<br />

47<br />

44<br />

45<br />

46<br />

P4.5<br />

P3.7/RD#<br />

XTAL2<br />

XTAL1<br />

P4.4<br />

P3.6/WR#<br />

P4.3<br />

NIC<br />

NIC<br />

P3.1/TxD<br />

P3.2/INT0#<br />

P3.3/INT1#<br />

P3.4/T0<br />

P3.5/T1<br />

37<br />

38<br />

39<br />

40<br />

41<br />

42<br />

43<br />

<strong>AT89C51ID2</strong><br />

PLCC68<br />

P0.4/AD4<br />

P5.4<br />

P5.3<br />

P0.5/AD5<br />

P0.6/AD6<br />

NIC<br />

P0.7/AD7<br />

EA#<br />

PI2.0/SCL<br />

ALE<br />

P1.6/CEX3/SCK<br />

P1.7/CEX4/MOSI<br />

RST<br />

NIC<br />

NIC<br />

NIC<br />

P3.0/RxD<br />

NIC<br />

SDA<br />

P1.5/CEX2/MISO<br />

60<br />

59<br />

58<br />

57<br />

56<br />

55<br />

54<br />

53<br />

51<br />

52<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

16<br />

17<br />

19<br />

18<br />

27<br />

28<br />

29<br />

30<br />

31<br />

32<br />

33<br />

34<br />

35<br />

36<br />

9<br />

8<br />

7<br />

6<br />

5<br />

3<br />

2<br />

1<br />

68<br />

P5.0<br />

P2.4/A12<br />

P2.3/A11<br />

P4.7<br />

P2.2/A10<br />

P4.6<br />

P2.0/A8<br />

P2.1/A9<br />

NIC<br />

VSS<br />

P5.5<br />

P0.3/AD3<br />

P0.2/AD2<br />

P5.6<br />

P0.1/AD1<br />

P0.0/AD0<br />

P5.7<br />

VCC<br />

XTALB2<br />

P1.0/T2/XTALB1<br />

4<br />

PSEN#<br />

NIC<br />

P2.7/A15<br />

P2.6/A14<br />

P5.2<br />

P5.1<br />

P2.5/A13<br />

67<br />

65<br />

64<br />

63<br />

62<br />

61<br />

66<br />

20<br />

21<br />

22<br />

23<br />

26<br />

25<br />

24<br />

P4.0<br />

P1.1/T2EX/SS#<br />

P1.2/ECI<br />

P1.3/CEX0<br />

P4.1<br />

P1.4/CEX1<br />

P4.2<br />

NIC: Not Internaly Connected<br />

54<br />

53<br />

52<br />

51<br />

50<br />

49<br />

<strong>AT89C51ID2</strong><br />

VQFP64<br />

P0.4/AD4<br />

P5.4<br />

P5.3<br />

P0.5/AD5<br />

P0.6/AD6<br />

P0.7/AD7<br />

EA#<br />

PI2.0/SCL<br />

ALE<br />

PSEN#<br />

P1.5/CEX2/MISO<br />

P1.6/CEX3/SCK<br />

P1.7/A17/CEX4/MOSI<br />

RST<br />

NIC<br />

NIC<br />

NIC<br />

P3.0/RxD<br />

SDA<br />

P4.2<br />

48<br />

47<br />

46<br />

45<br />

44<br />

43<br />

42<br />

41<br />

39<br />

40<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

8<br />

10<br />

9<br />

17<br />

18<br />

19<br />

20<br />

21<br />

22<br />

23<br />

24<br />

25<br />

26<br />

64<br />

63<br />

62<br />

61<br />

60<br />

59<br />

58<br />

57<br />

56<br />

55<br />

P2.4/A12<br />

P2.3/A11<br />

P4.7<br />

P2.2/A10<br />

P2.1/A9<br />

NIC<br />

P4.6<br />

P2.0/A8<br />

VSS<br />

P4.5<br />

P5.5<br />

P0.3/AD3<br />

P0.2/AD2<br />

P5.6<br />

P0.1/AD1<br />

P0.0/AD0<br />

P5.7<br />

VCC<br />

XTALB2<br />

P1.0/T2/XTALB1<br />

11<br />

12<br />

13<br />

16<br />

15<br />

14<br />

P4.0<br />

P1.1/T2EX/SS#<br />

P1.2/ECI<br />

P1.3/CEX0<br />

P4.1<br />

P1.4/CEX1<br />

38<br />

37<br />

36<br />

33<br />

34<br />

35<br />

P3.7/RD#<br />

XTAL2<br />

XTAL1<br />

P4.4<br />

P3.6/WR#<br />

P4.3<br />

NIC<br />

P3.1/TxD<br />

P3.2/INT0#<br />

P3.3/INT1#<br />

P3.4/T0<br />

P3.5/T1<br />

27<br />

28<br />

29<br />

30<br />

31<br />

32<br />

P2.7/A15<br />

P2.6/A14<br />

P5.2<br />

P5.1<br />

P2.5/A13<br />

P5.0

Table 14. Pin Description<br />

Mnemonic<br />

Pin Number<br />

PLCC44 VQFP44 PLCC68 VQFP64<br />

12 <strong>AT89C51ID2</strong><br />

Type<br />

Name and Function<br />

V SS 22 16 51 40 I Ground: 0V reference<br />

V CC 44 38 17 8 I<br />

P0.0 - P0.7 43 - 36 37 - 30<br />

P1.0 - P1.7 2 - 9 40 - 44<br />

1 - 3<br />

15, 14,<br />

12, 11,<br />

9,6, 5, 3<br />

19, 21,<br />

22, 23,<br />

25, 27,<br />

28, 29<br />

6, 5, 3, 2,<br />

64,<br />

61,60,59<br />

10, 12,<br />

13, 14,<br />

16, 18,<br />

19, 20<br />

2 40 19 10 I/O P1.0: Input/Output<br />

3 41 21 12 I/O P1.1: Input/Output<br />

I/O<br />

I/O<br />

Power Supply: This is the power supply voltage for normal, idle and<br />

power-down operation<br />

Port 0: Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have<br />

1s written to them float and can be used as high impedance inputs. Port 0<br />

must be polarized to V CC or V SS in order to prevent any parasitic current<br />

consumption. Port 0 is also the multiplexed low-order address and data bus<br />

during access to external program and data memory. In this application, it<br />

uses strong internal pull-up when emitting 1s. Port 0 also inputs the code<br />

bytes during EPROM programming. External pull-ups are required during<br />

program verification during which P0 outputs the code bytes.<br />

Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1<br />

pins that have 1s written to them are pulled high by the internal pull-ups<br />

and can be used as inputs. As inputs, Port 1 pins that are externally pulled<br />

low will source current because of the internal pull-ups. Port 1 also receives<br />

the low-order address byte during memory programming and verification.<br />

Alternate functions for <strong>AT89C51ID2</strong> Port 1 include:<br />

I/O T2 (P1.0): Timer/Counter 2 external count input/Clockout<br />

I XTALB1 (P1.0): Sub Clock input to the inverting oscillator amplifier<br />

I T2EX: Timer/Counter 2 Reload/Capture/Direction Control<br />

I SS: SPI Slave Select<br />

4 42 22 13 I/O P1.2: Input/Output<br />

I ECI: External Clock for the PCA<br />

5 43 23 14 I/O P1.3: Input/Output<br />

6 44 25 16 I/O P1.4: Input/Output<br />

7 1 27 18 I/O P1.5: Input/Output<br />

I/O CEX0: Capture/Compare External I/O for PCA module 0<br />

I/O CEX1: Capture/Compare External I/O for PCA module 1<br />

I/O CEX2: Capture/Compare External I/O for PCA module 2<br />

I/O MISO: SPI Master Input Slave Output line<br />

8 2 28 19 I/O P1.6: Input/Output<br />

When SPI is in master mode, MISO receives data from the slave peripheral.<br />

When SPI is in slave mode, MISO outputs data to the master controller.<br />

I/O CEX3: Capture/Compare External I/O for PCA module 3<br />

I/O SCK: SPI Serial Clock<br />

9 3 29 20 I/O P1.7: Input/Output:<br />

4289A–8051–09/03

Table 14. Pin Description (Continued)<br />

Mnemonic<br />

XTALA1 21 15 49 38 I<br />

4289A–8051–09/03<br />

I/O CEX4: Capture/Compare External I/O for PCA module 4<br />

I/O MOSI: SPI Master Output Slave Input line<br />

<strong>AT89C51ID2</strong><br />

When SPI is in master mode, MOSI outputs data to the slave peripheral.<br />

When SPI is in slave mode, MOSI receives data from the master controller.<br />

Crystal A 1: Input to the inverting oscillator amplifier and input to the internal<br />

clock generator circuits.<br />

XTALA2 20 14 48 37 O Crystal A 2: Output from the inverting oscillator amplifier<br />

XTALB1 2 40 10 19 I<br />

Crystal B 1: (Sub Clock) Input to the inverting oscillator amplifier and input<br />

to the internal clock generator circuits.<br />

XTALB2 1 39 9 18 O Crystal B 2: (Sub Clock) Output from the inverting oscillator amplifier<br />

P2.0 - P2.7 24 - 31 18 - 25<br />

P3.0 - P3.7 11,<br />

13 - 19<br />

P4.0 - P4.7<br />

P5.0 - P5.7<br />

5,<br />

7 - 13<br />

54, 55,<br />

56, 58,<br />

59, 61,<br />

64, 65<br />

34, 39,<br />

40, 41,<br />

42, 43,<br />

45, 47<br />

43, 44,<br />

45, 47,<br />

48, 50,<br />

53, 54<br />

25, 28,<br />

29, 30,<br />

31, 32,<br />

34, 36<br />

11 5 34 25 I RXD (P3.0): Serial input port<br />

13 7 39 28 O TXD (P3.1): Serial output port<br />

14 8 40 29 I INT0 (P3.2): External interrupt 0<br />

15 9 41 30 I INT1 (P3.3): External interrupt 1<br />

16 10 42 31 I T0 (P3.4): Timer 0 external input<br />

17 11 43 32 I T1 (P3.5): Timer 1 external input<br />

I/O<br />

I/O<br />

Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2<br />

pins that have 1s written to them are pulled high by the internal pull-ups<br />

and can be used as inputs. As inputs, Port 2 pins that are externally pulled<br />

low will source current because of the internal pull-ups. Port 2 emits the<br />

high-order address byte during fetches from external program memory and<br />

during accesses to external data memory that use 16-bit addresses (MOVX<br />

@DPTR).In this application, it uses strong internal pull-ups emitting 1s.<br />

During accesses to external data memory that use 8-bit addresses (MOVX<br />

@Ri), port 2 emits the contents of the P2 SFR.<br />

Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3<br />

pins that have 1s written to them are pulled high by the internal pull-ups<br />

and can be used as inputs. As inputs, Port 3 pins that are externally pulled<br />

low will source current because of the internal pull-ups. Port 3 also serves<br />

the special features of the 80C51 family, as listed below.<br />

18 12 45 34 O WR (P3.6): External data memory write strobe<br />

19 13 47 36 O RD (P3.7): External data memory read strobe<br />

- -<br />

- -<br />

Pin Number<br />

PLCC44 VQFP44 PLCC68 VQFP64<br />

20, 24,<br />

26, 44,<br />

46, 50,<br />

53, 57<br />

60, 62,<br />

63, 7, 8,<br />

10, 13,<br />

16<br />

11, 15,<br />

17,33,<br />

35,39,<br />

42, 46<br />

49, 51,<br />

52, 62,<br />

63, 1, 4,<br />

7<br />

Type<br />

I/O<br />

I/O<br />

Name and Function<br />

Port 4: Port 4 is an 8-bit bidirectional I/O port with internal pull-ups. Port 5<br />

pins that have 1s written to them are pulled high by the internal pull-ups<br />

and can be used as inputs. As inputs, Port 4 pins that are externally pulled<br />

low will source current because of the internal pull-ups.<br />

Port 5: Port 5 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3<br />

pins that have 1s written to them are pulled high by the internal pull-ups<br />

and can be used as inputs. As inputs, Port 5 pins that are externally pulled<br />

low will source current because of the internal pull-ups.<br />

13

Table 14. Pin Description (Continued)<br />

Mnemonic<br />

PI2.0 - PI2.1<br />

Pin Number<br />

PLCC44 VQFP44 PLCC68 VQFP64<br />

34, 12 28, 6 1, 36 57, 26<br />

34 28 1 57 I/O SCL (PI2.0): 2-wire Serial Clock<br />

12 6 36 26 I/O<br />

RST 10 4 30 21 I<br />

14 <strong>AT89C51ID2</strong><br />

Type<br />

Name and Function<br />

Port I2: Port I2 is an open drain. It can be used as inputs (must be polarized<br />

to Vcc with external resistor to prevent any parasitic current consumption).<br />

SCL output the serial clock to slave peripherals<br />

SCL input the serial clock from master<br />

SDA (PI2.1): 2-wire Serial <strong>Data</strong><br />

SDA is the bidirectional 2-wire data line<br />

Reset: A high on this pin for two machine cycles while the oscillator is running,<br />

resets the device. An internal diffused resistor to V SS permits a poweron<br />

reset using only an external capacitor to V CC. This pin is an output when<br />

the hardware watchdog forces a system reset.<br />

ALE/PROG 33 27 68 56 O (I) Address Latch Enable/Program Pulse: Output pulse for latching the low<br />

byte of the address during an access to external memory. In normal operation,<br />

ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator<br />

frequency, and can be used for external timing or clocking. Note that one<br />

ALE pulse is skipped during each access to external data memory. This pin<br />

is also the program pulse input (PROG) during Flash programming. ALE<br />

can be disabled by setting SFR’s AUXR.0 bit. With this bit set, ALE will be<br />

inactive during internal fetches.<br />

PSEN 32 26 67 55 O Program Strobe ENable: The read strobe to external program memory.<br />

When executing code from the external program memory, PSEN is activated<br />

twice each machine cycle, except that two PSEN activations are<br />

skipped during each access to external data memory. PSEN is not activated<br />

during fetches from internal program memory.<br />

EA 35 29 2 58 I External Access Enable: EA must be externally held low to enable the<br />

device to fetch code from external program memory locations 0000H to<br />

FFFFH. If security level 1 is programmed, EA will be internally latched on<br />

Reset.<br />

4289A–8051–09/03

Oscillators<br />

4289A–8051–09/03<br />

<strong>AT89C51ID2</strong><br />

Overview Two oscillators are available for CPU:<br />

OSCA used for high frequency: Up to 40 MHz<br />

OSCB used for low frequency: 32.768 kHz<br />

Several operating modes are available and programmable by software:<br />

to switch OSCA to OSCB and vice-versa<br />

to stop OSCA or OSCB to reduce consumption<br />

In order to optimize the power consumption and the execution time needed for a specific<br />

task, an internal prescaler feature has been implemented between the selected oscillator<br />

and the CPU.<br />

Registers Table 15. CKSEL Register<br />

CKSEL - Clock Selection Register (85h)<br />

7 6 5 4 3 2 1 0<br />

- - - - - - - CKS<br />

Bit<br />

Number<br />

Bit<br />

Mnemonic Description<br />

7 - Reserved<br />

6 - Reserved<br />

5 - Reserved<br />

4 - Reserved<br />

3 - Reserved<br />

2 - Reserved<br />

1 - Reserved<br />

0 CKS<br />

CPU Oscillator Select Bit: (CKS)<br />

Cleared, CPU and peripherals connected to OSCB<br />

Set, CPU and peripherals connected to OSCA<br />

Programmed by hardware after a Power-up regarding Hardware Security Byte<br />

(HSB).HSB.OSC (Default setting, OSCA selected)<br />

Reset Value = 0000 000’HSB.OSC’b (see Hardware Security Byte (HSB))<br />

Not bit addressable<br />

15

16 <strong>AT89C51ID2</strong><br />

Table 16. OSCCON Register<br />

OSCCON- Oscillator Control Register (86h)<br />

7 6 5 4 3 2 1 0<br />

- - - - - SCLKT0 OscBEn OscAEn<br />

Bit<br />

Number<br />

Bit<br />

Mnemonic Description<br />

7 - Reserved<br />

6 - Reserved<br />

5 - Reserved<br />

4 - Reserved<br />

3 - Reserved<br />

2 SCLKT0<br />

1 OscBEn<br />

0 OscAEn<br />

Reset Value = XXXX X0’HSB.OSC’’HSB.OSC’b (see Hardware Security Byte (HSB))<br />

Not bit addressable<br />

Table 17. CKRL Register<br />

CKRL - Clock Reload Register<br />

Reset Value = 1111 1111b<br />

Not bit addressable<br />

Sub Clock Timer0<br />

Cleared by software to select T0 pin<br />

Set by software to select T0 Sub Clock<br />

Cleared by hardware after a Power Up<br />

OscB enable bit<br />

Set by software to run OscB<br />

Cleared by software to stop OscB<br />

Programmed by hardware after a Power-up regarding HSB.OSC (Default<br />

cleared, OSCB stopped)<br />

OscA enable bit<br />

Set by software to run OscA<br />

Cleared by software to stop OscA<br />

Programmed by hardware after a Power-up regarding HSB.OSC(Default Set,<br />

OSCA runs)<br />

7 6 5 4 3 2 1 0<br />

- - - - - - - -<br />

Bit<br />

Number Mnemonic Description<br />

7:0 CKRL<br />

Clock Reload Register:<br />

Prescaler value<br />

4289A–8051–09/03

4289A–8051–09/03<br />

Table 18. PCON Register<br />

PCON - Power Control Register (87h)<br />

Reset Value = 00X1 0000b<br />

Not bit addressable<br />

<strong>AT89C51ID2</strong><br />

7 6 5 4 3 2 1 0<br />

SMOD1 SMOD0 - POF GF1 GF0 PD IDL<br />

Bit<br />

Number<br />

Bit<br />

Mnemonic Description<br />

7 SMOD1<br />

6 SMOD0<br />

5 -<br />

4 POF<br />

3 GF1<br />

2 GF0<br />

1 PD<br />

0 IDL<br />

Serial port Mode bit 1<br />

Set to select double baud rate in mode 1, 2 or 3.<br />

Serial port Mode bit 0<br />

Cleared to select SM0 bit in SCON register.<br />

Set to select FE bit in SCON register.<br />

Reserved<br />

The value read from this bit is indeterminate. Do not set this bit.<br />

Power-Off Flag<br />

Cleared to recognize next reset type.<br />

Set by hardware when VCC rises from 0 to its nominal voltage. Can also be set<br />

by software.<br />

General purpose Flag<br />

Cleared by software for general purpose usage.<br />

Set by software for general purpose usage.<br />

General purpose Flag<br />

Cleared by software for general purpose usage.<br />

Set by software for general purpose usage.<br />

Power-Down mode bit<br />

Cleared by hardware when reset occurs.<br />

Set to enter power-down mode.<br />

Idle mode bit<br />

Cleared by hardware when interrupt or reset occurs.<br />

Set to enter idle mode.<br />

17

Functional Block<br />

Diagram<br />

Figure 2. Functional Oscillator Block Diagram<br />

XtalA1<br />

XtalA2<br />

PwdOscA<br />

Operating Modes<br />

Reset A hardware RESET puts the Clock generator in the following state:<br />

Functional Modes<br />

OscA<br />

OscAEn<br />

OSCCON<br />

XtalB1<br />

XtalB2<br />

FOSCA<br />

PwdOscB<br />

18 <strong>AT89C51ID2</strong><br />

Reset<br />

:2<br />

OscB<br />

OscBEn<br />

OSCCON<br />

CKRL<br />

1<br />

0<br />

X2<br />

CKCON0<br />

The selected oscillator depends on OSC bit in Hardware Security Byte (HSB).<br />

HSB.OSC = 1 (Oscillator A selected)<br />

OscAEn = 1 & OscBEn = 0: OscA is running, OscB is stopped.<br />

CKS = 1: OscA is selected for CPU.<br />

HSB.OSC = 0 (Oscillator B selected)<br />

OscAEn = 0 & OscBEn = 1: OscB is running, OscA is stopped.<br />

CKS = 0: OscB is selected for CPU.<br />

CLK Peripheral Clock<br />

PERIPH<br />

Normal Modes CPU and Peripherals clock depend on the software selection using CKCON0,<br />

CKCON1 and CKRL registers<br />

CKS bit in CKSEL register selects either OscA or OscB<br />

CKRL register determines the frequency of the OscA clock.<br />

Reload<br />

8-bit<br />

Prescaler-Divider<br />

0<br />

1<br />

CKRL=0xFF?<br />

FOSCB<br />

1<br />

0<br />

CKS<br />

CKSEL<br />

Idle<br />

CLK<br />

CPU<br />

:128 Sub<br />

Clock<br />

CPU clock<br />

4289A–8051–09/03

4289A–8051–09/03<br />

<strong>AT89C51ID2</strong><br />

It is always possible to switch dynamically by software from OscA to OscB, and vice<br />

versa by changing CKS bit.<br />

Idle Modes IDLE modes are achieved by using any instruction that writes into PCON.0 bit (IDL)<br />

IDLE modes A and B depend on previous software sequence, prior to writing into<br />

PCON.0 bit:<br />

IDLE MODE A: OscA is running (OscAEn = 1) and selected (CKS = 1)<br />

IDLE MODE B: OscB is running (OscBEn = 1) and selected (CKS = 0)<br />

The unused oscillator OscA or OscB can be stopped by software by clearing<br />

OscAEn or OscBEn respectively.<br />

IDLE mode can be canceled either by Reset, or by activation of any enabled<br />

interruption<br />

In both cases, PCON.0 bit (IDL) is cleared by hardware<br />

Exit from IDLE modes will leave Oscillators control bits (OscEnA, OscEnB, CKS)<br />

unchanged.<br />

Power Down Modes POWER DOWN modes are achieved by using any instruction that writes into<br />

PCON.1 bit (PD)<br />

POWER DOWN modes A and B depend on previous software sequence, prior to<br />

writing into PCON.1 bit:<br />

Both OscA and OscB will be stopped.<br />

POWER DOWN mode can be cancelled either by a hardware Reset, an external<br />

interruption, or the keyboard interrupt.<br />

By Reset signal: The CPU will restart according to OSC bit in Hardware Security Bit<br />

(HSB) register.<br />

By INT0 or INT1 interruption, if enabled: (standard behavioral), request on Pads<br />

must be driven low enough to ensure correct restart of the oscillator which was<br />

selected when entering in Power down.<br />

By keyboard Interrupt if enabled: a hardware clear of the PCON.1 flag ensure the<br />

restart of the oscillator which was selected when entering in Power down.<br />

Table 19. Overview<br />

PCON.1 PCON.0 OscBEn OscAEn CKS Selected Mode Comment<br />

0 0 0 1 1<br />

0 0 1 1 1<br />

0 0 1 0 0<br />

0 0 1 1 0<br />

NORMAL MODE<br />

A, OscB stopped<br />

NORMAL MODE<br />

A, OscB running<br />

NORMAL MODE<br />

B, OscA stopped<br />

NORMAL MODE<br />

B, OscA running<br />

X X 0 0 X INVALID<br />

X X X 0 1 INVALID<br />

X X 0 X 0 INVALID<br />

Default mode after power-up or<br />

Warm Reset<br />

Default mode after power-up or<br />

Warm Reset + OscB running<br />

OscB running and selected<br />

OscB running and selected +<br />

OscA running<br />

OscA & OscB cannot be stopped<br />

at the same time<br />

OscA must not be stopped, as<br />

used for CPU and peripherals<br />

OscB must not be stopped as<br />

used for CPU and peripherals<br />

19

Design Considerations<br />

Oscillators Control PwdOscA and PwdOscB signals are generated in the Clock generator and used to<br />

control the hard blocks of oscillators A and B.<br />

PwdOscA =’1’ stops OscA<br />

PwdOscB =’1’ stops OscB<br />

The following tables summarize the Operating modes:<br />

Prescaler Divider A hardware RESET puts the prescaler divider in the following state:<br />

– CKRL = FFh: FCLK CPU = FCLK PERIPH = FOSCA /2 (Standard C51 feature)<br />

CKS signal selects OSCA or OSCB: F CLK OUT = FOSCA or FOSCB Any value between FFh down to 00h can be written by software into CKRL register<br />

in order to divide frequency of the selected oscillator:<br />

– CKRL = 00h: minimum frequency<br />

FCLK CPU = FCLK PERIPH = FOSCA /1020 (Standard Mode)<br />

FCLK CPU = FCLK PERIPH = FOSCA /510 (X2 Mode)<br />

– CKRL = FFh: maximum frequency<br />

FCLK CPU = FCLK PERIPH = FOSCA /2 (Standard Mode)<br />

FCLK CPU = FCLK PERIPH = FOSCA (X2 Mode)<br />

20 <strong>AT89C51ID2</strong><br />

Table 19. Overview (Continued)<br />

PCON.1 PCON.0 OscBEn OscAEn CKS Selected Mode Comment<br />

0 1 X 1 1 IDLE MODE A<br />

0 1 1 X 0 IDLE MODE B<br />

1 X X 1 X<br />

POWER DOWN<br />

MODE<br />

The CPU is off, OscA supplies the<br />

peripherals, OscB can be disabled<br />

(OscBEn = 0)<br />

The CPU is off, OscB supplies the<br />

peripherals, OscA can be disabled<br />

(OscAEn = 0)<br />

The CPU and peripherals are off,<br />

OscA and OscB are stopped<br />

PCON.1 OscAEn PwdOscA Comments<br />

0 1 0 OscA running<br />

1 X 1<br />

0 0 1<br />

OscA stopped by<br />

Power-down mode<br />

OscA stopped by<br />

clearing OscAEn<br />

PCON.1 OscBEn PwdOscB Comments<br />

0 1 0 OscB running<br />

1 X 1<br />

0 0 1<br />

OscB stopped by<br />

Power-down mode<br />

OscB stopped by<br />

clearing OscBEn<br />

4289A–8051–09/03

4289A–8051–09/03<br />

– FCLK CPU and FCLK PERIPH , for CKRL0xFF<br />

In X2 Mode:<br />

In X1 Mode:<br />

F CPU<br />

F CPU<br />

Timer 0: Clock Inputs Figure 3. Timer 0: Clock Inputs<br />

FCLK PERIPH :6<br />

T0 pin<br />

Sub Clock<br />

Gate<br />

INT0<br />

TR0<br />

0<br />

1<br />

SCLKT0<br />

OSCCON<br />

= FCLKPERIPH<br />

= FCLKPERIPH<br />

0<br />

1<br />

C/T<br />

TMOD<br />

F OSCA<br />

= ----------------------------------------------<br />

2 × ( 255 – CKRL)<br />

F OSCA<br />

= ----------------------------------------------<br />

4 × ( 255 – CKRL)<br />

Control<br />

Timer 0<br />

<strong>AT89C51ID2</strong><br />

Note: The SCLKT0 bit in OSCCON register allows to select Timer 0 Subsidiary clock.<br />

SCLKT0 = 0: Timer 0 uses the standard T0 pin as clock input (Standard mode)<br />

SCLKT0 = 1: Timer 0 uses the special Sub Clock as clock input, this feature can be use<br />

as periodic interrupt for time clock.<br />

21

Enhanced Features In comparison to the original 80C52, the <strong>AT89C51ID2</strong> implements some new features,<br />

which are:<br />

22 <strong>AT89C51ID2</strong><br />

X2 option<br />

Dual <strong>Data</strong> Pointer<br />

Extended RAM<br />

Programmable Counter Array (PCA)<br />

Hardware Watchdog<br />

SPI interface<br />

4-level interrupt priority system<br />

power-off flag<br />

ONCE mode<br />

ALE disabling<br />

Enhanced features on the UART and the timer 2<br />

X2 Feature The <strong>AT89C51ID2</strong> core needs only 6 clock periods per machine cycle. This feature<br />

called ‘X2’ provides the following advantages:<br />

Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.<br />

Save power consumption while keeping same CPU power (oscillator power saving).<br />

Save power consumption by dividing dynamically the operating frequency by 2 in<br />

operating and idle modes.<br />

Increase CPU power by 2 while keeping same crystal frequency.<br />

In order to keep the original C51 compatibility, a divider by 2 is inserted between the<br />

XTAL1 signal and the main clock input of the core (phase generator). This divider may<br />

be disabled by software.<br />

Description The clock for the whole circuit and peripherals is first divided by two before being used<br />

by the CPU core and the peripherals.<br />

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is<br />

bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.<br />

Figure 4 shows the clock generation block diagram. X2 bit is validated on the rising edge<br />

of the XTAL1÷2 to avoid glitches when switching from X2 to STD mode. Figure 5 shows<br />

the switching mode waveforms.<br />

Figure 4. Clock Generation Diagram<br />

XTAL1 2<br />

FXTAL<br />

XTAL1:2<br />

0<br />

1<br />

X2<br />

CKCON0<br />

F OSC<br />

CKRL<br />

8 bit Prescaler<br />

F CLK CPU<br />

F CLK PERIPH<br />

4289A–8051–09/03

Figure 5. Mode Switching Waveforms<br />

4289A–8051–09/03<br />

XTAL1<br />

XTAL1:2<br />

X2 bit<br />

CPU clock<br />

F OSC<br />

STD Mode X2 Mode<br />

STD Mode<br />

<strong>AT89C51ID2</strong><br />

The X2 bit in the CKCON0 register (see Table 20) allows a switch from 12 clock periods<br />

per instruction to 6 clock periods and vice versa. At reset, the speed is set according to<br />

X2 bit of Hardware Security Byte (HSB). By default, Standard mode is active. Setting the<br />

X2 bit activates the X2 feature (X2 mode).<br />

The T0X2, T1X2, T2X2, UartX2, PcaX2, and WdX2 bits in the CKCON0 register (See<br />

Table 20.) and SPIX2 bit in the CKCON1 register (see Table 21) allows a switch from<br />

standard peripheral speed (12 clock periods per peripheral clock cycle) to fast peripheral<br />

speed (6 clock periods per peripheral clock cycle). These bits are active only in X2<br />

mode.<br />

23

24 <strong>AT89C51ID2</strong><br />

Table 20. CKCON0 Register<br />

CKCON0 - Clock Control Register (8Fh)<br />

7 6 5 4 3 2 1 0<br />

TWIX2 WDX2 PCAX2 SIX2 T2X2 T1X2 T0X2 X2<br />

Bit<br />

Number<br />

Bit<br />

Mnemonic Description<br />

7 TWIX2<br />

6 WDX2<br />

5 PCAX2<br />

4 SIX2<br />

3 T2X2<br />

2 T1X2<br />

1 T0X2<br />

0 X2<br />

2-wire clock (This control bit is validated when the CPU clock X2 is set; when X2<br />

is low, this bit has no effect)<br />

Cleared to select 6 clock periods per peripheral clock cycle.<br />

Set to select 12 clock periods per peripheral clock cycle.<br />

Watchdog Clock<br />

(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br />

has no effect).<br />

Cleared to select 6 clock periods per peripheral clock cycle.<br />

Set to select 12 clock periods per peripheral clock cycle.<br />

Programmable Counter Array Clock<br />

(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br />

has no effect).<br />

Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br />

periods per peripheral clock cycle.<br />

Enhanced UART Clock (Mode 0 and 2)<br />

(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br />

has no effect).<br />

Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br />

periods per peripheral clock cycle.<br />

Timer2 Clock<br />

(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br />

has no effect).<br />

Cleared to select 6 clock periods per peripheral clock cycle.<br />

Set to select 12 clock periods per peripheral clock cycle.<br />

Timer1 Clock<br />

(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br />

has no effect).<br />

Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br />

periods per peripheral clock cycle.<br />

Timer0 Clock<br />

(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br />

has no effect).<br />

Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br />

periods per peripheral clock cycle.<br />

CPU Clock<br />

Cleared to select 12 clock periods per machine cycle (STD mode) for CPU and<br />

all the peripherals. Set to select 6clock periods per machine cycle (X2 mode) and<br />

to enable the individual peripherals’X2’ bits. Programmed by hardware after<br />

Power-up regarding Hardware Security Byte (HSB), Default setting, X2 is<br />

cleared.<br />

Reset Value = 0000 000’HSB. X2’b (See “Hardware Security Byte”)<br />

Not bit addressable<br />

4289A–8051–09/03

4289A–8051–09/03<br />

Table 21. CKCON1 Register<br />

CKCON1 - Clock Control Register (AFh)<br />

Reset Value = XXXX XXX0b<br />

Not bit addressable<br />

<strong>AT89C51ID2</strong><br />

7 6 5 4 3 2 1 0<br />

- - - - - - - SPIX2<br />

Bit<br />

Number<br />

Bit<br />

Mnemonic Description<br />

7 - Reserved<br />

6 - Reserved<br />

5 - Reserved<br />

4 - Reserved<br />

3 - Reserved<br />

2 - Reserved<br />

1 - Reserved<br />

0 SPIX2<br />

SPI (This control bit is validated when the CPU clock X2 is set; when X2 is low,<br />

this bit has no effect).<br />

Clear to select 6 clock periods per peripheral clock cycle.<br />

Set to select 12 clock periods per peripheral clock cycle.<br />

25

Dual <strong>Data</strong> Pointer<br />

Register DPTR<br />

Figure 6. Use of Dual Pointer<br />

26 <strong>AT89C51ID2</strong><br />

7<br />

AUXR1(A2H)<br />

The additional data pointer can be used to speed up code execution and reduce code<br />

size.<br />

The dual DPTR structure is a way by which the chip will specify the address of an external<br />

data memory location. There are two 16-bit DPTR registers that address the external<br />

memory, and a single bit called DPS = AUXR1.0 (see Table 22) that allows the program<br />

code to switch between them (Refer to Figure 6).<br />

0<br />

DPS<br />

DPTR1<br />

DPTR0<br />

DPH(83H) DPL(82H)<br />

External <strong>Data</strong> Memory<br />

4289A–8051–09/03

4289A–8051–09/03<br />

Table 22. AUXR1 register<br />

AUXR1- Auxiliary Register 1(0A2h)<br />

<strong>AT89C51ID2</strong><br />

7 6 5 4 3 2 1 0<br />

Bit<br />

Number<br />

- - ENBOOT - GF3 0 - DPS<br />

7 -<br />

6 -<br />

Reset Value: XXXX XX0X0b<br />

Not bit addressable<br />

Note: *Bit 2 stuck at 0; this allows to use INC AUXR1 to toggle DPS without changing GF3.<br />

ASSEMBLY LANGUAGE<br />

Bit<br />

Mnemonic Description<br />

5 ENBOOT<br />

4 -<br />

Reserved<br />

The value read from this bit is indeterminate. Do not set this bit.<br />

Reserved<br />

The value read from this bit is indeterminate. Do not set this bit.<br />

Enable Boot Flash<br />

Cleared to disable boot ROM.<br />

Set to map the boot ROM between F800h - 0FFFFh.<br />

Reserved<br />

The value read from this bit is indeterminate. Do not set this bit.<br />

3 GF3 This bit is a general purpose user flag. *<br />

2 0 Always cleared.<br />

1 -<br />

0 DPS<br />

Reserved<br />

The value read from this bit is indeterminate. Do not set this bit.<br />

<strong>Data</strong> Pointer Selection<br />

Cleared to select DPTR0.<br />

Set to select DPTR1.<br />

; Block move using dual data pointers<br />

; Modifies DPTR0, DPTR1, A and PSW<br />

; note: DPS exits opposite of entry state<br />

; unless an extra INC AUXR1 is added<br />

;<br />

00A2 AUXR1 EQU 0A2H<br />

;<br />

0000 909000MOV DPTR,#SOURCE ; address of SOURCE<br />

0003 05A2 INC AUXR1 ; switch data pointers<br />

0005 90A000 MOV DPTR,#DEST ; address of DEST<br />

0008 LOOP:<br />

0008 05A2 INC AUXR1 ; switch data pointers<br />

000A E0 MOVX A,@DPTR ; get a byte from SOURCE<br />

000B A3 INC DPTR ; increment SOURCE address<br />

000C 05A2 INC AUXR1 ; switch data pointers<br />

000E F0 MOVX @DPTR,A ; write the byte to DEST<br />

000F A3 INC DPTR ; increment DEST address<br />

0010 70F6JNZ LOOP ; check for 0 terminator<br />

0012 05A2 INC AUXR1 ; (optional) restore DPS<br />

27

28 <strong>AT89C51ID2</strong><br />

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1<br />

SFR. However, note that the INC instruction does not directly force the DPS bit to a particular<br />

state, but simply toggles it. In simple routines, such as the block move example,<br />

only the fact that DPS is toggled in the proper sequence matters, not its actual value. In<br />

other words, the block move routine works the same whether DPS is ’0’ or ’1’ on entry.<br />

Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in<br />

the opposite state.<br />

4289A–8051–09/03

Expanded RAM<br />

(XRAM)<br />

Figure 7. Internal and External <strong>Data</strong> Memory Address<br />

4289A–8051–09/03<br />

0FFh to 6FFh 0FFh<br />

00<br />

<strong>AT89C51ID2</strong><br />

The <strong>AT89C51ID2</strong> provides additional Bytes of random access memory (RAM) space for<br />

increased data parameter handling and high level language usage.<br />

<strong>AT89C51ID2</strong> devices have expanded RAM in external data space configurable up to<br />

1792bytes (see Table 23.).<br />

The <strong>AT89C51ID2</strong> has internal data memory that is mapped into four separate<br />

segments.<br />

The four segments are:<br />

1. The Lower 128 bytes of RAM (addresses 00h to 7Fh) are directly and indirectly<br />

addressable.<br />

2. The Upper 128 bytes of RAM (addresses 80h to FFh) are indirectly addressable<br />

only.<br />

3. The Special Function Registers, SFRs, (addresses 80h to FFh) are directly<br />

addressable only.<br />

4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and<br />

with the EXTRAM bit cleared in the AUXR register (see Table 23).<br />

The lower 128 bytes can be accessed by either direct or indirect addressing. The Upper<br />

128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy<br />

the same address space as the SFR. That means they have the same address, but are<br />

physically separate from SFR space.<br />

XRAM<br />

Upper<br />

128 bytes<br />

Internal<br />

Ram<br />

indirect accesses<br />

80h 80h<br />

7Fh<br />

00<br />

Lower<br />

128 bytes<br />

Internal<br />

Ram<br />

direct or indirect<br />

accesses<br />

0FFh<br />

Special<br />

Function<br />

Register<br />

direct accesses<br />

0FFFFh<br />

00FFh up to 06FFh<br />

0000<br />

External<br />

<strong>Data</strong><br />

Memory<br />

When an instruction accesses an internal location above address 7Fh, the CPU knows<br />

whether the access is to the upper 128 bytes of data RAM or to SFR space by the<br />

addressing mode used in the instruction.<br />

Instructions that use direct addressing access SFR space. For example: MOV<br />

0A0H, # data, accesses the SFR at location 0A0h (which is P2).<br />

Instructions that use indirect addressing access the Upper 128 bytes of data RAM.<br />

For example: MOV @R0, # data where R0 contains 0A0h, accesses the data byte<br />

at address 0A0h, rather than P2 (whose address is 0A0h).<br />

The XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared<br />

and MOVX instructions. This part of memory which is physically located on-chip,<br />

logically occupies the first bytes of external data memory. The bits XRS0 and XRS1<br />

are used to hide a part of the available XRAM as explained in Table 23. This can be<br />

29

30 <strong>AT89C51ID2</strong><br />

useful if external peripherals are mapped at addresses already used by the internal<br />

XRAM.<br />

With EXTRAM = 0, the XRAM is indirectly addressed, using the MOVX instruction in<br />

combination with any of the registers R0, R1 of the selected bank or DPTR. An<br />

access to XRAM will not affect ports P0, P2, P3.6 (WR) and P3.7 (RD). For<br />

example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H,<br />

accesses the XRAM at address 0A0H rather than external memory. An access to<br />

external data memory locations higher than the accessible size of the XRAM will be<br />

performed with the MOVX DPTR instructions in the same way as in the standard<br />

80C51, with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and<br />

read timing signals. Accesses to XRAM above 0FFH can only be done by the use of<br />

DPTR.<br />

With EXTRAM = 1 , MOVX @Ri and MOVX @DPTR will be similar to the standard<br />

80C51.MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0<br />

and any output port pins can be used to output higher order address bits. This is to<br />

provide the external paging capability. MOVX @DPTR will generate a sixteen-bit<br />

address. Port2 outputs the high-order eight address bits (the contents of DPH) while<br />

Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ Ri and<br />

MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7<br />

(RD).<br />

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and<br />

upper RAM) internal data memory. The stack may not be located in the XRAM.<br />

The M0 bit allows to stretch the XRAM timings; if M0 is set, the read and write pulses<br />

are extended from 6 to 30 clock periods. This is useful to access external slow<br />

peripherals.<br />

4289A–8051–09/03

Registers Table 23. AUXR Register<br />

AUXR - Auxiliary Register (8Eh)<br />

4289A–8051–09/03<br />

Reset Value = XX00 10’HSB. XRAM’0b<br />

Not bit addressable<br />

<strong>AT89C51ID2</strong><br />

7 6 5 4 3 2 1 0<br />

- - M0 XRS2 XRS1 XRS0 EXTRAM AO<br />

Bit<br />

Number<br />

7 -<br />

6 -<br />

Bit<br />

Mnemonic Description<br />

5 M0<br />

Reserved<br />

The value read from this bit is indeterminate. Do not set this bit.<br />

Reserved<br />

The value read from this bit is indeterminate. Do not set this bit.<br />

Pulse length<br />

Cleared to stretch MOVX control: the RD/ and the WR/ pulse length is 6 clock<br />

periods (default).<br />

Set to stretch MOVX control: the RD/ and the WR/ pulse length is 30 clock<br />

periods.<br />

4 XRS2 XRAM Size<br />

3 XRS1<br />

XRS2 XRS1XRS0XRAM size<br />

0 0 0 256 bytes<br />

0 0 1 512 bytes<br />

2 XRS0<br />

0<br />

0<br />

1<br />

1<br />

0 768 bytes(default)<br />

1 1024 bytes<br />

1 0 0 1792 bytes<br />

1 EXTRAM<br />

0 AO<br />

EXTRAM bit<br />

Cleared to access internal XRAM using movx @ Ri/ @ DPTR.<br />

Set to access external memory.<br />

Programmed by hardware after Power-up regarding Hardware Security Byte<br />

(HSB), default setting, XRAM selected.<br />

ALE Output bit<br />

Cleared, ALE is emitted at a constant rate of 1/6 the oscillator frequency (or 1/3 if<br />

X2 mode is used). (default) Set, ALE is active only during a MOVX or MOVC<br />

instruction is used.<br />

31

Reset<br />

Introduction The reset sources are : Power Management, Hardware Watchdog, PCA Watchdog and<br />

Reset input.<br />

32 <strong>AT89C51ID2</strong><br />

Figure 8. Reset schematic<br />

RST<br />

Power<br />

Monitor<br />

Hardware<br />

Watchdog<br />

PCA<br />

Watchdog<br />

Reset Input The Reset input can be used to force a reset pulse longer than the internal reset controlled<br />

by the Power Monitor. RST input has a pull-down resistor allowing power-on<br />

reset by simply connecting an external capacitor to V CC as shown in Figure 9. Resistor<br />

value and input characteristics are discussed in the Section “DC Characteristics” of the<br />

<strong>AT89C51ID2</strong> datasheet.<br />

Figure 9. Reset Circuitry and Power-On Reset<br />

RST<br />

R RST<br />

VSS<br />

a. RST input circuitry<br />

To internal reset<br />

Internal Reset<br />

VDD<br />

+<br />

RST<br />

b. Power-on Reset<br />

4289A–8051–09/03

Reset Output<br />

4289A–8051–09/03<br />

<strong>AT89C51ID2</strong><br />

As detailed in Section “Hardware Watchdog Timer”, page 108, the WDT generates a 96clock<br />

period pulse on the RST pin. In order to properly propagate this pulse to the rest of<br />

the application in case of external capacitor or power-supply supervisor circuit, a 1 kΩ<br />

resistor must be added as shown Figure 10.<br />

Figure 10. Recommended Reset Output Schematic<br />

VDD<br />

+<br />

VDD<br />

VSS<br />

RST<br />

1K<br />

RST<br />

<strong>AT89C51ID2</strong><br />

To other<br />

on-board<br />

circuitry<br />

33

Power Monitor The POR/PFD function monitors the internal power-supply of the CPU core memories<br />

and the peripherals, and if needed, suspends their activity when the internal power supply<br />

falls below a safety threshold. This is achieved by applying an internal reset to them.<br />

34 <strong>AT89C51ID2</strong><br />

By generating the Reset the Power Monitor insures a correct start up when<br />

<strong>AT89C51ID2</strong> is powered up.<br />

Description In order to startup and maintain the microcontroller in correct operating mode, V CC has<br />

to be stabilized in the V CC operating range and the oscillator has to be stabilized with a<br />

nominal amplitude compatible with logic level VIH/VIL.<br />

These parameters are controlled during the three phases: power-up, normal operation<br />

and power going down. See Figure 11.<br />

Figure 11. Power Monitor Block Diagram<br />

VCC<br />

Power On Reset<br />

Power Fail Detect<br />

Voltage Regulator<br />

XTAL1 (1)<br />

RST pin<br />

PCA<br />

Watchdog<br />

Hardware<br />

Watchdog<br />

Regulated<br />

Supply<br />

Internal Reset<br />

CPU core<br />

Memories<br />

Peripherals<br />

Note: 1. Once XTAL1 High and low levels reach above and below VIH/VIL. a 1024 clock<br />

period delay will extend the reset coming from the Power Fail Detect. If the power<br />

falls below the Power Fail Detect threshold level, the Reset will be applied<br />

immediately.<br />

The Voltage regulator generates a regulated internal supply for the CPU core the memories<br />

and the peripherals. Spikes on the external Vcc are smoothed by the voltage<br />

regulator.<br />

4289A–8051–09/03

Figure 12. Power Fail Detect<br />

Vcc<br />

4289A–8051–09/03<br />

Reset<br />

Vcc<br />

<strong>AT89C51ID2</strong><br />

The Power fail detect monitor the supply generated by the voltage regulator and generate<br />

a reset if this supply falls below a safety threshold as illustrated in the Figure 12<br />

below.<br />

When the power is applied, the Power Monitor immediately asserts a reset. Once the<br />

internal supply after the voltage regulator reach a safety level, the power monitor then<br />

looks at the XTAL clock input. The internal reset will remain asserted until the Xtal1 levels<br />

are above and below VIH and VIL. Further more. An internal counter will count 1024<br />

clock periods before the reset is de-asserted.<br />

If the internal power supply falls below a safety level, a reset is immediately asserted.<br />

t<br />

35

Timer 2 The Timer 2 in the <strong>AT89C51ID2</strong> is the standard C52 Timer 2.<br />

It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2<br />

and TL2 are cascaded. It is controlled by T2CON (Table 24) and T2MOD (Table 25)<br />

registers. Timer 2 operation is similar to Timer 0 and Timer 1.C/T2 selects F OSC /12<br />

(timer operation) or external pin T2 (counter operation) as the timer clock input. Setting<br />

TR2 allows TL2 to increment by the selected input.<br />

36 <strong>AT89C51ID2</strong><br />

Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These<br />

modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).<br />

Refer to the <strong>Atmel</strong> 8-bit Microcontroller Hardware description for the description of Capture<br />

and Baud Rate Generator Modes.<br />

Timer 2 includes the following enhancements:<br />

Auto-reload mode with up or down counter<br />

Programmable clock-output<br />

Auto-Reload Mode The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with automatic<br />

reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (refer to<br />

the <strong>Atmel</strong> C51 Microcontroller Hardware description). If DCEN bit is set, Timer 2 acts as<br />

an Up/down timer/counter as shown in Figure 13. In this mode the T2EX pin controls the<br />

direction of count.<br />

When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the<br />

TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value<br />

in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.<br />

When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the<br />

timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers.<br />

The underflow sets TF2 flag and reloads FFFFh into the timer registers.<br />

The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of<br />

the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit<br />

resolution.<br />

4289A–8051–09/03

Programmable Clock-<br />

Output<br />

4289A–8051–09/03<br />

Figure 13. Auto-Reload Mode Up/Down Counter (DCEN = 1)<br />

FCLK PERIPH :6<br />

0<br />

1<br />

T2<br />

C/T2 TR2<br />

T2CON T2CON<br />

<strong>AT89C51ID2</strong><br />

T2EX:<br />

(DOWN COUNTING RELOAD VALUE)<br />

if DCEN=1, 1=UP<br />

FFh FFh<br />

(8-bit) (8-bit)<br />

if DCEN=1, 0=DOWN<br />

if DCEN = 0, up counting<br />

TL2<br />

(8-bit)<br />

RCAP2L<br />

(8-bit)<br />

TH2<br />

(8-bit)<br />

RCAP2H<br />

(8-bit)<br />

(UP COUNTING RELOAD VALUE)<br />

TOGGLE<br />

In the clock-out mode, Timer 2 operates as a 50%-duty-cycle, programmable clock generator<br />

(See Figure 14). The input clock increments TL2 at frequency F CLK PERIPH /2.The<br />

timer repeatedly counts to overflow from a loaded value. At overflow, the contents of<br />

RCAP2H and RCAP2L registers are loaded into TH2 and TL2.In this mode, Timer 2<br />

overflows do not generate interrupts. The formula gives the clock-out frequency as a<br />

function of the system oscillator frequency and the value in the RCAP2H and RCAP2L<br />

registers:<br />

Clock– OutFrequency<br />

F CLKPERIPH<br />

=<br />

--------------------------------------------------------------------------------------------<br />

4 × ( 65536 – RCAP2H ⁄ RCAP2L )<br />

For a 16 MHz system clock, Timer 2 has a programmable frequency range of 61 Hz<br />

(FCLK PERIPH /2 16 ) to 4 MHz (FCLK PERIPH /4). The generated clock signal is brought out to<br />

T2 pin (P1.0).<br />

Timer 2 is programmed for the clock-out mode as follows:<br />

Set T2OE bit in T2MOD register.<br />

Clear C/T2 bit in T2CON register.<br />

Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L<br />

registers.<br />

Enter a 16-bit initial value in timer registers TH2/TL2.It can be the same as the<br />

reload value or a different one depending on the application.<br />

To start the timer, set TR2 run control bit in T2CON register.<br />

It is possible to use Timer 2 as a baud rate generator and a clock generator simultaneously.<br />

For this configuration, the baud rates and clock frequencies are not<br />

independent since both functions use the values in the RCAP2H and RCAP2L registers.<br />

TF2<br />

T2CON<br />

T2CON<br />

EXF2<br />

TIMER 2<br />

INTERRUPT<br />

37

38 <strong>AT89C51ID2</strong><br />

Figure 14. Clock-Out Mode C/T2 = 0<br />

T2EX<br />

FCLK PERIPH<br />

T2<br />

:6<br />

TR2<br />

T2CON<br />

Toggle<br />

Q D<br />

EXEN2<br />

T2CON<br />

TL2<br />

(8-bit)<br />

RCAP2L<br />

(8-bit)<br />

T2OE<br />

T2MOD<br />

EXF2<br />

T2CON<br />

TH2<br />

(8-bit)<br />

RCAP2H<br />

(8-bit)<br />

OVER-<br />

FLOW<br />

TIMER 2<br />

INTERRUPT<br />