Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Design and Realization of a Prototype Hardware Platform for ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

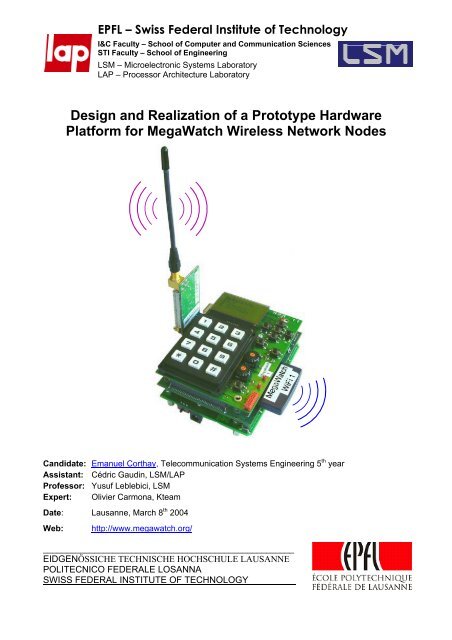

EPFL – Swiss Federal Institute <strong>of</strong> TechnologyI&C Faculty – School <strong>of</strong> Computer <strong>and</strong> Communication SciencesSTI Faculty – School <strong>of</strong> EngineeringLSM – Microelectronic Systems LaboratoryLAP – Processor Architecture Laboratory<strong>Design</strong> <strong>and</strong> <strong>Realization</strong> <strong>of</strong> a <strong>Prototype</strong> <strong>Hardware</strong><strong>Plat<strong>for</strong>m</strong> <strong>for</strong> MegaWatch Wireless Network NodesC<strong>and</strong>idate: Emanuel Corthay, Telecommunication Systems Engineering 5 th yearAssistant: Cédric Gaudin, LSM/LAPPr<strong>of</strong>essor: Yusuf Leblebici, LSMExpert: Olivier Carmona, KteamDate: Lausanne, March 8 th 2004Web:http://www.megawatch.org/______________________________________________________EIDGENÖSSICHE TECHNISCHE HOCHSCHULE LAUSANNEPOLITECNICO FEDERALE LOSANNASWISS FEDERAL INSTITUTE OF TECHNOLOGY

ProjectThe MegaWatch Wireless<strong>Plat<strong>for</strong>m</strong>TitleMaster's Thesis - Emanuel CorthayStatusVersion 1.0Keywordsmegawatch, wireless, plat<strong>for</strong>m, ad hoc, network,802.11, RF, hardware, transceiver, ARM, linux, watchExecutive SummaryThe MegaWatch project goal was to design <strong>and</strong> build a wireless network plat<strong>for</strong>m composed <strong>of</strong> 25prototype hardware units to experiment with self-organized, infrastructureless ad-hoc networks.Requirements included reconfigurable, autonomous, low power consumption, <strong>and</strong> powermeasurement capability. In the long term, it is intended that all the above functionality beintegrated in a small, watch size component.The design chosen was composed <strong>of</strong> five main blocks: two radio links, a power supply, extensionboard, <strong>and</strong> processing unit. An <strong>of</strong>f-the-shelf, XE-1202 digital radio circuit from Xemics wasselected as one radio link <strong>for</strong> low-power, short distance communications. A commercial wirelessLAN card, using the 802.11b st<strong>and</strong>ard protocol, provided a second independent monitoring radiolink. The power supply chosen was composed <strong>of</strong> three voltage regulators, a battery overdischargeprotection, <strong>and</strong> a power rectifier. The extension board supports both radio systems <strong>and</strong> contains ascreen, keyboard, buttons <strong>and</strong> LEDs to interact with the user. Two microcontrollers within theprocessor <strong>and</strong> extension board contain an ADC converter used <strong>for</strong> power measurements. The oneon the extension board also controls the LCD <strong>and</strong> keyboard <strong>of</strong> each unit. For maximum flexibility,the heart <strong>of</strong> the system is composed <strong>of</strong> an Altera Excalibur circuit, made up <strong>of</strong> an ARM9 system<strong>and</strong> a reprogrammable FPGA in a single chip.To run on the ARM9 system, the Linux operating system was selected. It was chosen <strong>for</strong> the gooddevelopment environment it provides, <strong>and</strong> the large number <strong>of</strong> free-s<strong>of</strong>tware applications <strong>and</strong>drivers available <strong>for</strong> it. The wireless LAN card, connected to the ARM processor, is accessiblefrom Linux to use the available wireless architecture as a monitoring network.A major component <strong>of</strong> this thesis was the design <strong>of</strong> a low level CSMA/CA based radio protocol <strong>for</strong>the short-range radio link. It was developed <strong>for</strong> low-data rate operations <strong>and</strong> implemented into theFPGA in VHDL. Six main functions were implemented including the transmission <strong>and</strong> reception <strong>of</strong>variable length payload frames <strong>of</strong> up 64 bytes, 2 FIFO buffers to store the payload, a CRC functionto detect erroneous transmission, as well as a hardware frame generator <strong>for</strong> ping <strong>and</strong> emergencymessage transmission. A 3-wire serial interface controller, used to program the external radiocircuit, was also part <strong>of</strong> the FPGA programming. During the FPGA design phase, importantper<strong>for</strong>mance parameters such as mode switching time <strong>and</strong> carrier detection system <strong>for</strong> the radiocircuit were identified.Fabrication <strong>of</strong> the 25 prototype two layer power supply <strong>and</strong> extension PCBs was done exclusivelyat EPFL, while the 12 layer main unit PCB was manufactured externally. A total <strong>of</strong> over 18,000components were ordered.Key future improvements include ad-hoc routing algorithms <strong>and</strong> application, power measurements<strong>and</strong> radio sub system protocol extensions. A Human-Machine-Interface will be developed usingthe keyboard <strong>and</strong> LCD to build a complete end user ad-hoc application.EPFL – Swiss Federal Institute <strong>of</strong> TechnologyCopyright © 2004 Emanuel Corthay – emanuel.corthay@a3.epfl.chPermission is granted to copy, distribute <strong>and</strong>/or modify this document under the terms <strong>of</strong> the GNUFree Documentation License, Version 1.2 or any later version published by the Free S<strong>of</strong>twareFoundation. A copy <strong>of</strong> the license is included at http://www.gnu.org/licenses/fdl.html

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay1 IntroductionTable <strong>of</strong> Contents1 INTRODUCTION 62 SCOPE AND PURPOSE 83 BACKGROUND 103.1 Today’s Wireless Network Systems 103.2 The Next Generation Ad-hoc Network Topology 103.3 Possible Applications 113.4 Existing St<strong>and</strong>ards 114 PROJECT GOALS 144.1 Long Term Vision 144.2 Master’s Thesis Work 165 PRELIMINARY RESEARCH 185.1 DoCoMo’s “Wristomo” Wristwatch mobile phone 185.2 Swatch GSM phone 195.3 Swatch Syncro Beat 195.4 Micros<strong>of</strong>t SPOT watches 195.5 WiseNET (CSEM) 195.6 BTNodes 205.7 Motes – TinyOS 205.7.1 UC Berkeley Motes (MICA) 205.7.2 Telos 802.15.4 Motes 215.8 IBM Linux Watch 215.9 MICS – Mobile In<strong>for</strong>mation <strong>and</strong> Communication Systems 226 THE MEGAWATCH HARDWARE PLATFORM DESIGN 246.1 Requirements 246.2 Overview 246.3 Main Processor Board 256.3.1 Introduction 256.3.2 <strong>Design</strong> choice 266.3.3 RokEPXA 276.4 Radio Links 286.4.1 Low Power Ad-hoc Link 286.4.2 WiFi Link 306.5 MegaWatch Extension Board 316.6 Power Measurement 346.7 Power Supply Boards 367 THE PROTOCOLS 383 / 81

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay1 Introduction7.1 Radio Protocol <strong>for</strong> the RF Circuit 387.1.1 Layer 1 – The Physical Layer ; Digital Modulation 397.1.2 Layer 2 – The Data Link Layer 417.1.3 Layer 3 – The Network Layer; Ad Hoc AODV 467.2 WiFi card : Wireless LAN 802.11b 467.3 Radio Circuit 3-wire Control Interface 467.4 Microcontroller Communication : I 2 C Interface 477.5 Conclusion 478 THE SOFTWARE 488.1 FPGA Radio Transceiver Core 488.1.1 Registers 498.1.2 Avalon Bus Controller 498.1.3 MAC Controller 508.1.4 Transmit Encoder 548.1.5 Receive Decoder 558.1.6 Transmitter <strong>and</strong> Receiver FIFO 568.1.7 Status Register 568.1.8 Control Register 578.1.9 CRC Generator <strong>and</strong> Decoder 588.1.10 R<strong>and</strong>om Number Generator 588.2 3-wire Control Core 588.3 Other Cores 608.4 Application S<strong>of</strong>tware 618.5 Microcontroller S<strong>of</strong>tware 618.6 Conclusion 619 THE MEGAWATCH PLATFORM FABRICATION 649.1 <strong>Design</strong> Phases 649.2 MegaWatch Extension Boards 659.3 Main Processor Board 679.4 Power Supply Board 689.5 Conclusion 6810 OPERATING SYSTEM 7011 AROUND THE PROJECT 7211.1 Project management 7211.2 Documents 7211.2.1 The MegaWatch Web Site 7211.2.2 Announcements 7211.3 Future <strong>of</strong> the Project 7211.3.1 Improvements 7211.3.2 Semester <strong>and</strong> Master projects 7312 CONCLUSION 7813 ACKNOWLEDGEMENTS 794 / 81

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay1 Introduction14 ABBREVIATIONS AND DEFINITIONS 8015 REFERENCES 8216 APPENDICESA. Component Selection Lista. MegaWatch Extension Boardb. Power Supplyc. RokEPXA_BB. Boards Schematicsd. MegaWatch Extension Boarde. Power Supplyf. RokEPXA_BC. PIN listD. Current Sense Resistors Estimated valuesE. Radio Core Detailed ViewF. Xemics Radio Circuit DatasheetG. VHDL Source CodeH. Development ToolsI. Partners In<strong>for</strong>mation5 / 81

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay1 Introduction1 IntroductionImagine wearing a watch that is more than just a watch. A watch that would be capable <strong>of</strong>exchanging in<strong>for</strong>mation with neighbouring watches. A watch that will locate your best friend youhave not seen in ages, <strong>and</strong> tell you he happens to be just around the corner, <strong>and</strong> send him ainvitation to join you <strong>for</strong> dinner right after lectures?This is the idea behind the MegaWatch project, a term project that spans beyond labs, faculty, <strong>and</strong>even EPFL; building a single low power chip with wireless capabilities that can go into a watch.This Master’s thesis work is but the first 6 months <strong>of</strong> this long term research project that will resultin 20 communicating prototype units, incorporating many different features to enable the researchef<strong>for</strong>ts <strong>of</strong> various EPFL laboratories. The challenge is to put together many different engineeringfields into a working prototype plat<strong>for</strong>m within a limited time <strong>and</strong> budget.Figure 1 The MegaWatch in the future every day’s life6 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay1 Introduction7 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay2 Scope <strong>and</strong> Purpose2 Scope <strong>and</strong> PurposeThe scope <strong>of</strong> the project is very wide. It is interdisciplinary, comprising many different engineeringfields (Electrical, Computer Science, Telecommunications …) as well as other less technicalengineering work (Project Management, Marketing, Business …). Several laboratories <strong>and</strong>different faculties at EPFL are involved, <strong>and</strong> industrial partners are interested in the project. Thepresented work is but a small piece <strong>of</strong> the whole, long term project, a snapshot <strong>of</strong> 6 months work.Thus, this document only focuses on the Master’s Thesis work done during that period <strong>of</strong> time. Itwill expose it from a high level system wide perspective. It is intended <strong>for</strong> people with engineeringskills in any discipline, <strong>of</strong>ten explaining concepts as they are used <strong>for</strong> people not familiar with them.A more in depth, thorough analysis <strong>of</strong> the different subjects involved is outside the scope <strong>of</strong> thisdocument <strong>and</strong> will be conducted later, this work being the starting point <strong>and</strong> enabler <strong>of</strong> research invarious fields.This paper is basically split into six sections:I. Introduction, background, project goalsII. Theoretical approach, design choices, protocolsIII. Practical hardware <strong>and</strong> s<strong>of</strong>tware implementationIV. Around the project, its future, conclusionV. Appendix. Practical in<strong>for</strong>mation to use the prototype units, as well as a description <strong>of</strong> thedevelopment tools can be found in this section.The document will describe the work done, explain the different design choices, encounteredproblems <strong>and</strong> challenges.The purpose <strong>of</strong> this document is to give answers to the following questions.• What is the MegaWatch project?• What are its challenges <strong>and</strong> long term research goals?• How does it work?• How can I use it <strong>for</strong> my own research?The document will continue to evolve after the Thesis report submission date. It will be taken bythe next people working on the project, in particular incorporate a rich user manual, <strong>and</strong>incorporate the work done by Cédric Gaudin, <strong>and</strong> semester project students.An abbreviations <strong>and</strong> definitions section at chapter 13 is available to help the reader throughout hisjourney into the description <strong>of</strong> this wireless communication system plat<strong>for</strong>m.8 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay2 Scope <strong>and</strong> Purpose9 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay3 Background3 BackgroundIn this section, today’s classical wireless network topology is presented, as well as the nextgeneration, with its possible applications. A quick overview <strong>of</strong> existing wireless st<strong>and</strong>ard ispresented.3.1 Today’s Wireless Network SystemsNowadays, almost all the wireless networks are infrastructure network. Each mobile unitcommunicates with an operator base station, the fixed infrastructure. Communications betweenmobile nodes, even if they are very close to each other, are not possible. The GSM cellular phonesystem [1] is a typical example <strong>of</strong> such an infrastructure, an operator maintained wireless network.The following picture shows how a transmission from one cell phone to another takes place. Evenwhen they are 1 meter apart from each other, the transmission always go through the base station,then the mobile operator fixed network concentrator <strong>and</strong> back to the second cell phone.MSCMobileStationBaseStationMSCMobileSwitchingCenterFigure 2 Cellular Phone Infrastructure Network3.2 The Next Generation Ad-hoc Network TopologyIn the Ad Hoc network topology, each unit can receive <strong>and</strong> transmit directly to its neighbours.Each unit then runs an ad-hoc algorithm to select the best route to reach a given destination,<strong>for</strong>warding a message from one unit to the other to the final recipient. Every node can act as arelay to <strong>for</strong>m a dense network.10 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay3 BackgroundFigure 3 A self-organized, Wireless Ad Hoc NetworkToday, there are no mass market products using this technique. But a lot <strong>of</strong> research is takingplace, <strong>and</strong> it will likely become tomorrow’s network architecture <strong>of</strong> choice.It is important to keep in mind that the infrastructure will not simply disappear. Rather, the sel<strong>for</strong>ganizednetwork will be used to access the nearest fixed wireless gateway. This gateway willlink the Ad-Hoc network with a larger, long-distance communication infrastructure when necessary.More in<strong>for</strong>mation on Ad-Hoc networks can be found in [2].3.3 Possible ApplicationsIf we succeed in providing watch size, wearable, distributed wireless communication nodes, thefollowing applications could become common in the future:• Support <strong>for</strong> helping people to meet (find them, determine who’s around)• Localisation <strong>and</strong> orientation(map, directions, emergency like avalanche, …)• Text messaging <strong>and</strong> paging• Local in<strong>for</strong>mation (cafeteria menu, on-site events, weather <strong>for</strong>ecast, e-shop, roomreservation, on-site white pages, …)• Revolutionary classroom support (instant polling, paperless course slides annotations, …)• Emergency call to anybody around• Address book <strong>and</strong> planner synchronisation/sharing3.4 Existing St<strong>and</strong>ardsSeveral wireless st<strong>and</strong>ards already exist, or are being actively developed.The largest wireless network in place is the well known GSM cell phone system. It reliesexclusively on an operator architecture, composed <strong>of</strong> many base stations distributed across acountry’s territory. Phone-to-phone wireless communications are not possible.The WiFi, or wireless LAN, based on the IEEE 802.11 st<strong>and</strong>ard is a popular wireless computernetwork. Today, most laptops come with an embedded wireless card. They can communicatedirectly with each other in Ad-Hoc mode, or with a base station that anyone can buy from acomputer reseller. A lot <strong>of</strong> experiments have already been conducted based on <strong>of</strong>f-the-self 802.11components, but their functionalities are limited to the st<strong>and</strong>ard. It is thus not possible to modifythe way they interact with each other to test new transmission systems. Moreover, they aredesigned <strong>for</strong> high speed data links, going up to 54 Mbps <strong>for</strong> recent models, <strong>and</strong> are not suitable <strong>for</strong>low-power applications.Bluetooth[3] is another st<strong>and</strong>ard, dedicated to very short distances, low data ratecommunications. It is intended as a replacement <strong>for</strong> cable connexions between devices at homeor in the <strong>of</strong>fice. Its range is limited to a maximum <strong>of</strong> 10 meters, <strong>and</strong> its data rate is <strong>of</strong> the order <strong>of</strong>11 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay3 Background200 Kbps. The power consumption is too high <strong>for</strong> our application. The protocol has a lot <strong>of</strong>overhead, <strong>and</strong> is not flexible enough to experiment with various Ad hoc protocols. It is <strong>for</strong> instancelimited to 8 units <strong>for</strong>ming a very small network, with one master <strong>and</strong> 7 slaves. Even though it ispossible to link together several such small networks in a so called tree squatternet network, moreadvanced topologies are not possible. For more in<strong>for</strong>mation, please consult [4].An emerging st<strong>and</strong>ard, the IEEE 802.15.4 [5] (also known as ZigBee [6]) is being activelydeveloped. It is intended specifically <strong>for</strong> low-speed (20 to 250 Kbps), low-power devices. Thespecifications are still in the draft phase, <strong>and</strong> no products were available <strong>for</strong> testing at thebeginning <strong>of</strong> this work. This is not true anymore, <strong>and</strong> as <strong>of</strong> February 2004, products compliant withthe draft version are starting to appear on the market. This st<strong>and</strong>ard should be closely monitoredin the future to see if it can be incorporated into MegaWatch as the wireless connectivity st<strong>and</strong>ardto support ad-hoc network applications.No existing solution was satisfactory to experiment <strong>and</strong> develop low-power, flexible Ad-Hocnetworks at the beginning <strong>of</strong> this work. Various testing hardware plat<strong>for</strong>ms (see section 5) havebeen developed in recent years, but do not meet the requirements set <strong>for</strong> this project in the nextsection.12 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay3 Background13 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay4 Project GoalsFuture Industrial Partners: CSEM, STI, Swatch- Technical Know-how- RF front-end- Market knowledge- Manufacturing <strong>and</strong> Packaging <strong>for</strong> large quantities- Costs optimization- MarketingA pole <strong>of</strong> competency has been <strong>for</strong>mally created under the name CSDA, Center <strong>for</strong> AdvancedDigital Systems. It incorporates most <strong>of</strong> the laboratories mentioned above, <strong>and</strong> some industrialpartners that are important <strong>for</strong> a lot <strong>of</strong> research <strong>and</strong> development projects involving hardware.That is because the gap between the academic <strong>and</strong> commercial perspective is important, <strong>and</strong> it is<strong>of</strong> great importance to work together to produce viable solutions to face tomorrow’s challenges.Network architecture:The envisioned MegaWatch network plat<strong>for</strong>m is a multi-tiered wireless network, composed <strong>of</strong> threelayers. In the campus environment, it can be described as follows:Layer 1:High-density network <strong>of</strong> low-cost, ultra-low-power MegaWatch intelligent terminals worn by everystudent. They communicate between themselves <strong>and</strong>/or with larger units acting as a gateway vialow-frequency data links.Layer 2:High per<strong>for</strong>mance mobile computing TermiNodes that act as computing plat<strong>for</strong>m <strong>and</strong> asintermediate jump-station (gateway) <strong>for</strong> wireless communication. Communication withMegaWatch(es) via low-frequency, with base-stations via high-frequency (WiFi 802.11b).Layer 3:Fixed wireless LAN (WLAN) base-stations operating on established st<strong>and</strong>ard 802.11b. Thisinfrastructure already exists at EPFL.What the project will bring:Figure 4 The proposed MegaWatch NetworkAs explained be<strong>for</strong>e, the project will create a pole <strong>of</strong> competency necessary to face tomorrowtechnical challenges. It will also provide a test plat<strong>for</strong>m <strong>for</strong> the following domains:- Reconfigurable <strong>Hardware</strong> to explore Ad hoc Algorithms <strong>and</strong> Protocols15 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay4 Project Goals- Wireless Security Experiments- Power Management, by exploring idleness detection techniques, dynamic voltage scaling<strong>and</strong> frequency scaling <strong>and</strong> power management policies- System-on-Chip, Network-on-Chip experiments- Applications <strong>and</strong> User Interface <strong>Design</strong>.Proposed Timetable:Figure 5 gives a possible project roll-out time plan:Figure 5 MegaWatch <strong>Prototype</strong>s IterationsFor more in<strong>for</strong>mation on long term goals, please consult [7] <strong>and</strong> [8].4.2 Master’s Thesis WorkAs explained be<strong>for</strong>e, the goal <strong>of</strong> this work is to develop the first MegaWatch prototype. It is mainlya technical development project that will enable a lot <strong>of</strong> ongoing research that has been waiting ona test plat<strong>for</strong>m to go further.The original project description was as follows:The goal <strong>of</strong> the Master’s thesis work is to build a low-power demonstration plat<strong>for</strong>m <strong>for</strong> ad-hocwireless network nodes. The prototype plat<strong>for</strong>m, part <strong>of</strong> a larger scientific research ef<strong>for</strong>t, willconsist <strong>of</strong> a low-power radio front-end, an reconfigurable logic unit with embedded processor(s),memory <strong>and</strong> a human-machine interface. Each prototype board will operate autonomously with itsown on-board battery, <strong>and</strong> will be capable <strong>of</strong> communicating with similar units in its receptionrange. Each unit will be required to keep an extended dynamic list <strong>of</strong> reachable-neighbour units,<strong>and</strong> to run an ad-hoc routing algorithm to receive <strong>and</strong> transmit individual data packets. The unitwill ideally be able to send time stamped event reports in real time via a 802.11b connexionintegrated on the board as a second radio link, thus allowing <strong>for</strong> independent per<strong>for</strong>manceevaluation <strong>of</strong> hardware <strong>and</strong> s<strong>of</strong>tware components (monitoring).16 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay4 Project GoalsThe RF front-end will be composed <strong>of</strong> a 433 MHz 20 kb/s data transceiver, under development atCSEM.Each unit processor will preferably run Linux so that a wide range <strong>of</strong> applications can eventually beported <strong>and</strong> implemented on this plat<strong>for</strong>m.By the end <strong>of</strong> the project, it is expected that about 20 identical units will be produced <strong>for</strong> real-timead-hoc network emulation <strong>and</strong> testing purposes.Proposed timetable:Month 1-2Month 2-3Month 4-5Month 6Discrete components prototype boards composed <strong>of</strong> the RF interface,the FPGA, micro controller <strong>and</strong> a simple I/O interfaceSelection <strong>of</strong> the components, construction <strong>of</strong> the first PCB board, debuggingFinal board design after debugging, communication protocol(radio MAC, synchronization, error correction, routing, etc.). Tests with 2+ nodesFull scale tests, demonstration, Masters' thesis reportThe first part will be mainly conducted at EPFL/LSM (1-2 months), <strong>and</strong> the second at CSEMNeuchâtel. Details regarding the internship at CSEM will be discussed at the beginning <strong>of</strong> theproject as to maximize efficiency <strong>and</strong> chances <strong>of</strong> success based on partners geographicallocalisation.In parallel to the thesis work, a reference manual will be written, <strong>and</strong> a web site constructed topublicise the project results.Updated Work Goals:The industrial partnership was cancelled shortly be<strong>for</strong>e the project started. Nonetheless, theproject did not suffer from this last minute change. Another radio circuit was selected, <strong>and</strong> thenecessary competency <strong>and</strong> material was available at EPFL.Personal goals:Some <strong>of</strong> the personal goals sought during the project include:- Work on a large scale <strong>and</strong> long term project involving team work with different partners,industrial if possible- Validate what I have learnt during my five years at EPFL by doing a hardware realizationthat involves many engineering fields- Gain greater project management <strong>and</strong> engineering skills- Continue to pursue my long term goal <strong>of</strong> building a versatile universal transceiver, projectthat was started by a semester project on s<strong>of</strong>tware defined radio17 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay5 Preliminary research5 Preliminary researchThis section gives a quick overview <strong>of</strong> existing projects that are similar to the MegaWatch. It is notan exhaustive product or project list. For each <strong>of</strong> them, we explain why they are not adapted to ourapplication requirements.For each presented product, the reader is invited to consult the given reference <strong>for</strong> morein<strong>for</strong>mation.5.1 DoCoMo’s “Wristomo” Wristwatch mobile phoneThis is the first commercial wristwatch-style cell phone on themarket (March 2003). Not surprisingly, it comes from Japan, acountry where people are willing to spend a lot <strong>of</strong> money onsuch devices.It is a waterpro<strong>of</strong> watch, that opens up into a functional Personal H<strong>and</strong>yphoneSystem (PHS) h<strong>and</strong>set when buttons on either side <strong>of</strong> the watch faceare pressed.The WRISTOMO is compatible with the "PALDIO E-mail" service, whichenables users to send/receive e-mails <strong>of</strong> up to 6,000 alphanumeric charactersvia the Internet without having to register with an Internet Service Provider.The wrist phone transfers data at up to 64 kbps. The WRISTOMO can accessthe "Browserphone Content" web pages <strong>of</strong> DoCoMo's service, as well as sitesbased on a subset <strong>of</strong> HTML, designed <strong>for</strong> mobile internet services. TheWRISTOMO is also equipped <strong>for</strong> DoCoMo's "Location based Web Sites,"which provide in<strong>for</strong>mation about restaurants, weather, transportation <strong>and</strong>other content based on the user's current location.The WRISTOMO comes with an in<strong>for</strong>mation synchronization feature thatautomatically exchanges in<strong>for</strong>mation with PCs, such as the address book ordaily planner. Whenever in<strong>for</strong>mation stored in the WRISTOMO or PC is changed, the other deviceis automatically updated either via the mobile Internet or an optional cable.Specifications <strong>of</strong> WRISTOMO:Height x Width x Thickness (mm) (when unfolded <strong>for</strong> h<strong>and</strong>set use) 171.5 x 40.4 x 18.5Weight (grams) Approx. 113 (including battery)Continuous talk time (minutes) Approx. 120Continuous st<strong>and</strong>-by time (hours) Approx. 200Data transmission speed 64 kbps/ 32 kbpsBody color Dark Gray MetallicA nice product, but not applicable <strong>for</strong> the MegaWatch application because PHS is an infrastructurest<strong>and</strong>ard which is not suited <strong>for</strong> ad hoc network experiments.18 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay5 Preliminary research5.2 Swatch GSM phoneDeveloped at Azulab, the Swatch group laboratory, this working watch GSMphone is only a prototype, <strong>and</strong> is not commercialized. Apparently, thegroup is not planning on launching this product at the moment <strong>for</strong> severalreasons.A nice product, but again it uses GSM which is not suited <strong>for</strong> ad hocnetwork experiments. In addition, as mentioned above, it is only at theprototype stage with no near term commercial prospects.5.3 Swatch Syncro BeatThis commercial product allows its possessor to exchange smallamounts <strong>of</strong> data between compatible watches using sounds.In<strong>for</strong>mation like business cards, alarms <strong>and</strong> melodies can betransmitted by pressing a button <strong>and</strong> maintaining the watches closeto each other. So called compatibility tests can be done, indicatinghow “compatible” the person is with its peer according to a certainnumber <strong>of</strong> criteria.In the same way, the watch can exchange data with a computerequipped with a sound card <strong>and</strong> a microphone.The wireless link is audio here, <strong>and</strong> cannot exceed a range <strong>of</strong> 1-2meters, making it unusable <strong>for</strong> our application.5.4 Micros<strong>of</strong>t SPOT watchesMicros<strong>of</strong>t's Smart Personal Objects Technology initiative aims to trans<strong>for</strong>meveryday small objects like watches, key chains <strong>and</strong> pens into intelligent,communicating devices. The watch “wrist net” project uses FM broadcast stationsto receive (only) the data modulated on a sub-carrier frequency, very similar to theEuropean Radio Data System (RDS).The first SPOT watches arrived in stores at the beginning <strong>of</strong> 2004, <strong>and</strong> <strong>of</strong>fer realtime weather <strong>and</strong> stock market in<strong>for</strong>mation, as well as paging capability. It comeswith a subscription system depending on what in<strong>for</strong>mation the user wants toreceive.This is a one-way, very low data rate wireless system that doesn’t fulfil our requirements.5.5 WiseNET (CSEM)The main objective <strong>of</strong> this research ef<strong>for</strong>t is to develop a low-power wireless ad-hoc network made<strong>of</strong> many distributed microsensors that are energetically autonomous (usually battery operated) <strong>and</strong>able to communicate amongst them <strong>and</strong> with the external world.Today, much <strong>of</strong> their ef<strong>for</strong>t is focused on developing a very low-power radio transceiver that canoperate from a single 1.5 V battery <strong>and</strong> last more than 5 years. The radio <strong>and</strong> the wireless protocol19 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay5 Preliminary researchare optimized <strong>for</strong> a very low duty cycle operation (typically a few percent). The radio transceiver isintegrated in a 0.18 µm st<strong>and</strong>ard digital CMOS process.Their research ef<strong>for</strong>t is more on RF front-end level, <strong>and</strong> the whole network is composed <strong>of</strong> verysmall units. They are limited to a very small memory size <strong>and</strong> computational power, <strong>and</strong> don’thave a usable product at the moment.For more in<strong>for</strong>mation, see [9]5.6 BTNodesThe BTnode is an autonomous wireless communication <strong>and</strong> computingplat<strong>for</strong>m based on a Bluetooth radio <strong>and</strong> a microcontroller. It serves asa demonstration plat<strong>for</strong>m <strong>for</strong> research in mobile <strong>and</strong> ad hoc connectednetworks <strong>and</strong> distributed sensor networks. It has been developed atETH Zurich [10].Specifications <strong>of</strong> the system:Microcontroller: Atmel ATmega 128L (8 MHz @ 8 MIPS)Memories: 64 Kbyte RAM, 128 Kbyte FLASH ROM, 4 Kbyte EEPROMBluetooth radio module, Ericsson ROK 101 007External Interfaces (ISP, UART, SPI, I2C, GPIO, ADC,...)4 LEDsSt<strong>and</strong>ard C ProgrammingBluetooth is not a viable solution <strong>for</strong> us, due to its limitations, as explained in 3.4.5.7 Motes – TinyOSTinyOS is an event based operating environment designed <strong>for</strong> use with embedded networkedsensors. More specifically, it is designed to support the concurrency intensive operations requiredby networked sensors with minimal hardware requirements. There are many TinyOS projectstaking place throughout the world, <strong>and</strong> a couple <strong>of</strong> hardware plat<strong>for</strong>m designed specifically to runthis OS. [11] The computational power is not sufficient <strong>for</strong> the envisaged MegaWatch application.5.7.1 UC Berkeley Motes (MICA)This sensor network system is based on an ATMega 128 microcontroller running at 4 MHz. Thememory is composed <strong>of</strong> a 512 K Flash, 4K <strong>of</strong> RAM <strong>and</strong> 128K <strong>for</strong> the program. The transceiver is aRFMTR1000 working at 915 MHz <strong>and</strong> 40 Kbps using ASK <strong>and</strong> has a 1 meter range. It comes withan extension sensor board.Figure 6 UC Berkley MotesThey also have a new SPEC prototype which is only a fraction <strong>of</strong> the size <strong>of</strong> the original.20 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay5 Preliminary researchThe radio range <strong>and</strong> computational power <strong>of</strong> this system is too small <strong>for</strong> our application.5.7.2 Telos 802.15.4 MotesThis is the first wireless circuit implementing the new IEEE 802.15.4 protocol. It was supposed tobe available in limited quantities at the beginning <strong>of</strong> 2004, but was not there at the beginning <strong>of</strong> theproject.More in<strong>for</strong>mation can be found at [12].Figure 7 Telos 802.15.4 Mote5.8 IBM Linux WatchAn IBM initiative to put Linux in a watch. It is not yet a commercial product, <strong>and</strong> no activity hasbeen reported on this project after 2001. The latest version includes a Bluetooth link.Figure 8 IBM Linux WatchWatch size 56mm x 48mm x 12mmWeight 44gCPU Low power 32-bit CPU (18-74 MHz)I/O device Touch panel, Roller wheelDisplay 96x120dots B/W STN LCD/VGA OLEDMemory DRAM 8MB, Flash 8MBCommunication Bluetooth (V1.0Bw/voice), IrDA (V1.2), UART (Cradle)Power Li-Polymer rechargeableOther Speaker, Mic, Buzzer, Tilt sensorCradle Charger, RS232C, AC-adapterOS Linux version 2.2, GUI X11R6Bluetooth stack IBM BlueDraker (L2CAP,SDP,RFCOMM)21 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay5 Preliminary research5.9 MICS – Mobile In<strong>for</strong>mation <strong>and</strong> Communication SystemsThis is not an existing product, but an interest group on wireless ad hoc networks. TheMegaWatch team keeps close ties with NIC members, who are eager to use the MegaWatchplat<strong>for</strong>m to test their theoretical results.Please consult their website at www.terminodes.org <strong>for</strong> more in<strong>for</strong>mation.22 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay5 Preliminary research23 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>Because existing hardware did not meet all <strong>of</strong> our requirements, a new plat<strong>for</strong>m has beendesigned. It is described theoretically in this chapter. The associated protocol, s<strong>of</strong>tware <strong>and</strong>realization is explained later in this document.6.1 RequirementsThe main requirements as stated in 4.2 are as follow:Build 20 autonomous, small <strong>for</strong>m factor wireless network units with the following characteristics:- A low-power radio interface to experiment with ad-hoc networks- A second independent radio link <strong>for</strong> real time monitoring <strong>of</strong> the units behavior- A powerful, easy to use, flexible processing unit to implement various communicationprotocols <strong>and</strong> applications- Power management <strong>and</strong> monitoring capabilities, <strong>for</strong> the radio subsystems as well as theprocessing unit- An intuitive, simple but yet powerful Human Machine interface to interact with the user- Several extension possibilitiesThe above must be achieved all within 6 months, thus requiring reuse <strong>of</strong> as much existing or <strong>of</strong>fthe-shelfhardware as possible. Financial constraints also influenced the design choices.6.2 OverviewThe units are separated into 5 main blocks, the 2 independent radio links supported by theMegaWatch extension board, the processor unit <strong>and</strong> the power supply. The RF link is the lowpowerradio system, whereas WiFi is the Wireless LAN link.UserRFMegaWatch Extension BoardCFWiFiMilli-BUSProcessor UnitA-BUSPower Supply BoardCircuitBoardExternalcomponentBusesFigure 9 MegaWatch Unit System Overview24 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>Each block is linked to the other via a bus. The two bus specifications are the result <strong>of</strong> team workamong students doing related projects at LAP. They are available on the MegaWatch website at[13] <strong>and</strong> [14].The Wireless LAN uses a st<strong>and</strong>ard Compact Flash (similar to PCMCIA) connector, <strong>and</strong> the RF isdirectly piggy-backed to the extension board.The processor unit used in this project is a revision <strong>of</strong> Cédric Gaudin’s original diploma work, theRokEPXA board. The RF <strong>and</strong> WiFi block are <strong>of</strong>f-the-shelf commercial products that we interfacedthrough the extension board to the system. The MegaWatch board has been entirely designed<strong>and</strong> built during this project. The power supply board is also an original work, but conducted jointlywith Cédric Gaudin.6.3 Main Processor Board6.3.1 IntroductionThe main board contains the heart <strong>of</strong> the system. It’s where the various data coming from theperipherals are analyzed <strong>and</strong> used according to a piece <strong>of</strong> s<strong>of</strong>tware that runs on a microprocessor.The s<strong>of</strong>tware can be st<strong>and</strong> alone or integrated within an operating system (OS). In the first case, itis compiled <strong>for</strong> the given processor or microcontroller architecture into fundamental instructionsexecuted sequentially. The developer must take care <strong>of</strong> everything. Moreover, having twodifferent applications running concurrently is not an easy task.By contrast, it can also be integrated within an OS. For more complex, integrated applications, theOS version is preferred, because a lot <strong>of</strong> features are made available to the developer throughst<strong>and</strong>ard, portable functions <strong>of</strong> the operating system.On embedded devices like the MegaWatch units, the available space, computational power <strong>and</strong>memory is a scarce resource. Thus, the OS <strong>and</strong> processor must be carefully chosen toaccommodate these special needs <strong>and</strong> use the available hardware as efficiently as possible. Atthe same time, the development must be as easy as possible <strong>for</strong> the developer.Another important thing to consider is the interface, or how to connect a given device to theprocessor. For advanced <strong>and</strong> wide-spread peripherals like memory, st<strong>and</strong>ard system bus definingthe electrical way to connect such a device to a processor exists. Examples include SDRAM, PCI,PCMCIA <strong>and</strong> CompactFlash. Most commercial processors then implement the bus directly on theprocessor through a certain number <strong>of</strong> specialized connections (referred to as PINs later in thisdocument), <strong>and</strong> include the associated controller on the chip. For less dem<strong>and</strong>ing peripherals,st<strong>and</strong>ard serial controllers <strong>for</strong> RS-232, I 2 C or SPI buses are usually integrated on most embeddedprocessors. That’s because they are very common <strong>for</strong> small peripherals like sensors, ADC <strong>and</strong>motors, or simply to communicate with a st<strong>and</strong>ard PC.This sounds like a very promising interface, but requires fairly complex peripherals with a controller<strong>for</strong> the given bus. At the same time, such a peripheral is usually composed <strong>of</strong> a monolithic, staticchip known as ASIC (Application-Specific Integrated Circuit). The advantage <strong>of</strong> these dedicatedchips is their low cost due to high volume manufacturing, <strong>and</strong> high speed, because the logic on thechip is dedicated to a certain task. On the other h<strong>and</strong>, if the features <strong>of</strong>fered do not meet therequirements <strong>for</strong> a system, there is no way to change them. That’s where an intermediate,reprogrammable solution comes into the picture. One such solution is an FPGA, or FieldProgrammable Gate Array. It not only <strong>of</strong>fers a flexible, custom interface solution, but can alsoimplement various programmable functions, as illustrated in figure 10.25 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>RFCustomPeripheralCustomInterface<strong>Hardware</strong>DataProcessingFPGASt<strong>and</strong>ardBusPeripheralsProcessorMemoryS<strong>of</strong>twareConfigurationFigure 10 General System PrincipleApplicationS<strong>of</strong>twareThe FPGA is basically composed <strong>of</strong> a large number <strong>of</strong> logical cells that can implementfundamental logic functions like logical gates, flip-flop <strong>and</strong> so on. Each cell is configured accordingto a static RAM memory that is loaded at startup from a configuration file sent to the chip. Theresult is a flexible hardware logic system with a s<strong>of</strong>tware component to configure the embeddedlogic. The FPGA also has drawbacks. It is generally more expensive than an ASIC solution <strong>for</strong>large production, consumes more power (the configuration memory essentially) <strong>and</strong> runs at lowerfrequency than an ASIC version (fixed wired network). But such a system is very powerful to test adesign (prototyping) be<strong>for</strong>e mass production, or <strong>for</strong> custom, low volume solutions. The reason issimple: you can program a complete system in s<strong>of</strong>tware that you want your hardware FPGA logicgates to do, <strong>and</strong> if it does not work as expected, you can simply change the code! The advantage<strong>of</strong> the s<strong>of</strong>tware approach (its flexibility) <strong>and</strong> <strong>of</strong> the hardware approach (its fast speed <strong>for</strong> dedicatedtasks) is thus united in a single FPGA circuit.For our application, where flexibility is a requirement, an FPGA solution is ideal. The radiosubsystem can be programmed into this FPGA, changed <strong>and</strong> tested at will. Also, once a goodradio subsystem runs on the FPGA, a real hardware, gate-level circuit design can be createdautomatically from the FPGA configuration s<strong>of</strong>tware, <strong>and</strong> integrated later as part <strong>of</strong> a dedicatedASIC circuit.6.3.2 <strong>Design</strong> choiceAltera has a chip family called Excalibur with the nice property <strong>of</strong> having both an FPGA <strong>and</strong>complete ARM9 processor system in a single chip. It also has the appropriate <strong>and</strong> integrated toolsto easily combine an FPGA <strong>and</strong> ARM design into a powerful <strong>and</strong> versatile system.Moreover, a Linux distribution <strong>for</strong> the ARM processor architecture exists <strong>and</strong> is being activelydeveloped as a joint <strong>and</strong> distributed free s<strong>of</strong>tware ef<strong>for</strong>t around the globe. This last argument setthe operating system that will be used to Linux as the application development environment.The selected Altera Excalibur ARM EPXA1F484C3 [15] chip has the following characteristics:• An ARM922T processor running at 133 MHz• A SDRAM SDR <strong>and</strong> DDR memory controller (512 Mo max)• Internal 32 Ko SRAM memory• Internal 16 Ko double access SRAM memory• External memory interface <strong>of</strong> maximum 4 times 32 Mo• Interrupt controller, UART <strong>and</strong> timers• FPGA with 100’000 logical gates running at 24 MHz26 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>It is very important to distinguish between the reconfigurable part <strong>of</strong> the Excalibur, <strong>and</strong> its VLSIARM part. The reconfigurable part, the FPGA, composed <strong>of</strong> hardware logic can host manydifferent systems, known as cores, according to a loaded s<strong>of</strong>tware configuration. Because itcontains both a s<strong>of</strong>tware <strong>and</strong> hardware component, it is commonly called “s<strong>of</strong>t-core” where as theVLSI part, burnt <strong>for</strong> once <strong>and</strong> <strong>for</strong> all into the chip, is called “hard-core.” These two componentsinteract with each other through a bridge, present on the chip.Building a Printed Circuit Board (PCB) to link the different hardware circuits <strong>for</strong> the Excalibur is alot <strong>of</strong> work. Fortunately, it has been successfully realized in Cédric Gaudin’s Master’s thesis workin March 2003 [16]. The card was named RokEPXA. A slightly modified version, called revision B,<strong>of</strong> Cédric’s original design was made. The main new feature is the addition <strong>of</strong> a powermeasurement device explained in 6.6.6.3.3 RokEPXAThe general architecture <strong>of</strong> the RokEPXA board is as follow:JTAGProgrammingInterfaceRS232PowerMeasurementAlteraExcaliburI 2 CA BUSPowerSupplySDRAMMemory64 MBExtensionConnectorsARMBridgeFPGAI 2 CSerial BusFlashMemory8 MBUSBConnectorFigure 11 RokEPXA rev. B OverviewMilli BUSMegaWatchExtensionThe memory controller <strong>of</strong> the Excalibur is connected to the two memories. An internal UARTpresent on the ARM part <strong>of</strong> the Excalibur provides a serial RS-232 interface. The lines dedicatedto the FPGA are connected to various connectors. Around 60 <strong>of</strong> them are connected to the Milli-Bus, allowing an extension board to be piggy-backed on top <strong>of</strong> the main board.The programming <strong>and</strong> debugging interface to the ARM <strong>and</strong> FPGA are accessible on the boardthough a dedicated connector. The same is true <strong>for</strong> the microcontroller used <strong>for</strong> the powermeasurement, as explained in Chapter 6.6.The ARM processor comes with a bus to link it with external peripherals named AHB. The ARMspecifications provide in<strong>for</strong>mation as to how to communicate on this bus. Two versions <strong>of</strong> this busare present on the Altera Excalibur chip. The first one, AHB1, is directly connected to the memory27 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>controller. The ARM is the only master on the bus. The second one, AHB2, is slower <strong>and</strong> is usedto connect to the different peripherals. In particular, it integrates the two bridges to the FPGA, one<strong>for</strong> the communication from the FPGA to the ARM, <strong>and</strong> one <strong>for</strong> the communication from the ARMto the FPGA. Figure 12 illustrates the internal structure <strong>of</strong> the Excalibur.ARM922TInterruptControllerWatchdogTimerSDRAMMemoryControllerUART(Flash)EBISlaveAHB1-2BridgeMasterAHB1ConfigurationLogicMasterAHB2MasterBridgeDPRAM1x16KoSRAM2x16Ko2xPLLResetmodule2xTimerSlaveBridgeSlaveMasterFPGAFigure 12 Internal Excalibur StructureFor more in<strong>for</strong>mation, see Cédric Gaudin’s report [16]. For more in<strong>for</strong>mation on the manufacturing<strong>of</strong> the cards, see 9.3.The electrical schematic is available in the appendix, as well as the physical line schematic,realized at EPFL/ACORT by George Vaucher.6.4 Radio Links6.4.1 Low Power Ad-hoc LinkBuilding a br<strong>and</strong> new radio circuit is a huge task. While digital systems, only attempting torecognize 1 from 0, tend to accommodate signal degradations, working with analog high frequencycomponents requires careful design. A good knowledge <strong>of</strong> issues related to this very sensitivespecialized field is necessary. The critical issue is related to the electromagnetic field effect. Athigh frequencies, strong signal interferences appear in adjacent lines, creating crosstalk problems.Bad impedance matching on lines creates reflected waves, further degrading the signal. To avoidthis problem, all lines must be matched to a given impedance. Sensitivity, linked to the noise in thesystem becomes a vital point, is one <strong>of</strong> the most important per<strong>for</strong>mance parameters <strong>of</strong> an RFcircuit.28 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>Even though experience is this field exists [17], it would be a Master’s thesis work in itself.Furthermore, the integration <strong>of</strong> an analog part in a single SoC solution comes later in this long termproject anyways. For all these reasons, it was decided that a commercial <strong>of</strong>f-the-shelf productwould be used <strong>for</strong> this first prototype in the <strong>for</strong>m <strong>of</strong> a mounted development kit. This approach alsominimizes the risks <strong>and</strong> speeds up the prototyping process, in order to have a first working solutionas a pro<strong>of</strong>-<strong>of</strong>-concept be<strong>for</strong>e going further in the project.Several products were considered <strong>and</strong> compared. Some <strong>of</strong> their characteristics are shown inTable 1 below. The first priority was to have a small power consumption. That includes theconsumption in transmit mode, but also in receive mode, <strong>and</strong> most importantly, in idle mode. Theraw transmission power, usually adaptable, is not the main criteria.The link frequency <strong>and</strong> speed is also <strong>of</strong> great importance. In general, when the carrier frequencyincreases, the power required to transmit increases as well, but so does the available throughput.For a given low volume traffic, if the speed is too slow, the latency time is greater, <strong>and</strong> theprobability <strong>of</strong> having two nodes transmitting at the same time, called a collision, is higher, becauseeach individual transmission lasts longer. On the other end, with a fast transmission, the radi<strong>of</strong>requency becomes free much faster after a transmission, reducing the number <strong>of</strong> requiredretransmissions because <strong>of</strong> collisions, thus reducing the overall power consumption. Several otherfactors also influence the power consumption <strong>of</strong> a radio systems, tightly linked to its per<strong>for</strong>mance.The best choice is thus not obvious. It is a question <strong>of</strong> which trade<strong>of</strong>f is the best <strong>for</strong> a givenapplication. More in<strong>for</strong>mation can be found in [18].Table 1 RF Chip ComparisonIn a previous semester project at LSM, the Nordic circuit was used. But its raw, unsynchronizedoutput makes the usage <strong>of</strong> a bit synchronizer in hardware outside the chip necessary. By contrast,both the Xemics <strong>and</strong> Chipcon circuits have a synchronized output <strong>and</strong> better per<strong>for</strong>mance, as wellas extra features like Received Signal Strength Indication (RSSI). The Chipcon chip has a betteroutput power <strong>and</strong> RSSI selection granularity, some extra power management <strong>and</strong> encodingfeatures <strong>and</strong> a faster data rate. The Xemics chip has a built-in pattern recognition system whichsends a signal when a certain synchronization bit sequence is received. The rest <strong>of</strong> the system isthus discharged <strong>of</strong> this task, saving power <strong>and</strong> programming time. It is to be noted that Xemics isa Swiss company, a spin-<strong>of</strong>f <strong>of</strong> CSEM in Neuchâtel, with which we have good contact. This is <strong>of</strong>significant importance, <strong>and</strong> can give the project team a competitive advantage when it comes tointegrating it into a single chip.It is not possible to clearly identify a winner between the Chipcon <strong>and</strong> the Xemics chip. Eventually,the Xemics development kit XM-1202 [20] available immediately was chosen. Its maincharacteristics are:• Programmable RF output power, max 15 dBm• High reception sensitivity down to –116 dBm• Low power consumption, RX 14 mA, TX 48 mA• Data rate from 4.8 to 76.8 Kbps• On chip frequency synthesizer, bit synchronization <strong>and</strong> pattern recognition29 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>• Received signal strength indicator• 2-level FSK digital modulation• Maximum range around 100 meters in buildings <strong>for</strong> low speed, high power transmissionFigure 13 Xemics XM-1202 Development Kit6.4.2 WiFi LinkFor simplicity, it was obvious that a simple <strong>of</strong>f-the-shelf CompactFlash Wireless LAN card(802.11b) would be perfect to serve as a real time monitoring wireless interface. The infrastructureavailable at EPFL (WiFi base stations) is already present; Linux drivers exist; <strong>and</strong> low cost highvolume WiFi components are very easy to find.Table 2 WiFi Compact Flash Card ComparisonThe difficulty at this stage was to integrate it into the system. Not surprisingly, given the 2.4 GHzhigh frequency used, it was shown that the antenna part <strong>of</strong> the Compact Flash card must be clear<strong>of</strong> all obstacles <strong>for</strong> the link to work. In particular, if a ground plane is close to the antenna, the linkdoes not work. The antenna part <strong>of</strong> the card has been placed as to stick out <strong>of</strong> the unit to avoidthat problem.A lot <strong>of</strong> the referenced cards below were discarded <strong>for</strong> various reasons, <strong>and</strong> in the remaining lot,the Pretec was chosen simply because it had been successfully tested in the LSA2 EPFLlaboratory during the Swarm-BOT project[20] in similar conditions, <strong>and</strong> under ARM Linux.Moreover, we were able to get a good price by joining the order <strong>of</strong> WiFi cards <strong>for</strong> the two projects.30 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>Figure 14 Pretec WiFi CardIts main characteristics are:• CompactFlash connector type I• 802.11b DSSS at 11, 5.5, 2 or 1 Mbps, max 14 dBm output power• Power consumption max 370 mA in transmit mode, 250 mA in receive mode <strong>and</strong> 20 mA inst<strong>and</strong>by mode• Linux drivers available <strong>for</strong> the Intersil Prism 2.5 integrated chipsetThe purpose <strong>of</strong> the WiFi card is threefold:• Provide an independent radio link <strong>for</strong> monitoring purposes• Provide a bridge possibility with the infrastructure network, thus providing a bridge to theinternet• Be available as a second radio interface <strong>for</strong> 802.11b ad hoc applications <strong>and</strong> testing6.5 MegaWatch Extension BoardThe extension card supports three major functions <strong>of</strong> the system. It must provide a practicalinterface to plug the two radio link modules, provide an easy-to-use Human-Machine-Interface, <strong>and</strong>integrate a power measurement circuit.The Figure 15 shows the general structure <strong>of</strong> the board. Each part is then discussed separately togive a good underst<strong>and</strong>ing <strong>of</strong> the design choices.31 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>RFButtonsLEDsLCD96 x 40Keyboard4 x 3AddressSelectorBuzzerMilli-BUSPowerSupplyCFButtonsLEDsADCuCVoltageReferenceI 2 Cserial busFPGAARMCircuitBoardExternalcomponentWiFiOnboardComponentFigure 15 MegaWatch Extension Board OverviewThe Compact Flash interface (CF) [21] is straight <strong>for</strong>ward, <strong>and</strong> is composed <strong>of</strong> a Compact Flashconnector placed under the extension board, at the right position to allow the antenna part <strong>of</strong> thecard to stick out <strong>of</strong> the unit.The RF link extension kit comes with a st<strong>and</strong>ard 20 male poles. A female version was simplyintegrated on one side <strong>of</strong> the extension board, providing the necessary power <strong>and</strong> signal lines tothe FPGA.For the Human-Machine-Interface, a 96 by 40 dot graphic LCD from Batron[22] was chosen. Itsmain advantage, aside from its graphical capabilities, is the fact that it comes with an integrated I 2 Cserial bus controller. This means that only two wires (aside from the power lines) need to beconnected to the device, <strong>and</strong> that these two wires are shared among several devices, thusreducing the overall required number <strong>of</strong> lines.The I 2 C is also used by a Cygnal 8051 F311 microcontroller[23] to transmit the currentmeasurement to the rest <strong>of</strong> the system, as explained in 6.6.This microcontroller is also used to detect the key pressed on the relatively small 4 by 3 keynumerical keyboard, similar to those <strong>of</strong> a telephone integrated on the board. Six <strong>of</strong> the buttons arealso directly linked to the microcontroller, as well as 4 LEDs. The big advantage <strong>of</strong> this choice isthat these components are independent <strong>of</strong> the FPGA, managed locally directly by thismicrocontroller. An other big advantage is that events that need to be sent to the FPGA or theprocessor, such as key pressed, can be multiplexed on the I 2 C bus, which in turns is connected tothe rest <strong>of</strong> the system through the FPGA. The result is a reduction <strong>of</strong> used FPGA lines <strong>for</strong> theLEDs, buttons <strong>and</strong> keyboard.32 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>In the future, the user will be able to type a message on the keyboard in an SMS like fashion.Also, a system <strong>of</strong> menus on the LCD can be managed directly from the microcontroller, with theappropriate s<strong>of</strong>tware (see 11.3.2).It was nonetheless decided to dedicate 7 special LEDs <strong>and</strong> 2 buttons <strong>for</strong> the RF operations. Theyare directly linked, along with two hexadecimal selectors used <strong>for</strong> the RF unit address, to theFPGA, <strong>and</strong> thus are totally independent <strong>of</strong> the microcontroller. This choice was motivated by thefollowing reasons:The radio management system will be implemented in the FPGA. In order to simplify thedevelopment <strong>of</strong> such a system, LED are extremely useful, especially in the debugging phase, asthey give a visual indication <strong>of</strong> what is going on inside the component. Additionally, the twobuttons allow the radio subsystem to be tested independently <strong>of</strong> the processor <strong>and</strong> per<strong>for</strong>m certainactions when they are pressed. Each button possesses an associated LED close to it, also linkedto the FPGA.The idea is to use one button as a ping button, <strong>and</strong> the other as an emergency button.The ping button will trigger the emission <strong>of</strong> a ping frame. Every unit that correctly received theframe will trigger the flashing <strong>of</strong> its ping LED (green), providing a visual indication <strong>of</strong> the nodes thatare within radio range <strong>of</strong> each other.The emergency button will send an emergency type frame. Each unit correctly receiving this framewill not only trigger the flashing <strong>of</strong> its emergency LED (red), but also relay the emergencyin<strong>for</strong>mation farther. Thus, every node reachable either directly or by using other units as a relaywill receive this in<strong>for</strong>mation <strong>and</strong> blinks its emergency LED, providing a visual indication <strong>of</strong> thewhole network connectivity.The user must be able to see what the radio subsystem is doing, in particular when it istransmitting <strong>and</strong> receiving. A dedicated LED <strong>for</strong> each function has been included on the extensionboard. One red LED to indicate the transmission, <strong>and</strong> one green <strong>for</strong> the reception. Additionally, 5other, more general purpose LEDs are present on the board. One has been used to indicate whenthe radio system is busy, one to indicate when the receive buffer has data <strong>for</strong> the processor, <strong>and</strong>one to indicate that data to be transmitted is stored in the FPGA <strong>and</strong> will be transmittedmomentarily. The two last LEDs do not have a particular function at the moment.The final physical layout showing the position <strong>of</strong> the various components mentioned above isillustrated in Figure 16. Pictures <strong>of</strong> the real final board are available in 9.2.33 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>TrimmerBoard 7.8 x 10.5mmMilli-BUS BLED RF: busy, TX, RX at top leftRX_buf <strong>and</strong> TX_buf at top rightThen LED misc0 <strong>and</strong> 1LCD 96*40OKPing button <strong>and</strong> LEDESCRFLED uCbuzhexWiFiAntHexadecimalAddressSelectoruCKeyboard802.11b :4.3 * 4.3 under the boardhexMilli-BUS AEmergency button <strong>and</strong> LEDCompact Flash connectorunderneathFigure 16 MegaWatch Extension LayoutThe electrical schematic is available in the appendix, as well as the physical line schematic,realized at ACORT by George Vaucher.6.6 Power MeasurementMeasuring the power consumption <strong>of</strong> the various parts <strong>of</strong> the system is required, in order toevaluate the per<strong>for</strong>mances <strong>of</strong> various designs both in hardware <strong>and</strong> s<strong>of</strong>tware. The simplest way todo this is by measuring the current that flows through an element. We assume we know thesupplied voltage to that element; that should not change too much in time. One can then calculatethe consumed power by doing a simple multiplication.In order to measure the current, an Analog to Digital Converter is needed. It converts an analogvalue into a digital binary number used by the processor to estimate the current value in mA. Asolution with an ADC coupled with an integrated I 2 C bus interface was sought, but no satisfactoryoption was found. Eventually, Cédric Gaudin came up with a microprocessor system fromCygnal, a System-on-chip that integrates an ADC, a microcontroller with Flash <strong>and</strong> RAMmemory, <strong>and</strong> plenty <strong>of</strong> input output PINs in a very small size package. The price was additionallyalso very competitive compared to other st<strong>and</strong>-alone ADC solutions.The main characteristics <strong>of</strong> this C 8051 F 311 [25] microcontroller are:• Real 10 bit ADC, with up to 200 Ksps sampling rate• 25 MHz 8051 microprocessor with 1 KB internal data RAM <strong>and</strong> 16 KB <strong>of</strong> flash memory• 25 I/O ports, within which 17 can be used as an input <strong>for</strong> the ADC.34 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>The general current measurement principle is shown in the figure below.RFI loadMAX4772Current SenseAmplifierLow PassFilterCygnalC8051F311microcontrollerSmall ValueSensing Resistor20xADC10 bituCI 2 CserialBUSMAX6033VoltageReference3.000 VoltFigure 17 Current Measurement CircuitA small value resistor is inserted in series into the circuit that is to be measured. It is veryimportant that the value <strong>of</strong> the resistor is small enough as to not disturb the circuit, typically lessthan an ohm. The drawback <strong>of</strong> this method is the voltage drop that exists on the resistor, <strong>and</strong> thesize <strong>of</strong> this resistor, that must be big enough to avoid heat dissipation problems.The higher the current that flows through the circuit (<strong>and</strong> thus through the resistor), the higher thevoltage potential drop on this resistor (Ohms law). This small voltage is then amplified by adedicated Maxim circuit.The output <strong>of</strong> that circuit then goes through a low pass filter, composed <strong>of</strong> a capacitor <strong>and</strong> resistorwhose value can be adjusted. This filter suppresses high frequency current changes. The result isan averaged voltage output that reflects the power consumption <strong>of</strong> the load. It ensures that <strong>for</strong> agiven ADC sampling frequency, some transitory current peaks do not affect the measurements.The result is a reading that accurately reflects the power consumption.Of course, the right measuring resistor must be carefully chosen, depending on the load. In orderto use the ADC at its maximum resolution, the maximum current measurement must correspond tothe full scale value <strong>of</strong> the converter.On the extension board, this maximum value is given by the external 3.000 voltage reference. Thecurrent sense amplifier has a gain <strong>of</strong> 20, thus, the maximum voltage on the sensing resistor mustbe 150 mV, small enough not to disturb the monitored circuit.We know that at any given time, the voltage on the resistor must not exceed 150 mV. If we knowthe maximum current that will flow through the resistor at any given time, it is then trivial todetermine the ohm value <strong>of</strong> the current sense resistor.This maximum value was estimated by practical measurements taken on the real Xemics chip <strong>for</strong>the RF part, <strong>and</strong> based solely on the datasheet specifications <strong>for</strong> the wireless LAN card, which wasnot yet available at the development time <strong>for</strong> testing.35 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>On the RokEPXA main board, a second microcontroller, similar to the one available on theextension board but smaller in size <strong>and</strong> number <strong>of</strong> PINs, was used. It is a C 8051 F330. Thepower consumption <strong>of</strong> the FPGA, ARM processor <strong>and</strong> memory is achieved through monitoring <strong>of</strong>the different voltages; 1.25, 1.8, 2.5, <strong>and</strong> 3.3 volts respectively. The only difference is the gain <strong>of</strong>the current sense amplifier, as depicted on the figure below.uCADC100 x50 x50 x20 x20 xI 1.25 VI 1.8 VI 2.5 VI 3.3 VI 5.0 VFigure 18 Current Measurement on the Processor BoardIt was decided to use a second separate microcontroller on the main board, <strong>for</strong> two reasons. Thefirst reason it because it makes the measurement on the main board units possible even withoutthe extension board. The second reason, more important, is that it is very difficult to measureanalog voltages values far from where they originate, because a long signal line will cause thesignal to deteriorate quickly due to losses, noise <strong>and</strong> interference problems.For the main board, each supplied voltage was monitored during various phases <strong>of</strong> the boardactivity to determine this maximum current approximately, thus determining the current senseresistor value.More thorough measurements to determine precisely these resistors as well as the low pass filterparameters will be conducted in the future (see 11.3). At the moment, only the raw currentmeasurement value can be read <strong>and</strong> printed on the LCD in order to validate the approach.A test with an oscilloscope also shows that the voltage measured at the output <strong>of</strong> the current senseamplifier is linearly dependant on the circuit current, measured by means <strong>of</strong> a non-intrusive, currentsense probe.6.7 Power Supply BoardsOriginally, the RokEPXA boards were using Adrian Spycher’s semester project power supplyboards. These boards, called SabusAlim [25], were originally designed to supply the variousvoltages required by the RokEPXA boards, the Armonie Xscale 250 boards [26], as well as thecyclope robot. This was achieved through the design <strong>of</strong> a common power supply bus systemcalled A-BUS [14] defining physical <strong>and</strong> logical connections <strong>for</strong> the various tensions as well asconnection to the robot circuit.This 4 layer power supply design comprises not only the power regulators <strong>for</strong> the various voltagesneeded, but also an ADC <strong>for</strong> the physical sensors, 2 motors drivers <strong>and</strong> a battery charger. Theheart <strong>of</strong> the system is a PsoC from Cypress Microsystems, communicating with the main boardsthrough a SPI or I 2 C serial bus.After careful consideration, it was decided that a completely new design was advantageous. Themain reason was that these boards had features that we did not need <strong>for</strong> our application, whichwould increase cost <strong>and</strong> manufacturing time. The second reason was that we found the boardsnot mature enough, suffering from small hardware <strong>and</strong> s<strong>of</strong>tware problems. Finally, the maincomponent <strong>of</strong> the original design was no longer available on the market within a reasonable time tocomplete the project.36 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay6 The MegaWatch <strong>Hardware</strong> <strong>Plat<strong>for</strong>m</strong> <strong>Design</strong>The design <strong>of</strong> these new boards was jointly conducted by Cédric Gaudin <strong>and</strong> myself. It wasoptimized <strong>for</strong> development time, manufacturing costs <strong>and</strong> reliability by making it as simple aspossible. It has only two layers, which means it can be done 100% internally at EPFL, <strong>and</strong> iscomposed <strong>of</strong> components that were available within a reasonable time to finish the project.Input6-15 VBattery 1Battery 2RectifierBypassFuse2AOverdischargeProtectionDS2720Power <strong>of</strong>f switch5VRegulatorMAX1649CSAConfigurationJumpers5VTripleRegulatorMAX1702BeGXRegulatorMAX1842EEEA-Bus5V3.3V2.5V1.25V1.8VFigure 19 Power Supply BoardA set <strong>of</strong> jumpers allow the user to select different voltages to send to the external peripherals. Thisfeature has been kept <strong>for</strong> compatibility reasons, so that the new version <strong>of</strong> the power supply canalso be used with other boards, like the Xscale250. The following set <strong>of</strong> voltages can be produced:First regulator:• 5 V, max 2.5 A (including other regulators)Triple regulator:• 3.3 Volt, max 1 A• Variable voltage between 0 <strong>and</strong> 5 V, 1.25 Volt selected, max 400 mA• 3.3, 2.5 or 1.8 V, 2.5 Volts selected, max 800 mALast regulator:• 1.5 V, 1.8 V, 2.5 V or variable between 1.1 <strong>and</strong> 5 V, 1.8 Volt selected, max 2 A37 / 83

The MegaWatch Wireless <strong>Plat<strong>for</strong>m</strong>Master's Thesis - Emanuel Corthay7 The Protocols7 The ProtocolsBe<strong>for</strong>e going into the details <strong>of</strong> the radio controller, or RF core, the choice <strong>of</strong> the communicationprotocols are exposed in this section.A protocol defines how different hardware communicates between each other, or more remotelythrough cables or radio links. It describes a common language <strong>and</strong> electrical interface used toenable interaction between hardware components.To make the definition <strong>of</strong> a communication protocol simpler, a st<strong>and</strong>ardized layer representationexists. The OSI, or Open System Interconnection, model defines a networking framework <strong>for</strong>implementing protocols in seven layers. Control is passed from one layer to the next, starting atthe application layer in one station or block, proceeding to the bottom layer, over the channel orline to the next station <strong>and</strong> back up the hierarchy.7.1 Radio Protocol <strong>for</strong> the RF CircuitIn the MegaWatch low-power radio link, the different tasks <strong>of</strong> the radio links done in the differentOSI levels, are done at different locations. Tasks that are redundant <strong>and</strong> require real timeprocessing, typically at the low physical level, are done purely in the hardware part. Tasks thatrequire more complex computation <strong>and</strong> memory, like routing decisions, are typically done ins<strong>of</strong>tware, i.e. in the processor. The following hardware <strong>and</strong> s<strong>of</strong>tware partitioning appeared to bethe most natural one, <strong>and</strong> has been applied to the low-power RF link <strong>of</strong> the MegaWatch plat<strong>for</strong>m:Layer 4 to 7To the applicationLayer 3NetworkLayer 2Data LinkLayer 1PhysicalLLCMACProvides transparent transfer <strong>of</strong> data between endsystems <strong>for</strong> end-user applicationDefines communication partners <strong>and</strong> extrarequirements like authenticationProvides packet switching, <strong>for</strong>warding, routing <strong>and</strong>sequencing, as well as addressing <strong>and</strong> errorh<strong>and</strong>lingProvides frame synchronization <strong>and</strong> errordetection <strong>and</strong> define the common rules tocommunicateMedia Access Control ; Gain access to thetransmission mediumDefines the physical connection between devices;Converts analog voltage or radio signals into a bitstreamDone in theRF chipDone in theFPGADone in theprocessorFigure 20 How <strong>and</strong> where the OSI representation is applied in the MegaWatch Units38 / 83