IntelR 80960 RN I/O Processor Datasheet

IntelR 80960 RN I/O Processor Datasheet

IntelR 80960 RN I/O Processor Datasheet

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

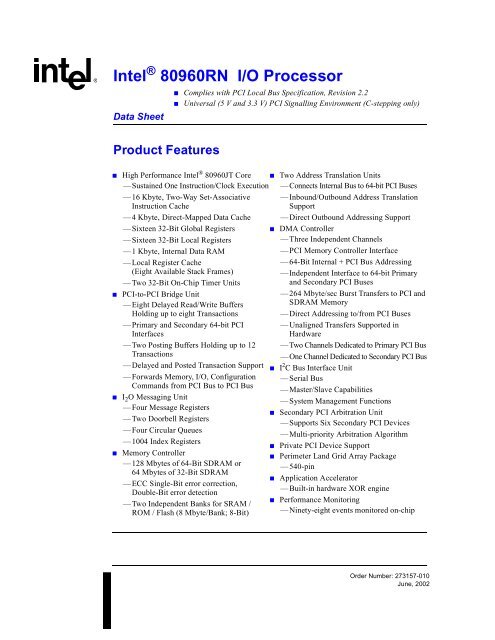

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Data Sheet<br />

Product Features<br />

■ Complies with PCI Local Bus Specification, Revision 2.2<br />

■ Universal (5 V and 3.3 V) PCI Signalling Environment (C-stepping only)<br />

■<br />

■<br />

■<br />

■<br />

High Performance Intel ® <strong>80960</strong>JT Core<br />

—Sustained One Instruction/Clock Execution<br />

—16 Kbyte, Two-Way Set-Associative<br />

Instruction Cache<br />

—4 Kbyte, Direct-Mapped Data Cache<br />

—Sixteen 32-Bit Global Registers<br />

—Sixteen 32-Bit Local Registers<br />

—1 Kbyte, Internal Data RAM<br />

—Local Register Cache<br />

(Eight Available Stack Frames)<br />

—Two 32-Bit On-Chip Timer Units<br />

PCI-to-PCI Bridge Unit<br />

—Eight Delayed Read/Write Buffers<br />

HoldinguptoeightTransactions<br />

—Primary and Secondary 64-bit PCI<br />

Interfaces<br />

—TwoPostingBuffersHoldingupto12<br />

Transactions<br />

—Delayed and Posted Transaction Support<br />

—Forwards Memory, I/O, Configuration<br />

Commands from PCI Bus to PCI Bus<br />

I 2 O Messaging Unit<br />

—Four Message Registers<br />

— Two Doorbell Registers<br />

—Four Circular Queues<br />

—1004 Index Registers<br />

Memory Controller<br />

—128 Mbytes of 64-Bit SDRAM or<br />

64 Mbytes of 32-Bit SDRAM<br />

—ECC Single-Bit error correction,<br />

Double-Bit error detection<br />

—Two Independent Banks for SRAM /<br />

ROM/Flash(8Mbyte/Bank;8-Bit)<br />

■<br />

■<br />

■<br />

■<br />

■<br />

■<br />

■<br />

■<br />

Two Address Translation Units<br />

— Connects Internal Bus to 64-bit PCI Buses<br />

—Inbound/Outbound Address Translation<br />

Support<br />

—Direct Outbound Addressing Support<br />

DMA Controller<br />

—Three Independent Channels<br />

—PCI Memory Controller Interface<br />

—64-Bit Internal + PCI Bus Addressing<br />

—Independent Interface to 64-bit Primary<br />

and Secondary PCI Buses<br />

—264 Mbyte/sec Burst Transfers to PCI and<br />

SDRAM Memory<br />

—Direct Addressing to/from PCI Buses<br />

—Unaligned Transfers Supported in<br />

Hardware<br />

— Two Channels Dedicated to Primary PCI Bus<br />

—One Channel Dedicated to Secondary PCI Bus<br />

I 2 C Bus Interface Unit<br />

—Serial Bus<br />

—Master/Slave Capabilities<br />

—System Management Functions<br />

Secondary PCI Arbitration Unit<br />

—Supports Six Secondary PCI Devices<br />

—Multi-priority Arbitration Algorithm<br />

Private PCI Device Support<br />

Perimeter Land Grid Array Package<br />

—540-pin<br />

Application Accelerator<br />

—Built-in hardware XOR engine<br />

Performance Monitoring<br />

—Ninety-eight events monitored on-chip<br />

Order Number: 273157-010<br />

June, 2002

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual<br />

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability<br />

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to<br />

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not<br />

intended for use in medical, life saving, or life sustaining applications.<br />

Intel may make changes to specifications and product descriptions at any time, without notice.<br />

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for<br />

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.<br />

The Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong> may contain design defects or errors known as errata which may cause the product to deviate from published<br />

specifications. Current characterized errata are available on request.<br />

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.<br />

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling<br />

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.<br />

Copyright © Intel Corporation, 2002<br />

Intel, Intel Solutions960 and Intel i960 are registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.<br />

*Other names and brands may be claimed as the property of others.<br />

Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Contents<br />

1.0 About this Document................................................................................................7<br />

1.1 Intel ® Solutions960 ® Program ...............................................................................7<br />

1.2 Terminology...........................................................................................................7<br />

1.3 Additional Information Sources .............................................................................7<br />

2.0 Functional Overview .................................................................................................8<br />

2.1 Key Functional Units .............................................................................................9<br />

2.1.1 PCI-to-PCI Bridge Unit .............................................................................9<br />

2.1.2 Private PCI Device Support......................................................................9<br />

2.1.3 DMA Controller.........................................................................................9<br />

2.1.4 Address Translation Unit ..........................................................................9<br />

2.1.5 Messaging Unit.........................................................................................9<br />

2.1.6 Memory Controller Unit ..........................................................................10<br />

2.1.7 I2C Bus Interface Unit ............................................................................10<br />

2.1.8 Secondary PCI Arbitration Unit ..............................................................10<br />

2.1.9 Application Accelerator Unit ...................................................................10<br />

2.1.10 Performance Monitor Unit ......................................................................10<br />

2.1.11 Bus Interface Unit...................................................................................10<br />

2.2 Intel ® i960 ® Core Features (Intel ® <strong>80960</strong>JT).......................................................11<br />

2.2.1 Burst Bus................................................................................................12<br />

2.2.2 Timer Unit...............................................................................................12<br />

2.2.3 Priority Interrupt Controller .....................................................................12<br />

2.2.4 Faults and Debugging ............................................................................12<br />

2.2.5 On-Chip Cache and Data RAM ..............................................................12<br />

2.2.6 Local Register Cache .............................................................................13<br />

2.2.7 Test Features .........................................................................................13<br />

2.2.8 Memory-Mapped Control Registers .......................................................13<br />

2.2.9 Instructions, Data Types and Memory Addressing Modes.....................13<br />

3.0 Package Information...............................................................................................15<br />

3.1 Package Introduction...........................................................................................15<br />

3.1.1 Functional Signal Definitions ..................................................................15<br />

3.1.1.1 Signal Pin Descriptions .............................................................16<br />

3.1.2 540-Lead H-PBGA Package ..................................................................26<br />

3.2 Package Thermal Specifications .........................................................................38<br />

3.2.1 Thermal Specifications ...........................................................................38<br />

3.2.1.1 Ambient Temperature................................................................38<br />

3.2.1.2 Case Temperature ....................................................................38<br />

3.2.1.3 Thermal Resistance ..................................................................39<br />

3.2.2 Thermal Analysis....................................................................................39<br />

3.3 Heat Sink Information..........................................................................................40<br />

3.4 Vendor Information..............................................................................................40<br />

3.4.1 Socket-Header Vendor...........................................................................40<br />

3.4.2 Burn-in Socket Vendor ...........................................................................40<br />

3.4.3 Shipping Tray Vendor.............................................................................41<br />

3.4.4 Logic Analyzer Interposer Vendor ..........................................................41<br />

3.4.5 JTAG Emulator Vendor ..........................................................................41<br />

3.5 ............................................................................................................................41<br />

Data Sheet 3

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

4.0 Electrical Specifications........................................................................................42<br />

4.1 Absolute Maximum Ratings ................................................................................42<br />

4.2 V CC5REF Pin Requirements (V DIFF ).....................................................................43<br />

4.3 V CCPLL Pin Requirements ...................................................................................43<br />

4.4 Targeted DC Specifications ................................................................................44<br />

4.5 Targeted AC Specifications.................................................................................46<br />

4.5.1 Clock Signal Timings..............................................................................46<br />

4.5.2 PCI Interface Signal Timings..................................................................47<br />

4.5.3 Intel ® <strong>80960</strong>JN Core Interface Timings.................................................. 48<br />

4.5.4 SDRAM/Flash Interface Signal Timings .................................................48<br />

4.5.5 Boundary Scan Test Signal Timings ...................................................... 49<br />

4.5.6 I2C Interface Signal Timings .................................................................. 50<br />

4.6 AC Timing Waveforms ........................................................................................51<br />

4.7 AC Test Conditions ............................................................................................. 53<br />

5.0 Device Identification on Reset............................................................................54<br />

4 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Figures<br />

Tables<br />

1 Intel ® <strong>80960</strong><strong>RN</strong> Functional Block Diagram ..................................................... 8<br />

2 Intel ® <strong>80960</strong>JT Core Block Diagram ............................................................. 11<br />

3 540L H-PBGA Package Diagram (Top and Side View) ................................ 26<br />

4 540L H-PBGA Package Diagram (Bottom View) .......................................... 27<br />

5 Thermocouple Attachment - A) No Heatsink / B) With Heatsink ................... 38<br />

6 V CC5REF Current-Limiting Resistor................................................................ 43<br />

7 V CCPLL Lowpass Filter .................................................................................. 43<br />

8 P_CLK, TCK, DCLKIN, DCLKOUT Waveform............................................. 51<br />

9 T OV Output Delay Waveform......................................................................... 51<br />

10 T OF Output Float Waveform .......................................................................... 52<br />

11 T IS and T IH Input Setup and Hold Waveform ................................................ 52<br />

12 I 2 C Interface Signal Timings.......................................................................... 52<br />

13 AC Test Load (all signals except SDRAM and Flash signals)....................... 53<br />

1 Related Documentation................................................................................... 7<br />

2 Instruction Set .............................................................................................. 14<br />

3 Pin Description Nomenclature....................................................................... 16<br />

4 Memory Controller Signals ............................................................................ 17<br />

5 Primary PCI Bus Signals ............................................................................... 20<br />

6 Secondary PCI Arbiter Signals...................................................................... 21<br />

7 Secondary PCI Bus Signals .......................................................................... 22<br />

8 Intel ® <strong>80960</strong>Jx Core Signals and Configuration Straps................................. 24<br />

9 I 2 C, JTAG, Core Signals ............................................................................... 25<br />

10 540-Lead H-PBGA Package — Signal Name Order ..................................... 28<br />

11 540-Lead H-PBGA Pinout — Ballpad Number Order.................................... 33<br />

12 540-Lead H-PBGA Package Thermal Characteristics .................................. 39<br />

13 Heat Sink Vendors and Contacts .................................................................. 40<br />

14 Socket-Header Vendor.................................................................................. 40<br />

15 Burn-in Socket Vendor .................................................................................. 40<br />

16 Shipping Tray Vendor.................................................................................... 41<br />

17 Logic Analyzer Interposer Vendor ................................................................. 41<br />

18 JTAG Emulator Vendor ................................................................................. 41<br />

19 Operating Conditions..................................................................................... 42<br />

20 V DIFF Specification for Dual Power Supply Requirements (3.3 V, 5 V)......... 43<br />

21 DC Characteristics ........................................................................................ 44<br />

22 I CC Characteristics ........................................................................................ 45<br />

23 Input Clock Timings....................................................................................... 46<br />

24 SDRAM Output Clock Timings ...................................................................... 46<br />

25 PCI Signal Timings....................................................................................... 47<br />

26 Intel ® <strong>80960</strong>JN Core Signal Timings............................................................. 48<br />

27 SDRAM / Flash Signal Timings..................................................................... 48<br />

28 Boundary Scan Test Signal Timings ............................................................. 49<br />

29 I2C Interface Signal Timings ......................................................................... 50<br />

30 Device ID Registers...................................................................................... 54<br />

Data Sheet 5

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

This Page Intentionally Left Blank<br />

6 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

1.0 About this Document<br />

This is the data sheet for the Intel ® <strong>80960</strong><strong>RN</strong> processor. This data sheet contains a functional<br />

overview, mechanical data (package signal locations and simulated thermal characteristics),<br />

targeted electrical specifications (simulated), and bus functional waveforms. Detailed functional<br />

descriptions other than parametric performance is published in the i960 ® RM/<strong>RN</strong> I/O <strong>Processor</strong><br />

Developer’s Manual.<br />

1.1 Intel ® Solutions960 ® Program<br />

The Intel ® Solutions960 ® program features a wide variety of development tools which support the<br />

i960 ® processor family. Many of these tools are developed by partner companies; some are<br />

developed by Intel, such as profile-driven optimizing compilers. For more information on these<br />

products, contact your local Intel representative.<br />

1.2 Terminology<br />

In this document, the following terms are used:<br />

• Primary and Secondary PCI buses are the <strong>80960</strong><strong>RN</strong> processor’s external PCI buses which<br />

conform to PCI SIG specifications.<br />

• Intel ® <strong>80960</strong> core refers to the Intel ® <strong>80960</strong>JT processor which is integrated into the <strong>80960</strong><strong>RN</strong><br />

processor.<br />

1.3 Additional Information Sources<br />

Intel documentation is available from your local Intel Sales Representative or Intel Literature Sales.<br />

Intel Corporation<br />

Literature Sales<br />

P.O. Box 5937<br />

Denver, CO 80217-9808<br />

1-800-548-4725<br />

Table 1.<br />

Related Documentation<br />

Document Title<br />

Order / Contact<br />

i960 ® RM/<strong>RN</strong> I/O <strong>Processor</strong> Developer’s Manual Intel Order # 273158<br />

i960 ® Jx Microprocessor User’s Guide Intel Order # 272483<br />

i960 ® RM/<strong>RN</strong>/RS I/O <strong>Processor</strong> Specification Update Intel Order # 273164<br />

PCI Local Bus Specification, Revision 2.2 PCI Special Interest Group 1-800-433-5177<br />

PCI-to-PCI Bridge Architecture Specification, Revision 1.1 PCI Special Interest Group 1-800-433-5177<br />

I 2 C Peripherals for Microcontrollers<br />

Philips Semiconductor<br />

Data Sheet 7

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

2.0 Functional Overview<br />

As indicated in Figure 1, the <strong>80960</strong><strong>RN</strong> processor combines many features with the <strong>80960</strong>JT to create<br />

an intelligent I/O processor. Subsections following the figure briefly describe the main features; for<br />

detailed functional descriptions, refer to the i960 ® RM/<strong>RN</strong> I/O <strong>Processor</strong> Developer’s Manual.<br />

The PCI bus is an industry standard, high performance, low latency system bus that operates up to<br />

264 Mbyte/s. The <strong>80960</strong><strong>RN</strong> processor, a multi-function PCI device, is fully compliant with the<br />

PCI Local Bus Specification, Revision 2.2. Function 0 is the PCI-to-PCI bridge unit; Function 1 is<br />

the address translation unit.<br />

The PCI-to-PCI bridge unit is the path between two independent 64-bit PCI buses and provides the<br />

ability to overcome PCI electrical load limits. The addition of the Intel ® i960 ® core processor<br />

brings intelligence to the bridge.<br />

The <strong>80960</strong><strong>RN</strong> processor, object code compatible with the i960 core processor, is capable of<br />

sustained execution at the rate of one instruction per clock.<br />

The internal bus, a 64-bit PCI-like bus, is a high-speed interface to local memory and I/O. Physical<br />

and logical memory attributes are programmed via memory-mapped control registers (MMRs); an<br />

extension not found on the Intel ® i960Kx,SxorCxprocessors.<br />

Figure 1.<br />

Intel ® <strong>80960</strong><strong>RN</strong> Functional Block Diagram<br />

Local Memory<br />

(SDRAM, Flash)<br />

I 2 C Serial Bus<br />

<strong>80960</strong><strong>RN</strong> <strong>Processor</strong><br />

<strong>80960</strong> Core<br />

Memory<br />

Controller<br />

Bus<br />

Interface<br />

I 2 CBus<br />

Interface<br />

Application<br />

Accelerator<br />

Internal<br />

Arbitration<br />

64-bit Internal Bus<br />

Messaging<br />

Unit<br />

Two DMA<br />

Channels<br />

Address<br />

Translation<br />

One DMA<br />

Channel<br />

Address<br />

Translation<br />

64-bit/32-bit Primary PCI Bus<br />

PCI to PCI<br />

Bridge<br />

64-bit/32-bit Secondary PCI Bus<br />

Performance<br />

Monitoring<br />

Unit<br />

Secondary<br />

PCI Arbitration<br />

Unit<br />

8 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

2.1 Key Functional Units<br />

2.1.1 PCI-to-PCI Bridge Unit<br />

The PCI-to-PCI bridge unit (referred to as “bridge”) connects two independent PCI buses. Each<br />

PCI bus may be 32 or 64 bits wide. The bridge is fully compliant with the PCI-to-PCI Bridge<br />

Architecture Specification, Revision 1.1 published by the PCI Special Interest Group. The bridge<br />

forwards bus transactions on one PCI bus to the other PCI bus. Dedicated data queues support high<br />

performance bandwidth on the PCI buses. The <strong>80960</strong><strong>RN</strong> supports PCI 64-bit Dual Address Cycle<br />

(DAC) addressing.<br />

The bridge has dedicated PCI configuration space accessible through the primary PCI bus.<br />

2.1.2 Private PCI Device Support<br />

The <strong>80960</strong><strong>RN</strong> processor explicitly supports private PCI devices on the secondary PCI bus. The<br />

bridge and Address Translation Unit work together to hide private PCI devices from PCI<br />

configuration cycles and allow these hidden devices to use a private PCI address space. The<br />

Address Translation Unit issues PCI configuration cycles to configure hidden devices.<br />

2.1.3 DMA Controller<br />

The DMA Controller supports low-latency, high-throughput data transfers between PCI bus agents<br />

and local memory. Three separate DMA channels accommodate data transfers: two for primary<br />

PCI bus, one for the secondary PCI bus. The DMA Controller supports chaining and unaligned<br />

data transfers. The DMA Controller is programmable only through the i960 core processor.<br />

2.1.4 Address Translation Unit<br />

The Address Translation Unit (ATU) allows PCI transactions direct access to local memory. The<br />

<strong>80960</strong><strong>RN</strong> processor has direct access to both PCI buses. The ATU supports transactions between<br />

PCI address space and <strong>80960</strong><strong>RN</strong> processor address space.<br />

Address translation is controlled through programmable registers accessible from both the primary<br />

PCI interface and the <strong>80960</strong> core. Dual access to registers allows flexibility in mapping the two<br />

address spaces.<br />

2.1.5 Messaging Unit<br />

The Messaging Unit (MU) provides data transfer between the PCI system and the <strong>80960</strong><strong>RN</strong><br />

processor. The Messaging Unit uses interrupts to notify the PCI system or the <strong>80960</strong><strong>RN</strong> processor<br />

when new data arrives. The MU has four messaging mechanisms: Message Registers, Doorbell<br />

Registers, Circular Queues, and Index Registers. Each mechanism allows a host processor or<br />

external PCI device and the <strong>80960</strong><strong>RN</strong> processor to communicate through message passing and<br />

interrupt generation.<br />

Data Sheet 9

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

2.1.6 Memory Controller Unit<br />

The Memory Controller Unit (MCU) allows direct control of a local SDRAM and Flash subsystem.<br />

The MCU features programmable chip selects, a wait state generator and Error Correction and<br />

Detection. With the ATU configuration registers, local memory can be configured as PCI<br />

addressable memory or private processor memory.<br />

2.1.7 I 2 C Bus Interface Unit<br />

The I 2 C (Inter-Integrated Circuit) Bus Interface Unit allows the <strong>80960</strong> core to serve as a master and<br />

slave device residing on the I 2 C bus. The I 2 C bus is a serial bus developed by Philips<br />

Semiconductor comprising a two pin interface. The bus allows the <strong>80960</strong><strong>RN</strong> processor to interface<br />

to other I 2 C peripherals and microcontrollers for system management functions. It requires a<br />

minimum of hardware for an economical system to relay status and reliability information on the<br />

I/O subsystem to an external device. For more information, see I 2 C Peripherals for<br />

Microcontrollers (Philips Semiconductor).<br />

2.1.8 Secondary PCI Arbitration Unit<br />

The Secondary PCI Arbitration Unit provides PCI arbitration for the secondary PCI bus. The<br />

arbitration includes a fairness algorithm with programmable priorities and six external PCI Request<br />

and Grant signal pairs.<br />

2.1.9 Application Accelerator Unit<br />

The Application Accelerator Unit (AAU) provides hardware acceleration of XOR functions<br />

commonly used in RAID algorithms. Additionally, the AAU provides block moves within local<br />

memory. The Application Accelerator interfaces the internal bus and operates on data within local<br />

memory. The AAU is programmable through the i960 core processor and supports chaining and<br />

unaligned data transfers.<br />

2.1.10 Performance Monitor Unit<br />

The Performance Monitor Unit (PMU) allows software to monitor the performance of the different<br />

buses: Primary PCI, Secondary PCI, and Internal. Multiple performance characteristics are<br />

captured with 14 mode registers and a global time stamp register.<br />

2.1.11 Bus Interface Unit<br />

The Bus Interface Unit (BIU) provides an interface between the 100 MHz <strong>80960</strong>JT core and the<br />

66 MHz internal bus. To optimize performance, the BIU implements prefetching and write merging.<br />

10 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

2.2 Intel ® i960 ® Core Features (Intel ® <strong>80960</strong>JT)<br />

The processing power of the <strong>80960</strong><strong>RN</strong> processor comes from the 100 MHz <strong>80960</strong>JT processor<br />

core. The <strong>80960</strong>JT is a scalar implementation of the <strong>80960</strong> Core Architecture. Figure 2 shows a<br />

block diagram of the <strong>80960</strong>JT Core processor.<br />

Factors that contribute to the <strong>80960</strong>JT core’s performance include:<br />

• 100 MHz Single-clock execution of most instructions<br />

• Independent Multiply/Divide Unit<br />

• Efficient instruction pipeline minimizes pipeline break latency<br />

• Register and resource scoreboarding allow overlapped instruction execution<br />

• 128-bit register bus speeds local register caching<br />

• 16 Kbyte two-way set-associative, integrated instruction cache<br />

• 4 Kbyte direct-mapped, integrated data cache<br />

• 1 Kbyte integrated data RAM delivers zero wait state program data<br />

Figure 2.<br />

The <strong>80960</strong> core operates out of its own 32-bit address space, which is independent of the PCI<br />

address space. Local memory can be:<br />

• Made visible to the PCI address space<br />

• Kept private to the <strong>80960</strong>JT core<br />

• Allocated as a combination of the two<br />

Intel ® <strong>80960</strong>JT Core Block Diagram<br />

P_CLK<br />

TAP<br />

5<br />

PLL, Clocks,<br />

Power Mgmt<br />

Boundary Scan<br />

Controller<br />

8-Set<br />

Local Register<br />

Cache<br />

128<br />

Global / Local<br />

Register File<br />

SRC1 SRC2 DST<br />

Multiply<br />

Divide<br />

Unit<br />

SRC1<br />

SRC2<br />

DST<br />

Instruction Cache<br />

16 Kbyte Two-Way Set<br />

Associative<br />

Instruction Sequencer<br />

Constants<br />

Execution<br />

and<br />

Address<br />

Generation<br />

Unit<br />

Effective<br />

Address<br />

SRC1<br />

SRC2<br />

DST<br />

Control<br />

3 Independent 32-Bit SRC1, SRC2, and DST Buses<br />

Memory<br />

Interface<br />

Unit<br />

32-bit Addr<br />

32-bit Data<br />

SRC1<br />

DST<br />

32-bit buses<br />

address / data<br />

Physical Region<br />

Configuration<br />

Bus<br />

Control Unit<br />

Bus Request<br />

Queues<br />

Two 32-Bit<br />

Timers<br />

Control<br />

Address/<br />

Data Bus<br />

Interrupt<br />

Programmable<br />

Port<br />

Interrupt Controller 9<br />

Memory-Mapped<br />

Register Interface<br />

1Kbyte<br />

Data RAM<br />

4Kbyte<br />

Direct Mapped<br />

Data Cache<br />

32<br />

Data Sheet 11

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

2.2.1 Burst Bus<br />

2.2.2 Timer Unit<br />

A 32-bit high-performance bus controller interfaces the <strong>80960</strong><strong>RN</strong> processor to the Bus Interface<br />

Unit. The Bus Control Unit fetches instructions and transfers data on the internal bus at the rate of<br />

up to four 32-bit words per six clock cycles. The external address/data bus is multiplexed.<br />

Data caching is programmed through a group of logical memory templates and a defaults register.<br />

The Bus Control Unit’s features include:<br />

• Multiplexed external bus minimizes pin count<br />

• External ready control for address-to-data, data-to-data and data-to-next-address wait state types<br />

• Little endian byte ordering<br />

• Unaligned bus accesses performed transparently<br />

• Three-deep load/store queue decouples the bus from the <strong>80960</strong> core<br />

Upon reset, the <strong>80960</strong>JT conducts an internal self test. Before executing its first instruction, it<br />

performs an external bus confidence test by performing a checksum on the first words of the<br />

Initialization Boot Record.<br />

The timer unit (TU) contains two independent 32-bit timers that are capable of counting at several<br />

clock rates and generating interrupts. Each is programmed through the Timer Unit registers. These<br />

memory-mapped registers are addressable on 32-bit boundaries. Timers have a single-shot mode<br />

and auto-reload capabilities for continuous operation. Each timer has an independent interrupt<br />

request to the <strong>80960</strong>JT’s interrupt controller. The TU can generate a fault when unauthorized writes<br />

from user mode are detected.<br />

2.2.3 Priority Interrupt Controller<br />

Low interrupt latency is critical to many embedded applications. As part of its highly flexible<br />

interrupt mechanism, the <strong>80960</strong>JT exploits several techniques to minimize latency:<br />

• Interrupt vectors and interrupt handler routines can be reserved on-chip<br />

• Register frames for high-priority interrupt handlers can be cached on-chip<br />

• The interrupt stack can be placed in cacheable memory space<br />

2.2.4 Faults and Debugging<br />

The <strong>80960</strong>JT employs a comprehensive fault model. The processor responds to faults by making<br />

implicit calls to a fault handling routine. Specific information collected for each fault allows the<br />

fault handler to diagnose exceptions and recover appropriately.<br />

The processor also has built-in debug capabilities. With software, the <strong>80960</strong>JT may be configured<br />

to detect as many as seven different trace event types. Alternatively, mark and fmark instructions<br />

can generate trace events explicitly in the instruction stream. Hardware breakpoint registers are<br />

also available to trap on execution and data addresses.<br />

2.2.5 On-Chip Cache and Data RAM<br />

Memory subsystems often impose substantial wait state penalties. The <strong>80960</strong>JT integrates<br />

considerable storage resources on-chip to decouple CPU execution from the external bus. The<br />

<strong>80960</strong>JT includes a 16 Kbyte instruction cache, a 4 Kbyte data cache and 1 Kbyte data RAM.<br />

12 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

2.2.6 Local Register Cache<br />

The <strong>80960</strong>JT rapidly allocates and deallocates local register sets during context switches. The processor<br />

needs to flush a register set to the stack only when it saves more than seven sets to its local register cache.<br />

2.2.7 Test Features<br />

The <strong>80960</strong><strong>RN</strong> processor incorporates numerous features that enhance the user’s ability to test both<br />

the processor and the system to which it is attached. These features include ONCE (On-Circuit<br />

Emulation) mode and Boundary Scan (JTAG).<br />

The <strong>80960</strong>JT provides testability features compatible with IEEE Standard Test Access Port and<br />

Boundary Scan Architecture (IEEE Std. 1149.1).<br />

One of the boundary scan instructions, HIGHZ, forces the processor to float all its output pins (ONCE<br />

mode). ONCE mode can also be initiated at reset without using the boundary scan mechanism.<br />

ONCE mode is useful for board-level testing. This feature allows a mounted <strong>80960</strong><strong>RN</strong> processor to<br />

electrically “remove” itself from a circuit board allowing system-level testing where a remote<br />

tester can exercise the processor system.<br />

The test logic does not interfere with component or system behavior and ensures that components<br />

function correctly and the connections between various components are correct.<br />

The JTAG Boundary Scan feature is an alternative to conventional “bed-of-nails” testing.<br />

Boundary Scan can examine connections that might otherwise be inaccessible to a test system.<br />

2.2.8 Memory-Mapped Control Registers<br />

The <strong>80960</strong>JT is compliant with <strong>80960</strong> family architecture. Each memory-mapped, 32-bit register is<br />

accessed via memory-format instructions. The processor ensures that these accesses do not<br />

generate external bus cycles.<br />

2.2.9 Instructions, Data Types and Memory Addressing Modes<br />

As with all <strong>80960</strong> family processors, the instruction set supports several different data types and formats:<br />

• Bit<br />

• Bit fields<br />

• Integer (8-, 16-, 32-, 64-bit)<br />

• Ordinal (8-, 16-, 32-, 64-bit unsigned integers)<br />

• Triple word (96 bits)<br />

• Quad word (128 bits)<br />

The <strong>80960</strong>JT provides a full set of addressing modes for C and assembly:<br />

• Two Absolute modes<br />

• Five Register Indirect modes<br />

• Index with displacement mode<br />

• IP with displacement mode<br />

Data Sheet 13

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 2 shows the available <strong>80960</strong>JT instructions.<br />

Table 2.<br />

Instruction Set<br />

Data Movement Arithmetic Logical Bit, Bit Field and Byte<br />

Add<br />

Subtract<br />

Load<br />

Store<br />

Move<br />

Conditional Select<br />

Load Address<br />

Multiply<br />

Divide<br />

Remainder<br />

Modulo<br />

Shift<br />

Extended Shift<br />

Extended Multiply<br />

Extended Divide<br />

Add with Carry<br />

Subtract with Carry<br />

Conditional Add<br />

Conditional Subtract<br />

Rotate<br />

And<br />

Not And<br />

And Not<br />

Or<br />

Exclusive Or<br />

Not Or<br />

Or Not<br />

Nor<br />

Exclusive Nor<br />

Not<br />

Nand<br />

Set Bit<br />

Clear Bit<br />

Not Bit<br />

Alter Bit<br />

Scan For Bit<br />

Span Over Bit<br />

Extract<br />

Modify<br />

Scan Byte for Equal<br />

Byte Swap<br />

Comparison Branch Call/Return Fault<br />

Compare<br />

Conditional Compare<br />

Compare and Increment<br />

Compare and<br />

Decrement<br />

Test Condition Code<br />

Check Bit<br />

Unconditional Branch<br />

Conditional Branch<br />

Compare and Branch<br />

Call<br />

Call Extended<br />

Call System<br />

Return<br />

Branch and Link<br />

Conditional Fault<br />

Synchronize Faults<br />

Debug<br />

<strong>Processor</strong><br />

Management<br />

Atomic<br />

Flush Local Registers<br />

Modify Trace Controls<br />

Mark<br />

Force Mark<br />

Modify Arithmetic<br />

Controls<br />

Modify Process Controls<br />

Halt<br />

System Control<br />

Cache Control<br />

Interrupt Control<br />

Atomic Add<br />

Atomic Modify<br />

14 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

3.0 Package Information<br />

3.1 Package Introduction<br />

The <strong>80960</strong><strong>RN</strong> processor is offered in a Perimeter Land Grid Array (PBGA) package. This is a<br />

perimeter array package with five rows of ball connections in the outer area of the package. See<br />

Figure 4 “540L H-PBGA Package Diagram (Bottom View)” on page 27.<br />

3.1.1 Functional Signal Definitions<br />

This section defines the pins and signals in the following tables:<br />

• Table 3 “Pin Description Nomenclature” on page 16<br />

• Table 4 “Memory Controller Signals” on page 17<br />

• Table 5 “Primary PCI Bus Signals” on page 20<br />

• Table 6 “Secondary PCI Arbiter Signals” on page 21<br />

• Table 8 “Intel ® <strong>80960</strong>Jx Core Signals and Configuration Straps” on page 24<br />

• Table 9 “I 2 C, JTAG, Core Signals” on page 25<br />

Data Sheet 15

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

3.1.1.1 Signal Pin Descriptions<br />

Table 3.<br />

Pin Description Nomenclature<br />

Symbol<br />

Description<br />

I<br />

O<br />

I/O<br />

Input pin only<br />

Output pin only<br />

Pin can be either an input or output<br />

OD Open Drain pin<br />

- Pin must be connected as described<br />

N/C<br />

5V<br />

Sync(...)<br />

Async<br />

Prst(...)<br />

Srst(...)<br />

Irst(...)<br />

P32(...)<br />

S32(...)<br />

NO CONNECT. Do not make electrical connections to these balls.<br />

Input pin is 5 volt tolerant<br />

Synchronous. Inputs meet setup and hold times relative to an input clock.<br />

Sync(P) Synchronous to P_CLK<br />

Sync(D) Synchronous to DCLKIN<br />

Sync(T) Synchronous to TCK<br />

Asynchronous. Inputs may be asynchronous relative to P_CLK, DCLKIN, orTCK. All<br />

asynchronous signals are level-sensitive.<br />

While the P_RST# pin is asserted, the pin:<br />

Prst(1) Is driven to Vcc<br />

Prst(0) Is driven to Vss<br />

Prst(X) Is driven to unknown state<br />

Prst(H)IspulleduptoVcc<br />

Prst(L)IspulleddowntoVss<br />

Prst(Z) Floats<br />

Prst(Q) Is a valid output<br />

Since P_RST# is asynchronous, these are asynchronous events.<br />

While the S_RST# pin is asserted, the pin:<br />

Srst(1) Is driven to Vcc<br />

Srst(0) Is driven to Vss<br />

Srst(X) Is driven to unknown state<br />

Srst(H)IspulleduptoVcc<br />

Srst(L)IspulleddowntoVss<br />

Srst(Z) Floats<br />

Srst(Q) Is a valid output<br />

Note that S_RST# is asserted when P_RST# is asserted or BCR[6] is set with software.<br />

While the I_RST# pin is asserted, the pin:<br />

Irst(1) Is driven to Vcc<br />

Irst(0) Is driven to Vss<br />

Irst(X) Is driven to unknown state<br />

Irst(H)IspulleduptoVcc<br />

Irst(L)IspulleddowntoVss<br />

Irst(Z) Floats<br />

Irst(Q) Is a valid output<br />

Note that I_RST# is asserted when P_RST# is asserted or EBCR[5] is set with software.<br />

While the Primary PCI Bus is configured as a 32-bit PCI bus by the Primary central resource:<br />

P32(H) is pulled up internally to Vcc<br />

P32(L) is pulled down internally to Vss<br />

While the Secondary PCI Bus is configured as a 32-bit PCI bus with 32BITPCI_EN#:<br />

S32(H) is pulled up internally to Vcc<br />

S32(L) is pulled down internally to Vss<br />

16 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 4. Memory Controller Signals (Sheet 1 of 3)<br />

Name Count Type Description<br />

DCLKOUT<br />

1 O<br />

Irst(Q)<br />

SDRAM OUTPUT CLOCK dedicated for SDRAM memory<br />

subsystem.<br />

DCLKIN<br />

1 I SDRAM INPUT CLOCK dedicated for SDRAM memory<br />

subsystem. Used to skew DCLKOUT appropriately to<br />

accommodate flight time and clock buffer delays.<br />

SA[11:0]<br />

SBA[1:0]<br />

SRAS#<br />

SCAS#<br />

SDQM[7:0]<br />

SWE#<br />

SCE[1:0]#<br />

SCKE[1:0]<br />

DQ[63:0]<br />

SCB[7:0]<br />

ROE#<br />

RWE#<br />

RCE[1:0]#<br />

RALE<br />

12 O<br />

Irst(Q)<br />

2 O<br />

Irst(Q)<br />

1 O<br />

Irst(1)<br />

1 O<br />

Irst(1)<br />

8 O<br />

Irst(1)<br />

1 O<br />

Irst(1)<br />

2 O<br />

Irst(1)<br />

2 O<br />

Irst(Q)<br />

64 I/O<br />

Irst(1)<br />

Sync(D)<br />

8 I/O<br />

Irst(1)<br />

Sync(D)<br />

1 O<br />

Irst(1)<br />

1 O<br />

Irst(1)<br />

2 O<br />

Irst(1)<br />

1 O<br />

Irst(0)<br />

SDRAM MULTIPLEXED ADDRESS BUS carries the multiplexed<br />

row and column addresses to the SDRAM memory banks. For<br />

SA[10], see note 1.<br />

SDRAM INTE<strong>RN</strong>AL BANK SELECT indicates which of the SDRAM<br />

internal banks are read or written during the current transaction.<br />

SDRAM ROW ADDRESS STROBE indicates the presence of a valid<br />

row address on the Multiplexed Address Bus SA[11:0]. See note 1.<br />

SDRAM COLUMN ADDRESS STROBE indicates the presence of<br />

a valid column address on the Multiplexed Address Bus SA[11:0].<br />

Seenote1.<br />

SDRAM DATA MASK controls which of the eight bytes on the data<br />

bus should be written or read. When SDQM[7:0] asserted, the<br />

SDRAM devices do not accept/drive valid data from/to the byte<br />

lanes. When SDQM[7:0] deasserted, the SDRAM devices<br />

accept/drivevaliddatafrom/tothebytelanes.<br />

By convention, SDQM[1] masks two x8 SDRAM devices.<br />

Functionally, all SDQM[7:0] signals are equivalent.<br />

SDRAM WRITE ENABLE indicates that the current memory<br />

transaction is a write operation. See note 1.<br />

SDRAM CHIP ENABLE enables the SDRAM devices for a<br />

memory access (1 per bank supported). See note 1.<br />

SCKE[1:0] are the clock enables for the SDRAM memory.<br />

Deasserting will place the SDRAM in self-refresh mode. See note 1.<br />

DATA BUS carries 64-bit data to and from memory. During a data<br />

(T d ) cycle, read or write data is present on one or more contiguous<br />

bytes, comprising DQ[63:56], DQ[55:48], DQ[47:40], DQ[39:32],<br />

DQ[31:24], DQ[23:16], DQ[15:8] and DQ[7:0]. During write<br />

operations, unused pins are driven to determinate values.<br />

ERROR CORRECTION CODE carries the 8-bit ECC code to and<br />

from memory during data cycles.<br />

ROM OUTPUT ENABLE specifies, during a T a cycle, whether the<br />

operation is a write (1) or read (0) to the ROM interface. It remains<br />

valid during T d cycles. When ROE# is asserted, the data is<br />

transferred from the memory on RAD[16:9].<br />

ROM WRITE ENABLE indicates the direction data is to be<br />

transferred to/from ROM and controls the WE input on the ROM<br />

device. When RWE# is asserted, the data is transferred to the<br />

memory on DQ[7:0].<br />

FLASH CHIP ENABLE enables Flash devices for a memory access.<br />

ROM ADDRESS LATCH ENABLE indicates the cycle in which the<br />

address on RAD[16:3] should be externally latched for the Flash<br />

subsystem.<br />

Data Sheet 17

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 4. Memory Controller Signals (Sheet 2 of 3)<br />

Name Count Type Description<br />

RAD[16:9]<br />

RAD[8]<br />

RAD[7]<br />

RAD[6]/<br />

RST_MODE#<br />

(Config. Pin)<br />

RAD[5]<br />

RAD[4]/<br />

STEST<br />

(Config. Pin)<br />

RAD[3]/<br />

RETRY<br />

(Config. Pin)<br />

8 I/O<br />

5V<br />

Irst(X)<br />

Sync(D)<br />

1 O<br />

Prst(H)<br />

1 O<br />

Prst(H)<br />

1 I/O<br />

5V<br />

Prst(H)<br />

1 O<br />

Prst(H)<br />

1 I/O<br />

5V<br />

Prst(H)<br />

1 I/O<br />

5V<br />

Prst(H)<br />

FLASH ADDRESS/DATA BUS: Duringanaddress(T a ) cycle, bits<br />

16:9 contain a physical word address. During a data cycle (Td), bits<br />

16:9 carry data bits 16:9 of the Flash data byte.<br />

FLASH ADDRESS BUS: During an address (T a ) cycle, bit 8 contain<br />

a physical word address. RAD[8]. multiplexes physical address bits<br />

[22] with [8]. Refer to the MCU chapter of the i960 ® RM/<strong>RN</strong> I/O<br />

<strong>Processor</strong> Developer’s Manual for details.<br />

FLASH ADDRESS BUS: During an address (T a ) cycle, bit 7 contain<br />

a physical word address. RAD[7]. multiplexes physical address bits<br />

[21] with [7]. Refer to the MCU chapter of the i960 ® RM/<strong>RN</strong> I/O<br />

<strong>Processor</strong> Developer’s Manual for details.<br />

FLASH ADDRESS BUS: During an address (T a ) cycle, bit 6 contain<br />

a physical word address. RAD[6]. multiplexes physical address bits<br />

[20] with [6]. Within four clocks after the deassertion of P_RST#,<br />

this pin is an output only. Refer to the MCU chapter of the i960 ®<br />

RM/<strong>RN</strong> I/O <strong>Processor</strong> Developer’s Manual for details.<br />

RESET MODE is sampled at Primary PCI bus reset to determine if<br />

the <strong>80960</strong><strong>RN</strong> processor is to be held in reset. If asserted, the<br />

<strong>80960</strong><strong>RN</strong> processor will be held in reset until the <strong>80960</strong> <strong>Processor</strong><br />

Reset bit is cleared in the Extended Bridge Control Register.<br />

FLASH ADDRESS BUS: During an address (T a ) cycle, bit 5 contain<br />

a physical word address. RAD[5]. multiplexes physical address bits<br />

[19] with [5]. Within four clocks after the deassertion of P_RST#,<br />

this pin is an output only. Refer to the MCU chapter of the i960 ®<br />

RM/<strong>RN</strong> I/O <strong>Processor</strong> Developer’s Manual for details.<br />

FLASH ADDRESS BUS: During an address (T a ) cycle, bit 4 contain<br />

a physical word address. RAD[4]. multiplexes physical address bits<br />

[18] with [4]. Within four clocks after the deassertion of P_RST#,<br />

this pin is an output only. Refer to the MCU chapter of the i960 ®<br />

RM/<strong>RN</strong> I/O <strong>Processor</strong> Developer’s Manual for details.<br />

SELF TEST enables or disables the processor’s internal self-test<br />

feature at initialization. STEST is examined at the end of P_RST#.<br />

When STEST is asserted, the processor performs its internal<br />

self-test and the external bus confidence test. When STEST is<br />

deasserted, the processor performs only the external bus<br />

confidence test.<br />

0 = Self Test Disabled<br />

1 = Self Test Enabled<br />

FLASH ADDRESS BUS: During an address (T a ) cycle, bit 3 contain<br />

a physical word address. RAD[3]. multiplexes physical address bits<br />

[17] with [3]. Within four clocks after the deassertion of P_RST#,<br />

this pin is an output only. Refer to the MCU chapter of the i960 ®<br />

RM/<strong>RN</strong> I/O <strong>Processor</strong> Developer’s Manual for details.<br />

RETRY is sampled at Primary PCI bus reset to determine if the<br />

Primary PCI interface will be disabled. If high, the Primary PCI<br />

interface will disable PCI configuration cycles by signaling a Retry<br />

until the Configuration Cycle Retry bit is cleared in the Extended<br />

Bridge Control Register. If low, the Primary PCI interface allow<br />

configuration cycles to occur.<br />

18 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 4. Memory Controller Signals (Sheet 3 of 3)<br />

Name Count Type Description<br />

RAD[2]/<br />

32BITMEM_EN#<br />

(Config. Pin)<br />

RAD[1]/<br />

32BITPCI_EN#<br />

(Config. Pin)<br />

RAD[0]<br />

1 I/O<br />

5V<br />

Prst(H)<br />

1 I/O<br />

5V<br />

Prst(H)<br />

1 O<br />

Prst(H)<br />

FLASH ADDRESS BUS: During an address (T a ) cycle, bit 2<br />

contains a physical word address. Within four clocks after the<br />

deassertion of P_RST#, this pin is an output only. Refer to the MCU<br />

chapter of the i960 ® RM/<strong>RN</strong> I/O <strong>Processor</strong> Developer’s Manual for<br />

details.<br />

32-BIT Memory Enable The 32BITMEM_EN# signal is sampled at<br />

Primary PCI Reset to notify the memory controller if 32-bit wide<br />

SDRAM memories are connected to the memory controller.<br />

If 32BITMEM_EN# is high, the memory controller supports the<br />

64-bit SDRAM protocol for accesses to SDRAM memories.<br />

If 32BITMEM_EN# is low, the memory controller supports the<br />

32-bit SDRAM protocol for accesses to SDRAM memories.<br />

FLASH ADDRESS BUS: During an address (T a ) cycle, bit 1<br />

contains a physical word address. Within four clocks after the<br />

deassertion of P_RST#, this pin is an output only. Refer to the MCU<br />

chapter of the i960 ® RM/<strong>RN</strong> I/O <strong>Processor</strong> Developer’s Manual for<br />

details.<br />

32-BIT Secondary PCI Enable The 32BITPCI_EN# signal is<br />

sampled at Primary PCI Reset to notify the secondary PCI arbiter<br />

NOT to generate the 64-bit protocol of the rising edge of the<br />

secondary reset for the secondary PCI bus.<br />

If 32BITPCI_EN# is high, the secondary PCI arbiter asserts<br />

S_REQ64# during S_RST#, indicating the secondary PCI bus is a<br />

64-bit bus.<br />

If 32BITPCI_EN# is low, the secondary PCI arbiter does not assert<br />

S_REQ64# during S_RST#, indicating the secondary PCI bus is<br />

NOT a 64-bit bus.<br />

FLASH ADDRESS BUS: During an address (T a ) cycle, bit 0<br />

contains a physical word address. Refer to the MCU chapter of the<br />

i960 ® RM/<strong>RN</strong> I/O <strong>Processor</strong> Developer’s Manual for details.<br />

NOTE:<br />

1. These pins remain functional for 20 DCLKIN periods after I_RST# is asserted for a warm boot. The<br />

designated Irst() state applies after 20 DCLKIN periods after I_RST# is asserted. For more details, refer to<br />

the MCU Chapter of the i960 ® RM/<strong>RN</strong> I/O <strong>Processor</strong> Developer’s Manual.<br />

Data Sheet 19

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 5. Primary PCI Bus Signals (Sheet 1 of 2)<br />

Name Count Type Description<br />

P_AD[31:0] 32<br />

P_AD[63:32] 32<br />

P_PAR 1<br />

P_PAR64 1<br />

P_C/BE[3:0]# 4<br />

P_C/BE[7:4]# 4<br />

P_REQ# 1<br />

P_REQ64# 1<br />

P_GNT# 1<br />

P_ACK64# 1<br />

P_FRAME# 1<br />

P_IRDY# 1<br />

P_TRDY# 1<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

P32(H)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

P32(H)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

P32(H)<br />

O<br />

Prst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

P32(Z)<br />

I<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

P32(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

PRIMARY PCI ADDRESS/DATA is the multiplexed PCI address<br />

and bottom 32 bits of the data bus.<br />

PRIMARY PCI DATA is the upper 32 bits of the primary PCI data<br />

bus driven during the data phase.<br />

PRIMARY PCI BUS PARITY is even parity across P_AD[31:0] and<br />

P_C/BE[3:0]#.<br />

PRIMARY PCI BUS UPPER DWORD PARITY is even parity<br />

across P_AD[63:32] and P_C/BE[7:4]#.<br />

PRIMARY PCI BUS COMMAND and BYTE ENABLES are<br />

multiplexed on the same PCI pins. During the address phase, they<br />

define the bus command. During the data phase, they are used as<br />

byte enables for P_AD[31:0].<br />

PRIMARY PCI BUS BYTE ENABLES are as byte enables for<br />

P_AD[63:32] during the data phase.<br />

PRIMARY PCI BUS REQUEST indicates to the primary PCI bus<br />

arbiter that the <strong>80960</strong><strong>RN</strong> processor desires use of the PCI bus.<br />

PRIMARY PCI BUS REQUEST 64-BIT TRANSFER indicates the<br />

attempt of a 64-bit transaction on the primary PCI bus. If the target<br />

is 64-bit capable, the target acknowledges the attempt with the<br />

assertion of P_ACK64#.<br />

PRIMARY PCI BUS GRANT indicates that access to the primary<br />

PCI bus has been granted.<br />

PRIMARY PCI BUS ACKNOWLEDGE 64-BIT TRANSFER<br />

indicates that the device has positively decoded its address as the<br />

target of the current access and the target is willing to transfer data<br />

using the full 64-bit data bus.<br />

PRIMARY PCI BUS CYCLE FRAME is asserted to indicate the<br />

beginning and duration of an access.<br />

PRIMARY PCI BUS INITIATOR READY indicates the initiating<br />

agent’s ability to complete the current data phase of the<br />

transaction. During a write, it indicates that valid data is present on<br />

the Address/Data bus. During a read, it indicates the processor is<br />

ready to accept the data.<br />

PRIMARY PCI BUS TARGET READY indicates the target agent’s<br />

ability to complete the current data phase of the transaction. During a<br />

read, it indicates that valid data is present on the Address/Data bus.<br />

During a write, it indicates the target is ready to accept the data.<br />

20 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 5. Primary PCI Bus Signals (Sheet 2 of 2)<br />

Name Count Type Description<br />

P_STOP# 1<br />

P_DEVSEL# 1<br />

P_SERR# 1<br />

P_CLK 1<br />

P_RST# 1<br />

P_PERR# 1<br />

P_LOCK# 1<br />

P_IDSEL 1<br />

P_INT[A:D]# 4<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

I/O<br />

5V<br />

OD<br />

Sync(P)<br />

Prst(Z)<br />

I<br />

5V<br />

I<br />

5V<br />

Async<br />

I/O<br />

5V<br />

Sync(P)<br />

Prst(Z)<br />

I<br />

5V<br />

Sync(P)<br />

I<br />

5V<br />

Sync(P)<br />

O<br />

OD<br />

Prst(Z)<br />

PRIMARY PCI BUS STOP indicates a request to stop the current<br />

transaction on the primary PCI bus.<br />

PRIMARY PCI BUS DEVICE SELECT is driven by a target agent<br />

that has successfully decoded the address. As an input, it indicates<br />

whether or not an agent has been selected.<br />

PRIMARY PCI BUS SYSTEM ERROR is driven for address parity<br />

errors on the primary PCI bus.<br />

PRIMARY PCI BUS INPUT CLOCK provides the timing for all<br />

primary PCI transactions and is the clock source for all internal<br />

<strong>80960</strong><strong>RN</strong> units.<br />

PRIMARY RESET brings PCI-specific registers, sequencers, and<br />

signals to a consistent state. When P_RST# is asserted:<br />

PCI output signals are driven to a known consistent state.<br />

PCI bus interface output signals are three-stated.<br />

open drain signals such as P_SERR# are floated.<br />

P_RST# may be asynchronous to P_CLK when asserted or<br />

deasserted. Although asynchronous, deassertion must be<br />

guaranteed to be a clean, bounce-free edge.<br />

PRIMARY PCI BUS PARITY ERROR is asserted when a data<br />

parity error occurs during a primary PCI bus transaction.<br />

PRIMARY PCI BUS LOCK indicates the need to perform an atomic<br />

operation on the primary PCI bus.<br />

PRIMARY PCI BUS INITIALIZATION DEVICE SELECT is used to<br />

select the <strong>80960</strong><strong>RN</strong> during a Configuration Read or Write<br />

command on the primary PCI bus.<br />

PRIMARY PCI BUS INTERRUPT requests an interrupt. The<br />

assertion and deassertion of P_INT[A:D]# is asynchronous to<br />

P_CLK. A device asserts its P_INT[A:D]# line when requesting<br />

attention from its device driver. Once the P_INT[A:D]# signal is<br />

asserted, it remains asserted until the device driver clears the<br />

pending request. P_INT[A:D]# Interrupts are level sensitive.<br />

Table6.<br />

SecondaryPCIArbiterSignals<br />

Name Count Type Description<br />

S_REQ[5:0]#<br />

S_GNT[5:0]#<br />

6 I<br />

5V<br />

Sync(P)<br />

6 O<br />

Srst(Z)<br />

SECONDARY PCI BUS REQUESTS are the request signals from<br />

devices 0 through 5 on the secondary PCI bus.<br />

SECONDARY PCI BUS GRANT are grant signals sent to devices<br />

5-0 on the secondary PCI bus<br />

Data Sheet 21

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 7. Secondary PCI Bus Signals (Sheet 1 of 2)<br />

Name Count Type Description<br />

S_AD[31:0] 32<br />

S_AD[63:32] 32<br />

S_PAR 1<br />

S_PAR64 1<br />

S_C/BE[3:0]# 4<br />

S_C/BE[7:4]# 4<br />

S_REQ64# 1<br />

S_ACK64# 1<br />

S_FRAME# 1<br />

S_IRDY# 1<br />

S_TRDY# 1<br />

S_STOP# 1<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(0)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

S32(H)<br />

I/O<br />

Sync(P)<br />

Srst(0)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

S32(H)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(0)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

S32(H)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Q)<br />

S32(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

S32(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

SECONDARY PCI ADDRESS/DATA is the multiplexed secondary<br />

PCI address and lower 32 bits of the data bus.<br />

SECONDARY PCI DATA is the upper 32 bits of the secondary PCI<br />

data bus.<br />

SECONDARY PCI BUS PARITY is even parity across S_AD[31:0]<br />

and S_C/BE[3:0]#.<br />

SECONDARY PCI BUS UPPER DWORD PARITY is even parity<br />

across S_AD[63:32] and S_C/BE[7:4]#.<br />

SECONDARY PCI BUS COMMAND and BYTE ENABLES are<br />

multiplexed on the same PCI pins. During the address phase, they<br />

define the bus command. During the data phase, they are used as<br />

the byte enables for S_AD[31:0].<br />

SECONDARY PCI BYTE ENABLES are used as byte enables for<br />

S_AD[63:32] during secondary PCI data phases.<br />

SECONDARY PCI BUS REQUEST 64-BIT TRANSFER indicates<br />

the attempt of a 64-bit transaction on the secondary PCI bus. If the<br />

target is 64-bit capable, the target acknowledges the attempt with<br />

the assertion of S_ACK64#.<br />

SECONDARY PCI BUS ACKNOWLEDGE 64-BIT TRANSFER<br />

indicates that the device has positively decoded its address as the<br />

target of the current access, indicates the target is willing to transfer<br />

data using 64 bits.<br />

SECONDARY PCI BUS CYCLE FRAME is asserted to indicate the<br />

beginning and duration of an access.<br />

SECONDARY PCI BUS INITIATOR READY indicates the initiating<br />

agent’s ability to complete the current data phase of the<br />

transaction. During a write, it indicates that valid data is present on<br />

the secondary Address/Data bus. During a read, it indicates the<br />

processor is ready to accept the data.<br />

SECONDARY PCI BUS TARGET READY indicates the target<br />

agent’s ability to complete the current data phase of the<br />

transaction. During a read, it indicates that valid data is present on<br />

the secondary Address/Data bus. During a write, it indicates the<br />

target is ready to accept the data.<br />

SECONDARY PCI BUS STOP indicates a request to stop the<br />

current transaction on the secondary PCI bus.<br />

22 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 7. Secondary PCI Bus Signals (Sheet 2 of 2)<br />

Name Count Type Description<br />

S_DEVSEL# 1<br />

S_SERR# 1<br />

S_RST# 1<br />

S_PERR# 1<br />

S_LOCK# 1<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

I/O<br />

5V<br />

OD<br />

Sync(P)<br />

Srst(Z)<br />

O<br />

Async<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

I/O<br />

5V<br />

Sync(P)<br />

Srst(Z)<br />

SECONDARY PCI BUS DEVICE SELECT is driven by a target<br />

agent that has successfully decoded the address. As an input, it<br />

indicates whether or not an agent has been selected.<br />

SECONDARY PCI BUS SYSTEM ERROR is driven for address<br />

parity errors on the secondary PCI bus.<br />

SECONDARY PCI BUS RESET is an output based on P_RST#. It<br />

brings PCI-specific registers, sequencers, and signals to a<br />

consistent state. When P_RST# is asserted or BCR[6] is set, it<br />

causes S_RST# to assert and:<br />

• PCI output signals are driven to a known consistent state.<br />

• PCI bus interface output signals are three-stated.<br />

• open drain signals such as S_SERR# are floated<br />

S_RST# may be asynchronous to S_CLKIN when asserted or<br />

deasserted. Although asynchronous, deassertion must be<br />

guaranteed to be a clean, bounce-free edge.<br />

SECONDARY PCI BUS PARITY ERROR is asserted when a data<br />

parity error during a secondary PCI bus transaction.<br />

SECONDARY PCI BUS LOCK indicates the need to perform an<br />

atomic operation on the secondary PCI bus.<br />

Data Sheet 23

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 8.<br />

Intel ® <strong>80960</strong>Jx Core Signals and Configuration Straps<br />

Name Count Type Description<br />

SECONDARY PCI BUS INTERRUPT REQUESTS. S_INT[D:A]#<br />

assertion and deassertion is asynchronous to P_CLK. Asdevice<br />

asserts S_INT[D:A]# when requesting attention from it device<br />

driver. When S_INT[D:A]# is asserted, it remains asserted until the<br />

device driver clears the pending request. S_INT[D:A]# interrupts<br />

are level low sensitive.<br />

XINT[3:0]#/<br />

S_INT[D:A]#<br />

4<br />

I<br />

5V<br />

Async<br />

EXTE<strong>RN</strong>AL INTERRUPT. External devices use this signal to<br />

request an interrupt service. These signals operate in dedicated<br />

mode, where each signal is assigned a dedicated interrupt level.<br />

The S_INT[D:A]#/XINT[3:0]# signals can be directed as follows:<br />

Sec. PCIPrimary PCIi960 core processor<br />

S_INTA#⇒P_INTA# or XINT0#<br />

S_INTB#⇒P_INTB# or XINT1#<br />

S_INTC#⇒P_INTC# or XINT2#<br />

S_INTD#⇒P_INTD# or XINT3#<br />

XINT[5:4]# 2<br />

NMI# 1<br />

I<br />

5V<br />

Async<br />

I<br />

5V<br />

Async<br />

EXTE<strong>RN</strong>AL INTERRUPT pins are used to request <strong>80960</strong><strong>RN</strong><br />

interrupt service.<br />

NON-MASKABLE INTERRUPT causes an i960 core processor<br />

non-maskable interrupt event to occur. NMI# is the highest priority<br />

interrupt source.<br />

V CC5REF 1 -<br />

V CCPLL 3 -<br />

INPUT REFERENCE VOLTAGE is strapped to 5 V. This reference<br />

voltage allows the <strong>80960</strong><strong>RN</strong> input pins to be 5 V tolerant.<br />

PLL POWER is a separate V CC supply pin for the phase lock loop<br />

clock generator. It is intended for external connection to the V CC<br />

board plane. In noisy environments, add a simple bypass filter<br />

circuit to reduce noise-induced clock jitter and its effects on timing<br />

relationships.<br />

FAIL# 1<br />

O<br />

Irst(0)<br />

FAIL indicates a failure of the processor’s built-in self-test<br />

performed during initialization. FAIL# is asserted immediately upon<br />

reset and toggles during self-test to indicate the status of individual<br />

tests:<br />

When self-test passes, the processor deasserts FAIL# and<br />

commences operation from user code.<br />

When self-test fails, the processor asserts FAIL# and then stops<br />

executing. Self-test failing does not cause the bridge to stop<br />

execution.<br />

0 = Self Test Failed<br />

1 = Self Test Passed<br />

24 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 9.<br />

I 2 C, JTAG, Core Signals<br />

Name Count Type Description<br />

TCK 1<br />

I<br />

5V<br />

TEST CLOCK is an input which provides the clocking function for<br />

the IEEE 1149.1 Boundary Scan Testing (JTAG). State information<br />

and data are clocked into the component on the rising edge and<br />

data is clocked out of the component on the falling edge.<br />

TDI 1<br />

I<br />

5V<br />

Sync(T)<br />

TDO 1 O<br />

TEST DATA INPUT is the serial input pin for the JTAG feature. TDI<br />

is sampled on the rising edge of TCK, during the SHIFT-IR and<br />

SHIFT-DR states of the Test Access Port. This signal has a weak<br />

internal pull-up to ensure proper operation when this signal is<br />

unconnected.<br />

TEST DATA OUTPUT is the serial output pin for the JTAG feature.<br />

TDO is driven on the falling edge of TCK during the SHIFT-IR and<br />

SHIFT-DR states of the Test Access Port. At other times, TDO floats.<br />

TRST# 1<br />

TMS 1<br />

SDA 1<br />

SCL 1<br />

LCDINIT# 1<br />

I_RST# 1<br />

ONCE#<br />

(Config. Pin)<br />

1<br />

I<br />

5V<br />

Async<br />

I<br />

5V<br />

Sync(T)<br />

I/O<br />

5V<br />

OD<br />

Irst(Z)<br />

I/O<br />

5V<br />

OD<br />

Irst(Z)<br />

I<br />

Sync(I)<br />

O<br />

Async<br />

I<br />

5V<br />

TEST RESET asynchronously resets the Test Access Port (TAP)<br />

controller function of IEEE 1149.1 Boundary Scan Testing (JTAG).<br />

This signal has a weak internal pull-up to ensure proper operation<br />

when this signal is unconnected.<br />

TEST MODE SELECT is sampled at the rising edge of TCK to<br />

select the operation of the test logic for IEEE 1149.1 Boundary<br />

Scan testing. This signal has a weak internal pull-up to ensure<br />

proper operation when this signal is unconnected.<br />

I 2 CDATAis used for data transfer and arbitration on the I 2 Cbus.<br />

I 2 CCLOCKprovides synchronous operation of the I 2 Cbus.<br />

LCD INITIALIZATION is a static signal used to initialize the internal<br />

logic for the LCD960 debugger. This signal has an internal pull-up<br />

for normal operation.<br />

INTE<strong>RN</strong>AL BUS RESET indicates when the internal bus has been<br />

reset with P_RST# or a software reset.<br />

ONCE MODE: The processor samples this pin during reset. If it is<br />

asserted LOW at the end of reset, the processor enters ONCE<br />

Mode. In ONCE Mode, the processor stops all clocks and floats all<br />

output pins except the TDO and RAD[8:0] pins. The pin has a weak<br />

internal pull-up which is active during reset to ensure normal<br />

operation if the pin is left unconnected.<br />

Data Sheet 25

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

3.1.2 540-Lead H-PBGA Package<br />

Figure 3.<br />

540L H-PBGA Package Diagram (Top and Side View)<br />

Pin#1Corner<br />

42.500 ± 0.200<br />

GC<strong>80960</strong><strong>RN</strong>100<br />

SSSSSS<br />

MALAY<br />

FFFFFFFF-[{SN}]<br />

M<br />

INTEL © ‘98<br />

27.700<br />

27.700<br />

42.500 ± 0.200<br />

0.55 ± 0.15<br />

Slug<br />

1.56 REF<br />

Seating Plane<br />

1.025 ± 0.075<br />

3.845 ± 0.255<br />

Ball spacing is 1.270<br />

Ball width is 0.750 ± 0.150<br />

2.150 ± 0.150<br />

NOTES:<br />

1. All dimensions and tolerances conform to ANSI Y14.5M 1982.<br />

2. Dimensions are measured at the maximum solder ball diameter parallel to primary datum.<br />

3. Primary datum and seating plane are defined by the spherical crowns of the solder balls.<br />

4. All dimensions are in millimeters.<br />

5. S spec numbers are only printed on the C-X steppings.<br />

26 Data Sheet

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Figure 4.<br />

540L H-PBGA Package Diagram (Bottom View)<br />

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32<br />

AM<br />

AL<br />

AK<br />

AJ<br />

AH<br />

AG<br />

AF<br />

AE<br />

AD<br />

AC<br />

AB<br />

AA<br />

Y<br />

W<br />

V<br />

U<br />

T<br />

R<br />

P<br />

N<br />

M<br />

L<br />

K<br />

J<br />

H<br />

G<br />

F<br />

E<br />

D<br />

C<br />

B<br />

A<br />

AM<br />

AL<br />

AK<br />

AJ<br />

AH<br />

AG<br />

AF<br />

AE<br />

AD<br />

AC<br />

AB<br />

AA<br />

Y<br />

W<br />

V<br />

U<br />

T<br />

R<br />

P<br />

N<br />

M<br />

L<br />

K<br />

J<br />

H<br />

G<br />

F<br />

E<br />

D<br />

C<br />

B<br />

A<br />

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32<br />

Data Sheet 27

Intel ® <strong>80960</strong><strong>RN</strong> I/O <strong>Processor</strong><br />

Table 10. 540-Lead H-PBGA Package — Signal Name Order (Sheet 1 of 5)<br />

Signal Ball # Signal Ball # Signal Ball #<br />

DCLKIN E21 DQ35 C24 N/C AG1<br />

DCLKOUT A22 DQ36 E24 N/C AL16<br />

DQ00 D22 DQ37 B25 P_ACK64# V5<br />

DQ01 A23 DQ38 E25 P_AD00 U1<br />

DQ02 C23 DQ39 C26 P_AD01 U2<br />

DQ03 A24 DQ40 A27 P_AD02 U3<br />

DQ04 D24 DQ41 C27 P_AD03 T1<br />

DQ05 A25 DQ42 A28 P_AD04 T3<br />

DQ06 C25 DQ43 G32 P_AD05 T4<br />

DQ07 A26 DQ44 H31 P_AD06 T5<br />

DQ08 E26 DQ45 H28 P_AD07 R1<br />

DQ09 B27 DQ46 J30 P_AD08 R3<br />