FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

FR60 MB91460E Series - Microcontrollers - Fujitsu

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

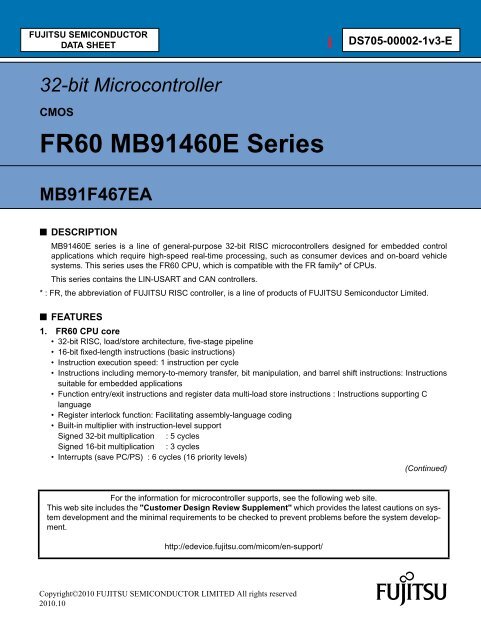

FUJITSU SEMICONDUCTOR<br />

DATA SHEET<br />

32-bit Microcontroller<br />

CMOS<br />

<strong>FR60</strong> <strong>MB91460E</strong> <strong>Series</strong><br />

MB91F467EA<br />

■ DESCRIPTION<br />

<strong>MB91460E</strong> series is a line of general-purpose 32-bit RISC microcontrollers designed for embedded control<br />

applications which require high-speed real-time processing, such as consumer devices and on-board vehicle<br />

systems. This series uses the <strong>FR60</strong> CPU, which is compatible with the FR family* of CPUs.<br />

This series contains the LIN-USART and CAN controllers.<br />

* : FR, the abbreviation of FUJITSU RISC controller, is a line of products of FUJITSU Semiconductor Limited.<br />

■ FEATURES<br />

1. <strong>FR60</strong> CPU core<br />

• 32-bit RISC, load/store architecture, five-stage pipeline<br />

• 16-bit fixed-length instructions (basic instructions)<br />

• Instruction execution speed: 1 instruction per cycle<br />

• Instructions including memory-to-memory transfer, bit manipulation, and barrel shift instructions: Instructions<br />

suitable for embedded applications<br />

• Function entry/exit instructions and register data multi-load store instructions : Instructions supporting C<br />

language<br />

• Register interlock function: Facilitating assembly-language coding<br />

• Built-in multiplier with instruction-level support<br />

Signed 32-bit multiplication : 5 cycles<br />

Signed 16-bit multiplication : 3 cycles<br />

• Interrupts (save PC/PS) : 6 cycles (16 priority levels)<br />

(Continued)<br />

For the information for microcontroller supports, see the following web site.<br />

This web site includes the "Customer Design Review Supplement" which provides the latest cautions on system<br />

development and the minimal requirements to be checked to prevent problems before the system development.<br />

http://edevice.fujitsu.com/micom/en-support/<br />

Copyright©2010 FUJITSU SEMICONDUCTOR LIMITED All rights reserved<br />

2010.10<br />

DS705-00002-1v3-E

<strong>MB91460E</strong> <strong>Series</strong><br />

(Continued)<br />

• Harvard architecture enabling program access and data access to be performed simultaneously<br />

• Instructions compatible with the FR family<br />

2. Internal peripheral resources<br />

• General-purpose ports : Maximum 170 ports<br />

• DMAC (DMA Controller)<br />

Maximum of 5 channels able to operate simultaneously. (External to external : 1 channel)<br />

3 transfer sources (external pin/internal peripheral/software)<br />

Activation source can be selected using software.<br />

Addressing mode specifies full 32-bit addresses (increment/decrement/fixed)<br />

Transfer mode (demand transfer/burst transfer/step transfer/block transfer)<br />

Transfer data size selectable from 8/16/32-bit<br />

Multi-byte transfer enabled (by software)<br />

DMAC descriptor in I/O areas (200H to 240H, 1000H to 1024H)<br />

• A/D converter (successive approximation type)<br />

10-bit resolution: 24 channels<br />

Conversion time: minimum 1 µs<br />

• External interrupt inputs : 14 channels<br />

8 channels shared with CAN RX or I2C pins<br />

• Bit search module (for REALOS)<br />

Function to search from the MSB (most significant bit) for the position of the first “0”, “1”, or changed bit in a word<br />

• LIN-USART (full duplex double buffer): 5 channels<br />

Clock synchronous/asynchronous selectable<br />

Sync-break detection<br />

Internal dedicated baud rate generator<br />

• I 2 C* bus interface (supports 400 kbps): 3 channels<br />

Master/slave transmission and reception<br />

Arbitration function, clock synchronization function<br />

• CAN controller (C-CAN): 2 channels<br />

Maximum transfer speed: 1 Mbps<br />

32 transmission/reception message buffers<br />

• Stepper motor controller : 6 channels<br />

4 high current output to each channel<br />

2 synchronized PWMs per channel (8/10-bit)<br />

• Sound generator : 1 channel<br />

Tone frequency : PWM frequency divide-by-two (reload value + 1)<br />

• Alarm comparator : 1 channel<br />

Monitor external voltage<br />

Generate an interrupt in case of voltage lower/higher than the defined thresholds (reference voltage)<br />

• 16-bit PPG timer : 12 channels<br />

• 16-bit PFM timer : 1 channel<br />

• 16-bit reload timer: 8 channels<br />

• 16-bit free-run timer: 8 channels (1 channel each for ICU and OCU)<br />

• Input capture: 8 channels (operates in conjunction with the free-run timer)<br />

• Output compare: 4 channels (operates in conjunction with the free-run timer)<br />

• Up/Down counter: 3 channels (3*8-bit or 1*16-bit + 1*8-bit)<br />

• Watchdog timer<br />

(Continued)<br />

2 DS705-00002-1v3-E

<strong>MB91460E</strong> <strong>Series</strong><br />

(Continued)<br />

• Real-time clock<br />

• Low-power consumption modes : Sleep/stop mode function<br />

• Supply Supervisor: Low voltage detection circuit for external VDD5 and internal 1.8V core voltage<br />

• Clock supervisor<br />

Monitors the sub-clock (32 kHz) and the main clock (4 MHz) , and switches to a recovery clock (CR oscillator,<br />

etc.) when the oscillations stop.<br />

• Clock modulator<br />

• Clock monitor<br />

• Sub-clock calibration<br />

Corrects the real-time clock timer when operating with the 32 kHz or CR oscillator<br />

• Main oscillator stabilization timer<br />

Generates an interrupt in sub-clock mode after the stabilization wait time has elapsed on the 23-bit stabilization<br />

wait time counter<br />

• Sub-oscillator stabilization timer<br />

Generates an interrupt in main clock mode after the stabilization wait time has elapsed on the 15-bit stabilization<br />

wait time counter<br />

3. Shutdown mode<br />

• In low leakage shutdown mode, the internal main power supply is switched off. Only the following resources<br />

and meories remain active:<br />

- Standby RAM (16 KByte)<br />

- Real Time Clock<br />

- 4 MHz oscillator, 32 kHz oscillator, RC oscillator<br />

- Power management logic<br />

- Hardware Watchdog and Clock Supervisor<br />

4. Package and technology<br />

• Package : LQFP-208 (low profile QFP)<br />

• CMOS 0.18 µm technology<br />

• Power supply range 3 V to 5 V (1.9V/1.8 V internal logic provided by a step-down voltage converter)<br />

• Operating temperature range: between − 40˚C and + 105˚C<br />

DS705-00002-1v3-E 3

<strong>MB91460E</strong> <strong>Series</strong><br />

■ PRODUCT LINEUP<br />

Feature MB91FV460B<br />

MB91F467DA<br />

MB91F467DB<br />

MB91F467EA<br />

Max. core frequency (CLKB) 100MHz 96MHz 100MHz<br />

Max. resource frequency (CLKP) 50MHz 48MHz 50MHz<br />

Max. external bus freq. (CLKT) 50MHz 48MHz 50MHz<br />

Max. CAN frequency (CLKCAN) 50MHz 48MHz 50MHz<br />

Technology 0.18um 0.18um 0.18um<br />

Software-Watchdog yes yes yes<br />

Hardware-Watchdog<br />

(RC osc. based)<br />

yes (disengageable),<br />

can be activated in<br />

SLEEP/STOP<br />

4 DS705-00002-1v3-E<br />

yes<br />

yes,<br />

can be activated in<br />

SLEEP/STOP<br />

Bit Search yes yes yes<br />

Reset input (INITX) yes yes yes<br />

Clock Modulator yes yes yes<br />

Clock Monitor yes yes yes<br />

Low Power Mode yes yes yes<br />

Shutdown Mode<br />

no,<br />

emulation by software<br />

no yes<br />

DMA 5 ch 5 ch 5 ch<br />

MMU/MPU MPU (16 ch) 1) MPU (8 ch) 1) MPU (8 ch) 1)<br />

Flash memory<br />

2112 KByte or external<br />

emulation SRAM<br />

1088 KByte 1088 KByte<br />

Flash Protection yes yes yes<br />

D-RAM 64 KByte 32 KByte 64 KByte<br />

ID-RAM 64 KByte 32 KByte 48 KByte<br />

Standby RAM no no 16 KByte<br />

Flash-Cache (F-cache) 16 KByte 8 KByte 8 KByte<br />

Boot-ROM / BI-ROM 16 KByte Boot Flash 4 KByte 4 KByte<br />

RTC 1 ch 1 ch 1 ch<br />

Free Running Timer 8 ch 8 ch 8 ch<br />

ICU 8 ch 8 ch 8 ch<br />

OCU 8 ch 4 ch 4 ch<br />

Reload Timer 8 ch 8 ch 8 ch<br />

PPG 16-bit 16 ch 12 ch 12 ch<br />

PFM 16-bit 1 ch 1 ch 1 ch

<strong>MB91460E</strong> <strong>Series</strong><br />

Sound Generator 1 ch 1 ch 1 ch<br />

Up/Down Counter (8/16-bit) 4 ch (8-bit)/2ch(16-bit) 3 ch (8-bit) / 1 ch (16-bit) 3 ch (8-bit)/1ch(16-bit)<br />

C_CAN 6 ch (128msg) 3 ch (32msg) 2 ch (32msg)<br />

LIN-USART 16 ch FIFO 1 ch + 4 ch FIFO 1 ch + 4 ch FIFO<br />

I2C (400k) 8 ch 3 ch 3 ch<br />

FR external bus<br />

yes (32bit addr,<br />

32bit data)<br />

yes (26bit addr,<br />

32bit data)<br />

yes (26bit addr,<br />

32bit data)<br />

External Interrupts 32 ch 14 ch 14 ch<br />

SMC 6 ch 6 ch 6 ch<br />

ADC (10 bit)<br />

Feature MB91FV460B<br />

32 ch, with<br />

Range Comparator<br />

MB91F467DA<br />

MB91F467DB<br />

DS705-00002-1v3-E 5<br />

24 ch<br />

MB91F467EA<br />

24 ch, with<br />

Range Comparator<br />

Alarm Comparator 2 ch 1 ch 1 ch<br />

Supply Supervisor<br />

(low voltage detection)<br />

yes yes yes<br />

Clock Supervisor yes yes yes<br />

Main clock oscillator 4MHz 4MHz 4MHz<br />

Sub clock oscillator 32kHz 32kHz 32kHz<br />

RC Oscillator 100kHz / 2MHz 100kHz / 2MHz 100kHz / 2MHz<br />

PLL x 25 x 24 x 25<br />

DSU4 yes - -<br />

EDSU yes (32 BP) *1 yes (16 BP) *1 yes (16 BP) *1<br />

Supply Voltage 1.8V + 3V / 5V 3V / 5V 3V / 5V<br />

Regulator no yes yes<br />

Power Consumption n.a. < 2 W < 1.3 W<br />

Temperatur Range (Ta) 0..70 C -40..105 C -40..105 C<br />

Package BGA896 QFP208 LQFP208

<strong>MB91460E</strong> <strong>Series</strong><br />

Feature MB91FV460B<br />

MB91F467DA<br />

MB91F467DB<br />

Power on to PLL run < 20 ms < 20 ms < 20 ms<br />

Flash Download Time < 8 sec typical < 6 sec typical < 6 sec typical<br />

*1 : MPU channels use EDSU breakpoint registers (shared operation between MPU and EDSU).<br />

MB91F467EA<br />

6 DS705-00002-1v3-E

<strong>MB91460E</strong> <strong>Series</strong><br />

DS705-00002-1v3-E 7<br />

■ PIN ASSIGNMENT<br />

1. MB91F467EA<br />

(TOP VIEW)<br />

FPT-208P-M06<br />

Note: Difference versus MB91460D series: At pins 95+96, RX2 and TX2 of CAN2 are removed.<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

16<br />

17<br />

18<br />

19<br />

20<br />

21<br />

22<br />

23<br />

24<br />

25<br />

26<br />

27<br />

28<br />

29<br />

30<br />

31<br />

32<br />

33<br />

34<br />

35<br />

36<br />

37<br />

38<br />

39<br />

40<br />

41<br />

42<br />

43<br />

44<br />

45<br />

46<br />

47<br />

48<br />

49<br />

50<br />

51<br />

52<br />

156<br />

155<br />

154<br />

153<br />

152<br />

151<br />

150<br />

149<br />

148<br />

147<br />

146<br />

145<br />

144<br />

143<br />

142<br />

141<br />

140<br />

139<br />

138<br />

137<br />

136<br />

135<br />

134<br />

133<br />

132<br />

131<br />

130<br />

129<br />

128<br />

127<br />

126<br />

125<br />

124<br />

123<br />

122<br />

121<br />

120<br />

119<br />

118<br />

117<br />

116<br />

115<br />

114<br />

113<br />

112<br />

111<br />

110<br />

109<br />

108<br />

107<br />

106<br />

105<br />

VDD5<br />

P29_7/AN7<br />

P29_6/AN6<br />

P29_5/AN5<br />

P29_4/AN4<br />

P29_3/AN3<br />

P29_2/AN2<br />

P29_1/AN1<br />

P29_0/AN0<br />

ALARM_0<br />

AVCC5<br />

AVRH5<br />

AVSS5<br />

P16_7/PPG15/ATGX<br />

P16_6/PPG14/PFM<br />

P16_5/PPG13/SGO<br />

P16_4/PPG12/SGA<br />

P16_3/PPG11<br />

P16_2/PPG10<br />

P16_1/PPG9<br />

P16_0/PPG8<br />

P17_7/PPG7<br />

P17_6/PPG6<br />

P17_5/PPG5<br />

P17_4/PPG4<br />

VSS5<br />

VDD5<br />

P14_7/ICU7/TIN7/TTG7/15<br />

P14_6/ICU6/TIN6/TTG6/14<br />

P14_5/ICU5/TIN5/TTG5/13<br />

P14_4/ICU4/TIN4/TTG4/12<br />

P14_3/ICU3/TIN3/TTG11<br />

P14_2/ICU2/TIN2/TTG10<br />

P14_1/ICU1/TIN1/TTG9<br />

P14_0/ICU0/TIN0/TTG8<br />

P15_3/OCU3/TOT3<br />

P15_2/OCU2/TOT2<br />

P15_1/OCU1/TOT1<br />

P15_0/OCU0/TOT0<br />

P18_6/SCK7/ZIN3/CK7<br />

P18_5/SOT7/BIN3<br />

P18_4/SIN7/AIN3<br />

P18_2/SCK6/ZIN2/CK6<br />

P18_1/SOT6/BIN2<br />

P18_0/SIN6/AIN2<br />

P19_6/SCK5/CK5<br />

P19_5/SOT5<br />

P19_4/SIN5<br />

P19_2/SCK4/CK4<br />

P19_1/SOT4<br />

P19_0/SIN4<br />

VSS5<br />

VSS5<br />

P01_0/D16<br />

P01_1/D17<br />

P01_2/D18<br />

P01_3/D19<br />

P01_4/D20<br />

P01_5/D21<br />

P01_6/D22<br />

P01_7/D23<br />

P00_0/D24<br />

P00_1/D25<br />

P00_2/D26<br />

P00_3/D27<br />

P00_4/D28<br />

P00_5/D29<br />

P00_6/D30<br />

P00_7/D31<br />

P07_0/A0<br />

P07_1/A1<br />

P07_2/A2<br />

P07_3/A3<br />

P07_4/A4<br />

P07_5/A5<br />

P07_6/A6<br />

P07_7/A7<br />

VDD35<br />

VSS5<br />

P06_0/A8<br />

P06_1/A9<br />

P06_2/A10<br />

P06_3/A11<br />

P06_4/A12<br />

P06_5/A13<br />

P06_6/A14<br />

P06_7/A15<br />

P05_0/A16<br />

P05_1/A17<br />

P05_2/A18<br />

P05_3/A19<br />

P05_4/A20<br />

P05_5/A21<br />

P05_6/A22<br />

P05_7/A23<br />

P04_0/A24<br />

P04_1/A25<br />

P08_0/WRX0<br />

P08_1/WRX1<br />

P08_2/WRX2<br />

P08_3/WRX3<br />

P08_4/RDX<br />

P08_5/BGRNTX<br />

VDD35<br />

53<br />

54<br />

55<br />

56<br />

57<br />

58<br />

59<br />

60<br />

61<br />

62<br />

63<br />

64<br />

65<br />

66<br />

67<br />

68<br />

69<br />

70<br />

71<br />

72<br />

73<br />

74<br />

75<br />

76<br />

77<br />

78<br />

79<br />

80<br />

81<br />

82<br />

83<br />

84<br />

85<br />

86<br />

87<br />

88<br />

89<br />

90<br />

91<br />

92<br />

93<br />

94<br />

95<br />

96<br />

97<br />

98<br />

99<br />

100<br />

101<br />

102<br />

103<br />

104<br />

208<br />

207<br />

206<br />

205<br />

204<br />

203<br />

202<br />

201<br />

200<br />

199<br />

198<br />

197<br />

196<br />

195<br />

194<br />

193<br />

192<br />

191<br />

190<br />

189<br />

188<br />

187<br />

186<br />

185<br />

184<br />

183<br />

182<br />

181<br />

180<br />

179<br />

178<br />

177<br />

176<br />

175<br />

174<br />

173<br />

172<br />

171<br />

170<br />

169<br />

168<br />

167<br />

166<br />

165<br />

164<br />

163<br />

162<br />

161<br />

160<br />

159<br />

158<br />

157<br />

VDD35<br />

P02_7/D15<br />

P02_6/D14<br />

P02_5/D13<br />

P02_4/D12<br />

P02_3/D11<br />

P02_2/D10<br />

P02_1/D9<br />

P02_0/D8<br />

P03_7/D7<br />

P03_6/D6<br />

P03_5/D5<br />

P03_4/D4<br />

P03_3/D3<br />

P03_2/D2<br />

P03_1/D1<br />

P03_0/D0<br />

P13_2/DEOTX0/DEOP0<br />

P13_1/DACKX0<br />

P13_0/DREQ0<br />

VSS5<br />

P25_7/SMC2M5<br />

P25_6/SMC2P5<br />

P25_5/SMC1M5<br />

P25_4/SMC1P5<br />

HVSS5<br />

HVDD5<br />

P25_3/SMC2M4<br />

P25_2/SMC2P4<br />

P25_1/SMC1M4<br />

P25_0/SMC1P4<br />

P26_7/SMC2M3/AN31<br />

P26_6/SMC2P3/AN30<br />

P26_5/SMC1M3/AN29<br />

P26_4/SMC1P3/AN28<br />

HVSS5<br />

HVDD5<br />

P26_3/SMC2M2/AN27<br />

P26_2/SMC2P2/AN26<br />

P26_1/SMC1M2/AN25<br />

P26_0/SMC1P2/AN24<br />

P27_7/SMC2M1/AN23<br />

P27_6/SMC2P1/AN22<br />

P27_5/SMC1M1/AN21<br />

P27_4/SMC1P1/AN20<br />

HVSS5<br />

HVDD5<br />

P27_3/SMC2M0/AN19<br />

P27_2/SMC2P0/AN18<br />

P27_1/SMC1M0/AN17<br />

P27_0/SMC1P0/AN16<br />

VSS5<br />

VSS5<br />

P08_6/BRQ<br />

P08_7/RDY<br />

P09_0/CSX0<br />

P09_1/CSX1<br />

P09_2/CSX2<br />

P09_3/CSX3<br />

P09_6/CSX6<br />

P09_7/CSX7<br />

P10_1/ASX<br />

P10_2/BAAX<br />

P10_3/WEX<br />

P10_4/MCLKO<br />

P10_5/MCLKI<br />

P10_6/MCLKE<br />

MONCLK<br />

VSS5<br />

MD_2<br />

MD_1<br />

MD_0<br />

INITX<br />

X1A<br />

X0A<br />

X1<br />

X0<br />

VDD5<br />

VSS5<br />

VCC18C<br />

VDD5R<br />

VDD5R<br />

P24_0/INT0<br />

P24_1/INT1<br />

P24_2/INT2<br />

P24_3/INT3<br />

P24_4/INT4/SDA2<br />

P24_5/INT5/SCL2<br />

P24_6/INT6/SDA3<br />

P24_7/INT7/SCL3<br />

P23_0/RX0/INT8<br />

P23_1/TX0<br />

P23_2/RX1/INT9<br />

P23_3/TX1<br />

P23_4/INT10<br />

P23_5<br />

P22_0/INT12<br />

P22_2/INT13<br />

P22_4/SDA0/INT14<br />

P22_5/SCL0<br />

P20_0/SIN2/AIN0<br />

P20_1/SOT2/BIN0<br />

P20_2/SCK2/ZIN0/CK2<br />

VDD5<br />

QFP-208

<strong>MB91460E</strong> <strong>Series</strong><br />

■ PIN DESCRIPTION<br />

1. MB91F467EA<br />

Pin no. Pin name I/O<br />

2 to 9<br />

10 to 17<br />

18 to 25<br />

28 to 35<br />

36 to 43<br />

44, 45<br />

46 to 49<br />

50<br />

51<br />

54<br />

55<br />

56 to 59<br />

60, 61<br />

62<br />

63<br />

64<br />

65<br />

I/O circuit<br />

type * 1<br />

Function<br />

P01_0 to P01_7<br />

General-purpose input/output ports<br />

I/O A<br />

D16 to D23 Signal pins of external data bus (bit16 to bit23)<br />

P00_0 to P00_7<br />

General-purpose input/output ports<br />

I/O A<br />

D24 to D31 Signal pins of external data bus (bit24 to bit31)<br />

P07_0 to P07_7<br />

General-purpose input/output ports<br />

I/O A<br />

A0 to A7 Signal pins of external address bus (bit0 to bit7)<br />

P06_0 to P06_7<br />

General-purpose input/output ports<br />

I/O A<br />

A8 to A15 Signal pins of external address bus (bit8 to bit15)<br />

P05_0 to P05_7<br />

General-purpose input/output ports<br />

I/O A<br />

A16 to A23 Signal pins of external address bus (bit16 to bit23)<br />

P04_0, P04_1<br />

General-purpose input/output ports<br />

I/O A<br />

A24, A25 Signal pins of external address bus (bit24, bit25)<br />

P08_0 to P08_3<br />

General-purpose input/output ports<br />

I/O A<br />

WRX0 to WRX3 External write strobe output pins<br />

P08_4<br />

General-purpose input/output port<br />

I/O A<br />

RDX External read strobe output pin<br />

P08_5<br />

General-purpose input/output port<br />

I/O A<br />

BGRNTX External bus release reception output pin<br />

P08_6<br />

General-purpose input/output port<br />

I/O A<br />

BRQ External bus release request input pin<br />

P08_7<br />

General-purpose input/output port<br />

I/O A<br />

RDY External ready input pin<br />

P09_0 to P09_3<br />

General-purpose input/output ports<br />

I/O A<br />

CSX0 to CSX3 Chip select output pins<br />

P09_6, P09_7<br />

General-purpose input/output ports<br />

I/O A<br />

CSX6, CSX7 Chip select output pins<br />

P10_1<br />

General-purpose input/output port<br />

I/O A<br />

ASX Address strobe output pin<br />

P10_2<br />

General-purpose input/output port<br />

I/O A<br />

BAAX Burst address advance output pin<br />

P10_3<br />

General-purpose input/output port<br />

I/O A<br />

WEX Write enable output pin<br />

P10_4<br />

General-purpose input/output port<br />

I/O A<br />

MCLKO Clock output pin for memory<br />

(Continued)<br />

8 DS705-00002-1v3-E

(Continued)<br />

Pin no. Pin name I/O<br />

66<br />

I/O circuit<br />

type *1<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

Function<br />

P10_5<br />

General-purpose input/output port<br />

I/O A<br />

MCLKI Clock input pin for memory<br />

67<br />

P10_6<br />

MCLKE<br />

I/O A<br />

General-purpose input/output port<br />

Clock enable signal pin for memory<br />

68 MONCLK O M Clock monitor pin<br />

70 MD_2 I G<br />

71 MD_1 I G Mode setting pins<br />

72 MD_0 I G<br />

73 INITX I H External reset input pin<br />

74 X1A ⎯ J2 Sub clock (oscillation) output<br />

75 X0A ⎯ J2 Sub clock (oscillation) input<br />

76 X1 ⎯ J1 Clock (oscillation) output<br />

77 X0 ⎯ J1 Clock (oscillation) input<br />

83 to 86<br />

87<br />

88<br />

89<br />

90<br />

91<br />

92<br />

93<br />

P24_0 to P24_3<br />

General-purpose input/output ports<br />

I/O A<br />

INT0 to INT3 External interrupt input pins<br />

P24_4<br />

General-purpose input/output port<br />

INT4 I/O C External interrupt input pin<br />

SDA2 I2C bus DATA input/output pin<br />

P24_5<br />

General-purpose input/output port<br />

INT5 I/O C External interrupt input pin<br />

SCL2 I2C bus clock input/output pin<br />

P24_6<br />

General-purpose input/output port<br />

INT6 I/O C External interrupt input pin<br />

SDA3 I2C bus DATA input/output pin<br />

P24_7<br />

General-purpose input/output port<br />

INT7 I/O C External interrupt input pin<br />

SCL3 I2C bus clock input/output pin<br />

P23_0<br />

General-purpose input/output port<br />

RX0 I/O A RX input pin of CAN0<br />

INT8 External interrupt input pin<br />

P23_1<br />

General-purpose input/output port<br />

I/O A<br />

TX0 TX output pin of CAN0<br />

P23_2<br />

General-purpose input/output port<br />

RX1 I/O A RX input pin of CAN1<br />

INT9 External interrupt input pin<br />

(Continued)<br />

DS705-00002-1v3-E 9

<strong>MB91460E</strong> <strong>Series</strong><br />

(Continued)<br />

Pin no. Pin name I/O<br />

I/O circuit<br />

type *1<br />

Function<br />

94<br />

P23_3<br />

TX1<br />

I/O A<br />

General-purpose input/output port<br />

TX output pin of CAN1<br />

95 *2<br />

P23_4<br />

INT10<br />

I/O A<br />

General-purpose input/output port<br />

External interrupt input pin<br />

96 *2 P23_5 I/O A General-purpose input/output port<br />

97<br />

98<br />

99<br />

100<br />

101<br />

102<br />

103<br />

106<br />

107<br />

108<br />

P22_0<br />

General-purpose input/output port<br />

I/O A<br />

INT12 External interrupt input pin<br />

P22_2<br />

General-purpose input/output port<br />

I/O A<br />

INT13 External interrupt input pin<br />

P22_4<br />

General-purpose input/output port<br />

SDA0 I/O C I2C bus data input/output pin<br />

INT14 External interrupt input pin<br />

P22_5<br />

General-purpose input/output port<br />

I/O C<br />

SCL0 I2C bus clock input/output pin<br />

P20_0<br />

General-purpose input/output port<br />

SIN2 I/O A Data input pin of USART2<br />

AIN0 Up/down counter input pin<br />

P20_1<br />

General-purpose input/output port<br />

SOT2 I/O A Data output pin of USART2<br />

BIN0 Up/down counter input pin<br />

P20_2<br />

General-purpose input/output port<br />

SCK2<br />

ZIN0<br />

I/O A<br />

Clock input/output pin of USART2<br />

Up/down counter input pin<br />

CK2 External clock input pin of free-run timer 2<br />

P19_0<br />

General-purpose input/output port<br />

I/O A<br />

SIN4 Data input pin of USART4<br />

P19_1<br />

General-purpose input/output port<br />

I/O A<br />

SOT4 Data output pin of USART4<br />

P19_2<br />

General-purpose input/output port<br />

SCK4 I/O A Clock input/output pin of USART4<br />

CK4 External clock input pin of free-run timer 4<br />

(Continued)<br />

10 DS705-00002-1v3-E

(Continued)<br />

Pin no. Pin name I/O<br />

109<br />

110<br />

111<br />

112<br />

113<br />

114<br />

115<br />

116<br />

117<br />

118 to 121<br />

122 to 129<br />

I/O circuit<br />

type *1<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

Function<br />

P19_4<br />

General-purpose input/output port<br />

I/O A<br />

SIN5 Data input pin of USART5<br />

P19_5<br />

General-purpose input/output port<br />

I/O A<br />

SOT5 Data output pin of USART5<br />

P19_6<br />

General-purpose input/output port<br />

SCK5 I/O A Clock input/output pin of USART5<br />

CK5 External clock input pin of free-run timer 5<br />

P18_0<br />

General-purpose input/output port<br />

SIN6 I/O A Data input pin of USART6<br />

AIN2 Up/down counter input pin<br />

P18_1<br />

General-purpose input/output port<br />

SOT6 I/O A Data output pin of USART6<br />

BIN2 Up/down counter input pin<br />

P18_2<br />

General-purpose input/output port<br />

SCK6<br />

ZIN2<br />

I/O A<br />

Clock input/output pin of USART6<br />

Up/down counter input pin<br />

CK6 External clock input pin of free-run timer 6<br />

P18_4<br />

General-purpose input/output port<br />

SIN7 I/O A Data input pin of USART7<br />

AIN3 Up/down counter input pin<br />

P18_5<br />

General-purpose input/output port<br />

SOT7 I/O A Data output pin of USART7<br />

BIN3 Up/down counter input pin<br />

P18_6<br />

General-purpose input/output port<br />

SCK7<br />

ZIN3<br />

I/O A<br />

Clock input/output pin of USART7<br />

Up/down counter input pin<br />

CK7 External clock input pin of free-run timer 7<br />

P15_0 to P15_3<br />

General-purpose input/output ports<br />

OCU0 to OCU3 I/O A Output compare output pins<br />

TOT0 to TOT3 Reload timer output pins<br />

P14_0 to P14_7<br />

General-purpose input/output ports<br />

ICU0 to ICU7 Input capture input pins<br />

TIN0 to TIN7<br />

TTG8 to TTG11,<br />

I/O A External trigger input pins of reload timer<br />

TTG4/12 to<br />

TTG7/15<br />

External trigger input pins of PPG timer<br />

(Continued)<br />

DS705-00002-1v3-E 11

<strong>MB91460E</strong> <strong>Series</strong><br />

(Continued)<br />

Pin no. Pin name I/O<br />

132 to 135<br />

136 to 139<br />

140<br />

141<br />

142<br />

I/O circuit<br />

type *1<br />

Function<br />

P17_4 to P17_7<br />

General-purpose input/output ports<br />

I/O A<br />

PPG4 to PPG7 Output pins of PPG timer<br />

P16_0 to P16_3<br />

General-purpose input/output ports<br />

I/O A<br />

PPG8 to PPG11 PPG timer output pins<br />

P16_4<br />

General-purpose input/output port<br />

PPG12 I/O A Output pin of PPG timer<br />

SGA SGA output pin of sound generator<br />

P16_5<br />

General-purpose input/output port<br />

PPG13 I/O A Output pin of PPG timer<br />

SGO SGO output pin of sound generator<br />

P16_6<br />

General-purpose input/output port<br />

PPG14 I/O A Output pin of PPG timer<br />

PFM Pulse frequency modulator output pin<br />

P16_7<br />

General-purpose input/output port<br />

143 PPG15 I/O A PPG timer output pin<br />

ATGX A/D converter external trigger input pin<br />

147 ALARM_0 I N Alarm comparator input pin<br />

148 to 155<br />

158<br />

159<br />

160<br />

161<br />

164<br />

P29_0 to P29_7<br />

General-purpose input/output ports<br />

I/O B<br />

AN0 to AN7 Analog input pins of A/D converter<br />

P27_0<br />

General-purpose input/output port<br />

SMC1P0 I/O F Controller output pin of Stepper motor<br />

AN16 Analog input pin of A/D converter<br />

P27_1<br />

General-purpose input/output port<br />

SMC1M0 I/O F Controller output pin of Stepper motor<br />

AN17 Analog input pin of A/D converter<br />

P27_2<br />

General-purpose input/output port<br />

SMC2P0 I/O F Controller output pin of Stepper motor<br />

AN18 Analog input pin of A/D converter<br />

P27_3<br />

General-purpose input/output port<br />

SMC2M0 I/O F Controller output pin of Stepper motor<br />

AN19 Analog input pin of A/D converter<br />

P27_4<br />

General-purpose input/output port<br />

SMC1P1 I/O F Controller output pin of Stepper motor<br />

AN20 Analog input pin of A/D converter<br />

(Continued)<br />

12 DS705-00002-1v3-E

(Continued)<br />

Pin no. Pin name I/O<br />

165<br />

166<br />

167<br />

168<br />

169<br />

170<br />

171<br />

174<br />

175<br />

176<br />

177<br />

I/O circuit<br />

type *1<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

Function<br />

P27_5<br />

General-purpose input/output port<br />

SMC1M1 I/O F Controller output pin of Stepper motor<br />

AN21 Analog input pin of A/D converter<br />

P27_6<br />

General-purpose input/output port<br />

SMC2P1 I/O F Controller output pin of Stepper motor<br />

AN22 Analog input pin of A/D converter<br />

P27_7<br />

General-purpose input/output port<br />

SMC2M1 I/O F Controller output pin of Stepper motor<br />

AN23 Analog input pin of A/D converter<br />

P26_0<br />

General-purpose input/output port<br />

SMC1P2 I/O F Controller output pin of Stepper motor<br />

AN24 Analog input pin of A/D converter<br />

P26_1<br />

General-purpose input/output port<br />

SMC1M2 I/O F Controller output pin of Stepper motor<br />

AN25 Analog input pin of A/D converter<br />

P26_2<br />

General-purpose input/output port<br />

SMC2P2 I/O F Controller output pin of Stepper motor<br />

AN26 Analog input pin of A/D converter<br />

P26_3<br />

General-purpose input/output port<br />

SMC2M2 I/O F Controller output pin of Stepper motor<br />

AN27 Analog input pin of A/D converter<br />

P26_4<br />

General-purpose input/output port<br />

SMC1P3 I/O F Controller output pin of Stepper motor<br />

AN28 Analog input pin of A/D converter<br />

P26_5<br />

General-purpose input/output port<br />

SMC1M3 I/O F Controller output pin of Stepper motor<br />

AN29 Analog input pin of A/D converter<br />

P26_6<br />

General-purpose input/output port<br />

SMC2P3 I/O F Controller output pin of Stepper motor<br />

AN30 Analog input pin of A/D converter<br />

P26_7<br />

General-purpose input/output port<br />

SMC2M3 I/O F Controller output pin of Stepper motor<br />

AN31 Analog input pin of A/D converter<br />

(Continued)<br />

DS705-00002-1v3-E 13

<strong>MB91460E</strong> <strong>Series</strong><br />

(Continued)<br />

Pin no. Pin name I/O<br />

178<br />

179<br />

180<br />

181<br />

184<br />

185<br />

186<br />

187<br />

189<br />

190<br />

191<br />

192 to 199<br />

200 to 207<br />

I/O circuit<br />

type *1<br />

Function<br />

P25_0<br />

General-purpose input/output port<br />

I/O E<br />

SMC1P4 Controller output pin of Stepper motor<br />

P25_1<br />

General-purpose input/output port<br />

I/O E<br />

SMC1M4 Controller output pin of Stepper motor<br />

P25_2<br />

General-purpose input/output port<br />

I/O E<br />

SMC2P4 Controller output pin of Stepper motor<br />

P25_3<br />

General-purpose input/output port<br />

I/O E<br />

SMC2M4 Controller output pin of Stepper motor<br />

P25_4<br />

General-purpose input/output port<br />

I/O E<br />

SMC1P5 Controller output pin of Stepper motor<br />

P25_5<br />

General-purpose input/output port<br />

I/O E<br />

SMC1M5 Controller output pin of Stepper motor<br />

P25_6<br />

General-purpose input/output port<br />

I/O E<br />

SMC2P5 Controller output pin of Stepper motor<br />

P25_7<br />

General-purpose input/output port<br />

I/O E<br />

SMC2M5 Controller output pin of Stepper motor<br />

P13_0<br />

General-purpose input/output port<br />

I/O A<br />

DREQ0 DMA external transfer request input<br />

P13_1<br />

General-purpose input/output port<br />

I/O A<br />

DACKX0 DMA external transfer acknowledge output pin<br />

P13_2<br />

General-purpose input/output port<br />

DEOTX0 I/O A DMA external transfer EOT (End of Track) output pin<br />

DEOP0 DMA external transfer EOP (End of Process) output pin<br />

P03_0 to P03_7<br />

General-purpose input/output ports<br />

I/O A<br />

D0 to D7 Signal pins of external data bus (bit0 to bit7)<br />

P02_0 to P02_7<br />

General-purpose input/output ports<br />

I/O A<br />

D8 to D15 Signal pins of external data bus (bit8 to bit15)<br />

*1 : For information about the I/O circuit type, refer to “■ I/O CIRCUIT TYPES”.<br />

*2 : Difference versus MB91460D series: At pins 95+96, RX2 and TX2 of CAN2 are removed.<br />

14 DS705-00002-1v3-E

2. Power supply/Ground pins<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

Pin no. Pin name I/O Function<br />

1, 27, 53, 69, 79, 105,<br />

131, 157, 188<br />

VSS5<br />

Ground pins<br />

163, 173, 183 HVSS5 Ground pins for Stepper motor controller<br />

26, 52, 208 VDD35 Power supply pins for external data bus<br />

78, 104, 130, 156 VDD5 Power supply pins<br />

162, 172, 182 HVDD5 Supply Power supply pins for Stepper motor controller<br />

81, 82 VDD5R Power supply pins for internal regulator<br />

144 AVSS5 Analog ground pin for A/D converter<br />

146 AVCC5 Power supply pin for A/D converter<br />

145 AVRH5 Reference power supply pin for A/D converter<br />

80 VCC18C Capacitor connection pin for internal regulator<br />

DS705-00002-1v3-E 15

<strong>MB91460E</strong> <strong>Series</strong><br />

■ I/O CIRCUIT TYPES<br />

Type Circuit Remarks<br />

A<br />

pull-up control<br />

CMOS level output<br />

(programmable IOL = 5mA, IOH = -5mA<br />

driver strength<br />

and IOL = 2mA, IOH = -2mA)<br />

control<br />

2 different CMOS hysteresis inputs with input<br />

data line<br />

shutdown function<br />

Automotive input with input shutdown function<br />

TTL input with input shutdown function<br />

Programmable pull-up resistor: 50kΩ approx.<br />

R<br />

pull- down control<br />

CMOS hysteresis type1<br />

CMOS hysteresis type2<br />

Automotive inputs<br />

TTL input<br />

standby control for<br />

input shutdown<br />

B<br />

pull-up control<br />

CMOS level output<br />

(programmable IOL = 5mA, IOH = -5mA<br />

driver strength<br />

control<br />

and IOL = 2mA, IOH = -2mA)<br />

2 different CMOS hysteresis inputs with input<br />

data line<br />

pull- down control<br />

shutdown function<br />

Automotive input with input shutdown function<br />

TTL input with input shutdown function<br />

Programmable pull-up resistor: 50kΩ approx.<br />

Analog input<br />

R<br />

CMOS hysteresis type1<br />

CMOS hysteresis type2<br />

Automotive inputs<br />

TTL input<br />

standby control for<br />

input shutdown<br />

analog input<br />

16 DS705-00002-1v3-E

Type Circuit Remarks<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

C<br />

pull-up control<br />

CMOS level output (IOL = 3mA, IOH = -3mA)<br />

2 different CMOS hysteresis inputs with input<br />

shutdown function<br />

Automotive input with input shutdown function<br />

data line<br />

TTL input with input shutdown function<br />

Programmable pull-up resistor: 50kΩ approx.<br />

R<br />

pull- down control<br />

CMOS hysteresis type1<br />

CMOS hysteresis type2<br />

Automotive inputs<br />

TTL input<br />

standby control for<br />

input shutdown<br />

D<br />

pull-up control<br />

CMOS level output (IOL = 3mA, IOH = -3mA)<br />

2 different CMOS hysteresis inputs with input<br />

shutdown function<br />

Automotive input with input shutdown function<br />

data line<br />

TTL input with input shutdown function<br />

Programmable pull-up resistor: 50kΩ approx.<br />

Analog input<br />

R<br />

pull- down control<br />

CMOS hysteresis type1<br />

CMOS hysteresis type2<br />

Automotive inputs<br />

TTL input<br />

standby control for<br />

input shutdown<br />

analog input<br />

DS705-00002-1v3-E 17

<strong>MB91460E</strong> <strong>Series</strong><br />

Type Circuit Remarks<br />

E<br />

pull-up control<br />

CMOS level output<br />

(programmable IOL = 5mA, IOH = -5mA<br />

driver strength<br />

and IOL = 2mA, IOH = -2mA,<br />

control<br />

and IOL = 30mA, IOH = -30mA)<br />

data line<br />

2 different CMOS hysteresis inputs with input<br />

shutdown function<br />

Automotive input with input shutdown function<br />

TTL input with input shutdown function<br />

pull- down control<br />

Programmable pull-up resistor: 50kΩ approx.<br />

R<br />

CMOS hysteresis type1<br />

CMOS hysteresis type2<br />

Automotive inputs<br />

TTL input<br />

standby control for<br />

input shutdown<br />

F<br />

pull-up control<br />

CMOS level output<br />

(programmable IOL = 5mA, IOH = -5mA<br />

driver strength<br />

control<br />

and IOL = 2mA, IOH = -2mA,<br />

and IOL = 30mA, IOH = -30mA)<br />

data line<br />

2 different CMOS hysteresis inputs with input<br />

shutdown function<br />

Automotive input with input shutdown function<br />

TTL input with input shutdown function<br />

Programmable pull-up resistor: 50kΩ approx.<br />

pull- down control<br />

Analog input<br />

R<br />

CMOS hysteresis type1<br />

CMOS hysteresis type2<br />

Automotive inputs<br />

TTL input<br />

standby control for<br />

input shutdown<br />

analog input<br />

18 DS705-00002-1v3-E

Type Circuit Remarks<br />

G Mask ROM and EVA device:<br />

R<br />

Hysteresis<br />

inputs<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

CMOS Hysteresis input pin<br />

Flash device:<br />

CMOS input pin<br />

12 V withstand (for MD [2:0])<br />

H CMOS Hysteresis input pin<br />

Pull-up resistor value: 50 kΩ approx.<br />

Pull-up<br />

Resistor<br />

R<br />

Hysteresis<br />

inputs<br />

J1 High-speed oscillation circuit:<br />

• Programmable between oscillation mode<br />

X1<br />

(external crystal or resonator connected<br />

to X0/X1 pins) and<br />

R<br />

Fast external Clock Input (FCI) mode<br />

(external clock connected to X0 pin)<br />

0<br />

1<br />

Xout • Feedback resistor = approx. 2 * 0.5 MΩ.<br />

Feedback resistor is grounded in the center<br />

when the oscillator is disabled or in FCI mode.<br />

X0<br />

R<br />

FCI or osc disable<br />

FCI<br />

J2 Low-speed oscillation circuit:<br />

• Feedback resistor = approx. 2 * 5 MΩ.<br />

X1A<br />

Xout Feedback resistor is grounded in the center<br />

when the oscillator is disabled.<br />

R<br />

X0A<br />

R<br />

osc disable<br />

DS705-00002-1v3-E 19

<strong>MB91460E</strong> <strong>Series</strong><br />

Type Circuit Remarks<br />

K<br />

pull-up control<br />

CMOS level output<br />

(programmable IOL = 5mA, IOH = -5mA<br />

driver strength<br />

and IOL = 2mA, IOH = -2mA)<br />

control<br />

2 different CMOS hysteresis inputs with input<br />

data line<br />

shutdown function<br />

Automotive input with input shutdown function<br />

TTL input with input shutdown function<br />

Programmable pull-up resistor: 50kΩ approx.<br />

pull- down control<br />

LCD SEG/COM output<br />

R<br />

CMOS hysteresis type1<br />

CMOS hysteresis type2<br />

Automotive inputs<br />

TTL input<br />

standby control for<br />

input shutdown<br />

LCD SEG/COM<br />

L<br />

pull-up control<br />

CMOS level output<br />

(programmable IOL = 5mA, IOH = -5mA<br />

driver strength<br />

control<br />

and IOL = 2mA, IOH = -2mA)<br />

2 different CMOS hysteresis inputs with input<br />

data line<br />

shutdown function<br />

Automotive input with input shutdown function<br />

TTL input with input shutdown function<br />

Programmable pull-up resistor: 50kΩ approx.<br />

Analog input<br />

pull- down control<br />

LCD Voltage input<br />

R<br />

CMOS hysteresis type1<br />

CMOS hysteresis type2<br />

Automotive inputs<br />

TTL input<br />

standby control for<br />

input shutdown<br />

VLCD<br />

20 DS705-00002-1v3-E

Type Circuit Remarks<br />

M CMOS level tri-state output<br />

(IOL = 5mA, IOH = -5mA)<br />

N<br />

tri-state control<br />

data line<br />

analog input line<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

Analog input pin with protection<br />

DS705-00002-1v3-E 21

<strong>MB91460E</strong> <strong>Series</strong><br />

■ HANDLING DEVICES<br />

1. Preventing Latch-up<br />

Latch-up may occur in a CMOS IC if a voltage higher than (VDD5, VDD35 or HVDD5) or less than (VSS5 orHVSS5)<br />

is applied to an input or output pin or if a voltage exceeding the rating is applied between the power supply pins<br />

and ground pins. If latch-up occurs, the power supply current increases rapidly, sometimes resulting in thermal<br />

breakdown of the device. Therefore, be very careful not to apply voltages in excess of the absolute maximum<br />

ratings.<br />

2. Handling of unused input pins<br />

If unused input pins are left open, abnormal operation may result. Any unused input pins should be connected<br />

to pull-up or pull-down resistor (2KΩ to 10KΩ) or enable internal pullup or pulldown resisters (PPER/PPCR)<br />

before the input enable (PORTEN) is activated by software. The mode pins MD_x can be connected to VSS5 or<br />

VDD5 directly. Unused ALARM input pins can be connected to AVSS5 directly.<br />

3. Power supply pins<br />

In MB91460 series, devices including multiple power supply pins and ground pins are designed as follows; pins<br />

necessary to be at the same potential are interconnected internally to prevent malfunctions such as latch-up.<br />

All of the power supply pins and ground pins must be externally connected to the power supply and ground<br />

respectively in order to reduce unnecessary radiation, to prevent strobe signal malfunctions due to the ground<br />

level rising and to follow the total output current ratings. Furthermore, the power supply pins and ground pins of<br />

the MB91460 series must be connected to the current supply source via a low impedance.<br />

It is also recommended to connect a ceramic capacitor of approximately 0.1 µF as a bypass capacitor between<br />

power supply pin and ground pin near this device.<br />

This series has a built-in step-down regulator. Connect a bypass capacitor of 4.7 µF (use a X7R ceramic<br />

capacitator) to VCC18C pin for the regulator.<br />

4. Crystal oscillator circuit<br />

Noise in proximity to the X0 (X0A) and X1 (X1A) pins can cause the device to operate abnormally. Printed circuit<br />

boards should be designed so that the X0 (X0A) and X1 (X1A) pins, and crystal oscillator, as well as bypass<br />

capacitors connected to ground, are located near the device and ground.<br />

It is recommended that the printed circuit board layout be designed such that the X0 and X1 pins or X0A and<br />

X1A pins are surrounded by ground plane for the stable operation.<br />

Please request the oscillator manufacturer to evaluate the oscillational characteristics of the crystal and this<br />

device.<br />

5. Notes on using external clock<br />

When using the external clock, it is necessary to simultaneously supply the X0 (X0A) and the X1 (X1A) pins. In<br />

the described combination, X1 (X1A) should be supplied with a clock signal which has the opposite phase to<br />

the X0 (X0A) pins. At X0 and X1, a frequency up to 16 MHz is possible.<br />

(Continued)<br />

22 DS705-00002-1v3-E

(Continued)<br />

Example of using opposite phase supply<br />

X0 (X0A)<br />

X1 (X1A)<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

DS705-00002-1v3-E 23

<strong>MB91460E</strong> <strong>Series</strong><br />

6. Mode pins (MD_x)<br />

These pins should be connected directly to the power supply or ground pins. To prevent the device from entering<br />

test mode accidentally due to noise, minimize the lengths of the patterns between each mode pin and power<br />

supply pin or ground pin on the printed circuit board as possible and connect them with low impedance.<br />

7. Notes on operating in PLL clock mode<br />

If the oscillator is disconnected or the clock input stops when the PLL clock is selected, the microcontroller may<br />

continue to operate at the free-running frequency of the self-oscillating circuit of the PLL. However, this selfrunning<br />

operation cannot be guaranteed.<br />

8. Pull-up control<br />

The AC standard is not guaranteed in case a pull-up resistor is connected to the pin serving as an external bus pin.<br />

9. Notes on PS register<br />

As the PS register is processed in advance by some instructions, when the debugger is being used, the exception<br />

handling may result in execution breaking in an interrupt handling routine or the displayed values of the flags in<br />

the PS register being updated.<br />

As the microcontroller is designed to carry out reprocessing correctly upon returning from such an EIT event,<br />

the operation before and after the EIT always proceeds according to specification.<br />

• The following behavior may occur if any of the following occurs in the instruction<br />

immediately after a DIV0U/DIV0S instruction:<br />

(a) a user interrupt or NMI is accepted;<br />

(b) single-step execution is performed;<br />

(c) execution breaks due to a data event or from the emulator menu.<br />

1. D0 and D1 flags are updated in advance.<br />

2. An EIT handling routine (user interrupt/NMI or emulator) is executed.<br />

3. Upon returning from the EIT, the DIV0U/DIV0S instruction is executed<br />

and the D0 and D1 flags are updated to the same values as those in 1.<br />

• The following behavior occurs when an ORCCR, STILM, MOV Ri,PS instruction is executed<br />

to enable a user interrupt or NMI source while that interrupt is in the active state.<br />

1. The PS register is updated in advance.<br />

2. An EIT handling routine (user interrupt/NMI or emulator) is executed.<br />

3. Upon returning from the EIT, the above instructions are executed and the PS register<br />

is updated to the same value as in 1.<br />

24 DS705-00002-1v3-E

■ NOTES ON DEBUGGER<br />

1. Execution of the RETI Command<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

If single-step execution is used in an environment where an interrupt occurs frequently, the corresponding<br />

interrupt handling routine will be executed repeatedly to the exclusion of other processing. This will prevent the<br />

main routine and the handlers for low priority level interrupts from being executed (For example, if the time-base<br />

timer interrupt is enabled, stepping over the RETI instruction will always break on the first line of the time-base<br />

timer interrupt handler).<br />

Disable the corresponding interrupts when the corresponding interrupt handling routine no longer needs debugging.<br />

2. Break function<br />

If the range of addresses that cause a hardware break (including event breaks) is set to the address of the<br />

current system stack pointer or to an area that contains the stack pointer, execution will break after each<br />

instruction regardless of whether the user program actually contains data access instructions.<br />

To prevent this, do not set (word) access to the area containing the address of the system stack pointer as the<br />

target of the hardware break (including an event breaks).<br />

3. Operand break<br />

It may cause malfunctions if a stack pointer exists in the area which is set as the DSU operand break. Do not<br />

set the access to the areas containing the address of system stack pointer as a target of data event break.<br />

DS705-00002-1v3-E 25

<strong>MB91460E</strong> <strong>Series</strong><br />

■ BLOCK DIAGRAM<br />

1. MB91F467EA<br />

Flash-Cache<br />

8 KByte<br />

Flash memory<br />

1088 KByte (MB91F467EA)<br />

ID-RAM<br />

48 KByte<br />

(MB91F467EA)<br />

Extended D-bus<br />

32<br />

Standby-RAM<br />

16 KByte<br />

(MB91F467EA)<br />

Always ON Logic<br />

INT0 to INT3,<br />

INT6 to INT9<br />

INT0 to INT10,<br />

INT12 to INT14<br />

ICU0 to ICU7<br />

OCU0 to OCU3<br />

AIN0,AIN2,AIN3<br />

BIN0,BIN2,BIN3<br />

ZIN0,ZIN2,ZIN3<br />

ALARM_0<br />

DREQ0<br />

DACKX0<br />

DEOP0<br />

DEOTX0<br />

PFM<br />

<strong>FR60</strong> CPU<br />

core<br />

I-bus<br />

32<br />

D-bus<br />

32<br />

Bus converter<br />

DMAC<br />

5 channels<br />

Hardware Watchdog<br />

Real time clock<br />

Shutdown / Recovery<br />

Control<br />

External interrupt<br />

14 channels<br />

Interrupt controller<br />

Input capture<br />

8 channels<br />

Output compare<br />

4 channels<br />

Up/down counter<br />

3 channels<br />

PFM timer<br />

1 channel<br />

Alarm comparator<br />

1 channel<br />

D-RAM<br />

64 KByte<br />

CAN<br />

2 channels<br />

Bit search<br />

32 16<br />

bus adapter<br />

R-bus<br />

16<br />

External<br />

bus<br />

interface<br />

Clock modulator<br />

Clock supervisor<br />

Clock control<br />

BAAX<br />

WEX<br />

ASX<br />

RDX<br />

RX0 to RX1<br />

TX0 to TX1<br />

WRX0 to WRX3<br />

BRQ<br />

MCLKE<br />

MCLKI<br />

BGRNTX<br />

CSX0 to CSX3,CSX6,CSX7<br />

A0 to A25<br />

D0 to D31<br />

TTG8 to TTG11, TTG4/12 to TTG7/15<br />

PPG4 to PPG15<br />

TIN0 to TIN7<br />

TOT0 to TOT3<br />

CK2,CK4 to CK7<br />

SIN2,SIN4 to SIN7<br />

SOT2,SOT4 to SOT7<br />

SCK2,SCK4 to SCK7<br />

SDA0,SDA2,SDA3<br />

SCL0,SCL2,SCL3<br />

AN0 to AN7,<br />

AN16 to AN31<br />

ATGX<br />

SMC1P0 to SMC1P5<br />

SMC1M0 to SMC1M5<br />

SMC2P0 to SMC2P5<br />

SMC2M0 to SMC2M5<br />

26 DS705-00002-1v3-E<br />

MCLKO<br />

Clock monitor MONCLK<br />

PPG timer<br />

12 channels<br />

Reload timer<br />

8 channels<br />

Free-run timer<br />

8 channels<br />

LIN-USART<br />

5 channels<br />

I C<br />

3 channels<br />

2<br />

A/D converter<br />

24 channels<br />

Stepper motor controller<br />

6 channels<br />

Sound generator<br />

1 channel<br />

Always ON Logic<br />

SGA<br />

SGO

■ A/D CONVERTER / RANGE COMPARATOR<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

The new A/D Converter with Range Comparator is available on MB91FV460B and some new flash devices and<br />

is backward compatible to the A/D converter used on older devices. Beside the Range Comparator, 32 separated<br />

result data registers, a second interrupt flag and a new behaviour regarding reading the ADCS0.ACH[5:0] bits<br />

have been implemented.<br />

There is one software incompatibility: Read-modify-write operation to the register ADCS0 is not allowed. See<br />

the description of the ADCS0.ACH[5:0] bits on 35ff.<br />

This chapter provides an overview of the A/D converter, describes the register structure and functions, and<br />

describes the operation of the A/D converter.<br />

1. Overview of A/D Converter and A/D Range Comparator<br />

The A/D converter converts analog input voltages into digital values and provides the following features. Any<br />

ADC cannel can be assigned to one of 4 Range Comparators.<br />

1.1. Features of the A/D converter:<br />

• Conversion time: minimum 1us per channel.<br />

• RC type successive approximation conversion with sample & hold circuit<br />

• 10-bit or 8-bit resolution<br />

• Program section analog input from 32 channels<br />

• 1 common result data register and 32 dedicated channel result data registers<br />

• Single conversion mode: Convert the specified channel(s) only once.<br />

• Continuous mode: Repeatedly convert the specified channels.<br />

• Scan conversion mode: Continuous conversion of multiple channels, programmable for up to 32 channels<br />

• Stop mode: Convert one channel, then temporarily halt until the next activation.<br />

(Enables synchronization of the conversion start timing.)<br />

• A/D conversion can be followed by an A/D conversion interrupt request to CPU. This interrupt, an option that<br />

is ideal for continuous processing can be used to start a DMA transfer of the results of A/D conversion to<br />

memory.<br />

• A/D conversion of all enabled channels (scan conversion) can be followed by an A/D End of Scan interrupt<br />

request to CPU. The data is stored into dedicated channel result registers, which can be read out using DMA<br />

transfer.<br />

• Conversion startup may be by software, external trigger (falling edge) or timer (rising edge).<br />

1.2. Features of the A/D Range Comparator (RCO):<br />

• 4 conversion result Range Comparator channels, comparing the upper 8 bit of the conversion result with an<br />

upper and a lower threshold. The thresholds are programmable for the 4 comparators independendly.<br />

• Any ADC channel can be assigned to one of the 4 range comparators.<br />

• The comparision results will set “overflow” and “interrupt” flags per ADC channel, depending on the configuration.<br />

It is possible to configure the comparision for:<br />

- “out of range”: The flags are set if the A/D result is below the lower OR above the upper threshold.<br />

- “inside range”: The flags are set if the A/D result is above the lower AND below the upper threshold.<br />

• The configuration can be set individually per ADC channel.<br />

• Range comparision can be followed by an A/D Range Comparator interrupt request to CPU.<br />

DS705-00002-1v3-E 27

<strong>MB91460E</strong> <strong>Series</strong><br />

2. A/D Converter Input Impedance<br />

The following figure shows the sampling circuit of the A/D converter:<br />

Analog<br />

signal<br />

source<br />

Rext ANx<br />

Rin<br />

Analog SW<br />

28 DS705-00002-1v3-E<br />

Cin<br />

Do not set Rext over maximum sampling time (Tsamp).<br />

Rext = Tsamp / (7*Cin) - Rin<br />

ADC

3. Block Diagram of A/D Converter<br />

The following figure shows block diagram of A/D converter.<br />

AN0<br />

AN1<br />

AN2<br />

AN3<br />

AN4<br />

AN5<br />

AN6<br />

AN7<br />

AN8<br />

AN9<br />

AN10<br />

AN11<br />

AN12<br />

AN13<br />

AN14<br />

AN15<br />

AN16<br />

AN17<br />

AN18<br />

AN19<br />

AN20<br />

AN21<br />

AN22<br />

AN23<br />

AN24<br />

AN25<br />

AN26<br />

AN27<br />

AN28<br />

AN29<br />

AN30<br />

AN31<br />

MPX<br />

Input Circuit<br />

ATGX<br />

16- bit<br />

Reload Timer<br />

CLKP<br />

Sample & Hold<br />

circuit<br />

Decoder<br />

Comparator<br />

ADC<br />

Range<br />

Comparator<br />

4 digital<br />

comparators<br />

with upper<br />

and lower<br />

threshold<br />

32 * 2 flags<br />

(2 flags per<br />

ADC channel)<br />

AVCC AVRH AVRL AVSS<br />

D/A converter<br />

Sequential<br />

comparison register<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

A/D data register<br />

A/D control register 2<br />

A/D control register 0<br />

A/D control register 1<br />

Prescaler<br />

32<br />

A/D channel<br />

data registers<br />

ADCD00<br />

to<br />

ADCD31<br />

RCO Flags<br />

RCO INT<br />

ADC S 0/1<br />

Operating<br />

Clock<br />

DS705-00002-1v3-E 29<br />

INT2<br />

INT<br />

R - Bus

<strong>MB91460E</strong> <strong>Series</strong><br />

4. Registers of the A/D Converter<br />

The A/D converter with Range Comparator has the following registers:<br />

Address<br />

(ADC0)<br />

Address<br />

(ADC1 *1 )<br />

x=0 or 1 for ADC0, ADC1 * 1 respectively<br />

+0 +1 +2 +3<br />

Register<br />

0001A0H 0005E0H ADxERH ADxERL A/D channel Enable register<br />

0001A4H 0005E4H ADxCS1 ADxCS0 ADxCR1 ADxCR0<br />

A/D Control / Status register 0 + 1,<br />

A/D Conversion Result register<br />

0001A8H 0005E8H ADxCT1 ADxCT0 ADxSCH ADxECH<br />

Sampling timer setting register,<br />

Start Channel setting register,<br />

End Channel setting register<br />

0006B0H 0006DCH ADxCS2 - - - A/D Control / Status register 2<br />

000688H 0006B4H RCOxH0 RCOxL0 RCOxH1 RCOxL1<br />

00068CH 0006B8H RCOxH2 RCOxL2 RCOxH3 RCOxL3<br />

Range Comparator 0,1 High/Low threshold<br />

registers<br />

Range Comparator 2,3 High/Low threshold<br />

registers<br />

000690H 0006BCH RCOxIRS<br />

Range Comparator Inverted Range Select<br />

control<br />

000694H 0006C0H RCOxOF Range Comparator Overflow flags<br />

000698H 0006C4H RCOxINT Range Comparator Interrupt flags<br />

0006A0H 0006CCH ADxCC0 ADxCC1 ADxCC2 ADxCC3 Channel control for ch 0 to 7<br />

0006A4H 0006D0H ADxCC4 ADxCC5 ADxCC6 ADxCC7 Channel control for ch 8 to 16<br />

0006A8H 0006D4H ADxCC8 ADxCC9 ADxCC10 ADxCC11 Channel control for ch 16 to 23<br />

0006ACH 0006D8H ADxCC12 ADxCC13 ADxCC14 ADxCC15 Channel control for ch 24 to 31<br />

0006E0H 000720H ADCxD0 ADCxD1 ADC Channel Data register, channel 0,1<br />

0006E4H 000724H ADCxD2 ADCxD3 ADC Channel Data register, channel 2,3<br />

0006E8H 000728H ADCxD4 ADCxD5 ADC Channel Data register, channel 4,5<br />

0006ECH 00072CH ADCxD6 ADCxD7 ADC Channel Data register, channel 6,7<br />

0006F0H 000730H ADCxD8 ADCxD9 ADC Channel Data register, channel 8,9<br />

0006F4H 000734H ADCxD10 ADCxD11 ADC Channel Data register, channel 10,11<br />

0006F8H 000738H ADCxD12 ADCxD13 ADC Channel Data register, channel 12,13<br />

0006FCH 00073CH ADCxD14 ADCxD15 ADC Channel Data register, channel 14,15<br />

000700H 000740H ADCxD16 ADCxD17 ADC Channel Data register, channel 16,17<br />

000704H 000744H ADCxD18 ADCxD19 ADC Channel Data register, channel 18,19<br />

000708H 000748H ADCxD20 ADCxD21 ADC Channel Data register, channel 20,21<br />

00070CH 00074CH ADCxD22 ADCxD23 ADC Channel Data register, channel 22,23<br />

000710H 000750H ADCxD24 ADCxD25 ADC Channel Data register, channel 24,25<br />

000714H 000754H ADCxD26 ADCxD27 ADC Channel Data register, channel 26,27<br />

000718H 000758H ADCxD28 ADCxD29 ADC Channel Data register, channel 28,29<br />

00071CH 00075CH ADCxD30 ADCxD31 ADC Channel Data register, channel 30,31<br />

30 DS705-00002-1v3-E

1. On MB91F467E, ADC1 does not exist.<br />

4.1. A/D Input Enable Register (ADER)<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

This register enables the analog input functions of the A/D converter. On MB91FV460B, additionally the bit<br />

ADCHE in PORTEN register influences the enabling of analog input.<br />

• ADERH : Access: Word, Half-word, Byte<br />

31 30 29 28 27 26 25 24 Bit<br />

ADE31 ADE30 ADE29 ADE28 ADE27 ADE26 ADE25 ADE24<br />

0 0 0 0 0 0 0 0 Initial value<br />

R/W R/W R/W R/W R/W R/W R/W R/W Attribute<br />

23 22 21 20 19 18 17 16 Bit<br />

ADE23 ADE22 ADE21 ADE20 ADE19 ADE18 ADE17 ADE16<br />

0 0 0 0 0 0 0 0 Initial value<br />

R/W R/W R/W R/W R/W R/W R/W R/W Attribute<br />

• ADERL : Access: Word, Half-word, Byte<br />

15 14 13 12 11 10 9 8 Bit<br />

ADE15 ADE14 ADE13 ADE12 ADE11 ADE10 ADE9 ADE8<br />

0 0 0 0 0 0 0 0 Initial value<br />

R/W R/W R/W R/W R/W R/W R/W R/W Attribute<br />

7 6 5 4 3 2 1 0 Bit<br />

ADE7 ADE6 ADE5 ADE4 ADE3 ADE2 ADE1 ADE0<br />

0 0 0 0 0 0 0 0 Initial value<br />

R/W R/W R/W R/W R/W R/W R/W R/W Attribute<br />

[ADE31-0]: A/D Input Enable<br />

PORTEN.<br />

ADEn<br />

ADCHE<br />

0 [initial] X<br />

1<br />

0 [initial]<br />

1<br />

Function<br />

Analog input of A/D channel n is disabled.<br />

The ADC will not sample/convert this channel.<br />

Analog input of the channel n is enabled. Additionally, the port function register<br />

(PFR,EPFR) of the corresponding port must be set . The PFR/EPFR will switch<br />

the port to input direction (output driver = HiZ) and disable the digital input lines.<br />

Analog input of the channel n is enabled. Setting the port function register(s) is<br />

not necessary. ADEn will disable the digital input lines of the ports, but it does<br />

not change the port’s direction.<br />

• Software reset (RST) clears ADEn and PORTEN.ADCHE to 0.<br />

• Be sure to set start channel and end channel to cover all enabled channels.<br />

DS705-00002-1v3-E 31

<strong>MB91460E</strong> <strong>Series</strong><br />

4.1. A/D Control Status Registers (ADCS2, ADCS1, ADCS0)<br />

The A/D control status registers control and show the status of A/D converter. Do not overwrite ADCS0 register<br />

during A/D converting.<br />

• ADCS2 : Access: Byte<br />

15 14 13 12 11 10 9 8 Bit<br />

BUSY INT INTE PAUS - - INT2 INTE2<br />

0 0 0 0 0 0 0 0 Initial value<br />

R R R R R0 R0 R/W R/W Attribute<br />

[bits 15:12] BUSY, INT, INTE, PAUS<br />

These bits are a mirror of the corresponding bits in ADCS1, intended to quickly read out all status and interrupt<br />

information using only one register access. To write the bits, access them via ADCS1.<br />

[bits 11:10] -<br />

These bits do not exist. Read operation returns 0.<br />

[bit 9] INT2 (End of Scan Flag)<br />

The End of Scan flag is set when conversion data of the last channel is stored in ADCR, whereas the last channel<br />

is defined by ADECH register setting.<br />

• If bit 8 (INTE2) is "1" when this bit is set, and the ADC runs in continous conversion mode, an End of Scan<br />

interrupt request is generated or, if activation of DMA is enabled, DMA is activated.<br />

• Only clear this bit by writing "0" when A/D conversion is halted.<br />

• Initialized to "0" by a reset.<br />

• If DMA is used, this bit is cleared at the end of DMA transfer.<br />

• Read-modify-write operations read this bit as “1”.<br />

[bit 8] INTE2 (Enable End of Scan Interrupt)<br />

INTE2 enables the End of Scan interrupt in continous conversion mode. In the other conversion modi, this bit<br />

has no effect.<br />

Additionally, setting INTE2 changes the protect function of converted data (see description of ADCS1.PAUS).<br />

INTE2 Function<br />

0 [initial]<br />

1<br />

Disable End of Scan interrupt,<br />

ADC result protection protects the ADCR register data.<br />

Enable End of Scan interrupt,<br />

ADC result protection protects the ADCD0...ADCD31 register data<br />

(in continous conversion mode only)<br />

32 DS705-00002-1v3-E

• ADCS1 : Access: Half-word, Byte<br />

[bit 15] BUSY (busy flag and stop)<br />

<strong>MB91460E</strong> <strong>Series</strong><br />

15 14 13 12 11 10 9 8 Bit<br />

BUSY INT INTE PAUS STS1 STS0 STRT reserved<br />

0 0 0 0 0 0 0 0 Initial value<br />

R/W R/W R/W R/W R/W R/W R/W R/W Attribute<br />

BUSY Function<br />

Reading<br />

Writing<br />

A/D converter operation indication bit. Set on activation of A/D conversion<br />

and cleared on completion.<br />

Writing "0" to this bit during A/D conversion forcibly terminates conversion.<br />

Use to forcibly terminate in continuous and stop modes.<br />

• Read-modify-write instructions read the bit as "1".<br />

• Cleared on the completion of A/D conversion in single conversion mode.<br />

• In continuous and stop mode, the flag is not cleared until conversion is terminated by writing "0".<br />

• Initialized to "0" by a software reset (RST).<br />

• Do not specify forcible termination and software activation (BUSY="0" and STRT="1") at the same time.<br />

[bit 14] INT (End of Conversion Interrupt flag)<br />

This bit is set when conversion data is stored in ADCR.<br />

• If bit 5 (INTE) is "1" when this bit is set, an interrupt request is generated or, if activation of DMA is enabled,<br />

DMA is activated.<br />

• Only clear this bit by writing "0" when A/D conversion is halted.<br />

• Initialized to "0" by a software reset (RST).<br />

• If DMA is used, this bit is cleared at the end of DMA transfer.<br />

[bit 13] INTE (End of Conversion Interrupt enable)<br />

This bit is enables or disables the conversion completion interrupt.<br />

INTE Function<br />

0 Disable interrupt [Initial value]<br />

1 Enable interrupt<br />

• Cleared by a software reset (RST).<br />

DS705-00002-1v3-E 33

<strong>MB91460E</strong> <strong>Series</strong><br />

[bit 12] PAUS (A/D converter pause)<br />

This bit is set when A/D conversion temporarily halts.<br />

The A/D converter has one register to store the conversion result (ADCR) and additionally 32 ADC channel data<br />

registers. If a conversion is finished and the data of the previous conversion has not been read out before,<br />

previous data would be overwritten.<br />

To avoid this problem, the next conversion data is not stored in the data registers until the previous value has<br />

been read out (e.g. by DMA). A/D conversion halts during this time. A/D conversion resumes when the ADC<br />

interrupt flag ADCR1.INT is cleared.<br />

The register protection function depends on the conversion mode and the setting of ADCR2.INTE2:<br />

Mode INTE2 Function<br />

Single,<br />

Stop<br />

X Protect ADCR (the common result register)<br />

Continous<br />

0 Protect ADCR (the common result register)<br />

1 Protect ADCD0...ADCD31 (the dedicated channel data registers)<br />

• In continous mode with INTE2==1, PAUS is set when data of the start channel (set by ADSCH) is ready for<br />

writing to the registers, but IRQ2 (End of Scan interrupt) is active.<br />

• In the other modes or if INTE2==0, PAUS is set when data of any channel is ready for writing to the registers,<br />

but IRQ (End of Conversion) is active.<br />

• PAUS is cleared by writing "0" or by a reset. (Not cleared at the end of DMA transfer.) However when waiting<br />

condition of DMA transfer, this bit cannot be cleared.<br />

• Regarding protect function of converted data, see Section “6. Operation of A/D Converter".<br />

[bit 11, 10] STS1, STS0 (Start source select)<br />

These bits select the A/D activation source.<br />

STS1 STS0 Function<br />

0 0 Software activation [Initial value]<br />

0 1 External trigger pin activation and software activation<br />

1 0 Timer activation and software activation<br />

1 1 External trigger pin activation, timer activation and software activation<br />

• These bits are initialized "00" by software reset (RST).<br />

• In multiple-activation modes, the first activation to occur starts A/D conversion.<br />

• The activation source changes immediately on writing to the register. Therefore care is required when switching<br />

activation mode during A/D operation.<br />

• The A/D converter detects falling edges on the external trigger pin. When external trigger level is "L" and if<br />

these bits are changed to external trigger activation mode, A/D converting may starts.<br />

• Selecting the timer selects the 16-bit reload timer 7.<br />

34 DS705-00002-1v3-E

<strong>MB91460E</strong> <strong>Series</strong><br />

[bit 9] STRT (Start)<br />

Writing "1" to this bit starts A/D conversion (software activation).<br />

• Write "1" again to restart conversion.<br />

• Initialized to "0" by a software reset (RST).<br />

• In continuous and stop mode, restarting is not occurred. Check BUSY bit before writing "1". (Activate conversion<br />

after clearing.)<br />

• Do not specify forcible termination and software activation (BUSY="0" and STRT="1") at the same time.<br />

[bit 8] reserved bit<br />

Always write "0" to this bit.<br />

• ADCS0 : Access: Half-word, Byte. Read-modify-write access is not allowed<br />

7 6 5 4 3 2 1 0 Bit<br />

MD1 MD0 S10 ACH4 ACH3 ACH2 ACH1<br />

ACH0 /<br />

ACHMD<br />

0 0 0 0 0 0 0 0 Initial value<br />

R/W R/W R/W R R R R R,W * 1 Attribute<br />

1. ACHMD is a new, control bit, see “[bit 0] ACHMD (ACH register mode, write-only)” on page 36.<br />

[bit 7, 6] MD1, MD0 (A/D converter mode set)<br />

These bits the operation mode.<br />

MD1 MD0 Operating mode<br />

0 0 Single mode 1 (Reactivation during A/D conversion is allowed)<br />

0 1 Single mode 2 (Reactivation during A/D conversion is not allowed)<br />

1 0 Continuous mode (Reactivation during A/D conversion is not allowed)<br />

1 1 Stop mode (Reactivation during A/D conversion is not allowed)<br />

• Single mode: A/D conversion is continously performed from the selected start channel (ADSCH)<br />

to the selected end channel (ADECH). The conversion stops once it has been done<br />

for all these channels.<br />

• Continuous mode:A/D conversion is repeatedly performed from the selected start channel (ADSCH)<br />

to the selected end channel (ADECH) in a row.<br />

• Stop mode: A/D conversion is performed from the selected start channel (ADSCH) to<br />

the selected end channel (ADECH), followed by a pause after each channel.<br />

The conversion is resumed upon activation.<br />

When A/D conversion is started in continuous mode or stop mode, conversion operation continued until stopped<br />

by the BUSY bit.<br />

Conversion is stopped by writing "0" to the BUSY bit.<br />

On activation after forcibly stopping, conversion starts from the start channel, selected by ADSCH register.<br />

Reactivation during A/D conversion is disabled for any of the timer, external trigger and software start sources<br />

in single mode 2, continuous and stop mode.<br />

DS705-00002-1v3-E 35

<strong>MB91460E</strong> <strong>Series</strong><br />

[bit 5] S10<br />

This bit defines resolution of A/D conversion. If this bit set "0", the resolution is 10-bit. In the other case, resolution<br />

is 8-bit and the conversion result is stored to ADCR0 and in the lower 8 bits of the dedicated ADC result registers.<br />

• Initialized to "0" by a reset.<br />

[bit 4 to 0] ACH4-0 (Analog convert select channel, read-only)<br />

These bits show the number of the currently or previously converted analog channel, depending on bit ACHMD<br />

(see below).<br />

ACH4 ACH3 ACH2 ACH1 ACH0 Converted channel<br />

0 0 0 0 0 AN0<br />

0 0 0 0 1 AN1<br />

... ...<br />

1 1 1 1 0 AN30<br />

1 1 1 1 1 AN31<br />

• Writing these bits has no effect (bit 0 is writeable with special function ADCHMD).<br />

• Initialized to "0000" by software reset (RST).<br />

[bit 0] ACHMD (ACH register mode, write-only)<br />