# TI Designs High-Accuracy AC Voltage and Current Measurement AFE for Feeder Terminal Unit Reference Design

# Texas Instruments

## **TI Designs**

This TI Design solution addresses the analog front-end needs for merging units, protection relays, DTUs, FTUs, and bay control units that require measurement of multiple voltage and current inputs (16 or more) accurately over wide input range using a simple serial peripheral interface (SPI). Using the ADS8688/ADS8688A ADC, the need for external signal conditioning of the analog input can be minimized based on the application and the input signal level. This AFE design implementation is modular, allowing easy expansion of channels while at the same time keeping the connectivity to the processor minimal by using the SPI daisy chain feature of the ADS8688/ADS8688A ADC.

## **Design Resources**

| TIDA-00307 | Design Page    |

|------------|----------------|

| ADS8688    | Product Folder |

| ADS8698    | Product Folder |

| ADS8668    | Product Folder |

| CSD17571Q2 | Product Folder |

| TPS70933   | Product Folder |

| TPS70950   | Product Folder |

| ADS8688A   | Product Folder |

| ADS8678    | Product Folder |

|            |                |

ASK Our E2E Experts TI E2E" WEBENCH® Calculator Tools

All trademarks are the property of their respective owners.

## **Design Features**

- Design is based on ADS8688 (16-bit SAR ADC)

- ADC offers SPI to the host

- Design compatible with ADS8688A, ADS8678, ADS8668

- Two ADCs have been daisy chained to increase the number of inputs

- Based on ADC selection, ±10.24 V, ±5.12 V, ±2.56 V, ±1.28 V, and ±0.64 V programmable input ranges available for accurate measurement of low amplitude input signals

- Data output: 500K samples

- Additional ADC channel without PGA (AUX\_IN)

- Dual and single supply operation

- Input overvoltage protection: up to ±20 V

- On-Chip, 4.096-V reference with low drift

- AC sensor inputs with 50, 60, or 400 Hz can be used; Ranges compatible to electronic current transformer output requirements as per IEC60044-8

### **Featured Applications**

- Merging Units for Smart Grid applications

- Multi-function protection relays

- Power Quality Analyzer

- FTU, DTU, or RTU

#### System Description

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

#### 1 System Description

#### 1.1 Issues With the Existing Grid

An electrical grid is an enormous and extremely complex system consisting of centralized power plants, transmission lines, and distribution networks. An electrical grid is capable of carrying gigawatts (GW) of power while continuously balancing supply with fluctuating demand with remarkable reliability, providing little downtime.

Smart grid technologies have addressed the following electrical grid issues:

- Power outages and disruptions in the quality of power

- ٠ Inefficiency with managing peak loads

- No support for robust information flow

- Limited support for distributed generation ٠

#### 1.2 Smart Grid

Although access to electricity has enabled major advancements in technology, which has in turn driven an increase in the demand for electricity, little has changed in how electricity is generated, transmitted, and distributed to consumers. The term smart grid refers to new technology that brings the century-old method of electricity generation and distribution into the 21st century through computerized automation and control.

The smart grid technology builds upon the current grid system but uses digital technology that enables two-way communication between a power distribution utility company and customers. The ability for twoway communication creates an automated and widely-distributed electricity network that can protect, monitor, and optimize the operation of the interconnected components. This new automated network allows for utility companies to respond more efficiently to customer demand, and enables consumers to take more control over their energy usage through increased access to information.

The smart grid is composed of a number of interconnected components that monitor use and share realtime data. One of the most important parts of the smart grid is smart meters. Similar to the standard meters connected to homes and offices, smart meters collect and provide utility companies information about energy use and consumption, however smart meters provide these data more frequently. Smart meters can also communicate with appliances and programs inside homes and workplaces. Smart meters enable both utility companies and consumers to know how much energy is being used in real-time.

Similar to how smart meters communicate between utility companies and consumers, smart transmission and distribution devices can allow utility companies and transmission or distribution centers to communicate with each other. This communication can help utility companies identify inefficiencies in the transmission and distribution processes, ultimately leading to significant cost savings for the utility company and reduced electricity rates for the consumer.

Characteristics of smart grid technologies enable many functions beyond the capabilities of the existing electrical. A smart grid does the following:

- Provides the utility company with actionable information

- Provides the consumer with actionable information

- Provides customers with information about their electricity usage patterns and costs

- Automates and decentralizes decisions

- Supports and enhances new technologies

The smart grid concept penetrates throughout the entire grid to include:

- Smart meters

- Smart feeders

- Smart substations

High-Accuracy AC Voltage and Current Measurement AFE for Feeder Terminal Unit Reference Design

- Smart transmission

- Smart centralized generation

## 1.2.1 Key Technologies Used in Smart Grid Applications

- Sensing and Measurement Sensing and measurement allow utility companies and consumers to understand and react to the state of the electrical grid in real-time. For example, households can monitor their energy demand and the current price of electricity through smart meters, which communicate with home networks that link smart appliances and display devices.

- Integrated Communications High-speed, standardized, two-way communication allows for real-time information flows and decision-making among all grid components. Several existing technologies, including wide-area wireless internet and cellular networks, could provide the required communications infrastructure.

- Advanced Components Advanced components such as GPS systems, current-limiting conductors, advanced energy storage, and power electronics will improve generation, transmission, and distribution capacity and operational intelligence for utility companies.

- Advanced Control Methods The task of managing an electrical grid becomes more complex as more information becomes available to grid controllers and faster response times are required. Advanced control systems find and process important information quickly, streamlining operations and providing clarity to human operators.

## 1.2.2 Key Applications of Smart Grid Technologies

The smart grid technologies that form the foundation of a new grid enable new smart grid applications, including the following:

- Automatic meter reading (AMR)

- Advanced metering infrastructure (AMI)

- Real-time pricing (RTP)

- Demand response (DR)

- Smart Charging and vehicle-to-grid

- Distribution automation

- Distributed generation integration

System Description

## 1.3 Process Bus Overview

A process bus is a bus or LAN used at the process level, that is, in near proximity to the measured, controlled, or both types of components.

In general, a process bus is used because it does the following:

- · Satisfies the need for an interface with an optical voltage and current transformers

- Eliminates copper wiring in the field

- Minimizes configuration time

- Optimizes reconfiguration

The process bus enables the sending of digitized sampled measured values (SMV) from electronic instrument transformers to protect and control relays. The process bus also allows the connection of intelligent switchgear devices such as circuit breakers, disconnectors, or earthing switches. The features of the process bus include the following:

- Fiber-optical (fiber-optic) digital switchyard

- Merging Units (MUs) are digital interfaces to analog signals in the switchyard.

- CTs, VTs, circuit breakers, switchgear, sensors at power transformers, and others

- · Ideally located at direct proximity to primary equipment

- Protection relay can be reduced to a CPU with Ethernet card, without any IO modules

The topologies of the process bus include the following:

- Point-to-point, Merging Units with multiple direct connections to IEDs

- No high accuracy global time reference required, IEDs as synch masters, scalability issues

- Process bus as an Ethernet network is isolated from the station bus

- Increased security and simplified engineering, required dual homed IEDs

- Process bus shares a common Ethernet network with the station bus

- This solution is cost effective requires careful network engineering for logical separation.

- Process bus as redundant PRP Stars

- Zero-time recovery, duplication of network, higher cost of network infrastructure

- Process bus as multiple redundant HSR rings

- Cost-effective, large network-traffic traversing all nodes, maintenance issues

The performance requirements of the process bus performance include the following:

- Time-accuracy requirements in energy automation applications:

- 1-s SCADA

- 100-ms distribution automation

- 1-ms substation automation (sequence of events)

- 10-µs process bus

- 1-µs synchrophasors

- Merging Unit delay bound (primary sensor to Ethernet) according to IEC 61869-9:

- 1.5 ms for protection

- 10 ms for metering

- Timing:

- Currently PPS and IRIG-B are specified in 61850-9-2LE. According to 61850-9-2LE the Merging Unit will have the timestamp accuracy of category T4 which is specified in IEC 61850-5 as ±4 μs

NOTE: Data shifted at the receiving IEDs by just 30 µs results in a half-degree phase-angle error.

4

## 1.4 Merging Unit

Merging Units are analog interface units located in the substation yard. Merging Units interface with conventional or non-conventional instrument transformers and send the sampled current and voltage values over fiber, which eliminate the copper wires between the substation primary equipment and the protection as well as control and measuring devices.

As an example, Merging Units are used in substation automation systems for collecting and forwarding sensor data to further devices such as intelligent electronic devices (IEDs) provided for protection, control purposes, or both on a higher level of the respective substation automation system.

A Merging Unit is the interface from the physical analog world to the digital world using communication networks. The analog signal is converted to a digital signal and transmitted through sampled-values (SV) network communication protocol.

The IEC 61850-9-2LE Merging Unit is the optimal solution for process bus interfacing. The Merging Unit allows the consolidation of measurements made in the switchyard by feeding protection relays, meters, and fault recorders located in the control room. The use of fiber-optic communications makes the Merging Unit inherently safe. By eliminating the majority of copper wiring, the Merging Unit addresses key technical and logistic challenges affecting the cost of substation design, construction, and maintenance. The robust and simple architecture of the open IEC 61850-9-2LE process bus allows a mixture of relay, meter, and fault-recording equipment manufacturers. The Merging Unit collects data from conventional instrument transformers and converts the analog signals into a digital protocol defined by IEC 61850-9-2LE. The Merging Unit transmits the converted signal through fiber-optics using industrial-grade Ethernet hardware. Because of the low electrical burden to the instrument transformers, the Merging Unit can be inserted into an operational substation without impacting existing installations. This technology allows the customer to access process bus information at the substation and at higher level control and monitoring facilities.

The sampled values frame as specified in IEC 61850-9-2LE with a sampling rate of 80 samples per cycle has a total size of approximately 180 bytes. At 50 Hz with the sampling rate of 80 samples per cycle, a single Merging Unit sending frames consumes a bandwidth of approximately 6Mb/s. At 60 Hz with a sampling rate of 80 samples per cycle, the sending frame consumes a bandwidth of approximately 7.2 Mb/s. The IEC 61850-9-2LE data set *PhsMeas1* equals a total of eight elements: four currents and four voltages. One Merging Unit can have multiple sets of data.

The sampled value streams for protection and measurement is shown in Table 1:

| PROFILE                                                                          | POINTS<br>PER<br>CYCLE               | SAMPLES<br>PER<br>PACKAGE | TOTAL SAMPLING                    | PACKAGES PER SECOND          |

|----------------------------------------------------------------------------------|--------------------------------------|---------------------------|-----------------------------------|------------------------------|

| Protection                                                                       | 80 1 4000 to 4800 samples per second |                           |                                   | 4000 (50 Hz) to 4800 (60 Hz) |

| Measurement<br>(Power quality monitoring and<br>waveform recording applications) | 256                                  | 8                         | 12800 to 15360 samples per second | 1600 (50Hz) to 1920 (60 Hz)  |

## Table 1. Samples Values Data Stream

## 1.5 Protection Relay

Protective relays detect defective lines, apparatus, or other power system conditions of an abnormal or dangerous nature. Protective relays also initiate appropriate control over circuit action. Relays detect and locate faults by measuring electrical quantities in the power system which are different during normal and intolerable conditions. The most important role of protective relays is to protect individuals and then to protect equipment. Protective relays are also tasked to minimize the damage and expense caused by insulation breakdowns which (above overloads) are called *faults*. These faults can occur as a result of insulation deterioration or unforeseen events such as lightening strikes or power trips caused by contact with trees and foliage.

Relays are not required to operate during normal operation, but must immediately activate to handle intolerable system conditions. This immediate availability criterion is necessary to avoid serious outages and damages to either parts of or the entire power network. In theory, a relay system should be capable of responding to an infinite number of abnormalities that may occur within the network. However, in practice, some compromises must be made by comparing risks. Ensuring stability and security of the entire power system is difficult if only local measurements are employed in monitoring, protection, and control schemes. One way to overcome this difficulty is to develop system-wide protection and control mechanisms that complementary to the conventional local and zonal protection strategies. To implement such mechanisms, synchronized phasor measurements can serve as an effective data source to extract critical information about the condition of the system. Synchronized-phasor measurement capabilities are one of the features available in the most advanced protective relays that are commercially available. The use of this feature is proliferating.

Protection relays are intelligent electronic devices (IEDs) that receive measured signals from the secondary side of CTs and VTs. The relays detect whether or not the protected unit is in a stressed condition (based on the type and configuration of the unit). A trip signal is sent by protective relays to the circuit breakers to disconnect the faulty components from the power system if necessary. Protective relays are categorized based on the equipment type protected such as generators, transmission lines, transformers, and loads.

Typical subsystems of a protection relay include the following:

- Power Supply

- Wide input range (TI designs available to meet these requirements)

- 24 to 300-V DC

- 20 to 265-V AC

- High-efficiency SMPS

- CPU

- High-speed 32-Bit RISC CPU

- > 120 MIPS

- FLASH memory

- Easy firmware upgrades

- High-speed communication support

- 10/100-Mbps Ethernet LAN

- Redundant fiber

- DSP and CT or VT

- Modular CT or VT configurations up to 8 CT or VTs

- High-speed digital sampling

- 16-bit AD

- More than 64 samples per power cycle

- High-speed DSP

- Digital I/O

- Control outputs

- Solid-state

- Electromechanical, multiple types

- Fast activation speeds (less than 4 ms)

- Status inputs

- Dry and wet contacts

- 18 to 300-V DC

- Fast detection speeds (< 4 ms)

- DC analog I/O

- Transducer type inputs

- dcmA

- DC Voltage

- Resistive

- Communications

- High-speed serial

- Asynchronous (9600 to 115 KBaud)

- Fiber optic (single and multimode)

- Channel redundancy

The analog-input requirements include the following:

- Current and voltage inputs

- Secondary of CT, secondary of potential divider

- Low-voltage DC analog input (transducer input)

- 0 to 20 mA

- 4 to 20 mA

- 0 to 5 V

- 0 to 10 V

- RTD (Pt, Ni, Cu)

- · Number of current and voltage channels for protection relays

- 4 to 16 channels

- Low-voltage DC analog input (transducer input)

- 4 to 32 channels

## 1.6 TI Analog Front End Design With ADS8688

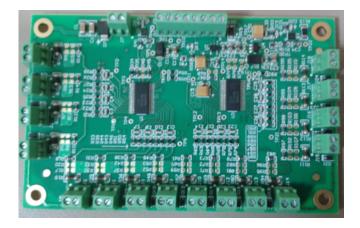

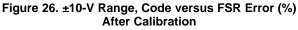

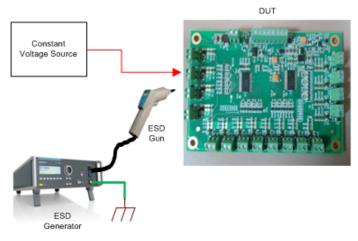

TI has a large portfolio of analog-to-digital converters (ADCs). The ADS8688 device is very well suited for measurement applications in grid infrastructure. This ADC module can measure AC inputs (voltage or current inputs). Sixteen channels are provided on the module and each channel can be configured as a current or voltage input. This TI design also includes an external protection circuit and has been tested and verified to be compliant with IEC61000-4 standards for ESD and Surge requirements.

This TI design demonstrates the following capabilities:

- Using the ADS8688 16-bit ADC to sample current and voltage inputs

- Increasing the number of analog input channels to 16 by daisy-chaining two ADCs

- Sampling of analog inputs at both protection and metering sampling rates as per IEC 61850-9-2LE

- Interfacing through a simple SPI avoids the need for an FPGA (field-programmable gate array)

The design also meets the accuracy and sampling speed requirements for Merging Units, protection relays, multifunction energy meters, and power meters.

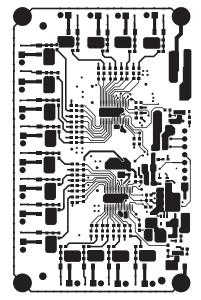

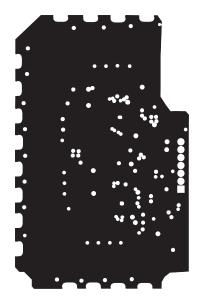

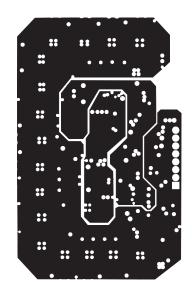

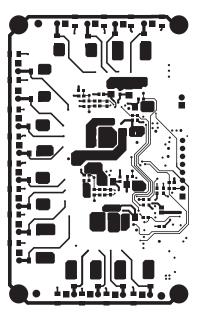

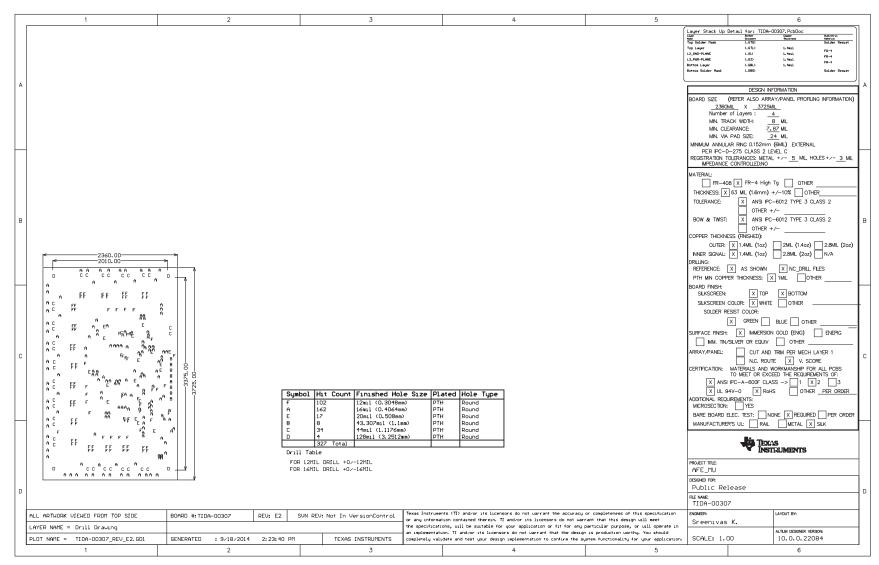

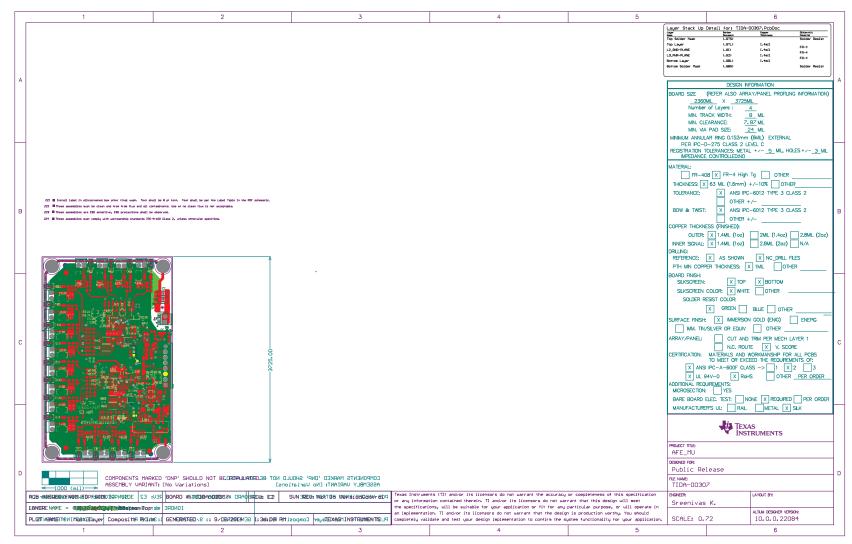

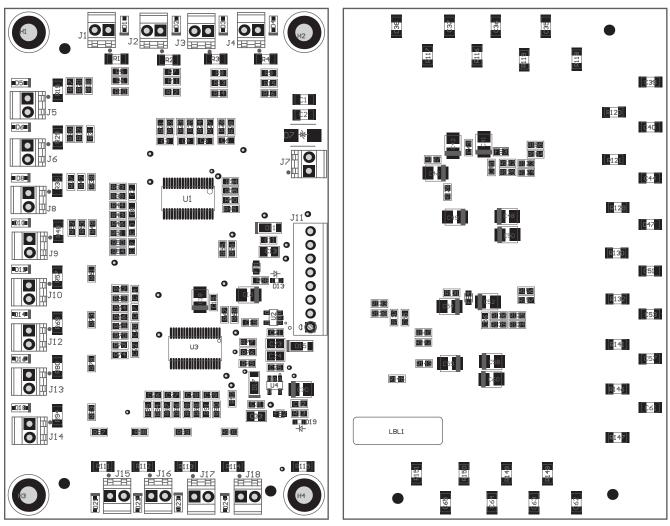

See the design tool folder (www.ti.com/tool/TIDA-00307) or Section 8 for the design files to evaluate this design including: schematics, bill of materials (BOM), PCB layout (Altium), and Gerber files.

**Design Features**

#### 2 **Design Features**

Table 2 lists the TIDA-00307 design features.

| Table 2. I | Design | Features | for | TIDA-00307 |

|------------|--------|----------|-----|------------|

|------------|--------|----------|-----|------------|

| REQUIREMENTS             | SPECIFICATION FEATURES                                                  |

|--------------------------|-------------------------------------------------------------------------|

| ADC                      | 16-bit, 8-channel, 500-kHz sampling rate ADS8688                        |

| Number of channels       | 8 channels per ADC (ninth channel without PGA)                          |

| Accuracy                 | $< \pm 0.25\%$ , without calibration at 25°C                            |

| Input voltage range      | ±10.24 V, ±5.12 V, ±2.56 V                                              |

| Input impedance          | > 1 MΩ                                                                  |

| Daisy chain              | Two ADS8688 devices in daisy-chain configuration                        |

| Power supply             | 5-V analog supply<br>3.3-V digital I/O supply                           |

| Interface                | Four-wire SPI-compatible interface                                      |

| Analog input connectors  | Eight 2-pin screw-type terminals for each ADC to connect analog inputs. |

| ESD immunity             | IEC 61000-4-2 : 4-kV contact discharges                                 |

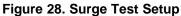

| Surge transient immunity | IEC 61000-4-5: ±1-kV (CM) on signal ports                               |

| Overvoltage protection   | ±20 V                                                                   |

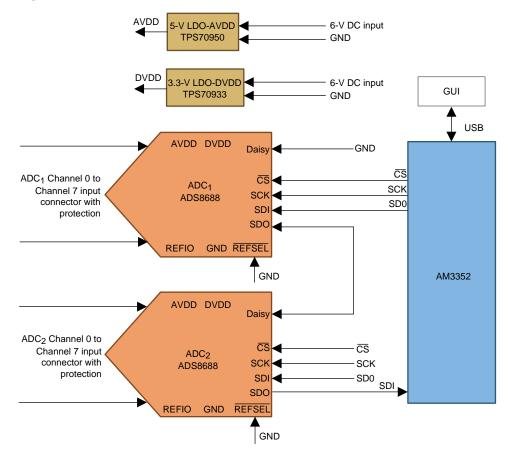

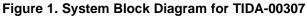

#### 3 **Block Diagram**

High-Accuracy AC Voltage and Current Measurement AFE for Feeder Terminal Unit Reference Design

### 3.1 ADC

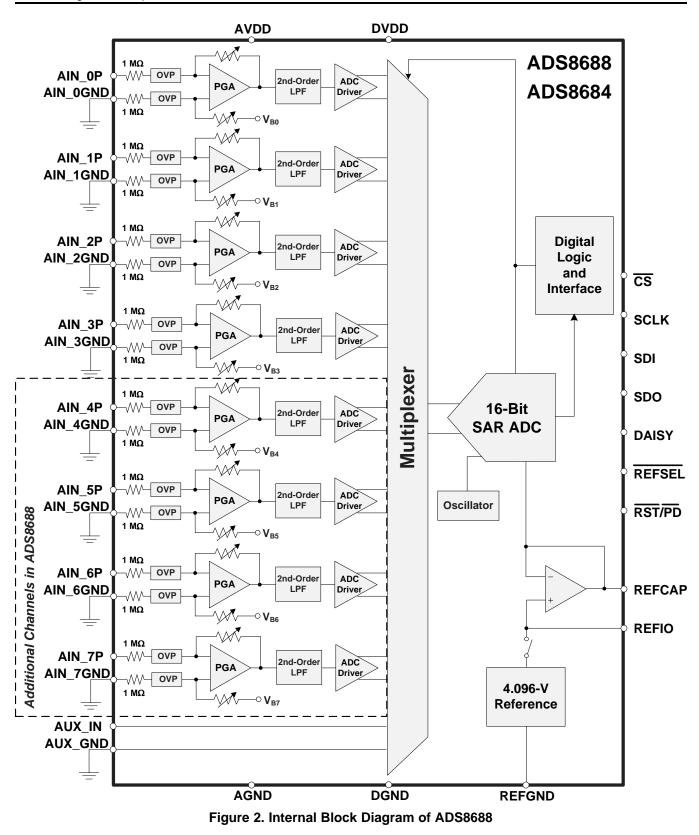

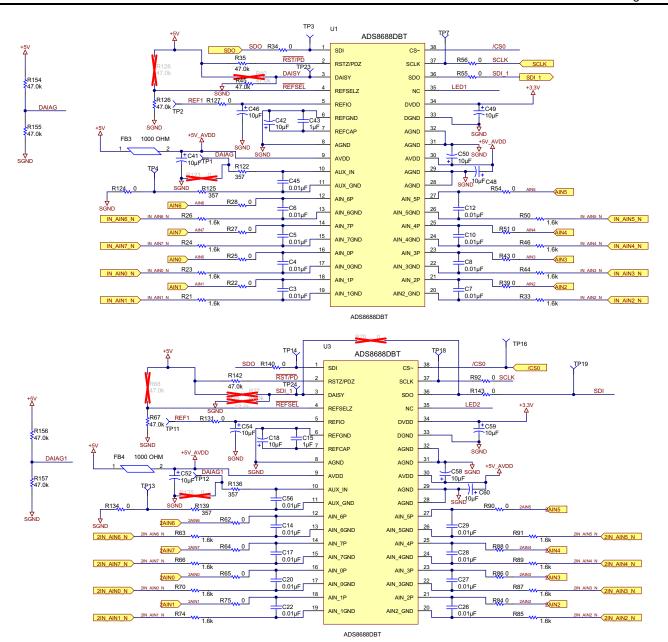

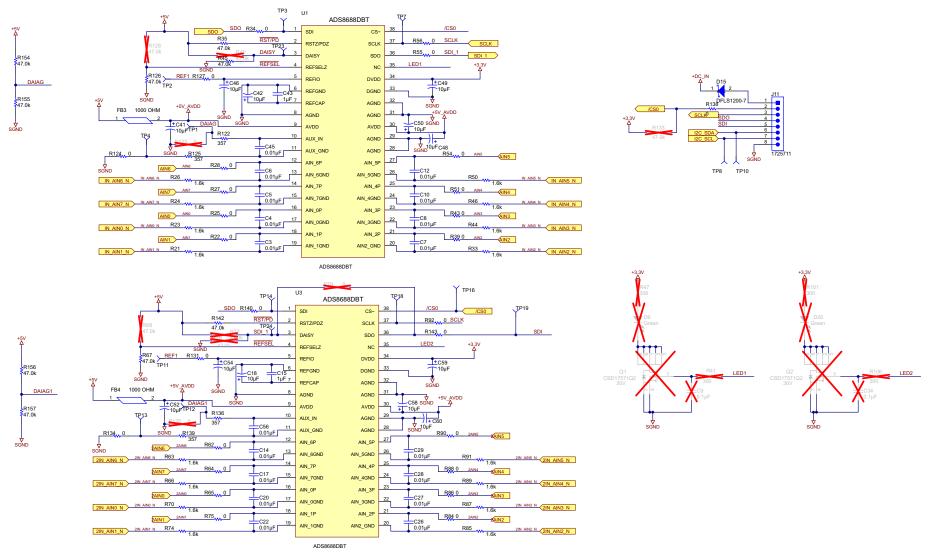

The ADCs used in this design are the ADS8688 device. The ADS8688 device is a 16-bit, 500-kSPS, 8channel, single-supply, SAR ADC with a bipolar Input. This ADC has an on-chip, 4.096-V reference with low drift. Two ADCs are used in this design which can be configured as either internal or external reference.

## 3.2 Daisy Chaining

The ADS8688 device features a simple SPI-compatible serial interface with an option to daisy chain multiple ADCs. The two ADCs are daisy chained in this design.

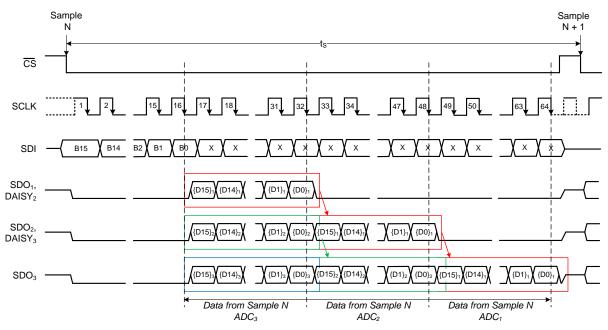

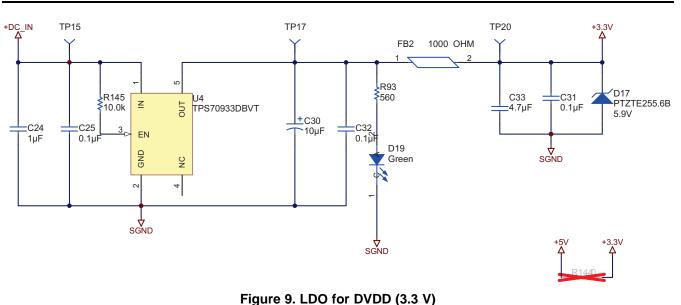

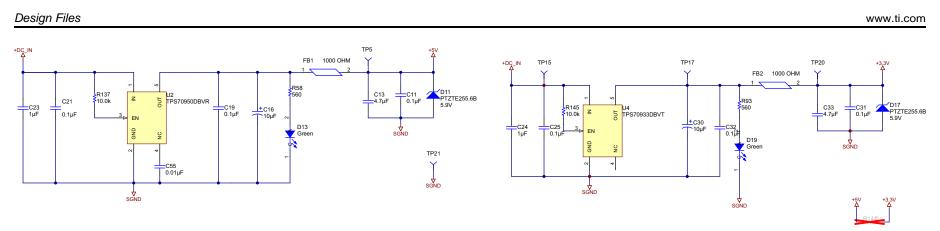

## 3.3 Power Supply

This design incorporates the TPS70933 device for a 3.3-V power supply and the TPS70950 device for a 5-V power supply. The TPS70933 device is a 150-mA, 30-V, ultra-low  $I_{Q}$ , wide-input low-dropout regulator with reverse current protection. The TPS70950 device is a 150-mA, 30-V, ultra-low  $I_{Q}$ , wide-input low-dropout regulator with reverse current protection.

## 3.4 Digital Interface

This ADC module is interfaced to the AM3352 ARM Cortex-A8 processor using an SPI-compatible interface.

## 3.5 Analog Input Connector and Protection

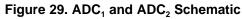

Two pin screw-type connectors (one per channel, total of 16) are provided for connecting the AC analog inputs. The inputs are protected against ESD and Surge. The input applied is single-ended. The following bipolar ranges can be applied:  $\pm 2.56$  V,  $\pm 5.12$  V, and  $\pm 10.24$  V.

### 3.6 ADC Diagnosis

The AUX\_IN ADC channel is configured to be used for diagnosis. The ADC can be sampled during power up or at frequent intervals for diagnosis of the ADC. This channel does not have a PGA at the input.

### 4 Circuit Design and Component Selection

### 4.1 ADC

The ADS8688 device is an 8-channel integrated data-acquisition systems-based device on a 16-bit successive approximation (SAR) ADC. The device operates at a throughput of 500 kSPS. The device features integrated analog front-end circuitry for each input channel with overvoltage protection up to  $\pm 20$  V, an 8-channel multiplexer with automatic and manual scanning modes, and an on-chip 4.096-V reference with extremely low drift. Operating on a single analog supply of 5 V, each input channel on the device can support true bipolar input ranges of  $\pm 2.56$  V,  $\pm 5.12$  V and  $\pm 10.24$  V. The input range selection occurs by programming the software of the internal device registers and is independent for each channel. The device offers a 1-M $\Omega$ , constant resistive-input impedance regardless of the selected input range.

The ADS8688 device offers a SPI-compatible serial interface to the digital host and also supports a daisy chain configuration for multiple devices. The digital supply can operate from 1.65 to 5.25 V, enabling direct interface to a wide range of host controllers

The device also offers integrated front-end signal processing including a multiplexer, second-order antialiasing filter, ADC driver amplifier, and an extended industrial-temperature range. These features make the ADS8688 device ideal for any standard-industrial analog-input measurements. Figure 2 shows the basic block diagram of the device.

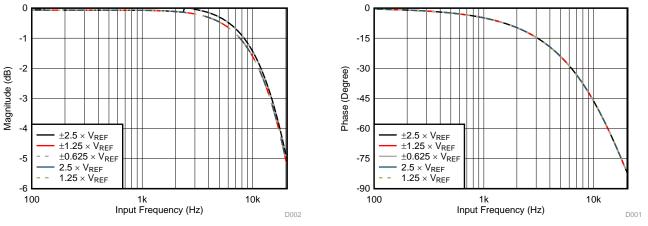

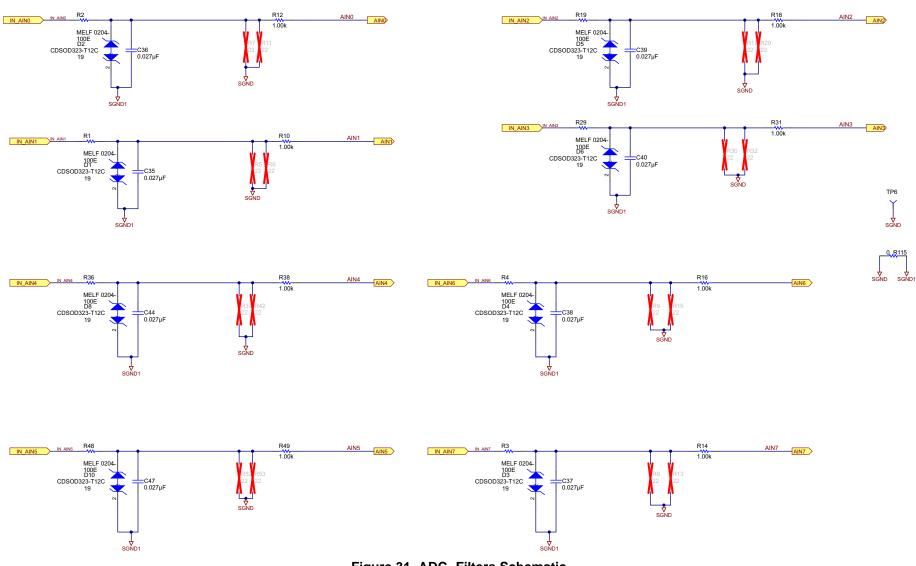

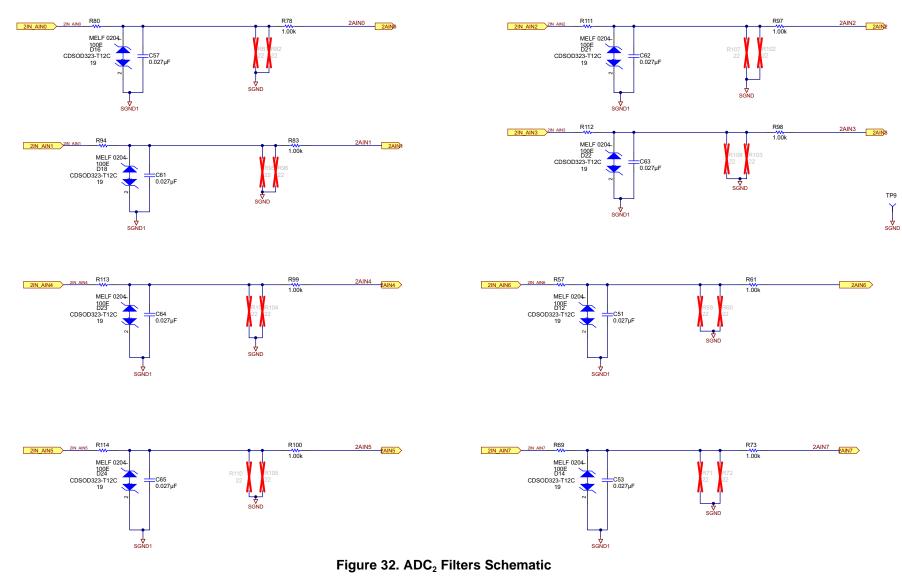

#### 4.1.1 Second-Order, Low-Pass Filter (LPF)

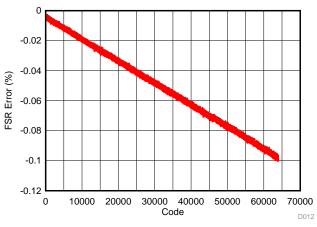

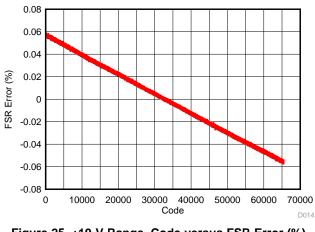

To mitigate the noise of the front-end amplifiers and gain resistors of the PGA, each analog input channel of the ADS8688 features a second-order, antialiasing LPF at the output of the PGA. Figure 3 and Figure 4 show the magnitude and phase response of the analog antialiasing filter, respectively. For maximum performance, the -3-dB cutoff frequency for the antialiasing filter is typically set to 15 kHz. The performance of the filter is consistent across all input ranges supported by the ADC.

Figure 3. Second-Order LPF Magnitude Response

Figure 4. Second-Order LPF Phase Response

### **ADC filter Performance**

#### **ADC Driver** 4.1.2

To meet the performance of a 16-bit SAR ADC at the maximum sampling rate (500 kSPS), the sample and hold capacitors at the input of the ADC must be successfully charged and discharged during the acquisition-time window. This drive requirement at the inputs of the ADC requires the use of a highbandwidth, low-noise, and stable amplifier buffer. Such an input driver is integrated in the front-end signal path of each analog input channel of the device. During transition from one channel of the multiplexer to another channel, the fast integrated driver ensures that the multiplexer output settles to 16-bit accuracy within the acquisition time of the ADC regardless of the input levels on the respective channels.

#### 4.1.3 **Multiplexer**

The ADS8688 device features an integrated 8-channel analog multiplexer (MUX). For each analog input channel, the voltage difference between the positive analog input, AIN\_nP, and the negative ground input, AIN\_nGND, is conditioned by the analog front-end circuitry before it is fed into the multiplexer. The output of the multiplexer is directly sampled by the ADC. The multiplexer in the device can scan these analog inputs in either manual or auto-scan mode, as explained in the Channel Sequencing Modes section of the ADS8688 datasheet. In manual mode (MAN Ch n), the channel is selected for every sample by a register write. In auto-scan mode (AUTO RST), the channel number automatically increments on every CS falling edge after the present channel is sampled. The analog inputs can be selected for an auto scan with register settings. The devices automatically scan only the selected analog inputs in ascending order. The maximum overall throughput for the ADS8688 device is specified at 500 kSPS across all channels. The throughput per channel is dependent on the number of channels selected in the multiplexer scanning sequence. For example, the throughput per channel is equal to 250 kSPS if only two channels are selected but it is equal to 125 kSPS per channel if four channels are selected.

### 4.1.4 Reference

The ADS8688 device can operate with either an internal voltage reference or an external voltage reference using the internal buffer. The internal or external reference selection is determined by an external REFSEL pin. The devices have a built-in buffer amplifier to drive the actual reference input of the internal ADC core for maximizing performance.

## 4.1.5 Internal Reference

The devices have an internal 4.096-V (nominal value) reference. To select the internal reference, the REFSEL pin must be tied low or connected to the AGND pin. When the internal reference is used, the REFIO pin (pin 5) becomes an output pin with the internal reference value. TI recommends placing a  $10-\mu$ F (minimum) decoupling capacitor between the REFIO pin and the REFGND (pin 6) pin, as shown in Figure 5. The capacitor must be placed as close to the REFIO pin as possible. The output impedance of the internal bandgap circuit creates a low-pass filter with this capacitor to band-limit the noise of the reference. The use of a smaller capacitor value allows higher reference noise in the system, thus degrading SNR (signal-to-noise ratio) and SINAD (signal-to-noise and distortion ratio) performance. Do not use the REFIO pin to drive external AC or DC loads because the REFIO pin has limited current output capability. The REFIO pin can be used as a source if followed by a suitable operational amplifier buffer (such as the OPA320 device).

In the current design both ADCs are used as an internal reference. Optionally, when the ADCs are configured in daisy-chain mode,  $ADC_1$  can be configured as an internal reference and  $ADC_2$  can be configured as an external reference. When  $ADC_1$  is configured as an internal reference, the reference output is available on the REFIO pin which can be the reference input for  $ADC_2$ . This configuration is required when the accuracy is expected to be same for both  $ADC_1$  and  $ADC_2$  which also reduces power consumption. The internal and external reference is pin configurable (REFSEL).

Figure 5. ADS8688 Connections for Using an Internal 4.096-V Reference

Figure 6. Two ADCs Connected in Daisy Chain Mode

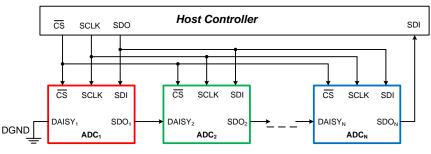

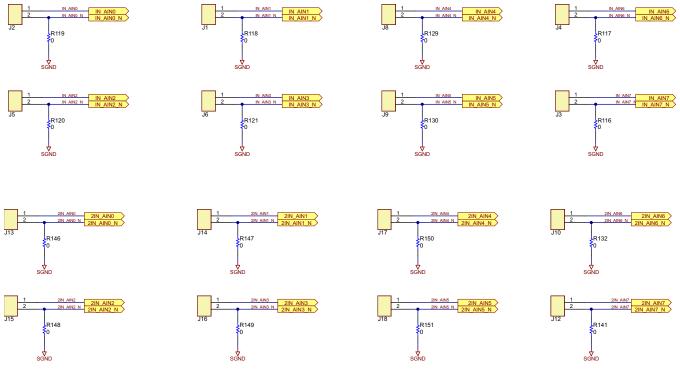

#### 4.2 **Daisy Chain Configuration**

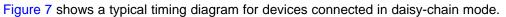

Figure 7 shows a typical connection diagram with multiple devices in daisy-chain mode. The  $\overline{CS}$ , SCLK, and SDI inputs of all devices are connected together and controlled by a single  $\overline{CS}$ , SCLK, and SDO pin of the host controller, respectively. The DAISY<sub>1</sub> input pin of the first ADC in the chain is connected to the DGND pin. The SDO1 output pin is connected to the DAISY<sub>2</sub> input of ADC<sub>2</sub>. The SDON pin of the Nth ADC  $(ADC_N)$  in the chain is connected to the SDI pin of the host controller. The devices do not require any special hardware or software configuration to enter daisy-chain mode.

Figure 7. Daisy-Chain Diagram

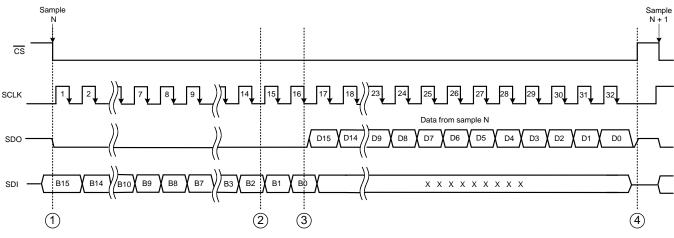

Figure 8. Timing Diagram for Devices Connected in Daisy-Chain Mode

At the falling edge of the CS signal, all devices sample the input signal at the respective selected channels and enter into conversion phase. For the first 16 SCLK cycles, the internal register settings for the next conversion can be entered using the SDI line, which is common to all devices in the chain. During this time period, the SDO outputs for all devices remain low. At the end of conversion, every ADC in the chain loads the respective conversion result into an internal 16-bit shift register. At the 16th SCLK falling edge, every ADC in the chain outputs the MSB (most-significant bit) on the respective SDO output pin. On every subsequent SCLK falling edge, the internal shift register of each ADC latches the data available on the DAISY<sub>N</sub> pin and shifts out the next bit of data on the SDO pin. Therefore, the digital host receives the data of ADC<sub>N</sub>, followed by the data of ADC<sub>N-1</sub>, and so forth (in MSB-first fashion). In total, a minimum of  $16 \times N$

SCLK falling edges are required to capture the outputs of all N devices in the chain. This example uses three devices in a daisy-chain connection. Therefore,  $3 \times 16 = 48$  SCLK cycles are required to capture the outputs of all devices in the chain along with the 16 SCLK cycles to input the register settings for the next conversion, resulting in a total of 64 SCLK cycles for the entire data frame. The overall throughput of the system is reduced proportionally with the number of devices connected in a daisy-chain configuration.

Referring to Figure 7, the following is true:

- The SDI pins for all devices are connected together so each device operates with the same internal configuration. This limitation can be overcome by spending additional host controller resources to control the SDI input of devices with unique configurations.

- If the number of devices connected in daisy-chain mode is more than four, loading increases on the shared output lines from the host controller (CS, SDO, and SCLK). This increased loading may lead to digital timing errors. This limitation can be overcome by using digital buffers on the shared outputs from the host controller before feeding the shared digital lines into additional devices.

- **NOTE:** If a daisy configuration is not required and only one device is used, make the following changes:

- 1. Remove R45 and Mount R40

- 2. Mount R79

- 3. Remove U3

- **NOTE:** The current TI design is a non-isolated interface to the host. If an isolated interface is required, this design can be interfaced to the TIDA-00300 design. Care must be taken with respect to the isolator delay influencing the data output rate performance. The TIDA-00300 design is configured for 5 V. The ADC module must also be configured for 5 V.

## 4.3 Power Supply

### 4.3.1 3.3-V I/O Power Supply

The TPS70933 regulator is an ultra-low quiescent-current devices designed for power-sensitive applications. A precision bandgap and error amplifier provides 2% accuracy over temperature. A quiescent current of only 1 µA makes this device an ideal solution for battery-powered always-on systems that require very little idle-state power dissipation. This device has thermal-shutdown, current-limit, and reverse-current protections for added safety. The regulator can enter shutdown mode by pulling the EN pin low. The shutdown current in this mode goes down to 150 nA (typical). The TPS70933 device series is available in SON-6, SOT-23-5, and SOT-223-4 packages.

The features of the TPS70933 device include the following:

- Ultra-low I<sub>o</sub>: 1 µA

- Reverse current protection

- Low I<sub>SHUTDOWN</sub>: 150 nA

- Input voltage range: 2.7 to 30 V

- Supports 200-mA peak output

- Low dropout: 245 mV at 50 mA

- 2% accuracy over temperature

- Available in fixed-output voltages: 1.2 to 6.5 V

- Thermal shutdown and overcurrent protection

#### Circuit Design and Component Selection

**NOTE:** The ADS8688 device can be configured to operate with single supply. Remove the components shown in Figure 9 and populate R144 to configure the ADC for 5-V operation.

### 4.3.2 5-V Analog Power Supply

The TPS70950 regulator is an ultra-low quiescent-current devices designed for power-sensitive applications. A precision bandgap and error amplifier provides 2% accuracy over temperature. A quiescent current of only 1  $\mu$ A makes this device an ideal solution for battery-powered always-on systems that require very little idle-state power dissipation. This device has thermal-shutdown, current-limit, and reverse-current protections for added safety. The regulator enters shutdown mode by pulling the EN pin low. The shutdown current in this mode goes down to 150 nA, typical. The TPS70950 device series is available in SON-6, SOT-23-5, and SOT-223-4 packages.

The features of the TPS70950 device include the following

- Ultra-low I<sub>Q</sub>: 1 μA

- Reverse current protection

- Low I<sub>SHUTDOWN</sub>: 150 nA

- Input voltage range: 2.7 to 30 V

- Supports 200-mA peak output

- Low dropout: 245 mV at 50 mA

- 2% accuracy over temperature

- Available in fixed-output voltages: 1.2 to 6.5 V

- Thermal shutdown and overcurrent protection

Figure 10. LDO for AVDD (5V)

## 4.3.3 Power Supply Recommendations

## Table 3. Typical Power-Supply Current Requirements

| SUPPLY TYPE | AC          | 0 <b>C</b> <sub>1</sub>  | ADC <sub>2</sub> |              |  |

|-------------|-------------|--------------------------|------------------|--------------|--|

| SUPPLITIFE  | VOLTAGE (V) | VOLTAGE (V) CURRENT (mA) |                  | CURRENT (mA) |  |

| Analog      | 5           | 16                       | 5                | 16           |  |

| I/O         | 3.3         | 1                        | 3.3              | 1            |  |

The device uses two separate power supplies: AVDD and DVDD. The internal circuits of the device operate on the AVDD supply, while the DVDD supply is used for the digital interface. The AVDD and DVDD supplies can be independently set to any value within the permissible range.

The AVDD supply pins must be decoupled with the AGND pin by using a minimum  $10-\mu$ F and  $1-\mu$ F capacitor on each supply. Place the  $1-\mu$ F capacitor as close to the supply pins as possible. Place a minimum  $10-\mu$ F decoupling capacitor very close to the DVDD supply to provide the high-frequency digital switching current. The effect of using the decoupling capacitor is shown by the difference in the power-supply rejection ratio (PSRR) performance of the device.

## 4.4 Digital Interface

## 4.4.1 Digital Pin Description

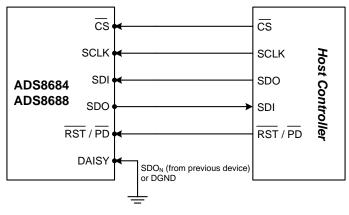

Figure 11 shows the digital data interface for the ADS8688 device.

The digital pin descriptions are as follows:

- CS (Input) The CS pin is an active-low, chip-select signal. The CS pin is also used as a control signal to trigger a conversion on the falling edge. Each data frame begins with the falling edge of the CS signal. The analog input channel to be converted during a particular frame is selected in the previous frame. On the CS falling edge, the devices sample the input signal from the selected channel and a conversion is initiated using the internal clock. The device settings for the next data frame can be input during this conversion process. When the CS signal is high, the ADC is considered to be in an idle state.

- SCLK (Input) This pin indicates the external clock input for the data interface. All synchronous accesses to the device are timed with respect to the falling edges of the SCLK signal.

- SDI (Input) The SDI pin is the serial data input line. The host processor uses the SDI pin to program the internal device registers for device configuration. At the beginning of each data frame, the CS signal goes low and the data on the SDI line are read by the device at every falling edge of the SCLK signal for the next 16 SCLK cycles. Any changes made to the device configuration in a particular data frame are applied to the device on the subsequent falling edge of the CS signal.

- **SDO (Output)** The SDO pin is the serial data output line. The device uses the SDO pin to output conversion data. The size of the data output frame varies depending on the register setting for the SDO format. A low level on the CS signal releases the SDO pin from the hi-Z state. The SDO pin is kept low for the first 15 SCLK falling edges. The MSB of the output data stream is clocked out on SDO on the 16th SCLK falling edge, followed by the subsequent data bits on every falling edge thereafter. The SDO line goes low after the entire data frame is output and goes to a hi-Z state when the CS signal goes high.

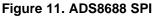

## 4.5 Analog Input Connector and Protection

The ADC module contains a terminal block that provides connections for sixteen analog inputs. The inputs can be configured to measure current or voltage inputs. The inputs are protected against ESD and Surge.

Figure 12. Analog Inputs

Table 4 lists the EMC test requirements.

### **Table 4. EMC Test Requirements**

| TEST AND STANDARD                           | TEST LEVEL               |

|---------------------------------------------|--------------------------|

| IEC 61000-4-2 Electrostatic Discharge (ESD) | ±4-kV contact discharges |

| IEC 61000-4-5 Surge                         | ±1-kV on signal ports    |

The transient voltage suppressor (TVS) diodes are used to clamp the surge voltage to safer limits with high-voltage capacitors Y-caps in parallel. In addition, two Y-caps have been placed at key locations to shunt transient energy quickly to earth ground. The Y-caps provides low impedance to fast transients and TVS diodes provides immunity against high voltage spikes.

## 4.6 ADC Diagnosis

The AUX\_IN ADC channel is configured to be used for diagnosis. The 2.5-V DC voltage is connected as input for measurement and diagnosis. This channel does not have the PGA circuit and so the measurement occurs without any gain or configurable range.

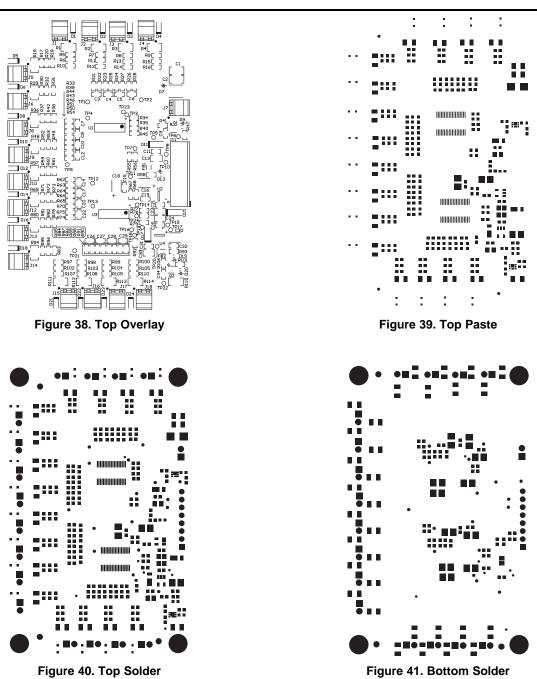

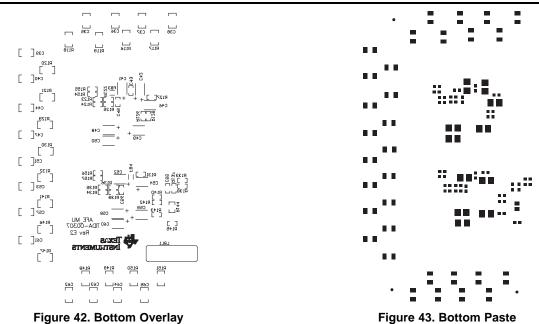

## 4.7 Layout Guidelines

When configuring the ADCs in daisy-chain mode ensure that the traces are matched for the SCLK pin and the chip select for both ADCs connected in daisy-chain configuration.

The following lists the general layout guidelines:

- Partition the PCB into analog and digital sections. Ensure that the analog signals are separated from the digital signals. This layout helps keep the analog input and reference input signals away from the digital noise. In this layout example, the analog input and reference signals are routed on the lower side of the board while the digital connections are routed on the top side of the board.

- Using a dedicated ground plane is encouraged.

- Power sources to the ADS8688 device must be well-bypassed. Placing vias between the AVDD pin, DVDD pin, and the bypass capacitors must be avoided. All ground pins must be connected to the ground plane using short, low-impedance paths.

- Two decoupling capacitors are used for the REFCAP pin. The first capacitor is a small, 1-μF, X7Rgrade, 0603-size ceramic capacitor placed close to the device pins for decoupling the high-frequency signals. The second capacitor is has a value of 10-μF which provides the charge required by the reference circuit of the device. Both of these capacitors must be directly connected to the device pins without any vias between the pins and capacitors.

- The REFIO pin also must be decoupled with a 10-μF capacitor if the internal reference of the device is used. The capacitor must be placed close to the device pins.

## 4.8 Enhancements Based on Application

There are multiple devices that are pin compatible and have the same input ranges. The required ADC can be chosen based on the application and the system cost. Table 5 provides details on different ADCs that can be considered.

| SPECIFICATIONS                         | ADS8698                                   | ADS8688                                   | ADS8688A                                                                                             | ADS8678                                                                     | ADS8668                                                                     |

|----------------------------------------|-------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Resolution (bits)                      | 18                                        | 16                                        | 16                                                                                                   | 14                                                                          | 12                                                                          |

| Sample rate (max)<br>(KSPS)            | 500                                       | 500                                       | 500                                                                                                  | 500                                                                         | 500                                                                         |

| Number of input channels               | 8                                         | 8                                         | 8                                                                                                    | 8                                                                           | 8                                                                           |

| Operating<br>temperature range<br>(°C) | -40 to 125                                | -40 to 125                                | -40 to 125                                                                                           | -40 to 125                                                                  | -40 to 125                                                                  |

| Interface                              | Serial SPI                                | Serial SPI                                | Serial SPI                                                                                           | Serial SPI                                                                  | Serial SPI                                                                  |

| Input range (V)                        | ±10.24<br>±5.12<br>±2.56<br>10.24<br>5.12 | ±10.24<br>±5.12<br>±2.56<br>10.24<br>5.12 | $\pm 10.24$<br>$\pm 5.12$<br>$\pm 2.56$<br>$\pm 1.28$<br>$\pm 0.64$<br>10.24<br>5.12<br>2.56<br>1.28 | ±10.24<br>±5.12<br>±2.56<br>±1.28<br>±0.64<br>10.24<br>5.12<br>2.56<br>1.28 | ±10.24<br>±5.12<br>±2.56<br>±1.28<br>±0.64<br>10.24<br>5.12<br>2.56<br>1.28 |

**Table 5. ADC Selection Based on Applications**

## 5 Software Description

## 5.1 Configuration for Daisy Chain

When the devices are configured in daisy-chain mode, all of the devices receive the same command input.

## 5.1.1 Device Features Selection Control Register (address = 03h)

The bits in this register can be used to configure the device ID for daisy-chain operation and configure the output bit format on SDO.

### Figure 13. Feature Select Register

| 7   | 6      | 5              | 4 | 3 | 2           | 1 | 0   |

|-----|--------|----------------|---|---|-------------|---|-----|

| DE  | V[1:0] | 1              | 0 | 1 | SDO[2:0]    |   |     |

| R/W | R/W    | R              | R | R | R/W R/W R/W |   | R/W |

|     |        | Desident and a |   |   |             |   |     |

LEGEND: R/W = Read/Write; R = Read only

## Table 6. Feature Select Register Field Descriptions

| BIT | FIELD    | TYPE | RESET | DESCRIPTION                                                                                                                                                                                     |

|-----|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | DEV[1:0] | R/W  | 0h    | Device ID bits.<br>00 = ID for device 0 in daisy-chain mode<br>01 = ID for device 1 in daisy-chain mode<br>10 = ID for device 2 in daisy-chain mode<br>11 = ID for device 3 in daisy-chain mode |

| 5   | 1        | R    | 1h    | Must always be set to 1                                                                                                                                                                         |

| 4   | 0        | R    | 0h    | Must always be set to 0                                                                                                                                                                         |

| 3   | 1        | R    | 1h    | Must always be set to 1                                                                                                                                                                         |

| 2:0 | SDO[2:0] | R/W  | 0h    | SDO data format bits (refer to Table 7).                                                                                                                                                        |

### Table 7. Description of Program Register Bits for SDO Data Format

| SDO FORMAT | BEGINNING OF THE                      | OUTPUT FORMAT                                         |                     |                   |                   |  |  |

|------------|---------------------------------------|-------------------------------------------------------|---------------------|-------------------|-------------------|--|--|

| SDO[2:0}   | OUTPUT BIT STREAM                     | BITS[24:9]                                            | BITS[8:5]           | BITS[4:3]         | BITS[2:0]         |  |  |

| 000        | 16th SCLK falling edge;<br>no latency | Conversion result for selected<br>channel (MSB-first) | SDO pulled low      |                   |                   |  |  |

| 001        | 16th SCLK falling edge;<br>no latency | Conversion result for selected<br>channel (MSB-first) | Channel address SDC |                   | ulled low         |  |  |

| 010        | 16th SCLK falling edge;<br>no latency | Conversion result for selected<br>channel (MSB-first) | Channel address     | Device<br>address | SDO pulled<br>low |  |  |

| 011        | 16th SCLK falling edge;<br>no latency | Conversion result for selected<br>channel (MSB-first) | Channel address     | Device<br>address | Input range       |  |  |

Software Description

www.ti.com

## Table 8. Data Output Sequence with ADS8688 Daisy Chaining

| WORD OUTPUT (ASSUMING ALL EIGHT<br>CHANNELS ARE CONFIGURED) | ADC <sub>1</sub> (DAISY CHAIN INPUT GROUNDED) | ADC2 (SDO FOR ADC <sub>1</sub> CONNECTED TO<br>ADC2 DAISY CHAIN INPUT) |

|-------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------|

| Word 1                                                      |                                               | CH0                                                                    |

| Word 2                                                      | CH0                                           |                                                                        |

| Word 3                                                      |                                               | CH1                                                                    |

| Word 4                                                      | CH1                                           |                                                                        |

| Word 5                                                      |                                               | CH2                                                                    |

| Word 6                                                      | CH2                                           |                                                                        |

| Word 7                                                      |                                               | CH3                                                                    |

| Word 8                                                      | CH3                                           |                                                                        |

| Word 9                                                      |                                               | CH4                                                                    |

| Word 10                                                     | CH4                                           |                                                                        |

| Word 11                                                     |                                               | CH5                                                                    |

| Word 12                                                     | CH5                                           |                                                                        |

| Word 13                                                     |                                               | CH6                                                                    |

| Word 14                                                     | CH6                                           |                                                                        |

| Word 15                                                     |                                               | CH7                                                                    |

| Word 16                                                     | CH7                                           |                                                                        |

#### 5.1.1.1 Achieving Simultaneous Sampling by Daisy-chaining

Simultaneous sampling can be achieved in protection relays by connecting the voltage inputs to ADC1 and current inputs to ADC<sub>2</sub>. Because the sampling for both the ADCs occurs at the same time a high level of simultaneous sampling is achieved. The only error may be because of the phase difference between the two ADC internal oscillator.

Guidelines to achieve simultaneous sampling include the following:

- Ensure minimum delay between the chip select for the two ADCs. ٠

- Ensure the same reference is used which reduces the error and also saves power (connect the ADC<sub>1</sub> reference to the ADC<sub>2</sub> reference and disable the ADC<sub>2</sub> internal reference).

## 5.2 ADC Input Configuration

Range Select Registers (address = 05h (channel 0), 06h (channel 1), 07h (channel 2), 08h (channel 3), 09h (channel 4), 0Ah (channel 5), 0Bh (channel 6), 0Ch (channel 7))

Software Description

These registers allow the selection of input ranges for all individual channels (n = 0 to 7 for ADS8688). The default value for these registers is 00h.

|   |   | Figui | e 14. Channe | i // input Kang | je Registers |                |     |

|---|---|-------|--------------|-----------------|--------------|----------------|-----|

| 7 | 6 | 5     | 4            | 3               | 2            | 1              | 0   |

| 0 | 0 | 0     | 0            | 0               |              | Range_CHn[2:0] |     |

| R | R | R     | R            | R               | R/W          | R/W            | R/W |

|   |   |       |              |                 |              |                |     |

## Figure 14. Channel n Input Range Registers

LEGEND: R/W = Read/Write; R = Read only

## Table 9. Channel n Input Range Registers Field Descriptions

| BIT | FIELD                   | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-------------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | 0                       | R    | 0h    | Must always be set to 0                                                                                                                                                                                                                                                                                                                                                                     |

| 2:0 | Range_CH <i>n</i> [2:0] | R/W  | Oh    | Input range selection bits for channel n (n = 0 to 3 for ADS8684 and n = 0 to 7 for ADS8688).<br>000 = Input range is set to $\pm 2.5 \times V_{REF}$<br>001 = Input range is set to $\pm 1.25 \times V_{REF}$<br>010 = Input range is set to $\pm 0.625 \times V_{REF}$<br>101 = Input range is set to 0 to 2.5 $\times V_{REF}$<br>110 = Input range is set to 0 to 1.25 $\times V_{REF}$ |

## 5.2.1 ADC Gain Control — Programmable Gain Amplifier (PGA)

The devices offer a programmable gain amplifier (PGA) at each individual analog input channel, which converts the original single-ended input signal into a fully-differential signal to drive the internal 16-bit ADC. The PGA also adjusts the common-mode level of the input signal before being fed into the ADC to ensure maximum usage of the ADC input dynamic range. Depending on the range of the input signal, the PGA gain can be accordingly adjusted by setting the Range\_CHn[2:0] (n = 0 to 3 or 7) bits in the program register. The default or power-on state for the Range\_CHn[2:0] bits is 000, which corresponds to an input signal range of  $\pm 2.5 \times V_{REF}$ . Table 10 lists the various configurations of the Range\_CHn[2:0] bits for the different analog input voltage ranges.

The PGA uses a very highly-matched network of resistors for multiple gain configurations. Matching between these resistors and the amplifiers across all channels is accurately trimmed to keep the overall gain error low across all channels and input ranges.

| ANALOG INPUT RANGE           | Range_CHn[2:0] |       |       |  |  |  |

|------------------------------|----------------|-------|-------|--|--|--|

| ANALOG INPUT RANGE           | BIT 2          | BIT 1 | BIT 0 |  |  |  |

| $\pm 2.5 \times V_{REF}$     | 0              | 0     | 0     |  |  |  |

| ±1.25 × V <sub>REF</sub>     | 0              | 0     | 1     |  |  |  |

| ±0.625 × V <sub>REF</sub>    | 0              | 1     | 0     |  |  |  |

| 0 to 2.5 × V <sub>REF</sub>  | 1              | 0     | 1     |  |  |  |

| 0 to 1.25 × V <sub>REF</sub> | 1              | 1     | 0     |  |  |  |

### Table 10. Input Range Selection Bits Configuration

24

## 5.3 ADC Sampling

## 5.3.1 Auto-Scan Sequencing Control Registers

In AUTO\_RST mode, the device automatically scans the preselected channels in ascending order with a new channel selected for every conversion. Each individual channel can be selectively included in the auto channel sequencing. For the channels that are not selected for auto sequencing, the analog front-end circuitry can be individually powered down.

## 5.3.2 Manual Channel Selection Including Aux Channel — Command Register Description

The command register is a 16-bit, write-only register that is used to set the operating modes of ADS8688. The settings in this register are used to select the channel sequencing mode (AUTO\_RST or MAN\_Ch\_n), configure the device in standby (STDBY) or power-down (PWR\_DN) mode, and reset (RST) the program registers to their default values. All command settings for this register are listed in Table 11. During power-up or reset, the default content of the command register is all 0s and the device waits for a command to be written before being placed into any mode of operation The device executes the command at the end of this particular data frame when the CS signal goes high.

| REGISTER                                           | MSB BYTE |     |     |     |     |     |    |    | LSB BYTE  | COMMAND | OPERATION IN NEXT FRAME              |  |

|----------------------------------------------------|----------|-----|-----|-----|-----|-----|----|----|-----------|---------|--------------------------------------|--|

| REGISTER                                           | B15      | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B[7:0]    | (Hex)   |                                      |  |

| Continued Operation<br>(NO_OP)                     | 0        | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0000 0000 | 0000h   | Continue operation in previous mode  |  |

| Standby<br>(STDBY)                                 | 1        | 0   | 0   | 0   | 0   | 0   | 1  | 0  | 0000 0000 | 8200h   | Device is placed into standby mode   |  |

| Power Down<br>(PWR_DN)                             | 1        | 0   | 0   | 0   | 0   | 0   | 1  | 1  | 0000 0000 | 8300h   | Device is powered down               |  |

| Reset program registers<br>(RST)                   | 1        | 0   | 0   | 0   | 0   | 1   | 0  | 1  | 0000 0000 | 8500h   | Program register is reset to default |  |

| Auto Ch. Sequence with Reset<br>(AUTO_RST)         | 1        | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0000 0000 | A000h   | Auto mode enabled following a reset  |  |

| Manual Ch 0 Selection<br>(MAN_Ch_0)                | 1        | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0000 0000 | C000h   | Channel 0 input is selected          |  |

| Manual Ch 1 Selection<br>(MAN_Ch_1)                | 1        | 1   | 0   | 0   | 0   | 1   | 0  | 0  | 0000 0000 | C400h   | Channel 1 input is selected          |  |

| Manual Ch 2 Selection<br>(MAN_Ch_2)                | 1        | 1   | 0   | 0   | 1   | 0   | 0  | 0  | 0000 0000 | C800h   | Channel 2 input is selected          |  |

| Manual Ch 3 Selection<br>(MAN_Ch_3)                | 1        | 1   | 0   | 0   | 1   | 1   | 0  | 0  | 0000 0000 | CC00h   | Channel 3 input is selected          |  |

| Manual Ch 4 Selection<br>(MAN_Ch_4) <sup>(1)</sup> | 1        | 1   | 0   | 1   | 0   | 0   | 0  | 0  | 0000 0000 | D000h   | Channel 4 input is selected          |  |

| Manual Ch 5 Selection<br>(MAN_Ch_5)                | 1        | 1   | 0   | 1   | 0   | 1   | 0  | 0  | 0000 0000 | D400h   | Channel 5 input is selected          |  |

| Manual Ch 6 Selection<br>(MAN_Ch_6)                | 1        | 1   | 0   | 1   | 1   | 0   | 0  | 0  | 0000 0000 | D800h   | Channel 6 input is selected          |  |

| Manual Ch 7 Selection<br>(MAN_Ch_7)                | 1        | 1   | 0   | 1   | 1   | 1   | 0  | 0  | 0000 0000 | DC00h   | Channel 7 input is selected          |  |

| Manual AUX Selection<br>(MAN_AUX)                  | 1        | 1   | 1   | 0   | 0   | 0   | 0  | 0  | 0000 0000 | E000h   | AUX channel input is selected        |  |

## Table 11. Command Register Map

<sup>(1)</sup> Shading indicates bits, registers, or both not included in the 4-channel version of the device.

## 5.3.3 Auto-Scan Sequence Enable Register (address = 01h)

This register selects individual channels for sequencing in AUTO\_RST mode. The default value for this register is FFh, which implies that in default condition all channels are included in the auto-scan sequence.

Software Description

## Figure 15. AUTO\_SEQ\_EN Register

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| CH7_EN | CH6_EN | CH5_EN | CH4_EN | CH3_EN | CH2_EN | CH1_EN | CH0_EN |

| R/W    |

LEGEND: R/W = Read/Write

| BIT | FIELD  | TYPE | RESET | DESCRIPTION                                                                                                                                     |

|-----|--------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CH7_EN | R/W  | 1h    | Channel 7 enable.<br>0 = Channel 7 is not selected for sequencing in AUTO_RST mode<br>1 = Channel 7 is selected for sequencing in AUTO_RST mode |

| 6   | CH6_EN | R/W  | 1h    | Channel 6 enable.<br>0 = Channel 6 is not selected for sequencing in AUTO_RST mode<br>1 = Channel 6 is selected for sequencing in AUTO_RST mode |

| 5   | CH5_EN | R/W  | 1h    | Channel 5 enable.<br>0 = Channel 5 is not selected for sequencing in AUTO_RST mode<br>1 = Channel 5 is selected for sequencing in AUTO_RST mode |

| 4   | CH4_EN | R/W  | 1h    | Channel 4 enable.<br>0 = Channel 4 is not selected for sequencing in AUTO_RST mode<br>1 = Channel 4 is selected for sequencing in AUTO_RST mode |

| 3   | CH3_EN | R/W  | 1h    | Channel 3 enable.<br>0 = Channel 3 is not selected for sequencing in AUTO_RST mode<br>1 = Channel 3 is selected for sequencing in AUTO_RST mode |

| 2   | CH2_EN | R/W  | 1h    | Channel 2 enable.<br>0 = Channel 2 is not selected for sequencing in AUTO_RST mode<br>1 = Channel 2 is selected for sequencing in AUTO_RST mode |

| 1   | CH1_EN | R/W  | 1h    | Channel 1 enable.<br>0 = Channel 1 is not selected for sequencing in AUTO_RST mode<br>1 = Channel 1 is selected for sequencing in AUTO_RST mode |

| 0   | CH0_EN | R/W  | 1h    | Channel 0 enable.<br>0 = Channel 0 is not selected for sequencing in AUTO_RST mode<br>1 = Channel 0 is selected for sequencing in AUTO_RST mode |

## Table 12. AUTO\_SEQ\_EN Field Descriptions

## 5.4 SPI for ADC Data Acquisition

#### 5.4.1 Data Acquisition Example

This section provides an example of how a host processor can use the device interface to configure the device internal registers as well as convert and acquire data for sampling a particular input channel. Figure 16 shows the timing diagram.

Figure 16. Device Operation Using the Serial Interface Timing Diagram

Four events are shown in Figure 16. These events are described as follows:

- **Event 1** The host initiates a data conversion frame through a falling edge of the  $\overline{CS}$  signal. The analog input signal at the instant of the  $\overline{CS}$  falling edge is sampled by the ADC and conversion is performed using an internal oscillator clock. The analog input channel converted during this frame is selected in the previous data frame. The internal register settings of the device for the next conversion can be input during this data frame using the SDI and SCLK inputs. Initiate SCLK at this instant and latch data on the SDI line into the device on every SCLK falling edge for the next 16 SCLK cycles. At this instant, SDO goes low because the device does not output internal conversion data on the SDO line during the first 16 SCLK cycles.

- Event 2 During the first 16 SCLK cycles, the device completes the internal conversion process and data are now ready within the converter. However, the device does not output data bits on SDO until the 16th falling edge appears on the SCLK input. Because the ADC conversion time is fixed (the maximum value is given in the *Electrical Characteristics* table of the data sheet), the 16th SCLK falling edge must appear after the internal conversion is over, otherwise data output from the device is incorrect. Therefore, the SCLK frequency cannot exceed a maximum value, as provided in the Timing Requirements: Serial Interface table of the data sheet.

- Event 3 At the 16th falling edge of the SCLK signal, the device reads the LSB of the input word on the SDI line. The device does not read anything from the SDO line for the remaining data frame. On the same edge, the MSB of the conversion data is output on the SDO line and can be read by the host processor on the subsequent falling edge of the SCLK signal. For 16 bits of output data, the LSB can be read on the 3-s SCLK falling edge. The SDO outputs 0 on subsequent SCLK falling edges until the next conversion is initiated.

- **Event 4**—When the internal data from the device is received, the host terminates the data frame by deactivating the  $\overline{CS}$  signal to high. The SDO output goes into a hi-Z state until the next data frame is initiated, as explained in Event 1.

## 5.5 ADC Transfer Function, Range Selection, and RMS Calculation

## 5.5.1 ADC Transfer Function

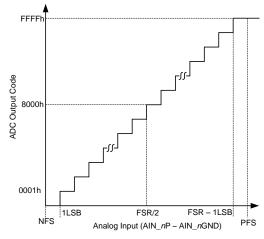

The ADS8688 device is a multichannel device that supports single-ended, bipolar, and unipolar input ranges on all input channels. The output of the device is in straight binary format for both bipolar and unipolar input ranges. The format for the output codes is the same across all analog channels. Figure 17 shows the ideal transfer characteristic for each ADC channel for all input ranges. The full-scale range (FSR) for each input signal is equal to the difference between the positive full-scale (PFS) input voltage and the negative full-scale (NFS) input voltage. The least-significant bit (LSB) size is equal to FSR / 216 = FSR / 65536 because the resolution of the ADC is 16 bits. For a reference voltage of  $V_{REF} = 4.096$  V, the LSB values corresponding to the different input ranges are listed in Table 13.

Figure 17. 16-Bit ADC Transfer Function (Straight Binary Format)

| INPUT RANGE                  | POSITIVE FULL<br>SCALE | NEGATIVE FULL<br>SCALE | FULL-SCALE RANGE | LSB (µV) |

|------------------------------|------------------------|------------------------|------------------|----------|

| $\pm 2.5 \times V_{REF}$     | 10.24 V                | –10.24 V               | 20.48 V          | 312.5    |

| $\pm 1.25 \times V_{REF}$    | 5.12 V                 | –5.12 V                | 10.24 V          | 156.25   |

| $\pm 0.625 \times V_{REF}$   | 2.56 V                 | –2.56 V                | 5.12 V           | 78.125   |

| 0 to 2.5 × $V_{REF}$         | 10.24 V                | 0 V                    | 10.24 V          | 156.25   |

| 0 to 1.25 × V <sub>REF</sub> | 5.12 V                 | 0 V                    | 5.12 V           | 78.125   |

Table 13. ADC LSB Values for Different Input Ranges (V<sub>REF</sub> = 4.096 V)

Software Description

#### 5.5.2 Range Select Registers (address = 05h (Channel 0), 06h (Channel 1), 07h (Channel 2), 08h (Channel 3), 09h (Channel 4, 0Ah (Channel 5), 0Bh (Channel 6), 0Ch (Channel 7)

~

These registers allow the selection of input ranges for all individual channels (n = 0 to 3 for ADS8684 and n = 0 to 7 for ADS8688). The default value for these registers is 00h.

|   | Figure 18. Channel <i>n</i> input Range Registers |   |   |   |                |     |     |  |  |  |

|---|---------------------------------------------------|---|---|---|----------------|-----|-----|--|--|--|

| 7 | 6                                                 | 5 | 4 | 3 | 2              | 1   | 0   |  |  |  |

| 0 | 0                                                 | 0 | 0 | 0 | Range_CHn[2:0] |     |     |  |  |  |

| R | R                                                 | R | R | R | R/W            | R/W | R/W |  |  |  |

LEGEND: R/W = Read/Write; R = Read only

### Table 14. Channel n Input Range Registers Field Descriptions

| BIT | FIELD                   | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                |

|-----|-------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | 0                       | R    | 0h    | Must always be set to 0.                                                                                                                                                                                                                                                                                                                                                                   |

| 2:0 | Range_CH <i>n</i> [2:0] | R/W  | Oh    | Input range selection bits for channel n (n = 0 to 3 for ADS8684 and n= 0 to 7 for ADS8688).<br>000 = Input range is set to $\pm 2.5 \times V_{REF}$<br>001 = Input range is set to $\pm 1.25 \times V_{REF}$<br>010 = Input range is set to $\pm 0.625 \times V_{REF}$<br>101 = Input range is set to 0 to 2.5 $\times V_{REF}$<br>110 = Input range is set to 0 to 1.25 $\times V_{REF}$ |

#### 5.5.3 **RMS Calculation Procedure**

Use the following steps to calculate the RMS (root-mean-squar) value:

- Step 1. Configure the ADC for bipolar input.

- Step 2. Set the required voltage input (variable) and frequency (50 or 60 Hz).

- Step 3. Sample the input at 500 kSPS or the required sample rate.

- Subtract FSR / 2 (offset) from all of the samples (the ADC is unipolar). Step 4.

- Step 5. Square all of the samples and accumulate.

- Step 6. Count the number of samples accumulated.

- Step 7. Divide the accumulated samples by the number of samples accumulated.

- Calculate the square root of the accumulated samples. Step 8.

- Step 9. Scale the code with the configured input range (for example: 10.24 V = Full range).

#### 6 **Test Setup**

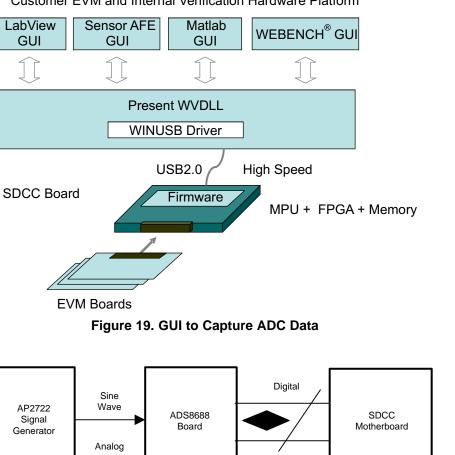

Customer EVM and Internal Verification Hardware Platform

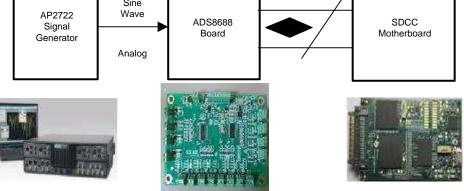

Figure 20. ADC Measurement Setup

The LabVIEW-based GUI is used to interface to the SDCC motherboard. The SDCC motherboard interfaces with the ADS8688 board through SPI interface.

## 7 Test Results

## 7.1 Functional Testing

|                     | MEASURED VALUES |                |

|---------------------|-----------------|----------------|

| Analog power supply | AVDD + 5-V DC   | 4.995 to 4.996 |

| I/O power supply    | DVDD + 3.3 DC   | 3.299 to 3.301 |

| ADC reference       | REFIO 4.096     | 4.097 to 4.098 |

## 7.2 ADC Functionality

### 7.2.1 Functional Testing with Daisy Chain

All of the 8 input channels for  $ADC_1$  and  $ADC_2$  sense the applied input voltage and provide the equivalent ADC codes. No accuracy was tested as part of this test.

### 7.2.2 Settings Made for Interfacing with ADC

## Table 16. ADC Interface Settings

| PARAMETERS                                      | SETTINGS                                                                 |

|-------------------------------------------------|--------------------------------------------------------------------------|

| Clock                                           | The clock programmed was 17 MHz                                          |

| Frame size                                      | The frame size was 48 Bits (16 command + CH1 (16 bits) + Ch2 (16 Bites)) |

| Delay between samples                           | >2 clocks                                                                |

| Analog input applied to Channel 0 and Channel 4 | 5-V DC, 3.5-V <sub>RMS</sub> AC                                          |

## 7.2.3 Observations

30

## Table 17. ADC Input Sensing

| ADC CHANNELS | AC INPUT         | SENSING          | DC INPUT SENSING |                  |  |

|--------------|------------------|------------------|------------------|------------------|--|

| ADC CHANNELS | ADC <sub>1</sub> | ADC <sub>2</sub> | ADC <sub>1</sub> | ADC <sub>2</sub> |  |

| Channel 0    | OK               | OK               | OK               | OK               |  |

| Channel 1    | OK               | OK               | OK               | OK               |  |

| Channel 2    | OK               | OK               | OK               | OK               |  |

| Channel 3    | OK               | OK               | OK               | OK               |  |

| Channel 4    | OK               | OK               | OK               | OK               |  |

| Channel 5    | OK               | OK               | OK               | ОК               |  |

| Channel 6    | OK               | OK               | OK               | ОК               |  |

| Channel 7    | OK               | OK               | OK               | OK               |  |

## 7.3 Analog Input Voltage Measurement

## 7.3.1 Procedure

- Applied an AC voltage as listed in Section 7.4 and Section 7.6 with a frequency of 60 Hz

- Captured samples using LabVIEW-based GUI

- The AM3352 processor interfaced with the ADS8688 device using SPI

- Greater than 10K ADC samples were captured

- RMS was computed for the captured samples

- All errors were measured are without any software calibration

## Table 18. Input Connectors for ADC<sub>1</sub> and ADC<sub>2</sub>

| CHANNELS  | ADC <sub>1</sub> CONNECTOR | ADC <sub>2</sub> CONNECTOR |

|-----------|----------------------------|----------------------------|

| Channel 0 | J2                         | J13                        |

| Channel 1 | J1                         | J14                        |

| Channel 2 | J5                         | J15                        |

| Channel 3 | J6                         | J16                        |

| Channel 4 | J8                         | J17                        |

| Channel 5 | J9                         | J18                        |

| Channel 6 | J3                         | J10                        |

| Channel 7 | J3                         | J12                        |

Test Results

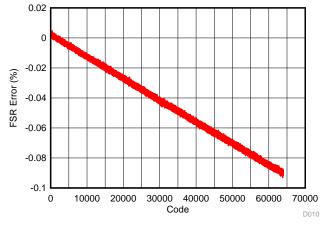

#### 7.4 **Observations**

| ADC CHANNELS | ADC <sub>1</sub> (FIRST IN THE DA<br>DAISY-CHAIN INPU |              | ADC <sub>2</sub> (LAST IN THE DAISY CHAIN) |              |  |

|--------------|-------------------------------------------------------|--------------|--------------------------------------------|--------------|--|

|              | APPLIED INPUT (V)                                     | MEASURED (V) | APPLIED INPUT (V)                          | MEASURED (V) |  |

| Channel 0    | 3.553                                                 | 3.5512       | 3.553                                      | 3.552        |  |

| Channel 1    | 3.551                                                 | 3.55         | 3.551                                      | 3.5501       |  |

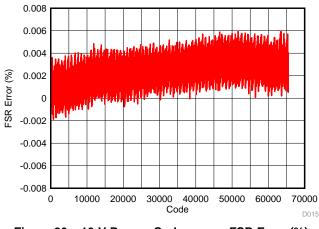

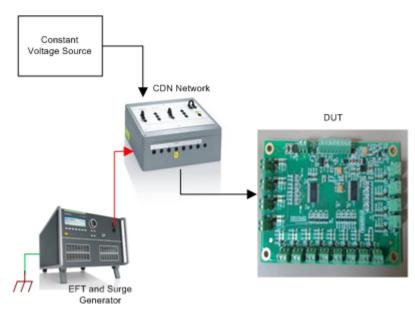

| Channel 2    | 3.5532                                                | 3.5512       | 3.5532                                     | 3.552        |  |