### 7 Series FPGA Transceivers

Wolfgang Mödinger, Xilinx FAE SO-Open-Days, Vienna December 2012

### **Agenda**

- > Why Transceivers?

- Update on 7-Series Status first 28nm FPGAs shipping since March!

- > Transceiver Overview

- > Transceiver Architecture

- Block Diagrams + Supported Protocols

- Optics Support

- Backplane Support

- 28Gbps Support (special section)

- > 7 Series Overview

- Family Tables

- Schedule

- Summary

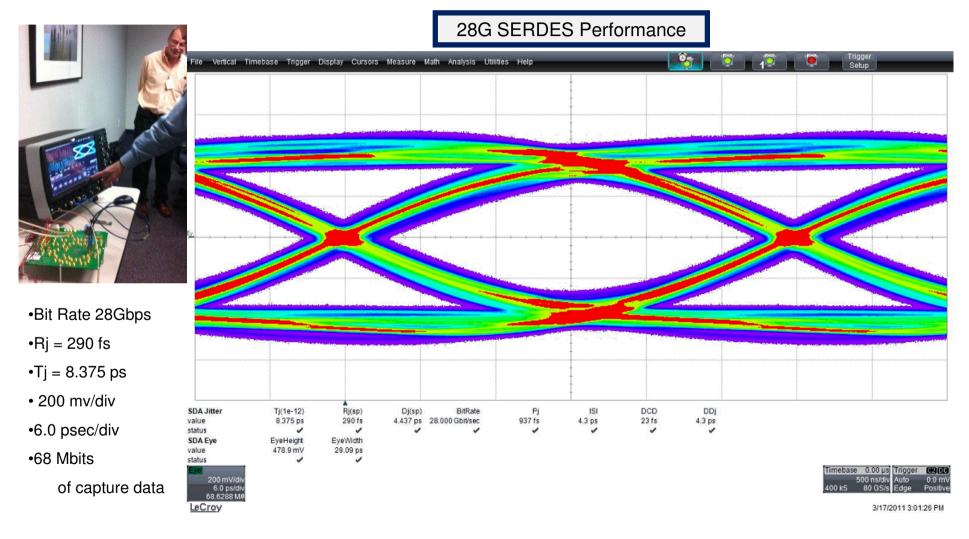

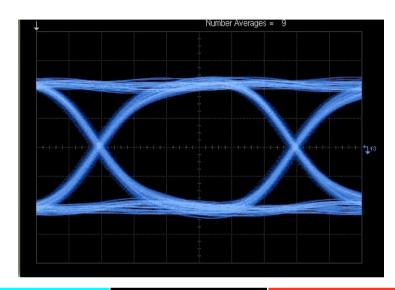

## **GTZ 28G Serdes Test Chip LC Tank PLL Eye Diagram**

**Period: 97ps (10.3125Gbps)**

TJ: 14.78ps @ 1e-12 BER (15%)

RJ: 654.30fs (9%) DJ: 5.62ps (6%)

|                               | 10G SFP+<br>Spec | Xilinx<br>7series G | ГХ |

|-------------------------------|------------------|---------------------|----|

| Random Jitter<br>(Rj) @ 1^-12 | 0.15UI           | 0.09 UI             | 1  |

| Deterministic<br>Jitter (Dj)  | 0.15UI           | 0.06 UI             | 1  |

| Total Jitter (Tj)             | 0.28UI           | 0.15 UI             |    |

#### **DISCLAIMER!**

This data is very early, typical silicon and based on 1 week of testing!

### **Transceiver Overview**

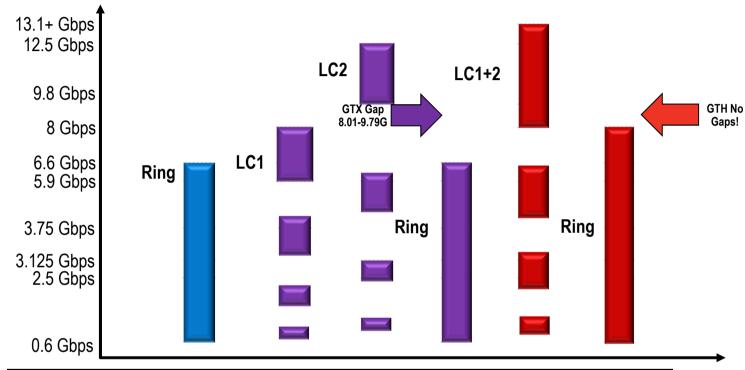

### 7 Series Transceiver Roadmap 40nm => 28nm Roadmap

### 7 Series Min/Max Performance by Package/Speed Grade

|                | Α   | rtix G             | ТР          |     | Kintex G           | TX           | Virte | ex GTX  | Virte | x GTH   | Virte | x GTZ |

|----------------|-----|--------------------|-------------|-----|--------------------|--------------|-------|---------|-------|---------|-------|-------|

| Speed<br>Grade | min | max<br>(FB,<br>CS) | max<br>(FF) | min | max<br>(FB,<br>CS) | max<br>(FF)* | min   | max     | min   | max     | min*  | max   |

| -1 C/I LE      | 0.5 | 3.75               | 3.75        | 0.5 | 6.6                | 6.6          | 0.5   | 6.6     | 0.5   | 8.5     | 2.45  | 25.78 |

| -2 C/I LE      | 0.5 | 5.4                | 6.6         | 0.5 | 6.6                | 10.3125      | 0.5   | 10.3125 | 0.5   | 10.3125 | 2.45  | 25.78 |

| -2 E           | N/A | N/A                | N/A         | N/A | N/A                | N/A          | 0.5   | 10.3125 | 0.5   | 11.3    | 2.45  | 25.78 |

| - 2 GE         | N/A | N/A                | N/A         | N/A | N/A                | N/A          | 0.5   | 12.5    | 0.5   | 13.1    | 2.45  | 28.05 |

| -3 E           | 0.5 | 5.4                | 6.6         | 0.5 | 6.6                | 12.5         | 0.5   | 12.5    | 0.5   | 13.1    | N/A   | N/A   |

#### Notes:

- This table describe max/min rates, more details in the following slides

- 10G+ performance in K7 requires FF package (lidded flipchip)

- E temp grade is 0'C 100'C temp range

- GTZ frequency range is 19.6G to max with /2, /4 and /8 dividers

- Rates from 500Mbps to 0Mbps can be supported with XAPP875

## 7 Series Transceiver Architecture PLL Range (-3E speed grade)

| Divider | Artix | 7 GTP   | Kinte      | x7/Virtex7 G | TX       | Virte          | c7 GTH  |

|---------|-------|---------|------------|--------------|----------|----------------|---------|

| Dividei | LC    | Ring    | LC1        | LC2          | Ring     | LC1+2          | Ring    |

| /1      | N/A   |         | 5.9-8.0    | 9.8-12.5     |          | 8.0-13.1       |         |

| /2      | N/A   |         | 2.9-4.0    | 4.9-6.25     |          | 4.0-6.55       |         |

| /4      | N/A   |         | 1.45-2.0   | 2.4-3.125    |          | 2.0-3.25       |         |

| /8      | N/A   |         | 0.7-1.26   | 1.2-1.56     |          | 1.0-1.6        |         |

|         |       | 0.6-6.6 |            |              | 0.6-6.6  | \/!! !b !\/ ** | 0.6-8.0 |

|         |       |         | XILINX CON | NFIDENTIAL   | <b>~</b> | XILIIVX 🌽      | ALL PRO |

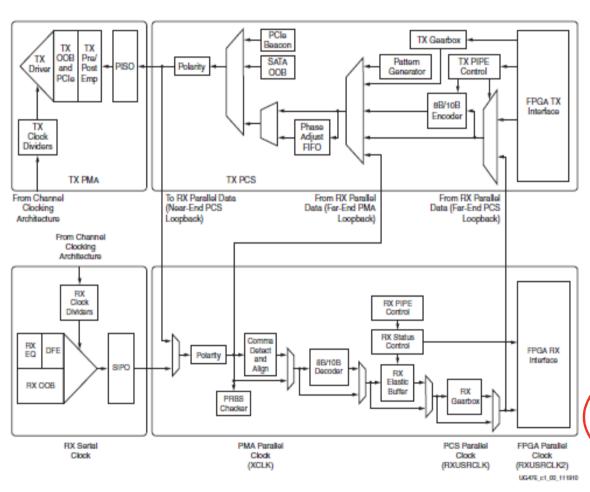

## 7 Series Architecture Block Diagram of a Single Channel (GTX)

- ➤ One "channel" is one TX and one RX

- > Key Features:

- Datapaths:

- 0G to 12.5G\* for GTX

- Equalization:

- TX Pre/Post Emphasis

- RX AGC

- RX CTLE (linear EQ)

- RX DFE

- Debug/Test

- Hard Logic PRBS gen/check

- 2D eyescan

<sup>\* 0</sup>G – 0.499G requires XAPP 875

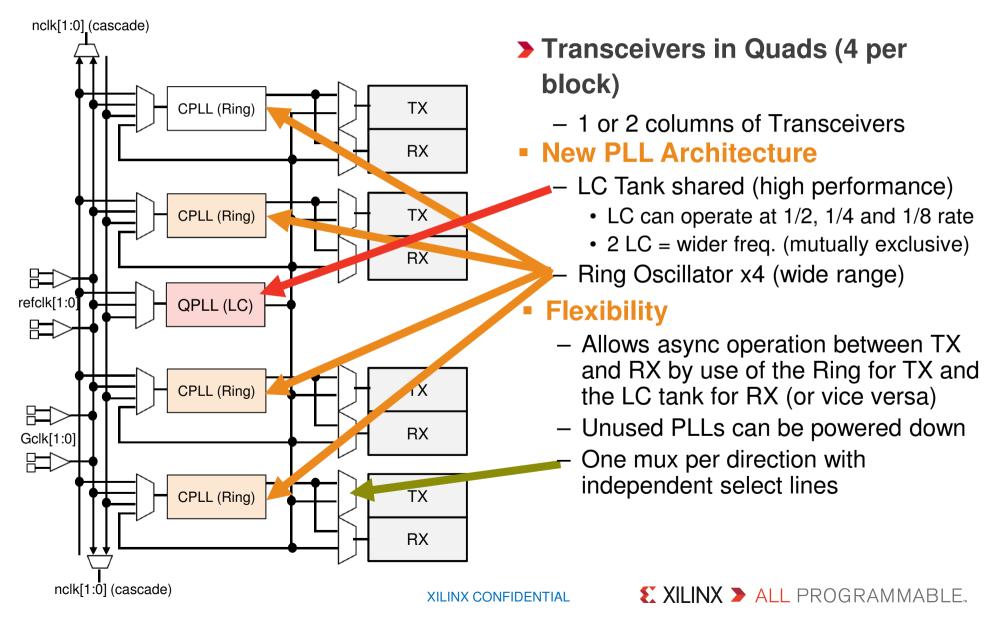

## 7 Series GTX and GTH Transceiver Architecture Block Diagram of Transceiver Quad

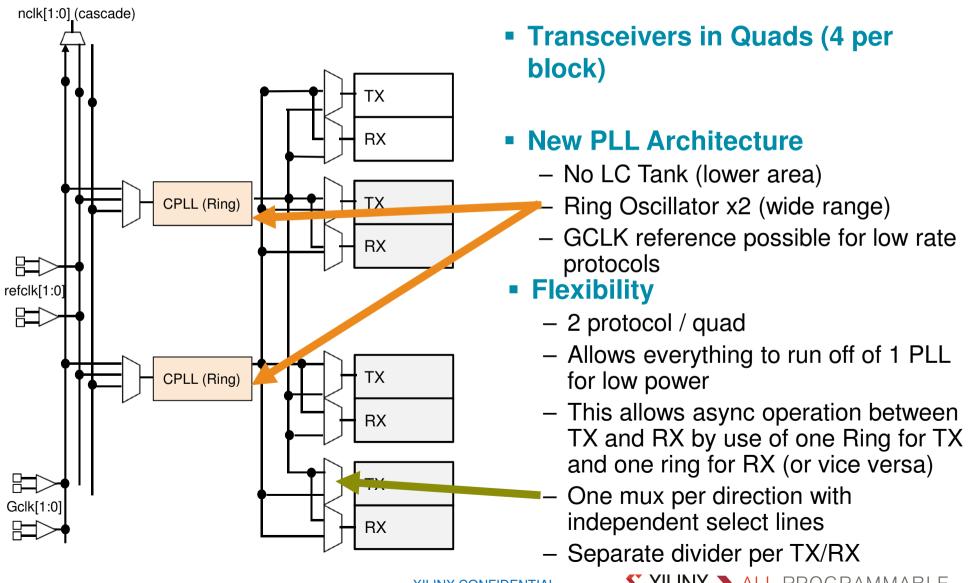

### 7 Series GTP Transceiver Architecture **Block Diagram of Transceiver Quad**

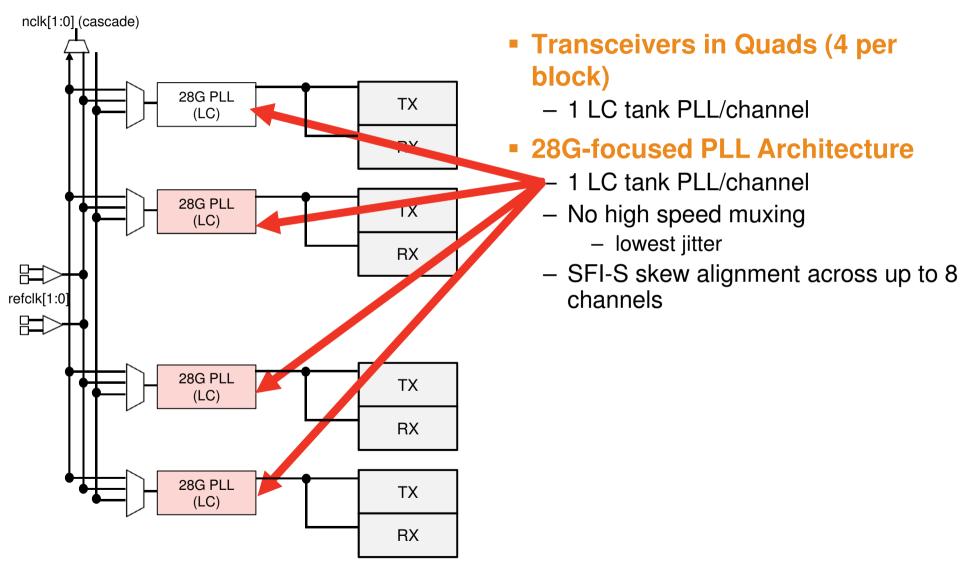

# 7 Series GTZ Transceiver Architecture Block Diagram of Transceiver Octal

## 7 Series Transceiver Architecture Major Supported Protocols

| Protocol            | Artix-7 GTP                                                                                                                                     | Kintex-7/Virtex-7 GTX                                                                                                                                      | Virtex-7 GTH                                                                                                                                                                                                                                      | Virtex-7 GTZ                                                                                                                                                                                                                                                                                                                                                             |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Express         | Gen1, 2                                                                                                                                         | Gen1, 2, 3                                                                                                                                                 | Gen1, 2, 3                                                                                                                                                                                                                                        | (supported on GTH)                                                                                                                                                                                                                                                                                                                                                       |

| Ethernet            | 1GE, 2.5GE,<br>XAUI, RXAUI                                                                                                                      | 1GE, 2.5GE, XAUI, RXAUI,<br>10GBase-R, 10G-KR*, 40GE, 100GE                                                                                                | 1GE, 2.5GE, XAUI, RXAUI, 10GBase-R, 10G-KR (enhanced), 40GE, 100GE                                                                                                                                                                                | 100GE (25.7G)                                                                                                                                                                                                                                                                                                                                                            |

| SONET/OTU           | OC-3/12/48                                                                                                                                      | OC-3/12/48/192, OTU1/2/3/4                                                                                                                                 | OC-3/12/48/192, OTU1/2/3/4                                                                                                                                                                                                                        | OTU4 w 7% FEC (27.95G)<br>SFI-S, OTL4.4                                                                                                                                                                                                                                                                                                                                  |

| Interlaken          | <= 6.6G                                                                                                                                         | <=6.5G, 10.3125G 12.5G                                                                                                                                     | <=6.5G, 10.3125G, 12.5G                                                                                                                                                                                                                           | 20.625G (2x10.3125),<br>25G (2x12.5G)                                                                                                                                                                                                                                                                                                                                    |

| Custom<br>Backplane | <= 3.125G                                                                                                                                       | <=6.5G, CEI-11-LR*                                                                                                                                         | <= 6.5G, CEI-11LR (enhanced)                                                                                                                                                                                                                      | (supported on GTH)                                                                                                                                                                                                                                                                                                                                                       |

| PON                 | BPON, GPON, GEPON<br>( up to 1.25 BCDR)                                                                                                         | BPON, GPON, GEPON, 10GEPON,<br>10GGPON (up to 2.5G BCDR)                                                                                                   | BPON, GPON, GEPON,<br>10GEPON, 10GGPON                                                                                                                                                                                                            | (supported on GTH)                                                                                                                                                                                                                                                                                                                                                       |

| CPRI/OBSAI          | 0.614, 1.2, 2.4, 3.0,<br>4.9, 6.6                                                                                                               | 0.614, 1.2, 2.4, 3.0, 4.9,<br>6.14, 9.8, 12                                                                                                                | 0.614, 1.2, 2.4, 3.0, 4.9,<br>6.14, 9.8, 12                                                                                                                                                                                                       | 2.4, 3.0, 4.9, 6.0, 9.8, 19.6, 24                                                                                                                                                                                                                                                                                                                                        |

| Serial Rapid IO     | Gen1, 2                                                                                                                                         | Gen1, 2                                                                                                                                                    | Gen1, 2                                                                                                                                                                                                                                           | (supported on GTH)                                                                                                                                                                                                                                                                                                                                                       |

| SDI                 | SD/HD/3G-SDI                                                                                                                                    | SD/HD/3G-SDI/10G-SDI                                                                                                                                       | SD/HD/3G/10G-SDI                                                                                                                                                                                                                                  | (supported on GTH)                                                                                                                                                                                                                                                                                                                                                       |

| DisplayPort         | 1.6, 2.7, 5.4                                                                                                                                   | 1.6, 2.7, 5.4                                                                                                                                              | 1.6, 2.7, 5.4                                                                                                                                                                                                                                     | (supported on GTH)                                                                                                                                                                                                                                                                                                                                                       |

| QPI                 | х                                                                                                                                               | 4.8, 6.4`                                                                                                                                                  | 4.8, 6.4, 8.0, 9.6                                                                                                                                                                                                                                | (supported on GTH)                                                                                                                                                                                                                                                                                                                                                       |

| Fiber Channel       | 1G, 2G                                                                                                                                          | 1G, 2G, 4G, 10G                                                                                                                                            | 1G, 2G, 4G, 8G, 10G                                                                                                                                                                                                                               | FC32 (28.05G), FC20,<br>FC16, FC10                                                                                                                                                                                                                                                                                                                                       |

| SATA/SAS            | 1.5G, 3G, 6G                                                                                                                                    | 1.5G, 3G, 6G                                                                                                                                               | 1.5G, 3G, 6G                                                                                                                                                                                                                                      | (supported on GTH)                                                                                                                                                                                                                                                                                                                                                       |

| Aurora              | Up to 6.6G                                                                                                                                      | Up to 12.5G                                                                                                                                                | Up to 13.1G                                                                                                                                                                                                                                       | Up to 28.05G                                                                                                                                                                                                                                                                                                                                                             |

|                     | PCI Express Ethernet  SONET/OTU  Interlaken  Custom Backplane  PON  CPRI/OBSAI  Serial Rapid IO  SDI  DisplayPort  QPI  Fiber Channel  SATA/SAS | PCI Express         Gen1, 2           Ethernet         1GE, 2.5GE, XAUI, RXAUI           SONET/OTU         OC-3/12/48           Interlaken         <= 6.6G | PCI Express         Gen1, 2         Gen1, 2, 3           Ethernet         1GE, 2.5GE, XAUI, RXAUI, 10GBase-R, 10G-KR*, 40GE, 100GE           SONET/OTU         OC-3/12/48         OC-3/12/48/192, OTU1/2/3/4           Interlaken         <= 6.6G | PCI Express         Gen1, 2         Gen1, 2, 3         Gen1, 2, 3           Ethernet         1GE, 2.5GE, XAUI, RXAUI, 10GBase-R, 10G-KR*, 40GE, 100GE         1GE, 2.5GE, XAUI, RXAUI, 10GBase-R, 10G-KR*, 40GE, 100GE           SONET/OTU         OC-3/12/48         OC-3/12/48/192, OTU1/2/3/4         OC-3/12/48/192, OTU1/2/3/4           Interlaken         <= 6.6G |

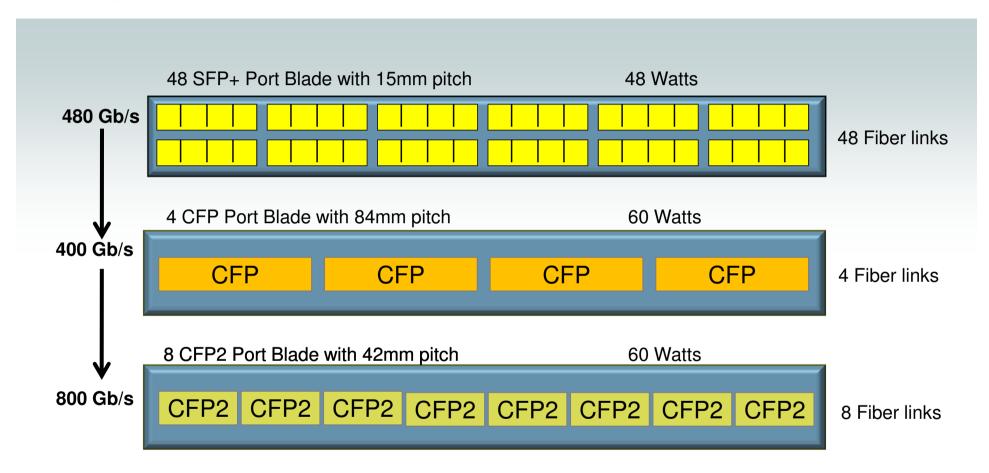

# Optical Interfaces Optics Support: what is planned.

|                                              |           |                                                                          | 40nm          |        | 28           | nm     |        |

|----------------------------------------------|-----------|--------------------------------------------------------------------------|---------------|--------|--------------|--------|--------|

| Protocol                                     | Module    | Notes                                                                    | V6 HXT<br>GTH | A7 GTP | K7/V7<br>GTX | V7 GTH | V7 GTZ |

| 100GE/OTU4                                   | CFP       | 10x10.3G / 10x12.5G                                                      |               |        |              |        |        |

|                                              | CXP       | 10x10.3G / 10x12.5G                                                      |               |        |              |        |        |

|                                              | CFP2      | 4x25.78G / 4x27.95G                                                      |               |        |              |        |        |

| 40GE/OTU3                                    | 300pin    | 17x2.488G                                                                |               |        | V            |        |        |

|                                              | (lim)QSFP | 4x10.3125G                                                               |               |        |              |        |        |

| 10GE/OTU2/OC<br>192/FC10/<br>CPRI9.8/6/4.9/3 | (lim)SFP+ | 1x9.95G / 1x10.3G /<br>1x10.5G / 1x10.7G /<br>1x11.3G /<br>1x9.8/6/4.9/3 | <b>V</b>      |        | 1            |        |        |

|                                              | XFP       | 1x9.95G / 1x10.3G /<br>1x10.5G / 1x10.7G /<br>1x11.3G / 1x9.8G           |               |        |              |        |        |

|                                              | XENPAK    | 4x3.125G                                                                 |               |        |              |        |        |

| GigE /<br>OC-48/12/3 FC<br>4/2/1             | SFP       | 1x1.25G / 1x2.488G /<br>1x0.622G / 1x0.155G                              | V             |        |              | 1      |        |

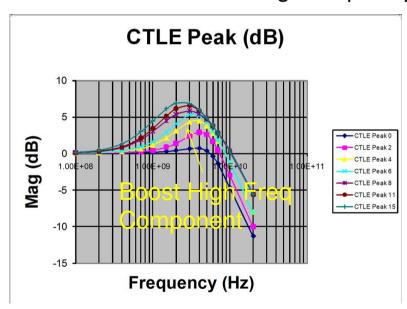

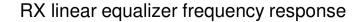

## **Backplanes and Equalization Technique #1: Linear Equalization**

### **➤ Linear Equalization**

- Transmitter: Attenuate low frequency and/or boost high frequency

- Receiver: Boost high frequency

- Compensate insertion loss

- Limitation: Boost high frequency noise

TX pre-emphasis attenuate low frequency & boost high frequency

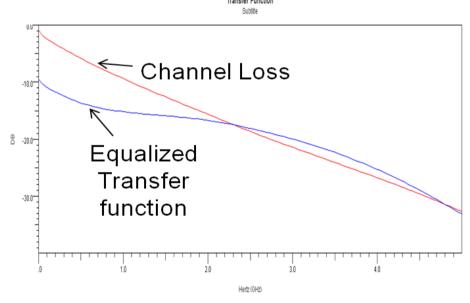

## Backplane and Equalization Technique #2: Decision Feedback Equalization

### ➤ Decision Feedback Equalization (DFE)

- A nonlinear equalizer that uses previous symbols to eliminate the Inter-Symbol-Interference (ISI) on current symbol.

- The ISI on current symbol, caused by previous symbols, is subtracted by DFE.

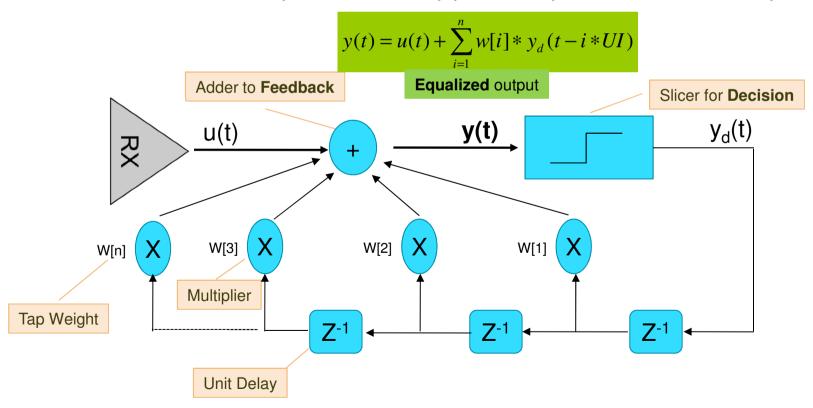

## **Backplane and Equalization DFE Challenge and Limitation**

- > Tap weight

- Ideal tap weights

- LMS Adaptation

- > Error propagation

- > Speed requirement

Tap weight based on ISI

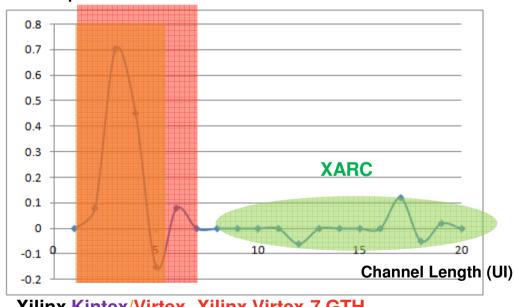

## **Backplane and Equalization XARC – Xilinx Advanced Reflection Cancellation**

### > DFE for Reflection

- Regular DFE cancels reflections near the package

- Virtex-7 GTH with DFE + XARC cancels reflections farther in the channel

\* XARC = Xilinx Advanced Reflection Cancellation

Xilinx Kintex/Virtex Xilinx Virtex-7 GTH

GTX 7 fixed + XARC

# **Backplanes and Equalization Backplane Support with 7-Series**

| Geometry                 | 40nm                           | 28nm                           |                                   |

|--------------------------|--------------------------------|--------------------------------|-----------------------------------|

| Parameter                | V6 HXT                         | K7/V7GTX                       | V7GTH                             |

| Max Rate                 | 11.18 (LC)                     | 12.5                           | 13.1                              |

| LC Tank                  | 11.18                          | 12.5                           | 13.1                              |

| TX Jitter (all 10 lanes) | < 0.28 UI                      | 0.15 UI typ<br>(preliminary)   | TBD (equal or better to GTX)      |

| TX Pre/Post emphasis     | Yes                            | Yes                            | Yes                               |

| RX Linear<br>EQ          | Adaptive                       | Adaptive                       | Adaptive                          |

| RX DFE<br>#taps          | 3                              | 5                              | 11 (7 fixed + 4 sliding up to 50) |

| RX DFE<br>Adaptive Y/N   | Adaptive (3 <sup>rd</sup> gen) | Adaptive (4 <sup>th</sup> gen) | Adaptive (5 <sup>th</sup> gen)    |

| 10G-KR<br>support Y/N    | No<br>(IP tested @ UNH)        | Good                           | Best                              |

| Internal<br>Eyescan Y/N  | 1D (3 <sup>rd</sup> gen)       | 2D (4 <sup>th</sup> gen)       | 2D (5 <sup>th</sup> gen)          |

Significant

Improvements in 10G

Long-Reach Support

for 28nm!

V7 GTH will be the best backplane transceiver in any FPGA

### **7-series Transceiver Tools**

## **Transceiver Tools A Note on Tools and Usability**

### Xilinx-generated IP cores

- Xilinx engineers encapsulate the Transceiver in their cores

- Easier for customers and prevents misconfiguration

- Examples: PCIe, 10GE, Interlaken, CPRI, SDI, etc.

#### Xilinx Transceiver Wizard

- Allows pre-configured settings for common protocols

- Allows GUI-based customization for customer protocols

- Performs clocking and other transceiver connectivity DRCs

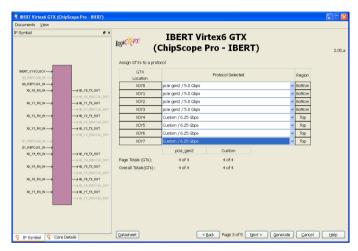

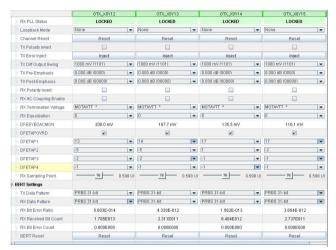

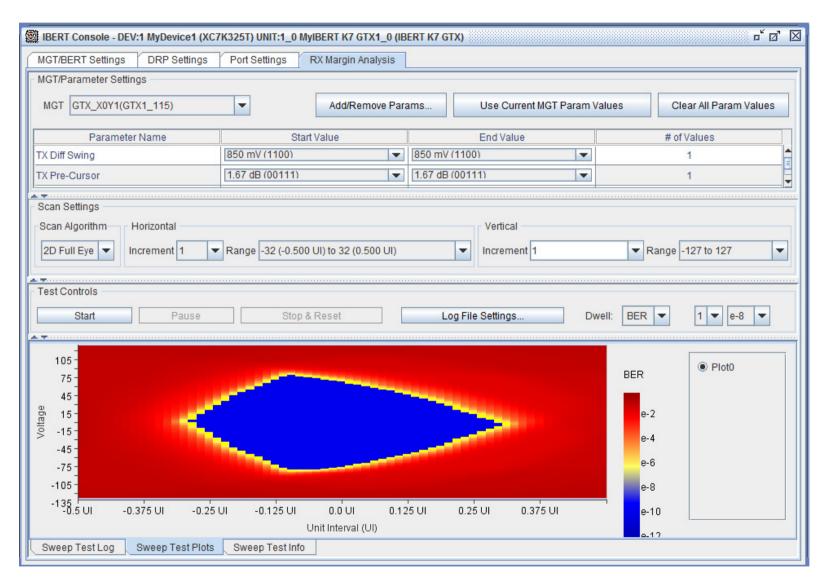

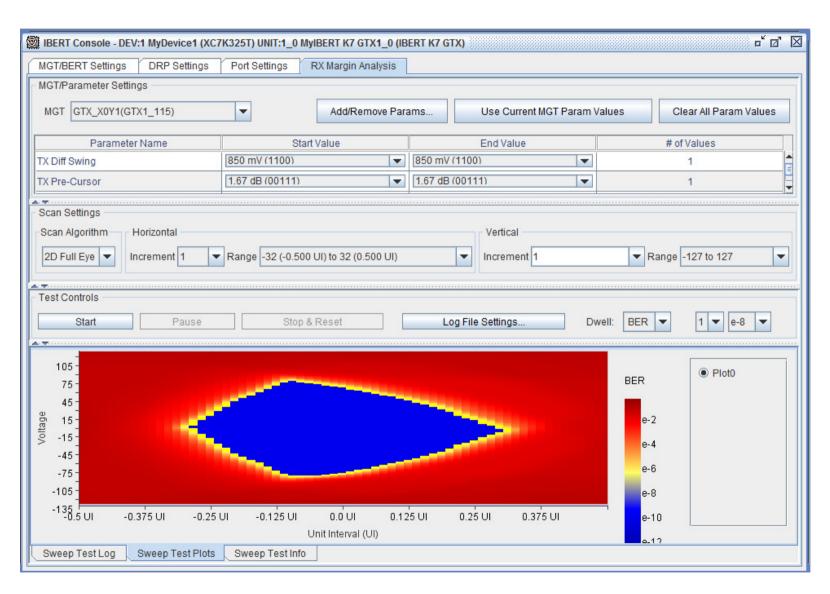

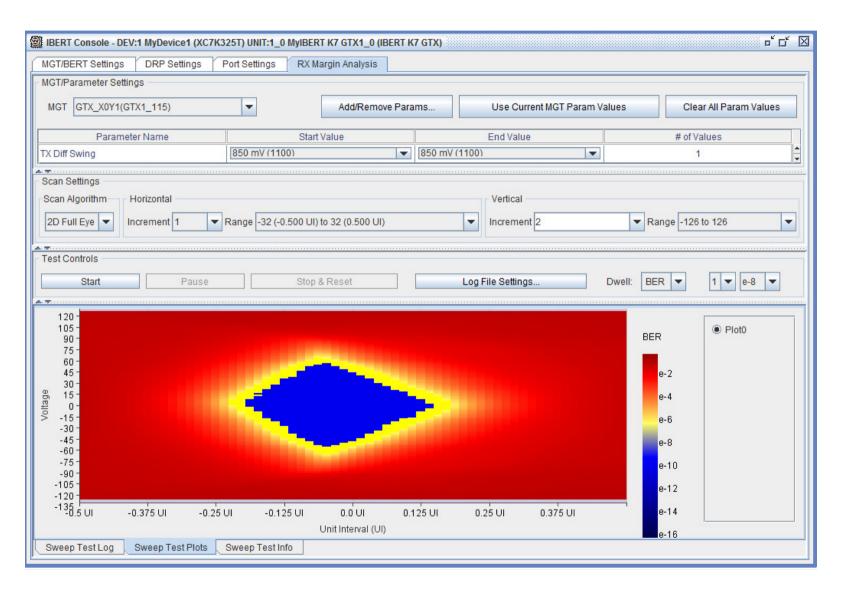

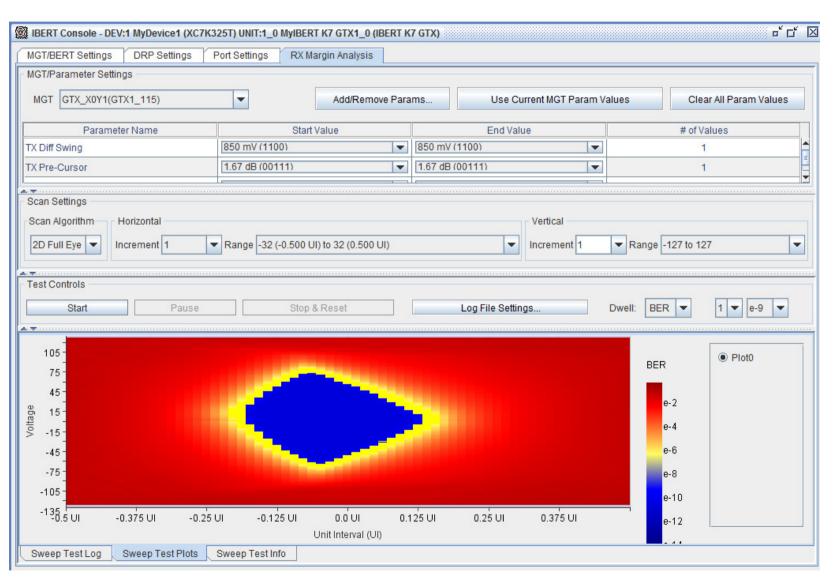

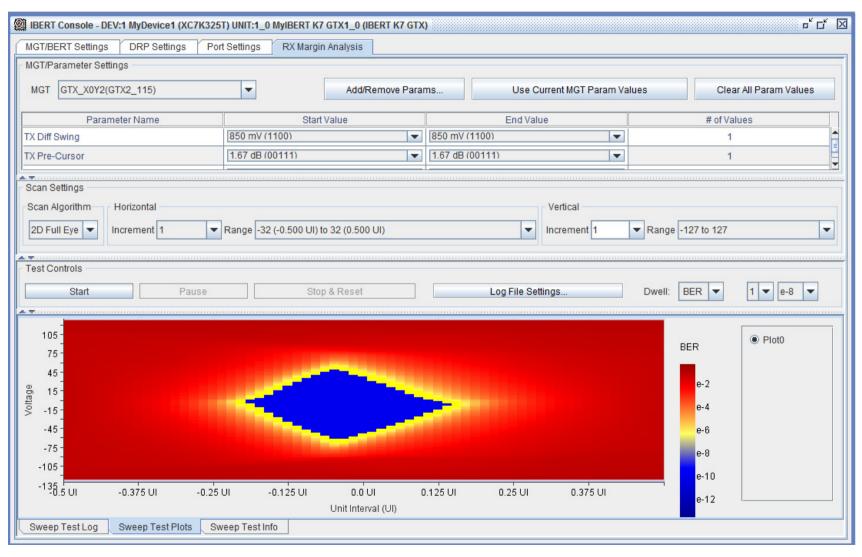

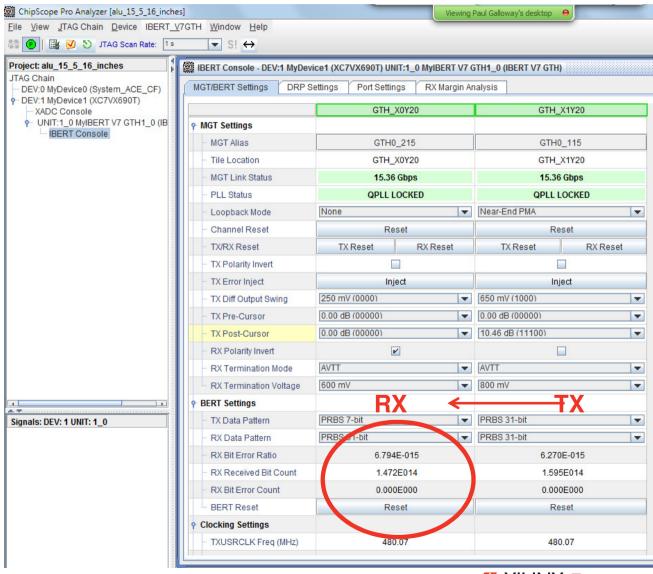

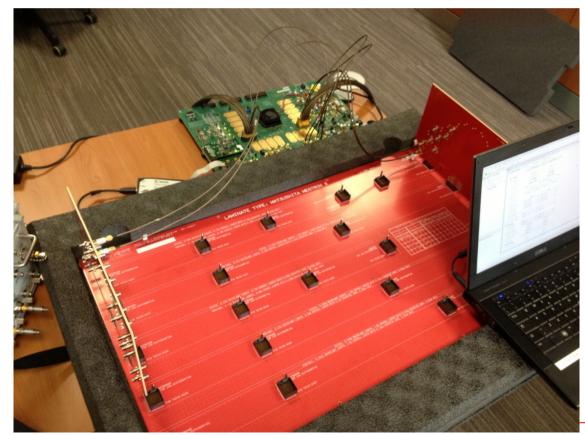

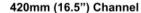

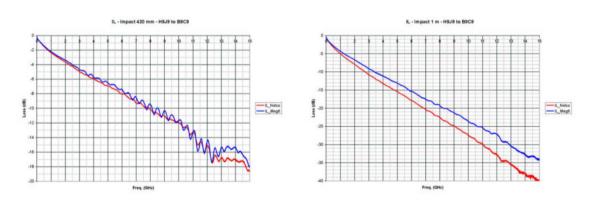

### Xilinx Chipscope IBERT

- Allows hardware evaluation of backplanes with the real FPGA

- Allows in-system debug for system bringup and manufacturing burn-in

- IBERT GUI Key Features

- Hardware PRBS Generator/Checker

- Eye Height and TX Pre-emphasis adjustment

- Eyescan allows margining of channel in Hardware

## **Transceiver Tools IBERT - Integrated Bit Error Rate Tester**

IBERT Generator GUI

Targets the FPGA on your board

- 6 Series Bathtub plots from run time GUI

- 7 Series will be statistical eye using non-destructive eye monitor

- Gives you relative measurements of channel margin and EQ performance

Run time GUI

Controls the transceivers on your board

Adjust all transceiver parameters - swing

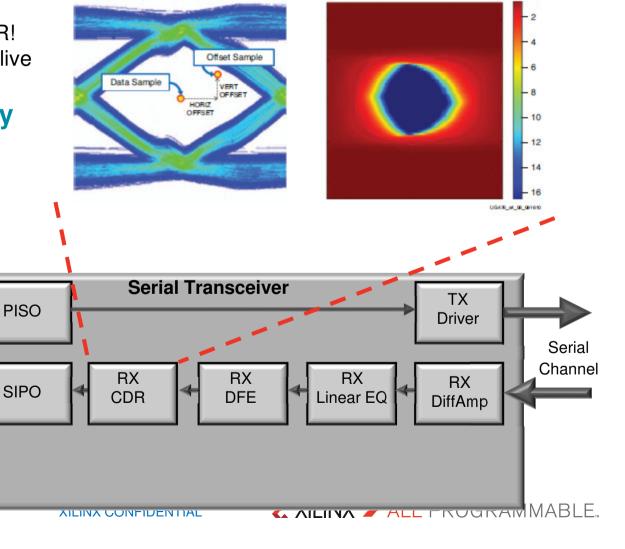

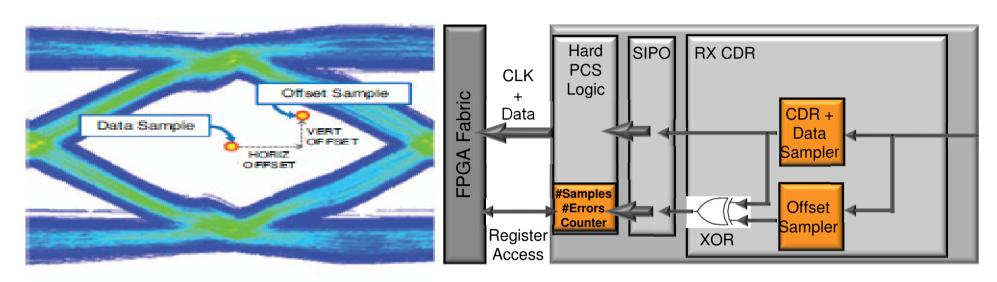

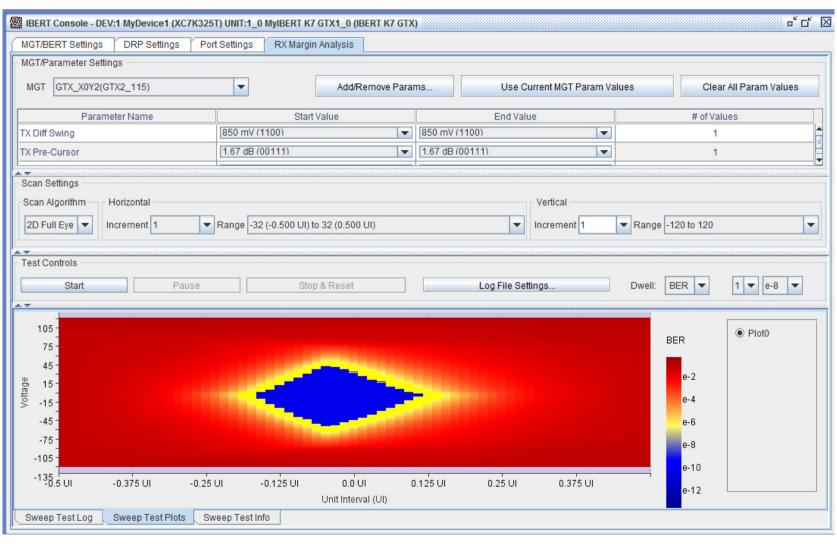

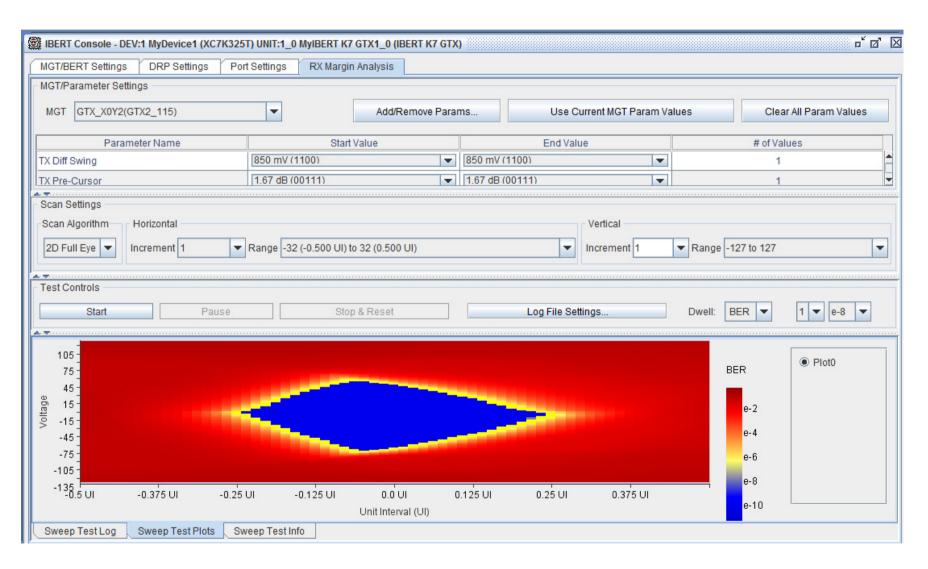

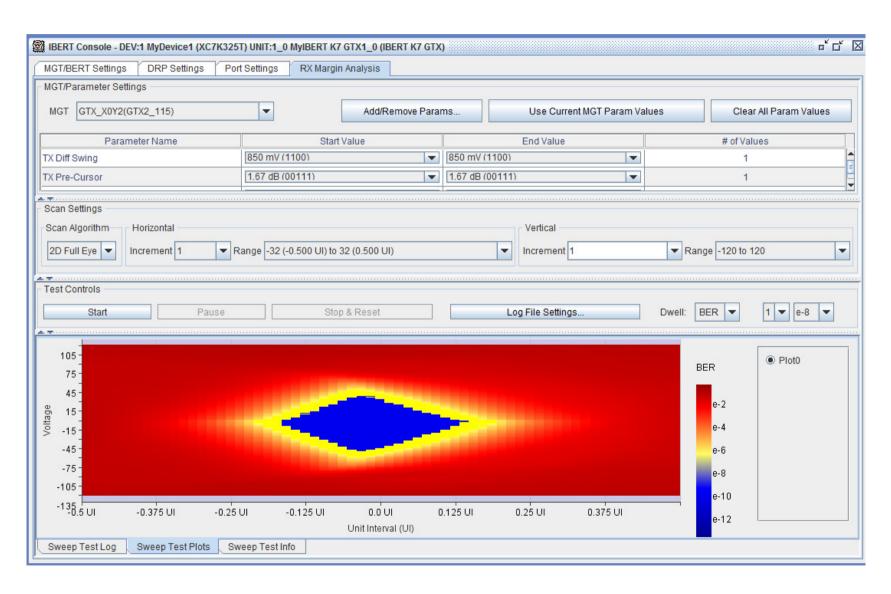

# Transceiver Tools: 7-Series Chipscope w. IBERT and Eye Scan)

#### Look inside the receiver!

- View Post-EQ eye

- Measure and extrapolate BER!

- Non-destructive scanning on live data!

Hard PCS

Logic

### Proven Xilinx Technology

-PGA Fabric

- 5<sup>th</sup> generation eye scan

- 2D eye plot (T and V)

## Transceiver Tools: How Does Non-Destructive Eye Scan Work?

- Two Samplers in RX Path

- Data Sampler:

- same as regular CDR

- Always in center of eye

- Offset Sampler

- Moveable sampler to trace the eye

- If Data and Offset Sampler have different value, a Bit Error has occurred at the Offset Sampler!

- # samples and #errors recorded in PCS counter

- Allows non-destructive EyeScan on LIVE data w/o creating Data Errors

| Data | Offset | Bit Error? |

|------|--------|------------|

| 0    | 0      | 0          |

| 0    | 1      | 1          |

| 1    | 0      | 1          |

| 1    | 1      | 0          |

### Scan Eye 12.5G 156.25MHz refclk (PRBS 7)

# Transceiver Tools: How Does Non-Destructive Eye Scan Work?

Application Note: 7 Series FPGAs

XAPP743 (v1.0) October 18, 2012

### Eye Scan with MicroBlaze Processor MCS

Author: Mike Jenkins and David Mahashin

#### Summary

This application note describes code that executes on an internal MicroBlaze™ processor, implementing the algorithm to measure a statistical eye (bit error ratio (BER) versus time and voltage offset) at the post-equalization data sampling point within the receiver of a 7 series FPGA transceiver. Point-by-point measured data is stored in block RAM to be burst read by an external host PC.

#### Introduction to Eye Scan

As line rates and channel attenuation increase, receiver equalizers are more often enabled to overcome channel attenuation. This poses a challenge to system bring-up because the quality of the line cannot be determined by measuring the far-end eye opening at the receiver pins. At high line rates, the received eye measured on the printed circuit board can appear to be completely closed even though the internal eye after the receiver equalizer is open.

Virtex-7HT

Details on our 28Gbps GTZ Transceiver

## Tackling the Power / Bandwidth Density Problem

Power Density is the Primary Limiting Factor

To Maximizing Density and Minimize Power Consumption

# **28G GTZ Transceiver Key Features Summary**

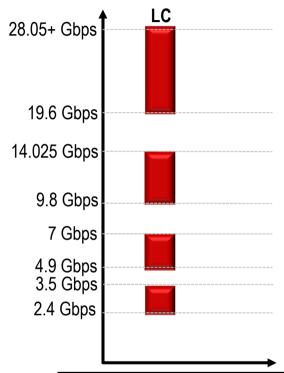

#### Wide Range : 28.05G – 19.6G

- Full range available in Extended Commercial Temperature Grade (0-100'C)

- Allows support of "next generation" CPRI @ 19.6Gbps

- /2, /4 and /8 dividers allow support of 10G and lower datarates

#### Highest Performance : 28G LC Tank Architecture

- GTZ purpose-built for highest performance @ 28Gbps for CEI-28G specs

- One LC/channel for maximum performance (no muxing or fanout)

- Shared reference clock in quad granularity

#### Designed for Signal Integrity

- Proprietary Noise-Isolating Architecture offers nearly 15dB better isolation

- Ceramic packaging for lowest loss

- Extra package ground shielding isolated from SelectIO and GTH transceivers

- Pinout for interface to 4x28G CFP2 optics (e.g. TX0, TX1, TX2, TX3, RX0, RX1, RX2, RX3)

### Signal Conditioning Circuitry

- Controllable Signal Swing and Pre-Emphasis

- Auto-Adaptive Equalization to resolve high loss of PCB @ 28G

### The Industry's Best Serial Debug Tools

Horizontal and Vertical Eyescan tools for channel optimization

## **GTZ Transceiver Speed Grade, Frequency Range, Protocol Support**

| Speed   | Virtex- | 7HT GTZ |

|---------|---------|---------|

| Grade   | min     | max     |

| -1L C/E | n/a     | n/a     |

| -1 C/E  | 2.4     | 25.78   |

| -2 C/E  | 2.4     | 28.05   |

| -3 E    | N/A     | N/A     |

| Market   | Protocol      | Virtex-7HT GTZ                             |

|----------|---------------|--------------------------------------------|

| General  | PCI Express   | (supported on GTH)                         |

|          | Ethernet      | 100GE (25.7G)                              |

| Wired    | SONET/OTU     | OTU4 w 7% FEC (27.95G)<br>SFI-S and OTL4.4 |

|          | Interlaken    | 20.625G (2x10.3125) and 25G (2x12.5G)      |

|          | Backplane     | (supported on GTH)                         |

| Wireless | CPRI/OBSAI    | 2.4, 3.0, 4.9, 6.14, 9.8, 12, 19.6, 24     |

| Other    | Fiber Channel | FC32 (28.05G), FC20, FC16, FC10            |

| Other    | Aurora        | Up to 28.05G                               |

| Divider | Virtex-7HT GTZ |

|---------|----------------|

| Dividei | LC             |

| /1      | 19.6-28.05     |

| /2      | 9.8-14.025     |

| /4      | 4.9 - 7.0      |

| /8      | 2.4 - 3.5      |

## **Artix-7 FPGA Family Table**

Optimized for Lowest Cost and Lowest Power Application (1.0V, 0.9V)

|                                         |                  |                                      | and the same of |          |                        |                     |                     |                    |                  |              |                                      |                                       |

|-----------------------------------------|------------------|--------------------------------------|-----------------|----------|------------------------|---------------------|---------------------|--------------------|------------------|--------------|--------------------------------------|---------------------------------------|

|                                         |                  |                                      |                 |          | SL FPGAs               |                     |                     |                    | LT FPGAs<br>ance |              | Artix-7                              | T FPGAs                               |

|                                         |                  | Part Number                          | XC7A208L        | XC7A358L | XC7A508L               | XC7A758L            | XC7A208LT           | XC7A358LT          | XC7A508LT        | XC7A758LT    | XC7A100T                             | XC7A200T                              |

|                                         |                  | Slices                               | 2,500           | 5,142    | 8,200                  | 11,194              | 2,500               | 5,142              | 8,200            | 11,194       | 15,850                               | 33,650                                |

| Logic Resources                         | (6)              | Logic Cells                          | 16,000          | 32,909   | 52,480                 | 71,642              | 16,000              | 32,909             | 52,480           | 71,642       | 101,440                              | 215,360                               |

|                                         |                  | CLB Filp-Flops                       | 20,000          | 41,135   | 65,600                 | 89,552              | 20,000              | 41,136             | 65,600           | 89,552       | 126,800                              | 269,200                               |

| 0000                                    |                  | Maximum Distributed RAM (Kbits)      | 208             | 453      | 688                    | 974                 | 208                 | 453                | 688              | 974          | 1,188                                | 2,888                                 |

| Memory<br>Resources                     |                  | Block RAM/FIFO w/ ECC (36Kb/ts each) | 30              | 65       | 95                     | 125                 | 30                  | 65                 | 95               | 125          | 135                                  | 365                                   |

| ((((((((((((((((((((((((((((((((((((((( |                  | Total Block RAM (Kbits)              | 1,080           | 2,340    | 3,420                  | 4,500               | 1,080               | 2,340              | 3,420            | 4,500        | 4,860                                | 13,140                                |

| Clock Resources                         |                  | CMTs (1 MMCM + 1 PLL)                | 3               | 3        | 4                      | 4                   | 3                   | 3                  | 4                | 4            | 6                                    | 10                                    |

| I/O Resources                           | (6)              | Maximum Single-Ended I/O             | 216             | 216      | 300                    | 300                 | 216                 | 216                | 300              | 300          | 300                                  | 500                                   |

| IO Resources                            |                  | Maximum Differential I/O Pairs       | 54              | 54       | 72                     | 72                  | 54                  | 54                 | 72               | 72           | 144                                  | 240                                   |

|                                         |                  | DSP48E1 Sices                        | 60              | 120      | 180                    | 240                 | 60                  | 120                | 180              | 240          | 240                                  | 740                                   |

| Embedded<br>Hard IP<br>Resources        |                  | PCI Express® <sup>(1)</sup>          | _               | _        | _                      | _                   | 1                   | 1                  | 1                | 1            | 1                                    | 1                                     |

|                                         |                  | Agile Mixed Signal (AMS) / XADC      | 1               | 1        | 1                      | -1                  | 1                   | - 3                | 1                | 1            | 1                                    | 1                                     |

|                                         |                  | Configuration AES / HMAC Blocks      | 1               | 1        | 1                      | 1                   | 1                   | 1                  | 1                | 1            | 1                                    | 1                                     |

|                                         |                  | GTP Transceivers (6.6 Gb/s Max Rate) | -               | -        | _                      | <del></del>         | 4                   | 4                  | 8                | 8            | 8                                    | 16                                    |

|                                         |                  | Commercial                           | -1, -2          | -1, -2   | -1, -2                 | -1, -2              | -1, -2              | -1,-2              | -1, -2           | -1, -2       | -1, -2                               | -1, -2                                |

| Speed Grades                            |                  | Extended                             | -2L, -3         | -2L, -3  | -2L, -3                | -2L, -3             | -2L, -3             | -2L, -3            | -2L, -3          | -2L, -3      | -2L, -3                              | -2L, -3                               |

|                                         |                  | Industrial                           | -1, -2          | -1, -2   | -1, -2                 | -1, -2              | -1, -2              | -1, -2             | -1, -2           | -1, -2       | -1, -2                               | -1, -2                                |

|                                         | Package (2), (3) | Dimensions (mm)                      |                 | Avalab   | le User I/O: 3.3V Sele | cti/O™ HR I/O, 3.3V | Belecti/O™ HD I/O P | ins (GTP Transcelv | ers)             |              | Available User I/O: 3.3V<br>(GTP Tra | / Selecti/O™ HR I/O PI<br>enscelvers) |

|                                         | CPG236           | 10 x 10                              | 48, 52          | 48, 52   |                        |                     |                     |                    |                  |              |                                      |                                       |

|                                         | C8G325           | 15 x 15                              | 108, 108        | 108, 108 |                        |                     | l. l                |                    |                  |              |                                      |                                       |

|                                         | C8G484           | 19 x 19                              |                 |          | 144, 156               | 144, 156            |                     |                    |                  |              | 12                                   |                                       |

|                                         | CPG237           | 10 x 10                              |                 |          |                        |                     | 48, 52 (1)          | 48, 52 (1)         |                  |              |                                      |                                       |

|                                         | C8G326           | 15 x 15                              |                 |          |                        |                     | 108, 77 (4)         | 108, 77 (4)        | 108, 77 (4)      | 108, 77 (4)  |                                      |                                       |

|                                         | C8G485           | 19 x 19                              |                 |          |                        |                     | 108, 108 (4)        | 108, 108 (4)       | 126, 108 (6)     | 126, 108 (6) |                                      |                                       |

|                                         | FGG677           | 27 x 27                              |                 |          |                        |                     |                     |                    | 144, 156 (8)     | 144, 156 (8) |                                      |                                       |

| Ī                                       | C8G324           | 15 x 15                              |                 |          |                        |                     |                     |                    |                  |              | 210 (0)                              |                                       |

|                                         | FTG256           | 17 x 17                              |                 |          |                        |                     |                     |                    |                  |              | 170 (0)                              |                                       |

|                                         | 8BG484           | 19 x 19                              |                 |          |                        |                     |                     |                    |                  |              |                                      | 285 (4)                               |

| Footprint                               | FGG484           | 23 x 23                              |                 |          |                        |                     |                     |                    |                  |              | 285 (4)                              |                                       |

| Compatible                              | FBG484           | 23 x 23                              |                 |          |                        |                     |                     |                    |                  |              |                                      | 285 (4)                               |

| Footprint                               | FGG676           | 27 x 27                              |                 |          |                        |                     |                     |                    |                  |              | 300 (8)                              |                                       |

| Compatible                              | FBG676           | 27 x 27                              |                 |          |                        |                     |                     |                    |                  |              |                                      | 422.41                                |

|                                         | FFG1156          | 35 x 35                              |                 |          |                        |                     |                     |                    |                  |              |                                      | 00 (16)                               |

CPG: 0.5mm Wire-bond chip-scale: C8G: 0.8mm Wire-bond chip-scale: FTG: 1.0mm Wire-bond fine-pitch: 8BG: 0.8mm Wire-bond fine-pitch: FBG: 1.0mm Wire-bond fine-pitch:

Notes: 1. Supports PCI Express Base 2.1 specification at Gen1 and Gen2 data rates.

2. Leaded package option available for all packages.

Up to 16 Transceivers @ 6.6G

<sup>3.</sup> Device migration is available within the Artix-7 family for like packages but is not supported between other 7 series families.

### **Kintex-7 FPGA Family Table**

|            |                                         |                                                                                       | C                               | (Intex-7 FPGAs<br>Optimized for Best P<br>1.0V, 0.9V) | Price-Performance |                          |                                            |                         |             |           |

|------------|-----------------------------------------|---------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------|-------------------|--------------------------|--------------------------------------------|-------------------------|-------------|-----------|

|            |                                         |                                                                                       | Part Number                     | XC7K70T                                               | XC7K160T          | XC7K325T                 | XC7K356T                                   | XC7K410T                | XC7K420T    | XC7K480   |

|            |                                         |                                                                                       | Sices <sup>(1)</sup>            | 10,250                                                | 25,350            | 50,950                   | 55,680                                     | 63,550                  | 65,150      | 74,850    |

|            | Logic Resources                         |                                                                                       | Logic Cells                     | 65,600                                                | 162,240           | 328,080                  | 358,160                                    | 408,720                 | 416,960     | 477,760   |

|            |                                         |                                                                                       | CLB Flip-Flope                  | 82,000                                                | 202,800           | 407,600                  | 445,200                                    | 508,400                 | 521,200     | 597,200   |

|            | 700000                                  | Maximum                                                                               | Distributed RAM (Kbits)         | 838                                                   | 1,938             | 4,000                    | 4,938                                      | 5,663                   | 5,763       | 6,588     |

|            | Memory<br>Resources                     | Block RAMFIFO                                                                         | O w/ ECC (36Kbits each)         | 135                                                   | 325               | 445                      | 715                                        | 795                     | 835         | 955       |

|            | 100000000000000000000000000000000000000 |                                                                                       | Total Block RAM (Kbits)         | 4,880                                                 | 11,700            | 16,020                   | 25,740                                     | 28,620                  | 30,060      | 34,380    |

|            | Clock Resources                         | CMTs (1 MMCM + 1 PLI                                                                  |                                 | 6                                                     | 8                 | 10                       | 6                                          | 10                      | 7           | 8         |

|            | 10.0                                    | Maximum Single-Ended I/O <sup>(2)</sup> Maximum Differential I/O Pains <sup>(2)</sup> |                                 | 300                                                   | 400               | 500                      | 300                                        | 500                     | 350         | 400       |

|            | I/O Resources                           |                                                                                       |                                 | 144                                                   | 192               | 240                      | 144                                        | 240                     | 168         | 192       |

|            |                                         |                                                                                       | DSP48E1 Slices                  | 240                                                   | 600               | 840                      | 1,440                                      | 1,540                   | 1,680       | 1,920     |

|            | Embedded                                | PCI Express Interface Blocks <sup>(1)</sup>                                           |                                 | 1                                                     | 1                 | 1                        | 1                                          | 1                       | 1           | 1         |

|            | Hard IP                                 | Agile Mix                                                                             | Agile Mixed Signal (AMS) / XADC |                                                       | 1                 | 1                        | 1                                          | 1                       | 1           | 1         |

|            | Resources                               | Configure                                                                             | Configuration AES / HMAC Blocks |                                                       | 1                 | 1                        | 1                                          | 1                       | 1           | 1         |

|            |                                         | GTX 12.5 Gb/s Transceivers                                                            |                                 | 8                                                     | 8                 | 16                       | 24                                         | 18                      | 28          | 32        |

|            |                                         | 100                                                                                   | Commercial                      | -1, -2                                                | -1, -2            | -1, -2                   | -1, -2                                     | -1, -2                  | -1, -2      | -1, -2    |

|            | Speed Grades                            |                                                                                       | Extended                        | -21., -3                                              | -21., -3          | -21.,-3                  | -21.,-3                                    | -2L, -3                 | -21.,-3     | -21, -3   |

|            |                                         |                                                                                       | Industrial                      | -1, -2                                                | -1,-2             | -1, -2                   | -1, -2                                     | -1, -2                  | -1, -2      | -1, -2    |

|            | Configuration                           | Confi                                                                                 | guration Memory (Mbits)         | 23.2                                                  | 45.1              | 88.2                     | 105.1                                      | 122.0                   | 122.6       | 140.1     |

|            | <b>A</b>                                | Package                                                                               | Area                            |                                                       |                   | Available User I/O: 3.3V | SelectiO <sup>TM</sup> Pins, 1.8V SelectiC | Pine (GTX Transceivers) |             |           |

|            |                                         | Lidless flip chip BGA                                                                 | supporting 6.6 Gb/s serial      | line rates (1.0mm half spac                           | ing)              |                          |                                            |                         |             |           |

| 00         | 11.                                     | FBG484 <sup>(4)</sup>                                                                 | 23 x 23 mm                      | 185, 100 (4)                                          | 185, 100 (4)      |                          |                                            |                         |             |           |

| 6 <b>G</b> |                                         | FBG876 <sup>(4)</sup>                                                                 | 27 x 27 mm                      | 200, 103, (8)                                         | 250, 150 (8)      | 250, 150 (8)             |                                            | 250, 150 (8)            |             |           |

|            | _                                       | FBG900 <sup>(4)</sup>                                                                 | 31 x 31 mm                      |                                                       |                   | 350, 150 (16)            |                                            | 350, 150 (16)           |             |           |

|            | 8                                       | Flip chip BGA suppor                                                                  | rting 12.5 Gb/s serial line ra  | tes (1.0mm ball spacing)                              |                   |                          |                                            |                         |             |           |

| 5 <b>G</b> |                                         | FFG876 <sup>(4)</sup>                                                                 | 27 x 27 mm                      |                                                       | 250, 150 (8)      | 250, 150 (8)             |                                            | 250, 150 (8)            |             |           |

| JG         |                                         | FFG900 <sup>(K)</sup>                                                                 | 31 x 31 mm                      |                                                       |                   | 350, 150 (16)            | N.                                         | 350, 150 (18)           |             |           |

|            |                                         | FFG901 <sup>(4)</sup>                                                                 | 31 x 31 mm                      |                                                       |                   |                          | 300, 0 (24)                                |                         | 350, 0 (28) | 380, 0    |

|            | <b>V</b>                                | FFG1158 <sup>(6)</sup>                                                                | 35 x 35 mm                      |                                                       |                   |                          |                                            |                         | 350, 0 (28) | 400 0 (30 |

Notes: 1. A single Kintex-7 FPGA CLB comprises two slices, with each containing four 6-input LUTs and eight Flip-Flops, for a total of eight 6-LUTs and 16 Flip-Flops per CLB.

From 4 to 32 GTX Transceivers @ up to 12.5G

<sup>2.</sup> Refer to data sheet for details on I/O standards support.

<sup>3.</sup> Hard block supports PCI Express Base 2.1 specification at Gen1 and Gen2 data rates. Gen3 supported with soft IP.

<sup>4.</sup> Leaded package options ("FBxxx" or "FFxxx") available for the following Kintex-7 devices: XC7K160T, XC7K325T, XC7K355T, XC7K410T, XC7K420T, XC7K480T

<sup>5.</sup> Preliminary product information, subject to change. Please contact your Xilinx representative for the latest information.

|                          | rtex                                              |                | (,,                                                                                                            |                                                                                                    | (1.0\/, 0.9\/   |                |                |                |                 |                |                 | (1.0V)                       | NAME OF TAXABLE |

|--------------------------|---------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------|----------------|----------------|----------------|-----------------|----------------|-----------------|------------------------------|-----------------|

| - 1                      |                                                   | Part Number    | XC7V585T                                                                                                       | XC7V2000T                                                                                          | XC7VX330T       | XC7VX415T      | XC7VX485T      | XC7VX550T      | XC7VX690T       | XC7VX980T      |                 | XC7VH580T                    | XC7VH8701       |

|                          | EasyPath™ Cost Reduction Solutions <sup>(1)</sup> |                | XCE7V585T                                                                                                      | XCE7V2000T                                                                                         | XCE7VX330T      | XCE7VX415T     | XCE7VX485T     | XCE7VX550T     | XCE7VX690T      | XCE7VX980T     | XCE7VX1140T     | -                            | -               |

| Logic<br>Resources       | Slices                                            |                |                                                                                                                | 305,400                                                                                            | 51,000          | 64,400         | 75,900         | 86,600         | 108,300         | 153,000        | 178,000         | 90,700                       | 136,900         |

|                          | Logic Cells<br>CLB Flip-Floos                     |                | San Printer Street, St | 1,954,560                                                                                          | 326,400         | 412,160        | 485,760        | 554,240        | 693,120         | 979,200        | 1,139,200       | 580,480                      | 876,160         |

|                          |                                                   |                | 728,400                                                                                                        | 2,443,200                                                                                          | 408,000         | 515,200        | 607,200        | 692,800        | 866,400         | 1,224,000      | 1,424,000       | 725,600                      | 1,095,200       |

| Memory<br>Resources      | Maximum Distributed RAM (Kb)                      |                | 6,938                                                                                                          | 21,550                                                                                             | 4,388           | 6,525          | 8,175          | 8,725          | 10,888          | 13,838         | 17,700          | 8,850                        | 13,275          |

|                          | Block RAM/FIFO w/ ECC (36 Kb each)                |                | 795                                                                                                            | 1,292                                                                                              | 750             | 880            | 1,030          | 1,180          | 1,470           | 1,500          | 1,880           | 940                          | 1,410           |

|                          | Total Block RAM (Kb)                              |                | 28,620                                                                                                         | 46,512                                                                                             | 27,000          | 31,680         | 37,080         | 42,480         | 52,920          | 54,000         | 67,680          | 33,840                       | 50,760          |

| Clocking                 | CMTs (1 MMCM + 1 PLL)                             |                | 18                                                                                                             | 24                                                                                                 | 14              | 12             | 14             | 20             | 20              | 18             | 24              | 12                           | 18              |

| I/O Resources            | Maximum Single-Ended I/O                          |                | 850                                                                                                            | 1,200                                                                                              | 700             | 600            | 700            | 600            | 1,000           | 900            | 1,100           | 600                          | 650             |

|                          | Maximum Differential I/O Pairs                    |                | 408                                                                                                            | 576                                                                                                | 336             | 288            | 336            | 288            | 480             | 432            | 528             | 288                          | 312             |

| Embedded IP<br>Resources | DSP48E1 Silces                                    |                | 1,260                                                                                                          | 2,160                                                                                              | 1,120           | 2,160          | 2,800          | 2,880          | 3,600           | 3,600          | 3,360           | 1,680                        | 2,520           |

|                          | PCI Express Gen2                                  |                | 3                                                                                                              | 4                                                                                                  | _               | _              | 4              | _              | _               | _              | _               | _                            | _               |

|                          | PCI Express Gen3                                  |                | _                                                                                                              | _                                                                                                  | 2               | 2              | _              | 2              | 3               | 3              | 4               | 2                            | 3               |

|                          | Aglie Mixed Signal (AMS) / XADO                   |                | 1                                                                                                              | 1                                                                                                  | 1               | 1              | 1              | 1              | 1               | 1              | 1               | 1                            | 1               |

|                          | Configuration AES / HMAC Blocks                   |                | 1                                                                                                              | 1                                                                                                  | 1               | 1              | 1              | 1              | 1               | 1              | 1               | 1                            | 1               |

|                          | GTX 12.5 Gb/s Transcelvers <sup>(2)</sup>         |                | 36                                                                                                             | 36                                                                                                 | _               | _              | 56             | _              | _               | _              | _               | _                            | _               |

|                          | GTH 13.1 Gb/s Transcelvers <sup>(3)</sup>         |                | _                                                                                                              | _                                                                                                  | 28              | 48             | _              | 80             | 80              | 72             | 96              | 48                           | 72              |

|                          | GTZ 28.05 Gb/s Transcelvers                       |                | _                                                                                                              | _                                                                                                  | _               | _              | _              | _              | _               | _              | _               | 8                            | 16              |

|                          | Commercial                                        |                | -12                                                                                                            | -1, -2                                                                                             | -1, -2          | -1, -2         | -1, -2         | -1, -2         | -1, -2          | -12            | -12             | -1, -2                       | -1, -2          |

| Speed Grades             | Extended <sup>(4)</sup>                           |                | -2L3                                                                                                           | -2L, -2G                                                                                           | -2L3            | -2L3           | -2L3           | -2L, -3        | -2L, -3         | -2L            | -2L, -2G        | -2L -2G                      | -2L, -2G        |

|                          | Industrial                                        |                | -1, -2                                                                                                         | -1                                                                                                 | -12             | -12            | -12            | -12            | -12             | -1             | -1              |                              | _               |

|                          | Package <sup>(5)</sup> Area                       |                |                                                                                                                | Available User I/O: 3.3V Selecti/O <sup>TM</sup> Pins, 1.8V Selecti/O Pins (GTX, GTH Transcelvers) |                 |                |                |                |                 |                |                 | 1.8V SelectiO Pins (GTH, GTZ |                 |

|                          | Flip chip, fine pitch BGA (1.0 mm ball spacing)   |                | Available open inc. 0.00 delection Pills, 1.00 delection Pills (GTA, GTT Hallacevers)                          |                                                                                                    |                 |                |                |                |                 |                |                 |                              |                 |

|                          | FFG1157                                           | 35 x 35 mm     | 0, 600 (20, 0)                                                                                                 |                                                                                                    | n enn/n 20\     | 0, 600 (0, 20) | 0, 600 (20, 0) |                | 0, 600 (0, 20)  |                |                 |                              |                 |

| Footprint<br>Compatible  | FFG1761                                           | 42.5 x 42.5 mm | 100, 750 (36, 0)                                                                                               |                                                                                                    | 50, 650 (0, 28) | 0,000 (0,20)   | 0,700 (28, 0)  |                | 0, 850 (0, 36)  |                |                 |                              |                 |

|                          |                                                   |                | 100, 750 (56, 0)                                                                                               |                                                                                                    | 30, 630 (0, 26) |                | 0, 700 (20, 0) |                | u, asu (u, so)  |                |                 |                              |                 |

|                          | FHG1761                                           | 45 x 45 mm     |                                                                                                                | 0, 857 (36, 0)                                                                                     |                 |                |                |                |                 |                |                 |                              |                 |

|                          | FLG1925                                           | 45 x 45 mm     |                                                                                                                | 0, 12 0 (16, 0)                                                                                    |                 |                |                |                |                 |                |                 |                              |                 |

|                          | FFG1158                                           | 35 x 35 mm     |                                                                                                                |                                                                                                    |                 | 0, 350 (0, 48) | 0, 350 (48, 0) | 0, 350 (0, 48) |                 |                |                 |                              |                 |

| Footprint<br>Compatible  | FFG1926                                           | 45 x 45 mm     |                                                                                                                |                                                                                                    |                 |                |                |                | 0, 720 (0, 64)  | 0, 720 (0, 64) |                 |                              |                 |

|                          | FLG1926                                           | 45 x 45 mm     |                                                                                                                |                                                                                                    |                 |                |                | - 6            |                 |                | 0, 720 (0, 64)  |                              |                 |

|                          | FFG1927                                           | 45 x 45 mm     |                                                                                                                |                                                                                                    |                 | 0, 600 (0, 48) | 0, 600 (56, 0) | 0, 600 (0, 80) | 0, 600 (0, 80)  |                |                 |                              |                 |

| Footprint<br>Compatible  | FFG1928                                           | 45 x 45 mm     |                                                                                                                |                                                                                                    |                 |                |                |                |                 | 0, 480 (0, 72) |                 |                              |                 |

|                          | FLG1928                                           | 45 x 45 mm     |                                                                                                                |                                                                                                    |                 |                |                |                |                 |                | 0, 480 (0, 96)  |                              |                 |

| Footprint<br>Compatible  | FFG1930                                           | 45 x 45 mm     |                                                                                                                |                                                                                                    |                 |                | 0, 700 (24, 0) |                | 0, 1000 (0, 24) | 0, 900 (0, 24) |                 |                              |                 |

|                          | FLG1930                                           | 45 x 45 mm     |                                                                                                                |                                                                                                    |                 |                |                |                |                 |                | 0, 1100 (0, 24) |                              |                 |

|                          | Ceramic flip chip, fine pitch BGA (1.0 mm ball s  |                | spacing)                                                                                                       |                                                                                                    |                 |                |                |                |                 |                |                 |                              |                 |

|                          | HCG1155                                           | 35 x 35 mm     |                                                                                                                |                                                                                                    |                 |                |                |                |                 |                |                 | 400 (24, 8)                  |                 |

|                          | HCG1931                                           | 45 x 45 mm     |                                                                                                                |                                                                                                    |                 |                |                |                |                 |                |                 | 600 (48, 8)                  | 650 (42, 8)     |

|                          | HCG1932                                           | 45 x 45 mm     |                                                                                                                |                                                                                                    |                 |                |                |                |                 |                |                 | 300 (48, 8)                  | 300 ( 2, 16     |

Virtey 7 FDCAe

<sup>2. 12.5</sup> Gb/s support in "-3E", "-2GE" speed/temperature grade; 10.3125 Gb/s support in "2C", "-2LE", and "-2I" speed grade.