# Sampling and Processing Real-World Data with 7 Series FPGAs

Follow @avnetX-fest Tweet this event: #avtX-fest

www.facebook.com/X-fest2012

#### **FPGAs offer unmatched system performance and flexibility**

- Explore complexities in analog signal chain components and learn how digitally controlled Analog Front Ends (AFE) increase design flexibility

- Learn how to maximize low and medium performance standalone data converters

- Understand capabilities and benefits of XADC component

- Accelerate your prototype with Pmods<sup>™</sup> and FMC evaluation boards

- Analog signal chain

- Standalone data converter solutions

- XADC solution and the customizable analog interface

- Prototyping with expansion boards

- Analog signal chain

- Standalone data converter solutions

- XADC solution and the customizable analog interface

- Prototyping with expansion boards

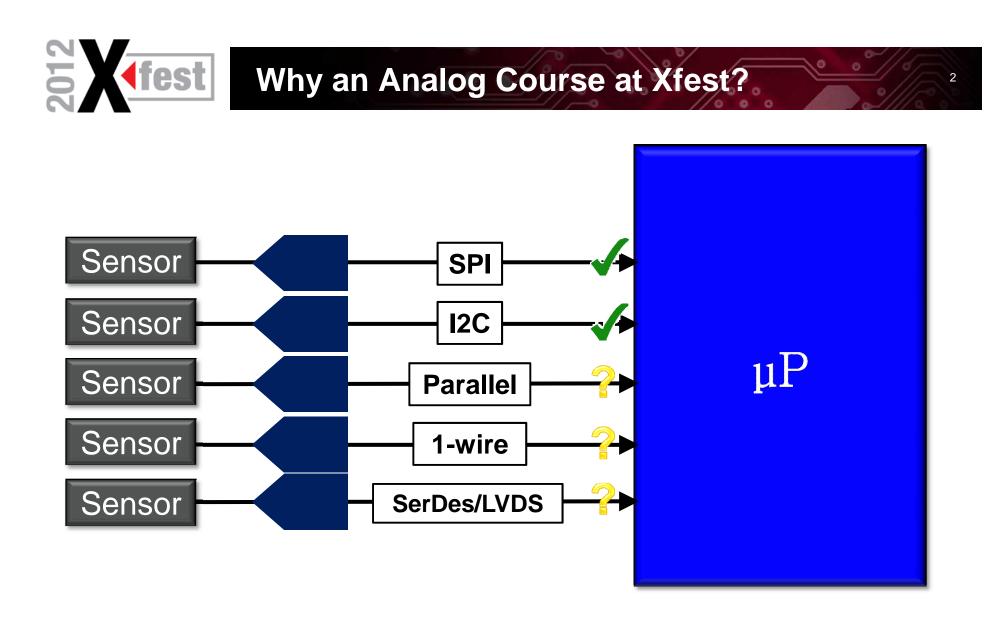

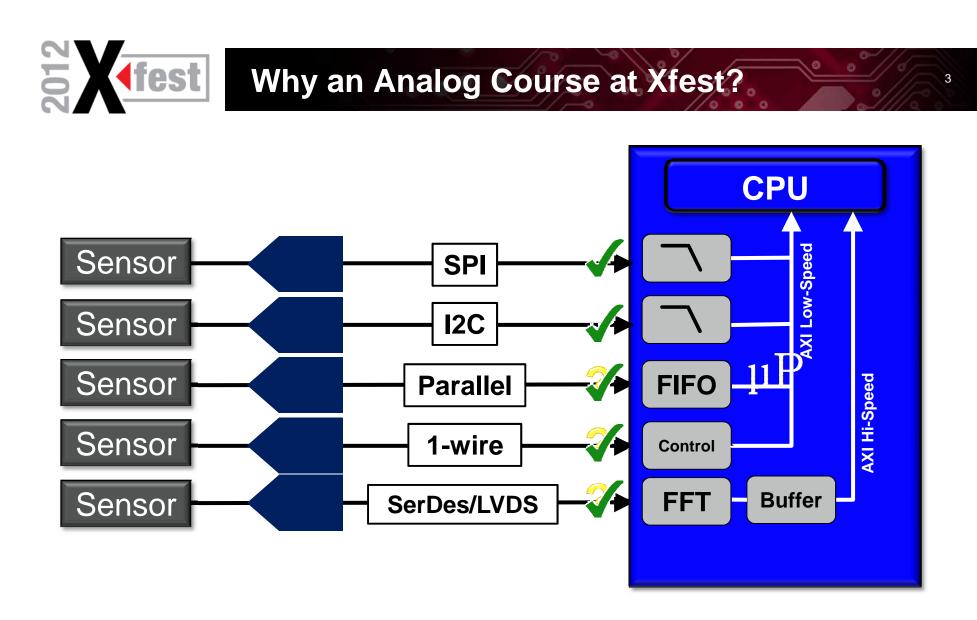

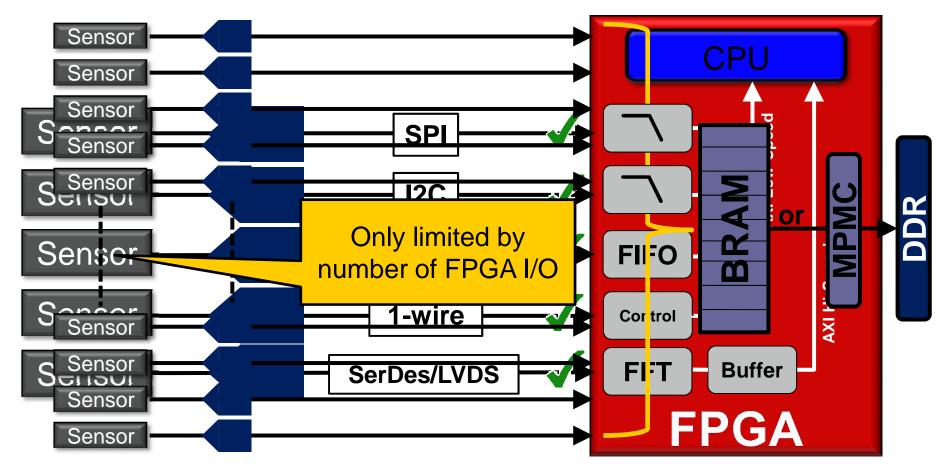

- Demand for sensor critical applications is increasing

- Often measuring such things as temperature, weight, shock/vibration, air quality and more

- System designers must design optimal signal path solution for varying sensor types

- Sensor types require optimal analog signal chains

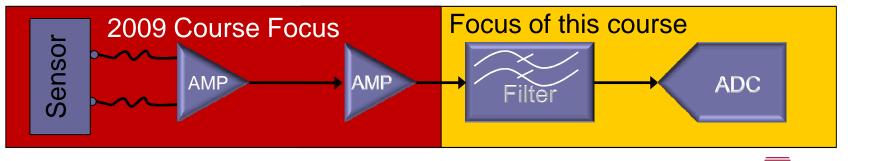

- Covered in 2009 X-fest Analog Course

Sensors require optimal analog interfaces

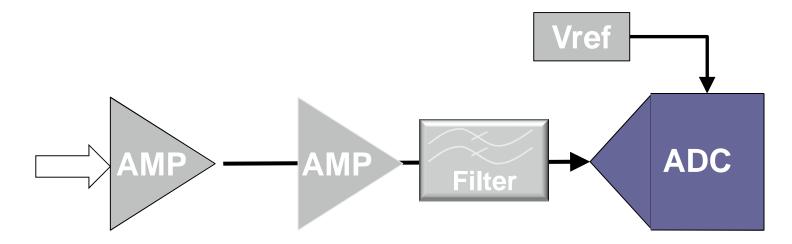

- To achieve maximum ADC performance you must carefully build the analog signal chain!

- For example, inputs to SAR ADC's look like dynamic loads, thus amplifier selection is critical

- It's important to select the right

- Input amplifier or buffer

- Voltage (or current) reference

- Voltage reference buffer (for multiple ADC systems)

# **ADC Amplifiers**

- Consult reference material from supplier

- ADC's datasheet

- ADC's website

- Evaluation board docs

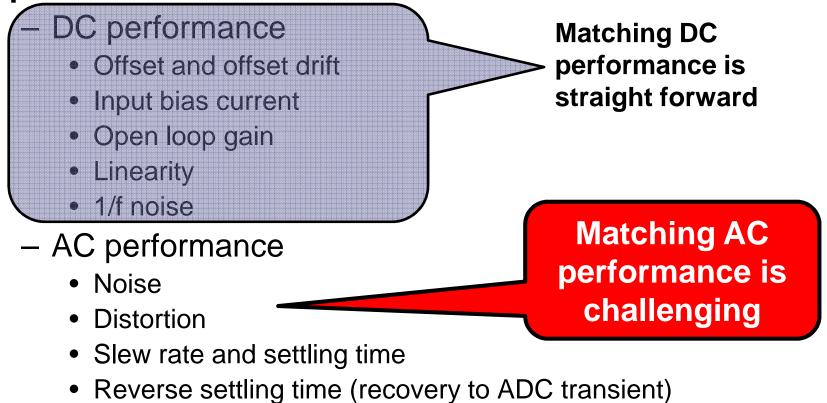

# Look at the published AC specs for alternatives

- Slew rate

- Forward settling time

- Reverse settling time

- Look at output resistance

Pick an op amp that does not degrade the ADC performance

AC performance must be known for the exact circuit configuration used in the ADC driver circuit

- Too many possibilities to include in a datasheet

- Datasheets provide a very good start for selecting candidates

- Ultimately the op-amp circuit must be prototyped to measure AC performance

#### Evaluation boards provide an easy way to do this

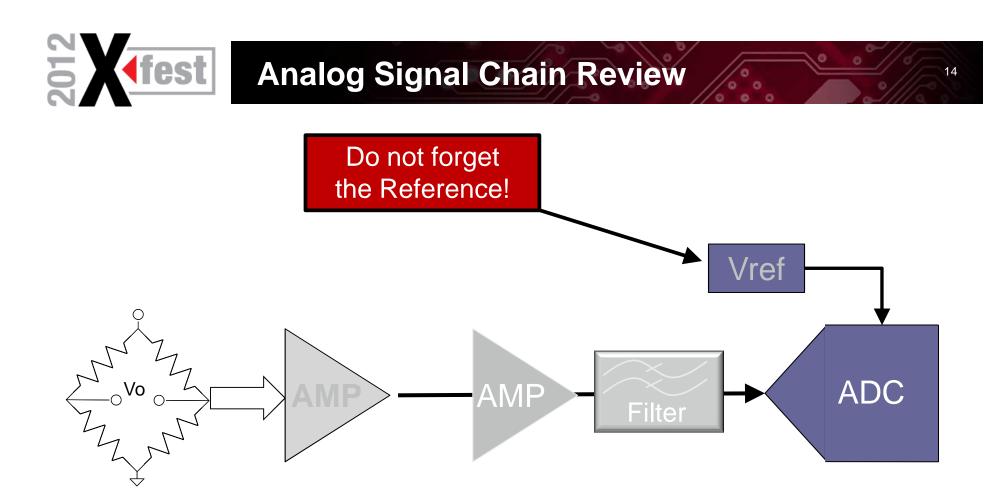

# A clean voltage reference is critical as well

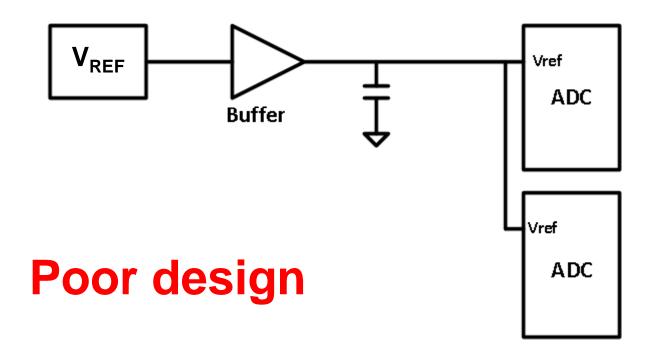

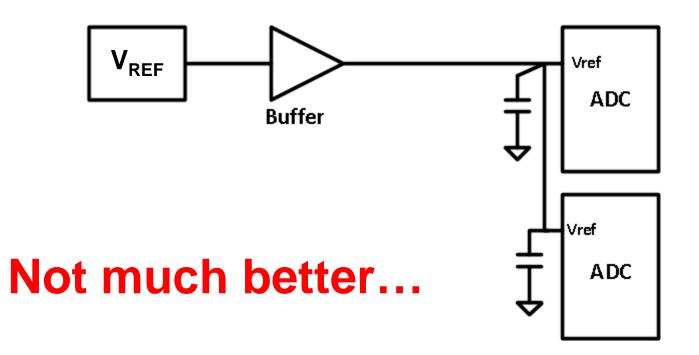

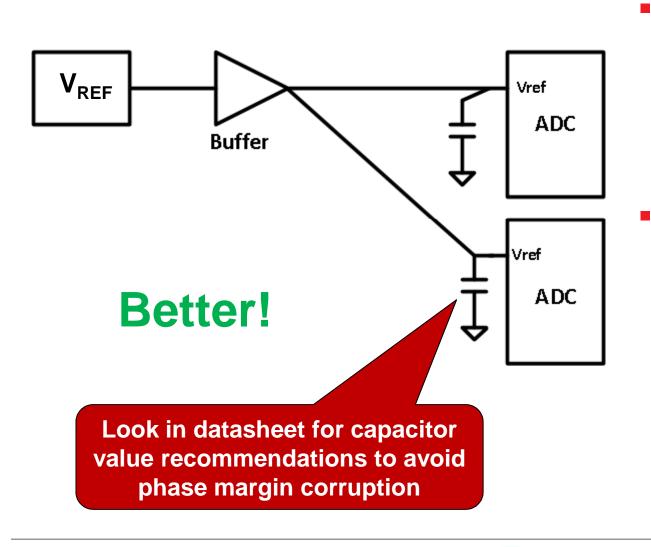

When referencing multiple ADC's, what's the best method?

## **Referencing Multiple ADCs**

One reference capacitor is required at each ADC

17

Use a star configuration to prevent crosstalk between ADCs

AVNET"

- Most suppliers provide analog simulation tools that evaluate the circuitry

- Simulations are only as good as the models and input stimulus

- There's no substitute for testing under the exact operating conditions

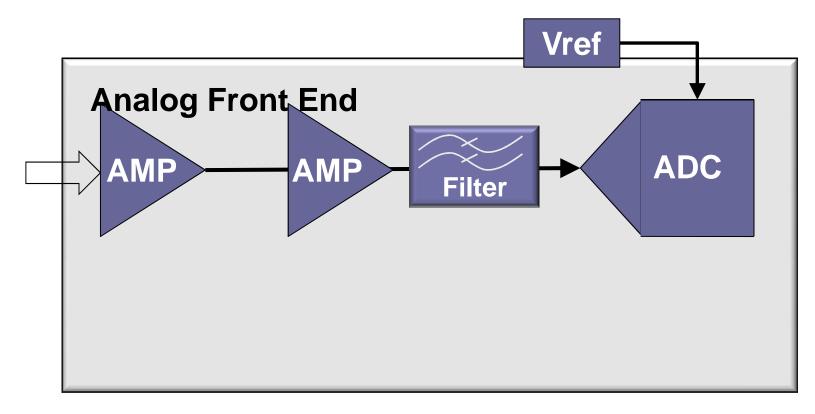

## Why not integrate all of this into a single IC?

# What is an Analog Front End?

- What's next?

- How about combining it all into a single IC?

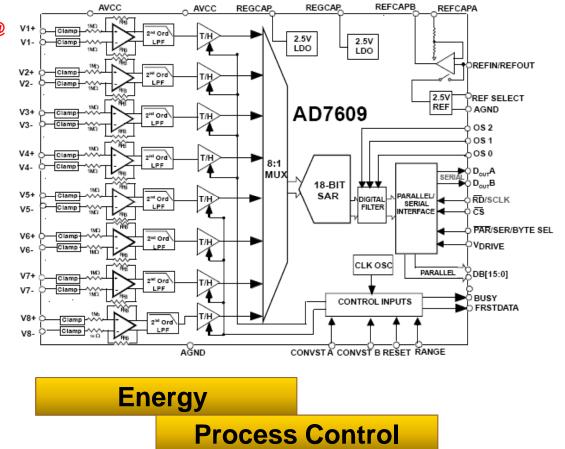

#### ADI AD7609 : 18 Bit, 8-Channel ADC

#### **Building Block for High Dynamic Range Applications**

#### Features

- 8 channels simultaneous sampling @ 200KSPS

- Single 5V supply operation

- Differential Analog Inputs +/-20V & +/-10V

- Analog Inputs can withstand 7KV HBM ESD

- +/-16.5V Analog input clamp protection

- 1Meg Resistor input impedance

- 2nd Order Analog Anti-Alias Filter

- Backend Digital filter

- 2.5V reference and reference buffer

- SPI and Parallel interface

#### Performance

- 18 Bits No Missing Codes

- INL +/- 2.5LSB (Typ)

- 91 dB SNR @ 200k

- 105 dB DR @3.125ksps (digital filter on, OSR = 64)

- 105mW Power (Typ)

- NFS/PFS Code 0.1% FSR over Temperature

- Analog signal chain

- Standalone data converter solutions

- XADC solution and the customizable analog interface

- Prototyping with expansion boards

- We've talked about the signal chain...

- How do we choose the ADC?

# **Choosing the Right ADC**

- Resolution

- Bandwidth of interest

- Input

- Input types (Unipolar, Bipolar, +/-10V)

- Channel count

- Mux'ed vs. simultaneous sampling

- Interface

- Size

- Power consumption

- ADC architecture

- Error & dynamic specifications

- Other system considerations

- Internal/External Reference, FIFO, PGA, GPIO

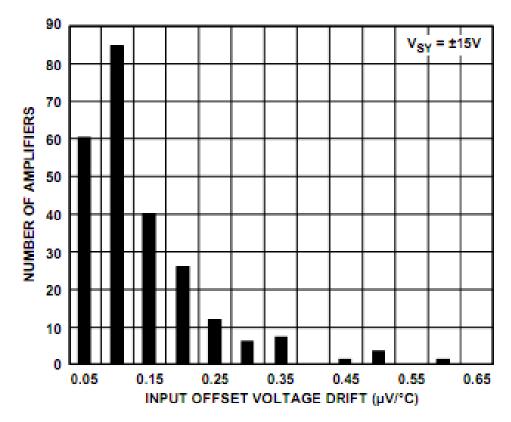

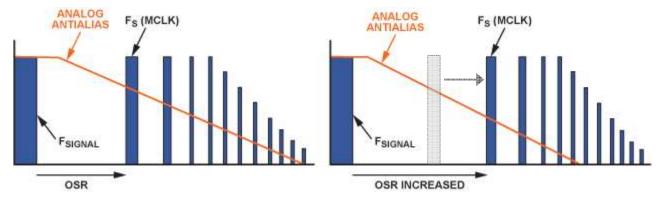

- When evaluating ADC performance it's important to understand errors

- Linearity errors

- Gain errors

- DC offset errors

- Input offset and offset drift

- Input offset can be calibrated out

- Drift cannot

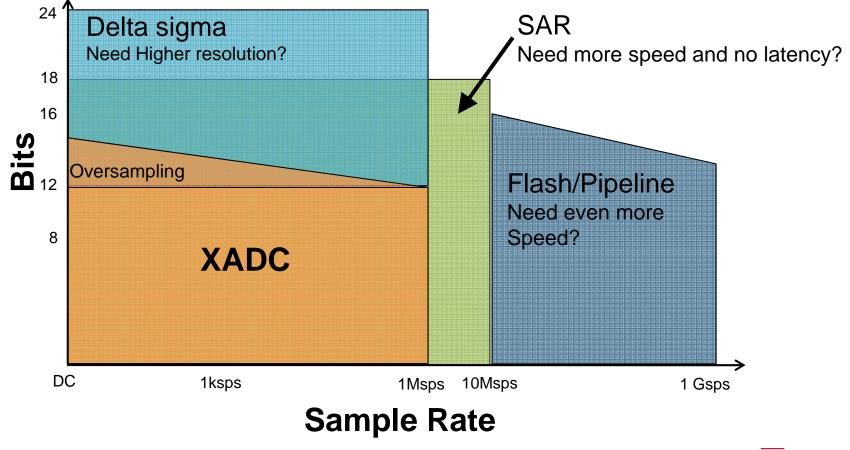

#### Sampling Rate vs. Resolution

#### Analog to Digital Converter Topologies

| Topology    | Typical Resolution | Typical Sample<br>Rate | Details                                                |

|-------------|--------------------|------------------------|--------------------------------------------------------|

| Flash       | < 16 bits          | 100M – 3G              | Fastest Sample Rate<br>Costly, Big, > Power            |

| Pipeline    | 8-16 bits          | 1M – 500M              | High Speed<br>Low Latency                              |

| SAR         | 8-18 bits          | 20K – 10M              | Low Latency<br>Low Power (= SPS)                       |

| Delta Sigma | 12-31 bits         | 15 – 4M                | Excellent Line Rejection<br>Built-in Filtering (OverS) |

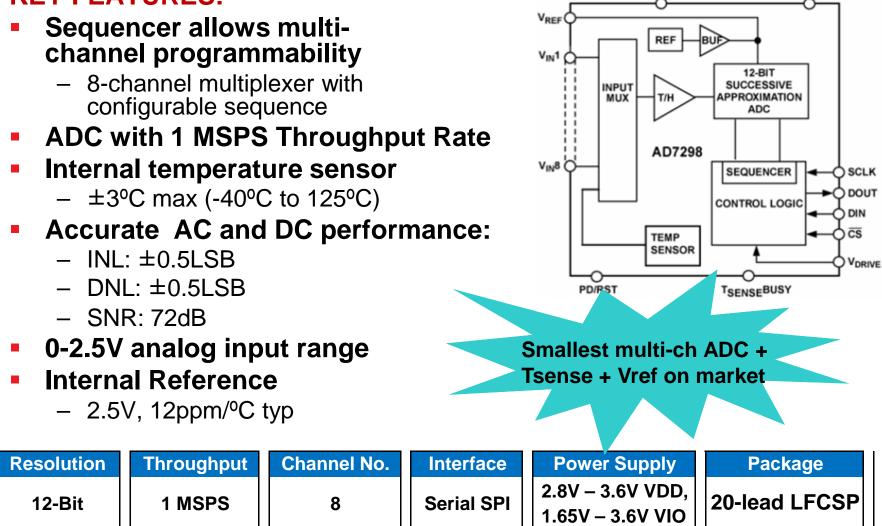

#### Analog Devices AD7298

#### **KEY FEATURES:**

Copyright © 2012. Avnet, Inc. All rights reserved.

26

GND

/DD

#### Analog signal chain

- Standalone data converter solutions

- XADC solution and the customizable analog interface

- Prototyping with expansion boards

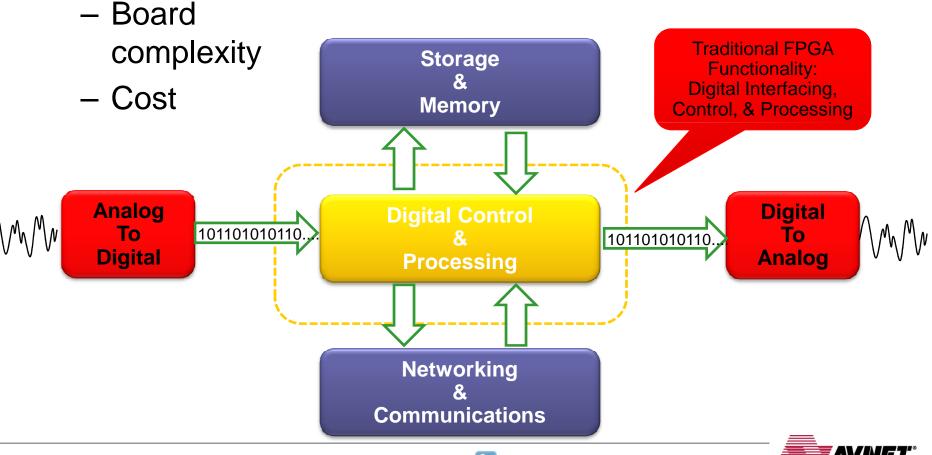

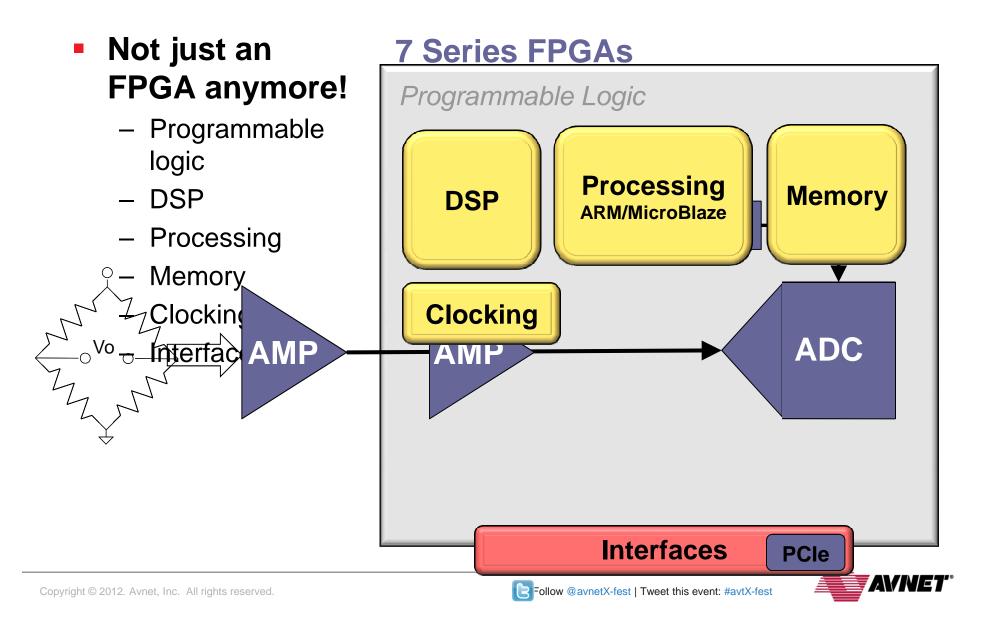

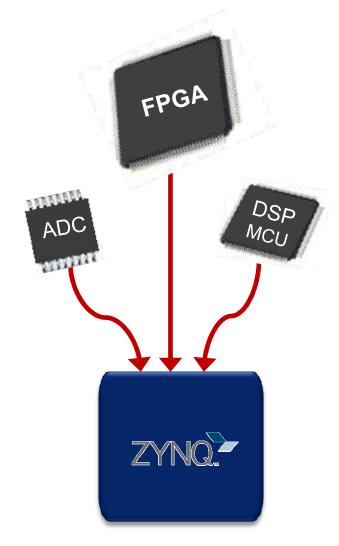

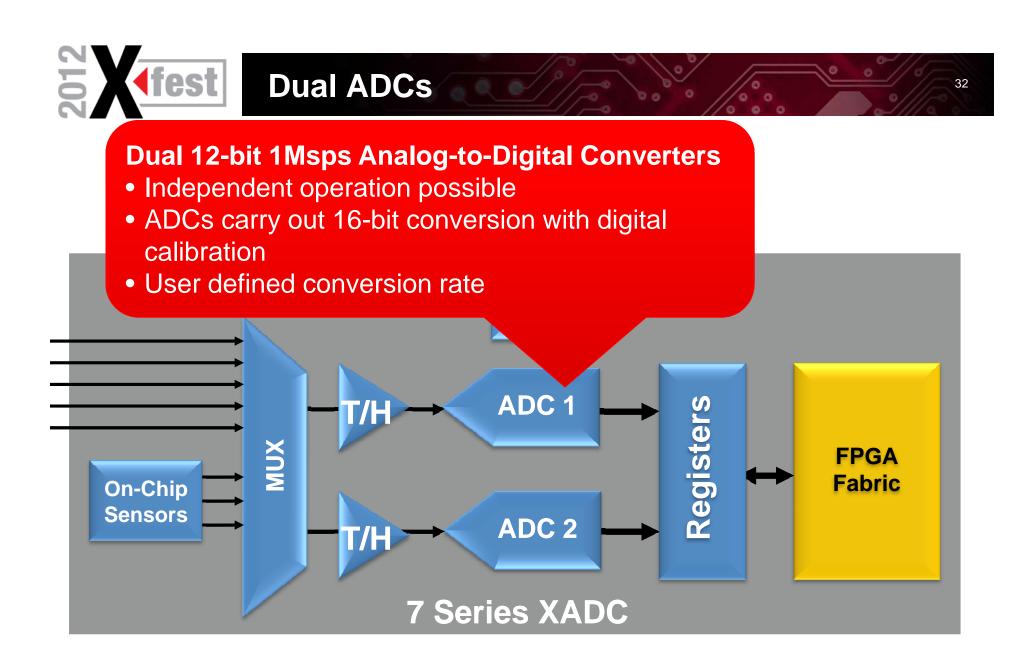

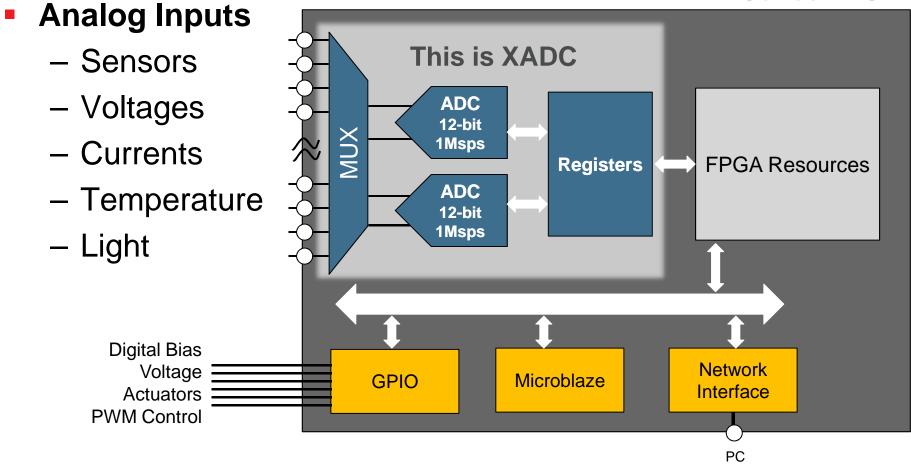

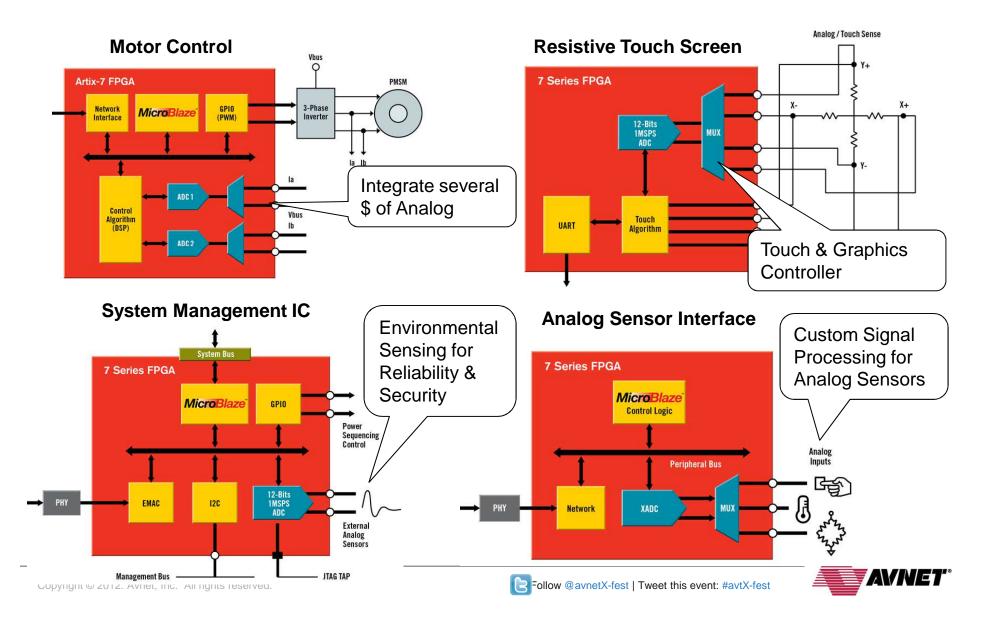

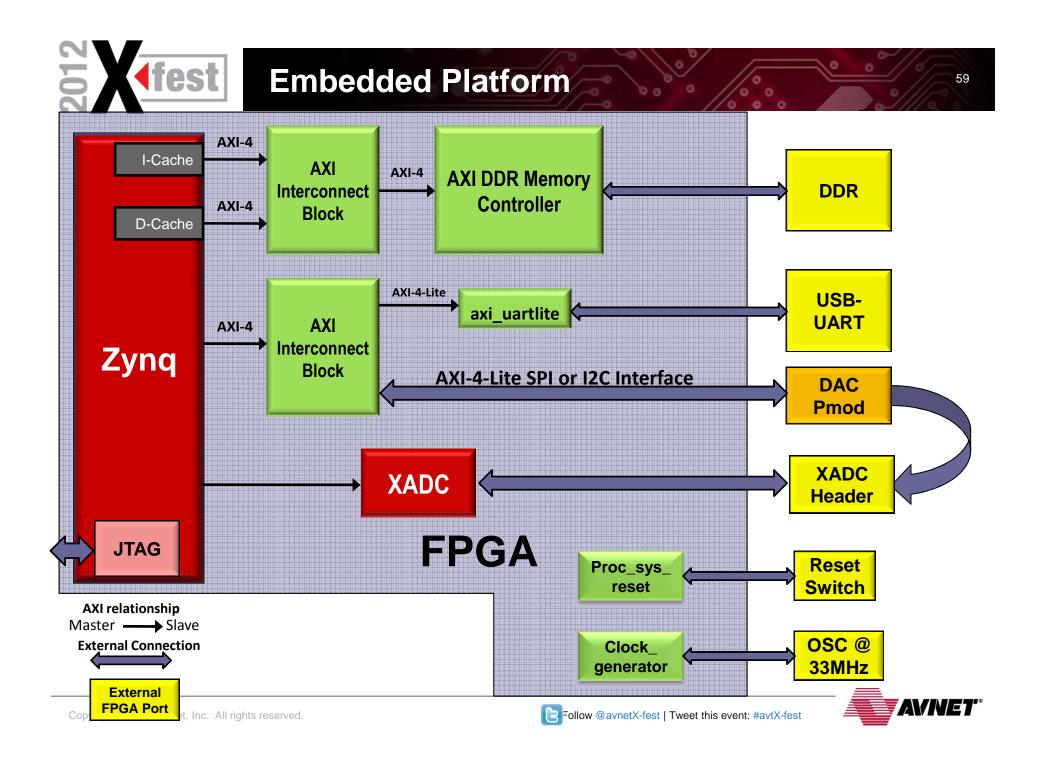

## Integrating an ADC into the FPGA

#### Adding analog to an FPGA reduces

- IC count

#### Introducing the XADC

#### **Benefits of Integration**

- Reduced Cost

- Elimination of discrete analog components and associated board area

- Reduce obsolescence

- Customization of Analog Interface

- Flexible analog interface

- Configure up to 17 analog inputs

- Change ADC timing

- Logic can be used for:

- Calibration

- Signal processing, etc.

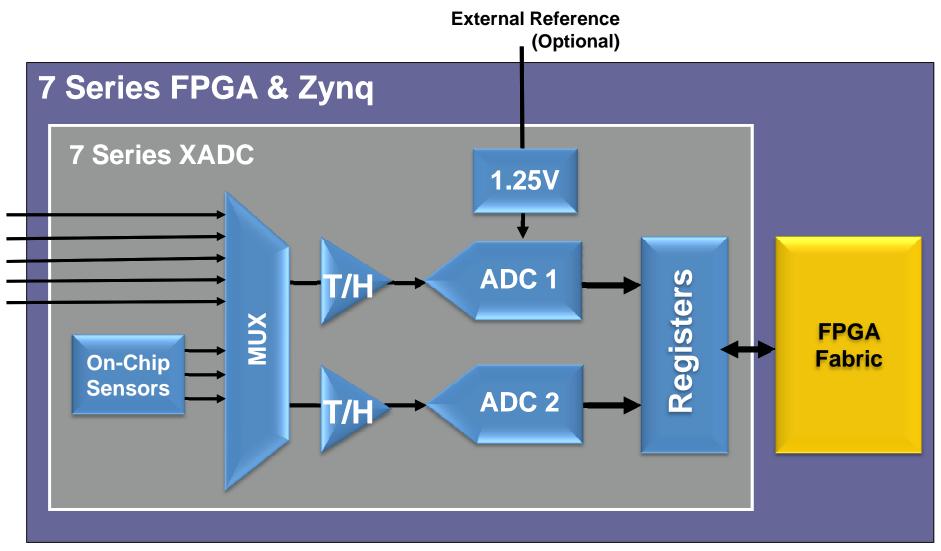

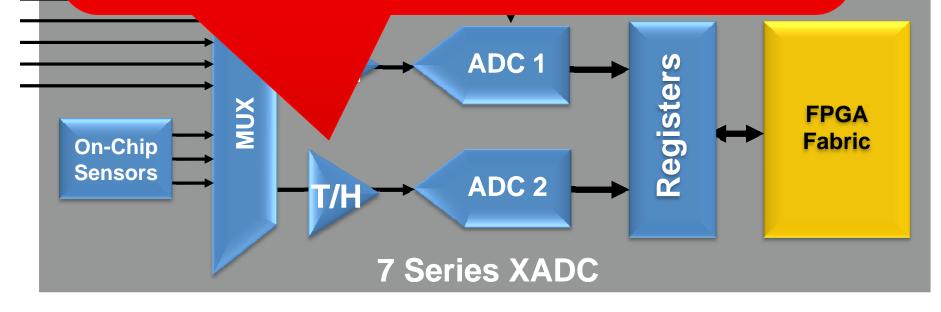

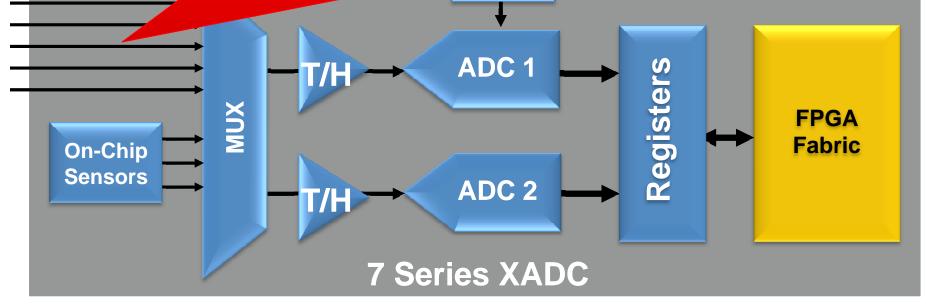

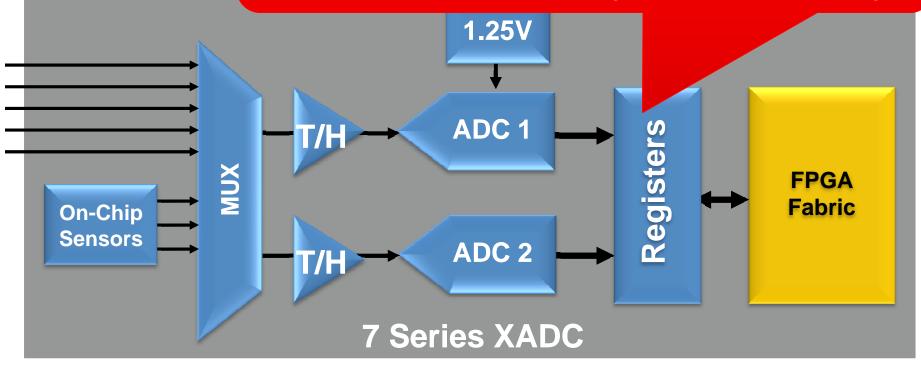

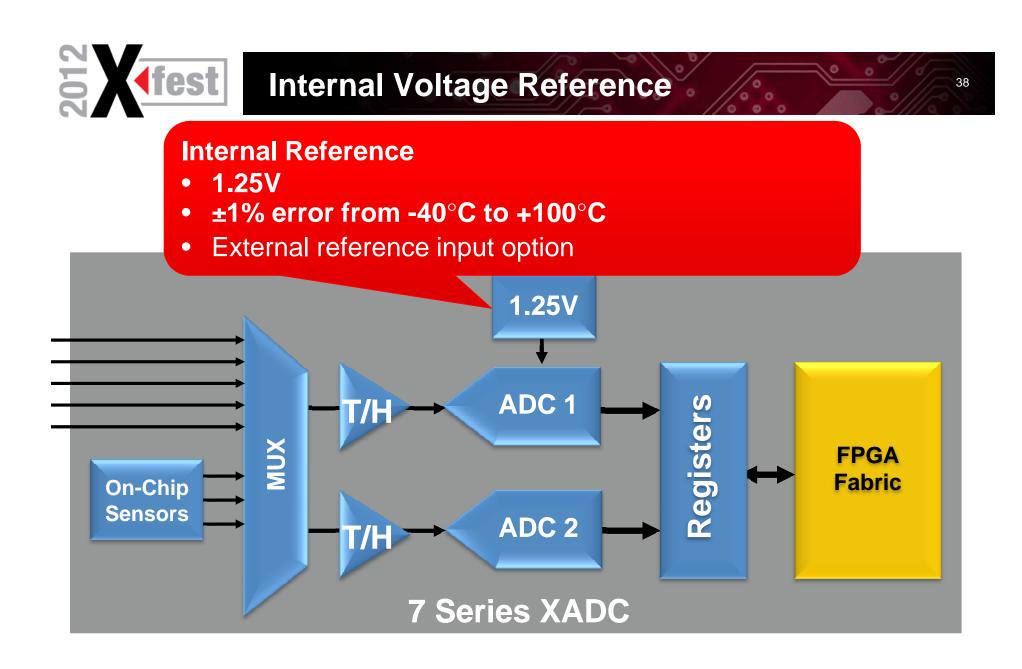

## XADC Block Diagram

#### Separate Track & Hold Amplifiers

#### Two Flexible Track & Hold (T/H) Amplifiers

- Precise control of sampling timing & simultaneous sampling capability

- True differential sampling of analog signals reduces common mode noise

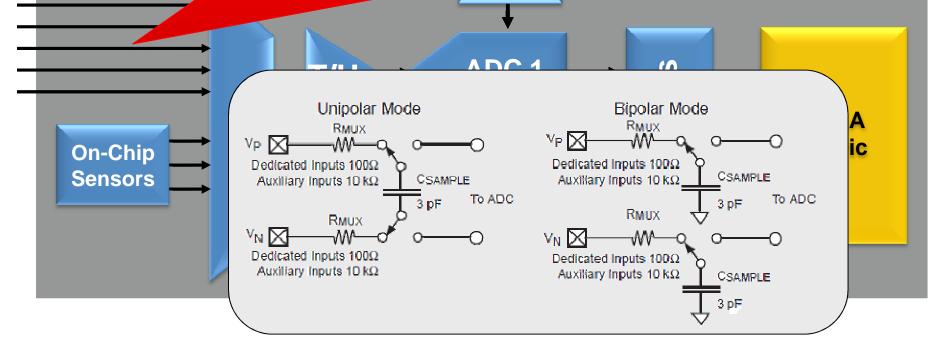

- Supports unipolar and bipolar analog inputs

#### Flexible External Analog Inputs

**External Analog Input Channels**

- One dedicated input channel for use with external analog multiplexer

- On-chip multiplexer with up to 16 analog inputs supported using dual purpose digital IO

Note: Auxiliary channels 6, 7, 13, 14, and 15 are not supported on Kintex-7 devices

#### Flexible External Analog Inputs

#### **External Analog Input Channels**

- Full scale input range is 1V p-p

- Use differential configuration for common mode noise rejection

- Lower input impedance on dedicated input

- Minimum acquisition time is 3ns (300ns for auxiliary inputs)

## **High Speed Digital Interface**

#### **Programmable XADC Operation**

- 250MHz Read / Write Register access

- Operation can be altered at any time via FPGA Interface

- Full customization possible using FPGA based control logic

## **EXADC Wizard Simplifies HDL Instantiation**

| Documents                                                             |                                                                                                   |                                                                                                                                                                             |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mbol                                                                  | 6 ×                                                                                               | (P) XADC Wizard                                                                                                                                                             |

| DI_IN[15:0] →<br>DADDR_IN[6:0] →<br>DEN_IN →<br>DWE_IN →<br>DCLK_IN → | → DO_OUT[15:0]<br>→ DRDY_OUT<br>→ USER_TEMP_ALARM_OUT<br>→ VCCINT_ALARM_OUT<br>→ VCCAUX_ALARM_OUT | Component Name XADC_wiz Sim File Name design Startup Channel Selection Simultaneous Sampling                                                                                |

|                                                                       | →ot_out<br>→vbram_alarm_out E<br>→Alarm_out                                                       | <ul> <li>Independent ADC</li> <li>Single Channel</li> <li>Channel Sequencer</li> </ul>                                                                                      |

| VP_IN →<br>VN_IN →<br>VAUXP0 →<br>VAUXP1 →                            | → CHANNEL_OUT[4:0]<br>→ EOC_OUT<br>→ EOS_OUT<br>→ BUSY_OUT<br>→ JTAGLOCKED_OUT                    | Timing Mode <ul> <li>Continuous Mode</li> <li>Event Mode</li> </ul>                                                                                                         |

| VALIXN1                                                               | → JTAGBUSY_OUT<br>→ JTAGBUSY_OUT<br>→ MUXADDR_OUT[4:0]                                            | DRP Timing options          Image: DCLK         DCLK Frequency (MHz):       100.0         Range: 8250         ADC conversion rate (kSPS):       1000         Range: 1541000 |

| VALIXN4                                                               |                                                                                                   | Increase acquisition time Clock divider value = 4 ADC Clock Frequency(MHz) = 25.00                                                                                          |

### Wizard simplifies XADC Instantiation No HDL experience required – even analog guys can get started

## **XADC Safety Alarms**

- Trigger and reset thresholds for temp alarms

- **Upper and lower** voltage thresholds for on-chip power supplies

| LogiCXRE               | XAD               | C Wizard |                   |  |  |  |

|------------------------|-------------------|----------|-------------------|--|--|--|

| Enable Alarm           | IS                |          |                   |  |  |  |

| Over Temperature Alarm |                   |          |                   |  |  |  |

|                        | OT Trigger (°C)   |          | OT Reset (°C)     |  |  |  |

| 🔽 Enable               | 125.0             |          | 70.0              |  |  |  |

|                        | Range: -40.0125.0 |          | Range: -40.0125.0 |  |  |  |

| User Temperature Alarm |                   |          |                   |  |  |  |

|                        | UT Trigger (°C)   |          | UT Reset (°C)     |  |  |  |

| 🔽 Enable               | 85.0              |          | 60.0              |  |  |  |

|                        | Range: -40.0125.0 |          | Range: -40.0125.0 |  |  |  |

| Vccint Alarm           |                   |          |                   |  |  |  |

| v cente / den          | Lower (Volts)     |          | Upper (Volts)     |  |  |  |

| 🔽 Enable               | 0.97              |          | 1.03              |  |  |  |

|                        | Range: 0.971.00   |          | Range: 1.01.03    |  |  |  |

| Vccaux Alarm           |                   |          |                   |  |  |  |

|                        | Lower (Volts)     |          | Upper             |  |  |  |

| 🔽 Enable               | 1.75              |          | 1.89              |  |  |  |

|                        | Range: 1.711.8    |          | Range: 1.81.89    |  |  |  |

|                        |                   |          |                   |  |  |  |

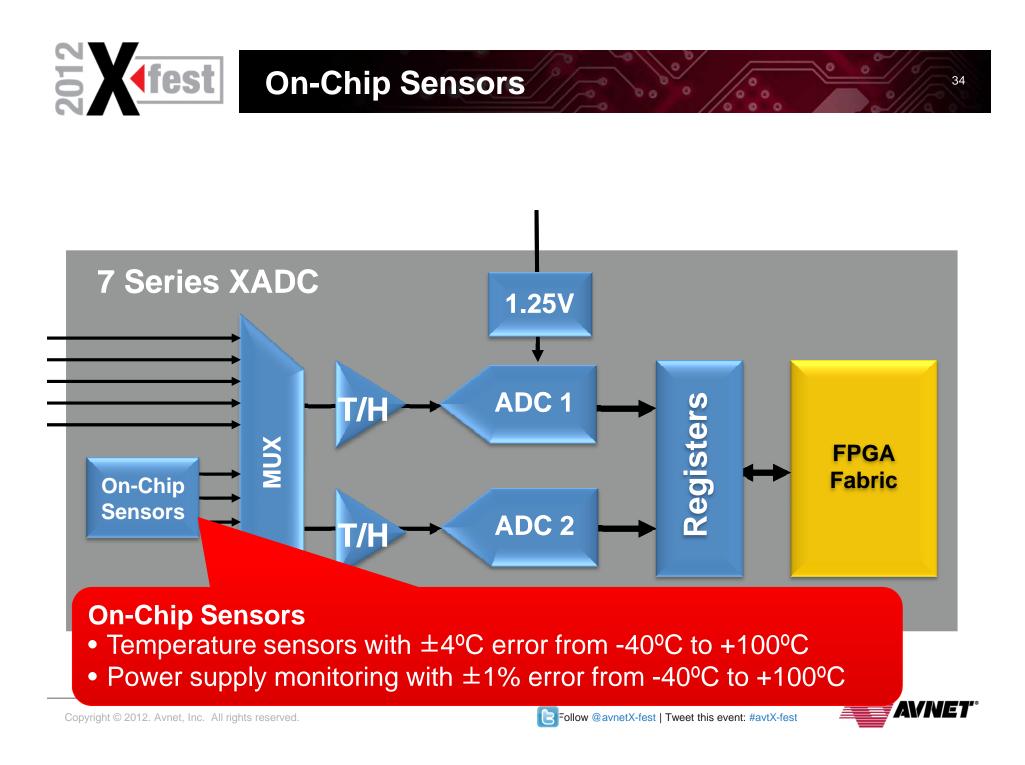

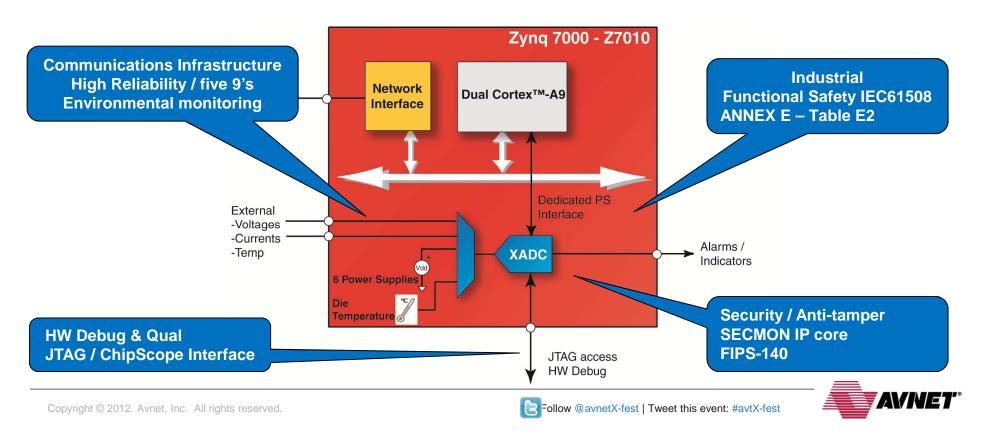

- XADC is a high quality & flexible analog interface new to 7 series

- Dual 12-bit 1Msps ADCs, On-Chip Sensors, 17 flexible analog inputs, Track & Holds with programmable signal conditioning

- Integration of up to \$2-3 of external ADC functionality

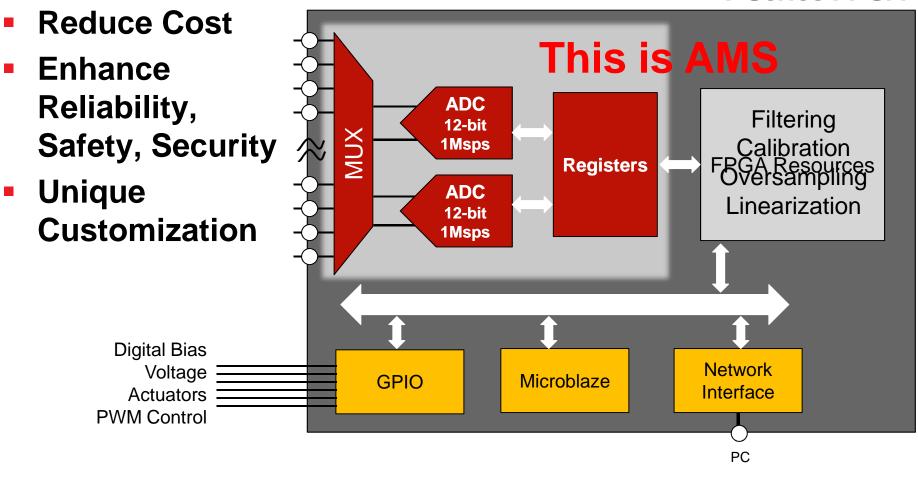

### Agile Mixed Signal (AMS)

Using the FPGA programmable logic to customize the XADC & replace other external analog functions e.g., linearization, calibration, filtering, and DC balancing to improve data conversion resolution.

## AMS = More Than Just an Integrated ADC

#### 7 Series FPGA

## AMS = More Than Just an Integrated ADC

7 Series FPGA

43

## **AMS = combination of analog & programmable logic**

### Remember, there are many sensor types

- Each having it's own output range

- Weigh-scale systems typically use load-cell bridge sensors with maximum full-scale outputs of 1 mV to 2 mV

- In ADC applications, dynamic range is the ratio of the RMS value of the full scale to the RMS noise

For an *N*-bit ADC, the dynamic range (DR) can be calculated as:

DR = 6.021 N + 1.763 dB

So for a 12-bit ADC: Dynamic Range = 74dB

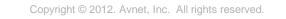

- One method for increasing the dynamic range of a successive-approximation ADC is to implement oversampling

- As a general rule, every doubling of the sampling frequency yields approximately a 3-dB improvement in noise performance

- Decimation in FPGA can average samples and increase dynamic range

- Even more with calibration values

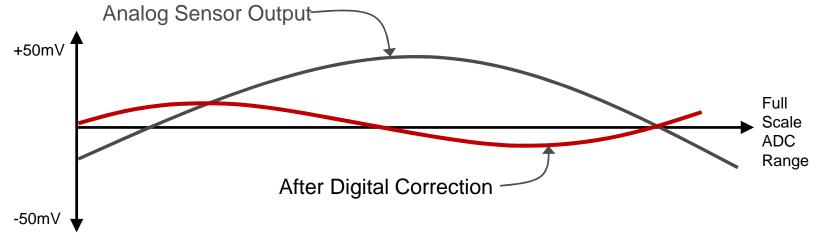

FPGA resources, including DSP, BRAM and logic, can be applied to correct or calibrate the transfer function of the sensor

Integral nonlinearity (INL) is the deviation of the values on an actual transfer function from a straight line

- Linearization of a large number of channels is very efficient

- Same resource can be shared across all channels due to the high FPGA fabric clock rates

As noted before, every doubling of the sampling frequency increases dynamic range by 3dB

From before, 12-bit ADC: Dynamic Range = 74dB

```

Experiment: Oversample by 64 2^{Oversample\_rate} = 64; OSR = 6

```

```

Every doubling increases 3dB

```

```

3dB x 6 (OSR) = 18dB increase!

```

### 92dB

- What to do with Oversampled data?

- Decimation and Gain Control in FPGA!

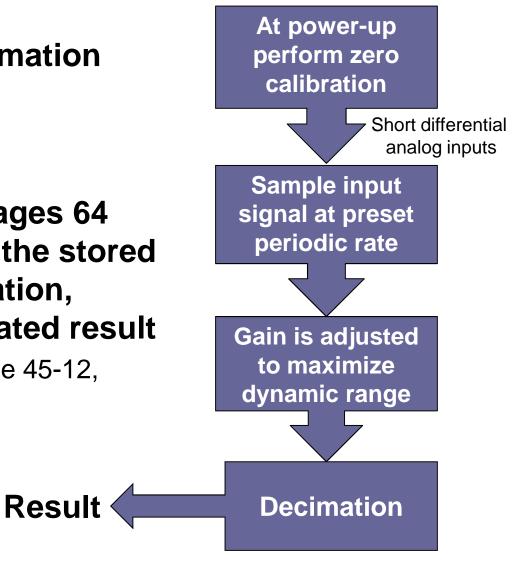

## **AMS – Oversampling and Decimation**

- Here is a look at a decimation algorithm in an FPGA

- Decimation block averages 64 stored samples. Using the stored gain and offset information, produces a new decimated result

- See ADI's Analog Dialogue 45-12, December'11

### Increasing DR by 18dB using resources already available!

49

ANNET

## AMS Examples

- All Applications & Devices

- Generic requirement for Virtex, Kintex, Artix, & Zynq devices

- Enhance Reliability, Safety, and Security of FPGA designs

- Mandated in many applications & covered by industry standards

## Agile Mixed Signal Benefits

### Reduce Cost

- Integration of discrete analog components and reduced board area

- Also eliminate risk of obsolesce & reduce long lead times for proprietary analog components

### Enhanced Reliability, Safety & Security

- On chip sensors for improved reliability, safety & security

- Monitoring of the physical environment required in a wide range of applications

### Unique Customization

- Programmable logic customizes the XADC to address diverse needs

- Simplify external analog signal conditioning / Enhance ADC performance

- Oversampling & decimation , calibration, linearization, and signal processing etc.

## XADC vs. Discrete ADC's

### When is XADC a good fit?

## Agenda

- Analog signal chain

- Standalone data converter solutions

- XADC solution and the customizable analog interface

- Prototyping with expansion boards

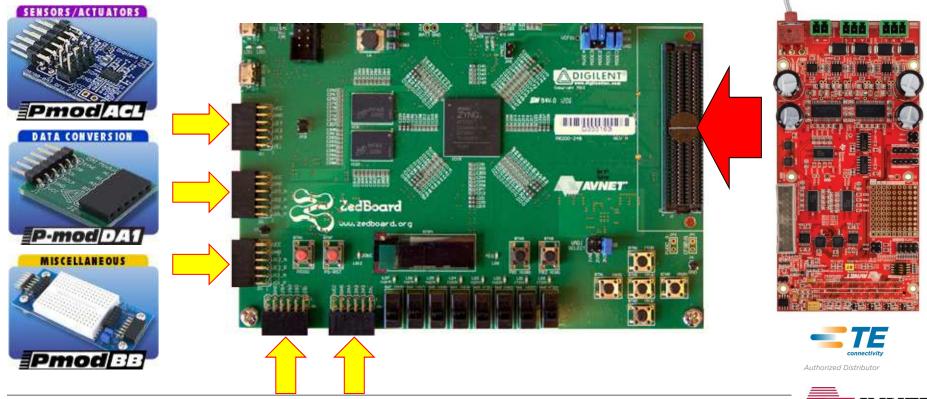

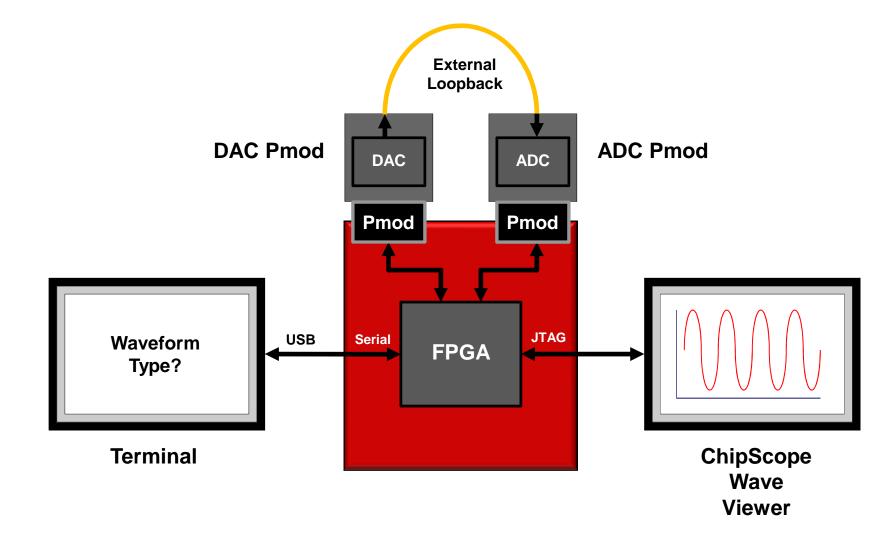

## **Prototyping with Evaluation Boards**

### Pmods and FMC cards allow rapid prototyping

- Pmods = Peripheral Modules

- Data Converters, Wireless/Bluetooth, SD Card, LCD

- Over 50 available, many more coming soon

- Many low-cost add-on peripheral modules as low as \$10

- FMC = FPGA Mezzanine Card

- Feature high performance circuitry, typically > \$100

- Over 30 available, many more coming soon

- Available reference designs allow you to quickly and easily:

- Evaluate the capability of the circuitry

- Use the code examples as starting points to integrate this type of functionality into your design

## Prototyping designs has never been easier

### <u>Pmods</u>

**FMC**

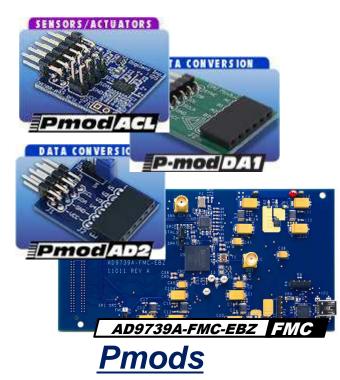

## **Analog Devices Evaluation Boards**

- 12-, 16-, and 24-bit ADCs

- 8-, 12-, and 16-bit DAC's

- 3-axis Accelerometer

- Gyroscope

- Digital Potentiometer

- I2C Temp Sensor

Reference Designs with Immediate Results

57

- Hi-speed 14-bit DAC @ 2.5GSPS

- High-speed 16-bit ADC @ 250MSPS

- RF Transmit and Receive channels

- Interposer for SDP-B

### <u>AMS</u>

- Instrumentation

Amplifier Board

- RF RMS Detector

- RF LogAmp Detector

Sample Pmod Reference Design 58

Copyright © 2012. Avnet, Inc. All rights reserved.

Sollow @avnetX-fest | Tweet this event: #avtX-fest

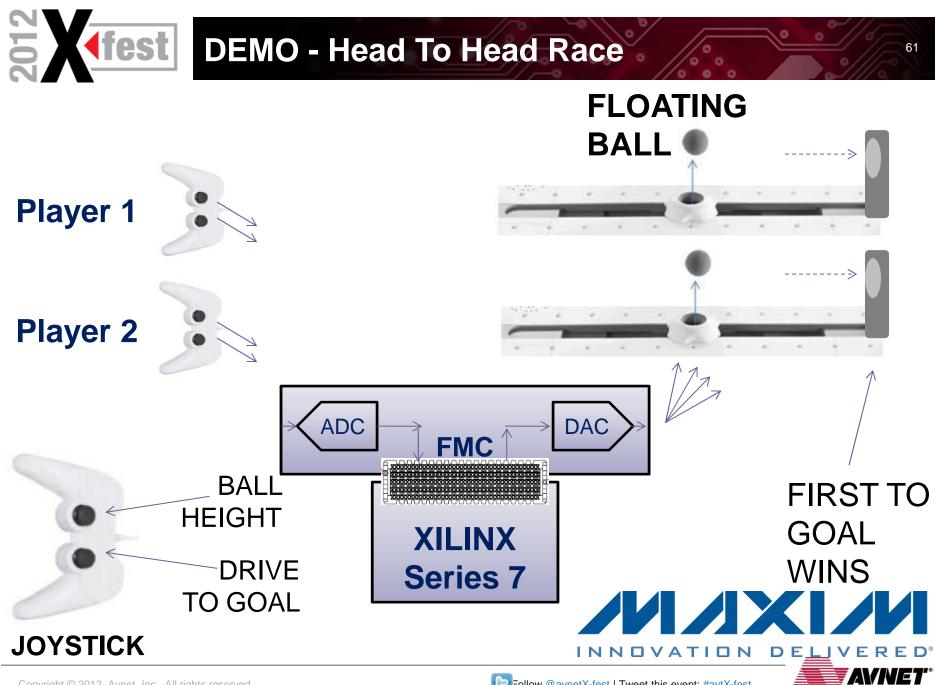

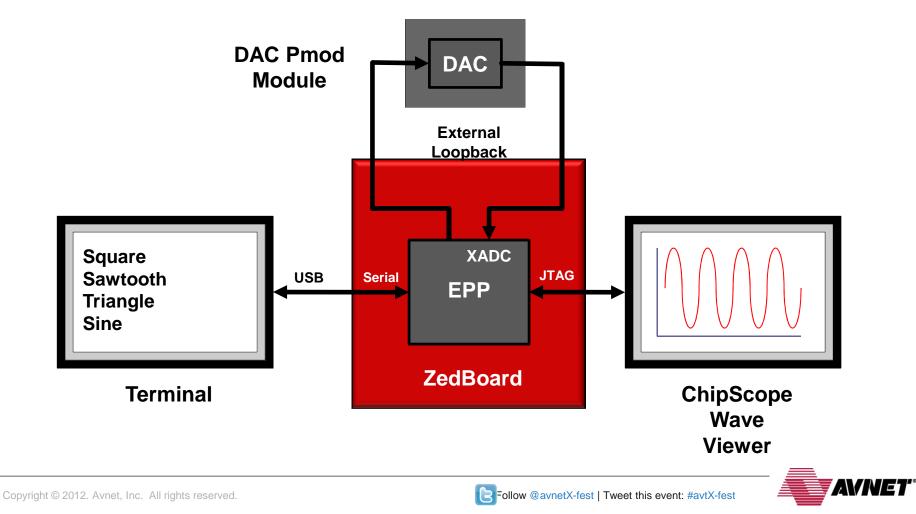

### See XADC sampling real-time waveforms

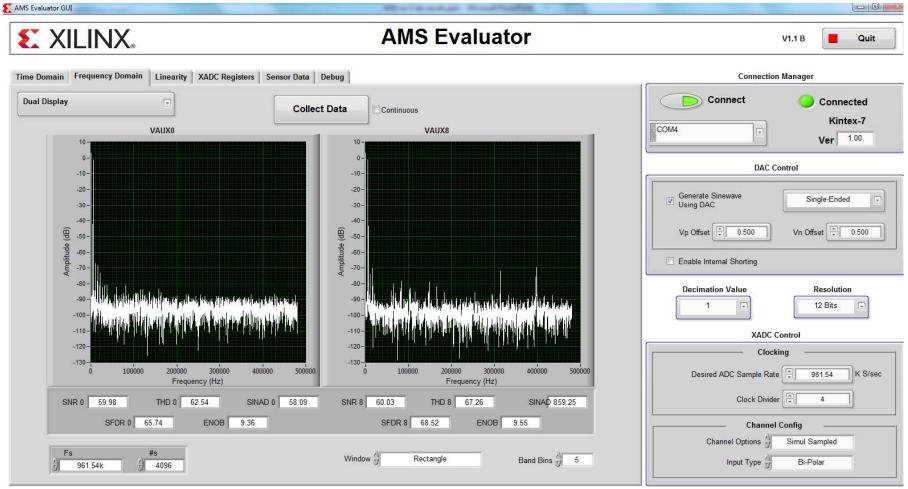

## DEMO – AMS Evaluator

### **Evaluator, Frequency Domain Simultaneous Sampling**

### See it at the Xilinx Booth

63

Copyright © 2012. Avnet, Inc. All rights reserved.

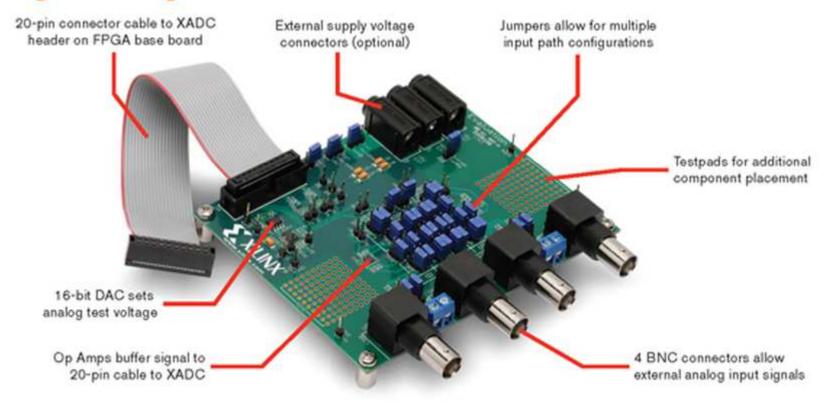

## **AMS Evaluation Card**

#### Agile Mixed Signal Evaluation Card

- Visit supplier tables to see running demos with evaluation boards

- Purchase an evaluation board with a Pmod or FMC

- Download our reference designs and experiment!

- Attend other Xfest courses

- Wireless Communication Systems Course

- FPGA-Based Motor Control Course

- Additional Training

- Avnet Speedway or On-Ramp Training

- Xilinx Training

- Agile Mixed Signaling

- Any DSP/System Generator

# Thank You Please Visit the Demo Area

Follow @avnetX-fest Tweet this event: #avtX-fest

www.facebook.com/X-fest2012