H8DA8 H8DAE H8DAR-8 H8DAR-i

# **USER'S MANUAL**

The information in this User's Manual has been carefully reviewed and is believed to be accurate. The vendor assumes no responsibility for any inaccuracies that may be contained in this document, makes no commitment to update or to keep current the information in this manual, or to notify any person or organization of the updates.

The manufacturer reserves the right to make changes to the product described in this manual at any time and without notice. This product, including software, if any, and documentation may not, in whole or in part, be copied, photocopied, reproduced, translated or reduced to any medium or machine without prior written consent.

IN NO EVENT WILL THE MANUFACTURER BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN PARTICULAR, THE VENDOR SHALL NOT HAVE LIABILITY FOR ANY HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE COSTS OF REPAIRING, REPLACING, INTEGRATING, INSTALLING OR RECOVERING SUCH HARDWARE, SOFTWARE, OR DATA.

Any disputes arising between manufacturer and customer shall be governed by the laws of Santa Clara County in the State of California, USA. The State of California, County of Santa Clara shall be the exclusive venue for the resolution of any such disputes. The manufacturer's total liability for all claims will not exceed the price paid for the hardware product.

Manual Revision 1.1

Release Date: October 5, 2006

Unless you request and receive written permission from the manufacturer, you may not copy any part of this document.

Information in this document is subject to change without notice. Other products and companies referred to herein are trademarks or registered trademarks of their respective companies or mark holders.

Copyright © 2006

All rights reserved.

Printed in the United States of America

# **Preface**

# **About This Manual**

This manual is written for system integrators, PC technicians and knowledgeable PC users. It provides information for the installation and use of the H8DA8/H8DAE/H8DAR-8/H8DAR-i serverboard. The H8DA8/H8DAE/H8DAR-8/H8DAR-i is based on the AMD-8131/8111 chipset and supports single or dual AMD Opteron 200 series type processors in 940-pin microPGA ZIF sockets and up to 32 GB of DDR266 or 16 GB of DDR333/400.

Please refer to the serverboard specifications pages on our web site for updates on supported processors. This product is intended to be professionally installed.

# **Manual Organization**

**Chapter 1** includes a checklist of what should be included in your serverboard box, describes the features, specifications and performance of the serverboard and provides detailed information about the chipset.

**Chapter 2** begins with instructions on handling static-sensitive devices. Read this chapter when installing the processor(s) and memory modules and when installing the serverboard in a chassis. Also refer to this chapter to connect the floppy and hard disk drives, the serial ports, the mouse and keyboard and the twisted wires for the power and reset buttons and the system LEDs.

If you encounter any problems, see **Chapter 3**, which describes troubleshooting procedures for the video, the memory and the setup configuration stored in CMOS. For quick reference, a general FAQ (Frequently Asked Questions) section is provided. Instructions are also included for contacting technical support. In addition, you can visit our web site for more detailed information.

**Chapter 4** includes an introduction to BIOS and provides detailed information on running the CMOS Setup utility.

Appendix A provides BIOS Error Beep Code Messages.

**Appendix B** lists BIOS POST Checkpoint Codes.

# **Table of Contents**

| Prefa | ce |

|-------|----|

|-------|----|

| Abo | ut This Manual                          | iii  |

|-----|-----------------------------------------|------|

| Man | nual Organization                       | iii  |

| Cha | apter 1: Introduction                   |      |

| 1-1 | Overview                                | 1-1  |

|     | Checklist                               | 1-1  |

|     | H8DA8/H8DAE Image                       | 1-3  |

|     | H8DA8/H8DAE Serverboard Layout          | 1-4  |

|     | H8DA8/H8DAE Quick Reference             | 1-5  |

|     | H8DAR-8/H8DAR-i Serverboard Layout      | 1-6  |

|     | H8DAR-8/H8DAR-i Quick Reference         | 1-7  |

|     | H8DAR-8/H8DAR-i Image                   | 1-8  |

|     | Serverboard Features                    | 1-9  |

|     | AMD-8131 Chipset: System Block Diagram  | 1-11 |

| 1-2 | Chipset Overview                        | 1-12 |

| 1-3 | PC Health Monitoring                    | 1-13 |

| 1-4 | Power Configuration Settings            | 1-14 |

| 1-5 | Power Supply                            | 1-15 |

| 1-6 | Super I/O                               | 1-16 |

| Cha | apter 2: Installation                   |      |

| 2-1 | Static-Sensitive Devices                | 2-1  |

| 2-2 | Processor and Heatsink Installation     | 2-2  |

| 2-3 | Mounting the Serverboard into a Chassis | 2-4  |

| 2-4 | Installing Memory                       | 2-4  |

| 2-5 | I/O Port and Control Panel Connections  | 2-7  |

| 2-6 | Connecting Cables                       | 2-8  |

|     | Power Supply Connectors                 | 2-8  |

|     | Secondary Power Connector               | 2-8  |

|     | NMI Button                              | 2-8  |

|     | Power LED                               | 2-8  |

|     | HDD LED                                 | 2-9  |

|     | NIC1 LED                                | 2-9  |

|     | NIC2 LED                                | 2-9  |

|     | Overheat/Fan Fail LED                       | . 2-9 |

|-----|---------------------------------------------|-------|

|     | Power Fail LED                              | . 2-9 |

|     | Reset Button                                | 2-10  |

|     | Power Button                                | 2-10  |

|     | Universal Serial Bus Ports (USB0/1)         | 2-10  |

|     | Chassis Intrusion                           | 2-10  |

|     | Serial Ports                                | 2-11  |

|     | Power Fail and Alarm Reset Header           | 2-11  |

|     | Fan Headers                                 | 2-11  |

|     | JLAN1/2 (Ethernet Ports)                    | 2-11  |

|     | Extra USB Headers                           | 2-12  |

|     | Power LED/Speaker                           | 2-12  |

|     | ATX PS/2 Keyboard/Mouse Ports               | 2-12  |

|     | Wake-On-LAN                                 | 2-13  |

|     | Wake-On-Ring                                | 2-13  |

|     | SMB Power (I <sup>2</sup> C) Header         | 2-13  |

|     | SMB Header                                  | 2-13  |

| 2-7 | Jumper Settings                             | 2-14  |

|     | Explanation of Jumpers                      | 2-14  |

|     | CMOS Clear                                  | 2-14  |

|     | JLAN1/2 Enable/Disable                      | 2-15  |

|     | VGA Enable/Disable                          | 2-15  |

|     | I <sup>2</sup> C to PCI Enable/Disable      | 2-15  |

|     | SCSI Controller Enable/Disable              | 2-15  |

|     | SCSI Termination Enable/Disable             | 2-16  |

|     | 3rd Power Supply Fail Signal Enable/Disable | 2-16  |

|     | Watch Dog Enable/Disable                    | 2-16  |

|     | Onboard Speaker Enable/Disable              | 2-17  |

|     | PCI-X Slot Speed                            | 2-17  |

| 2-8 | Onboard Indicators                          | 2-18  |

|     | JLAN1/2 LEDs                                | 2-18  |

|     | +3.3V Power LED                             | 2-18  |

| 2-9 | Floppy, IDE and SCSI Drive Connections      | 2-19  |

|     | Floppy Connector                            | 2-19  |

|     | IDE Connectors                              | 2-20  |

|     | SCSI Connectors                             | 2-21  |

# **Chapter 3: Troubleshooting** No Video ..... 3-2 3-3 3-4 Chapter 4: BIOS 4-1 4-2 4-3 Advanced Settings Menu ......4-2 4-4 4-5 Boot Menu ...... 4-11 4-6 Security Menu ...... 4-13 4-7 Chipset Menu ...... 4-14 4-8 4-9 Exit Menu 4-19 **Appendices:** Appendix B: BIOS POST Checkpoint Codes...... B-1

# **Chapter 1**

# Introduction

# 1-1 Overview

# Checklist

Congratulations on purchasing your computer serverboard from an acknowledged leader in the industry. Our boards are designed with the utmost attention to detail to provide you with the highest standards in quality and performance.

Please check that the following items have all been included with your serverboard. If anything listed here is damaged or missing, contact your retailer.

# Included with retail box only

- One (1) H8DA8/H8DAE/H8DAR-8/H8DAR-i serverboard

- One (1) IDE cable (CBL-036)

- One (1) floppy cable (CBL-022)

- Two (2) CPU backplates (BKT-0004)

- Two (2) heatsink retention modules with four (4) screws (BKT-0005)

- One (1) I/O backpanel shield for chassis (CSE-PT7)

- One (1) CD containing drivers and utilities

# Notes

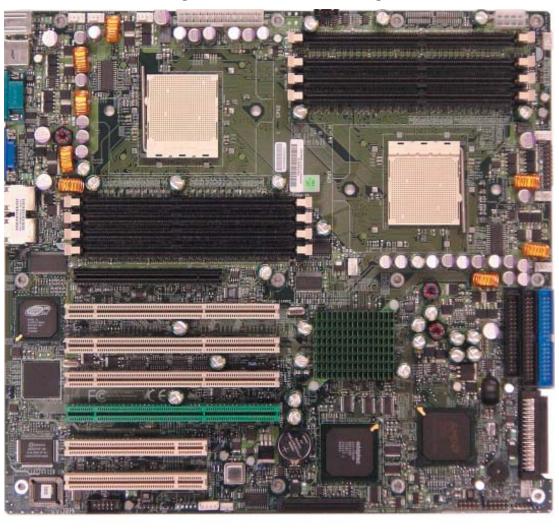

Figure 1-1. H8DA8/H8DAE Image

JPW2 ATX Power J24 J101 FAN5 FAN6 FAN8 (CPU2 Fan) J1B4 CPU1 DIMM 1B USB0/1 CPU1 DIMM 1A CPU1 DIMM 2B СОМ1 CPU1 DIMM 2A CPU2 FAN1 VGA JF1 CPU1 CPU2 DIMM 2A FAN2 CPU2 DIMM 2B JLAN2 CPU2 DIMM 1A CPU2 DIMM 1B FAN7 (CPU1 Fan) FAN3 1U IPMI PCI-X 133/100 MHz #6 Rage XL Graphics ☐ JPG1 JFDD1 JIDE#2 AMD-8131 PCI-X 133/100 MHz #5 □ ЈРХВ0 PCI-X 66 MHz #4 JPA3 PCI-X 66 MHz #3 ZCR □ DP1 Adaptec AMD-8111 JK1/JWOR/JOH/JL1 Battery Winbond Super I/O PCI 33 MHz #2 JPXA0 □□JI²C1/2 □ JBT1 SCSI Controlle PCI 33 MHz #1 BIOS FAN4 J22 \_\_\_ JWOL COM2 JB2

Figure 1-2. H8DA8/H8DAE Serverboard Layout (not drawn to scale)

# Notes:

Jumpers not indicated are for test purposes only.

SCSI components, connectors and jumpers are for the H8DA8 only.

# H8DA8/H8DAE Quick Reference

| Jumpers              | Description                            | Default Setting    |

|----------------------|----------------------------------------|--------------------|

| J3P                  | 3rd Power Fail Signal En/Dis           | Open (Disabled)    |

| JBT1                 | CMOS Clear                             | See Section 2-7    |

| JI <sup>2</sup> C1/2 | I <sup>2</sup> C to PCI Enable/Disable | Closed (Enabled)   |

| JPA1*                | SCSI Controller En/Disable             | Pins 1-2 (Enabled) |

| JPA2/3*              | SCSI CH A/B Term. En/Dis               | Open (Enabled)     |

| JPG1                 | VGA Enable/Disable                     | Pins 1-2 (Enabled) |

| JPL                  | JLAN1/JLAN2 En/Disable                 | Pins 1-2 (Enabled) |

| JPXA0                | PCI-X Slot #3/4 Speed                  | Open (Auto)        |

| JPXB0                | PCI-X Slot #5/6 Speed                  | Open (Auto)        |

| JWD                  | Watch Dog                              | Pins 1-2 (Reset)   |

| Connectors | Description     |

|------------|-----------------|

| 1U IPMI    | IPMI 2.0 Socket |

COM1, COM2 COM1/COM2 Serial Port/Header

DP1 Onboard +3.3V Power LED

Fans 1-8 System Fan Headers

J22 System Management Bus Header

J24 I<sup>2</sup>C Header

J101 PS/2 Keyboard/Mouse Ports

J1B4 24-Pin ATX Power Connector

JA1\* Ultra320 SCSI Channel A Connector

JAR Power Supply Alarm Reset Header

JB2\* Ultra320 SCSI Channel B Connector

JD1 Internal Speaker (Buzzer) Enable/Power LED Header

JF1 Front Panel Connector

JFDD1 Floppy Disk Drive Connector

JIDE#1/JIDE#2 IDE#1/IDE#2 Connectors

JK1 Keylock Header

JL1 Chassis Intrusion Header

JLAN1/2 Gigabit Ethernet (RJ45) Ports

JOH1 Overheat Warning Header

JP10 Power Fail and Alarm Reset Header

JPW2 8-Pin Power Connector

JWOL Wake-On-LAN Header

JWOR Wake-On-Ring Header

SPKR Onboard Speaker (Buzzer)

USB0/1 Universal Serial Ports1/2

USB2/3/4 USB Headers VGA Video Port

\*H8DA8 only

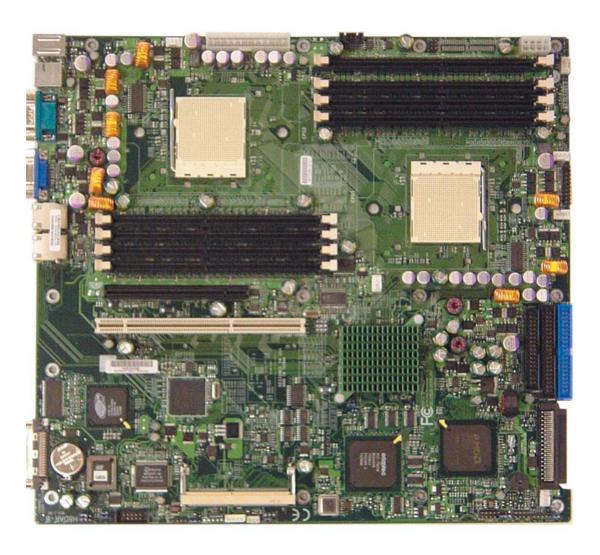

JPW2 & SA FAN5 ATX Power J101 J1B4 CPU1 DIMM 1B USB0/1 CPU1 DIMM 1A CPU1 DIMM 2B CPU1 DIMM 2A COM1 CPU2 FAN1 VGA CPU1 JLAN1 FAN2 CPU2 DIMM 2A CPU2 DIMM 2B JLAN2 CPU2 DIMM 1A CPU2 DIMM 1B FAN4 1U IPMI PCI-X 100 MHz #6 JIDE#2 AMD-8131 Broadcom BCM5704 JPA3 JK1/JWOR/JOH/JL1 JB2 Adaptec JA1 AMD-8111 DP1 7902W SCSI Controller Winbond Super I/O FAN3 USB2/3

Figure 1-3. H8DAR-8/H8DAR-i Serverboard Layout (not drawn to scale)

# Notes:

Jumpers not indicated are for test purposes only.

SCSI components, connectors and jumpers are for the H8DAR-8 only.

# H8DAR-8/H8DAR-i Quick Reference

| Jumpers              | Description                            | <b>Default Setting</b> |

|----------------------|----------------------------------------|------------------------|

| J3P                  | 3rd Power Fail Signal En/Dis           | Open (Disabled)        |

| JBT1                 | CMOS Clear                             | See Section 2-7        |

| JI <sup>2</sup> C1/2 | I <sup>2</sup> C to PCI Enable/Disable | Closed (Enabled)       |

| JPA1*                | SCSI Controller En/Disable             | Pins 1-2 (Enabled)     |

| JPA2/3*              | SCSI CH A/B Term. En/Dis               | Open (Enabled)         |

| JPG1                 | VGA Enable/Disable                     | Pins 1-2 (Enabled)     |

| JPL                  | JLAN1/JLAN2 En/Disable                 | Pins 1-2 (Enabled)     |

| JPXB0                | PCI-X Slot #6 Speed                    | Open (Auto)            |

| JWD                  | Watch Dog                              | Pins 1-2 (Reset)       |

**Connectors Description**

1U IPMI IPMI 2.0 Socket

COM1/COM2 COM1/COM2 Serial Port/Header

DP1 Onboard +3.3V Power LED

Fans 1-5 System Fan Headers

J22 System Management Bus Header

J24 I<sup>2</sup>C Header

J101 PS/2 Keyboard/Mouse Ports

J1B4 24-Pin ATX Power Connector

JA1\* Ultra320 SCSI Channel A Connector

JAR Power Supply Alarm Reset Header

JB2\* Ultra320 SCSI Channel B Connector

JD1 Internal Speaker (Buzzer) Enable/Power LED Header

JF1 Front Panel Connector

JFDD1 Floppy Disk Drive Connector

JIDE#1/JIDE#2 IDE#1/IDE#2 Connectors

JK1 Keylock Header

JL1 Chassis Intrusion Header

JLAN1/2 Gigabit Ethernet (RJ45) Ports

JOH1 Overheat Warning Header

JP10 Power Fail and Alarm Reset Header

JPW2 8-Pin Power Connector

JR1 64-bit, 100 MHz PCI-X Slot

JWOL Wake-On-LAN Header

JWOR Wake-On-Ring Header

SPKR Onboard Speaker (Buzzer)

USB0/1/2/3/4 Universal Serial Bus (Ports: 0/1, Headers: 2/3/4)

VGA Video Port

\*H8DAR-8 only

Figure 1-4. H8DAR-8/H8DAR-i Image

# **Serverboard Features**

# **CPU**

Single or dual AMD Opteron 200 series 64-bit processors in 940-pin microPGA ZIF sockets

## **Memory**

Eight dual/single channel DIMM slots supporting up to 32 GB of registered ECC DDR266 or up to 16 GB of registered ECC DDR400/333 SDRAM

Note: Memory capacities are halved for single CPU systems. Refer to Section 2-4 before installing.

#### **Chipset**

AMD-8131/8111

# **Expansion Slots**

# H8DA8/H8DAE:

• Two (2) 64-bit, 133/100 MHz PCI-X (3.3V)

Note: These two slots share a single bus. When both slots are populated they will run at 100 MHz.

• Two (2) 64-bit, 66 MHz PCI-X (3.3V)

Note: PCI-X-#3 will support a Zero Channel RAID card

Two (2) 32-bit, 33 MHz PCI (5V)

# H8DAR-8/H8DAR-i:

• One (1) 64-bit, 100 MHz PCI-X (3.3V)

#### **BIOS**

- 4 Mb Firmware Hub AMIBIOS® Flash ROM

- APM 1.2, DMI 2.3, PCI 2.2, ACPI 1.0 (ACPI 2.0 is BIOS supported), Plug and Play (PnP), SMBIOS2.3

# **PC Health Monitoring**

- Onboard monitors for CPU core voltages, Hyper Transport voltage (1.2V), memory voltage (2.5V), DDR temination voltage (1.25V), +3.3V, +5V, ±12V, +1.8V, +5V stby and +3.3V stby

- · Fan status monitor with firmware/software speed control

- · Watch Dog, NMI

- Environmental temperature monitoring via BIOS

- Power-up mode control for recovery from AC power loss

- · System resource alert

- Hardware BIOS virus protection

- · Auto-switching voltage regulator for the CPU core

#### **ACPI Features**

- Microsoft OnNow

- Slow blinking LED for suspend state indicator

- BIOS support for USB keyboard

- · Main switch override mechanism

- Internal/external modem ring-on

# Onboard I/O

- Adaptec 7902W dual channel Ultra320 SCSI controller (H8DA8 and H8DAR-8 only)

- Adaptec SCSI RAID 2010S supported (Host RAID 0, 1, 10, JBOD: H8DA8 only)

- Adaptec SCSI RAID 2015S supported (Host RAID 0, 1, 10, JBOD: H8DAR-8 only)

- Two (2) ATA133 IDE headers

- One (1) floppy port interface (up to 2.88 MB)

- Two (2) Fast UART 16550 compatible serial connectors (1 header, 1 port)

- Broadcom BCM5704 Ethernet controller supports two Gigabit LAN ports

- PS/2 mouse and PS/2 keyboard ports

- Up to five (5) USB (Universal Serial Bus) 1.1 ports/headers

- · ATI Rage 8 MB XL graphics chip

- VGA port

# **Other**

- Wake-on-Ring (JWOR)

- Wake-on-LAN (JWOL)

- Onboard +3.3V power LED ("DP1")

# **CD Utilities**

· BIOS flash upgrade utility

## **Dimensions**

Extended ATX form factor, 12" x 13.05" (305 x 332 mm)

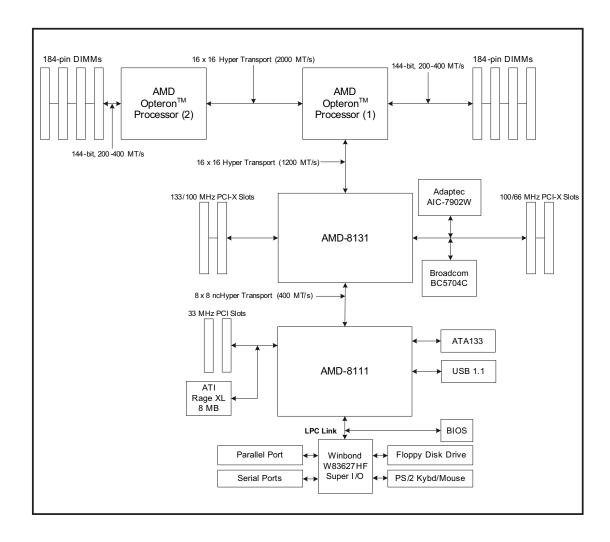

Figure 1-5. AMD-8131/8111™ Chipset: System Block Diagram

**Note:** This is a general block diagram and may not exactly represent the features on your serverboard. See the previous pages for the actual specifications of your serverboard.

# 1-2 Chipset Overview

The H8DA8/H8DAE/H8DAR-8/H8DAR-i serverboard is based on the AMD-8131<sup>™</sup> chipset. This chipset is composed of two main components: the AMD-8131 HyperTransport<sup>™</sup> PCI-X Tunnel and the AMD-8111<sup>™</sup> HyperTransport<sup>™</sup> I/O Hub. The AMD-8131 chipset provides high performance and an excellent feature-set for multi-processor server solutions. Controllers for the system memory are built directly into the processors.

# 8131 HyperTransport PCI-X Tunnel

This hub includes AMD-specific technology that provides two PCI-X bridges with each bridge supporting a 64-bit data bus as well as separate PCI-X operational modes and independent transfer rates. Each bridge supports up to five PCI masters that include clock, request and grant signals. This hub connects to the processors and through them to system memory. It also interfaces directly with the SCSI and Ethernet controllers.

# 8111 HyperTransport I/O Hub

The 8111 I/O hub provides the interface between the 8131 hub and various subsystems including the Winbond Super I/O functions, the onboard graphics, the IDE controller and the USB ports.

# HyperTransport Technology

HyperTransport technology is a high-speed, low latency point to point link that was designed to increase the communication speed by a factor of up to 48x between integrated circuits. This is done partly by reducing the number of buses in the chipset to reduce bottlenecks and by enabling a more efficient use of memory in multi-processor systems. The end result is a significant increase in bandwidth within the chipset.

# 1-3 PC Health Monitoring

This section describes the PC health monitoring features of the H8DA8/H8DAE/H8DAR-8/H8DAR-i. The serverboard has an onboard System Hardware Monitor chip that supports PC health monitoring.

Onboard Voltage Monitors for the CPU Core voltages, Hyper Transport voltage (1.2V), memory voltage (2.5V), DDR temination voltage (1.25V), +3.3V, +5V, ±12V, +1.8V, +5V stby and +3.3V stby

The onboard voltage monitor will scan these voltages continuously. Once a voltage becomes unstable, it will give a warning or send an error message to the screen. Users can adjust the voltage thresholds to define the sensitivity of the voltage monitor. Real time readings of these voltage levels are all displayed in BIOS.

# Fan Status Monitor with Firmware/Software Speed Control

The PC health monitor can check the RPM status of the cooling fans. The onboard fans are controlled by thermal management via BIOS.

# CPU Overheat/Fan Fail LED and Control

This feature is available when the user enables the CPU overheat/Fan Fail warning function in the BIOS. This allows the user to define an overheat temperature. When this temperature is exceeded or when a fan failure occurs, then, the Overheat/Fan Fail warning LED is triggered.

# Auto-Switching Voltage Regulator for the CPU Core

The 3-phase-switching voltage regulator for the CPU core can support up to 80A and auto-sense voltage IDs ranging from 0.875 V to 1.6V. This will allow the regulator to run cooler and thus make the system more stable.

# 1-4 Power Configuration Settings

This section describes the features of your serverboard that deal with power and power settings.

### Microsoft OnNow

The OnNow design initiative is a comprehensive, system-wide approach to system and device power control. OnNow is a term for a PC that is always on but appears to be off and responds immediately to user or other requests.

# Slow Blinking LED for Suspend-State Indicator

When the CPU goes into a suspend state, the chassis power LED will start blinking to indicate that the CPU is in suspend mode. When the user presses any key, the CPU will wake-up and the LED will automatically stop blinking and remain on.

# **BIOS Support for USB Keyboard**

If a USB keyboard is the only keyboard in the system, it will function like a normal keyboard during system boot-up.

#### Main Switch Override Mechanism

When an ATX power supply is used, the power button can function as a system suspend button. When the user depresses the power button, the system will enter a SoftOff state. The monitor will be suspended and the hard drive will spin down. Depressing the power button again will cause the whole system to wake-up. During the SoftOff state, the ATX power supply provides power to keep the required circuitry in the system alive. In case the system malfunctions and you want to turn off the power, just depress and hold the power button for 4 seconds. The power will turn off and no power will be provided to the serverboard.

# Wake-On-LAN (JWOL)

Wake-On-LAN is defined as the ability of a management application to remotely power up a computer that is powered off. Remote PC setup, up-dates and access tracking can occur after hours and on weekends so that daily LAN traffic is kept to a minimum and users are not interrupted. The serverboard has a 3-pin header (JWOL) to connect to the 3-pin header on a Network Interface Card (NIC) that has

WOL capability. Wake-On-LAN must be enabled in BIOS. Note that Wake-On-LAN can only be used with an ATX 2.01 (or above) compliant power supply.

# Wake-On-Ring Header (JWOR)

Wake-up events can be triggered by a device such as the external modem ringing when the system is in the SoftOff state. Note that external modem ring-on can only be used with an ATX 2.01 (or above) compliant power supply.

# 1-5 Power Supply

As with all computer products, a stable power source is necessary for proper and reliable operation. It is even more important for processors that have high CPU clock rates of 1 GHz and faster.

The H8DA8/H8DAE/H8DAR-8/H8DAR-i accommodates 12V ATX power supplies. Although most power supplies generally meet the specifications required by the CPU, some are inadequate. A 2 amp current supply on a 5V Standby rail is strongly recommended.

It is strongly recommended that you use a high quality power supply that meets 12V ATX power supply Specification 1.1 or above. Additionally, in areas where noisy power transmission is present, you may choose to install a line filter to shield the computer from noise. It is recommended that you also install a power surge protector to help avoid problems caused by power surges.

**Warning:** To prevent the possibility of explosion, do not use the wrong type of onboard CMOS battery or install it upside down.

# 1-6 Super I/O

The disk drive adapter functions of the Super I/O chip include a floppy disk drive controller that is compatible with industry standard 82077/765, a data separator, write pre-compensation circuitry, decode logic, data rate selection, a clock generator, drive interface control logic and interrupt and DMA logic. The wide range of functions integrated onto the Super I/O greatly reduces the number of components required for interfacing with floppy disk drives. The Super I/O supports two 360 K, 720 K, 1.2 M, 1.44 M or 2.88 M disk drives and data transfer rates of 250 Kb/s, 500 Kb/s or 1 Mb/s.

It also provides two high-speed, 16550 compatible serial communication ports (UARTs), one of which supports serial infrared communication. Each UART includes a 16-byte send/receive FIFO, a programmable baud rate generator, complete modem control capability and a processor interrupt system. Both UARTs provide legacy speed with baud rate of up to 115.2 Kbps as well as an advanced speed with baud rates of 250 K, 500 K, or 1 Mb/s, which support higher speed modems.

The Super I/O provides functions that comply with ACPI (Advanced Configuration and Power Interface), which includes support of legacy and ACPI power management through a SMI or SCI function pin. It also features auto power management to reduce power consumption.

The IRQs, DMAs and I/O space resources of the Super I/O can be flexibly adjusted to meet ISA PnP requirements, which support ACPI and APM (Advanced Power Management).

# Chapter 2 Installation

# 2-1 Static-Sensitive Devices

Electric Static Discharge (ESD) can damage electronic components. To prevent damage to your system board, it is important to handle it very carefully. The following measures are generally sufficient to protect your equipment from ESD.

# **Precautions**

- Use a grounded wrist strap designed to prevent static discharge.

- Touch a grounded metal object before removing the board from the antistatic bag.

- Handle the board by its edges only; do not touch its components, peripheral chips, memory modules or gold contacts.

- When handling chips or modules, avoid touching their pins.

- Put the serverboard and peripherals back into their antistatic bags when not in use.

- For grounding purposes, make sure your computer chassis provides excellent conductivity between the power supply, the case, the mounting fasteners and the serverboard.

- Use only the correct type of CMOS onboard battery as specified by the manufacturer. Do not install the CMOS onboard battery upside down, which may result in a possible explosion.

# Unpacking

The serverboard is shipped in antistatic packaging to avoid static damage. When unpacking the board, make sure the person handling it is static protected.

# **Installation Procedures**

Follow the procedures as listed below to install the serverboard into a chassis:

- 1. Install the processor(s) and the heatsink(s).

- 2. Install the serverboard in the chassis.

- 3. Install the memory and add-on cards.

- 4. Finally, connect the cables and install the drivers.

#### Processor and Heatsink Installation 2-2

Exercise extreme caution when handling and installing the processor. Always connect the power cord last and always remove it before adding, removing or changing any hardware components.

# Installing the CPU Backplates

Two CPU backplates (BKT-0004) are included in the retail box. The backplates prevent the CPU area of the serverboard from bending and provide a base for attaching the heatsink retention modules. To install, begin by peeling off the release paper to expose the adhesive. On the underside of the serverboard, locate the two holes on either side of the CPU socket. Attach the adhesive side of the backplate to the board by inserting the standoffs into the two holes and applying light pressure so that the backplate sticks to the underside of the board. Repeat for the second CPU socket. See Figure 2-1.

# Installing the Processor (install to the CPU#1 socket first)

1. Lift the lever on CPU socket #1 until it points straight up.

2. Use your thumb and your index finger to hold the CPU. Locate pin 1 on the CPU socket and pin 1 on the CPU. Both are marked with a triangle.

3. Align pin 1 of the CPU with pin 1 of the socket. Once aligned, carefully place the CPU into the socket. Do not drop the CPU on the socket, move the CPU horizontally or vertically or rub the CPU against the socket or against any pins of the socket, which may damage the CPU and/or the socket.

- 4. With the CPU inserted into the socket, inspect the four corners of the CPU to make sure that it is properly installed and flush with the socket.

- 5. Gently press the CPU socket lever down until it locks in the plastic tab. For a dual-processor system, repeat these steps to install another CPU into the CPU#2 socket.

**Note:** if using a single processor, only CPU 1 DIMM slots are addressable.

# **Installing the Heatsink Retention Modules**

Two heatsink retention modules (BKT-0005) and four screws are included in the retail box. Once installed, these are used to help attach the heatsinks to the CPUs. To install, position the module so that the CPU backplate standoffs insert through the holes on the heatsink retention module and the four feet on the module contact the serverboard. Secure the retention module to the backplate with two of the screws provided. See Figure 2-1. Repeat for the second CPU socket. **Note:** BKT-0005 is included for use with non-proprietary heatsinks only. When installing proprietary heatsinks, only BKT-0004 (CPU backplate) is needed. The BKT-0005 retention module was designed to provide compatibility with clip-and-cam type heatsinks from third parties.

Heatsink retention module

CPU socket

Serverboard

release paper

CPU backplate

Figure 2-1. CPU Backplate/Heatsink Retention Module Installation

# Installing the Heatsink

We recommend the use of active type heatsinks (except for 1U systems). Use the Fan7 header for the CPU1 fan and the Fan8 header for the CPU2 fan due to fan monitoring and wiring considerations. To install the heatsinks, please follow the installation instructions included with your heatsink package (not included).

# 2-3 Mounting the Serverboard into a Chassis

All serverboards and motherboards have standard mounting holes to fit different types of chassis. Make sure that the locations of all the mounting holes for both the serverboard and the chassis match. Although a chassis may have both plastic and metal mounting fasteners, metal ones are highly recommended because they ground the serverboard to the chassis. Make sure that the metal standoffs click in or are screwed in tightly.

#### 1. Check the compatibility of the serverboard ports and the I/O shield

The H8DA8/H8DAE/H8DAR-8/H8DAR-i serverboard requires a chassis that can support extended ATX boards of 12" x 13.05" in size. Make sure that the I/O ports on the serverboard align with their respective holes in the I/O shield at the rear of the chassis.

# 2. Mounting the serverboard onto the mainboard tray in the chassis

Carefully mount the serverboard onto the mainboard tray by aligning the serverboard mounting holes with the raised metal standoffs in the tray. Insert screws into all the mounting holes in the serverboard that line up with the standoffs. Then use a screwdriver to secure the serverboard to the mainboard tray - tighten until just snug (if too tight you might strip the threads). Metal screws provide an electrical contact to the serverboard ground to provide a continuous ground for the system.

# 2-4 Installing Memory

# CAUTION

Exercise extreme care when installing or removing memory modules to prevent any possible damage.

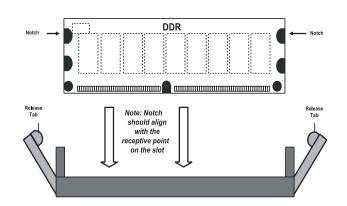

- 1. Insert each memory module vertically into its slot, paying attention to the notch along the bottom of the module to prevent inserting the module incorrectly (see Figure 2-2). See support information below.

- 2. Gently press down on the memory module until it snaps into place.

**Note:** each processor has its own built-in memory controller, so CPU2 DIMMs cannot be addressed if only a single CPU is installed. 128 MB, 256 MB, 512 MB, 1 GB, 2 GB\* and 4 GB\* memory modules are supported.

# Support

The H8DA8/H8DAE/H8DAR-8/H8DAR-i supports single or dual-channel, registered ECC DDR400/333/266 SDRAM.

Both interleaved and non-interleaved memory are supported, so you may populate any number of DIMM slots (see note on previous page and charts on following page). The CPU2 DIMM slots can only be accessed when two CPUs are installed (however, the CPU2 DIMM slots are not required to be populated when two CPUs are installed).

Populating two adjacent slots at a time with memory modules of the same size and type will result in interleaved (128-bit) memory, which is faster than non-interleaved (64-bit) memory.

# Optimizing memory performance

If two processors are installed, it is better to stagger pairs of DIMMs across both sets of CPU DIMM slots, e.g. first populate CPU1 slots 1A and 1B, then CPU2 slots 1A, and 1B, then the next two CPU1 slots, etc. This balances the load over both CPUs to optimize performance.

**Maximum memory (two CPUs)**: 32 GB for DDR266 and 16 GB for DDR400/333. If only one CPU is installed, maximum supported memory is halved (16 GB for DDR266 and 8 GB for DDR400/333).

Figure 2-2. Side and Top Views of DDR Installation

#### To Install:

Insert module vertically and press down until it snaps into place. The release tabs should close - if they do not you should close them yourself.

Note the notch in the slot and on the bottom of the DIMM. These prevent the DIMM from being installed incorrectly.

#### To Remove:

Use your thumbs to gently push each release tab outward to release the DIMM from the slot.

|                | Populating Memory Banks for 128-bit Operation |                |                |                |                |                |                |

|----------------|-----------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|

| CPU1<br>DIMM1A | CPU1<br>DIMM1B                                | CPU1<br>DIMM2A | CPU1<br>DIMM2B | CPU2<br>DIMM1A | CPU2<br>DIMM1B | CPU2<br>DIMM2A | CPU2<br>DIMM2B |

| Х              | Х                                             |                |                |                |                |                |                |

| Х              | Х                                             |                |                | X              | Х              |                |                |

| X              | X                                             |                |                |                |                | Х              | Х              |

| X              | X                                             |                |                | X              | Х              | Х              | Х              |

| Х              | X                                             | X              | Х              |                |                |                |                |

| X              | X                                             | X              | Х              | X              | Х              |                |                |

| X              | X                                             | Х              | Х              |                |                | X              | Х              |

| X              | X                                             | X              | Х              | X              | Х              | X              | Х              |

|                |                                               | X              | Х              |                |                |                |                |

|                |                                               | Х              | Х              | X              | Х              |                |                |

|                |                                               | Х              | X              |                |                | Х              | Х              |

|                |                                               | Х              | X              | Х              | Х              | Х              | Х              |

**Notes:** X indicates a populated DIMM slot. If adding at least four DIMMs (with two CPUs installed), the configurations with DIMMs spread over <u>both</u> CPUs (and not like the configuration in row 5) will result in optimized performance. Note that the first two DIMMs must be installed in the CPU1 memory slots.

|                | Populating Memory Banks for 64-bit Operation |                |                |                |                |                |                |

|----------------|----------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|

| CPU1<br>DIMM1A | CPU1<br>DIMM1B                               | CPU1<br>DIMM2A | CPU1<br>DIMM2B | CPU2<br>DIMM1A | CPU2<br>DIMM1B | CPU2<br>DIMM2A | CPU2<br>DIMM2B |

| Х              |                                              |                |                |                |                |                |                |

|                |                                              | Х              |                |                |                |                |                |

| Х              |                                              | Х              |                |                |                |                |                |

| Х              |                                              |                |                | X              |                |                |                |

| Х              |                                              |                |                |                |                | Х              |                |

|                |                                              | X              |                | X              |                |                |                |

|                |                                              | X              |                |                |                | X              |                |

# 2-5 I/O Port and Control Panel Connections

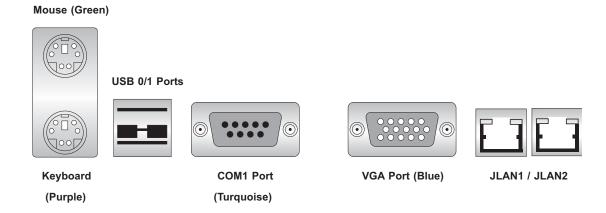

The I/O ports are color coded in conformance with the PC99 specification to make setting up your system easier. See Figure 2-3 below for the colors and locations of the various I/O ports.

Figure 2-3. I/O Port Locations and Definitions

# **Front Control Panel**

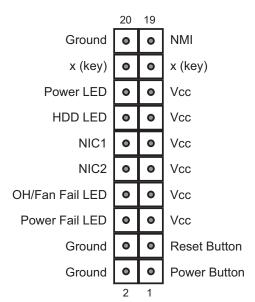

JF1 contains header pins for various front control panel connectors. See Figure 2-4 for the pin definitions of the various connectors. Refer to Section 2-6 for details.

Figure 2-4. JF1: Front Control Panel Header (JF1)

# 2-6 Connecting Cables

# **Power Supply Connectors**

The primary power supply connector (J1B4) on the H8DA8/H8DAE/H8DAR-8/H8DAR-i meets the SSI (Superset ATX) 24-pin specification. Refer to the table on the right for the pin definitions of the ATX 24-pin power connector.

Note: You must also connect the 8pin (JPW2) power connector to your power supply (see below).

| ATX Power 24-pin Connector<br>Pin Definitions (J1B4) |            |      |            |  |  |

|------------------------------------------------------|------------|------|------------|--|--|

| Pin#                                                 | Definition | Pin# | Definition |  |  |

| 13                                                   | +3.3V      | 1    | +3.3V      |  |  |

| 14                                                   | -12V       | 2    | +3.3V      |  |  |

| 15                                                   | COM        | 3    | COM        |  |  |

| 16                                                   | PS_ON      | 4    | +5V        |  |  |

| 17                                                   | COM        | 5    | COM        |  |  |

| 18                                                   | COM        | 6    | +5V        |  |  |

| 19                                                   | COM        | 7    | COM        |  |  |

| 20                                                   | Res (NC)   | 8    | PWR_OK     |  |  |

| 21                                                   | +5V        | 9    | 5VSB       |  |  |

| 22                                                   | +5V        | 10   | +12V       |  |  |

| 23                                                   | +5V        | 11   | +12V       |  |  |

| 24                                                   | COM        | 12   | +3.3V      |  |  |

# Secondary Power Connector

In addition to the Primary ATX power connector (above), the Secondary 12v 8-pin power connector at JPW2 must also be connected to your power supply. See the table on the right for pin definitions.

| Secondary Power<br>Connector<br>Pin Definitions (JPW2) |                |  |

|--------------------------------------------------------|----------------|--|

| Pins Definition                                        |                |  |

| 1 through 4                                            | rough 4 Ground |  |

| 5 through 8 +12V                                       |                |  |

**Required Connection**

#### **NMI** Button

The non-maskable interrupt button header is located on pins 19 and 20 of JF1. Refer to the table on the right for pin definitions.

| NMI Button<br>Pin Definitions (JF1) |            |  |  |

|-------------------------------------|------------|--|--|

| Pin#                                | Definition |  |  |

| 19                                  | Control    |  |  |

| 20                                  | Ground     |  |  |

# **Power LED**

The Power LED connection is located on pins 15 and 16 of JF1. Refer to the table on the right for pin definitions.

| Power LED<br>Pin Definitions (JF1) |            |  |  |  |

|------------------------------------|------------|--|--|--|

| Pin#                               | Definition |  |  |  |

| 15                                 | Vcc        |  |  |  |

| 16                                 | Control    |  |  |  |

## **HDD LED**

The HDD (IDE Hard Disk Drive) LED connection is located on pins 13 and 14 of JF1. Attach the IDE hard drive LED cable to display disk activity. Refer to the table on the right for pin definitions.

| HDD LED<br>Pin Definitions (JF1) |           |  |  |

|----------------------------------|-----------|--|--|

| Pin# Definition                  |           |  |  |

| 13 Vcc                           |           |  |  |

| 14                               | HD Active |  |  |

#### NIC1 LED

The NIC1 (Network Interface Controller) LED connection is located on pins 11 and 12 of JF1. Attach the NIC1 LED cable to display network activity. Refer to the table on the right for pin definitions.

| NIC1 LED<br>Pin Definitions (JF1) |             |  |  |

|-----------------------------------|-------------|--|--|

| Pin# Definition                   |             |  |  |

| 11 Vcc                            |             |  |  |

| 12                                | NIC1 Active |  |  |

## NIC2 LED

The NIC2 (Network Interface Controller) LED connection is located on pins 9 and 10 of JF1. Attach the NIC2 LED cable to display network activity. Refer to the table on the right for pin definitions.

| NIC2 LED<br>Pin Definitions (JF1) |             |  |  |

|-----------------------------------|-------------|--|--|

| Pin# Definition                   |             |  |  |

| 9                                 | Vcc         |  |  |

| 10                                | NIC2 Active |  |  |

# Overheat/Fan Fail LED

Connect an LED to the OH connection on pins 7 and 8 of JF1 to provide advanced warning of chassis overheating. Refer to the table on the right for pin definitions.

| OH/Fan Fail LED<br>Pin Definitions (JF1) |            |  |  |  |

|------------------------------------------|------------|--|--|--|

| Pin#                                     | Definition |  |  |  |

| 7                                        | Vcc        |  |  |  |

| 8                                        | Control    |  |  |  |

# **Power Fail LED**

The Power Fail LED connection is located on pins 5 and 6 of JF1. Refer to the table on the right for pin definitions. This feature is only available for systems with redundant power supplies.

| Power Fail LED<br>Pin Definitions (JF1) |         |  |  |

|-----------------------------------------|---------|--|--|

| Pin# Definition                         |         |  |  |

| 5                                       | Vcc     |  |  |

| 6                                       | Control |  |  |

#### Reset Button

The Reset Button connection is located on pins 3 and 4 of JF1. Attach it to the hardware reset switch on the computer case. Refer to the table on the right for pin definitions.

| Reset Button<br>Pin Definitions (JF1) |        |  |  |

|---------------------------------------|--------|--|--|

| Pin# Definition                       |        |  |  |

| 3                                     | Reset  |  |  |

| 4                                     | Ground |  |  |

## **Power Button**

The Power Button connection is located on pins 1 and 2 of JF1. Momentarily contacting both pins will power on/off the system. This button can also be configured to function as a suspend button (see the Power Button Mode setting in BIOS). To turn off the power when set to suspend mode, depress the button for at least 4 seconds. Refer to the table on the right for pin definitions.

| Power Button<br>Pin Definitions (JF1) |        |  |  |

|---------------------------------------|--------|--|--|

| Pin# Definition                       |        |  |  |

| 1                                     | PW_ON  |  |  |

| 2                                     | Ground |  |  |

# Universal Serial Bus Ports (USB0/1)

Two Universal Serial Bus ports (USB1.1) are located beside the keyboard/mouse ports. See the table on the right for pin definitions.

| Universal Serial Bus Ports<br>Pin Definitions (USB0/1) |        |     |        |  |

|--------------------------------------------------------|--------|-----|--------|--|

| USB0 USB1 Pin # Definition Pin # Definition            |        |     |        |  |

| 1                                                      | +5V    | 1   | 1 +5V  |  |

| 2 PO- 2 PO-                                            |        | PO- |        |  |

| 3 PO+                                                  |        | 3   | PO+    |  |

| 4                                                      | Ground | 4   | Ground |  |

#### Chassis Intrusion

A Chassis Intrusion header is located at JL1. Attach the appropriate cable to inform you of a chassis intrusion.

| Chassis Intrusion Pin Definitions (JL1) |                 |  |  |

|-----------------------------------------|-----------------|--|--|

| Pin# Definition                         |                 |  |  |

| 1                                       | Intrusion Input |  |  |

| 2                                       | Ground          |  |  |

#### **Serial Ports**

The COM1 serial port is located beside the VGA port. COM2 is a header on the serverboard located near the BIOS chip (see serverboard layout for location). See the table on the right for pin definitions.

| Serial Port Pin Definitions<br>(COM1/COM2) |        |    |     |  |  |

|--------------------------------------------|--------|----|-----|--|--|

| Pin # Definition Pin # Definition          |        |    |     |  |  |

| 1                                          | DCD    | 6  | DSR |  |  |

| 2                                          | RXD    | 7  | RTS |  |  |

| 3                                          | TXD    | 8  | CTS |  |  |

| 4                                          | DTR    | 9  | RI  |  |  |

| 5                                          | Ground | 10 | NC  |  |  |

**Note:** Pin 10 is included on the header but not on the port. NC indicates no connection.

# Power Fail and Alarm Reset Header

Connect a cable from your power supply to the JP10 header to provide you with warning of a power supply failure. The warning signal is passed through the PWR\_LED pin to indicate a power failure. See the table on the right for pin definitions.

# Power Fail/Alarm Reset Header Pin Definitions (JP10) Pin# Definition 1 P/S 1 Fail Signal 2 P/S 2 Fail Signal 3 P/S 3 Fail Signal 4 Reset (from MB)

**Note:** This feature is only available when using redundant power supplies.

## **Fan Headers**

The H8DA8/H8DAE has eight fan headers (FAN1-FAN8) and the H8DAR-8/H8DAR-i has five fan headers (FAN1-FAN5). Fan speed is controlled with a BIOS setting. See the table on the right for pin definitions. **Note:** the H8DAR-8 and H8DAR-i have 3-pin fan headers. Pin 4 on the table is not included on these headers.

| Fan Header<br>Pin Definitions<br>(FAN1-8) |                |  |  |

|-------------------------------------------|----------------|--|--|

| Pin# Definition                           |                |  |  |

| 1                                         | Ground (Black) |  |  |

| 2                                         | +12V (Red)     |  |  |

| 3                                         | 3 Tachometer   |  |  |

| 4 PWM Control                             |                |  |  |

# JLAN1/2 (Ethernet Ports)

Two Gigabit Ethernet ports (designated JLAN1 and JLAN2) are located beside the VGA port. These ports accept RJ45 type cables.

#### **Extra USB Headers**

Three additional USB1.1 headers (USB2/3/4) are included on the serverboard. These may be connected to provide front side access. A USB cable (not included) is needed for the connection. See the table on the right for pin definitions.

| Ex                                            | Extra Universal Serial Bus Headers<br>Pin Definitions (USB2/3/4) |   |               |  |

|-----------------------------------------------|------------------------------------------------------------------|---|---------------|--|

| USB2 USB3/4 Pin # Definition Pin # Definition |                                                                  |   |               |  |

| 1                                             | +5V                                                              | 1 | +5V           |  |

| 2                                             | PO-                                                              | 2 | PO-           |  |

| 3                                             | PO+                                                              | 3 | PO+           |  |

| 4                                             | Ground                                                           | 4 | Ground        |  |

| 5                                             | Key                                                              | 5 | No connection |  |

# Power LED/Speaker

On JD1, pins 1, 2, and 3 are for the power LED and pins 4 through 7 are for the speaker. See the tables on the right for pin definitions.

**Note:** The speaker connector pins are for use with an external speaker. If you wish to use the onboard speaker, you should close pins 6 and 7 with a jumper.

| PWR LED Connector<br>Pin Definitions (JD1) |            |  |

|--------------------------------------------|------------|--|

| Pin#                                       | Definition |  |

| 1                                          | +Vcc       |  |

| 2                                          | -Vcc       |  |

| 3                                          | -Vcc       |  |

| Speaker Connector<br>Pin Definitions (JD1) |                        |  |

|--------------------------------------------|------------------------|--|

| Pin#                                       | Definition             |  |

| 4                                          | Red wire, Speaker data |  |

| 5                                          | No connection          |  |

| 6                                          | Buzzer signal          |  |

| 7                                          | Speaker data           |  |

# ATX PS/2 Keyboard and PS/2 Mouse Ports

The ATX PS/2 keyboard and the PS/2 mouse ports are located at J101. See the table on the right for pin definitions.

| PS/2 Keyboard and<br>Mouse Port Pin<br>Definitions (J101) |            |  |

|-----------------------------------------------------------|------------|--|

| Pin#                                                      | Definition |  |

| 1                                                         | Data       |  |

| 2                                                         | NC         |  |

| 3                                                         | Ground     |  |

| 4                                                         | vcc        |  |

| 5                                                         | Clock      |  |

| 6                                                         | NC         |  |

# Wake-On-LAN

The Wake-On-LAN header is designated JWOL. See the table on the right for pin definitions. You must have a LAN card with a Wake-On-LAN connector and cable to use the Wake-On-LAN feature.

| Wake-On-LAN<br>Pin Definitions<br>(JWOL) |             |  |

|------------------------------------------|-------------|--|

| Pin#                                     | Definition  |  |

| 1                                        | +5V Standby |  |

| 2                                        | Ground      |  |

| 3                                        | Wake-up     |  |

# Wake-On-Ring

The Wake-On-Ring header is designated JWOR. This function allows your computer to receive and "wake-up" by an incoming call to the modem when in suspend state. See the table on the right for pin definitions. You must have a Wake-On-Ring card and cable to use this feature.

| Wake-On-Ring<br>Pin Definitions<br>(JWOR) |                |  |

|-------------------------------------------|----------------|--|

| Pin#                                      | Definition     |  |

| 1                                         | Ground (Black) |  |

| 2                                         | Wake-up        |  |

# SMB Power (I<sup>2</sup>C) Header

The header at J24 is for I<sup>2</sup>C, which may be used to monitor the status of the power supply, fans and system temperature. See the table on the right for pin definitions.

| SMB Power (I <sup>2</sup> C)<br>Pin Definitions (J24) |            |  |

|-------------------------------------------------------|------------|--|

| Pin#                                                  | Definition |  |

| 1                                                     | Clock      |  |

| 2                                                     | Data       |  |

| 3                                                     | N/A        |  |

| 4                                                     | N/A        |  |

| 5                                                     | N/A        |  |

#### SMB Header

The System Management Bus header is located at J22. Connect the appropriate cable here to utilize SMB on your system. See the table on the right for pin definitions.

| SMB<br>Pin Definitions (J22) |            |  |

|------------------------------|------------|--|

| Pin#                         | Definition |  |

| 1                            | SMB Data   |  |

| 2                            | Ground     |  |

| 3                            | SMB Clock  |  |

| 4                            | N/A        |  |

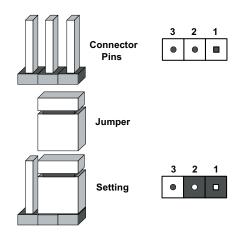

# 2-7 Jumper Settings

# **Explanation of Jumpers**

To modify the operation of the serverboard, jumpers can be used to choose between optional settings. Jumpers create shorts between two pins to change the function of the connector. Pin 1 is identified with a square solder pad on the printed circuit board. See the diagram at right for an example of jumping pins 1 and 2. Refer to the serverboard layout page for jumper locations.

**Note 1:** On two-pin jumpers, "Closed" means the jumper is on and "Open" means the jumper is off the pins.

#### **CMOS Clear**

JBT1 is used to clear CMOS and will also clear any passwords. Instead of pins, this jumper consists of contact pads to prevent accidentally clearing the contents of CMOS.

To clear CMOS.

- 1) First power down the system and unplug the power cord(s).

- 2) With the power disconnected, short the CMOS pads with a metal object such as a small screwdriver for at least four seconds.

- 3) Remove the screwdriver (or shorting device).

- 4) Reconnect the power cord(s) and power on the system.

# Notes:

# Do not use the PW ON connector to clear CMOS.

The onboard battery does not need to be removed when clearing CMOS, however you must short JBT1 for at least four seconds.

#### JLAN1/2 Enable/Disable

Change the setting of jumper JPL to enable or disable the JLAN1 and JLAN2 Gb Ethernet ports. See the table on the right for jumper settings. The default setting is enabled

| JLAN1/2 Enable/Disable<br>Jumper Settings (JPL) |            |

|-------------------------------------------------|------------|

| Jumper Setting                                  | Definition |

| Pins 1-2                                        | Enabled    |

| Pins 2-3                                        | Disabled   |

#### VGA Enable/Disable

JPG1 allows you to enable or disable the VGA port. The default position is on pins 1 and 2 to enable VGA. See the table on the right for jumper settings.

| VGA Enable/Disable<br>Jumper Settings (JPG1) |            |

|----------------------------------------------|------------|

| Jumper Setting                               | Definition |

| Pins 1-2 Enabled                             |            |

| Pins 2-3 Disabled                            |            |

#### I<sup>2</sup>C to PCI Enable/Disable

JI<sup>2</sup>C1/2 pair of jumpers allow you to connect the System Management Bus to any one of the PCI slots. The default setting is closed (on) for both jumpers to enable the connection. Both connectors must have the same setting (JI<sup>2</sup>C1 is for data and JI<sup>2</sup>C2 is for the clock). See the table on right for jumper settings.

| I <sup>2</sup> C to PCI Enable/Disable<br>Jumper Settings<br>(JI <sup>2</sup> C1/2) |  |  |  |

|-------------------------------------------------------------------------------------|--|--|--|

| Jumper Setting Definition                                                           |  |  |  |

| Closed Enabled                                                                      |  |  |  |

| Open Disabled                                                                       |  |  |  |

## SCSI Controller Enable/ Disable (H8DA8/H8DAR-8)

Jumper JPA1 is used to enable or disable the Adaptec SCSI controller. The default setting is on pins 1-2 to enable SCSI. See the table on right for jumper settings.

| SCSI Enable/Disable<br>Jumper Settings (JPA1) |            |  |

|-----------------------------------------------|------------|--|

| Both Jumpers                                  | Definition |  |

| Pins 1-2                                      | Enabled    |  |

| Pins 2-3                                      | Disabled   |  |

## SCSI Termination Enable/ Disable (H8DA8/H8DAR-8)

Jumper JPA2 and JPA3 are used to enable or disable termination for the SCSI Channel A and B connectors, respectively. The default setting for both is open to enable termination. See the table on right for jumper settings.

**Note:** In order for the SCSI drives to function properly, please do not change the default setting (enabled) set by the manufacturer.

| 3rd | Power   | Supply | Fail | Signal |

|-----|---------|--------|------|--------|

| Ena | ble/Dis | sable  |      |        |

The system can notify you in the event of a power supply failure. This feature assumes that three redundant power supply units are installed in the chassis. If you only have one or two power supplies installed, you should disable the function with the J3P header to prevent false alarms. See the table on the right for jumper settings.

| Watch | Dog | <b>Enab</b> | le/D | isabl | e |

|-------|-----|-------------|------|-------|---|

JWD controls the Watch Dog function. Watch Dog is a system monitor that can reboot the system when a software application hangs. Pins 1-2 will cause WD to reset the system if an application has frozen. Pins 2-3 will generate a non-maskable interrupt signal for the application that is frozen. See the table on the right for jumper settings. Watch Dog must also be enabled in BIOS.

| SCSI Term. Enable/Disable<br>Jumper Settings (JPA2/JPA3) |            |  |

|----------------------------------------------------------|------------|--|

| Jumper Setting                                           | Definition |  |

| Open                                                     | Enabled    |  |

| Closed                                                   | Disabled   |  |

| 3rd Power Supply Fail Signal<br>Jumper Settings (J3P) |         |

|-------------------------------------------------------|---------|

| Jumper Setting Definition                             |         |

| Open                                                  | Enabled |

| Closed Disabled                                       |         |

| Watch Dog<br>Jumper Settings (JWD) |       |

|------------------------------------|-------|

| Jumper Setting Definition          |       |

| Pins 1-2                           | Reset |

| Pins 2-3 NMI                       |       |

| Open Disabled                      |       |

**Note:** When enabled, the user needs to write their own application software in order to disable the Watch Dog Timer.

# Onboard Speaker Enable/ Disable

The JD1 header allows you to use either an external speaker or the internal (onboard) speaker. For an onboard speaker, close pins 6 and 7 with a jumper. For an external speaker, connect the speaker wires to pins 4 through 7. See the table on the right for settings and the Power LED/Speaker table (previous section) for pin definitions.

| Onboard Speaker Enable/Disable<br>Jumper Settings (JD1) |                               |  |

|---------------------------------------------------------|-------------------------------|--|

| Pins Definition                                         |                               |  |

| 6-7 Jump for onboard speaker                            |                               |  |

| 4-7                                                     | Attach external speaker wires |  |

#### **PCI-X Slot Speed**

Jumpers JPXA0 and JPXB0 on the H8DA8/H8DAE can be used to change the speed of PCI-X slots 3 and 4 and PCI-X slots 5 and 6, respectively. On the H8DAR-8/H8DAR-i, jumper JPXB0 can be used to change the speed of PCI-X slot 6. See the tables on the right for jumper settings.

| H8DA8/H8DAE: PCI-X Slot Speed<br>Jumper Settings (JPXA0/JPXB0) |              |  |

|----------------------------------------------------------------|--------------|--|

| Jumper Setting Definition                                      |              |  |

| Open                                                           | Auto         |  |

| Pins 1-2                                                       | PCI-X 66 MHz |  |

| Pins 2-3                                                       | PCI 66 MHz   |  |

Note: JPXA0 controls the speed for PCI-X slots #3 and #4 and JPXB0 controls the speed for PCI-X slots #5 and #6. The default setting for both is Auto.

| H8DAR-8/H8DAR-i: PCI-X Slot Speed<br>Jumper Settings (JPXB0) |              |

|--------------------------------------------------------------|--------------|

| Jumper Setting Definition                                    |              |

| Open                                                         | Auto         |

| Pins 1-2                                                     | PCI-X 66 MHz |

| Pins 2-3                                                     | PCI 66 MHz   |

**Note:** JPXB0 controls the speed for PCI-X slot #6. The default setting is Auto.

## 2-8 Onboard Indicators

#### JLAN1/JLAN2 LEDs

The Ethernet ports (located beside the VGA port) have two LEDs. One LED indicates activity while the other may be green, amber or off to indicate the speed of the connection. See the table on the right for the functions associated with the connection speed LED.

| JLAN LED<br>(Connection Speed Indicator) |        |  |

|------------------------------------------|--------|--|

| LED Color Definition                     |        |  |

| Off                                      | 10 MHz |  |

| Green 100 MHz                            |        |  |

| Amber 1 GHz                              |        |  |

#### +3.3V Power LED

When illuminated, the DP1 LED indicates that power from the power supply is being supplied to the serverboard (DP1 indicates the presence of +3.3V). See the table on the right for DP1 LED states.

|       | +3.3V Power LED<br>(DP1)        |

|-------|---------------------------------|

| Color | System Status                   |

| Green | Power present on serverboard    |

| Off   | No power present on serverboard |

## 2-9 Floppy, IDE and SCSI Drive Connections

Use the following information to connect the floppy and hard disk drive cables.

- The floppy disk drive cable has seven twisted wires.

- A red mark on a wire typically designates the location of pin 1.

- A single floppy disk drive ribbon cable has 34 wires and two connectors to provide for two floppy disk drives. The connector with twisted wires always connects to drive A, and the connector that does not have twisted wires always connects to drive B.

- The 80-wire ATA133 IDE hard disk drive cable that came with your system has two connectors to support two drives. This special cable should be used to take advantage of the speed this new technology offers. The blue connector connects to the onboard IDE connector interface and the other connector(s) to your hard drive(s). Consult the documentation that came with your disk drive for details on actual jumper locations and settings for the hard disk drive.

## **Floppy Connector**

The floppy connector is located beside the IDE#2 connector. See the table on the right for pin definitions.

| Floppy Drive Connector<br>Pin Definitions (JFDD1) |            |      |                 |

|---------------------------------------------------|------------|------|-----------------|

| Pin#                                              | Definition | Pin# | Definition      |

| 1                                                 | GND        | 2    | FDHDIN          |

| 3                                                 | GND        | 4    | Reserved        |

| 5                                                 | Key        | 6    | FDEDIN          |

| 7                                                 | GND        | 8    | Index-          |

| 9                                                 | GND        | 10   | Motor Enable    |

| 11                                                | GND        | 12   | Drive Select B- |

| 13                                                | GND        | 14   | Drive Select A- |

| 15                                                | GND        | 16   | Motor Enable    |

| 17                                                | GND        | 18   | DIR-            |

| 19                                                | GND        | 20   | STEP-           |

| 21                                                | GND        | 22   | Write Data-     |

| 23                                                | GND        | 24   | Write Gate-     |

| 25                                                | GND        | 26   | Track 00-       |

| 27                                                | GND        | 28   | Write Protect-  |

| 29                                                | GND        | 30   | Read Data-      |

| 31                                                | GND        | 32   | Side 1 Select-  |

| 33                                                | GND        | 34   | Diskette        |

## **IDE Connectors**

There are no jumpers to configure the onboard IDE#1 and #2 connectors. See the table on the right for pin definitions.

| IDE Drive Connectors Pin Definitions (JIDE#1/JIDE#2) |               |      |               |

|------------------------------------------------------|---------------|------|---------------|

| Pin#                                                 | Definition    | Pin# | Definition    |

| 1                                                    | Reset IDE     | 2    | Ground        |

| 3                                                    | Host Data 7   | 4    | Host Data 8   |

| 5                                                    | Host Data 6   | 6    | Host Data 9   |

| 7                                                    | Host Data 5   | 8    | Host Data 10  |

| 9                                                    | Host Data 4   | 10   | Host Data 11  |

| 11                                                   | Host Data 3   | 12   | Host Data 12  |

| 13                                                   | Host Data 2   | 14   | Host Data 13  |

| 15                                                   | Host Data 1   | 16   | Host Data 14  |

| 17                                                   | Host Data 0   | 18   | Host Data 15  |

| 19                                                   | Ground        | 20   | Key           |

| 21                                                   | DRQ3          | 22   | Ground        |

| 23                                                   | I/O Write     | 24   | Ground        |

| 25                                                   | I/O Read      | 26   | Ground        |

| 27                                                   | IOCHRDY       | 28   | BALE          |

| 29                                                   | DACK3         | 30   | Ground        |

| 31                                                   | IRQ14         | 32   | IOCS16        |

| 33                                                   | Addr1         | 34   | Ground        |

| 35                                                   | Addr0         | 36   | Addr2         |

| 37                                                   | Chip Select 0 | 38   | Chip Select 1 |

| 39                                                   | Activity      | 40   | Ground        |

# SCSI Connectors (H8DA8/H8DAR-8)

Refer to the table at right for pin definitions for the Ultra320 SCSI connectors located at JA1 and JB2.

|      | Ultra320 SCSI Drive Connectors<br>Pin Definitions (JA1/JB2) |      |            |

|------|-------------------------------------------------------------|------|------------|

| Pin# | Definition                                                  | Pin# | Definition |

| 1    | +DB (12)                                                    | 35   | -DB (12)   |

| 2    | +DB (13)                                                    | 36   | -DB (13)   |

| 3    | +DB (14)                                                    | 37   | -DB (14)   |

| 4    | +DB (15)                                                    | 38   | -DB (15)   |

| 5    | +DB (P1)                                                    | 39   | -DB (P1)   |

| 6    | +DB (0)                                                     | 40   | -DB (0)    |

| 7    | +DB (1)                                                     | 41   | -DB (1)    |

| 8    | +DB (2)                                                     | 42   | -DB (2)    |

| 9    | +DB (3)                                                     | 43   | -DB (3)    |

| 10   | +DB (4)                                                     | 44   | -DB (4)    |

| 11   | +DB (5)                                                     | 45   | -DB (5)    |

| 12   | +DB (6)                                                     | 46   | -DB (6)    |

| 13   | +DB (7)                                                     | 47   | -DB (7)    |

| 14   | +DB (P)                                                     | 48   | -DB (P)    |

| 15   | Ground                                                      | 49   | Ground     |

| 16   | DIFFSENS                                                    | 50   | Ground     |

| 17   | TERMPWR                                                     | 51   | TERMPWR    |

| 18   | TERMPWR                                                     | 52   | TERMPWR    |

| 19   | Reserved                                                    | 53   | Reserved   |

| 20   | Ground                                                      | 54   | Ground     |

| 21   | +ATN                                                        | 55   | -ATN       |

| 22   | Ground                                                      | 56   | Ground     |

| 23   | +BSY                                                        | 57   | -BSY       |

| 24   | +ACK                                                        | 58   | -ACK       |

| 25   | +RST                                                        | 59   | -RST       |

| 26   | +MSG                                                        | 60   | -MSG       |

| 27   | +SEL                                                        | 61   | -SEL       |

| 28   | +C/D                                                        | 62   | -C/D       |

| 29   | +REQ                                                        | 63   | -REQ       |

| 30   | +I/O                                                        | 64   | -I/O       |

| 31   | +DB (8)                                                     | 65   | -DB (8)    |

| 32   | +DB (9)                                                     | 66   | -DB (9)    |

| 33   | +DB (10)                                                    | 67   | -DB (10)   |

| 34   | +DB (11)                                                    | 68   | -DB (11)   |

# Notes

## **Chapter 3**

## **Troubleshooting**

## 3-1 Troubleshooting Procedures

Use the following procedures to troubleshoot your system. If you have followed all of the procedures below and still need assistance, refer to the 'Technical Support Procedures' and/or 'Returning Merchandise for Service' section(s) in this chapter. Always disconnect the AC power cord before adding, changing or installing any hardware components.

#### **Before Power On**

- 1. Check that the onboard Power LED is lit (DP1 on the serverboard).

- 2. Make sure that the 8-pin 12v power connector at JPW2 is connected to your power supply.

- 3. Make sure that no short circuits exist between the serverboard and chassis.

- 4. Disconnect all ribbon/wire cables from the serverboard, including those for the keyboard and mouse.

- 5. Remove all add-on cards.

- 6. Install a CPU and heatsink (making sure it is fully seated) and connect the chassis speaker and the power LED to the serverboard. Check all jumper settings as well.

- 7. Use the correct type of onboard CMOS battery as recommended by the manufacturer. To avoid possible explosion, do not install the CMOS battery upside down.

#### No Power

- 1. Make sure that no short circuits exist between the serverboard and the chassis.

- 2. Verify that all jumpers are set to their default positions.

- 3. Check that the 115V/230V switch on the power supply is properly set.

- 4. Turn the power switch on and off to test the system.

- 5. The battery on your serverboard may be old. Check to verify that it still supplies ~3VDC. If it does not, replace it with a new one.

#### No Video

- 1. If the power is on but you have no video, remove all the add-on cards and cables.

- 2. Use the speaker to determine if any beep codes exist. Refer to Appendix A for details on beep codes.

#### NOTE