# Intel® Xeon Phi™ Coprocessor x100 Product Family

**Datasheet**

**April 2015**

By using this document, in addition to any agreements you have with Intel, you accept the terms set forth below.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: <a href="http://www.intel.com/design/literature.htm">http://www.intel.com/design/literature.htm</a>

This document contains information on products in the design phase of development.

All products, computer systems, dates and figures specified are preliminary based on current expectations, and are subject to change without notice.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families: Go to: <u>Learn About Intel® Processor Numbers</u>

Document ID Number: 328209 004EN

Intel, Xeon, Xeon Phi, and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others.

Copyright © 2012, 2013 and 2014, Intel Corporation. All rights reserved.

## **Table of Contents**

| 1 | Intro                                   | luction                                                                         |   |

|---|-----------------------------------------|---------------------------------------------------------------------------------|---|

|   | 1.1                                     | Reference Documentation                                                         | 7 |

|   | 1.2                                     | Conventions and Terminology                                                     | 7 |

|   |                                         | 1.2.1 Terminology                                                               | 7 |

| 2 | Turka                                   | © Xeon Phi™ Coprocessor Architecture                                            | ` |

| 2 |                                         |                                                                                 |   |

|   | 2.1                                     | Intel® Xeon Phi™ Coprocessor Product Overview                                   |   |

|   |                                         | 2.1.1 Intel® Xeon Phi™ Coprocessor Board Design                                 |   |

|   |                                         | 2.1.2 System Management Controller (SMC)                                        |   |

|   |                                         | 2.1.3 Intel® Xeon Phi™ Coprocessor Silicon                                      |   |

|   |                                         | 2.1.4 Intel® Xeon Phi™ Coprocessor Product Family                               |   |

|   |                                         | 2.1.5 Intel® Xeon Phi™ Coprocessor 7120D/5120D(Dense Form Factor)               | 3 |

| 3 | Ther                                    | nal and Mechanical Specification15                                              | 5 |

|   | 3.1                                     | Mechanical Specifications                                                       |   |

|   | 3.2                                     | Intel® Xeon Phi™ Coprocessor Thermal Specification                              |   |

|   | 0                                       | 3.2.1 Intel® Xeon Phi™ Coprocessor Thermal Management                           |   |

|   | 3.3                                     | Intel® Xeon Phi™ Coprocessor Thermal Solutions                                  |   |

|   | 5.5                                     | 3.3.1 3120A and 7120A Active Cooling Solution                                   |   |

|   |                                         | 3.3.2 7120P/SE10P/5110P/3120P/31S1P Passive Cooling Solution                    |   |

|   | 3.4                                     | Cooling Solution Guidelines for SE10X/7120X and 7120D/5120D                     |   |

|   | • • • • • • • • • • • • • • • • • • • • | 3.4.1 Thermal Considerations                                                    |   |

|   |                                         | 3.4.2 Thermal Profile and Cooling                                               |   |

|   |                                         | 3.4.3 Mechanical Considerations                                                 |   |

|   |                                         | 3.4.4 Mechanical Shock and Vibration Testing                                    |   |

|   | 3.5                                     | Intel® Xeon Phi™ Coprocessor PCI Express* Card Extender Bracket Installation 40 |   |

|   | 0.0                                     | 3.5.1 Bracket Installation Steps                                                |   |

|   |                                         | ·                                                                               |   |

| 4 |                                         | © Xeon Phi™ Coprocessor Pin Descriptions                                        |   |

|   | 4.1                                     | PCI Express* Signals                                                            |   |

|   | 4.3                                     | 4.1.1 PROCHOT_N (Pin B12)                                                       |   |

|   | 4.2                                     | Supplemental Power Connector(s)                                                 |   |

|   | 4.3                                     | Dense Form Factor (5120D) Edge Connector Pins                                   |   |

|   |                                         | 4.3.1 Baseboard Requirements of 5120D                                           |   |

|   |                                         | 4.3.2 AC Coupling on 5120D Data Pins                                            | L |

| 5 | Pow                                     | r Specification and Management53                                                | 3 |

|   | 5.1                                     | 5110P SKU Power Options53                                                       | 3 |

|   | 5.2                                     | Intel® Xeon Phi™ Coprocessor Power States54                                     | 1 |

|   | 5.3                                     | P-states and Turbo Mode57                                                       |   |

| 6 | Man                                     | geability61                                                                     | 1 |

| U | 6.1                                     | Intel® Xeon Phi™ Coprocessor Manageability Architecture                         |   |

|   |                                         |                                                                                 |   |

|   | 6.2                                     | System Management Controller (SMC)                                              |   |

|   | 6.3                                     | General SMC Features and Capabilities                                           |   |

|   | <i>c</i> 4                              | 6.3.1 Catastrophic Shutdown Detection                                           |   |

|   | 6.4                                     | Host / In-Band Management Interface (SCIF)                                      |   |

|   | 6.5                                     | System and Power Management                                                     |   |

|   | 6.6                                     | Out of Band / PCI Express* SMBus / IPMB Management Capabilities                 |   |

|   |                                         | 6.6.1 IPMB Protocol                                                             |   |

|   |                                         | 6.6.2 Polled Master-Only Protocol                                               |   |

|   | c =                                     | 6.6.3 Supported IPMI Commands                                                   |   |

|   | 6.7                                     | SMC LED_ERROR and Fan PWM                                                       | ኃ |

## **List of Figures**

| 2-1  | Intel® Xeon Phi <sup>™</sup> Coprocessor Board Schematic                                                | . 9 |

|------|---------------------------------------------------------------------------------------------------------|-----|

| 2-2  | Intel® Xeon Phi <sup>™</sup> Coprocessor Board Top side (for reference only)                            | 11  |

| 2-3  | Intel® Xeon Phi™ Coprocessor Board, Back side (reference only)                                          |     |

| 2-4  | Intel® Xeon Phi™ Coprocessor Silicon Layout                                                             |     |

| 2-5  | 7120D/5120D Dense Form Factor, Topside                                                                  |     |

| 3-1  | Location of Mounting Holes on the Intel® Xeon Phi™ Coprocessor Card (in mils)                           |     |

| 3-2  | Dimensions of the Intel® Xeon Phi™ Coprocessor Card (in mils)                                           |     |

| 3-3  | Entering and Exiting Thermal Throttling (PROCHOT)                                                       |     |

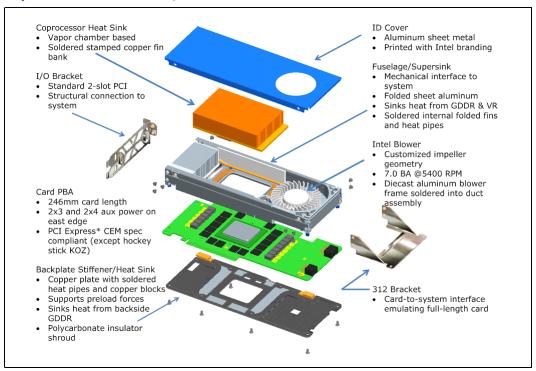

| 3-4  | Exploded View of 3120A / 7120A Active Solution                                                          |     |

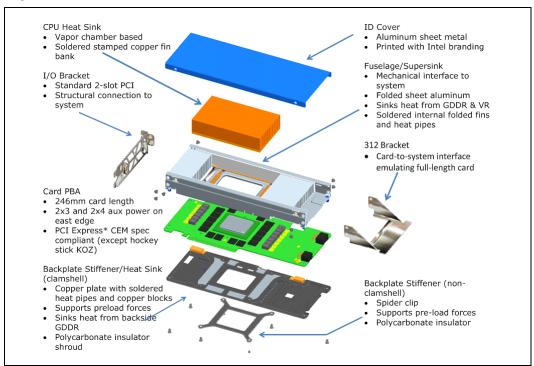

| 3-5  | Exploded View of Passive Thermal Solution                                                               |     |

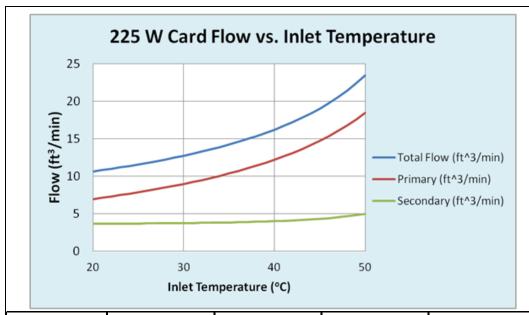

| 3-6  | Airflow Requirement vs. 45oC Inlet Temperature for the 5110P at 225W TDP                                | 23  |

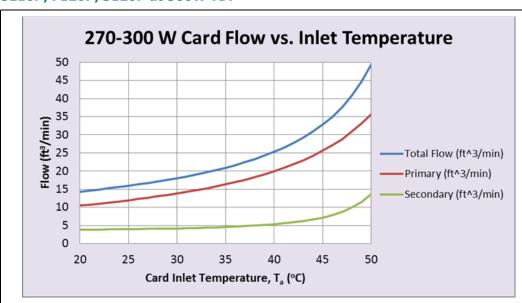

| 3-7  | Airflow Requirement vs. Inlet Temperature for the 31S1P at 270W TDP and SE10P/7120P/3120P at 300W TDP24 |     |

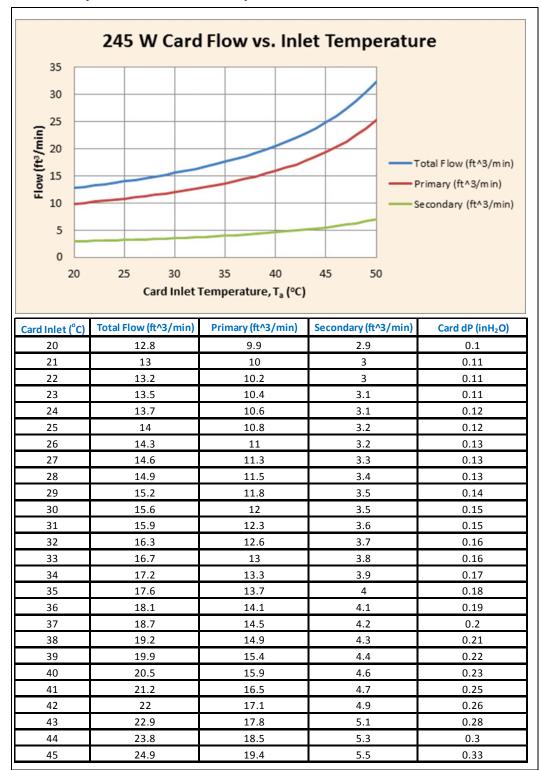

| 3-8  | Airflow Requirement vs. Inlet Temperature for the 5110P Card at 245W TDP                                | 25  |

| 3-9  | SE10X/7120X Power Profile for Coprocessor Intensive Workload (all values in Watts)                      |     |

| 3-10 | SE10X/7120X Power Profile for Memory Intensive Workload (all values in Watts)                           |     |

| 3-11 | 5120D Power Profile: Coprocessor Centric (all values in Watts)                                          |     |

| 3-12 | 5120D Power Profile: Memory Centric (all values in Watts)                                               |     |

| 3-13 | 7120D Power Profile: Coprocessor Centric (all values in Watts)                                          |     |

| 3-14 | 7120D Power Profile: Memory Centric (all values in Watts)                                               |     |

| 3-15 | 7120D/5120D VR Thermal Sensors for Custom Cooling Consideration                                         |     |

| 3-16 | SE10X/7120X SKU Coprocessor Junction Temperature (Tjunction) vs Power                                   |     |

| 3-17 | SE10X/7120X SKU Coprocessor Case Temperature (Tcase) vs Power                                           |     |

| 3-18 | SE10X/7120X Board Top Side                                                                              |     |

| 3-19 | SE10X/7120X Board Bottom Side                                                                           |     |

| 3-20 | 7120D/5120D Board Top Side                                                                              |     |

| 3-21 | 7120D/5120D Board Bottom Side                                                                           |     |

| 3-22 | Contents of Intel® Xeon Phi™ Coprocessor Package Shipment                                               |     |

| 3-23 | Overlap Lid                                                                                             |     |

| 3-24 | Clearance Lid                                                                                           | 41  |

| 3-25 | Overlap Lid Removal                                                                                     | 42  |

| 3-26 | Tilt Overlap Lid and Slide as shown to Disengage Tabs                                                   | 42  |

| 3-27 | OEM Bracket Installation                                                                                |     |

| 3-28 | OEM Bracket Installation                                                                                | 43  |

| 3-29 | Replace Lid on "Overlap Lid" Units                                                                      | 44  |

| 3-30 | Replace Lid on "Overlap Lid" Units (cont.)                                                              |     |

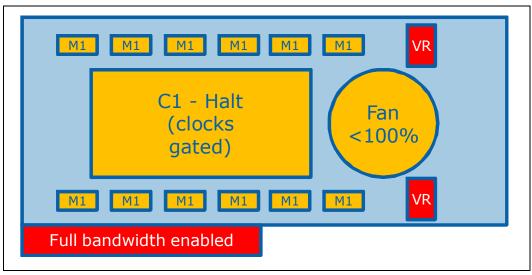

| 5-1  | Coprocessor in C0-state and Memory in M0-state                                                          |     |

| 5-2  | Some cores are in C0-state and other cores in C1-state; Memory in M0-state                              | 55  |

| 5-3  | All Cores In C1 state; Memory In M1 state                                                               | 55  |

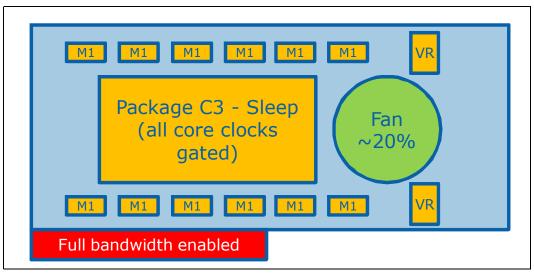

| 5-4  | All Cores In Package-C3 State; Memory In M1                                                             | 56  |

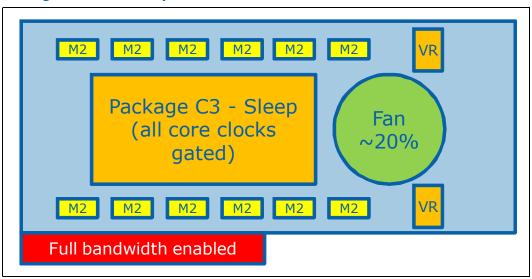

| 5-5  | Package-C3 and Memory M2 state                                                                          | 56  |

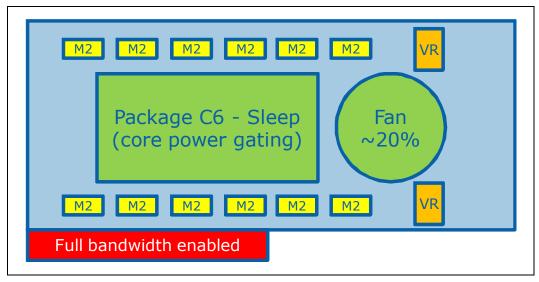

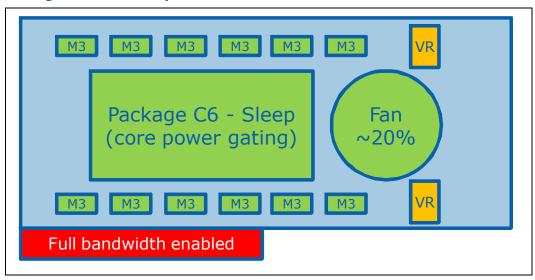

| 5-6  | Package-C6 and Memory M2 state                                                                          | 57  |

| 5-7  | Package-C6 and Memory M3 state                                                                          | 57  |

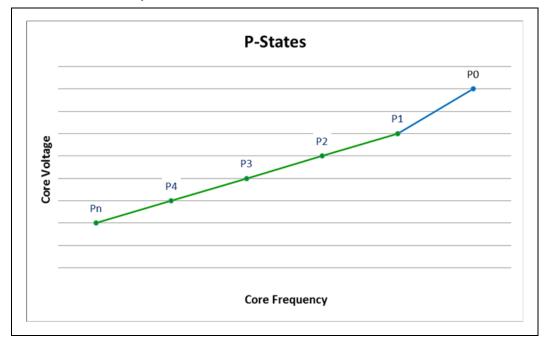

| 5-8  | Intel® Xeon Phi™ coprocessor P-States and Turbo                                                         | 59  |

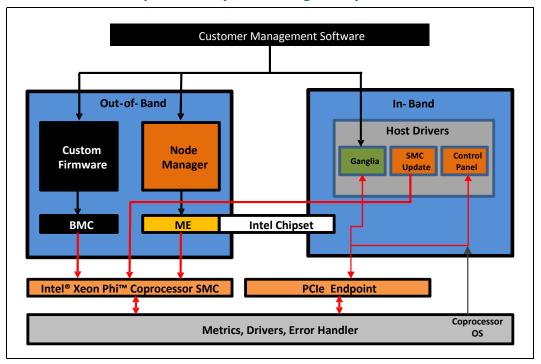

| 6-1  | Intel® Xeon Phi™ Coprocessor System Manageability Architecture                                          | 62  |

| 6-1  | Write Block Command Diagram                                                                             | 68  |

| 6-2  | Read Block Command Diagram                                                                              | 69  |

## **List of Tables**

| 1-1  | Related Documents                                                  | 7    |

|------|--------------------------------------------------------------------|------|

| 1-2  | General Terminology                                                | 7    |

| 2-1  | Intel® Xeon Phi™ Coprocessor Product Family                        | . 13 |

| 3-1  | Intel® Xeon Phi™ Coprocessor Mechanical Specification              | . 15 |

| 3-2  | Intel® Xeon Phi™ Coprocessor Thermal Specification                 | 18   |

| 3-3  | Component Thermal Specification on SE10X/7120X and 7120D/5120D     | 32   |

| 3-4  | Board Component Heights                                            | 35   |

| 3-5  | Dynamic Load Shift Specification                                   | . 39 |

| 4-1  | PCI Express* Connector Signals on the Intel® Xeon Phi™ Coprocessor | 45   |

| 4-2  | 5120D (DFF) SKU Pinout                                             | 48   |

| 4-3  | 51xxD Power Rail Requirements on Baseboard                         | . 51 |

| 5-1  | Intel® Xeon Phi™ Coprocessor Power States                          | . 53 |

| 6-1  | SMBus Write Commands                                               | 68   |

| 6-2  | Miscellaneous Command Details                                      | 69   |

| 6-3  | FRU Related Command Details                                        | 69   |

| 6-4  | SDR Related Command Details                                        | . 70 |

| 6-5  | SEL Related Command Details                                        |      |

| 6-6  | Sensor Related Command Details                                     |      |

| 6-7  | General Command Details                                            |      |

| 6-8  | CPU Package Config Read Request Format                             | . 71 |

| 6-9  | CPU Package Config Read Response Format                            |      |

| 6-10 | CPU Package Config Write Request Format                            |      |

| 6-11 | CPU Package Config Write Response Format                           |      |

| 6-12 | Set SM Signal Request Format                                       |      |

| 6-13 | Set SM Signal Response Format                                      |      |

| 6-14 | OEM Command Details                                                |      |

| 6-15 | Set Fan PWM Adder Command Request Format                           |      |

| 6-16 | Set Fan PWM Adder Command Response Format                          |      |

| 6-17 | Get POST Register Request Format                                   |      |

| 6-18 | Get POST Register Response Format                                  |      |

| 6-19 | Assert Forced Throttle Request Format                              |      |

| 6-20 | Assert Forced Throttle Response Format                             |      |

| 6-21 | Enable External Throttle Request Format                            |      |

| 6-22 | Enable External Throttle Response Format                           |      |

| 6-23 | OEM Get Throttle Reason Request Format                             |      |

| 6-24 | OEM Get Throttle Reason Response Format                            |      |

|      | Table of Sensors                                                   |      |

|      | Status Sensor Report Format                                        |      |

| 6-27 | LED Indicators                                                     | 78   |

## **Revision History**

| Document Number Revision Number Description                                   |                                                                                                                                                                                                                                                                                                                  | Date                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 32829                                                                         | 004                                                                                                                                                                                                                                                                                                              | Added a disclaimer regarding the default SMC address of 0x30.                                                                                                                                                                                                                                                                                                                                                                                        | April 2015 |

| 328209                                                                        | Updated product SKU Table 2-1. Added 31S1P, 7120A and 7120D.     Added SKUs 31S1P and 7120A to relevant figures, paragraphs and tables throughout document.     Added thermal throttling due to hot to VRs, Section 3.4.1.1.     Minor changes and clarifications in power management and manageability chapter. |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | April 2014 |

| 328209 002 • Update Table 3 • Update Table 3 • Other 6 • Added • Update manag |                                                                                                                                                                                                                                                                                                                  | <ul> <li>Updated product SKU Table 2-1.</li> <li>Updated mechanical specification Table 3-1 and thermal specification Table 3-2.</li> <li>Other changes in thermal and mechanical specification chapter.</li> <li>Added significant information on 5120D in pin list chapter.</li> <li>Updated power state numbers in Table 5-1 and added Turbo in power management chapter</li> <li>Changes and clarifications in manageability chapter.</li> </ul> | June 2013  |

| 328209                                                                        | 001                                                                                                                                                                                                                                                                                                              | • First Intel <sup>®</sup> Xeon Phi™ Coprocessor Datasheet release.                                                                                                                                                                                                                                                                                                                                                                                  |            |

## **Introduction**

#### 1.1 **Reference Documentation**

Table 1-1 lists most of the applicable documents. For complete list of documentation, contact your local Intel representative or go to www.intel.com.

#### **Table 1-1. Related Documents**

| Document                                                                               | Document ID               |

|----------------------------------------------------------------------------------------|---------------------------|

| Intel® Xeon Phi™ Coprocessor Specification Update                                      | 328205-006EN <sup>1</sup> |

| Intel <sup>®</sup> Xeon Phi <sup>™</sup> Coprocessor Safety Compliance Guide           | 328206-001EN <sup>1</sup> |

| Intel <sup>®</sup> Xeon Phi <sup>™</sup> Coprocessor System Software Developer's Guide | 328207-001EN <sup>1</sup> |

| Intel® Xeon Phi™ Coprocessor Thermal Mechanical Models                                 | 328208-001EN <sup>1</sup> |

| Intel <sup>®</sup> Xeon Phi™ Coprocessor Dense Form Factor Models                      | N/A <sup>1</sup>          |

| Intel® Xeon Phi™ Coprocessor Instruction Set Reference Manual                          | N/A <sup>2</sup>          |

| Intel® Xeon™ Processor Family External Design Specification (EDS) Volume 1             | N/A <sup>1</sup>          |

| PCI Express* Card Electromechanical Specification, Revision 2.0                        | N/A <sup>3</sup>          |

| PCI Express* 225W/300W High Power Card Electromechanical Specification, Revision 1.0   | N/A <sup>3</sup>          |

| Intelligent Platform Management Bus Communications Protocol Specification, v1.0        | N/A                       |

| Intelligent Platform Management Interface Specification, v2.0                          | N/A                       |

Note: 1. http://www.intel.com/content/www/us/en/processors/xeon/xeon-technical-resources.html

Note: 2. http://software.intel.com/en-us/forums/intel-many-integrated-core/

Note: 3. http://www.pcisig.com/

#### **Conventions and Terminology** 1.2

#### 1.2.1 **Terminology**

Document ID Number: 328209 004EN

This section provides the definitions of some of the terms used in this document.

#### **General Terminology Table 1-2.**

| Terminology | Definition                                |

|-------------|-------------------------------------------|

| BGA         | Ball Grid Array                           |

| BMC         | Baseboard Management Controller           |

| DFF         | Dense Form Factor                         |

| ECC         | Error Correction Code                     |

| FET         | Field Effect Transistor                   |

| FRU         | Field Replaceable Unit                    |

| GDDR        | Graphics Double Data Rate                 |

| IBP         | Intel Business Portal                     |

| IPMB        | Intelligent Platform Management Bus       |

| IPMI        | Intelligent Platform Management Interface |

| ME          | Manageability Engine                      |

### Table 1-2. General Terminology

| Terminology | Definition                                         |

|-------------|----------------------------------------------------|

| MPSS        | Many Integrated Core Platform Software Stack       |

| PCIe        | PCI Express*                                       |

| PID         | Proportional-Integral-Derivative control algorithm |

| PWM         | Pulse Width Modulation                             |

| RAS         | Reliability Accessibility Serviceability           |

| SCIF        | Symmetric Communications Interface                 |

| SDK         | Software Development Kit                           |

| SDR         | Sensor Data Record                                 |

| SEL         | System Event Log                                   |

| SKU         | Stock Keeping Unit                                 |

| SMBus       | System Management Bus                              |

| SMC         | System Management Controller                       |

| TDP         | Thermal Design Power                               |

| VID         | Coprocessor Voltage Identification                 |

| VR          | Voltage Regulator                                  |

| XTAL        | Crystal Oscillator                                 |

|             | •                                                  |

## 2 Intel® Xeon Phi™ Coprocessor Architecture

### 2.1 Intel® Xeon Phi™ Coprocessor Product Overview

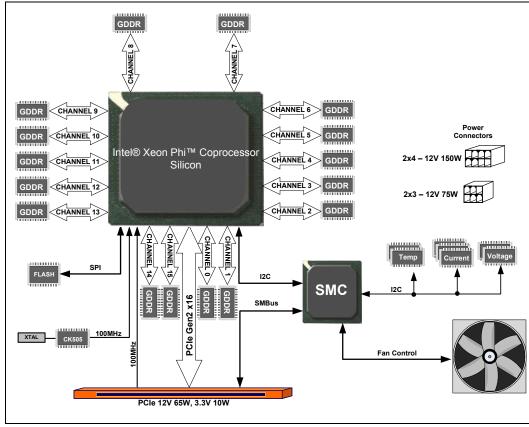

Figure 2-1. Intel<sup>®</sup> Xeon Phi™ Coprocessor Board Schematic<sup>1</sup>

#### Notes:

Document ID Number: 328209 004EN

1. On-board fan is available on Intel<sup>®</sup> Xeon Phi™ Coprocessor 3120A and 7120A SKUs only.

The Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor consists of the following primary subsystems:

- Many Integrated Core (MIC) coprocessor silicon and GDDR5 memory.

- System Management Controller (SMC), thermal sensors (inlet air, outlet air, coprocessor on-die thermal, and single GDDR5 sensor) and fan (only on 3120A and 7120A products; see SKU matrix Table 2-1).

- Voltage regulators (VRs) powered by the motherboard through the PCI Express\* connector, a 2x4 (150W) and a 2x3 (75W) auxiliary power connector on the east edge of the card. Along with power through the PCI Express\* connector, the 300W SKUs need both 2x4 and 2x3 connectors to be driven by system power supplies. The 225W SKU may be powered only through the PCI Express\* connector and the 2x4 connector.

- PCI Express\* connections.

- The clock system is integrated in the coprocessor including an on-board 100MHz +/

50ppm reference clock, and requires only the PCI Express\* 100MHz reference clock input from the motherboard.

The Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor provides the following high-level features:

- A many-core coprocessor.

- Maximum 16-channel GDDR memory interface with an option to enable ECC.

- PCI Express\* 2.0 x16 interface with optional SMBus management interface.

- Node Power and Thermal Management, including power capping support.

- +12V power monitoring and on-board fan Proportional-Integral-Derivative (PID) controller (3120A and 7120A SKUs).

- On-board flash device that loads the coprocessor OS on boot.

- Card level RAS features and recovery capabilities.

### 2.1.1 Intel<sup>®</sup> Xeon Phi<sup>™</sup> Coprocessor Board Design

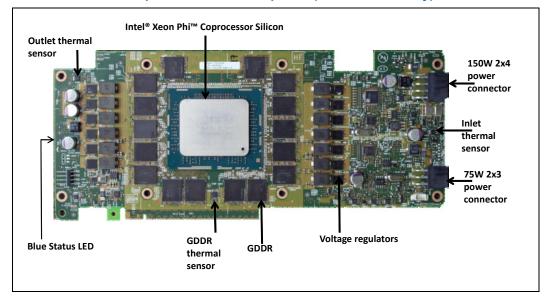

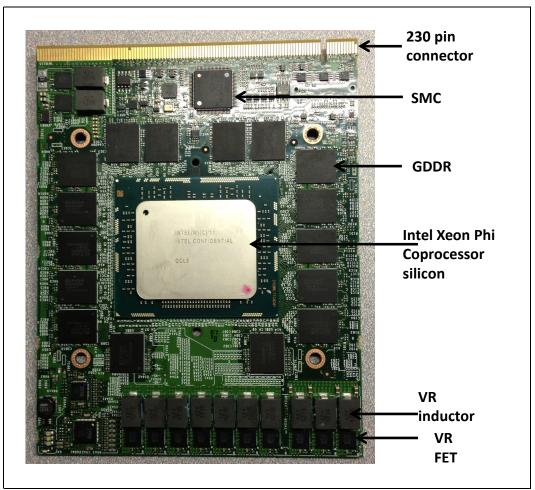

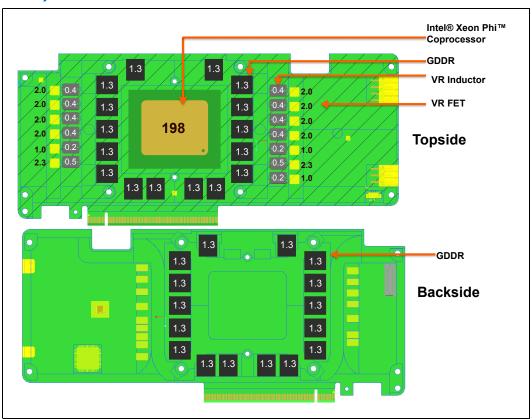

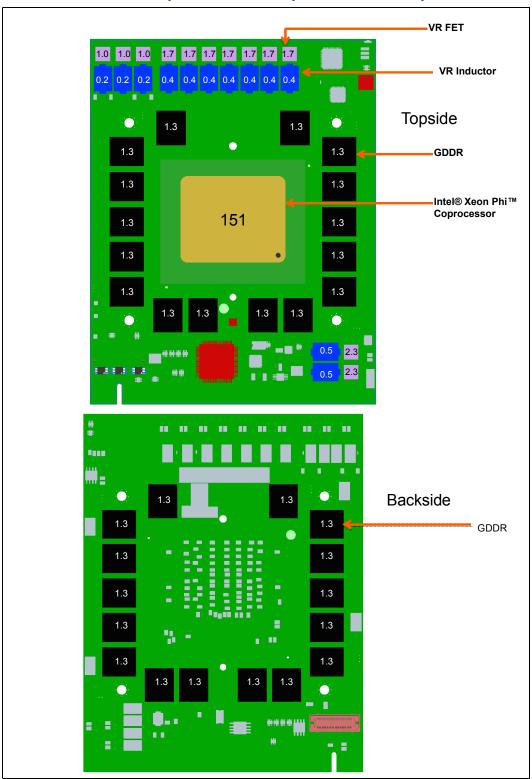

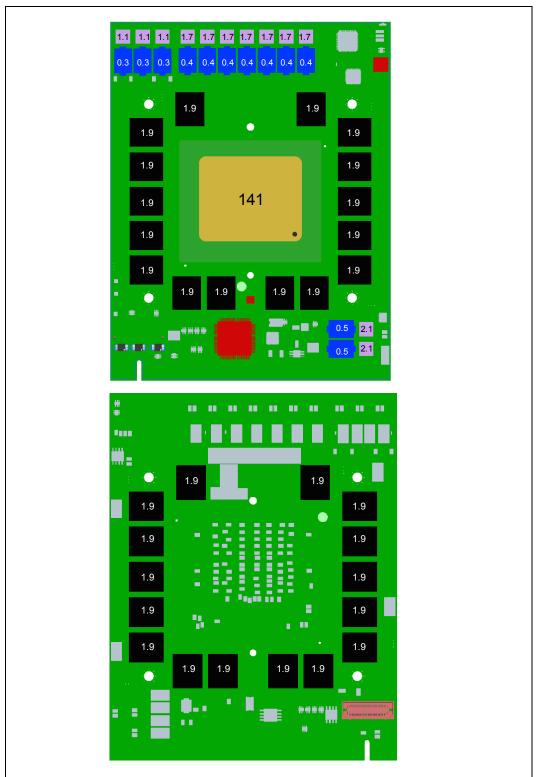

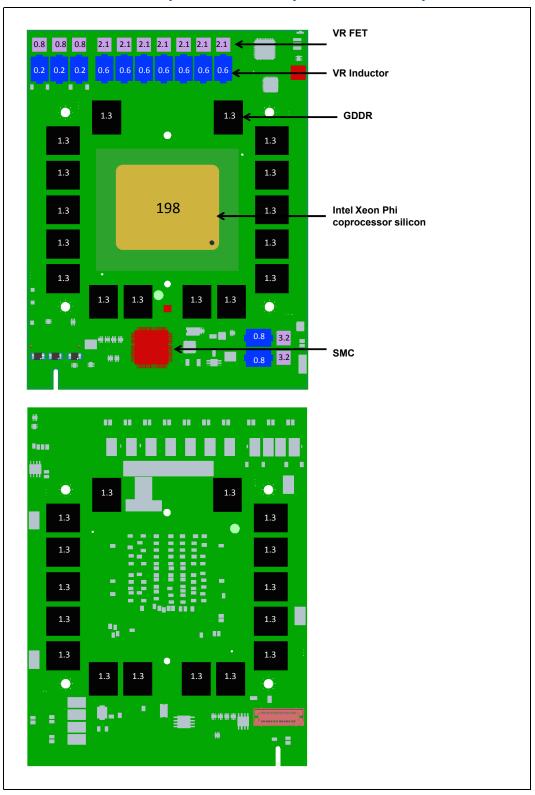

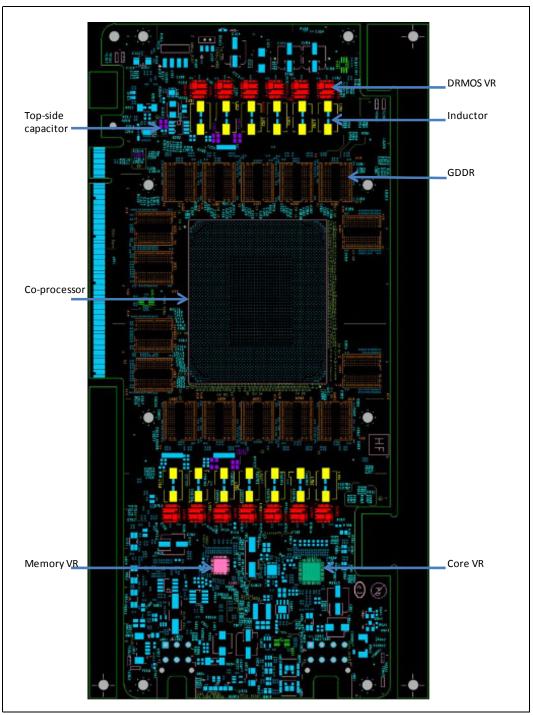

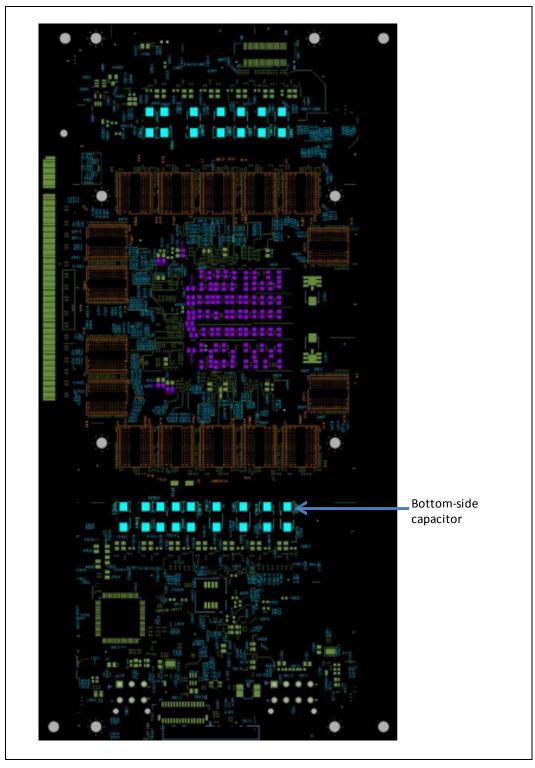

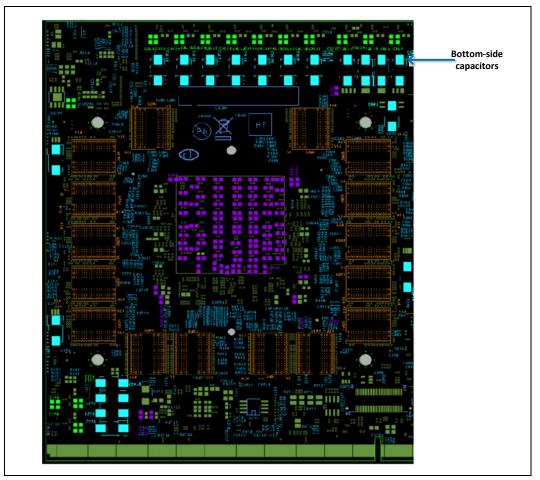

The Intel<sup>®</sup> Xeon Phi™ coprocessor is a PCI Express\* compliant high-power add-in product, with an integrated thermal and mechanical solution (see SKU matrix Table 2-1 for exceptions). It supports a maximum of 16 GDDR memory channels, distributed on both sides of the PCB inside the coprocessor package. Each memory channel supports two 16-bit wide GDDR device (for a maximum of 32 devices), combining to give 32-bit wide data. Figure 2-2 and Figure 2-3 show the front and back sides of the PCB. The two notches along the top edge of the card are used to attach the cooling plate for the GDDR devices on the backside of the PCB (side not containing the Intel<sup>®</sup> Xeon Phi™ coprocessor silicon). The VRs are split right and left to help reduce direct current resistance and current density.

The Intel<sup>®</sup> Xeon Phi™ coprocessor supports 2 power groups for a total of 4 primary low-voltage rails: a group consisting of VDDG, VDDQ, and VSFR power rails, and another group consisting only of VCCP. The VCCP, VDDG, and VDDQ rails are powered from the PCI Express\* edge connector and the auxiliary 12V inputs. The VSFR rail is powered from the PCI Express\* edge connector 3.3V input (~5W). VCCP is the coprocessor core voltage rail, while VDDQ, VDDG and VSFR supply power to memory, portions of the coprocessor and miscellaneous circuitry in the coprocessor.

Figure 2-2. Intel® Xeon Phi™ Coprocessor Board Top side (for reference only)

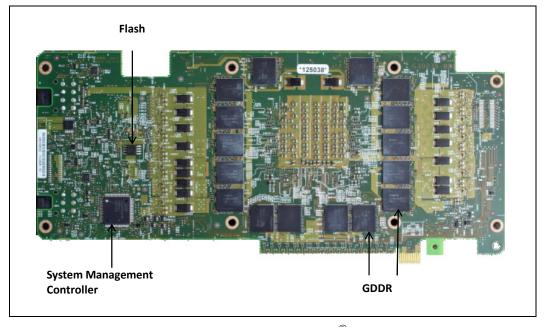

Figure 2-3. Intel® Xeon Phi™ Coprocessor Board, Back side (reference only)

Note:

Figure 2-2 and 2-3 are representative of the final Intel $^{\circledR}$  Xeon Phi $^{\intercal}$  Coprocessor board without the package thermal and mechanical solution.

### **2.1.2 System Management Controller (SMC)**

The SMC has three I2C interfaces. This allows the SMC to have direct connection to the coprocessor I2C interface, an on-board I2C sensor bus and a third interface through the SMBus pins of the PCI Express\* connector to the system management solution. The I2C interface between the SMC and coprocessor is used for polling coprocessor thermal status information. The sensor bus allows board thermal, input power, and current

sense monitoring for system fan and power control. This information is forwarded to the coprocessor for power state control. The SMBus interface can be used by system for chassis fan control with the passive heat sink card and for integration with the Node Management controller in the platform. Communication with the system baseboard management controller (BMC) or peripheral control hub (PCH) occurs over the SMBus using the standard IPMB protocol. See chapter on manageability for more details.

### 2.1.3 Intel® Xeon Phi™ Coprocessor Silicon

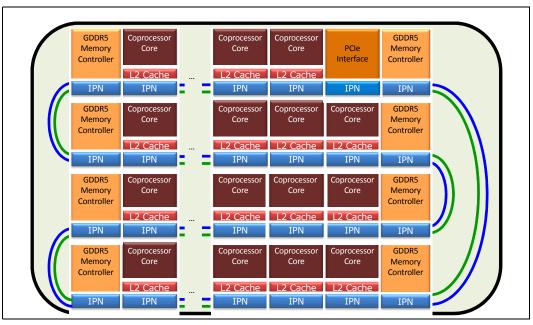

### Figure 2-4. Intel® Xeon Phi™ Coprocessor Silicon Layout

Figure 2-4 is a conceptual drawing of the general structure of the Intel<sup>®</sup> Xeon Phi™ coprocessor architecture, and does not imply actual distances, latencies, etc. The cores, PCIe Interface logic, and GDDR5 memory controllers are connected via an Interprocessor Network (IPN) ring, which can be thought of as independent bidirectional ring.

The L2 caches are shown here as slices per core, but can also be thought of as a fully coherent cache, with a total size equal to the sum of the slices. Information can be copied to each core that uses it to provide the fastest possible local access, or a single copy can be present for all cores to provide maximum cache capacity.

The Intel® Xeon  $Phi^{TM}$  coprocessor can support up to 61 cores (making a 30.5 MB L2) cache) and 8 memory controllers with 2 GDDR5 channels each. The maximum number of cores and total card memory varies with Intel® Xeon  $Phi^{TM}$  coprocessor SKU; refer to the  $Intel^{\textcircled{R}}$  Xeon  $Phi^{TM}$  Coprocessor Specification Update for information.

Communication around the ring follows a Shortest Distance Algorithm (SDA). Coresident with each core structure is a portion of a distributed tag directory. These tags are hashed to distribute workloads across the enabled cores. Physical addresses are also hashed to distribute memory accesses across the memory controllers.

### 2.1.4 Intel® Xeon Phi™ Coprocessor Product Family

#### **Table 2-1.** Intel® Xeon Phi™ Coprocessor Product Family

| SKU                   | Card TDP (Watts) | Cooling Solution <sup>1</sup> |

|-----------------------|------------------|-------------------------------|

| 3120A                 | 300              | Active                        |

| 3120P / 7120P / SE10P | 300              | Passive <sup>2,4</sup>        |

| 7120X / SE10X         | 300              | None <sup>2,3,4</sup>         |

| 31S1P                 | 270              | Passive                       |

| 7120A                 | 270              | Active                        |

| 7120D                 | 270              | None <sup>6</sup>             |

| 5120D                 | 245              | None <sup>5</sup>             |

| 5110P <sup>6</sup>    | 225              | Passive                       |

#### Notes:

Document ID Number: 328209 004EN

- 1. Passive cooling solution uses topside heatsink (vapor chamber and copper fins) and backside aluminum plate. Active cooling uses on-card dual-intake blower.

- 2. SE10P/SE10X are limited edition one-time only SKUs.

- 3. Same performance and card configuration as the 7120P/SE10P but without Intel heatsink or chassis retention mechanism; allows for custom thermal and mechanical design by users.

- 4. 7120P/7120X feature Turbo.

- Dense Form Factor (DFF): Smaller physical footprint than the other Intel® Xeon Phi™ coprocessor products, for innovative platform designs with unique PCI Express\* interface, PCI Express\* 2.0 specification compliant.

- 6. Refer to Section 5.1 for note on total card TDP of 5110P.

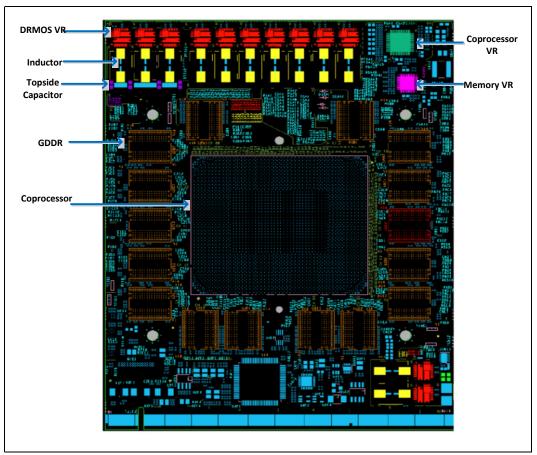

## 2.1.5 Intel® Xeon Phi™ Coprocessor 7120D/5120D(Dense Form Factor)

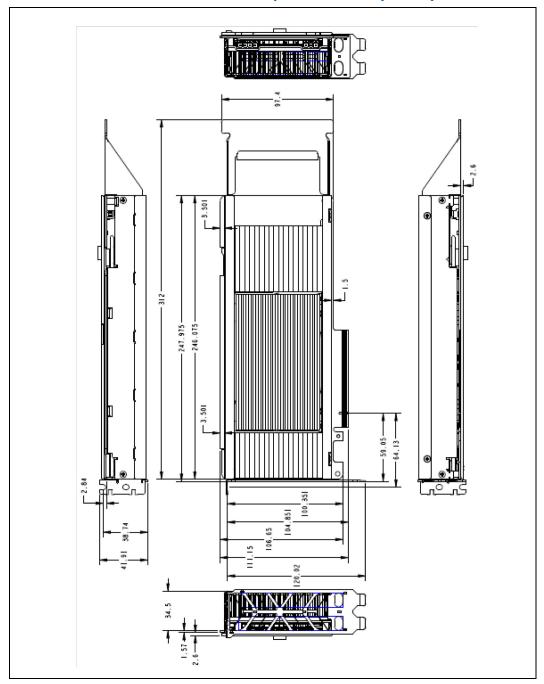

The Intel® Xeon Phi<sup>™</sup> coprocessor 7120D/5120D products, also known as Dense Form Factor (DFF), are derivatives of the standard Intel® Xeon Phi<sup>™</sup> coprocessor PCI Express\* form-factor card. The high-level features of the DFFs are:

- Maximum TDP of 270W for the 7120D and 245W for the 5120D

- GDDR on both sides of the card.

- 117.35mm(4.62") x 149.86mm(5.9") PCB.

- 230-pin unique edge finger designed to industry standard x24 PCI Express\* connector, PCI Express\* 2.0 compliant. The unique edge finger pin definition requires signal routing on baseboard and 12V filter per card.

- All power to the card is supplied through the connector.

- There is no auxiliary 2x4 or 2x3 power connector on the card.

- Supports vertical, straddle or right-angle mating connectors.

- On board SMC. The manageability features and software capabilities remain the same as for other Intel® Xeon Phi™ coprocessor products.

- To allow for system design innovation and differentiation, Intel will ship only the

assembled and fully functional PCB, without heatsink or chassis retention

mechanism. This allows system designers to implement their own cooling solution

and connector of choice. Due to presence of GDDR5 memory components on the

backside of the DFF board, a custom cooling design must comprehend both sides of

the DFF product.

- Baseboard designers must ensure the signal integrity of all PCI Express\* signals as they pass the connector of choice and reach the connector fingers of the DFF product.

Figure 2-5. 7120D/5120D Dense Form Factor, Topside

## 3 Thermal and Mechanical Specification

### 3.1 Mechanical Specifications

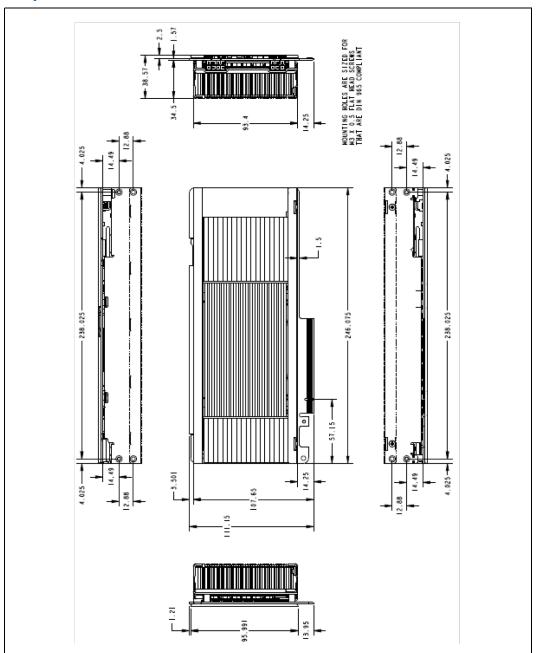

The mechanical features of the Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor are compliant with the *PCI Express\* 225W/300W High Power Card Electromechanical Specification 1.0.*

Table 3-1 shows the mechanical specifications of Intel<sup>®</sup> Xeon  $Phi^{TM}$  coprocessor passive and active SKUs.

### **Table 3-1.** Intel<sup>®</sup> Xeon Phi<sup>™</sup> Coprocessor Mechanical Specification

| Parameter                               | Specification        |

|-----------------------------------------|----------------------|

| Product Length                          | 247.9mm <sup>1</sup> |

| Primary Side Height Keep-in             | 34.8mm               |

| Secondary Side Height Keep-in           | 2.67mm               |

| 3120A/7120A SKU mass                    | 1400g                |

| 7120P/SE10P/5110P/3120P/31S1P SKUs mass | 1200g                |

| 7120D/5120D SKUs mass                   | 183g                 |

| 7120X/SE10X SKUs mass                   | 225g                 |

#### Notes:

Document ID Number: 328209 004EN

Figure 3-1 shows the mounting holes and Figure 3-2 shows the relevant dimensions of the Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor passive and active cards for chassis retention. Refer to the *Intel<sup>®</sup> Xeon Phi<sup>™</sup> Coprocessor Thermal Mechanical Models* for PTC\* Creo (previously Pro-Engineer), Icepak and FloTHERM\* models.

<sup>1.</sup> Inclusive of I/O bracket

Figure 3-1 Location of Mounting Holes on the Intel<sup>®</sup> Xeon Phi<sup>™</sup> Coprocessor Card (in mils)

Figure 3-2 Dimensions of the Intel<sup>®</sup> Xeon Phi™ Coprocessor Card (in mils)

## 3.2 Intel® Xeon Phi™ Coprocessor Thermal Specification

### Table 3-2. Intel<sup>®</sup> Xeon Phi<sup>™</sup> Coprocessor Thermal Specification

| Parameter                              | Specification                                       |

|----------------------------------------|-----------------------------------------------------|

| T <sub>RISE</sub>                      | 10°C                                                |

| Max T <sub>INLET</sub>                 | 45°C                                                |

| Max T <sub>EXHAUST</sub>               | 70°C                                                |

| T <sub>case (processor)</sub> min, max | 5°C, 95°C                                           |

| T <sub>control</sub>                   | ~82°C <sup>1</sup>                                  |

| T <sub>throttle</sub>                  | 104°C <sup>2</sup>                                  |

| T <sub>thermtrip</sub>                 | $\sim (T_{\text{throttle}} + 20^{\circ}\text{C})^3$ |

#### Notes:

- T<sub>control</sub> is the setpoint at which the system fans must ramp up towards full power (or RPM) to maintain the Intel® Xeon Phi™ coprocessor temperature around T<sub>control</sub> and prevent throttling. It is a requirement that the system BMC use IPMB commands to query the SMC on the coprocessor card for accurate T<sub>control</sub> value as this value can vary between 80°C and 84°C.

- 2. When the coprocessor junction temperature ( $T_{\text{junction}}$ ) reaches  $T_{\text{throttle}}$ , the SMC will force thermal throttle which will drop frequency to lowest supported value and reduce total coprocessor power. It is a requirement that the system BMC query the SMC on the coprocessor card for accurate  $T_{\text{throttle}}$  value.

- 3. If the coprocessor temperature reaches T<sub>thermtrip</sub>, the coprocessor OS will take action to shutdown the card to prevent damage to the coprocessor. This includes shutting down the coprocessor VRs, and the only way to restart the coprocessor is by rebooting the host system. T<sub>thermtrip</sub> should not be considered a specification; it can change between SKUs, and is given here as guidance.

## 3.2.1 Intel® Xeon Phi™ Coprocessor Thermal Management

Thermal management on the Intel® Xeon Phi<sup>™</sup> coprocessor card is achieved through a combination of coprocessor based sensors, card level sensors and inputs, and a coprocessor frequency control circuit. Reducing card temperature is accomplished by adjusting the frequency of the coprocessor. Lowering the coprocessor frequency will reduce the power dissipation and consequently the temperature.

The coprocessor carries in it a factory calibrated Digital Temperature Sensor (DTS) that monitors coprocessor temperature, also called junction temperature ( $T_{junction}$ ). Data from this sensor is available to the BMC or other system software via both in-band (direct software reads) and out-of-band (over the PCI Express\* SMBus) interface. Refer to chapter titled "Manageability" for more information on how to read the junction temperature. System management software can use this data to monitor the silicon temperature and take any appropriate actions. Systems that adjust airflow based on component temperatures must monitor the coprocessor's DTS to ensure sufficient cooling is always available.

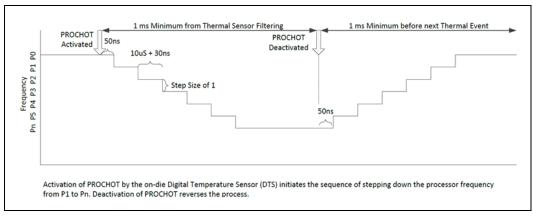

In addition to making thermal information available to system manageability software, the DTS is constantly comparing the coprocessor temperature to the factory set maximum permissible temperature called  $T_{throttle}$ . If the measured temperature at any time exceeds  $T_{throttle}$  (a state also known as PROCHOT), then the coprocessor will automatically step down the operating frequency (or Pstate) in an attempt to reduce the temperature (this is often referred to as "thermal throttling"). Once the temperature has dropped below  $T_{throttle}$ , the frequency will be brought back up to the original setting. See Figure 3-3 below.

Within 50ns of detecting  $T_{throttle}$ , the DTS circuit begins stepping down the P-states until Pn is reached. Each frequency step is approximately 100MHz; the exact value will depend on the starting frequency. After each step, the DTS will wait 10uS before taking the next step. The number of steps, or P-states, depends on the starting frequency and the minimum frequency supported by the processor. Once Pn is reached, the frequency will be held at that level for approximately 1ms, or until the temperature has dropped below Tprochot, whichever is longer.

If throttling continues for more than 100ms, the coprocessor OS will reduce the voltage setting in order to further decrease the power dissipation. The voltage settings are preprogrammed at the factory and cannot be reconfigured.

Upon removal of the thermal event, the process reverses and the voltage and frequency are stepped back up to the P1 state. Although the process to reduce frequency is managed by the coprocessor circuits, the sequence to bring the coprocessor back to P1 is controlled by the coprocessor OS. As a result, the precise timings of the step changes may be slightly longer than 10uS.

Figure 3-3 Entering and Exiting Thermal Throttling (PROCHOT)

Document ID Number: 328209 004EN

## 3.3 Intel<sup>®</sup> Xeon Phi<sup>™</sup> Coprocessor Thermal Solutions

There are two types of thermal solutions to address the Intel<sup>®</sup> Xeon Phi™ coprocessor power limits: a passive solution for most SKUs as indicated in Table 2-1 (which relies on forced convection airflow provided by the system) and an active solution on the 3120A and 7120A SKUs (which uses a high performance blower.) The active solution is designed to operate in an 'adjacent card configuration' such that the impedance from a nearby flow blockage is accounted for within the design. Both passive and active solutions come with cooling backplates that augment the stiffness of the Intel<sup>®</sup> Xeon Phi™ coprocessor card by counteracting the preload applied by the primary side (housing the coprocessor). This also protects the structural integrity of the coprocessor and GDDR packages during a shock event, and to provide a protective cover.

Given the requirement to dissipate backside GDDR heat within the 2.67 mm keep-in height prescribed by the PCI Express\* specification, the backplate is designed to transfer the GDDR heat from the secondary side via heat pipes to the primary side thermal solution.

### 3.3.1 3120A and 7120A Active Cooling Solution

For the 3120A and 7120A SKUs, the Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor thermal-mechanical solution utilizes a supersink approach in which a primary heatsink is used to cool the coprocessor while a metallic fuselage/supersink cools the VR and GDDR components. Figure 3-4 illustrates the key components of the active cooling design.

In the fuselage/supersink approach, the duct is metallic and performs both structural and thermal roles. In its 'fuselage' function, the duct provides structural support for the forces generated by the coprocessor thermal interface, protects against shock events, and channels airflow through the card. In its 'supersink' function, the duct contains internal fins, heat pipes, and diecast blower frame. The internal heat pipes serve to transmit heat from GDDR (both top- and bottom-side) and VR components to the internal fin banks, diecast blower frame, and metal fuselage structure where it can be effectively transferred to the airstream. The duct also contains horizontal webs which interface to the east and west GDDR as well as to the VR FETs. Together, these structures dissipate heat lost from the GDDR and VR components into the air.

The coprocessor thermal path is separated from the GDDR and VR components, and utilizes a heatsink with parallel plate fins and vapor chamber base.

The active solution also contains a high-performance dual-intake blower that operates up to 5400 rpm at 20W of motor power. The blower has been designed to maximize the pressure drop capability and is able to deliver up to 35  $\rm ft^3/min$  in an open airflow environment. When installed on the card, the blower delivers 31  $\rm ft^3/min$  with no adjacent blockage. When an adjacent card is considered, the resultant impedance loss causes the flow rate to drop to 23  $\rm ft^3/min$ . The active thermal solution is designed to provide sufficient cooling even in the latter scenario.

## 3.3.2 7120P/SE10P/5110P/3120P/31S1P Passive Cooling Solution

For the passive heat sink on the 7120P/SE10P/5110P/3120P/31S1P SKUs, the Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor thermal & mechanical solution also utilizes a 'fuselage/ supersink' approach. Figure 3-5 illustrates the key components of the passive design.

Figure 3-5 Exploded View of Passive Thermal Solution

As in the active thermal solution, the duct is metallic and performs both structural and thermal roles. In its 'fuselage' function, the duct provides structural support for the forces generated by the CPU thermal interface, protects against shock events, and channels airflow through the card. In its 'supersink' function, the duct contains internal fins and heat pipes. The internal heat pipes serve to transmit heat from GDDR (both top- and bottom-side) and VR components to the internal fin banks, diecast blower frame, and metal fuselage structure where it can be effectively transferred to the airstream. The passive solution does not have a diecast blower frame as it relies upon forced airflow from the host system. In place of the blower and frame, an additional fin bank is added to dissipate waste heat from GDDR and VR components. The fin spacing of all fin banks as well as of the CPU heat sink fin bank have been optimized for receiving system-supplied airflow. A backplate stiffener/heat sink is used.

#### 3.3.2.1 System Airflow for 5110P SKUs

In order to ensure adequate cooling of the 5110P SKUs with a  $45^{\circ}$ C inlet temperature, the system must be able to provide 20 ft<sup>3</sup>/min of airflow to the card with 4.3 ft<sup>3</sup>/min on the secondary side and the remainder on the primary side. The total pressure drop (assuming a multi-card installation conforming to the PCI Express\* mechanical specification) is 0.21 inch H<sub>2</sub>O at this flow rate.

**Note:** For systems with reversed airflow, the corresponding airflow requirement is expected to be within +/-5% tolerance of the values shown in the following tables.

If the system is able to provide a temperature lower than 45°C at the card inlet, then the total airflow can be reduced according to the graph and table in Figure 3-6.

If the 5110P SKU is powered by a 2x4 and a 2x3 connector, the card can support an additional 20W of power for maximum TDP of 245W (see Section 2.1.5 for more details). In this case, the corresponding airflow requirement for cooling the part as a 245W card is shown in Figure 3-8.

## 3.3.2.2 Airflow Requirement for SE10P/7120P/3120P/31S1P Passive Cooling Solution

In order to ensure adequate cooling of the SE10P/7120P/3120P 300W and 31S1P 270W SKUs with a  $45^{\circ}$ C inlet temperature, the system must be able to provide 33 ft<sup>3</sup>/min of airflow to the card with 7.2 ft<sup>3</sup>/min on the secondary side and the remainder on the primary side. The total pressure drop (assuming a multi-card installation conforming to the PCI Express\* mechanical specification) is 0.54 in H<sub>2</sub>O at this flow rate.

If the system is able to provide a temperature lower than 45°C at the card inlet, then the total airflow can be reduced according to the graph and table in Figure 3-7.

Airflow Requirement vs. 45°C Inlet Temperature for the 5110P at 225W TDP Figure 3-6

| Card Inlet (°C) | Total Flow (ft^3/min) | Primary (ft^3/min) | Secondary (ft^3/min) | Card dP(inch H <sub>2</sub> C |

|-----------------|-----------------------|--------------------|----------------------|-------------------------------|

| 20              | 10.6                  | 7                  | 3.7                  | 0.08                          |

| 21              | 10.8                  | 7.1                | 3.7                  | 0.08                          |

| 22              | 11                    | 7.3                | 3.7                  | 0.08                          |

| 23              | 11.2                  | 7.5                | 3.7                  | 0.08                          |

| 24              | 11.4                  | 7.7                | 3.7                  | 0.09                          |

| 25              | 11.6                  | 7.9                | 3.7                  | 0.09                          |

| 26              | 11.8                  | 8.1                | 3.7                  | 0.09                          |

| 27              | 12                    | 8.3                | 3.7                  | 0.09                          |

| 28              | 12.2                  | 8.5                | 3.7                  | 0.1                           |

| 29              | 12.5                  | 8.7                | 3.7                  | 0.1                           |

| 30              | 12.7                  | 9                  | 3.8                  | 0.1                           |

| 31              | 13                    | 9.2                | 3.8                  | 0.11                          |

| 32              | 13.3                  | 9.5                | 3.8                  | 0.11                          |

| 33              | 13.6                  | 9.8                | 3.8                  | 0.12                          |

| 34              | 13.9                  | 10.1               | 3.8                  | 0.12                          |

| 35              | 14.2                  | 10.4               | 3.8                  | 0.12                          |

| 36              | 14.6                  | 10.7               | 3.9                  | 0.13                          |

| 37              | 15                    | 11.1               | 3.9                  | 0.14                          |

| 38              | 15.4                  | 11.4               | 3.9                  | 0.14                          |

| 39              | 15.8                  | 11.8               | 4                    | 0.15                          |

| 40              | 16.2                  | 12.2               | 4                    | 0.16                          |

| 41              | 16.7                  | 12.7               | 4.1                  | 0.16                          |

| 42              | 17.2                  | 13.1               | 4.1                  | 0.17                          |

| 43              | 17.8                  | 13.6               | 4.2                  | 0.18                          |

| 44              | 18.4                  | 14.2               | 4.2                  | 0.19                          |

| 45              | 19.1                  | 14.7               | 4.3                  | 0.21                          |

Figure 3-7 Airflow Requirement vs. Inlet Temperature for the 31S1P at 270W TDP and SE10P/7120P/3120P at 300W TDP

| Card Inlet (°C) | Total Flow (ft^3/min) | Primary (ft^3/min) | Secondary (ft^3/min) | Card dP (inH <sub>2</sub> O) |

|-----------------|-----------------------|--------------------|----------------------|------------------------------|

| 20              | 14.4                  | 10.5               | 3.9                  | 0.13                         |

| 21              | 14.7                  | 10.8               | 3.9                  | 0.13                         |

| 22              | 15                    | 11.1               | 3.9                  | 0.14                         |

| 23              | 15.3                  | 11.3               | 3.9                  | 0.14                         |

| 24              | 15.6                  | 11.7               | 4                    | 0.15                         |

| 25              | 16                    | 12                 | 4                    | 0.15                         |

| 26              | 16.3                  | 12.3               | 4                    | 0.16                         |

| 27              | 16.7                  | 12.7               | 4.1                  | 0.16                         |

| 28              | 17.1                  | 13                 | 4.1                  | 0.17                         |

| 29              | 17.6                  | 13.4               | 4.1                  | 0.18                         |

| 30              | 18                    | 13.8               | 4.2                  | 0.19                         |

| 31              | 18.5                  | 14.3               | 4.3                  | 0.2                          |

| 32              | 19.1                  | 14.8               | 4.3                  | 0.21                         |

| 33              | 19.7                  | 15.3               | 4.4                  | 0.22                         |

| 34              | 20.3                  | 15.8               | 4.5                  | 0.23                         |

| 35              | 21                    | 16.4               | 4.6                  | 0.24                         |

| 36              | 21.7                  | 17                 | 4.7                  | 0.26                         |

| 37              | 22.5                  | 17.6               | 4.8                  | 0.27                         |

| 38              | 23.3                  | 18.4               | 5                    | 0.29                         |

| 39              | 24.3                  | 19.1               | 5.1                  | 0.31                         |

| 40              | 25.3                  | 20                 | 5.3                  | 0.34                         |

| 41              | 26.5                  | 20.9               | 5.6                  | 0.37                         |

| 42              | 27.8                  | 21.9               | 5.9                  | 0.4                          |

| 43              | 29.2                  | 23                 | 6.2                  | 0.44                         |

| 44              | 30.9                  | 24.2               | 6.7                  | 0.48                         |

| 45              | 32.8                  | 25.6               | 7.2                  | 0.54                         |

Figure 3-8 Airflow Requirement vs. Inlet Temperature for the 5110P Card at 245W TDP<sup>1</sup>

1. Refer to Section 5.1 for note on 5110P TDP.

## 3.4 Cooling Solution Guidelines for SE10X/7120X and 7120D/5120D

The Intel® Xeon Phi™ coprocessor SE10X/7120X and 7120D/5120D SKUs are shipped without a thermal solution, which gives system designers and integrators an opportunity to fit these SKUs into their custom designed chassis. These SKUs have GDDR components on the back side that must be cooled, in addition to the front side where the coprocessor resides. This section documents thermal and mechanical specifications and guidelines that would be useful to developers of custom designs.

### 3.4.1 Thermal Considerations

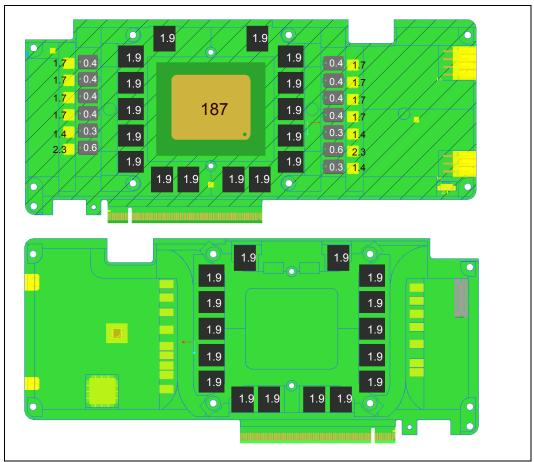

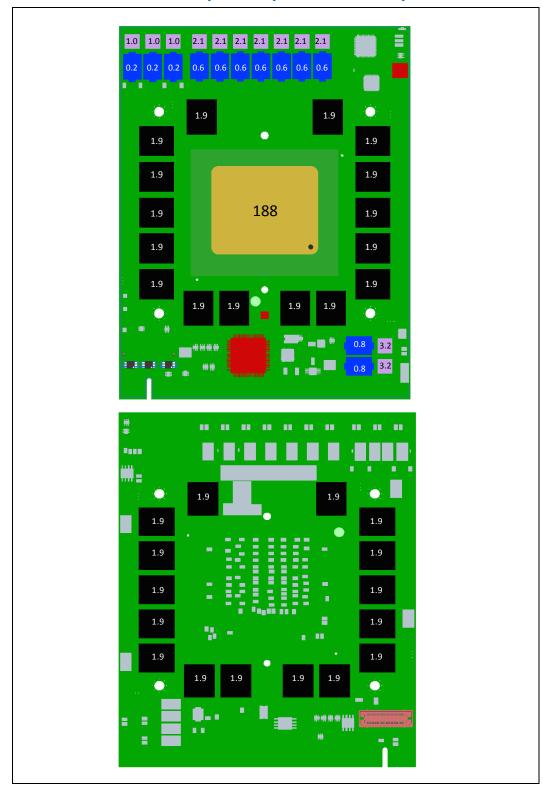

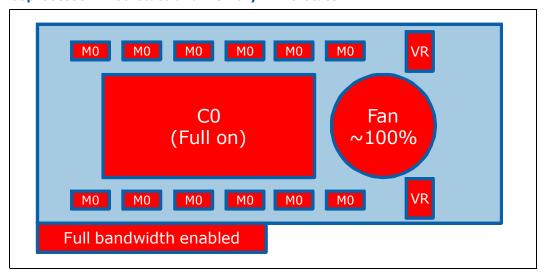

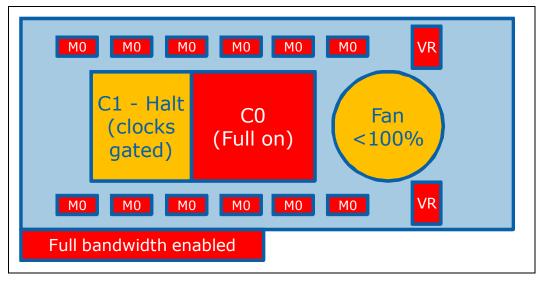

Figure 3-9 and Figure 3-10 show a schematic representation of the power profiles of the Intel® Xeon Phi<sup>™</sup> coprocessor SE10X/7120X products. Figure 3-11 to Figure 3-14 show a schematic representation of the power profiles of the 7120D/5120D product.

Figure 3-9 SE10X/7120X Power Profile for Coprocessor Intensive Workload (all values in Watts)

Figure 3-10 SE10X/7120X Power Profile for Memory Intensive Workload (all values in Watts)

Figure 3-11 5120D Power Profile: Coprocessor Centric (all values in Watts)

Figure 3-12 5120D Power Profile: Memory Centric (all values in Watts)

Figure 3-13 7120D Power Profile: Coprocessor Centric (all values in Watts)

Figure 3-14 7120D Power Profile: Memory Centric (all values in Watts)

Table 3-3 shows thermal specifications of components present on the SE10X/7120X and 7120D/5120D boards.

#### Table 3-3. Component Thermal Specification on SE10X/7120X and 7120D/5120D

| Component   | Thermal specification                      |  |  |

|-------------|--------------------------------------------|--|--|

| Coprocessor | T <sub>case</sub> ≤ 95°C                   |  |  |

| GDDR        | T <sub>case</sub> ≤ 85°C                   |  |  |

| VR FET      | T <sub>junction</sub> ≤ 150°C <sup>1</sup> |  |  |

| VR Inductor | T <sub>body</sub> ≤ 100°C                  |  |  |

#### Notes:

#### 3.4.1.1 VR Temperature and Thermal Throttling

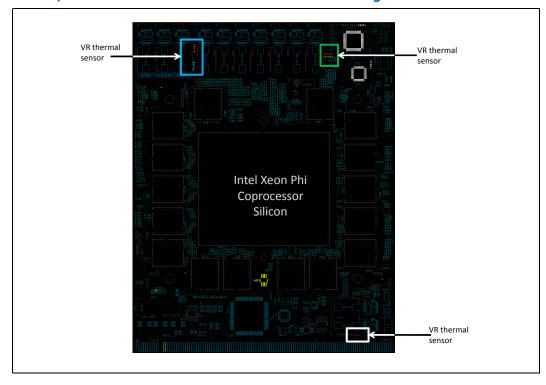

Some thermal sensors on the coprocessor are located in the field of the VR inductors and FETs that drive power to the coprocessor silicon, GDDR and other circuitry (Figure 3-15). These sensors continuously monitor the temperature of the circuit board. If the temperature reaches or exceeds 105° C, an interrupt will be sent to the SMC. In response to this interrupt, the SMC will assert PROCHOT to the coprocessor which in turn will force the coprocessor frequency to drop to the minimum supported value (approximately 600MHz). This frequency drop will reduce the power dissipation of the card and should allow the VR components to cool down. Once the temperature has dropped below 105° C, the VR controller will send a message to the SMC to de-assert PROCHOT. This will allow the coprocessor to return to the normal high frequency operating point.

Figure 3-15 7120D/5120D VR Thermal Sensors for Custom Cooling Consideration

<sup>1.</sup> While this is the component specification, on the passive and active  $Intel^{\textcircled{\$}}$  Xeon  $Phi^{\intercal M}$  coprocessor products, the junction temperature is limited to 135°C in order to prevent damage to the PCB.

### 3.4.2 Thermal Profile and Cooling

Document ID Number: 328209 004EN

The simplest cooling mechanism would involve running fans at full speed. For those custom air-cooled solutions that intend to be economical in fan power usage and acoustics, Figure 3-16 represents three regions on the SE10X/7120X coprocessor power consumption curve relevant to system fan control.

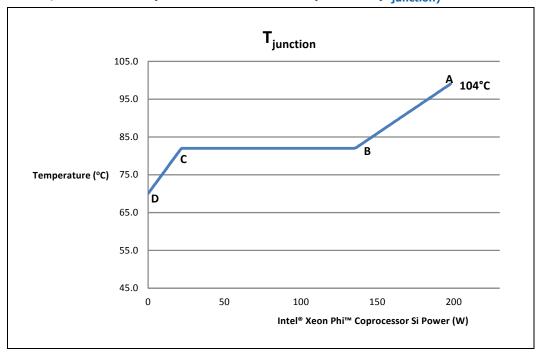

Figure 3-16 SE10X/7120X SKU Coprocessor Junction Temperature (T<sub>iunction)</sub> vs Power

Region (A-B) on the line represents the minimum necessary performance of a cooling solution to keep the coprocessor silicon temperature ( $T_{junction}$ ) below  $T_{throttle}$  of 104°C (Table 3-2), during high power dissipation. In this region, a cooling solution based on airflow would ensure the fans are operating at 100% capacity. In region B-C, the coprocessor power consumption is low enough that the cooling solution may be set to maintain the junction temperature at a target temperature. Finally, in region C-D, the coprocessor may need to be cooled to below the target temperature to maintain a reasonable exhaust air temperature.

Figure Figure 3-17 shows the analogous thermal behavior of T<sub>case</sub>.

Temperature (°C) 75.0

55.0

45.0

0 50 100 150 200

Intel® Xeon Phi™ Coprocessor Si Power (W)

Figure 3-17 SE10X/7120X SKU Coprocessor Case Temperature (T<sub>case)</sub> vs Power

For the region A-B, the cooling solution must maintain the case temperature below 95°C which will in turn maintain the coprocessor silicon junction temperature below 104°C. Assuming an air-cooled heat sink, at a maximum coprocessor power dissipation of 198W (Figure 3-9) and an inlet air temperature of 45°C, the following equation between coprocessor junction-to-case and case-to-air heat sink rating can be used to determine the minimum necessary performance of a cooling system:

$$T_{junction} = \Psi_{jc} * CPU_{power} + \Psi_{ca\_req} * CPU_{power} + T_{ambient}$$

The heat sink must have a  $\Psi_{\text{ca\_req}}$  value adequate to keep the coprocessor junction temperature at or below 104°C. The value for  $\Psi_{jc}$  is a characteristic of the Intel® Xeon  $\text{Phi}^{\text{\tiny{TM}}}$  coprocessor and may be treated as 0.047, a constant.

As the coprocessor power level goes down (region B-C), it is desirable to keep the junction temperature at or below a target temperature, here shown at 82°C. Since each coprocessor is programmed at the factory with the actual control temperature ( $T_{control}$ ), a sophisticated cooling system may continuously read the junction temperature from the card SMC and compare it to the programmed  $T_{control}$  to adjust airflow. The change in airflow over an air cooled heat sink affects the  $\Psi_{ca}$  value. It is common to reduce fan speed when maximum airflow is not needed to save power, reduce noise, or both.

In the B-C region, even though  $T_{junction}$  is at a constant value,  $T_{case}$  actually goes up a little bit at lower power consumption levels. This is because a variable fan speed results in a variable  $\Psi_{ca}$ , but a fixed  $\Psi_{ic}$ .

Finally, in the C-D region where the coprocessor consumes very little power, an air cooled heat sink using a variable fan speed to maintain a target junction temperature may slow the airflow down too much. If the airflow is too low, the junction temperature may be maintained properly, but the exhaust air temperature approaches the junction temperature. Data center design considerations, including safety, may dictate that a maximum allowable exhaust air temperature, such as 70°C, which in turn will set a maximum limit on  $\Psi_{\text{ca}}.$

### 3.4.3 Mechanical Considerations

- In the passive Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor products, the only component on the card with IHS load is the coprocessor. The compressive load is assumed to be approximately uniformly distributed over the IHS. The minimum load is 23lbf and maximum load is 75lbf. The mean pressure on the IHS is 33lbf.

- Hitachi Type7 is recommended as the thermal interface material (TIM).

- The gap filler used is the Bergquist 3500S35.

- The Intel passive heat sink is designed to nominal gaps of

GDDR: 0.3 +/- 0.1225 mm

VR FETs: 0.511 +/- 0.1225 mm

VR Inductors: 0.5 +/- 0.2 mm

Table 3-4 shows the maximum heights of the different components on the SE10X/7120X and 7120D/5120D products, along with the heights used in the product board design. Figure 3-18 and Figure 3-19 show the front and back sides of the SE10X/7120X SKU. Refer to the  $Intel^{\circledR}$  Xeon  $Phi^{\intercal}$  Coprocessor Thermal Mechanical Models document for the SE10X/7120X SKU. Refer to the  $Intel^{\circledR}$  Xeon  $Phi^{\intercal}$  Coprocessor Dense Form Factor Models document for information on 5120D SKU.

**Table 3-4. Board Component Heights**

| Block                     | Color <sup>1</sup> | Component Height (mils) |         |         |

|---------------------------|--------------------|-------------------------|---------|---------|

|                           |                    | Min                     | Тур     | Max     |

| PCB Thickness             |                    | 57                      | 62      | 70      |

| Coprocessor               |                    | 171.221                 | 177.992 | 184.763 |

| GDDR                      | Orange             |                         | 47      | 47.25   |

| VR Inductor               | Yellow             |                         | 217     | 217     |

| VR phase controller       | Red                |                         | 35      | 39.37   |

| Coprocessor VR controller | Green              |                         | 37      | 37      |

| GDDR VR<br>controller     | Pink               |                         | 35      | 35.43   |

| Capacitor<br>topside      | Purple             |                         | 49      | 49      |

| Capacitor<br>backside     | Light blue         |                         | 83      | 83      |

#### Notes:

Document ID Number: 328209 004EN

1. Colors are in reference to Figure 3-18, Figure 3-19, Figure 3-20 and Figure 3-21.

Figure 3-18 SE10X/7120X Board Top Side

Figure 3-19 SE10X/7120X Board Bottom Side

Figure 3-20 7120D/5120D Board Top Side

Figure 3-21 7120D/5120D Board Bottom Side

#### 3.4.4 **Mechanical Shock and Vibration Testing**

Table 3-5 shows the recommended shock and vibration guidelines, and dynamic load shift specifications.

**Dynamic Load Shift Specification Table 3-5.**

| Test                              | Specification and Guidelines                                                                                                                                                                 |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Board Unpackaged Shock            | 50g trapezoidal; V:170in/s<br>drops: 3x each on 6 faces                                                                                                                                      |

| Board Unpackaged Random Vibration | 5Hz @ 0.01g <sup>2</sup> /Hz to 20Hz @0.02g <sup>2</sup> /Hz (slope up)<br>20Hz to 500Hz @ 0.02g <sup>2</sup> /Hz (flat)<br>Input acceleration is 2313g RMS<br>10mins per axis in all 3 axis |

**Table 3-5.** Dynamic Load Shift Specification

| Test                                  | Specification and Guidelines                                                                                                                                                                    |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Unpackaged Shock               | 25g trapezoidal; Varies by system weight (20-39lbs: 225 in/sec; 40-79lbs: 205 in/sec) drops: 2x each of 6 faces                                                                                 |

| System Unpackaged Random<br>Vibration | 5Hz @ 0.001g <sup>2</sup> /Hz to 20Hz @0.001g <sup>2</sup> /Hz (slope up)<br>20Hz to 500Hz @ 0.001g <sup>2</sup> /Hz (flat)<br>Input acceleration is 2.20g RMS<br>10mins per axis in all 3 axis |

# 3.5 Intel® Xeon Phi™ Coprocessor PCI Express\* Card Extender Bracket Installation

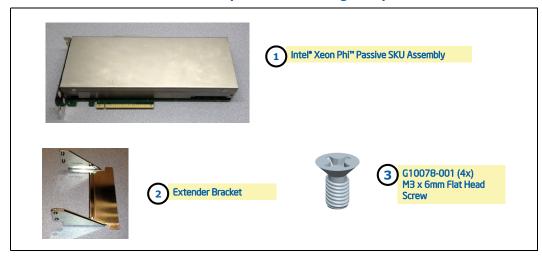

Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor cards are shipped without the PCI Express\* bracket (also known as extender bracket) being installed on the card. The purpose of this bracket is to interface with the chassis mechanical card guides for standard full-length PCI Express\* cards. In the shipped package, customers should expect to find:

- One Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor card with assembled thermal solution.

- One Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor card extender bracket.

- Four M3 x6mm flat head screws.

**Note:** The SE10X/7120X and 7120D/5120D SKUs are not shipped with the extender bracket.

Figure 3-22 Contents of Intel® Xeon Phi™ Coprocessor Package Shipment

#### **Bracket Installation Steps** 3.5.1

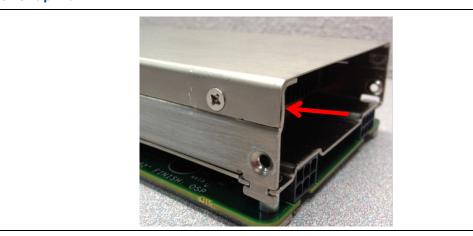

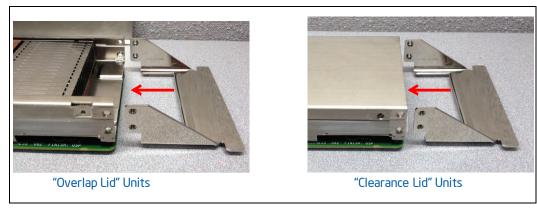

1. Determine Lid Type.

If the lid type is "overlap" where the lid covers the top mounting holes as shown in Figure 3-23, then go to Step 2.

If the lid type is "clearance" where the lid has cut-outs for mounting holes as shown in Figure 3-24, then go to Step 3.

Figure 3-23 Overlap Lid

Figure 3-24 Clearance Lid

- 2. Remove Overlap Lid.

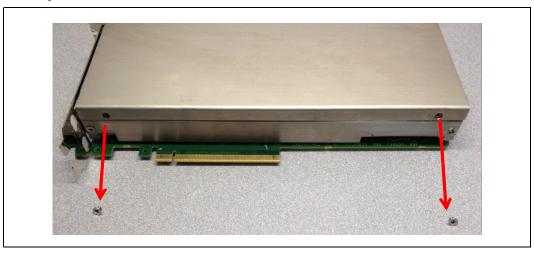

- a. Remove 2 of the M3x6mm screws retaining the lid, as shown in Figure 3-25.

Figure 3-25 Overlap Lid Removal

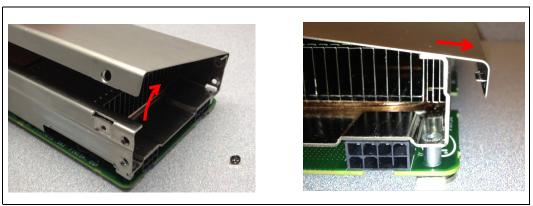

b. Remove Lid. Take care not to bend tabs, as shown in Figure 3-26.

Figure 3-26 Tilt Overlap Lid and Slide as shown to Disengage Tabs

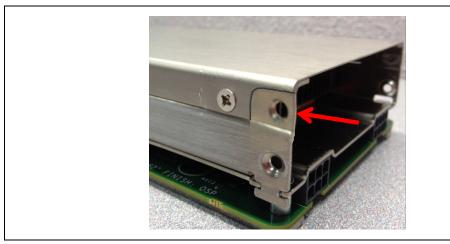

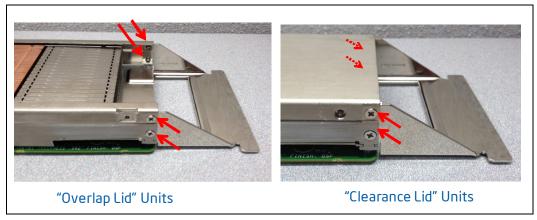

#### 3. Install OEM Bracket.

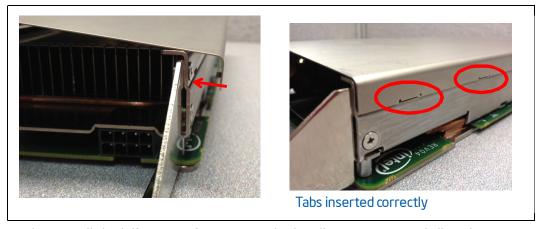

a. Insert the OEM bracket into the Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor card assembly, as shown in Figure 3-27.

Figure 3-27 OEM Bracket Installation

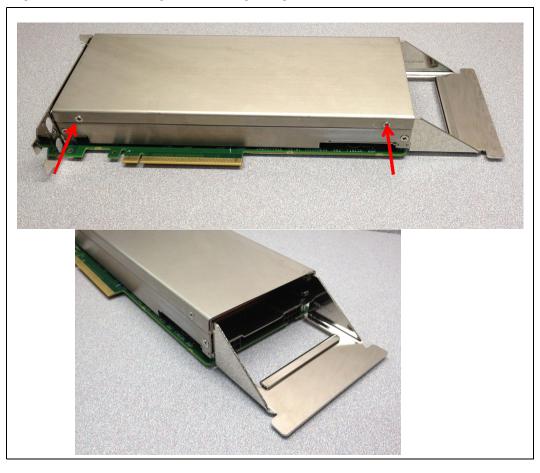

b. Install (4) M3 x 6mm Flat Head Screws; torque = 6inch-lbs, shown in Figure 3-

Figure 3-28 OEM Bracket Installation

Document ID Number: 328209 004EN

At this point, "clearance lid" units are ready to be mounted in the chassis.

- 4. Replace Lid on "Overlap Lid" Units Only

- a. Insert tabs into slots in card assembly, shown in Figure 3-29.

Figure 3-29 Replace Lid on "Overlap Lid" Units

b. Install the lid's screws (M3 x 6mm Flat head); torque = 6 inch-lbs, shown in Figure 3-30.

Figure 3-30 Replace Lid on "Overlap Lid" Units (cont.)

# 4 Intel<sup>®</sup> Xeon Phi<sup>™</sup> Coprocessor Pin Descriptions

# 4.1 PCI Express\* Signals

The PCI Express\* connector for the Intel<sup>®</sup> Xeon Phi<sup>TM</sup> coprocessor is a x16 interface and supports signals defined in the "PCI Express\* Card Electromechanical Specification". Signals called out in the PCI Express\* specification but not used on the Intel<sup>®</sup> Xeon Phi<sup>TM</sup> coprocessor are listed as "not used" in Table 4-1.

The symbol \_N at the end of a signal name indicates that the active or asserted state occurs when the signal is at a low voltage level. When \_N is not present after the signal name, the signal is asserted when at the high voltage level.

The following notations are used to describe the signal type:

- I Signal is an Input to the Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor

- O Signal is an Output from the Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor

- I/O Bidirectional Input/Output signal

- S Sense pin

Document ID Number: 328209 004EN

P Power supply signal, sourced from the PCI Express\* edge fingers or supplemental power connectors.

**Table 4-1.** PCI Express\* Connector Signals on the Intel® Xeon Phi™ Coprocessor

| Signal Name                                  | Signal<br>Type | Description                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXP_A_TX_[15:0]_DP<br>EXP_A_TX_[15:0]_DN     | 0              | PCI Express* Differential Transmit Pairs: 16-channel differential transmit pairs, referenced to the Intel <sup>®</sup> Xeon Phi <sup>™</sup> coprocessor. The EXP_A_TX_[15:0]_DP and EXP_A_TX_[15:0]_DP are connected to the PCI Express* device transmit pairs on the Intel <sup>®</sup> Xeon Phi <sup>™</sup> coprocessor. |

| EXP_A_RX_[15:0]_DP<br>EXP_A_RX_[15:0]_DN     | I              | PCI Express* Differential Receive Pairs: 16-channel differential receive pairs referenced to the Intel <sup>®</sup> Xeon Phi <sup>™</sup> coprocessor. The EXP_A_RX_[15:0]_DP and EXP_A_RX_[15:0]_DP are connected to the PCI Express* device receive pairs on the Intel <sup>®</sup> Xeon Phi <sup>™</sup> coprocessor.     |

| CK_PE_100M_16PORT_DP<br>CK_PE_100M_16PORT_DN | I              | PCI Express* Reference Clock: 100MHz differential clock I to Intel® Xeon Phi™ coprocessor for use by the coprocessor to properly recover data from the PCI Express* Interface.                                                                                                                                               |

| RST_PCIE_N                                   | I              | PCI Express* Reset Signal: RST_PCIE_N is a 3.3-volt active-low signal that when deasserted (high) indicates that the +12V and VCC3 power supplies are stable and within their specified tolerance.                                                                                                                           |

Table 4-1. PCI Express\* Connector Signals on the Intel® Xeon Phi™ Coprocessor