## int<sub>el</sub>.

### Intel<sup>®</sup> 82870P2 PCI/PCI-X 64-bit Hub 2 (P64H2)

**Datasheet**

January 2003

Document Number: 290732-002

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> PCI/PCI-X 64-bit Hub 2 (P64H2) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

www.intel.com

or call 1-800-548-4725

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2003, Intel Corporation

# int<sub>el</sub>,

### **Contents**

| <ol> <li>Related Documents</li></ol>                                                                                                                                | 17<br>19<br>21<br>25<br>27<br>28<br>29<br>31<br>31<br>32 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1.2       Intel <sup>®</sup> P64H2 Overview         2       Signal Description         2.1       Hub Interface         2.2       PCI Bus Interface 64-bit Extension | 17<br>19<br>21<br>25<br>27<br>28<br>29<br>31<br>31<br>32 |

| <ul> <li>2.1 Hub Interface</li> <li>2.2 PCI Bus Interface 64-bit Extension</li> </ul>                                                                               | 21<br>25<br>27<br>28<br>29<br>31<br>31<br>32             |

| 2.2 PCI Bus Interface 64-bit Extension                                                                                                                              | 25<br>27<br>28<br>29<br>31<br>31<br>32                   |

| 2.2 PCI Bus Interface 64-bit Extension                                                                                                                              | 25<br>27<br>28<br>29<br>31<br>31<br>32                   |

|                                                                                                                                                                     | 27<br>28<br>29<br>31<br>31<br>32                         |

|                                                                                                                                                                     | 28<br>29<br>31<br>31<br>32                               |

| 2.4 Interrupt Interface                                                                                                                                             | 29<br>31<br>31<br>32                                     |

| 2.5 Hot Plug Interface                                                                                                                                              | 31<br>31<br>32                                           |

| 2.6 SMBus Interface                                                                                                                                                 | 31<br>32                                                 |

| 2.7 Miscellaneous Signals                                                                                                                                           | 32                                                       |

| 2.8 Power and Reference Voltage Signals                                                                                                                             |                                                          |

| 2.9 Pin Straps                                                                                                                                                      |                                                          |

|                                                                                                                                                                     |                                                          |

| 3 Register Description                                                                                                                                              |                                                          |

| 3.1 Register Nomenclature and Access Attributes                                                                                                                     |                                                          |

| 3.2 Hub Interface-to-PCI Bridge PCI Configuration Registers (Device 31 and 29)                                                                                      |                                                          |

| 3.2.1 VID—Vendor ID Register (D29,31: F0)                                                                                                                           |                                                          |

| 3.2.2 DID—Device ID Register (D29,31: F0)                                                                                                                           |                                                          |

| <ul> <li>3.2.3 PD_CMD—PCI Primary Device Command Register (D29,31: F0)</li> <li>3.2.4 PD_STS—PCI Primary Device Status Register (D29,31: F0)</li> </ul>             |                                                          |

| 3.2.5 RID—Revision ID Register (D29,31: F0)                                                                                                                         |                                                          |

| 3.2.6 CC—Class Code Register (D29,31: F0)                                                                                                                           |                                                          |

| 3.2.7 CLS—Cache Line Size Register (D29,31: F0)                                                                                                                     |                                                          |

| 3.2.8 PMLT—Primary Master Latency Timer Register (D29,31: F0)                                                                                                       |                                                          |

| 3.2.9 HEADTYP—Header Type Register (D29,31: F0)                                                                                                                     |                                                          |

| 3.2.10 BNUM—Bus Number Register (D29,31: F0)                                                                                                                        |                                                          |

| 3.2.11 SMLT—Secondary Master Latency Timer (D29,31: F0)                                                                                                             |                                                          |

| 3.2.12 IOBL_ADR—I/O Base and Limit Address Register D29,31: F04                                                                                                     |                                                          |

| 3.2.13 SECSTS—Secondary Status Register (D29,31: F0)<br>3.2.14 MBL ADR—Memory Base and Limit Address Register (D29.31: F0)                                          |                                                          |

| 3.2.14 MBL_ADR—Memory Base and Limit Address Register (D29,31: F0)<br>3.2.15 PMBL_ADR—Prefetchable Memory Base and Limit Address                                    | . 40                                                     |

| Register (D29,31: F0)                                                                                                                                               | 46                                                       |

| 3.2.16 PREF_MEM_BASE_UPPER—Prefetchable Memory Base                                                                                                                 | 10                                                       |

| Upper 32 Bit Address Register (D29,31: F0)                                                                                                                          | 47                                                       |

| 3.2.17 PREF_MEM_LIM_UPPER—Prefetchable Memory Limit                                                                                                                 |                                                          |

| Upper 32 Bit Address Register (D29,31: F0)                                                                                                                          | 47                                                       |

| 3.2.18 IOBLU16_ADR—I/O Base and Limit Upper 16 Bit Address                                                                                                          | 17                                                       |

| Register (D29,31: F0)<br>3.2.19 CAPP—Capabilities List Pointer Register (D29,31: F0)                                                                                |                                                          |

| 3.2.20 INTR—Interrupt Information Register (D29,31: F0)                                                                                                             |                                                          |

| 3.2.21 BRIDGE_CNT—Bridge Control Register (D29,911 F0)                                                                                                              |                                                          |

| 3.2.22 CNF—P64H2 Configuration Register (D29,31: F0)                                                                                                                |                                                          |

| 3.2.23 MTT—Multi-Transaction Timer Register (D29,31: F0)                                                                                                            |                                                          |

## int<sub>el</sub>,

| 3.2.24   | STRP-P     | CI Strap Status Register (D29,31: F0)                     | . 52 |

|----------|------------|-----------------------------------------------------------|------|

| 3.2.25   |            | D—PCI-X Capabilities Identifier Register (D29,31: F0)     |      |

| 3.2.26   |            | -PCI-X Secondary Status Register (D29,31: F0)             |      |

| 3.2.27   |            | -PCI-X Bridge Status Register (D29,31: F0)                |      |

| 3.2.28   |            | —PCI-X Upstream Split Transaction Control                 |      |

|          | Register ( | D29,31: F0)                                               | . 55 |

| 3.2.29   |            | —PCI-X Downstream Split Transaction Control               |      |

|          | Register ( | D29,31: F0)                                               | . 55 |

| 3.2.30   |            | —RAS Status Register (D29,31: F0)                         |      |

| 3.2.31   | RAS_DI-    | -RAS Data Integrity Codes Register (D29,31: F0)           | . 59 |

| 3.2.32   | RAS_PH-    | -RAS PCI Header Register (D29,31: F0)                     | . 59 |

| 3.2.33   | RAS_PAL    | -RAS PCI Address Low Register (D29,31: F0)                | . 60 |

| 3.2.34   | RAS_PAF    | I-RAS PCI Address High Register (D29,31: F0)              | . 60 |

| 3.2.35   | RAS_PDL    | -RAS PCI Data Low 32 Bits Register (D29,31: F0)           | . 60 |

| 3.2.36   | RAS_PDH    | I-RAS PCI Data High 32 bits Register (D29,31: F0)         | . 61 |

| 3.2.37   | RAS_HH-    | -RAS Hub Interface Header Register (D29,31: F0)           | . 61 |

| 3.2.38   | RAS_HAL    | -RAS Hub Interface Address Low 32 Bits                    |      |

|          | Register ( | D29,31: F0)                                               | . 61 |

| 3.2.39   | RAS_HAR    | I—RAS Hub Interface Address High 32 Bits                  |      |

|          | Register ( | D29,31: F0)                                               | . 62 |

| 3.2.40   | RAS_HP-    | -RAS Hub Interface Prefetch Horizon Register (D29,31: F0  | ))62 |

| 3.2.41   | RAS_D0-    | -RAS Hub Interface DWord 0 Register (D29,31: F0)          | . 62 |

| 3.2.42   | RAS_D1-    | -RAS Hub Interface DWord 1 Register (D29,31: F0)          | . 63 |

| 3.2.43   | RAS_D2-    | -RAS Hub Interface DWord 2 Register (D29,31: F0)          | . 63 |

| 3.2.44   | RAS_D3-    | -RAS Hub Interface DWord 3 Register (D29,31: F0)          | . 63 |

| 3.2.45   | ACNF—A     | dditional P64H2 Configuration Register (D29,31: F0)       | . 64 |

| 3.2.46   | PCC—PC     | I Delay Compensation Control Register (D29,31: F0)        | . 66 |

| 3.2.47   | HCCR       | lub Interface Command/Control Register (D29,31: F0)       | . 67 |

| 3.2.48   | Prefetch ( | Control Registers                                         |      |

|          | 3.2.48.1   | PC33—Prefetch Control for 33 MHz<br>Register (D29,31: F0) |      |

|          |            | Register (D29,31: F0)                                     | . 68 |

|          | 3.2.48.2   | PC66—Prefetch Control for 66 MHz<br>Register (D29,31: F0) |      |

|          |            | Register (D29,31: F0)                                     | . 68 |

|          | 3.2.48.3   | PC100—Prefetch Control for 100 MHz                        |      |

|          |            | Register (D29,31: F0)                                     | . 69 |

|          | 3.2.48.4   | PC133—Prefetch Control for 133 MHz                        |      |

|          |            | Register (D29,31: F0)                                     | . 69 |

| Hot Plug | Controller | Registers (Device 31)                                     | . 70 |

| 3.3.1    | PCI Confi  | guration Registers                                        | . 70 |

|          | 3.3.1.1    | VID—Vendor ID Register (Device 31)                        |      |

|          | 3.3.1.2    | DID—Device ID Register (Device 31)                        |      |

|          | 3.3.1.3    | PCICMD—PCI Command Register (Device 31)                   |      |

|          | 3.3.1.4    | PCISTS—PCI Status Register (Device 31)                    |      |

|          | 3.3.1.5    | RID—Revision ID Register (Device 31)                      |      |

|          | 3.3.1.6    | CC-Class Code Register (Device 31)                        |      |

|          | 3.3.1.7    | MBAR-Memory Base Register (Device 31)                     |      |

|          | 3.3.1.8    | MBARU—Memory Base Address (Upper 32-bits)                 |      |

|          | -          | Register (Device 31)                                      | . 73 |

|          | 3.3.1.9    | SVID—Subsystem Vendor ID Register (Device 31)             | . 74 |

|          | 3.3.1.10   | SID—Subsystem ID Register (Device 31)                     |      |

|          | 3.3.1.11   | CAP_PTR—Capabilities Pointer Register (Device 31)         | . 74 |

|          | 3.3.1.12   | INTR—Interrupt Information Register (Device 31)           |      |

|          | 3.3.1.13   | SID—Slot ID Register (Device 31)                          |      |

|          | -          | <b>J</b> ( , , , , , , , , , , , , , , , , , ,            | -    |

3.3

|         | 3.3.1.14    | HPFC—Hot Plug Frequency Control Register                          |    |

|---------|-------------|-------------------------------------------------------------------|----|

|         |             | (Device 31)                                                       | 75 |

|         | 3.3.1.15    | MCNF—Miscellaneous Configuration Register                         |    |

|         |             | (Device 31)                                                       | 76 |

|         | 3.3.1.16    | FTR—Features Register (Device 31)                                 | 78 |

|         | 3.3.1.17    | SSEL—Slot Status Select Register (Device 31)                      |    |

|         | 3.3.1.18    | SSTS—Slot Status Register (Device 31)                             | 79 |

|         | 3.3.1.19    | SERR—SERR Status Register (Device 31)                             | 80 |

|         | 3.3.1.20    | MIDX—Alternate Memory Access Index Port Register                  |    |

|         |             | (Device 31)                                                       | 80 |

|         | 3.3.1.21    | MDTA—Alternate Memory Access Data Port Register                   |    |

|         |             | (Device 31)                                                       |    |

|         | 3.3.1.22    | XID—PCI-X Identifiers Register (Device 31)                        |    |

|         | 3.3.1.23    | XCR—PCI-X Command Register (Device 31)                            |    |

|         | 3.3.1.24    | XSR—PCI-X Status Register (Device 31)                             |    |

|         | 3.3.1.25    | ABAR—Alternate Base Register (Device 31)                          |    |

| 3.3.2   | Memory S    | Space Registers                                                   |    |

|         | 3.3.2.1     | GPT—General Purpose Timer Register                                |    |

|         | 3.3.2.2     | SE—Slot Enable Register                                           | 84 |

|         | 3.3.2.3     | MCNF—Miscellaneous Configuration Register                         |    |

|         | 3.3.2.4     | LEDC—LED Control Register                                         | 87 |

|         | 3.3.2.5     | HMIC—Hot Plug Interrupt Input and Clear Register                  | 88 |

|         | 3.3.2.6     | HMIR—Hot Plug Interrupt Mask Register                             | 89 |

|         | 3.3.2.7     | SIR—Serial Input Register                                         |    |

|         | 3.3.2.8     | GPO—General Purpose Output Register                               |    |

|         | 3.3.2.9     | HMIN—Hot Plug Non-Interrupt Inputs Register                       | 91 |

|         | 3.3.2.10    | SID—Slot ID Register                                              |    |

|         | 3.3.2.11    | SIRE—Switch Interrupt Redirect Enable Register                    | 91 |

|         | 3.3.2.12    | SPE—Slot Power Enable Register                                    |    |

|         | 3.3.2.13    | EMR—Extended Hot Plug Miscellaneous Register                      | 93 |

| I/OxAPI | C Interrupt | Controller Registers                                              | 94 |

| 3.4.1   | PCI Conf    | iguration Space Registers (Device 28 and 30)                      | 94 |

|         | 3.4.1.1     | VID—Vendor ID Register (D28,30: F0)                               |    |

|         | 3.4.1.2     | DID—Device ID Register (D28,30: F0)                               |    |

|         | 3.4.1.3     | PCICMD—PCI Device Command Register (D28,30: F0).                  |    |

|         | 3.4.1.4     | PCISTS—PCI Device Status Register (D28,30: F0)                    |    |

|         | 3.4.1.5     | RID—Revision ID Register (D28,30: F0)                             |    |

|         | 3.4.1.6     | CC-Class Code Register (D28,30: F0)                               |    |

|         | 3.4.1.7     |                                                                   |    |

|         | 3.4.1.8     | HDR—Header (D28,30: F0)<br>MBAR—Memory Base Register (D28,30: F0) | 98 |

|         | 3.4.1.9     | SS—Subsystem Identifier Register (D28,30: F0)                     |    |

|         | 3.4.1.10    | CAP_PTR—Capabilities Pointer Register (D28,30: F0)                |    |

|         | 3.4.1.11    | ABAR—Alternate Base Address Register (D28,30: F0)                 |    |

|         | 3.4.1.12    | XID—PCI-X Identifier Register (D28,30: F0)                        |    |

|         | 3.4.1.13    | XCR—PCI-X Command Register (D28,30: F0)                           |    |

|         | 3.4.1.14    | XSR—PCI-X Status Register (D28,30: F0)                            |    |

| 3.4.2   |             | emory Space Registers                                             |    |

|         | 3.4.2.1     | IDX—Index Register (D28,30: F0)                                   |    |

|         | 3.4.2.2     | WND—Window Register (D28,30: F0)                                  |    |

|         | 3.4.2.3     | PAR—IRQ Pin Assertion Register (D28,30: F0)                       |    |

|         | 3.4.2.4     | EOI—End of Interrupt Register (D28,30: F0)                        |    |

3.4

## int<sub>el</sub>.

|        | 3.4.3     | Indirect N | lemory Space Registers                             |       |

|--------|-----------|------------|----------------------------------------------------|-------|

|        |           | 3.4.3.1    | ID—APIC ID Register (D28,30: F0)                   | . 103 |

|        |           | 3.4.3.2    | VS—Version Register (D28,30: F0)                   |       |

|        |           | 3.4.3.3    | ARBID—Arbitration ID Register (D28,30: F0)         | . 104 |

|        |           | 3.4.3.4    | BCFG—Boot Configuration Register (D28,30: F0)      | . 105 |

|        |           | 3.4.3.5    | RDL—Redirection Table Low DWord Register           |       |

|        |           |            | (D28,30: F0)                                       |       |

|        |           | 3.4.3.6    | RDH—Redirection Table High Register (D28,30: F0)   | . 106 |

| 3.5    | SMBus     |            |                                                    |       |

|        | 3.5.1     | CMDSTS     | -Command / Status Register                         | . 108 |

|        | 3.5.2     | BNUM—I     | Bus Number Register                                | . 109 |

|        |           | 3.5.2.1    | DFNUM—Device / Function Number Register            | . 109 |

|        | 3.5.3     | RNUM—      | Register Number                                    | . 109 |

|        |           | 3.5.3.1    | DATA—Data Register                                 | . 110 |

|        | 3.5.4     | CFG—SM     | /Bus Configuration Register                        | . 110 |

| Functi | onal Desc | rintion    |                                                    | 112   |

|        |           | •          |                                                    |       |

| 4.1    |           |            |                                                    |       |

|        | 4.1.1     |            | of Changes                                         |       |

|        | 4.1.2     |            | on Types                                           |       |

|        | 4.1.3     |            | of 64-bit Environment                              |       |

|        | 4.1.4     |            |                                                    |       |

|        | 4.1.5     |            | nsactions                                          |       |

|        | 4.1.6     |            | ation Transactions                                 |       |

|        | 4.1.7     |            | on Termination                                     |       |

|        | 4.1.8     |            | les                                                |       |

|        | 4.1.9     |            | ndling                                             |       |

|        |           | 4.1.9.1    | Address Parity Errors                              |       |

|        |           | 4.1.9.2    | Data Parity Errors                                 |       |

|        |           | 4.1.9.3    | Hub Interface Configuration Write Transactions     |       |

|        |           | 4.1.9.4    | Read Transactions from Hub Interface Targeting PCI |       |

|        |           | 4.1.9.5    | Read Transactions from PCI Targeting Hub Interface | . 121 |

|        |           | 4.1.9.6    | Write Transactions on Hub Interface                |       |

|        |           |            | (Intel <sup>®</sup> P64H2 As Hub Interface Target) | . 122 |

|        |           | 4.1.9.7    | Write Transactions on Hub Interface                | 400   |

|        |           |            | (Intel <sup>®</sup> P64H2 As Hub Interface Master) | . 122 |

|        |           | 4.1.9.8    | Write Transactions on PCI                          | 400   |

|        |           | 1100       | (Intel <sup>®</sup> P64H2 As PCI Target)           | . 122 |

|        |           | 4.1.9.9    | Write Transactions on PCI                          | 400   |

|        |           | 4 4 0 40   | (Intel <sup>®</sup> P64H2 As PCI Master)           |       |

|        |           | 4.1.9.10   | System Errors<br>PCI SERR# Pin Assertion           |       |

|        |           | 4.1.9.11   |                                                    |       |

| 4.0    |           | 4.1.9.12   | Other System Errors                                |       |

| 4.2    |           |            |                                                    |       |

|        | 4.2.1     |            | d Encoding                                         |       |

|        | 4.2.2     |            |                                                    |       |

|        | 4.2.3     |            | nsactions                                          |       |

|        | 4.2.4     |            | elect Timing                                       |       |

|        | 4.2.5     |            | es                                                 |       |

|        | 4.2.6     | •          | sactions                                           |       |

|        |           | 4.2.6.1    | Completer Attributes                               |       |

|        |           | 4.2.6.2    | Requirements for Accepting Split Completions       |       |

|        |           | 4.2.6.3    | Split Completion Messages                          | . 126 |

|     | 4.2.7          | Arbitratio | n Among Multiple Split Completions                   | 127 |

|-----|----------------|------------|------------------------------------------------------|-----|

|     | 4.2.8          | Transacti  | on Termination as a PCI-X Target                     | 127 |

|     | 4.2.9          | Arbitratio | n                                                    | 127 |

|     | 4.2.10         | System I   | nitialization                                        | 128 |

|     | 4.2.11         | Bridge Bu  | uffer Requirements                                   | 129 |

|     | 4.2.12         |            | Inslation Between Interfaces                         |     |

|     |                | 4.2.12.1   | Conventional PCI to PCI-X / Hub Interface            | 129 |

|     |                | 4.2.12.2   | PCI-X to Conventional PCI (peer) / Hub Interface     | 130 |

|     | 4.2.13         | Locked T   | ransactions                                          |     |

|     | 4.2.14         | Error Sup  | port                                                 | 130 |

|     | 4.2.15         |            | on Termination Translation Between Interfaces        |     |

|     |                | 4.2.15.1   | Behavior of Hub Interface Initiated Cycles to        |     |

|     |                |            | PCI/PCI-X Receiving Immediate Terminations           | 131 |

|     |                | 4.2.15.2   | Behavior of Hub Interface Initiated Cycles to        |     |

|     |                |            | PCI-X Receiving Split Terminations                   | 132 |

|     |                | 4.2.15.3   | Hub Interface Action on Immediate Responses to       |     |

|     |                |            | PCI-X Split Completions                              | 133 |

|     | 4.2.16         | Configura  | ation Transactions                                   |     |

| 4.3 | Hot Pluc       |            | s                                                    |     |

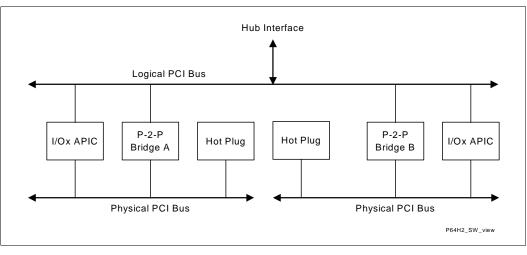

|     | 4.3.1          | •          | vrchitecture                                         |     |

|     | 1.0.1          | 4.3.1.1    | Output Control                                       |     |

|     |                | 4.3.1.2    | Input Control                                        |     |

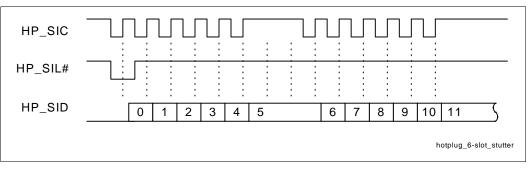

|     |                | 4.3.1.3    | Stutter Mode                                         |     |

|     |                | 4.3.1.4    | Serial Input Stream                                  |     |

|     |                | 4.3.1.5    | Serial Output Stream                                 |     |

|     |                | 4.3.1.6    | Power Sequencing                                     |     |

|     |                | 4.3.1.7    | Arbitration                                          |     |

|     |                | 4.3.1.8    | Power-on and Reset Initialization                    |     |

|     |                | 4.3.1.9    | PCI Card Initialization                              |     |

|     |                | 4.3.1.10   | Changing PCI Frequency/Modes                         |     |

|     | 4.3.2          |            | blexing in Single and Dual Slot Modes                |     |

|     | 4.3.3          |            | ot Mode PCI Bus Effects                              |     |

|     | 4.0.0          | 4.3.3.1    | Driving Bus To Ground When PCI Card is               | 100 |

|     |                | 1.0.0.1    | Disconnected                                         | 150 |

|     |                | 4.3.3.2    | Aborting Outbound PCI Cycles When Card is            |     |

|     |                | 1.0.0.2    | Disconnected                                         | 151 |

|     |                | 4.3.3.3    | Special Note on M66EN in Single Slot Mode            |     |

|     | 4.3.4          |            | ng SCI Instead of Interrupt                          |     |

|     | 4.3.5          |            | the Hot Plug Controller                              |     |

| 4.4 |                | -          |                                                      |     |

| 4.4 | 4.4.1          | •          | ow Addressing                                        |     |

|     | 4.4.1<br>4.4.2 |            | Window Addressing                                    |     |

|     | 4.4.Z          | 4.4.2.1    | Memory Base and Limit Address Registers              |     |

|     |                | 4.4.2.1    | Prefetchable Memory Base and Limit Address Registers | 103 |

|     |                | 4.4.2.2    | Registers, Upper 32-bit Registers                    | 150 |

|     | 4.4.3          |            |                                                      |     |

|     |                |            | Iressing                                             | 104 |

|     | 4.4.4          | Conngura   | ation Addressing                                     | 155 |

| 4.5.1       Comparison of Rules vs A PCI–PCI Bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5 | Transac   | tion Orderir  | ng                                               | 156 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|---------------|--------------------------------------------------|-----|

| 4.5.2       Ordering Relationships       156         4.5.3       Hub Interface Fence Special Cycle       157         4.5.4       Master Abort / Target Abort Completions on Hub Interface       157         4.5.4.1       Behavior of Hub Interface Initiated Cycles to<br>PCI/PCI-X Receiving Immediate Terminations       157         4.5.4.2       Behavior of Hub Interface Initiated Cycles PCI-X<br>Receiving Split Terminations       158         4.5.4.3       Hub Interface Action on Immediate Responses to<br>PCI-X Split Completions       159         4.5.4.4       Behavior of PCI/PCI-X Initiated Cycles to Hub Interface       159         4.6.1       Interrupt Controller (Device 30 and 28)       160         4.6.1       Interrupt Insertion       160         4.6.1       Pront-Side Interrupts (MSI)       160         4.6.2       Interrupt Delivery       160         4.6.3       Buffer Flushing       162         4.6.4       Bot Interrupt       162         4.7.1       Waveforms       163         4.7.1       Waveforms       164         4.7.1.2       Architecture       166         4.7.1.3       Data Transfer Examples       168         4.7.1.4       Configuration Space Registers       169         4.7.1.5       Memory Space Re                                            |     | 4.5.1     | Comparis      | on of Rules vs A PCI–PCI Bridge                  | 156 |

| 4.5.3       Hub Interface Fence Special Cycle       157         4.5.4       Master Abort / Target Abort Completions on Hub Interface       157         4.5.4.1       Behavior of Hub Interface Initiated Cycles to<br>PCI/PCI-X Receiving Immediate Terminations       157         4.5.4.2       Behavior of Hub Interface Initiated Cycles PCI-X<br>Receiving Split Terminations       158         4.5.4.3       Hub Interface Action on Immediate Responses to<br>PCI-X Split Completions       159         4.5.4.4       Behavior of PCI/PCI-X Initiated Cycles to Hub Interface       159         4.6.1       Interrupt Controller (Device 30 and 28)       160         4.6.1       Interrupt Insertion       160         4.6.1       Printerrupt Controller (Device 30 and 28)       160         4.6.1       Printerrupt Controller (Device 30 and 28)       160         4.6.2       Interrupt Insertion       160         4.6.3       Buffer Flushing       160         4.6.4       Boot Interrupt       160         4.6.3       Buffer Flushing       162         4.7.1       SMBus Signaling       163         4.7.1       Waveforms       164         4.7.1.1       Waveforms       164         4.7.1.3       Data Transfer Examples       168         4.7.1.4                                            |     | 4.5.2     |               |                                                  |     |

| 4.5.4       Master Abort / Target Abort Completions on Hub Interface       157         4.5.4.1       Behavior of Hub Interface Initiated Cycles to<br>PCI/PCI-X Receiving Immediate Terminations       157         4.5.4.2       Behavior of Hub Interface Initiated Cycles PCI-X<br>Receiving Split Terminations       158         4.5.4.3       Hub Interface Action on Immediate Responses to<br>PCI-X Split Completions       159         4.6       I/OxAPIC Interrupt Controller (Device 30 and 28)       160         4.6.1       Interrupt Insertion       160         4.6.1.2       Message Signaled Interrupts (MSI)       160         4.6.2       Interrupt Delivery       160         4.6.3       Butfer Flushing       162         4.6.4       Boot Interrupt       162         4.6.3       Butfer Flushing       162         4.6.4       Boot Interrupt       162         4.6.4       Boot Interrupt       162         4.7       SMBus Interface       163         4.7.1       Waveforms       164         4.7.1.4       Configuration Space Registers       169         4.7.2       Configuration Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171 <t< td=""><td></td><td>4.5.3</td><td></td><td></td><td></td></t<> |     | 4.5.3     |               |                                                  |     |

| 4.5.4.1       Behavior of Hub Interface Initiated Cycles to<br>PCI/PCI-X Receiving Immediate Terminations       157         4.5.4.2       Behavior of Hub Interface Initiated Cycles PCI-X<br>Receiving Split Terminations       158         4.5.4.3       Hub Interface Action on Immediate Responses to<br>PCI-X Split Completions       159         4.6       I/OxAPIC Interrupt Controller (Device 30 and 28)       160         4.6.1       Interrupt Insertion       160         4.6.1.1       Pin Interrupts       160         4.6.1.2       Message Signaled Interrupts (MSI)       160         4.6.2       Interrupt Delivery       160         4.6.3       Buffer Flushing       162         4.6.4       Boot Interrupt       160         4.6.3       Buffer Flushing       162         4.6.4       Boot Interrupt       162         4.6.3       Buffer Flushing       163         4.7.1       SMBus Signaling       163         4.7.1       Waveforms       164         4.7.1.1       Waveforms       166         4.7.1.3       Data Transfer Examples       169         4.7.2       Configuration Space Registers       169         4.7.4       Configuration Access Arbitration       170         4.8       Sys                                                                                        |     | 4.5.4     |               |                                                  |     |

| PCI/PCI-X Receiving Immediate Terminations         157           4.5.4.2         Behavior of Hub Interface Initiated Cycles PCI-X<br>Receiving Split Terminations         158           4.5.4.3         Hub Interface Action on Immediate Responses to<br>PCI-X Split Completions         159           4.5.4.4         Behavior of PCI/PCI-X Initiated Cycles to Hub Interface         159           4.6         I/OxAPIC Interrupt Controller (Device 30 and 28)         160           4.6.1         Interrupt Insertion         160           4.6.1.1         Pin Interrupts         160           4.6.2.1         Front-Side Interrupt Delivery         160           4.6.3         Buffer Flushing         162           4.6.4         Boot Interrupt         162           4.6.4         Boot Interrupt         162           4.6.3         Buffer Flushing         162           4.6.4         Boot Interrupt         162           4.7.1         SMBus Signaling         163           4.7.1.1         Waveforms         164           4.7.1.2         Architecture         166           4.7.1.3         Data Transfer Examples         169           4.7.1.4         Configuration Access Arbitration         170           4.8.2         Configuration Access Arbitration<                              |     |           |               |                                                  |     |

| 4.5.4.2       Behavior of Hub Interface Initiated Cycles PCI-X<br>Receiving Split Terminations       158         4.5.4.3       Hub Interface Action on Immediate Responses to<br>PCI-X Split Completions       159         4.6       I/OxAPIC Interrupt Controller (Device 30 and 28)       160         4.6.1       Interrupt Controller (Device 30 and 28)       160         4.6.1       Interrupt Controller (Device 30 and 28)       160         4.6.1       Pin Interrupts       160         4.6.2       Interrupt Delivery       160         4.6.2       Interrupt Delivery       160         4.6.3       Buffer Flushing       162         4.6.4       Boot Interrupt       162         4.7       SMBus Interface       163         4.7.1       SMBus Signaling       163         4.7.1.1       Wavforms       164         4.7.1.2       Architecture       166         4.7.1.3       Data Transfer Examples       168         4.7.1.4       Configuration Space Registers       169         4.7.1.5       Memory Space Registers       169         4.7.1       Software PCI Reset       172         4.8.1       Clocking       171         4.8.2       Component Reset       172                                                                                                                            |     |           |               | PCI/PCI-X Receiving Immediate Terminations       | 157 |

| Receiving Split Terminations         158           4.5.4.3         Hub Interface Action on Immediate Responses to<br>PCI-X Split Completions         159           4.5.4.4         Behavior of PCI/PCI-X Initiated Cycles to Hub Interface         159           4.6         I/OxAPIC Interrupt Controller (Device 30 and 28)         160           4.6.1         Interrupt Insertion         160           4.6.1         Interrupt Insertion         160           4.6.1.1         Pin Interrupts         160           4.6.2         Interrupt Delivery         160           4.6.2.1         Front-Side Interrupt Delivery         160           4.6.2.1         Front-Side Interrupt Delivery         160           4.6.3         Buffer Flushing         162           4.6.4         Boot Interrupt         162           4.7         SMBus Signaling         163           4.7.1         Waveforms         164           4.7.1.2         Architecture         166           4.7.1.3         Data Transfer Examples         168           4.7.1.4         Configuration Space Registers         169           4.7.1.5         Memory Space Registers         169           4.7.1         Configuration Access Arbitration         171                                                                         |     |           | 4.5.4.2       | Behavior of Hub Interface Initiated Cycles PCI-X |     |

| 4.5.4.3       Hub Interface Action on Immediate Responses to<br>PCI-X Split Completions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |           |               |                                                  | 158 |

| PCI-X Split Completions         159           4.5.4.4         Behavior of PCI/PCI-X Initiated Cycles to Hub Interface         159           4.6         I/OxAPIC Interrupt Controller (Device 30 and 28)         160           4.6.1         Interrupt Insertion         160           4.6.1         Pin Interrupts         160           4.6.1.1         Pin Interrupts         160           4.6.2         Interrupt Delivery         160           4.6.2.1         Front-Side Interrupt Delivery         160           4.6.3         Buffer Flushing         162           4.6.4         Boot Interrupt         162           4.6.4         Boot Interrupt         162           4.7         SMBus Interface         163           4.7.1         Waveforms         164           4.7.1.2         Architecture         166           4.7.1.3         Data Transfer Examples         168           4.7.1.4         Configuration Access Arbitration         170           4.8         System Setup         171           4.8.1         Clocking         171           4.8.2         Component Reset         172           4.8.2.3         PowerOK         173           4.8.2.4 <t< td=""><td></td><td></td><td>4.5.4.3</td><td></td><td></td></t<>                                                               |     |           | 4.5.4.3       |                                                  |     |

| 4.5.4.4       Behavior of PCI/PCI-X Initiated Cycles to Hub Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |           |               |                                                  | 159 |

| 4.6       I/OxAPIC Interrupt Controller (Device 30 and 28)       160         4.6.1       Interrupt Insertion       160         4.6.1       Pin Interrupts       160         4.6.1.1       Pin Interrupts       160         4.6.1.2       Message Signaled Interrupts (MSI)       160         4.6.2       Interrupt Delivery       160         4.6.3       Buffer Flushing       162         4.6.4       Boot Interrupt       162         4.6.4       Boot Interrupt       162         4.7       SMBus Signaling       163         4.7.1       SMBus Signaling       163         4.7.1       Waveforms       164         4.7.1.2       Architecture       166         4.7.1.4       Configuration Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.2.3       PowerOK       173         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173 </td <td></td> <td></td> <td>4.5.4.4</td> <td></td> <td></td>                                                                                                                                                |     |           | 4.5.4.4       |                                                  |     |

| 4.6.1       Interrupt Insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.6 | I/OxAPI   | C Interrupt ( |                                                  |     |

| 4.6.1.1       Pin Interrupts       160         4.6.1.2       Message Signaled Interrupts (MSI)       160         4.6.2       Interrupt Delivery.       160         4.6.3       Buffer Flushing.       162         4.6.4       Boot Interrupt       162         4.6.4       Boot Interrupt       162         4.6.7       SMBus Interface       163         4.7.1       SMBus Signaling.       163         4.7.1.1       Waveforms       164         4.7.1.2       Architecture       166         4.7.1.3       Data Transfer Examples       168         4.7.1.4       Configuration Space Registers       169         4.7.1.5       Memory Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.3       PowerOK       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Log                                                                                                                                                                                         |     |           |               |                                                  |     |

| 4.6.1.2       Message Signaled Interrupts (MSI)       160         4.6.2       Interrupt Delivery.       160         4.6.3       Buffer Flushing.       162         4.6.4       Boot Interrupt       162         4.6.4       Boot Interrupt       162         4.7       SMBus Interface.       163         4.7.1       SMBus Signaling.       163         4.7.1       Waveforms       164         4.7.1.1       Waveforms       166         4.7.1.2       Architecture       166         4.7.1.3       Data Transfer Examples       168         4.7.1.4       Configuration Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.2.3       PowerOK       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       <                                                                                                                                                                                              |     |           |               |                                                  |     |

| 4.6.2       Interrupt Delivery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |           |               |                                                  |     |

| 4.6.2.1       Front-Side Interrupt Delivery       160         4.6.3       Buffer Flushing       162         4.6.4       Boot Interrupt       162         4.7       SMBus Interface       163         4.7.1       SMBus Signaling       163         4.7.1       SMBus Signaling       163         4.7.1.1       Waveforms       164         4.7.1.2       Architecture       166         4.7.1.3       Data Transfer Examples       168         4.7.1.4       Configuration Space Registers       169         4.7.1.5       Memory Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.2.3       PowerOK       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Logging                                                                                                                                                                                                   |     | 4.6.2     | Interrupt D   |                                                  |     |

| 4.6.3       Buffer Flushing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | -         | •             |                                                  |     |

| 4.6.4       Boot Interrupt       162         4.7       SMBus Interface       163         4.7.1       SMBus Signaling       163         4.7.1       SMBus Signaling       163         4.7.1       Waveforms       164         4.7.1.2       Architecture       166         4.7.1.3       Data Transfer Examples       168         4.7.1.4       Configuration Space Registers       169         4.7.1.5       Memory Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.2.3       PowerOK       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Logging       176         4.9.3       Logged Errors       178         4.9.4       Allowable Error Combinations for RAS_STS                                                                                                                                                                                              |     | 4.6.3     | Buffer Flu    |                                                  |     |

| 4.7.1       SMBus Signaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 4.6.4     |               |                                                  |     |

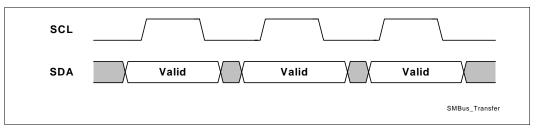

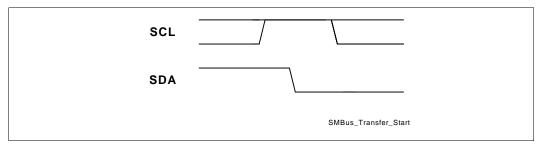

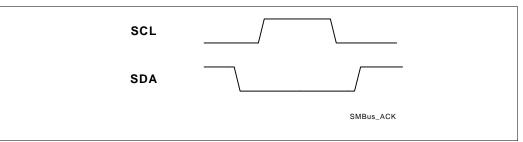

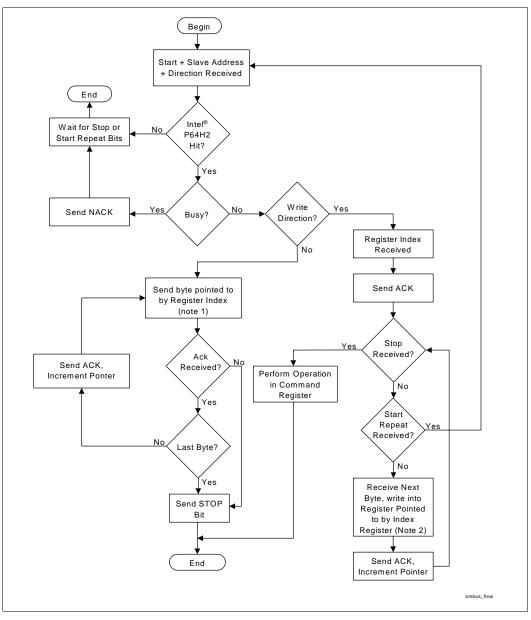

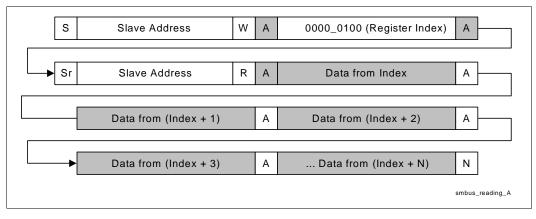

| 4.7.1.1       Waveforms       164         4.7.1.2       Architecture       166         4.7.1.3       Data Transfer Examples       168         4.7.1.4       Configuration Space Registers       169         4.7.1.5       Memory Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.2.3       PowerOK       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Logging       176         4.9.3       Logged Errors       178         4.9.4       Allowable Error Combinations for RAS_STS       178                                                                                                                                                                                                                                                                                                                                                                       | 4.7 | SMBus     | Interface     | ·                                                | 163 |

| 4.7.1.1       Waveforms       164         4.7.1.2       Architecture       166         4.7.1.3       Data Transfer Examples       168         4.7.1.4       Configuration Space Registers       169         4.7.1.5       Memory Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.2.3       PowerOK       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Logging       176         4.9.3       Logged Errors       178         4.9.4       Allowable Error Combinations for RAS_STS       178                                                                                                                                                                                                                                                                                                                                                                       |     |           |               |                                                  |     |

| 4.7.1.2       Architecture       166         4.7.1.3       Data Transfer Examples       168         4.7.1.4       Configuration Space Registers       169         4.7.1.5       Memory Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Logging       176         4.9.3       Logged Errors       178         4.9.4       Allowable Error Combinations for RAS_STS       178                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |           |               | 0 0                                              |     |

| 4.7.1.3       Data Transfer Examples       168         4.7.1.4       Configuration Space Registers       169         4.7.1.5       Memory Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.2.3       PowerOK       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Logging       176         4.9.3       Logged Errors       178         4.9.4       Allowable Error Combinations for RAS_STS       178                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |           | 4.7.1.2       |                                                  |     |

| 4.7.1.4Configuration Space Registers.1694.7.1.5Memory Space Registers.1694.7.2Configuration Access Arbitration1704.8System Setup.1714.8.1Clocking.1714.8.2Component Reset.1724.8.2.1Software PCI Reset.1724.8.2.2RSTIN#.1734.8.3I/OxAPIC System Assumptions1744.9Reliability, Availability, and Serviceability (RAS)1754.9.1Error Types1764.9.2Error Logging1764.9.3Logged Errors1784.9.4Allowable Error Combinations for RAS_STS178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |           |               |                                                  |     |

| 4.7.1.5       Memory Space Registers       169         4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Logging       176         4.9.3       Logged Errors       178         4.9.4       Allowable Error Combinations for RAS_STS       178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |           |               |                                                  |     |

| 4.7.2       Configuration Access Arbitration       170         4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Logging       176         4.9.3       Logged Errors       178         4.9.4       Allowable Error Combinations for RAS_STS       178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |           |               |                                                  |     |

| 4.8       System Setup       171         4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.2.3       PowerOK       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Logging       176         4.9.3       Logged Errors       178         4.9.4       Allowable Error Combinations for RAS_STS       178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 4.7.2     |               |                                                  |     |

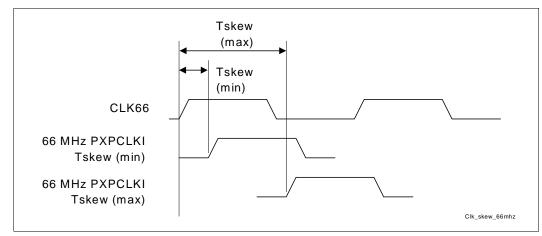

| 4.8.1       Clocking       171         4.8.2       Component Reset       172         4.8.2.1       Software PCI Reset       172         4.8.2.2       RSTIN#       173         4.8.2.3       PowerOK       173         4.8.3       I/OxAPIC System Assumptions       174         4.9       Reliability, Availability, and Serviceability (RAS)       175         4.9.1       Error Types       176         4.9.2       Error Logging       176         4.9.3       Logged Errors       178         4.9.4       Allowable Error Combinations for RAS_STS       178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.8 | Svstem    |               |                                                  |     |

| 4.8.2       Component Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |           |               |                                                  |     |

| 4.8.2.1       Software PCI Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | -         |               |                                                  |     |

| 4.8.2.2       RSTIN#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |           |               | Software PCI Reset                               | 172 |