### **Product Info Package V1.1**

Tricore CT166

Never stop thinking.

### AUDO-NG TC1766

### **Fast. Innovative. TriCore.** AUDO Next Generation TC1766

- + Extension of the award winning AUDO Architecture

- + 80 MHz high performance 32-bit TriCore™

- + 1,5 MByte embedded Flash

- + 72 KByte SRAM

- + Triple Bus Structure

- + Saving efforts in software and system costs

- + Speeding up software development with complete toolchain

- Ground-breaking peripherals e.g.

MSC: save I/O pins = system costs

FADC: waive external DSP ASICs

GPTA: realize scalable eMotor & Engine control

MLI: build up multi processor systems and eliminate expensive DPRAM

Never stop thinking.

### AUDO Next Generation TC1766 Info Package Overview

#### Content

- TC1766 at first sight

- Block Diagram

- Feature Overview

- misc. 'going into detail..'

- Core Concept

- Code Size

- Key Peripherals

- Tool Support

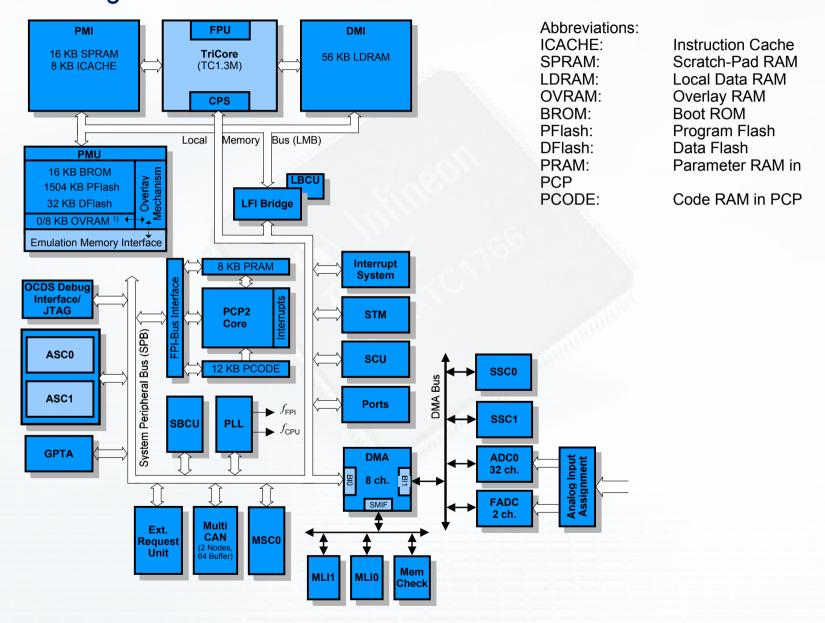

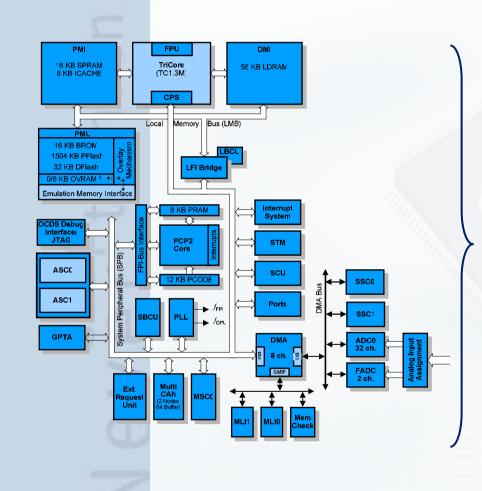

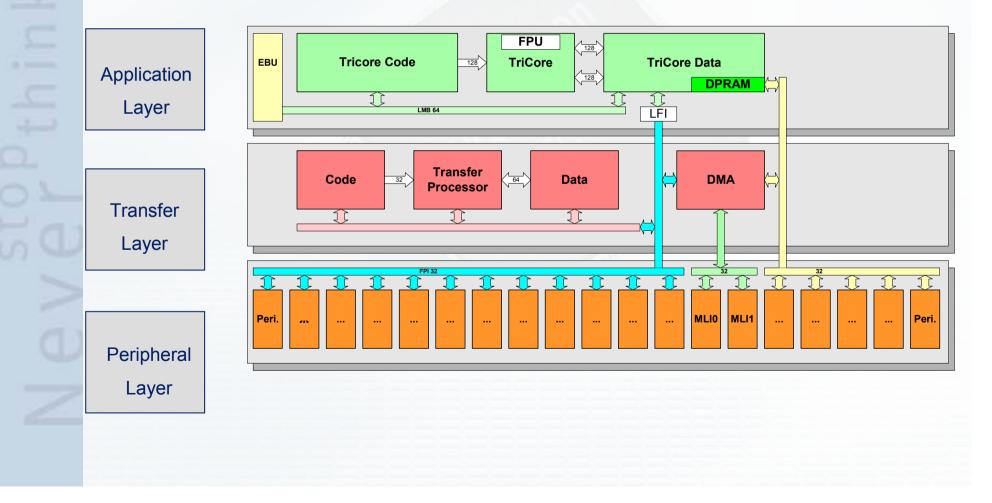

### AUDO Next Generation TC1766 Block Diagram

# **AUDO Next Generation TC1766** Feature Overview (1/5)

#### ■ High Performance 32-Bit CPU

- 32-bit architecture with 4 GBytes unified data, program, and input/output address space

- Fast automatic context-switch

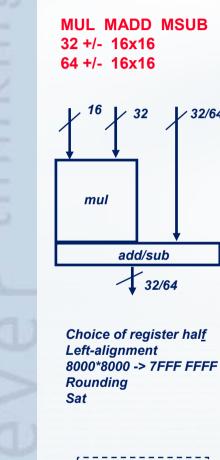

- Multiply-accumulate unit

- Single-precision Floating point unit

- Saturating integer arithmetic

- High performance on-chip peripheral bus (FPI Bus)

- Register based design with multiple variable register banks

- Bit handling

- Packed data operations

- Zero overhead loop

- Precise exceptions

- Flexible power management

#### Instruction Set with High Efficiency

- 16/32-bit instructions for reduced code size

- Data types include: Boolean, array of bits, character, signed and unsigned integer, integer with saturation, signed fraction, double word integers, and IEEE-754 single precision floating-point

- Data formats include: Bit, 8-bit byte, 16-bit half word, 32-bit word, and 64-bit double word data formats

- Powerful instruction set

- Flexible and efficient addressing mode for high code density

# **AUDO Next Generation TC1766** Feature Overview (2/5)

#### Integrated On-Chip Memories

- Code memory:

- 1,5 MByte on-chip Program Flash (PFLASH)

- 16 KByte Scratch-pad RAM (SPRAM)

- 8 KByte Instruction Cache (ICACHE)

- 16 KByte Boot ROM (BROM)

- Data memory

- 56 KByte Data Memory (SRAM)

- 8 KByte Overlay Memory (OVRAM)

- 32 KByte on-chip Data Flash (DFLASH)

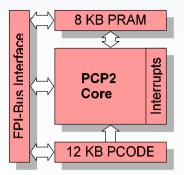

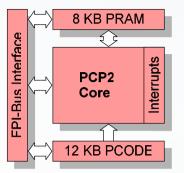

- PCP memory

- -12 KByte PCP Code Memory (CMEM), 8 KByte PCP Data Memory (PRAM)

# **AUDO Next Generation TC1766** Feature Overview (3/5)

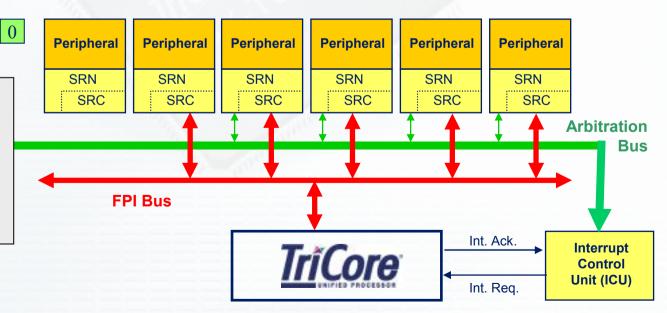

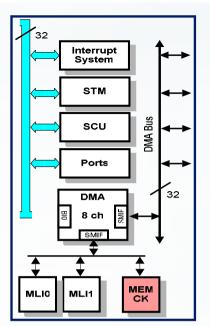

#### Interrupt System

- In total 104 Service Request Nodes (SRNs)

- Flexible interrupt prioritizing scheme with 256 interrupt priority levels

- Fast interrupt response

- Service requests are serviced by CPU or PCP2

#### Peripheral Control Processor (PCP2)

- Data move between any two memory or I/O locations

- Data move until predefined limit reached supported

- Read-Modify-Write capabilities

- Full computation capabilities including basic MUL/DIV

- Read/move data and accumulate it to previously read data

- Read two data values and perform arithmetic or logically operation and store result

- Bit handling capabilities (testing, setting, clearing)

- Flow control instructions (conditional/unconditional jumps, breakpoint)

# **AUDO Next Generation TC1766** Feature Overview (4/5)

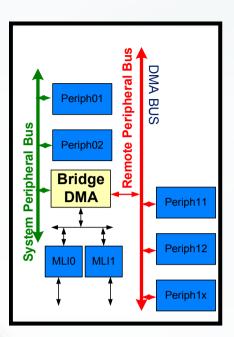

#### DMA Controller

- 8 independent DMA channels

- Programmable priority of the DMA sub-blocks on the bus interfaces

- Buffer capability for move actions on the buses (min. 1 move per bus is buffered).

- Individually programmable operation modes for each DMA channel

- Full 32-bit addressing capability of each DMA channel

- Programmable data width of DMA transfer/transaction: 8-bit, 16-bit, or 32-bit

- Micro Link bus interface support

- One register set for each DMA channel

- Flexible interrupt generation

- DMA Controller operates as bus bridge between System Peripheral Bus and Remote Peripheral Bus

#### Parallel I/O Ports

- 81 digital general purpose input/output (GPIO) port lines

- Input/output functionality individually programmable for each port line

- Programmable input characteristics (pull-up, pull-down, no pull device)

- Programmable output driver strength for EMI minimization (weak, medium, strong)

- Programmable output characteristics (push-pull, open drain)

- Programmable alternate output functions

- Output lines of each port can be updated port-wise or set/reset/toggled bit-wise

# **AUDO Next Generation TC1766** Feature Overview (5/5)

#### On-chip Peripheral Units

- Two Asynchronous/Synchronous Serial Channels (ASC) with baud-rate generator, parity, framing and overrun error detection

- Two Synchronous Serial Channels (SSC) with programmable data length and shift direction

- One Micro Second Channel Interface (MSC) for serial communication

- One CAN Module with two CAN nodes (MultiCAN) for high efficiency data handling via FIFO buffering and gateway data transfer

- Two Micro Link Serial Bus Interfaces (MLI) for serial multiprocessor communication

- One General Purpose Timer Array (GPTA) with a powerful set of digital signal filtering and timer functionality to realize autonomous and complex Input/Output management

- One medium speed Analog-to-Digital Converter Unit (ADC) with 8-bit, 10-bit, or 12-bit resolution and sixteen analog input each

- One fast Analog-to-Digital Converter Unit (FADC)

#### Package

- P/PG-LQFP-176 package, 0,5 mm pitch

#### Clock Frequencies

- Maximum CPU Clock Frequency: 80 MHz

- Maximum System Clock Frequency: 80 MHz

#### Temperature Rnage

- Ambient temperature: -40 ° to +125 °C

### AUDO Next Generation TC1766 Starter Kit Details

#### ■ Infineon TC1766 Starter Kit includes:

- TC1766 TriBoard

- StarterKit CD with all device and board information as PDF as well Getting Started Software and a Hands-On-Training for self-study

- DAvE (e.g. for generating peripheral initialization code)

- Demo CD of third party compiler and debugger vendors

- GNU C-Compiler full version

- Parallel cable for direct connection to the PCs LPT interface

- Extension Board for easy measurement of HW signals with a scope or a logic-analyzer

Order Information: <u>www.infineon.com/mc-starterkits</u>

- Order Number: B158-H8539-X-0-7600, SK-TC1766 Starter Kit

TC1766 Starter Kit

### going into detail..

### **TC1766 – Core Concept**

Tricore c 100

Never stop thinking.

### AUDO-NG – Outperforming Core Concept TriCore Architecture – Key Features and Benefits (1/2)

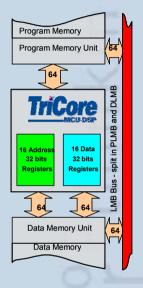

Program Memory Program Memory Unit 164 164 164 16 Address 32 bits Registers 16 Data 32 bits Registers 16 Data 32 bits Registers 164 164 164 164 164 Combining the the best of three worlds: RISC (MCU), DSP and µ-Controller together in a single core - TriCore offers maximum system performance for embedded real-time applications

#### **Key Features**

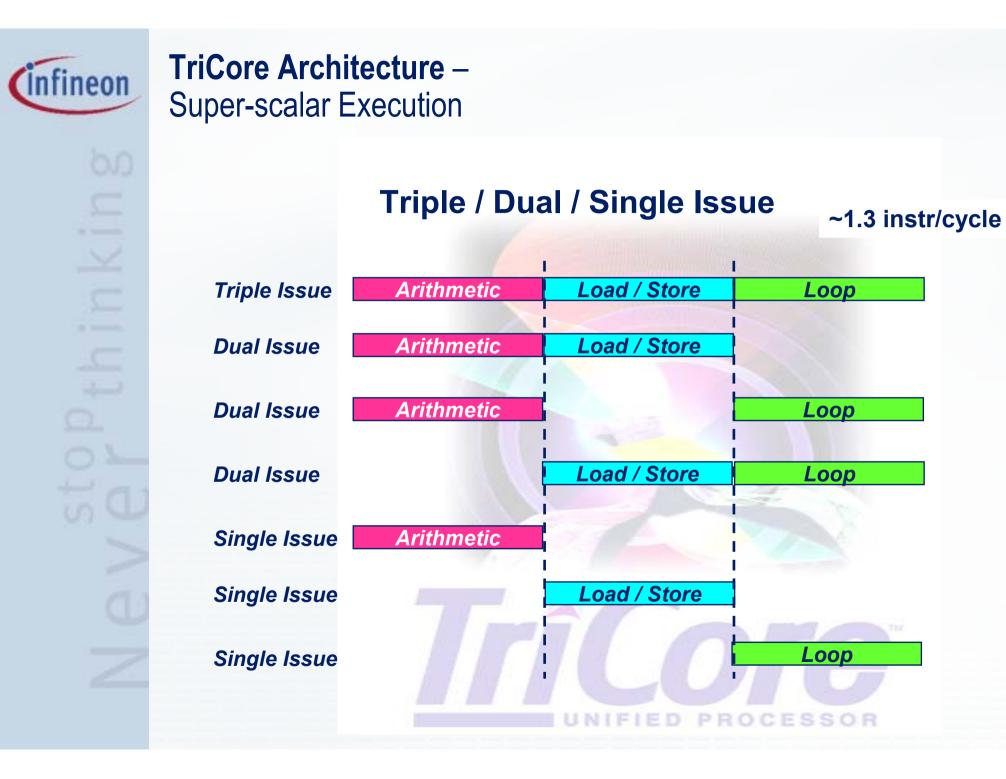

High Performance 32-bit TriCore CPU (TC v1.3) with 4-stage pipeline and triple issue super-scalar implementation (f<sub>CPU</sub> = 80 MHz) \*

#### Register sets

- 2x16 address/data 32 bits registers

- Switch upper shadowed half context in 2/4 cycles (the lower half in 4 cycles)

- mixed 16/32 bit instruction format

#### **Key Benefits**

Optimized chip-size to performance ratio for real-time critical embedded systems.

compressed Code-Density optimized for embedded FLASH memory usage

\* referring to TC1766

#### **Microcontroller Features/Highlights**

- fast interrupt response

- fast context switch (2-4 cycle -> 1/2 context)

- 16-bit and 32-bit instruction formats

- bit manipulation unit

- accumulated logical/ compare

- integrated peripheral support

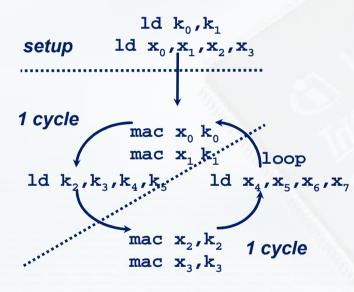

#### **DSP Features/Highlights**

- sustainable single-cycle dual-MAC

- DSP addressing modes

- zero overhead loop

- saturation and Q-Math

- overflow detection

- rounding

# Con RISC Processor Feature/Highlights

- 32-bit load/store Harvard architecture

- 16 address & 16 data registers

- super-scalar execution (4 stage pipeline)

- single data-memory model

- memory protection

iCore

• C/C++ and RTOS support

### AUDO-NG – Outperforming Core Concept TriCore Architecture – Key Features and Benefits (1/2)

Program Memory Program Memory Unit Program Memory Unit 64 **TriCcore** 16 Address 32 bits Registers 16 Data 82 bits Registers 64 16 Data Memory Unit Data Memory Unit Data Memory Combining the the best of three worlds: RISC (MCU), DSP and µ-Controller together in a single core - TriCore offers maximum system performance for embedded real-time applications

#### **Key Features**

High Performance 32-bit TriCore CPU (TC v1.3) with 4-stage pipeline and triple issue super-scalar implementation (f<sub>CPU</sub> = 80 MHz)

#### Register sets

- 2x16 address/data 32 bits registers

- Switch upper shadowed half context in 2/4 cycles (the lower half in 4 cycles)

#### Local Memory Bus (LMB)

- 64 bits data

- separated busses used for program and data (PLMB and DLMB)

- mixed 16/32 bit instruction format

#### **Key Benefits**

Optimized chip-size to performance ratio for real-time critical embedded systems.

- Separated instruction and data busses speed up the system performance due avoided arbitration conflict on a common bus

- compressed Code-Density optimized for embedded FLASH memory usage

Program Memory Program Memory U

64

TriCo

6 Addre 32 bits

64

Data Memory Un Data Memory

16 D

32 bi

### AUDO-NG – Outperforming Core Concept TriCore Architecture – Key Features and Benefits (2/2)

|   | Interrupt System                                                                                                                                                                                                                                                                                                 | sophisticated interrupt system with up                                                                                                                                                                                                                                     |  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   | <ul> <li>Flexible multi-master interrupt system<br/>(interrupts serviced by CPU, PCP or<br/>DMA)</li> <li>Hardware controlled context switch</li> <li>Hardware Interrupt Priority arbitration<br/>with 255 priority levels</li> <li>very fast interrupt response time<br/>resp. typ. 200 ns @ 80 MHz)</li> </ul> | to 255 HW arbitrated sources and very fast<br>response times is optimized for realtime<br>sensitive embedded applications                                                                                                                                                  |  |

| • | <b>powerful MAC unit</b> supports circular<br>buffer, No data overflow faults due to<br>saturating arithmetic and bit-reverse<br>addressing modes for DSP algorithms                                                                                                                                             | given scalability approach due to MCU and<br>DSP function merged in one core. Only on<br>tool set for development and emulation                                                                                                                                            |  |

|   | <b>single precision Floating Point Unit</b><br>(FPU) with integrated interrupt capability<br>for exception handling                                                                                                                                                                                              | tightly coupled coprocessor FPU support<br>with single precision IEEE-754 data format<br>compromises acceptable physical precision<br>demands with increased real time behavior<br>(unaltered fast 2 cycle context switch) and<br>reduced storage memory for FPU variables |  |

# TriCore Architecture –

### Powerful Interrupt Service System

| Features                                                                          | Benefits                                                                                |  |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| <ul> <li>Up to 4 x 255 request nodes (SRN),<br/>concurrently supported</li> </ul> | <ul><li>Meets real-time requirements</li><li>Zero Software overhead</li></ul>           |  |

| Parallel Arbiter HW to select highest<br>interrupt & clear when accepted          | <ul> <li>Ease of programming, High flexibility</li> <li>Large Number of SRNs</li> </ul> |  |

| <ul> <li>Automatic context save during<br/>branch to interrupt routine</li> </ul> | <ul> <li>Flexible grouping of request into<br/>priority groups</li> </ul>               |  |

Interrupt table - no jumps needed

4 3 2 1

5

#### TC1766 @ 80 Mhz

typ. 200 ns interrupt response time until execution of first instruction within Interrupt Service Routine (depending Interrupt Code Location and priority selection)

### **TriCore Architecture – DSP Some Results**

### **TriCore Architecture –**

# Reducing Cost and Complexity by merging MCU and DSP

#### Control and DSP development and integration/debug can all be done with the same development tools

- Optimized DSP library algorithms can be used out of the box

- Easy adaptation of DSP functions integrated in Automatic Code Generation tool package

- Devices can quickly be adapted to new market requirements

- smaller silicon

TriCore™one CPU<br/>one Tool<br/>one RTOSFast Time to Market<br/>New Features<br/>Lower Cost

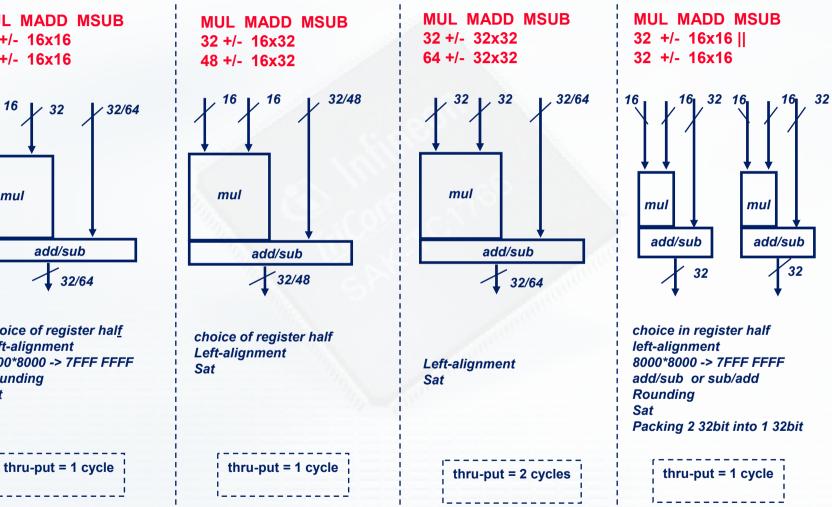

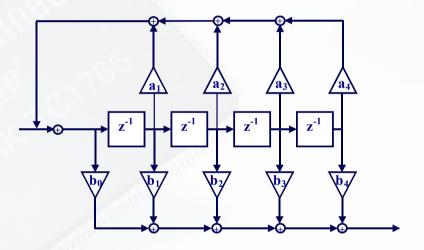

### **TriCore Architecture** – Supported DSP Operations

### Two MACs per cycle:

#### **Matrix calculus**

- Dual 16x16 hardware MAC

- Packed data

- Parallel load

- Mac-load-(loop) per cycle

### Sensors signal processing:

- Zero overhead loop

- Bit reverse addressing

### going into detail..

### TC1766 – Code Size

Core crise Tricore crise

Never stop thinking.

### TriCore Architecture – Code Size

With an Instruction Set tailored to real-time embedded control applications TriCore offers the best combination for optimized code performance and optimized code size:

| Key Features                                               | Key Benefits                                                                                                                                                         |  |  |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 16 & 32-bit instruction format                             | can be intermixed freely without setting mode bits<br>40% better code size vs. 32 bit instructions only                                                              |  |  |

| Dual & Triple operand instructions                         | well suited for C compiler, reduced overhead for<br>temporary operand loads/stores                                                                                   |  |  |

| Bit handling instructions                                  | cover control-oriented requirements, efficient in<br>control tasks and peripheral register access,<br>allow efficient SW state machine implementation                |  |  |

| Accumulated Logical/Compare                                | efficient code in state machine programming                                                                                                                          |  |  |

| Saturation Arithmetic and<br>Rounding/MIN/MAX instructions | <ul> <li>cuts off overhead for immediate result verification,<br/>done in HW by saturating math instructions (e.g.<br/>extensive lookup table algorithms)</li> </ul> |  |  |

| Embedded DSP instructions                                  | specific data formats and addressing modes, no overhead by additional instructions for operand handling (e.g. digital filter algorithm for knock detection           |  |  |

### going into detail..

### **TC1766 – Key Peripherals**

Tricore c 100

Never stop thinking.

#### Capabilities

The PCP2 is a freely programmable, single cycle, 32-bit processing unit with its own code and data memory unit (Harvard architecture) used as an interrupt service provider (HW Interrupt priority arbitration with 255 priority levels)

#### Structure and Benefits (1/2)

PCP provides programmable improved peripheral intelligence instead of static implementation

- off-loads TriCore from handling interrupt tasks and allows a parallel execution

- PCP fits best for real-time critical tasks due to very fast interrupt response time (typ. 225 ns)

- handles fast, interrupt-driven routines for peripheral control (e.g. counterpart of GPTA)

#### wide range of flexible programmable applications

- intelligent data pre-conditioning e.g. building up mean value of several concurrently sampled ADC values

- DMA data transportation like queued memory or FIFO structures e.g. coming from serial communication interfaces like CAN, SPI or ASC off-loads TriCore and realizes partially peripheral functionality in SW

- complex state machines easily can be coded e.g. flywheel driver SW

## **TC1766 Peripherals – PCP2** Peripheral Control Processor (2/3)

#### Capabilities

The PCP2 is a freely programmable, single cycle, 32-bit processing unit with its own code and data memory unit (Harvard architecture) used as an interrupt service provider (HW Interrupt priority arbitration with 255 priority levels)

#### Structure and Benefits (2/2)

PCP provides programmable improved peripheral intelligence instead of static implementation

- clear hierarchical SW partitioning possible by today's state of the art SW design techniques, e.g. mapping Low Level Driver Layer to the PCP

- one embedded tool chain environment for both TriCore and PCP already introduced and approved within AUDO family in a wide spread of applications

- TriCore/PCP multiprocessor approach supported by debugging/emulation

### **TC1766 Peripherals – PCP2** Peripheral Control Processor (3/3)

#### **Key Features**

- Smart interrupt driven Processor runs with f<sub>PCP</sub>=80 MHz @ f<sub>CPU</sub>= 80 MHz

- Harvard Architecture with separated Local Code (CMEM) and Parameter Memory (PRAM) SRAM sections

- Single cycle execution for most implemented instructions

#### Interrupt System

- HW controlled register context switch

- HW Interrupt priority arbitration with 255 priority levels

- very fast interrupt response time (typ.225ns @80MHz)

- channel restart/resume mode

- each implemented SRN can be flexible mapped to TriCore or PCP

#### Enhanced PCP Version 2 functions:

- self-posted PCP interrupt queue enlarged to 12 source request nodes

- deadlock avoidance implemented

- 3 nested interrupt levels supported

PCP serves as a "first line of defense" for intelligent programmable peripheral interrupt service requests

- PCP handles typical real-time critical tasks

- fast, interrupt-driven routines for peripheral control (e.g. counterpart of GPTA)

- manipulation/data pre-conditioning of DMA and peripheral data

- Channel restart/resume mode supports interrupt-vector-table entry or flexible statemachines with register context saved re-entry vector on EXIT instruction

- Clear hierarchical SW partitioning possible by mapping Low Level Driver Layer to PCP

- One embedded tool chain environment for TriCore C-Compiler and PCP assembler

- Multiprocessor approach TriCore/PCP supported by Debugging/Emulation concept

### Key Benefits

# **TC1766 Peripherals – DMA** Direct Memory Access Controller

#### Capabilities

The DMA (single move engine) supports 8 independent channels for high flexible memory or peripheral transfer operations. It additionally supports MLI operations and bridge functionality between the System Peripheral Bus (SPB) and the DMA bus.

#### **Structure and Benefits**

#### By mapping simple data transportation

tasks to the DMA controller, the TriCore CPU and Peripheral Control Processor (PCP) are significantly released and might focus on their application and low level driver tasks.

- flexible usage for single event or continuous transfer operation including programmable data width for 8/16 or 32 bit memory transfer transactions covers a wide range of feasible customer application requirements

- flexible interrupt generation from up to 18 different interrupt sources (e.g. data pattern recognition) fulfills clear hierarchical separation of HW driven data transfers and needed SW interaction

- programmable request wiring matrix of up to 8 hardwired possible inputs for each DMA channel supports maximum adaptation flexibility to the customer

- combination of hardwired channel priority with programmable SW priority for each individual DMA channel offers maximum adaptation to application demands

### TC1766 Peripherals – Memory Checker

#### **Capabilities**

Check dedicated memory portions (e.g. program memory flash or program SRAM memory of the PCP) in background for correctness (e.g. to be able to determine code corruption)

#### **Structure and Benefits**

The memory checker has implemented a polynomial generator which equals to the standard used within Ethernet:

$$\mathbf{G}^{32} = \mathbf{x}^{32} + \mathbf{x}^{26} + \mathbf{x}^{23} + \mathbf{x}^{22} + \mathbf{x}^{16} + \mathbf{x}^{12} + \mathbf{x}^{10} + \mathbf{x}^8 + \mathbf{x}^7 + \mathbf{x}^5 + \mathbf{x}^4 + \mathbf{x}^2 + \mathbf{x} + \mathbf{1}$$

Any bus master (TriCore CPU, PCP or DMA controller) might serve the memory checker located on the SMIF interface of the DMA module.

- checking a memory portion is feasible by a sequential move (read operation followed by a write operation) of dedicated memory portion to a a single address of the memory checker located on the SMIF interface

- simple compare function is needed to fell a decision whether calculated memory checker result matches to the pre-calculated expected result stored somewhere in the FLASH area

- using a DMA channel offloads TriCore CPU and PCP. Only READ operations are seen on the System Peripheral Bus (SPB) or the DMA Bus. The write operation to the memory checker by the move engine is hidden within the DMA (routed to SMIF interface) and does not require any bandwidth of the other buses

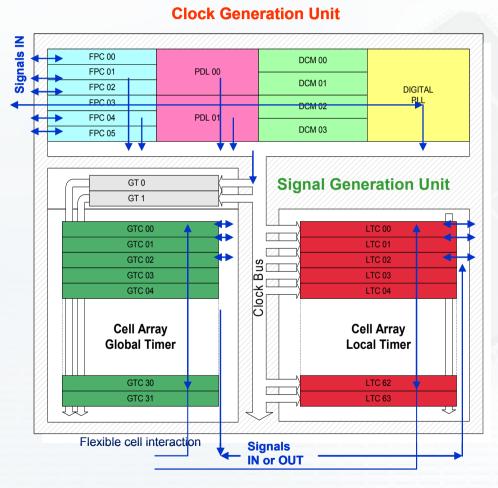

### **TC1766 Peripherals – GPTA** Functional Block Diagram

#### **Clock Generation Unit:**

| FPC                           | Filter and Prescaler Cell   |  |  |  |

|-------------------------------|-----------------------------|--|--|--|

|                               | amount of cells: 6          |  |  |  |

| PDL                           | Phase Discrimination Logic  |  |  |  |

|                               | amount of cells: 2          |  |  |  |

| DCM                           | Duty cycle Measurement Cell |  |  |  |

|                               | amount of cells: 4          |  |  |  |

| PLL                           | Phase Locked Loop           |  |  |  |

|                               | amount of cells: 1          |  |  |  |

| <b>Clock Distribution Bus</b> |                             |  |  |  |

|                               | amount of clock lines: 8    |  |  |  |

|                               |                             |  |  |  |

|                               |                             |  |  |  |

#### **Signal Generation Unit:**

| GT  | Global Timer (24bit)      |  |

|-----|---------------------------|--|

|     | amount of cells: 2        |  |

| GTC | Global Timer Cell (24bit) |  |

|     | amount of cells: 32       |  |

| LTC | Local timer Cell (16bit)  |  |

|     |                           |  |

amount of cells: 64

#### **Signal Cross Connection:**

- via the Clock Bus

- Pad connections to and between the FPC/GT/GTC/LTC cells

# **TC1766 Peripherals – GPTA** General Purpose Timer Array (1/2)

#### Capabilities

The GPTA offers very flexible filtering and high resolution signal acquisition, a digital PLL used for the generation of a higher resolution of input signals and due to its universal cell structure all kinds of enhanced counting, capture compare and PWM functionality.

#### **Structure and Benefits (1/2)**

perfect adaptation to target application by non-static modular cell approach compared to timer implementations of the competition:

- very flexible digital input filtering can be achieved by the usage of the implemented Filter Prescaler Cells (FPC). Flexible strategies between delayed and immediate debounce filtering are possible (e.g. for input filtering of the flywheel or the camshaft signals)

- tracking of all kind of rotating shafts (e.g. within a gearbox system) including the encoding of the signals for the forward and backward position can be easily achieved by usage of the Phase Discrimination Logic (PDL) cells which supports the decoding of 2 and 3 sensor input signals

- scalable high resolution for the generation of optimal distributed microticks as an angle reference counter signal for the engine position can be easily achieved by usage of the implemented digital PLL module

### **TC1766 Peripherals – GPTA** General Purpose Timer Array (2/2)

#### **Structure and Benefits (2/2)**

perfect adaptation to target application by non-static modular cell approach compared to timer implementations of the competition:

- independent access to time and angle domain by two global timers (GT0/GT1) with corresponding Global Timer Cell (GTC) array

- optimal support for capture/compare interaction corresponding to time or angle counters (e.g. injection or ignition for gasoline engines)

- all kinds of PWM generation are supported by the usage of the Local Timer Cell (LTC) array. Hereby all kind of desirable scalability in terms of

- autonomous full coherent high speed PWM generation from 0-100% duty cycle with five LTC cells driven completely in HW down to

- SW supported PWM generation from 10-90% duty cycle with minimum on one LTC cell of used GPTA resources can be easily implemented

- optimal application driven balance between precise HW driven event generation (e.g. HW driven start of ignition on pre-calculated engine angle) and SW driven interrupt tasks (e.g. reconfiguration of the compare value for next ignition start)

- Peripheral Control Processor (PCP2) is an ideal counterpart for the SW handling of short and real-time critical GPTA interrupt demands. PCP and GPTA may realize flywheel, ignition and injection low level driver functionality without any TriCore interaction

- In field test and repair feasible due to dynamic reconfigurable in/out multiplexer and array of replaceable blocks

# TC1766 Peripherals – ADC/Fast ADC Aanalog to Digital Converters ADC and Fast ADC

#### Capabilities

AUDO-NG incorporates two different implementations for ADC peripherals using successive approximation conversion principle:

- one ADC module with programmable resolution 8/10/12 bit and conversion time of 2,5  $\mu s$  @ 10bit

- with a sophisticated feature set for autonomous analog/digital data acquisition

- one Fast ADC module with 10 bit resolution and a minimum conversion time of 280 ns resp. (corresponding to 3,5 Msamples) including a data reduction filter with moving average

- auto-calibration mechanism build in at power up

FADC targeted application segments are knock detection and dynamic control of ignition by ion current measurement

#### **Structure and Benefits Fast ADC**

unique solution for knock detection without external ASICs or dedicated DSP

reduced SW load for FIR-Filter by usage of integrated decimation comb filter (e.g. data reduction by factor 6 from 1200 to 200 ksamples)

quick adaptation of the overall filter quality to the application demands by programmable adaptation of data rate used for the FIR filter

increase of ADC accuracy by data reduction filter and moving averaging filter (e.g. from 10 bit to 11 bit by selected oversampling factor of 4)

### TC1766 Peripherals – MLI Multiprocessor Link Interface

#### Capabilities

AUDO-NG incorporates two MLI modules which are used for a serial high speed inter processor connection to other AUDO-NG family members.

#### **Structure and Benefits MLI**

- serial high speed interface up to f<sub>MLI</sub>/2 (i.e. 40 MBaudps for TC1766) which is used for interprocessor communication between the AUDO\_NG family members and therefore offers the possibility of scalable processing power within an application

- parallel memory accesses to up to four memory windows automatically will be converted to serial high speed MLI protocol and vice versa at the other MLI device

- capability of posting up to four interrupts to the second processor on the other side by sending a command frame

- high efficient data transfer bandwidth supported (up to 35 MBaud) by special protocol for data, address offset or data and address offset

- for security reasons MLI interface is locked after HW reset and first has to be unlocked by the device itself

# TC1766 Peripherals – MSC Introduction of the Advanced Micro Second Bus

| EvolutionParallel Input<br>parallel StatusParallel Input<br>SPI InterfaceSPI +<br>µs -BusAdvanced<br>Micro Second Bus |                              |                                 |                                 |                                     |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------|---------------------------------|-------------------------------------|

| Pins / IO                                                                                                             | 16 + 16 = <mark>32</mark>    | 16 + 4 = <b>20</b>              | 4 + 3 = 7                       | 6                                   |

| performance                                                                                                           | PWM                          | PWM<br>configurability          | PWM<br>configurability          | PWM<br>configurabilit               |

| diagnostic                                                                                                            | 1 bit / channel<br>no memory | 2 bit / channel<br>fault memory | 2 bit / channel<br>fault memory | 2 bit / channel<br>fault memory     |

| interface                                                                                                             | parallel                     | parallel +<br>duplex bus        | duplex bus +<br>point - point   | point - point +<br>async . upstrean |

time

### TC1766 Peripherals – MSC Micro Second Channel

#### Capabilities

purpose of the MSC module is to set a new open standard for the serial high speed communication to power ASIC modules, like multi-switches (i.e. for ignition or injection drivers) including transfer of command frames, data frames and asynchronous diagnosis feedback from the device

#### **Structure and Benefits MSC**

Design goals for the new approach has been:

- parallel high speed PWM channels generated by the General Purpose Timer Array (GPTA) are serialized via MSC module and transferred to the corresponding MSC module within the connected power ASIC device without any additional SW load

- maximum resolution for transferred PWM data is 500 kHz or 2µs period length

- 2x2 signal wires Low-Voltage Differential Signals (LVDS) drivers implemented for high speed downstream signals (CLK and Data) for lower EMI

- asynchronous upstream channel implemented for diagnosis data for getting rid of SPI used polling mechanism

- 6 wires used to connect up to 32 high speed PWM channels instead of the standard SPI approach with 36; saving of up to 30 package pins on the MC and power asic side offers ability of smaller pin counts on packages for microcontroller and power asic and therefore saves system costs

- **scalable approach** supported for the connection of up to four MSC power devices to one module

- standard SPI protocol alternatively supported for high speed downstream channel

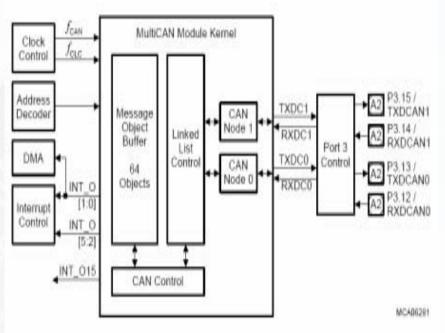

# **TC1766 Peripherals – MultiCAN** Feature Set and Module

- CAN functionality conform to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- 2 independent CAN nodes available

- **64** independent **message objects** (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to **1MBaud**, individual programmable for each node

- Flexible and powerful message transfer control and error handling capabilities

- Automatic gateway mode support

- 6 individually programmable interrupt

nodes

- CAN Analyzer Mode for bus monitoring

# infineon

# TC1766 Peripherals – System Benefits Summary – Peripheral Support

#### **TriCore Architecture**

combining three worlds of  $\mu$ Processor,  $\mu$ Controller and DSP results in scalable HW resources optimized for embedded Powertrain applications

#### optimized Bus Architecture

Three layer SW concept simplifies clear hierarchical separation of e.g. "Branding Application SW" based on the IP of the OEM and standard Low Level Driver SW delivered by the TIER1

AUDO-NG Peripheral Support and Connectivity Enhanced Peripheral Modules helps to lower system costs by:

- saving package pins of the μC through serialization (e.g. μs-Bus for external Power ASSP)

- porting external ASIC function to AUDO-NG (e.g. saving external Knock-ASIC by FADC usage)

- scalable system performance (e.g. connecting family members of AUDO-NG through MLI bus)

#### Extensive Development Support

World Leading Tool partners supporting all phases of development within the V-Cycle

# **TriCore Architecture** µC Partitioning: the three layer concept

To allow the right Function partitioning with clear Interfaces Infineon has designed the three layer approach:

### going into detail..

### **TC1766 – Tool Support**

Tricore c 100

Never stop thinking.

| infineon                        | Complete Tool Environment for System<br>Toolpartners for AUDO-NG Support                                         | Development<br>UDO-NG<br>utomotive UnifieD processor<br>Next Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 |                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                 | Specification →                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MODELING<br>SIMULATION          | MatlabSimulink (MathWorks)<br>ASCET-MD (ETAS)<br>MATRIXx (National Instruments)                                  | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PROTOTYPING                     | Prototyper (dSPACE)<br>ASCET-RP + ES1000 (ETAS)                                                                  | CT100 CT000 |

| AUTOMATIC<br>CODE<br>GENERATION | Targetlink (dSPACE)<br>RealTimeWorkshop (MathWorks)<br>ASCET-SE (ETAS)<br>DAvE (Infineon)                        | CALIBRATION & INSTR.<br>INCA (ETAS)<br>(dSPACE), VISION (ATI), CANape<br>(Vector), Gredi (Kleinknecht)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OPERATING<br>SYSTEM             |                                                                                                                  | INCA (ETAS), CalDesk<br>(dSPACE), VISION (ATI), CANape<br>(Vector), Gredi (Kleinknecht)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| COMPILER<br>DEBUGGER            | ERCOSEK (ETAS) ProOSEK (3Soft)<br>RTA OSEK (LiveDevices)<br>osCAN(Vector)<br>(Tasking)<br>(HighTec)<br>(Ashling) | TEST & VALIDATION<br>dSPACE Simulator (dSPACE)<br>LabCar (ETAS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| EMULATOR<br>DEBUGGER            | (Ashling)<br>(Hitex)<br>(Lauterbach) (pls)                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DEVELOPMENT<br>BOARD            | TriBoard (Infineon)<br>Low-Level Driver, Libraries, AppNotes (Infineon)                                          | INTEGRATED DEVELOPMENT<br>ENVIRONMENT<br>ASCET-SD (ETAS)<br>MATLAB/Simulink (MathWorks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

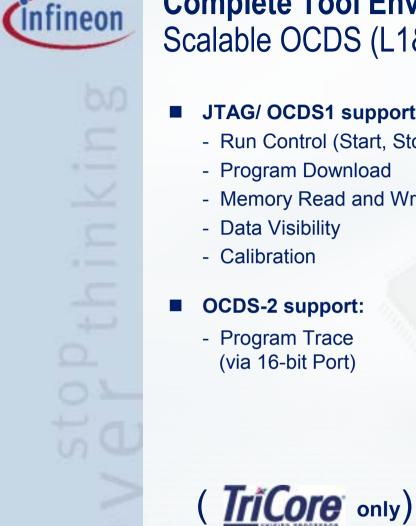

### **Complete Tool Environment for System Development** Scalable OCDS (L1&L2) Debug Support

- JTAG/ OCDS1 support (On Chip Debug Support):

- Run Control (Start, Stop, Breakpoints)

- Program Download

- Memory Read and Write Access at runtime

- Data Visibility

- Calibration

#### **OCDS-2** support:

- Program Trace (via 16-bit Port)

**Target Specific**

JTAG / OCDS-1 Debug Cable and Wiggler

JTAG + OCDS-2 Debug (RISC-TRACE)

### **Complete Tool Environment for System Development** TC1766 Debugger and RTOS Support

| <u> Compilers + Assembler</u> | Availability                      |                                                                                                     |                 |                 |

|-------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------|-----------------|-----------------|

|                               | <u>TCv1.3</u>                     | PCP2 Assembler                                                                                      | <u>FPU</u>      | <u>SFR sup.</u> |

| Tasking                       | now                               | now                                                                                                 | now             | now             |

| HighTec                       | now                               | now                                                                                                 | now             | now             |

| WindRiver Systems             | now                               | now                                                                                                 | now             | now             |

|                               | OCDS L1                           | OCDS L2 PCP 2 L1                                                                                    | <u>PCP 2 L2</u> |                 |

|                               |                                   |                                                                                                     |                 |                 |

| Ashling                       | now L                             | 2 trace available for 80MHz with upd                                                                |                 |                 |

| Ashling<br>Hitex              | now L                             | 2 trace available for 80MHz with upd<br>2 trace available for 80MHz                                 |                 |                 |

|                               | now L                             | 2 trace available for 80MHz with upd                                                                |                 |                 |

| Hitex                         | now L<br>now. L<br>now L          | 2 trace available for 80MHz with upd<br>2 trace available for 80MHz                                 |                 |                 |

| Hitex<br>Lauterbach           | now Linow. Linow. Li              | 2 trace available for 80MHz with upd<br>2 trace available for 80MHz<br>2 trace available for 80 MHz |                 |                 |

| Hitex<br>Lauterbach<br>pls    | now L<br>now. L<br>now L<br>now L | 2 trace available for 80MHz with upd<br>2 trace available for 80MHz<br>2 trace available for 80 MHz |                 |                 |

**<u>RTOS</u>** (using enhanced System Timer as standard OSEK peripheral)

| ETAS               | ERCOSEK                     |                 |

|--------------------|-----------------------------|-----------------|

| Vector             | osCAN tbd                   | AUDO-NG support |

| 3-Soft             | ProOSEK tbd                 | available       |

| LiveDevices (ETAS) | Realogy Real-Time Architect |                 |

# Never stop thinking.