# Final draft ETSI EN 302 084 V1.1.1 (1999-11)

European Standard (Telecommunications series)

# Transmission and Multiplexing (TM); The control of jitter and wander in transport networks

Reference

DEN/TM-01067 (jao00ico.PDF)

Keywords

control, performance, transmission, synchronization, interface, transport

#### **ETSI**

Postal address F-06921 Sophia Antipolis Cedex - FRANCE

Office address

650 Route des Lucioles - Sophia Antipolis Valbonne - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16 Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88

Internet

secretariat@etsi.fr Individual copies of this ETSI deliverable can be downloaded from http://www.etsi.org If you find errors in the present document, send your comment to: editor@etsi.fr

#### Important notice

This ETSI deliverable may be made available in more than one electronic version or in print. In any case of existing or perceived difference in contents between such versions, the reference version is the Portable Document Format (PDF). In case of dispute, the reference should be the printing on ETSI printers of the PDF version kept on a specific network drive within ETSI Secretariat.

#### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

> © European Telecommunications Standards Institute 1999. All rights reserved.

# Contents

| Intelle                                                      | ectual Property Rights                                                                                                                                                                                                                                                                                  | 5                          |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Forev                                                        | vord                                                                                                                                                                                                                                                                                                    | 5                          |

| Introc                                                       | luction                                                                                                                                                                                                                                                                                                 | 5                          |

| 1                                                            | Scope                                                                                                                                                                                                                                                                                                   | 6                          |

| 2                                                            | References                                                                                                                                                                                                                                                                                              | 6                          |

| 3<br>3.1<br>3.2                                              | Definitions and abbreviations<br>Definitions<br>Abbreviations                                                                                                                                                                                                                                           | 7                          |

| 4<br>4.1<br>4.2                                              | Network wander specification<br>Wander reference model<br>Specification of wander by MRTIE parameter                                                                                                                                                                                                    | 8                          |

| 5<br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.3<br>5.2.4 | Network limits for output jitter and wander<br>Network limits for output jitter<br>Network limits for output wander<br>2 048 kbit/s interface output wander limit<br>34 368 kbit/s interface output wander limit<br>139 264 kbit/s interface output wander limit<br>STM-N interface output wander limit | 10<br>11<br>12<br>13<br>13 |

| 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                  | Jitter and wander tolerance of equipment interfaces                                                                                                                                                                                                                                                     | 15<br>16<br>17<br>18<br>18 |

| Anne                                                         | <b>EXA (informative):</b> Wander limit considerations for SDH transport networks                                                                                                                                                                                                                        | 23                         |

| A.1<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6    | Introduction<br>Wander reference model for SDH<br>Sources of wander<br>Wander accumulation limiting effects<br>Network configuration and performance<br>Correlation of wander sources<br>Network conditions for the output wander limits.                                                               |                            |

| A.2                                                          | Derivation of wander specification limits                                                                                                                                                                                                                                                               | 25                         |

| Anne                                                         | x B (informative): Measurement methodologies for output wander                                                                                                                                                                                                                                          | 27                         |

| B.1<br>B.1.1                                                 | Synchronization interfaces                                                                                                                                                                                                                                                                              | 27                         |

| B.2<br>B.2.1<br>B.2.2<br>B.2.2.<br>B.2.2.                    |                                                                                                                                                                                                                                                                                                         |                            |

3

| Annex C (informative): | Measurement guidelines for input jitter and wander tolerance of equipment interfaces | 31 |

|------------------------|--------------------------------------------------------------------------------------|----|

| Annex D (informative): | Relation between parameters for input jitter tolerance and output jitter limits      | 33 |

| History                |                                                                                      |    |

# Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available from the ETSI Secretariat. Latest updates are available on the ETSI Web server (http://www.etsi.org/ipr).

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

# Foreword

This European Standard (Telecommunications series) has been produced by ETSI Technical Committee Transmission and Multiplexing (TM), and is now submitted for the Voting phase of the ETSI standards Two-step Approval Procedure.

| Proposed national transposition dates                                                  |                                 |  |  |

|----------------------------------------------------------------------------------------|---------------------------------|--|--|

| Date of latest announcement of this EN (doa):                                          | 3 months after ETSI publication |  |  |

| Date of latest publication of new National Standard or endorsement of this EN (dop/e): | 6 months after doa              |  |  |

| Date of withdrawal of any conflicting National Standard (dow):                         | 6 months after doa              |  |  |

# Introduction

In a transport network, jitter and wander accumulate on data paths according to the jitter and wander generation and transfer characteristics of each equipment interconnected. These equipments may be different types of multiplexers/demultiplexers, cross-connects and line systems, for example.

An excessive amount of jitter and wander can adversely affect both digital signals (e.g. by generation of bit errors, uncontrolled slips and other abnormalities) and analogue signals (e.g. by unwanted phase modulation of the transmitted signal). The consequences of such impairment will, in general, depend on the particular service that is being carried and the terminating or adaptation equipment involved.

It is therefore necessary to set limits on the magnitude of jitter and wander at network interfaces, in order to guarantee a proper quality of the transmitted signals and a proper design of the equipment.

The jitter and wander control philosophy of the present document is based on the need:

- to specify a maximum network limit of jitter and wander that should not be exceeded at any relevant interface;

- to specify a minimum equipment tolerance to jitter and wander that should be provided at any relevant interface;

- to establish a consistent framework for the specification of individual digital equipment types; and

- to provide sufficient information and guidelines for organizations to measure and study jitter and wander characteristics in any network configuration.

### 1 Scope

The present document specifies the relevant parameters and their limiting values that are able to satisfactorily control the amount of jitter and wander present at synchronous digital hierarchy (SDH) and plesiochronous digital hierarchy (PDH) network-network interfaces (NNI).

The present document also provides the minimum jitter and wander requirements at SDH and PDH user-network interfaces (UNI). However, particular terminals or services may have additional jitter and wander requirements and in those cases the relevant standards apply.

The jitter and wander requirements specified in the present document are applicable to the interfaces irrespective of the transport mechanism (PDH, SDH or ATM networks, for example).

The jitter and wander requirements for an interface will be different, depending on whether the signal at the interface is used to transport data only, or synchronization as well. The requirements for synchronization interfaces are specified in EN 300 462-3-1 [7] and reference is made to that document where appropriate.

The present document also specifies the jitter and wander requirements for interfaces using the generic frame structures at PDH rates as described in ETS 300 337 [3].

The electrical characteristics of the relevant network interfaces for SDH and PDH interfaces are described in specification ETS 300 166 [1] and the characteristics of SDH optical interfaces are described in specification ETS 300 232 [2].

# 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication, edition number, version number, etc.) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, subsequent revisions do apply.

- A non-specific reference to an ETS shall also be taken to refer to later versions published as an EN with the same number.

- [1] ETS 300 166: "Transmission and Multiplexing (TM); Physical and electrical characteristics of hierarchical digital interfaces for equipment using the 2 048 kbit/s-based Plesiochronous or Synchronous Digital Hierarchies".

- [2] ETS 300 232: "Transmission and Multiplexing (TM); Optical interfaces for equipments and systems relating to the Synchronous Digital Hierarchy [ITU-T Recommendation G.957 (1993), modified]".

- [3] ETS 300 337: "Transmission and Multiplexing (TM); Generic frame structures for the transport of various signals (including Asynchronous Transfer Mode (ATM) cells and Synchronous Digital Hierarchy (SDH) elements) at the ITU-T Recommendation G.702 hierarchical rates of 2 048 kbit/s, 34 368 kbit/s and 139 264 kbit/s".

- [4] EN 300 417-1-1: "Transmission and Multiplexing (TM); Generic requirements of transport functionality of equipment; Part 1-1: Generic processes and performance".

- [5] EN 300 462-1-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 1-1: Definitions and terminology for synchronization networks".

- [6] EN 300 462-2-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 2-1: Synchronization network architecture".

| [7]  | EN 300 462-3-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 3-1: The control of jitter and wander within synchronization networks".                                                                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [8]  | EN 300 462-4-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 4-1: Timing characteristics of slave clocks suitable for synchronization supply to Synchronous Digital Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH) equipment". |

| [9]  | EN 300 462-5-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 5-1: Timing characteristics of slave clocks suitable for operation in Synchronous Digital Hierarchy (SDH) equipment".                                                         |

| [10] | EN 300 462-6-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 6-1: Timing characteristics of primary reference clocks".                                                                                                                     |

| [11] | ITU-T Recommendation G.803: "Architecture of transport networks based on the synchronous digital hierarchy (SDH)".                                                                                                                                                                         |

| [12] | ITU-T Recommendation O.150: "General requirements for instrumentation for performance measurements on digital transmission equipment".                                                                                                                                                     |

| [13] | ITU-T Recommendation O.171: "Timing jitter and wander measuring equipment for digital systems which are based on the plesiochronous digital hierarchy (PDH)".                                                                                                                              |

| [14] | ITU-T Recommendation O.172: "Jitter and wander measuring equipment for digital systems which are based on the synchronous digital hierarchy (SDH)".                                                                                                                                        |

| [15] | ITU-T Recommendation G.703: "Physical/electrical characteristics of hierarchical digital                                                                                                                                                                                                   |

# 3 Definitions and abbreviations

interfaces".

# 3.1 Definitions

For the purposes of the present document, the following terms and definitions apply. Additional definitions relating to synchronization networks are provided in EN 300 462-1-1 [5], whilst the architectural principles of synchronization networks are described in EN 300 462-2-1 [6].

**traffic interface:** these interfaces may be synchronous (i.e. normally PRC-traceable) or asynchronous (e.g. meeting the frequency offset requirements of ETS 300 166 [1]). Network jitter and wander limits are specified in the present document and wander is specified using the MRTIE (Maximum Relative Time Interval Error) parameter. Input jitter and wander tolerance is also specified in the present document. This interface category can be further sub-divided as follows:

- interface is not able to provide synchronization, and is not required to. An example is an interface supporting only 34 368 kbit/s or 139 264 kbit/s PDH signals according to ETS 300 166 [1];

- interface is not able to provide synchronization at the defined performance level, but nevertheless is used to provide timing to other network elements such as terminal equipment, remote concentrators, etc. Examples include 2 048 kbit/s, 34 368 kbit/s and 139 264 kbit/s PDH signals and leased lines transported on SDH, which may be subject to pointer justifications. ITU-T Recommendation G.803 [11] recommends that these interfaces are not used for synchronization, but in some network applications there is little alternative;

- interface is able to provide synchronization at the defined performance level, in which case it is defined to be a synchronization interface. An example is STM-N interfaces. This sub-category may also include interfaces using the generic frame structures at PDH rates as described in ETS 300 337 [3].

**synchronization interface:** these interfaces are synchronous (i.e. normally PRC-traceable) and their requirements are not specified in the present document. The network limits for synchronization interfaces are specified using MTIE (Maximum Time Interval Error) and TDEV (Time Deviation) parameters with values given in EN 300 462-3-1 [7]. The input jitter and wander tolerance of clock equipment ports is specified in EN 300 462-4-1 [8] (for equipment containing an SSU function) and EN 300 462-5-1 [9] (for equipment containing an SEC function).

### 3.2 Abbreviations

For the purposes of the present document, the following abbreviations apply. Additional abbreviations relating to synchronization networks are provided in EN 300 462-1-1 [5].

| ATM    | Asynchronous Transfer Mode                                                   |

|--------|------------------------------------------------------------------------------|

| CMI    | Coded Mark Inversion                                                         |

| MRTIE  | Maximum Relative Time Interval Error                                         |

| MS-AIS | Multiplex Section Alarm Indication Signal                                    |

| MTIE   | Maximum Time Interval Error                                                  |

| NE     | Network Element                                                              |

| NNI    | Network-Network Interface                                                    |

| PDH    | Plesiochronous Digital Hierarchy                                             |

| pk-pk  | peak-to-peak                                                                 |

| PLL    | Phase Locked Loop                                                            |

| ppm    | parts per million                                                            |

| PRBS   | Pseudo-Random Binary Sequence                                                |

| PRC    | Primary Reference Clock                                                      |

| RTIE   | Relative Time Interval Error                                                 |

| SDH    | Synchronous Digital Hierarchy                                                |

| SEC    | SDH Equipment Clock                                                          |

| SSU    | Synchronization Supply Unit                                                  |

| STM-1e | Synchronous Transport Module, level 1 (electrical format CMI-encoded signal) |

| STM-N  | Synchronous Transport Module, level N                                        |

| TDEV   | Time Deviation                                                               |

| TIE    | Time Interval Error                                                          |

| UI     | Unit Interval                                                                |

| UIpp   | Unit Interval, peak-to-peak                                                  |

| UNI    | User-Network Interface                                                       |

| VC-n   | Virtual Container, level n                                                   |

|        |                                                                              |

# 4 Network wander specification

### 4.1 Wander reference model

Wander is always specified and measured as a Relative Time Interval Error (RTIE) between the signal of interest and some reference clock. However, the reference clock against which the RTIE is specified or measured depends on the type of signal of interest. For the purposes of the present document, two cases can be distinguished.

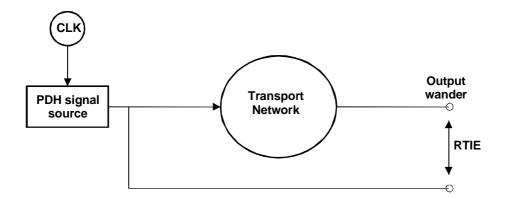

#### 1) Asynchronous PDH connection

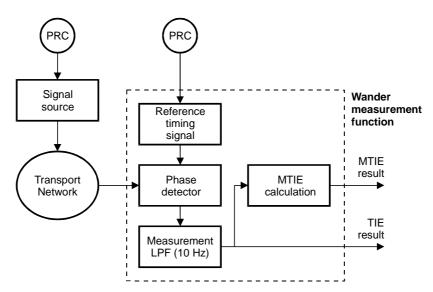

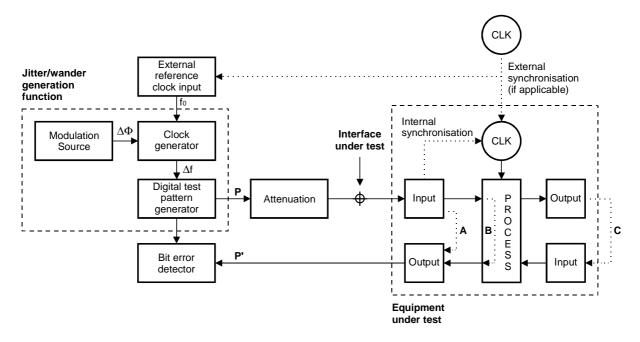

The appropriate reference for specifying the output wander of asynchronous PDH signals is the signal source itself. For measurement purposes, since that source is not normally available for use as the reference clock, it can be substituted by a suitably-filtered version of the output signal. Annex B has further information regarding this. The reference model is illustrated in figure 1.

8

NOTE: CLK frequency offset conforms to bit-rate specifications of ITU-T Recommendation G.703 [15].

#### Figure 1: Wander reference model for asynchronous PDH connection

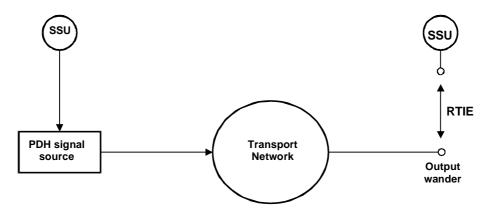

#### 2) Synchronous PDH connection

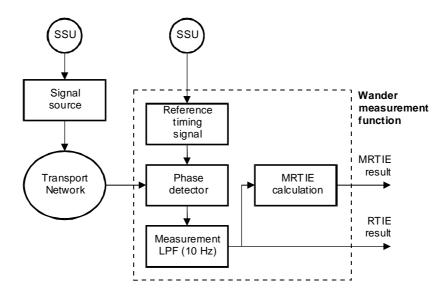

The appropriate reference for specifying the output wander of synchronous PDH signals (i.e. most 2 048 kbit/s signals as well as signals framed according to ETS 300 337 [3]) is the network clock reference used at the PDH signal termination. This means that the wander of two reference clock distribution networks is added to the output wander generated by the transport network. The reference model is illustrated in figure 2.

NOTE 1: SSU outputs conform to EN 300 462-3-1 [7] network wander limit. NOTE 2: Both SSUs are traceable to a PRC (but not necessarily the same PRC).

#### Figure 2: Wander reference model for synchronous PDH connection

Although for cases 1 and 2, different wander sources contribute to the total output wander, the resulting measured RTIE will not be very different. This is due to a lack of correlating effects and because statistically-speaking the transport network wander is the dominant source compared with the synchronization network wander. Consequently the same network limits have been set for both cases in the following output wander specifications.

The wander specifications of the present document are consistent with the derivation of limits outlined for the case of SDH network transport in annex A.

### 4.2 Specification of wander by MRTIE parameter

There are several parameters in use for specifying wander in standard specifications, such as MTIE and TDEV. For the purposes of the present document, MRTIE (Maximum Relative Time Interval Error) has been selected because it is most suitable to allow derivation of consequent equipment performance specifications.

For asynchronous payloads (refer to figure 1) the MRTIE specifies the wander accumulated by the network relative to the input signal phase. This is reasonable because it provides information for designing the filter required for any filtering of the transported signal clock in order to achieve the required phase stability of the payload.

9

For synchronous payloads (refer to figure 2) the MRTIE specifies the wander of the payload output relative to the clock phase of an input buffer (e.g. located in an exchange). This is reasonable because it provides information for designing the buffer size.

10

Measurement methodologies used to measure the MRTIE parameter are described in annex B.

# 5 Network limits for output jitter and wander

### 5.1 Network limits for output jitter

The limits given in table 1 represent the maximum permissible levels of jitter at interfaces within a digital network. Jitter as measured over a 60 second interval shall not exceed the limits given in table 1, when using the specified measurement bandwidths. The limits shall be met for all operating conditions and regardless of the amount of equipment preceding the interface. In general, these network limits are compatible with the minimum tolerance to jitter that all equipment input ports are required to provide.

There is a close relationship between network limits and input tolerance such that in terms of specification, the frequency bandwidth used for measurement and the frequency breakpoints used for tolerance, are defined using the same frequencies. In other words, the jitter measurement filter cut-off frequencies used in table 1 have the same values as the jitter tolerance mask corner frequencies used in clause 6. Annex D provides further information about this relationship.

The functional description for measuring output jitter at a digital interface can be found in ITU-T Recommendation O.172 [14].

The high-pass measurement filters of table 1 have a single-order characteristic and a roll-off of 20 dB/decade. The low-pass measurement filters have a maximally-flat, Butterworth characteristic and a roll-off of 60 dB/decade. Further specifications for the frequency response of the jitter measurement function such as measurement filter accuracy and additional allowed filter poles are given in ITU-T Recommendation O.172 [14].

Instrumentation in accordance with ITU-T Recommendations O.172 [14] and O.171 [13] is appropriate for measurement of jitter in SDH and PDH systems, respectively.

ITU-T Recommendation O.172 [14] includes test set specifications for the measurement of SDH tributaries operating at PDH bit-rates, where the test set requirements are more stringent than those relating only to PDH systems. Therefore, instrumentation in accordance with ITU-T Recommendation O.172 [14] shall be used at PDH interfaces in SDH systems.

| Interface |                                               | Measurement bandwidth                                                                                           | , Peak-to-peak amplitude                                                                                                                                                       |

|-----------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                               | -3 dB frequencies (Hz)                                                                                          | (Ulpp)                                                                                                                                                                         |

| 64 kbit/s |                                               | 20 to 20 k                                                                                                      | 0,25                                                                                                                                                                           |

| (note 1)  |                                               | 3 k to 20 k                                                                                                     | 0,05                                                                                                                                                                           |

| 2 048 kbi | t/s                                           | 20 to 100 k                                                                                                     | 1,5                                                                                                                                                                            |

|           |                                               | 18 k to 100 k (note 2)                                                                                          | 0,2                                                                                                                                                                            |

| 8 448 kbi | t/s                                           | 20 to 400 k                                                                                                     | 1,5                                                                                                                                                                            |

|           |                                               | 3 k to 400 k (note 2)                                                                                           | 0,2                                                                                                                                                                            |

| 34 368 kb | oit/s                                         | 100 to 800 k                                                                                                    | 1,5                                                                                                                                                                            |

|           |                                               | 10 k to 800 k                                                                                                   | 0,15                                                                                                                                                                           |

| 139 264   | kbit/s                                        | 200 to 3,5 M                                                                                                    | 1,5                                                                                                                                                                            |

|           |                                               | 10 k to 3,5 M                                                                                                   | 0,075                                                                                                                                                                          |

| STM-1e    |                                               | 500 to 1,3 M                                                                                                    | 1,5                                                                                                                                                                            |

| (note 3)  |                                               | 65 k to 1,3 M                                                                                                   | 0,075                                                                                                                                                                          |

| STM-1     |                                               | 500 to 1,3 M                                                                                                    | 1,5                                                                                                                                                                            |

|           |                                               | 65 k to 1,3 M                                                                                                   | 0,15                                                                                                                                                                           |

| STM-4     |                                               | 1 k to 5 M                                                                                                      | 1,5                                                                                                                                                                            |

|           |                                               | 250 k to 5 M                                                                                                    | 0,15                                                                                                                                                                           |

| STM-16    |                                               | 5 k to 20 M                                                                                                     | 1,5                                                                                                                                                                            |

|           |                                               | 1 M to 20 M                                                                                                     | 0,15                                                                                                                                                                           |

| STM-64    |                                               | 20 k to 80 M                                                                                                    | 1,5                                                                                                                                                                            |

|           |                                               | 4 M to 80 M                                                                                                     | (note 4)                                                                                                                                                                       |

| NOTE 1:   | For the d                                     | co-directional interface only.                                                                                  |                                                                                                                                                                                |

| NOTE 2:   | high-pas<br>and 80 k<br>different<br>agree ot | s cut-off frequency may be spe-<br>Hz (instead of 3 kHz) respectiv<br>operator networks, the values<br>herwise. | aces within the network of an operator, the<br>ecified to be 700 Hz (instead of 18 kHz)<br>vely. However, at interfaces between<br>in the table apply, unless involved parties |

|           |                                               | I format CMI-encoded, accord                                                                                    |                                                                                                                                                                                |

| NOTE 4:   |                                               |                                                                                                                 | ed. The effect of dispersion and                                                                                                                                               |

|           |                                               | arities on the eye opening and                                                                                  | on the choice of this value is for further                                                                                                                                     |

| NOTE 5:   | study.<br>UI Unit I                           | atoniali                                                                                                        |                                                                                                                                                                                |

| NUTE 5.   | 64 kbit/s                                     |                                                                                                                 |                                                                                                                                                                                |

|           | 2 048 kb                                      | · •                                                                                                             |                                                                                                                                                                                |

|           | 8 448 kb                                      |                                                                                                                 |                                                                                                                                                                                |

|           | 34 368 k                                      |                                                                                                                 |                                                                                                                                                                                |

|           | 0- 000 M                                      |                                                                                                                 |                                                                                                                                                                                |

|           | 139 26/                                       |                                                                                                                 |                                                                                                                                                                                |

|           | 139 264<br>STM-1                              |                                                                                                                 |                                                                                                                                                                                |

|           | STM-1                                         | 1 UI = 6,43 ns                                                                                                  |                                                                                                                                                                                |

|           |                                               | 1 UI = 6,43 ns<br>1 UI = 1,61 ns                                                                                |                                                                                                                                                                                |

| Table 1: Maximum | permissible | jitter at interfaces |

|------------------|-------------|----------------------|

|------------------|-------------|----------------------|

# 5.2 Network limits for output wander

The MRTIE specifications given in this clause are intended for application to both synchronous (i.e. normally PRC-traceable) and asynchronous (e.g. liable to a frequency offset) PDH interfaces of ETS 300 166 [1], refer to figure 1 and figure 2, respectively, for the reference network configurations.

It is required that, within a synchronized network, digital equipment provided at nodes shall accommodate permitted phase deviations on the incoming signal, i.e. under normal synchronized conditions, impairments will not occur.

However, it should be recognized that, as a result of some performance degradations, failure conditions, maintenance actions and other events, the RTIE between the incoming signal and the internal timing signal of the terminating equipment may exceed the jitter and wander tolerance of the equipment which may result in an abnormal event such as a controlled slip or bit-error burst.

In addition, at a node which connects to an independently-synchronized network (or where plesiochronous operation is used in national networks), the RTIE between the incoming signal and the internal timing signal of the terminating equipment may eventually exceed the jitter and wander tolerance of the equipment in which case an abnormal event such as a controlled slip may occur. The maximum permissible long-term mean controlled slip rate resulting from this mechanism is derived from the clock performance defined in EN 300 462-6-1 [10], i.e. no more than one slip in 70 days.

12

The wander measurement requirements (e.g. sampling time and measurement interval) for MTIE, MRTIE and TDEV parameters, the 10 Hz wander measurement filter characteristic and the functional description for measuring output wander are described in ITU-T Recommendation O.172 [14].

Instrumentation in accordance with ITU-T Recommendation O.172 [14] is appropriate for measurement of wander parameters at both SDH and PDH interfaces.

Measurement methodologies used to measure the MRTIE parameter are described in annex B.

### 5.2.1 2 048 kbit/s interface output wander limit

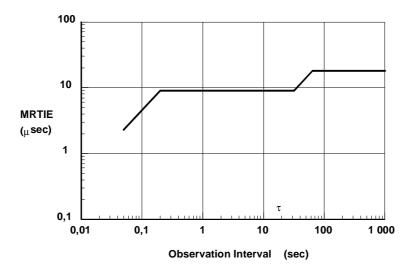

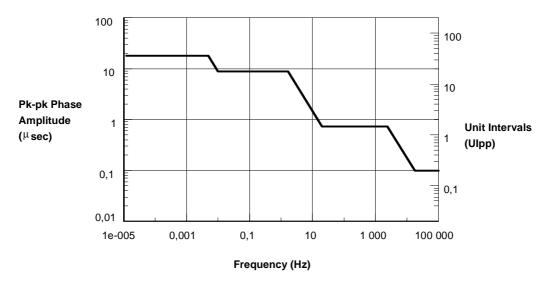

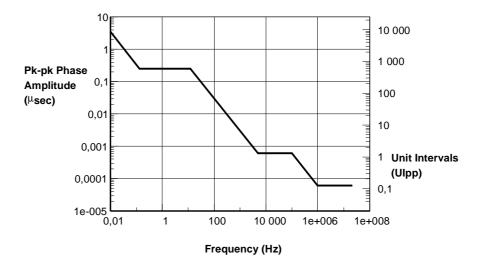

The maximum level of wander that may exist at a 2 048 kbit/s network interface, expressed in MRTIE, shall not exceed the limit given in table 2. The resultant overall specification is illustrated in figure 3.

| Observation Interval<br>τ (sec)                    |                                      | MRTIE requirement |  |

|----------------------------------------------------|--------------------------------------|-------------------|--|

| (                                                  | $0,05 < \tau \le 0,2$                | 46τ μs            |  |

| $0,2 < \tau \leq 32$                               |                                      | 9 μs              |  |

| $32 < \tau \le 64$                                 |                                      | 0,28τ μs          |  |

| 64 <                                               | <ul> <li>τ ≤ 1 000 (note)</li> </ul> | 18 μs             |  |

| NOTE: For the asynchronous configuration (refer to |                                      |                   |  |

| figure 1), the maximum observation interval to     |                                      |                   |  |

| be considered is 80 seconds.                       |                                      |                   |  |

Table 2: 2 048 kbit/s interface output wander limit

Figure 3: 2 048 kbit/s interface output wander limit

### 5.2.2 34 368 kbit/s interface output wander limit

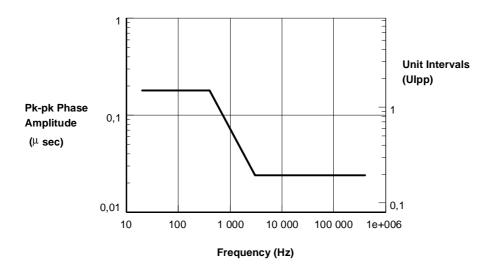

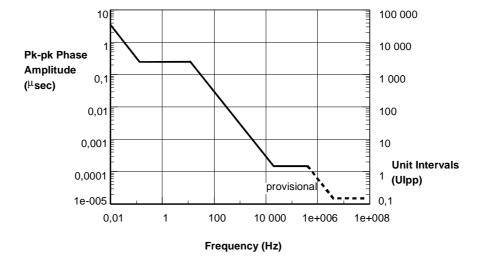

The maximum level of wander that may exist at a 34 368 kbit/s network interface, expressed in MRTIE, shall not exceed the limit given in table 3. The resultant overall specification is illustrated in figure 4. 34 368 kbit/s signals can be framed in accordance with ETS 300 337 [3]; in the case when these are used as a synchronization interface, the output wander limit is for further study.

13

| Observation Interval<br>τ (sec) | MRTIE requirement |

|---------------------------------|-------------------|

| $0,05<\tau\leq0,073$            | 14τ μs            |

| $0,073 < \tau \le 2,5$          | 1 μs              |

| $2,5 < \tau \le 10$             | 0,4τ μs           |

| $10 < \tau \le 80$              | 4 μs              |

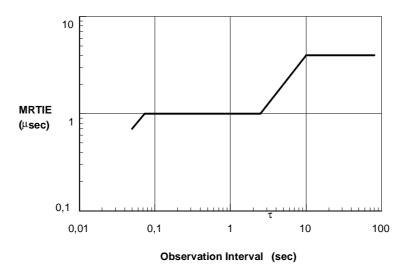

Table 3: 34 368 kbit/s interface output wander limit

Figure 4: 34 368 kbit/s interface output wander limit

### 5.2.3 139 264 kbit/s interface output wander limit

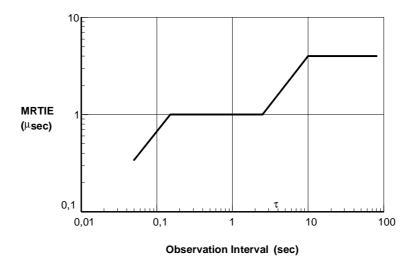

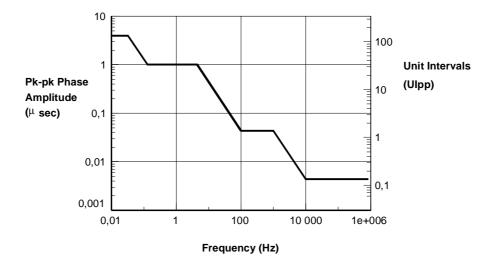

The maximum level of wander that may exist at a 139 264 kbit/s network interface, expressed in MRTIE, shall not exceed the limit given in table 4. The resultant overall specification is illustrated in figure 5. 139 264 kbit/s signals can be framed in accordance with ETS 300 337 [3]; in the case when these are used as a synchronization interface, the output wander limit is for further study.

| Observation Interval<br>τ (sec) | MRTIE requirement |

|---------------------------------|-------------------|

| $0,05 < \tau \le 0,15$          | 6,8τ μs           |

| $0,15<\tau\leq 2,5$             | 1 μs              |

| $2,5 < \tau \le 10$             | 0,4τ μs           |

| $10 < \tau \le 80$              | 4 μs              |

| Table 4: 139 264 | kbit/s | interface | output | wander | limit |

|------------------|--------|-----------|--------|--------|-------|

|------------------|--------|-----------|--------|--------|-------|

Figure 5: 139 264 kbit/s interface output wander limit

### 5.2.4 STM-N interface output wander limit

STM-N interfaces are defined as synchronization interfaces, and the network limits for wander at synchronization interfaces are specified in EN 300 462-3-1 [7].

# 6 Jitter and wander tolerance of equipment interfaces

In order to ensure that, in general, any equipment can be connected to any appropriate interface within a network, it is necessary to arrange that the input ports of all equipment are capable of accommodating levels of jitter and wander up to at least the minimum limits defined in the following clauses.

The jitter and wander tolerance of an SDH or PDH interface indicates the minimum level of phase noise that the input port shall accommodate whilst:

- not causing any alarms;

- not causing any slips; and

- not causing any bit errors; except for optical STM-N interfaces at jitter frequencies above f<sub>P</sub>, (refer to table 12, table 13 and table 14) where an equivalent 1 dB optical power penalty shall not be exceeded.

All digital input ports of equipment shall be able to tolerate a digital signal that has:

- electrical characteristics in accordance with the requirements of ETS 300 166 [1] or the optical characteristics of ETS 300 232 [2];

- a constant frequency offset (relative to the nominal value) in the range defined in table 5;

- a rate of change in frequency up to at least 0,5 ppm/minute for all STM-N interfaces; and

- a sinusoidal phase deviation having an amplitude-frequency relationship defined in the following clauses which indicates the appropriate limits for the different interfaces.

In principle, these requirements shall be met regardless of the information content of the digital signal. However, for test purposes, the content of the signal with jitter and wander modulation should be a structured test sequence as defined in the following clauses.

When specifying or assessing interface tolerance, two equipment operating conditions can be distinguished:

- non-synchronized operation, where the receiving equipment is not being timed from a source that is synchronous with the interface under consideration. In this case, it is the equipment capability to accommodate phase variation on the incoming signal (in terms of clock recovery circuitry and synchronizer/desynchronizer buffers) that is of interest;

- synchronized operation, where the receiving equipment is being timed from a source that is synchronous with the interface under consideration. In this case, slip buffer dimension and operation is also of interest.

Unless otherwise stated, the tolerance specifications in the following clauses apply to both asynchronous and synchronous operating conditions.

The jitter and wander limit above 10 Hz reflects the maximum permissible jitter magnitude in a digital network. However the limit below 10 Hz does not aim to represent the maximum permissible wander that might occur in practice. Below 10 Hz the limits are derived such that where necessary, the provision of this level of buffer storage at the input of an equipment facilitates the accommodation of wander generated in a large proportion of real connections.

For convenience of testing, the required tolerance is defined in terms of the peak-to-peak amplitude and frequency of sinusoidal jitter which modulates a digital test pattern. It is important to recognize that this test condition is not, in itself, intended to be representative of the type of jitter found in practice in a network.

Guidance on the measurement set-up for input jitter and wander tolerance is provided in annex C.

Instrumentation in accordance with ITU-T Recommendations O.172 [14] and O.171 [13] is appropriate for generation of jitter and wander in SDH and PDH systems, respectively.

| Interface                                                                                                  | Maximum<br>frequency offset<br>(± ppm) | Example Application                |

|------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------|

| 64 kbit/s                                                                                                  | 0                                      | Switch input channel               |

| 2 048 kbit/s                                                                                               | 0                                      | Switch, 1/0 cross-connect          |

| 2 048 kbit/s                                                                                               | 4,6                                    | Byte-synchronous mapping into SDH  |

| 2 048 kbit/s                                                                                               | 50                                     | PDH, asynchronous mapping into SDH |

| 8 448 kbit/s                                                                                               | 30                                     | PDH                                |

| 34 368 kbit/s                                                                                              | 20                                     | PDH, asynchronous mapping into SDH |

| 34 368 kbit/s                                                                                              | 4,6                                    | Signal defined in ETS 300 337 [3]  |

| 139 264 kbit/s                                                                                             | 15                                     | PDH, asynchronous mapping into SDH |

| 139 264 kbit/s                                                                                             | 4,6                                    | Signal defined in ETS 300 337 [3]  |

| STM-N                                                                                                      | 4,6                                    | SDH                                |

| STM-N                                                                                                      | 20                                     | MS-AIS in SDH regenerator sections |

| NOTE: Frequency offset values are aligned with ETS 300 166 [1], EN 300 462-5-1 [9] and EN 300 417-1-1 [4]. |                                        |                                    |

Table 5: Maximum frequency offset at interfaces

### 6.1 64 kbit/s input jitter and wander tolerance

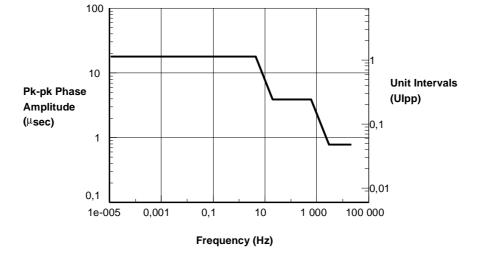

The level of jitter and wander that can be accommodated by a 64 kbit/s co-directional network interface, expressed in peak-to-peak sinusoidal phase deviation, shall exceed the limit given in table 6. The resultant overall specification is illustrated in figure 6. The test sequence to be used is a PRBS of length  $2^{11}$  - 1, defined in ITU-T Recommendation O.150 [12].

| Frequency<br>f (Hz) |                                          | rement<br>se amplitude) |

|---------------------|------------------------------------------|-------------------------|

| 12 μ < f ≤ 4,3      | 18 μs                                    | 1,2 UI                  |

| 4,3 < f ≤ 20        | 77 f <sup>-1</sup> μs                    | 5 f <sup>-1</sup> UI    |

| $20 < f \le 600$    | 3,9 μs                                   | 0,25 UI                 |

| 600 < f ≤ 3 k       | 2,3 x 10 <sup>3</sup> f <sup>-1</sup> μs | 150 f <sup>-1</sup> UI  |

| 3 k < f ≤ 20 k      | 0,78 μs                                  | 0,05 UI                 |

Figure 6: 64 kbit/s input jitter and wander tolerance limit

# 6.2 2 048 kbit/s input jitter and wander tolerance

The level of jitter and wander that can be accommodated by a 2 048 kbit/s network interface, expressed in peak-to-peak sinusoidal phase deviation, shall exceed the limits given in table 7. The resultant overall specification is illustrated in figure 7. The test sequence to be used is a PRBS of length  $2^{15}$  - 1, defined in ITU-T Recommendation O.150 [12].

| Frequency<br>f (Hz)                                                                                                                                                                                                                                                                                              | Requirement<br>(pk-pk phase amplitude) |                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------|

| 12 μ < f ≤ 4,88 m                                                                                                                                                                                                                                                                                                | 18 μs                                  | 37 UI                                    |

| 4,88 m < f ≤ 10 m                                                                                                                                                                                                                                                                                                | 0,088 f <sup>-1</sup> μs               | 0,18 f <sup>-1</sup> UI                  |

| 10 m < f ≤ 1,67                                                                                                                                                                                                                                                                                                  | 8,8 μs                                 | 18 UI                                    |

| 1,67 < f ≤ 20                                                                                                                                                                                                                                                                                                    | 15 f <sup>-1</sup> μs                  | 30 f <sup>-1</sup> UI                    |

| 20 < f ≤ 2,4 k (note)                                                                                                                                                                                                                                                                                            | 0,73 μs                                | 1,5 UI                                   |

| 2,4 k < f ≤ 18 k (note)                                                                                                                                                                                                                                                                                          | 1,8 x 10 <sup>3</sup> μs               | 3,6 x 10 <sup>3</sup> f <sup>-1</sup> UI |

| 18 k < f ≤ 100 k (note)                                                                                                                                                                                                                                                                                          | 0,098 μs                               | 0,2 UI                                   |

| NOTE: For 2 048 kbit/s interfaces within the network of an operator, the frequencies<br>may be specified as 93 Hz (instead of 2,4 kHz) and 700 Hz (instead of<br>18 kHz). However, at interfaces between different operator networks, the<br>values in the table apply, unless involved parties agree otherwise. |                                        |                                          |

Table 7: 2 048 kbit/s input jitter and wander tolerance limits

Figure 7: 2 048 kbit/s input jitter and wander tolerance limits

### 6.3 8 448 kbit/s input jitter and wander tolerance

The level of jitter and wander that can be accommodated by a 8 448 kbit/s network interface, expressed in peak-to-peak sinusoidal phase deviation, shall exceed the limit given in table 8. The resultant overall specification is illustrated in figure 8. The test sequence to be used is a PRBS of length  $2^{15}$  - 1, defined in ITU-T Recommendation O.150 [12].

| Table 8: 8 448 kbit/s input jitter and | I wander tolerance limit |

|----------------------------------------|--------------------------|

|----------------------------------------|--------------------------|

| Frequency<br>f (Hz)                                                                                                                                                                                                                                                                                      | Requirement<br>(pk-pk phase amplitude) |                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------|

| 20 < f ≤ 400 (note)                                                                                                                                                                                                                                                                                      | 0,18 μs                                | 1,5 UI                 |

| 400 < f ≤ 3 k (note)                                                                                                                                                                                                                                                                                     | 72 f <sup>-1</sup> μs                  | 600 f <sup>-1</sup> UI |

| 3 k < f ≤ 400 k (note)                                                                                                                                                                                                                                                                                   | 0,024 µs 0,2 UI                        |                        |

| NOTE: For 8 448 kbit/s interfaces within the network of an operator, the frequencies may be specified as 10,7 kHz (instead of 400 Hz) and 80 kHz (instead of 3 kHz). However, at interfaces between different operator networks, the values in the table apply, unless involved parties agree otherwise. |                                        |                        |

Figure 8: 8 448 kbit/s input jitter and wander tolerance limit

### 6.4 34 368 kbit/s input jitter and wander tolerance

The level of jitter and wander that can be accommodated by a 34 368 kbit/s network interface, expressed in peak-to-peak sinusoidal phase deviation, shall exceed the limit given in table 9. The resultant overall specification is illustrated in figure 9. The test sequence to be used is a PRBS of length  $2^{23}$  - 1, defined in ITU-T Recommendation O.150 [12]; for signals in accordance with ETS 300 337 [3], the test sequence to be used is for further study.

| Frequency<br>f (Hz) | Requirement<br>(pk-pk phase amplitude)   |                                          |

|---------------------|------------------------------------------|------------------------------------------|

| 10 m < f ≤ 32 m     | 4 μs                                     | 140 UI                                   |

| 32 m < f ≤ 130 m    | 0,13 f <sup>-1</sup> μs                  | 4,5 f <sup>-1</sup> UI                   |

| 130 m < f ≤ 4,4     | 1 μs                                     | 34 UI                                    |

| 4,4 < f ≤ 100       | 4,4 f <sup>-1</sup> μs                   | 150 f <sup>-1</sup> UI                   |

| 100 < f ≤ 1 k       | 44 ns                                    | 1,5 UI                                   |

| 1 k < f ≤ 10 k      | 4,4 x 10 <sup>4</sup> f <sup>-1</sup> ns | 1,5 x 10 <sup>3</sup> f <sup>-1</sup> UI |

| 10 k < f ≤ 800 k    | 4,4 ns                                   | 0,15 UI                                  |

Table 9: 34 368 kbit/s input jitter and wander tolerance limit

Figure 9: 34 368 kbit/s input jitter and wander tolerance limit

### 6.5 139 264 kbit/s input jitter and wander tolerance

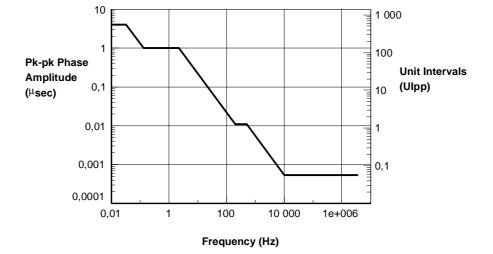

The level of jitter and wander that can be accommodated by a 139 264 kbit/s network interface, expressed in peak-to-peak sinusoidal phase deviation, shall exceed the limit given in table 10. The resultant overall specification is illustrated in figure 10. The test sequence to be used is a PRBS of length  $2^{23}$  - 1, defined in ITU-T Recommendation O.150 [12]; for signals in accordance with ETS 300 337 [3], the test sequence to be used is for further study.

| Frequency<br>f (Hz) |                                          | rement<br>e amplitude) |

|---------------------|------------------------------------------|------------------------|

| 10 m < f ≤ 32 m     | 4 μs                                     | 560 UI                 |

| 32 m < f ≤ 130 m    | 0,13 f <sup>-1</sup> μs                  | 18 f <sup>-1</sup> UI  |

| 130 m < f ≤ 2,2     | 1 μs                                     | 140 UI                 |

| $2,2 < f \le 200$   | 2,2 f <sup>-1</sup> μs                   | 300 f <sup>-1</sup> UI |

| $200 < f \le 500$   | 11 ns                                    | 1,5 UI                 |

| 500 < f ≤ 10 k      | 5,5 x 10 <sup>3</sup> f <sup>-1</sup> ns | 750 f <sup>-1</sup> UI |

| 10 k < f ≤ 3,5 m    | 0,54 ns                                  | 0,075 UI               |

Table 10: 139 264 kbit/s input jitter and wander tolerance limit

Figure 10: 139 264 kbit/s input jitter and wander tolerance limit

### 6.6 STM-N input jitter and wander tolerance

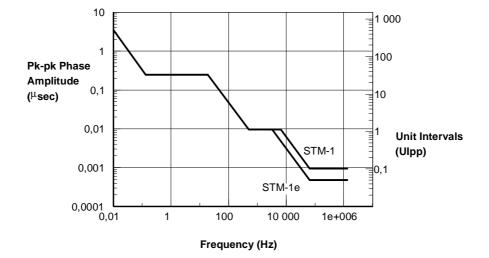

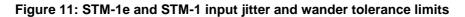

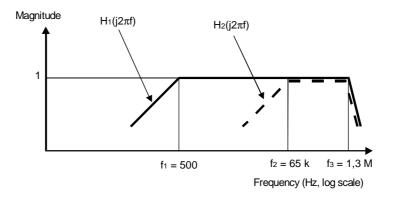

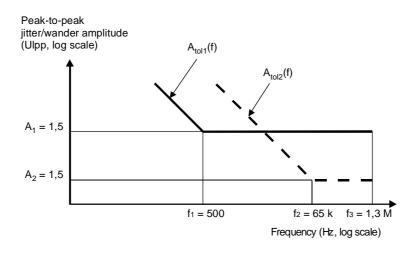

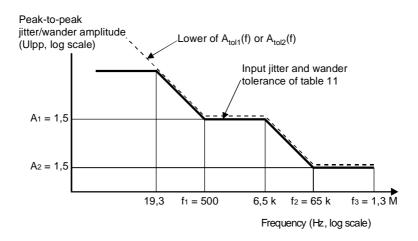

The level of jitter and wander that can be accommodated by a STM-N network interface, expressed in peak-to-peak sinusoidal phase deviation, shall exceed the limits given in tables 11, 12, 13, 14 and 15 for STM-1e, STM-1, STM-4, STM-16 and STM-64, respectively. The resultant overall specification is illustrated in figure 11, figure 12, figure 13 and figure 14 for STM-1e/-1, STM-4, STM-16 and STM-64, respectively. Guidance on the test sequences suitable for SDH systems is provided in ITU-T Recommendation O.172 [14].

| Frequency<br>f (Hz)    | Requirement, STM-1e interface<br>(pk-pk phase amplitude) |                                          |

|------------------------|----------------------------------------------------------|------------------------------------------|

| 10 m < f ≤ 130 m       | 0,033 f <sup>-1</sup> μs                                 | 5,1 f <sup>-1</sup> UI                   |

| 130 m < f ≤ 19,3       | 0,25 μs                                                  | 39 UI                                    |

| 19,3 < f ≤ 500         | 4,8 f <sup>-1</sup> μs                                   | 750 f <sup>-1</sup> UI                   |

| 500 < f ≤ 3,3 k        | 9,7 ns                                                   | 1,5 UI                                   |

| 3,3 k < f ≤ 65 k       | 3,2 x 10 <sup>4</sup> f <sup>-1</sup> ns                 | 4,9 x 10 <sup>3</sup> f <sup>-1</sup> UI |

| 65 k < f ≤ 1,3 M       | 0,48 ns                                                  | 0,075 UI                                 |

| NOTE: STM-1e interface | e is electrical format CMI-encode                        | d, according to                          |

| ETS 300 166 [1]        |                                                          |                                          |

| Table 11: STM-1e input jitter and wander tolerance limits |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

| Frequency<br>f (Hz)                     |                                          | STM-1 interface<br>e amplitude)          |

|-----------------------------------------|------------------------------------------|------------------------------------------|

| 10 m < f ≤ 130 m                        | 0,033 f <sup>-1</sup> μs                 | 5,1 f <sup>-1</sup> UI                   |

| 130 m < f ≤ 19,3                        | 0,25 μs                                  | 39 UI                                    |

| 19,3 < f ≤ 500                          | 4,8 f <sup>-1</sup> μs                   | 750 f <sup>-1</sup> UI                   |

| 500 < f ≤ 6,5 k (note)                  | 9,7 ns                                   | 1,5 UI                                   |

| 6,5 k < f ≤ 65 k                        | 6,3 x 10 <sup>4</sup> f <sup>-1</sup> ns | 9,8 x 10 <sup>3</sup> f <sup>-1</sup> UI |

| 65 k < f ≤ 1,3 M                        | 0,97 ns                                  | 0,15 UI                                  |

| NOTE: f <sub>P</sub> (refer to clause 6 | i) is 6,5 kHz for STM-1 interfac         | e.                                       |

Table 12: STM-1 input jitter and wander tolerance limits

| Frequency<br>f (Hz)                     | Requirement<br>(pk-pk phase amplitude)         |                                          |

|-----------------------------------------|------------------------------------------------|------------------------------------------|

| 10 m < f ≤ 130 m                        | 0,033 f <sup>-1</sup> μs                       | 21 f <sup>-1</sup> UI                    |

| 130 m < f ≤ 9,65                        | 0,25 μs                                        | 160 UI                                   |

| 9,65 < f ≤ 1 k                          | 2,4 f <sup>-1</sup> μs                         | 1,5 x 10 <sup>3</sup> f <sup>-1</sup> UI |

| 1 k < f ≤ 25 k (note)                   | 2,4 ns                                         | 1,5 UI                                   |

| 25 k < f ≤ 250 k                        | 6 x 10 <sup>4</sup> f <sup>-1</sup> ns         | 3,8 x 10 <sup>4</sup> f <sup>-1</sup> UI |

| 250 k < f ≤ 5 M                         | 0,24 ns                                        | 0,15 UI                                  |

| NOTE: f <sub>P</sub> (refer to clause 6 | <ol><li>is 25 kHz for STM-4 interfac</li></ol> | e.                                       |

Table 13: STM-4 input jitter and wander tolerance limit

| Frequency<br>f (Hz)                                              | Requir<br>(pk-pk phase)                | ement<br>e amplitude)                    |

|------------------------------------------------------------------|----------------------------------------|------------------------------------------|

| 10 m < f ≤ 130 m                                                 | 0,033 f <sup>-1</sup> μs               | 82 f <sup>-1</sup> UI                    |

| 130 m < f ≤ 12,1                                                 | 0,25 μs                                | 620 UI                                   |

| 12,1 < f ≤ 5 k                                                   | 3 f <sup>-1</sup> μs                   | 7,5 x 10 <sup>3</sup> f <sup>-1</sup> UI |

| 5 k < f ≤ 100 k (note)                                           | 0,6 ns                                 | 1,5 UI                                   |

| 100 k < f ≤ 1 M                                                  | 6 x 10 <sup>4</sup> f <sup>-1</sup> ns | 1,5 x 10 <sup>5</sup> f <sup>-1</sup> UI |

| 1 M < f ≤ 20 M                                                   | 0,06 ns                                | 0,15 UI                                  |

| NOTE: $f_P$ (refer to clause 6) is 100 kHz for STM-16 interface. |                                        |                                          |

| Table 14: STM-16 input jitter and wander tolerance limit |

|----------------------------------------------------------|

|----------------------------------------------------------|

Figure 13: STM-16 input jitter and wander tolerance limit

| Frequency<br>f (Hz)                                                                  | Requirement<br>(pk-pk phase amplitude) |                                        |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|--|--|

| 10 m < f ≤ 130 m                                                                     | 0,033 f <sup>-1</sup> μs               | 330 f <sup>-1</sup> UI                 |  |  |

| 130 m < f ≤ 12,1                                                                     | 0,25 μs                                | 2,5 x 10 <sup>3</sup> UI               |  |  |

| 12,1 < f ≤ 20 k                                                                      | 3 f <sup>-1</sup> μs                   | 3 x 10 <sup>4</sup> f <sup>-1</sup> UI |  |  |

| 20 k < f ≤ 400 k (note 1, 2)                                                         | 0,15 ns                                | 1,5 UI                                 |  |  |

| $400 \text{ k} < f \le 4 \text{ M}$                                                  | 6 x 10 <sup>4</sup> f <sup>-1</sup> ns | 6 x 10 <sup>5</sup> f <sup>-1</sup> UI |  |  |

| 4 M < f ≤ 80 M                                                                       | 0,015 ns                               | 0,15 UI (note 1)                       |  |  |

| NOTE 1: Values of 0,15 UI and 400 kHz are provisional and are for further study.     |                                        |                                        |  |  |

| NOTE 2: f <sub>P</sub> (refer to clause 6) is 400 kHz (note 1) for STM-64 interface. |                                        |                                        |  |  |

| Table 15: STM-64 in | put iitter | and wander | tolerance limit |

|---------------------|------------|------------|-----------------|

|                     |            |            |                 |

Figure 14: STM-64 input jitter and wander tolerance limit

# Annex A (informative): Wander limit considerations for SDH transport networks

# A.1 Introduction

The information in annex A is provided to assist an understanding of the derivation of the network wander limits and input wander tolerances that are specified in the present document.

### A.1.1 Wander reference model for SDH

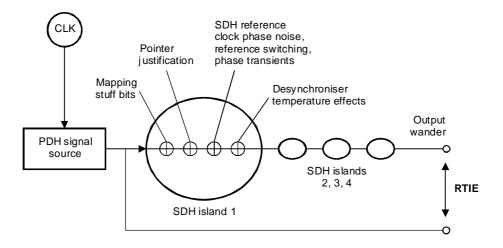

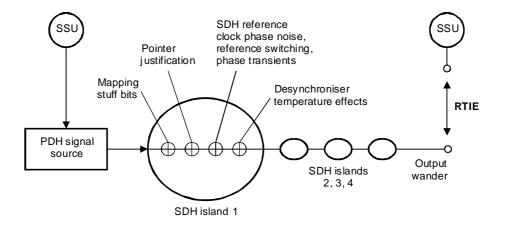

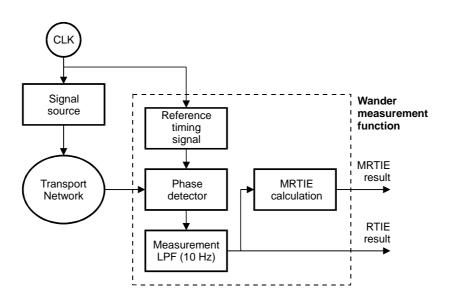

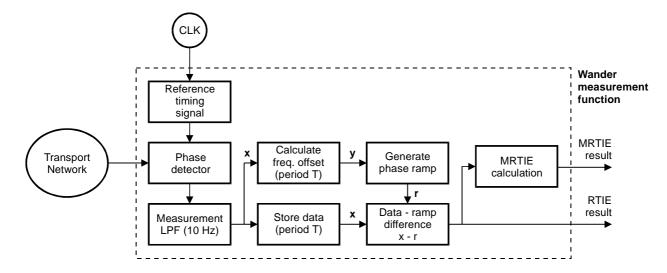

The wander reference models as shown in figure A.1 and figure A.2 are simplified representations of the wander reference model described in annex B of EN 300 462-3-1 [7]. They also illustrate how the generic reference models of figure 1 and figure 2 can accommodate network-specific sources of wander using the example of an SDH transport network.

Four cascaded SDH islands have been considered to be a reasonable modelling approach in previous jitter and wander accumulation computer simulation calculations. This approach is adopted in annex A. Figure A.1 and figure A.2 illustrate the principal sources of wander on network connections that have been considered when deriving the network limits and interface tolerances.

NOTE: CLK frequency offset conforms to bit-rate specifications of ITU-T Recommendation G.703 [15].

#### Figure A.1: Wander reference model for asynchronous PDH signals

NOTE 1: SSU outputs conform to EN 300 462-3-1 [7] network wander limit. NOTE 2: Both SSUs are traceable to a PRC (but not necessarily the same PRC).

#### Figure A.2: Wander reference model for synchronous PDH signals

### A.1.2 Sources of wander

The wander accumulated on payload signals when they are transported over a network connection employing SDH network elements depends on the total dynamic fill of all intermediate signal processing buffers in those network elements. The buffer fill of a single Network Element (NE) depends on the relative wander between the incoming data and the read clock. The read clock may be provided from an external source (e.g. in a pointer processor) or may be provided from a recovered clock (e.g. in a desynchronizer).

The buffer fill may be changed by reference clock phase noise and transient effects (e.g. bit-stuffing, pointer processing) and by temperature effects in phase-locked loops (e.g. desynchronizer clock recovery).

### A.1.3 Wander accumulation limiting effects

At least when considering 2 048 kbit/s connections, the total amount of these buffers in a single connection may exceed the 18  $\mu$ s limit requested as a limit for the daily wander in the present document. But under normal operating conditions, these buffer fills remain almost constant due to a stable network synchronization performance. Furthermore the fluctuating part of the buffer fills contributes only randomly to the accumulation because of a lack of correlating effects between different buffers.

### A.1.4 Network configuration and performance

The SDH islands (refer to figure A.1 and figure A.2) are normally internally-synchronized so that pointer justifications (at least at TU-12 level) are rare events. An exceptional case is when one or more of the NEs is operated using a clock source that is in holdover mode, so generating an approximately regular sequence of pointer justifications.

Under normal conditions, it is unlikely that two or more of these SDH islands are not internally-synchronized. It is also unlikely that a double pointer justification is generated in a single NE. Therefore it is improbable that the cumulative wander effect of more than two simultaneous pointer justifications will occur. Such rare cases may cause wander that will exceed the network limits specified in the present document.

In general, the performance of the SDH islands should be good enough that the error and slip performance of the transported signal are not more than marginally affected by excessive phase noise effects that would cause buffer overflow in some NE.

### A.1.5 Correlation of wander sources