# Design of a Closed-Loop, Bidirectional Brain Machine Interface System With Energy Efficient Neural Feature Extraction and PID Control

Xilin Liu, Student Member, IEEE, Milin Zhang, Member, IEEE, Andrew G. Richardson, Member, IEEE, Timothy H. Lucas, Member, IEEE, and Jan Van der Spiegel, Fellow, IEEE

Abstract-This paper presents a bidirectional brain machine interface (BMI) microsystem designed for closed-loop neuroscience research, especially experiments in freely behaving animals. The system-on-chip (SoC) consists of 16-channel neural recording front-ends, neural feature extraction units, 16channel programmable neural stimulator back-ends, in-channel programmable closed-loop controllers, global analog-digital converters (ADC), and peripheral circuits. The proposed neural feature extraction units includes 1) an ultra low-power neural energy extraction unit enabling a 64-step natural logarithmic domain frequency tuning, and 2) a current-mode action potential (AP) detection unit with time-amplitude window discriminator. A programmable proportional-integral-derivative (PID) controller has been integrated in each channel enabling a various of closed-loop operations. The implemented ADCs include a 10-bit voltage-mode successive approximation register (SAR) ADC for the digitization of the neural feature outputs and/or local field potential (LFP) outputs, and an 8-bit current-mode SAR ADC for the digitization of the action potential outputs. The multi-mode stimulator can be programmed to perform monopolar or bipolar, symmetrical or asymmetrical charge balanced stimulation with a maximum current of 4 mA in an arbitrary channel configuration. The chip has been fabricated in  $0.18\mu$  m CMOS technology, occupying a silicon area of 3.7 mm<sup>2</sup>. The chip dissipates 56  $\mu$ W/ch on average. General purpose low-power microcontroller with Bluetooth module are integrated in the system to provide wireless link and SoC configuration. Methods, circuit techniques and system topology proposed in this work can be used in a wide range of relevant neurophysiology research, especially closed-loop BMI experiments.

*Index Terms*—Brain machine interface, closed-loop, low-power, neural feature extraction, neural recording, neural stimulation, proportional-integral-derivative (PID).

Manuscript received February 5, 2016; revised April 17, 2016 and June 29, 2016; accepted July 14, 2016. Date of publication December 16, 2016; date of current version July 26, 2017. This work was supported in part by the National Science Foundation grant 1404041. This paper was recommended by Associate Editor A. Basu. (*Corresponding author: M. Zhang.*)

X. Liu and J. V. d. Spiegel are with the Department of Electrical and Systems Engineering (ESE), University of Pennsylvania, Philadelphia, PA 19104 USA (email: xilinliu@seas.upenn.edu; jan@seas.upenn.edu).

M. Zhang is with the Department of Electronic Engineering, Tsinghua University, Beijing 100084, China (email: zhangmilin@tsinghua.edu.cn).

A. G. Richardson and T. H. Lucas are with the Department of Neurosurgery, University of Pennsylvania, Philadelphia, PA 19104 USA (email: andrew.richardson@uphs.upenn.edu; Timothy.Lucas@uphs.upenn.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TBCAS.2016.2622738

#### I. INTRODUCTION

**B** RAIN machine interface (BMI) is a device designed to generate an artificial communication pathway between the brain and the external hardware. BMI has been widely used in neuroprosthetics system to restore the communication lines that has been lost due to neural injury or disease [1]. Clinical experimental results have shown that paralyzed individuals can control a prosthetic limb [2], [3] according to the motor intent decoded from neural signals recorded by a BMI. At the same time, neural stimulation has been used to apply encoded patterns to the brain as the sense of touch and proprioception according to state of the prosthesis and its interaction with the environment [4], [5]. Establishing a bidirectional, sensorimotor neural interface is necessary to achieving the level of performance required for this technology to be clinically relevant [6], [7]. Therefore, design of a bidirectional, closed-loop neural interface integrated neural recording, stimulation and the signal processing module is critical.

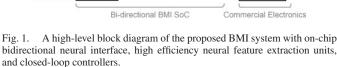

However, majority of existing designs are open-loop, singledirectional devices, focusing on either neural signal recording, or neural stimulation. The absence of a closed-loop BMI device limits the application of BMI in neuroscience research and clinical practice. In addition, in existing BMI system, neural signal processing is usually performed in high-speed external computer, which is impractical for a multiple electrode array (MEA) due to the high data rate and the delay caused in data interface and computer computation. Furthermore, the huge amount of neural data places a big challenge on data transmission, resulting in high power consumption and high data loss, especially for wireless system implementation. One promising solution to these problems is to implement the most computation intensive neural feature extraction units and closed-loop controllers onchip, which greatly reduces latency, wireless data rate, and system power consumption. Fig. 1 illustrates the high-level block diagram of the proposed BMI system.

Recently, BMI systems integrated on-chip signal processing have been reported in the literature [8]–[12]. In the reported designs, neural features, i.e., LFP energy and action potential are commonly used as effective neural features or feedback indicators. Both analog and digital implementations of the neural feature extraction modules have been proposed. The traditional analog implementation can achieve a higher power efficiency,

1932-4545 © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

but usually suffering from poor programmability and low linearity. While the conventional digital processor makes use of a serial computation, which will not be able to provide an efficient feature extraction capability for a large number of channels.

In this work, we proposed a fully programmable, bidirectional neural interface system for closed-loop neuroscience experiments. The system consists of a custom SoC, which performs noise sensitive neural signal recording, high safety neural stimulation, computation intensive neural feature extraction, and on-chip closed-loop operation. Novel implementation of digital-assisted analog parallel neural feature extraction units are proposed. The prototype system takes advantage of the programmability of general purpose microcontroller (MCU) with integrated flash memory, and universal wireless protocol (Bluetooth) to interface with general computers or work stations. Commercial sensor (3-axis accelerometer) has also been integrated in the system to monitoring the animal activities. Wireless inductive charging module is integrated for easily recharging the batteries.

This paper is organized as follows. Section II introduces the overall system with featured innovations. Section III describes the circuit implementation of each block. Experimental results are shown in Section IV, while Section V concludes the entire work.

# II. SYSTEM OVERVIEW AND MOTIVATIONS

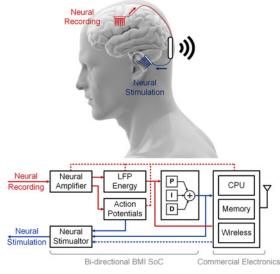

The goal of the proposed system is to provide a reliable generalized BMI for bidirectional and closed-loop neuroscience experiments, especially for experiments performed on freely behaving animals. To achieve this goal, design optimizations are performed from neuron-electronics interface level up to the system level. The overall architecture of the proposed BMI system is as shown in Fig. 2. The system consists of the custom SoC and general purpose electronics available off-the-shelf.

# A. Natural Logarithmic Domain Neural Energy Extraction

A substantial amount of information regarding motor intent can be inferred from field potential recordings [13], [14]. Field potentials, either recorded with electrodes penetrating into the brain or at the brain surface, reflect the summed activity of thousands to millions of neurons. Oscillations are particularly prominent in field potential recordings and reflect synchronous, rhythmic changes in activity across the network. The recorded oscillations contain information correlated with a number of different behavioral processes, i.e., motor planning [15]. While decoding intent from field potentials for a neuroprosthetic application, it is typical to extract energy from several discrete frequency bands [9].

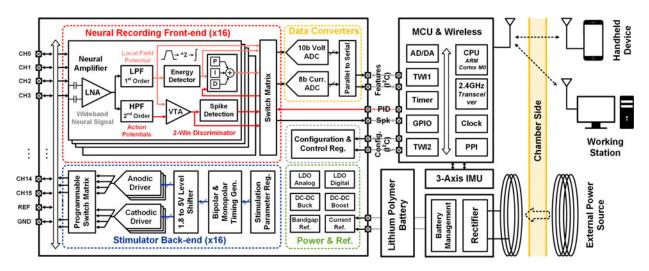

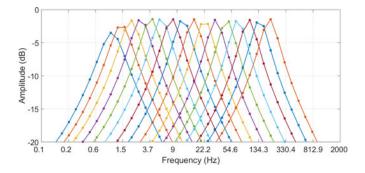

A variety of distinct brain oscillations exist, with center frequencies spaced logarithmically [16], as illustrated in Fig. 3. Linear tuning of the neural extraction filters is widely used in conventional LFP recording hardware designs, which is not efficient for extraction brain oscillations. A natural logarithmic domain tuning is proposed in this work, which provides sufficient resolution for extracting the low-frequency brain oscillations, without increasing the number of tuning steps.

# B. Closed-Loop System Using PID Controller

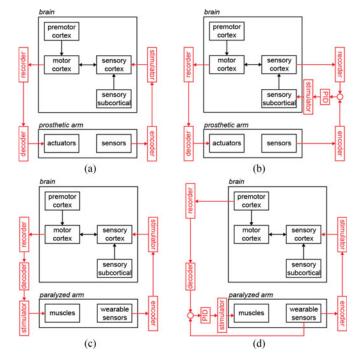

In a typical bidirectional BMI, as illustrated in Fig. 4(a), the user determines how to update the motor intent according to the encoded sensory information. In other words, the closedloop control policy origins from the brain not the neural interface system. However, there are BMI applications in which it could be useful to have a closed-loop mechanism, such as a PID controller, integrated into the system. As illustrated in Fig. 4(b), [17] proposed an application aiming to improve the sensory encoding capacity of the BMI. The method involves an encoder mapping sensing data acquired from a prosthetic to desired patterns related to the somatosensory cortex activity. The errors between these desired patterns and those recorded in somatosensory cortex are used in a PID controller to update stimulation of sub-cortical somatosensory areas in the thalamus or brainstem. This approach could elicit more continuous, natural sensory percepts compared to those evoked by the limited set of pre-programmed typical stimulation patterns [18].

Another application of the proposed neural interface system is to control a paralyzed arm, using muscle stimulation as shown in Fig. 4(c), rather than a prosthetic arm. Brain-controlled muscle stimulation has been shown to be a viable method of reanimating paralyzed arms in monkeys and humans [19]–[21]. In these studies the muscle stimulation, and thus the arm movement trajectory, was entirely driven by motor cortex activity. However, prior work has shown that recording from pre-motor cortical areas to decode motor goals, not entire intended trajectories, can improve performance and lower cognitive demand [22], [23]. Thus a second potential BMI application for a closedloop controller could be to update muscle stimulation based on the error between a decoded goal and the recorded state of the re-animated arm [24], as illustrated in Fig. 4(d).

Other examples for closed-loop bidirection BMI applications include deep brain stimulation (DBS) for Parkinson Disease control, with parameters modulated from the internal brain state.

Fig. 2. Architecture of the proposed bidirectional, closed-loop brain machine interface system. The system includes a custom system-on-chip (SoC) and supporting electronics. The SoC mainly consists of 1) 16-channel neural front-end with neural feature extraction units and closed-loop controller, 2) 16-channel programmable neural stimulators, 3) data converters, 4) power management, analog references, and peripheral circuits.

Fig. 3. Brain oscillation classes are shown together with the traditional frequency tuning points in linear steps, and the proposed tuning points in natural logarithmic domain. A total of 32 steps in a frequency range from 1 Hz to 200 Hz are shown for illustration.

Closed-loop stimulation of the sleep slow oscillation has been proposed to enhance memory [25]. In addition, sense-stimulate devices with closed-loop controllers have also been proposed for neuromodulatory applications [26] and for closed-loop electrophysiological studies [27]. PID controllers have been used to characterize input-output neuronal relationships [28].

PID control is the most commonly used control loop feedback mechanism. PID controller relies only on the process variable and the target value, not requiring the knowledge of a system model or the underlying process. Even though it has wide potential neuroscience applications, it has not been widely integrated in BMI hardwares. In this work, we implemented a programmable PID controller in each neural recording channel to enable a variety of closed-loop control experiments and applications.

#### C. bidirectional Neural Interface System Integration

The complete integrated BMI system is a battery powered portable device consists of the custom designed SoC and sup-

Fig. 4. Block diagram of closed-loop BMI applications. Functions of the proposed neural interface system are shown in red. (a) Standard bidirectional BMI for a prosthetic arm. (b) Same as (a) but with improved sensory encoding method using PID controller. (c) bidirectional BMI to re-animate paralyzed arm by decoding desired arm trajectory. (d) Same as (c) but decoding motor goal and implementing arm trajectory with PID controller.

porting electronics. The devices have been used in various neuroscience experiments including behavior experiments. The BMI device is designed to be housed in a secure chamber fixed on the animals' skull to conduct long term study while the animals are freely behaving like social interaction and locomotion.

The system-on-chip (SoC) mainly consists of 1) a 16-channel neural front-end with neural feature extraction and closed-loop controller, 2) a 16-channel programmable stimulators, 3) two ADCs with different specifications, 4) power management units, analog references, and other peripheral circuits. The 16-channel

Fig. 5. Circuit schematic of the proposed neural amplifier. (a) Capacitor coupled neural amplifier with pole shifting for stimulation artifact suppression. (b) Implementation of the feedback MOS pseudo resistor. (c) Low-noise OTA with source degeneration current mirrors.

IO pads are shared between recording and stimulation electrodes. Multiple chips can be used in parallel to boost the number of channels. The supporting electronics consist of 1) a general purpose MCU with integrated flash memory and wireless module (Bluetooth), 2) battery management circuit (including inductive charging), 3) expand flash memory (optional), and 4) 3-axis accelerometer (optional). A user interface has been designed in Matlab to support configuration and data readout. It is a modified version of our previous design [8].

### **III. CIRCUITS IMPLEMENTATION**

## A. Neural Recording Front-End

The overall signal flow of the proposed neural recording frontend has been illustrated in Fig. 2. The wide-band neural signals are acquired by the low-noise neural amplifiers, and then filtered into local field potential (LFP) and action potential (AP) bands for further neural feature extraction. The neural amplifier is designed with sufficient gain to release the noise requirement of the following filter stages.

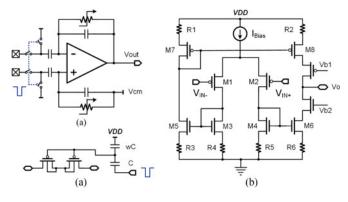

The circuit schematic of the implemented neural amplifier is show in Fig. 5(a). Capacitor coupled input stage is used to maximize the input range, and to remove the large DC offset from the electrode-tissue interface [29]. The mid-band gain is set to be 40 dB by the ratio of the input and the feedback capacitors [30]. MOS pseudo resistors are used to enable very low cutoff frequency operation, as shown in Fig. 5(b). The gates of the MOS pseudo resistors are set to high in normal operation. A synchronization signal from the stimulator can temporarily lower the resistance, and shift the high-pass corner to a higher frequency, thus preventing the recording amplifier from saturation in the stimulation artifacts [31]. The input stage can also be disconnected from the pads to prevent the high stimulation voltage from breaking the input gates. The switches are implemented by thick oxide transistors. The synchronization signal shares between blanking and pole shifting switches, but they can be independently enabled.

The circuit schematic of the core operational transconductance amplifier (OTA) is as shown in Fig. 5. A two-stage current mirror OTA is chosen with a dominate pole at the second stage [32]. The input differential pair is biased at the sub-threshold region to maximize the noise power efficiency [30]. Source degeneration current mirrors are used in the OTA to lower the noise contribution from the current mirror. By properly choosing the values of the resistors, the noise contributions from the source-degenerated current sources can be much smaller compared to the MOS transistors alone [33].

The output of the wide-band neural amplifier is split into two paths, the LFP and AP. A 1st order GmC lowpass filter [33] is implemented to attenuate the high frequency spikes. The lowpass frequency can be tuned by programming the biasing current of the Gm block. A 2nd order highpass filter [34] is used to remove the large low frequency oscillation for further action potential discrimination.

#### B. Neural Feature Extraction and PID Controller

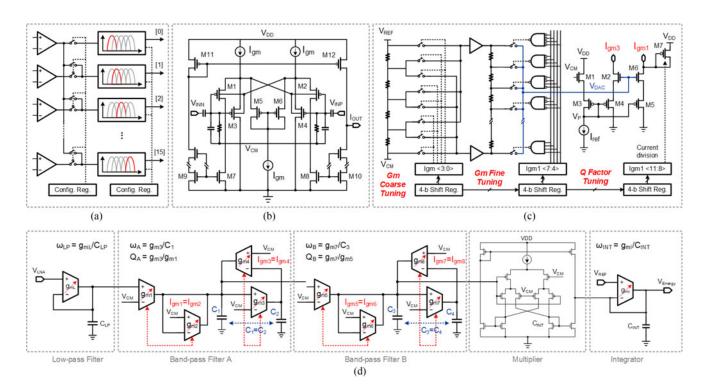

Each neural recording channel integrats a neural energy extraction module, an action potential detection module, and a PID controller. The 16 neural feature extraction units can be programmed and work independently. The filters in each channel can also be combined together as a filter bank to perform spectrum analysis for one channel, as illustrated in Fig. 6(a).

The processing flow of the extraction of LFP energy is as follows. A lowpass filter with a frequency corner of 300 Hz is first used to remove the high frequency spikes. Then, A 4thorder stagger-tuned biquad filter is used to bandpass the neural signal in a programmable frequency band [35]. The filtered signal is then squared in a Gilbert multiplier to calculate the energy, and energy integral is produced by a leaky integrator with a programmable time constant [36].

Given the low frequency nature of the neural signal, filters with very large time constant have to be implemented on chip. Op-amp based filter features high linearity and good signal-tonoise ratio (SNR), but suffering from high power consumption, large passive components (non-linear if MOS resistors are used), and difficulty in tuning. Switched capacitor filter is widely used due to its high accuracy and tunability [9], but the limitations in the tunable range, capacitor size, and additional clock generation circuitry are the bottlenecks. GmC filters can potentially realize large time constant in ultra low power and compact circuitry, thus have been widely used in biomedical applications [35]. In this work, a Gm block with a tunable transconductance range of two decades, with extended linear range has been implemented. The circuit schematic of the implemented Gm block is as shown in Fig. 6(b). The input transistors are biased in the sub-threshold region [37]. Thick oxide devices are used for low transconductance and low leakage. The transconductance features a linear relation with the biasing current in the sub-threshold region [38], as expressed

$$g_m = \frac{I_{DS}}{\zeta U_T} \tag{1}$$

where  $\zeta$  is a parameter that depends on process, and  $U_T = kT/q$ . The transconductance of the Gm block can be directly tuned by the biasing current. In order to realize a larger linear range, negative feedback is used in the input differential pair. A

Fig. 6. (a) The diagram of the 16-channel neural feature extraction module. The channel-level feature extraction unit works either independently, or combined together as a filter bank. (b) The circuit schematic of the transconductor  $(g_m)$  block. Negative feedback, bulk degeneration, and capacitor attenuation have been used to extend the linear input range. The biasing current is used to tune the transconductance. (c) The programmable tuning stage of the biquad filter. 64 steps natural exponential biasing current can be generated. (d) The processing circuits of the LFP signal. The processing flow includes a lowpass filter, a 4th-order stagger-tuned bandpass filter, a Gilbert multiplier, and a leaky integrator.

feedback path has an identical current amplitude to maximize the common mode voltage range, and reduce the distortion term by a factor of 4 [39]. Bulk degeneration [40] is also used to enhance the linear input range. Current division is used at the input differential pair to reduce the transconductance. Capacitor attenuation [41] is used to further reduce the input signal swing and lower the overall transconductance.

A programmable biasing current generation module is designed, as shown in Fig. 6(c). A two-step 6-bit resistor ladder DAC is used to generate 64 steps linear tuning voltage between  $V_{cm}$  and  $V_{ref}$ . An exponential current reference module is used to generate biasing current for the gm block. Transistors M1 to M6 are biased in the sub-threshold region. Thick oxide devices are used to minimize the leakage currents. When  $V_{DS}$  is higher the  $4U_T$ , the sub-threshold current can be expressed as

$$I_D = I_o \exp \frac{V_{GS}}{\zeta U_T}.$$

(2)

The currents can be expressed as

$$I_{ref} = I_{on} \exp \frac{V_{GS1}}{\zeta U_T} = I_{op} \exp \frac{V_{GS3}}{\zeta U_T}$$

(3)

$$I_{gm} = I_{on} \exp \frac{V_{GS2}}{\zeta U_T} = I_{op} \exp \frac{V_{GS4}}{\zeta U_T}.$$

(4)

Thus

$$V_{GS1} - V_{GS3} = V_{GS2} - V_{GS4} = \zeta U_T \ln\left(\frac{I_{op}}{I_{on}}\right).$$

(5)

Also

$$V_{CM} = V_{GS1} + V_{GS3} + V_P$$

(6)

$$V_{DAC} = V_{GS2} + V_{GS4} + V_P. (7)$$

Thus

I

$$V_{GS1} = \frac{1}{2} \left( V_{CM} - V_P + \zeta U_T \ln \left( \frac{I_{op}}{I_{on}} \right) \right)$$

(8)

$$V_{GS2} = \frac{1}{2} \left( V_{DAC} - V_P + \zeta U_T \ln \left( \frac{I_{op}}{I_{on}} \right) \right).$$

(9)

The generated biasing current can be expressed as

I

$$I_{gm} = I_{ref} \exp \frac{V_{DAC} - V_{CM}}{2\zeta U_T}.$$

(10)

Thus, the uniform voltage tuning results in an exponentially increasing biasing current, and so is the transconductance.

$$g_m \propto I_D \propto e^{(V_{DAC} - V_{CM})} \propto e^{code} \tag{11}$$

where *code* is the digital input of the DAC.  $I_{ref}$  is generated by on-chip bandgap reference, and is independent from temperature and supply voltage. Large gate area transistors are used in the current generation module and have been carefully layouted to minimize the mismatch. The process variation can be further calibrated by tuning the reference voltage.

The complete LFP energy extraction processing circuits are shown in Fig. 6(d). A staggered tuned 4th-order band-pass filter is implemented [42]. The center frequency and quality factor of each biquad are independently tuneable. Only two grounded capacitors are used in each biquad, realizing a high compactness. The transfer function of the given bandpass filter is given by

$$H(s) = \frac{s\frac{g_{m1}}{C_1}}{s^2 + s\frac{g_{m2}}{C_1} + \frac{g_{m3}g_{m4}}{C_1C_2}}.$$

(12)

In this work, the transconductance of the Gm blocks are set to be  $g_{m1} = g_{m2}$ , and  $g_{m3} = g_{m4}$ . The capacitors are set to be  $C_1 = C_2$ . Thus,

$$\omega_C = \sqrt{\frac{g_{m1}g_{m2}}{C_1 C_2}} = \frac{g_{m1}}{C_1}.$$

(13)

From Eq. (11) and Eq. (13)

$$\omega_C \propto g_m \propto e^{code} \tag{14}$$

Thus the center frequency of the biquad can be exponentially tuned by the digital code. And

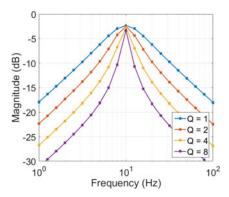

$$Q = \sqrt{\frac{C_1 g_{m3} g_{m4}}{C_2 g_{m2}^2}} = \frac{g_{m3}}{g_{m1}}.$$

(15)

M7 in Fig. 6(c) is a diode-connected transistors with same length as the current mirrors used in the gm block. The width of M7 can be programmed to divide the current reference, so the ratio of  $I_{gm1}$  and  $I_{gm3}$  can be programmed to tune the quality factor. Compared with prior publications, this implementation features small silicon area, high digital programmability and ultra low power consumption.

A Gilbert multiplier biased in the sub-threshold region is used to square the band-passed signal. The integral of the output current of the multiplier is computed in the leaky GmC integrator [35]. The moving window length can be tuned by programming the time constant of the integrator.

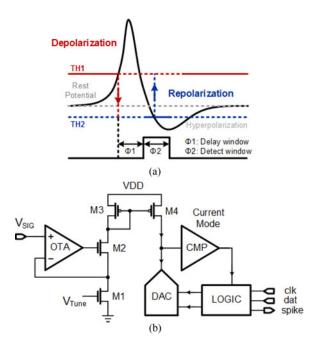

A current-mode AP discrimination unit has been integrated in each channel. Two amplitude thresholds and time windows are used to discriminate the APs from different neurons [8], as illustrated in Fig. 7(a). After the 2nd order highpass filter, the signal is converted from voltage to current in a tunable transconductance. The transconductance is set by the biasing voltage  $V_{Tune}$ , while M1 is in the deep triode region.  $V_{Tune}$  can also compensate the threshold variation of M1. The signal current is compared with the depolarization threshold current TH1, which is generated by an 8-bit current DAC. The depolarization threshold is usually set by  $5\sigma$  value of the signal, and is programed by the two wire interface (TWI), shown as dat and clock in the Fig. 7(b). The comparator is disable for a period of  $\Phi$  1, while the reference current switches to the repolarization threshold TH2. Within a period of  $\Phi 2$ , if the signal crosses the TH2, an action potential is detected.

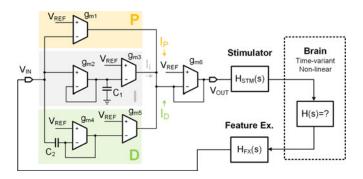

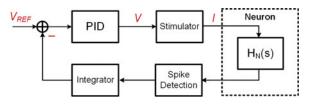

A programmable PID controller has been integrated to realize the close-loop control. The circuit schematic is shown in Fig. 8. In the proposed PID control system, the error signal is the difference between the extracted neural feature and its desired value. The output of the PID controller is a weighted sum of the error signal, the derivative of the error signal, and the integral of the error signal. The actuator in the system is the

Fig. 7. (a) Illustration of the action potential detection principle. (b) Circuit schematic of the programmable current mode spike detection unit with integrated programmable amplitude-window discriminator.

Fig. 8. PID block diagram and the circuit schematic of PID controller.

stimulator. The output of the PID controller can be used to modulate the stimulating current amplitude, stimulating frequency, or stimulation pulse width. The sensor in the system is the neural feature extraction unit. Either neural frequency energy or the action potential fire rate can be used as input of the PID controller. In this work, the fire rate is calculated and converted to a voltage signal in the embedded MCU. However, this part can be easily integrated on-chip in the future by using a lossy integrator.

The parameters for each of the P, I, and D components are independently programmable. The transfer function of the PID controller is given by

$$\frac{V_{out}(s)}{V_{err}(s)} = \frac{g_{m1}}{g_{m6}} + \frac{g_{m3}}{g_{m6}(1 + \frac{sC_1}{q_{m2}})} + \frac{g_{m5}}{g_{m6}(1 + \frac{g_{m4}}{sC_2})} \quad (16)$$

where  $V_{err} = V_{ref} - V_{in}$ . The gain of the P, I and D components are  $K_P = g_{m1}/g_{m6}$ ,  $K_I = g_{m3}/g_{m6}$ , and  $K_D = g_{m5}/g_{m6}$ . The time constant for the integrator is  $\tau_I = C_1/g_{m2}$ , and the

Fig. 9. (a) Block diagram of the current mode ADC. (b) The current mode comparator.

time constant for the differentiator is  $\tau_D = C_2/g_{m4}$ . The time constant is designed to be programmable in two decades, from 1 ms to 100 ms, or from 10 ms to 1 s. The programming and parameter choosing of the PID controller follows the established PID control theory [43], [44]. For complex neural system where accurate model can hardly be achieved, plant exploration based method can be used. The initial estimation of the optimal operating points can be learnt from the Zeigler-Nichols tuning method [45]. And the final controller parameters can be determined by using an iterative procedure, based on the least root mean square error. Consider the requirement of a BMI system, sufficient gain and phase margin must be guaranteed.

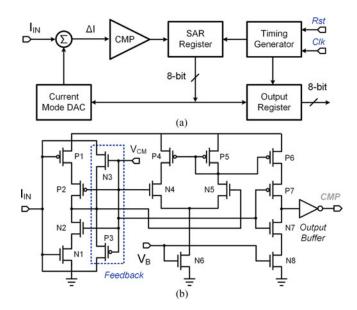

# C. Analog to Digital Converters

Two ADCs have been integrated on-chip to optimize the power efficiency of the data conversion. An 8-bit low-power current mode ADC has been implemented for the conversion of action potential signals, while a 10-bit voltage mode SAR ADC has been implemented for neural features and LFP digitizations. Action potential recording features lower linearity requirement compared with wideband neural signals or neural features. Current signals are more robust to noise in routing lines while the current operation allows lower supply voltage. A successive approximation register (SAR) architecture is chosen for this current-mode ADC. An 8-bit binary weighted current steering DAC with current calibration [46] is implemented to achieve good linearity. The designed current mode ADC works with a supply voltage of 0.9 V.

The block diagram of the current mode ADC is shown in Fig. 9(a). The ADC starts continuous sampling when the reset line is released. The circuit schematic of the current mode comparator is shown in Fig. 9(b). The input stage of the current comparator is a combination of capacitive input and resistive feedback [46], [47], as a trade-off between power, speed and sensitivity.

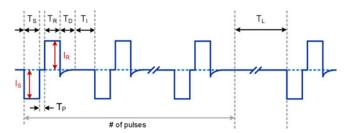

Fig. 10. Illustration of a typical biphasic stimulation waveform with the programmable parameters. (I<sub>S</sub>: stimulation current, I<sub>R</sub>: reversal current, T<sub>S</sub>: stimulation phase time, T<sub>R</sub>: reversal phase time, T<sub>D</sub>: discharging phase time, T<sub>P</sub>: phase interval, T<sub>I</sub>: pulse interval, T<sub>L</sub>: pulse group interval)

A 10-bit voltage mode SAR ADC with an energy efficient monotonic capacitor switching procedure [48] has been integrated. Single-ended operation is used in the feature extraction units to reduce the area, so a single-to-differential converter has been implemented to drive the differential sampling capacitors array. Spilt capacitor array is used to reduce the total capacitance, lowering the power consumption and the die area cost. The capacitors are realized as a standard metal-insulator-metal (MIM) structure, as provided in the design kit. Power-gating has been used to shut down the ADC modules to minimize the power leakage.

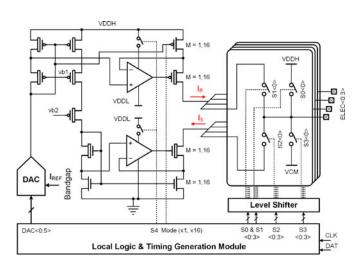

#### D. Multi-Mode Stimulator

16-channel current mode neural stimulators have been integrated in this work, which support functional electrical stimulation or deep brain stimulation. The stimulator is designed to be fully programmable to meet all the electrophysiology requirements. There are 4 independent driving modules, each includes a 1:4 demux to support 4 channels and provide near simultaneous stimulation. The stimulator can perform monopolar or bipolar, monophase or biphasic, symmetrical or asymmetrical charge balanced stimulation. A typical biphasic stimulation waveform is illustrated in Fig. 10. The logic and timing generation module of the stimulator can be programmed individually. The stimulator command and parameter registers are listed in Table I. In addition to the regular operating modes, the stimulator can be configure to output continuous current in order to test the DAC and output stage.

The circuit schematic of the multi-mode stimulator is shown in Fig. 11. The stimulator consists of three modules: 1) current mode DAC, high output impedance current sinks and sources, 2) high voltage switch matrix with level shifter, and 3) local logic and timing generation module. A 6-bit current mode DAC is used to generate the stimulation current reference. The output stage is designed with regulating op-amp, resulting an output impedance higher than 200 M $\Omega$ . The op-amp is disabled when the stimulator is in the idle mode to save power consumption. Thick oxide devices were used to tolerant high output impedance. For larger surface electrodes, a high current mode can be enabled to boost the output current to 4 mA. In the monophase mode, reversal phase is disabled. In the biphasic, monopolar mode, only one electrode is selected. In the biphasic, bipolar mode, the stimulation and counter electrodes can be selected arbitrarily from all the 16 channels.

TABLE I

STIMULATOR COMMAND AND PARAMETER REGISTERS

| CMD Addr.     | Description                  | Value                     |  |

|---------------|------------------------------|---------------------------|--|

| Word 00 [0:1] | Header                       | $0 \times 57$             |  |

| Word 00 [2:3] | Module position              | $0 \times 00-0 \times 11$ |  |

| Word 00 [4:5] | Stim. mode                   | 00-biphasic, monopolar    |  |

|               |                              | 01–biphasic, bipolar      |  |

|               |                              | 10-monophase              |  |

| Word 00 [6]   | Stim. power                  | 0-low (FS: 256 uA)        |  |

|               |                              | 1-high (FS: 4096 uA)      |  |

| Word 00 [7]   | Stim. on/off                 | 0-stimulator OFF          |  |

|               |                              | 1-stimulator ON           |  |

| Word 01 [0:1] | Stim. position               | $0 \times 00-0 \times 11$ |  |

| Word 01 [2:7] | Stim. magnitude $(I_S)$      | $0 \times 01-0 \times 3F$ |  |

| Word 02 [0:1] | Counter position             | $0 \times 00-0 \times 11$ |  |

| Word 02 [2:7] | Counter magnitude $(I_R)$    | $0 \times 01-0 \times 3F$ |  |

| Word 03 [0:7] | Stim. phase $(T_S)$          | 1 us–256 us               |  |

| Word 04 [0:7] | Reserval phase $(T_R)$       | 1 us–256 us               |  |

| Word 05 [0:3] | Phase interval $(T_P)$       | 1 us–16 us                |  |

| Word 05 [4:7] | Discharge phase $(T_D)$      | 16 us-1024 us             |  |

| Word 06 [0:3] | # of pulses                  | 1–16                      |  |

| Word 06 [4:7] | Pulse interval $(T_I)$       | 640 us-10 ms              |  |

| Word 07 [0:7] | Pulse group interval $(T_L)$ | 8 ms–2 s                  |  |

Fig. 11. The proposed multi-mode stimulator module. Each module demux to 4 channels. It consists of 1) a current mode DAC with high output impedance current sinks and sources, 2) a high voltage switch matrix, and 3) a local logic and timing generation module.

# E. System Integration

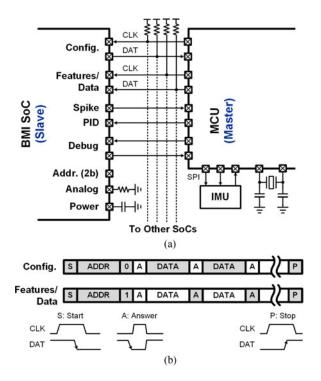

A battery powered PCB-based system has been integrated using the designed chip and off-the-shelf electronics. A 32-bit ARM Cortex M0 based wireless transceiver (Nordic Semiconductor nRF51822) is used as the central processor. The MCU integrated an intergrated 2.4 GHz wireless module and a Bluetooth 4.0 software stack, which enables an user-friendly interface to computers or mobile devices. The configuration of the SoC is stored in the flash memeroy of the MCU, and it can be programmed wirelessly by the Bluetooth link. Once the device is powered up, the MCU first reads the default configuration in the flash memory, and then configure the chip accordingly. The interface between the MCU and the chip is shown in Fig. 12. The configuration and data readout are through a simplified two-wire interface (TWI) module. The TWI module supports

Fig. 12. (a) Communication interface between the proposed chip and general purpose MCU (not all pads are shown). (b) Communication data format. The MCU (master) writes the gray sectors.

standard  $I^2C$  protocol [49] which is compatible with most general purpose MCU. The MCU works as the master and the chips work as slaves. The MCU first sends the address and the chip with a same address response. Only two pads are used to set up address, thus, the current implementation can support up to 4 chips (64 channels in total). This can be easily expend in the future to support 127 chips (full 8-b address). The *START*, *STOP* and *ANSWER* commands are also shown in Fig. 12.

T3168 and XKT510 are used as the wireless power transmitter and receiver ICs. The wireless charging uses a switching frequency of 125 kHz. MC73831 is used for battery management. A 3-axis accelerometer ADXL345 has also been integrated in the system, with 3-wire SPI interface to the MCU.

A 4.65 g 150 mAh lithium polymer battery is used to power up the system. On-chip DC-DC converters and regulators are intergrated to optimize the power efficiency. The analog frontend and voltage-mode ADC are designed to operate at 1.8 V. The current-mode ADC and the digital circuits operate at 0.9 V. The stimulator back-end is designed under 5 V power supply. The analog references are generated on-chip, while the digital clocks are provided by the external low-power MCU.

# **IV. EXPERIMENTAL RESULTS**

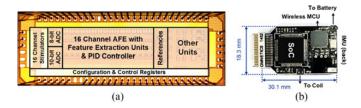

The design has been fabricated in 180 nm CMOS process, occupying a silicon area of 3.9 mm  $\times$  0.95 mm. The die photo is shown in Fig. 13(a), with major building blocks highlighted. One device we have made using the fabricated chip is shown in Fig. 13(b). The system includes two of the proposed chips to support 32 recording and stimulating channels. The dimension of the device is 30.1 mm  $\times$  18.3 mm, and the weight is 18 g

Fig. 13. (a) Micrography of the fabricated chip with major blocks highlighted. (b) A prototype of wireless portable Brain machine interface systems using the designed SoC.

Fig. 14. The measured frequency response of one stage biquad filter tuning in the proposed natural logarithmic steps.

Fig. 15. The measured the quality factor tuning of the biquad filter.

including the battery and inductive charging coil. Bench tests were performed to verify the functions and evaluate the performance of the proposed design. *In-vivo* experimental results performed on Rhesus macaque and Long-Evans rat are shown.

The measured input referred noise of the analog front-end is 4.57  $\mu$ Vrms in a 0.3 Hz–7 kHz bandwidth, with a noise efficiency factor (NEF) [30] of 4.77. The measured CMRR is 81 dB and the PSRR is 71 dB. The cut-off frequency to separate the LFP and action potential signals is tunable, and the default value is set to be 300 Hz.

The frequency response of the natural logarithmic tuning neural energy extraction module were measured. The reference voltages were calibrated to set the center frequency of the unit programming step. All the tuning process is done by programming the digital registers. Fig. 14 shows the measurements of every four steps out of the 64 possible steps, with a frequency ranging from 1 Hz to 200 Hz. Notice that the x-axis is plotted in natural logarithmic domain. Fig. 15 shows the measurements of the

TABLE II Key Specifications Summary

| Analog Front-end          | LNA Gain               | 40 dB                 |  |  |

|---------------------------|------------------------|-----------------------|--|--|

|                           | LNA Bandwidth          | 0.3 Hz-7 kHz          |  |  |

|                           | LNA Integral Noise     | 4.57 uV               |  |  |

|                           | LNA Power              | 9 uW                  |  |  |

|                           | LNA NEF/PEF            | 4.77/41.1             |  |  |

|                           | THD (10 mVpp Input)    | -61 dB                |  |  |

|                           | CMRR/PSRR              | 81 dB/71 dB           |  |  |

|                           | PGA + Filters Power/ch | 8 uW                  |  |  |

| Energy Extraction         | Center frequency       | 1 Hz-200 Hz           |  |  |

|                           | Tuning steps           | 64 natural log        |  |  |

|                           | Quality Factor         | 1-8                   |  |  |

|                           | Window length          | 10-500 ms             |  |  |

|                           | Ex + PID Power/ch      | 7 uW                  |  |  |

| Spike Discriminator       | Algorithm              | Window discrimination |  |  |

|                           | Amplitude Thresholds   | 6-bit                 |  |  |

|                           | Latency                | 10 us                 |  |  |

|                           | Avg. Power/ch          | 4 uW                  |  |  |

| ADC (Volt Mode/Curr Mode) | Sampling Rate          | 1 MSps/250 KSps       |  |  |

|                           | ENOB                   | 9.1/7.9               |  |  |

|                           | FoM(fJ/step)           | 34.2/10.7             |  |  |

|                           | Power (at 200 KSps)    | 7 uW/0.5 uW           |  |  |

| Stimulator                | Stim. Current          | 4 mA/200 uA           |  |  |

|                           | Amplitude Res.         | 6-bit                 |  |  |

|                           | Pulse width            | 1 us-255 us           |  |  |

| Total Power               | Chip Power/ch          | 56 uW/ch              |  |  |

|                           | MCII Winalass (aug)    | 8 mW                  |  |  |

|                           | MCU + Wireless (avg)   | 8 III W               |  |  |

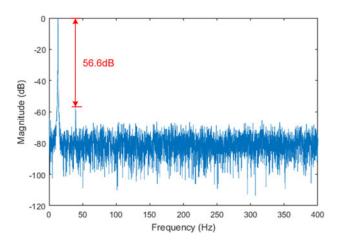

Fig. 16. The measured output spectrum of the biquad filter with an input tone of 26.6 Hz at 500 mVpp.

tuning of the quality factor. The other measured specifications are listed in Table II.

The measured output spectrum of one biquad stage filter with center frequency at 26.6 Hz is shown in Fig. 16. The input signal is 500 mVpp. A SFDR of 56.6 dB is achieved. The integral noise of one stage biquad filter is less than 0.12 mV with all quality factors.

The action potential discrimination module is tested by a dataset of extracellular recording of a crayfish abdominal ganglion, which contains four spontaneously active motor neurons. The SNR for the four neurons are 3.1 dB, 2.7 dB, 4.5 dB, 8.1 dB, respectively. The detection accuracy is defined as

$$Accuracy = \frac{T_P}{T_P + F_N + F_P} \tag{17}$$

Fig. 17. Diagram of the testing configuration. The major blocks used are PID controller, stimulator, action potential detector, a lossy integrator for finding spike rate and a neuron model. The on-chip stimulator is configured in the testing mode to output continuous current. The lossy integrator is implemented in the MCU. The neuron is modeled by another MCU.

where the  $T_P$  is the number of correct detections,  $F_P$  is the number of wrong detections, and  $F_N$  is the number of missed action potentials. The resulting detection accuracies of the four neurons using the designed action potential discriminator are 97.5%, 96.9%, 98.8%, and 100%, respectively.

A closed-loop neuronal response clamp experiment [27], [28] was set up to test the proposed chip. The nervous system of man's and/or animals' response to the rapidly changing sensory information in highly variable, complex dynamics. The dynamic response is reflected from single neuron to neuronal network. Thus, it is important to study the behavior in a closed-loop approach in the appropriate context of realistic input-output dependence. Voltage, current-clamps are well-known techniques [27] in closed-loop electrophysiology. Recently, dynamic neuronal response clamp technique was proposed to study the threshold dynamics of neuron using extracellular stimulation and recording. A modified version of this technique is employed to test the proposed closed-loop system including the PID controller, stimulator, and action potential detector.

The diagram of the designed testing system is illustrated in Fig. 17. The integrate and fire model [50] for the single neuron employed in this experiment can be expressed as

$$\tau_m \frac{dV}{dt} = V_m - V(t) + R_m I_s(t) \tag{18}$$

where  $\tau_m \approx 10$  ms is the membrane time constant,  $V_m$  is the resting membrane potential, V(t) is the actual membrane potential as a function of time,  $R_m \approx 10^7 \Omega$  and  $I_s(t)$  is the stimulation current. Once the membrane potential reaches a certain threshold  $V_{TH}$ , an action potential occurs and reset the potential back to its resting membrane potential. In this testing, an extra MCU (Atmel XMEGA 128A4U) with ADC and DAC was used to model the neuron. The MCU is running at a sampling rate of 100 KHz, corresponding to a time resolution  $dt = 10 \ \mu s$ . The continuous time differential equation is simplied by a discrete difference equation for implementing in MCU. The MCU's ADC measures the  $R_m I_s[t]$ , and the DAC generates V[t] based on the following equations:

$$V[t] = \begin{cases} \frac{V_m + R_m I_s[t-1] + \tau_m V[t-1]}{1 + \tau_m} & V[t-1] < V_{TH} \\ V_m & V[t-1] > V_{TH}. \end{cases}$$

(19)

The stimulator is reconfigured in a testing mode to output a continuous stimulation current to meet the requirement of

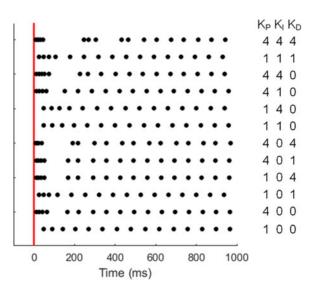

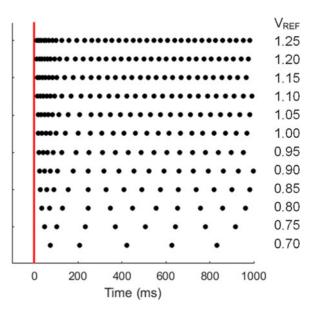

Fig. 18. The measured transient response of the dynamic neuronal clamp with different PID parameters. Relative values of P, I and D components are shown on the right.

intracellular stimulation. The stimulation current amplitude is modulated by the output voltage of the PID controller. The neural model response to the stimulation current, output the membrane potential. The action potential detector module evaluate the membrane potential voltage with a pre-defined threshold voltage. The output of the detector is a PWM wave, which is sent to the integrator and converted to a voltage promotional to the spike rate. In this work, the spike rate is converted to voltage in the embedded MCU, however, this part can be further integrated on-chip by using lossy integrator. The difference between the integrator's output voltage and the reference voltage is sent to the PID controller.

Fig. 18 shows 12 testing trails with different proportionalintegral-derivative parameters. The dots indicate the action potential's time stamps. A same reference was set at time 0, the neuron responses to the stimulation current until it settled at a constant fire rate. Fig. 19 shows 12 testing trails with different references. The neuron settled at a relative constant fire rate proportional to the reference, in a manner based on the choosing of the P, I, and D terms. Testing results show that by programming the parameters, one can control the behavior of the neuron without the knowledge of the exact model [27].

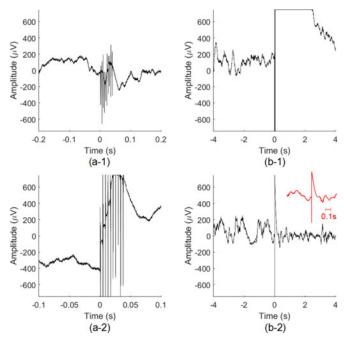

One *in-vivo* testing of the device was performed on a female Long-Evans rat, with a bipolar electrode pair implanted in the sensory cortex, and a monopolar electrode implanted in the motor cortex. LFPs were recorded using the designed device in both areas, as shown in Fig. 20(a). Stimulation was performed by the device in the sensory cortex, and the compliance voltage of the stimulating electrode was measured by instrumentation. Fig. 20(b) shows the measured compliance voltage of the stimulation pulse trains and a single pulse. A bidirectional stimulation and recording experiment was conducted by stimulating the rat's sensory cortex and recorded in the motor cortex. Fig. 21 shows the recording while different current amplitudes are used for stimulation. When the required stimulation current is too large (2 mA in this experiment, depending on the surface area and

Fig. 19. The measured transient response of the dynamic neuronal clamp with different references.

Fig. 20. *In-vivo* recording and stimulation in a Long-Evans rat using the proposed system. (a-1) Recording in the sensory cortex, and (a-2) the motor cortex. (b-1) Measured compliance voltage of stimulation pulse train in the sensory cortex, and (b-2) measured compliance voltage of a single pulse. Data in (b) is measured by instrumentation.

material of the electrode), the recording electrode would saturate. Discharge and shift the high pass frequency corner can help recover faster, so less information will lose due to the stimulation artifacts.

Another *in-vivo* testing of the device was performed on a male rhesus macaque (Macaca mulatta) with electrodes implanted chronically in the left hippocampus. In this experiment,

Fig. 21. *In-vivo* bidirectional recording and stimulation in a Long-Evans rat using the proposed system. (a-1) Recording in the motor cortex with stimulation in the sensory cortex with biphasic current of 20 uA and (a-2) 200 uA. (b-1) Shows recording electrode's saturation with a stimulation current of 2 mA, (b-2) shows the same stimulus current by with stimulation artifact reduction by discharging stimulation electrodes and shifting highpass frequency corner after the simulation. The up-right figure shows a +/-0.5 s time window.

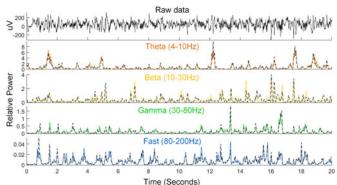

Fig. 22. *In-vivo* recording in a Rhesus macaque using the designed chip. The extracted energy in four brain oscillation bands (Theta, Beta, Gamma, and Fast) compared with the theoretical computations (dashed lines).

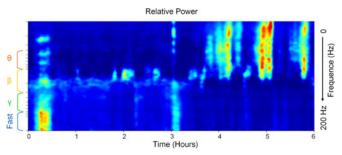

Fig. 23. The spectrum of a 6 hour continuous recording using the proposed system. The animal was from awake (high frequency oscillation more active) to sleep (low frequency oscillation more active).

TABLE III

COMPARISON WITH BIDIRECTIONAL NEURAL INTERFACE DESIGNS

| Reference           | Rhew [10]  | Cong [11]         | Limnuson [12] | Chen [51]         | Shulyzki [52] | Biederman [53] | This work       |

|---------------------|------------|-------------------|---------------|-------------------|---------------|----------------|-----------------|

| Publication         | 2014 JSSC  | 2014 ESSCIRC      | 2014 CICC     | 2014 JSSC         | 2015 TBioCAS  | 2015 JSSC      | -               |

| CMOS technology     | 180 nm     | 0.25 um and 90 nm | 0.35 um       | 180 nm            | 0.35 um       | 65 nm          | 180 nm          |

| ch # of rec./stim.  | 4/8        | 32/16             | 1/1           | 8/1               | 256/64        | 64/8           | 16/16           |

| AFE noise           | 6.3 uVrms  | 100 nV/rtHz       | 3.42 uVrms    | 5.23 uVrms        | 7.99 uVrms    | 7.5 uVrms      | 4.57 uVrms      |

| AFE NEF             | -          | -                 | 2.75          | 1.77              | 8.9           | 3.6            | 4.77            |

| Bandwidth (Hz)      | 0.64–6 k   | 0.5–1.7 k         | 0.1–12.3 k    | 0.1–10 k          | 10–5 k        | 10–8 k         | 0.3–7 k         |

| ADC ENOB            | 5.6        | 12                | 10            | 9.57              | -             | 8.2            | 9.1             |

| Feature extraction  | Custom DSP | Custom CPU        | Custom DSP    | Custom DSP        | -             | Custom DSP     | Parallel analog |

| Neural features     | Energy     | FFT               | _             | Spectrum, Entropy | _             | Spikes         | Energy, Spikes  |

| Feedback control    | PI         | -                 | _             |                   | _             | _              | PID             |

| Stim. mode          | Monopolar  | Monopolar         | Monopolar     | Bipolar           | Monopolar     | Bipolar        | Mono/bipolar    |

| Stim. artifact rej. | LP filter  | LP filter         | Subtraction   | _                 | Blanking      | _              | Pole-shifting   |

| Ouput current       | 4410 uA    | 12 mA             | 100 uA        | 30 uA             | 20–250 uA     | 900 uA         | 4 mA            |

the device was housed in a secure plastic chamber, which is fixed on the skull of the macaque. Continuous recording over 24 hours were conducted while the animal is freely behaving in the home cage. Fig. 22 shows a piece of 20 seconds LFP output, with extracted energy in four commonly used frequency bands (solid lines), including  $\theta$  band (4–10 Hz),  $\beta$  band (10–30 Hz),  $\gamma$ band (30–80 Hz), and Fast band (80–200 Hz), together with the theoretical computation (dashed lines). The power spectrum of 6 hours' recording present awake and sleep transition is shown in Fig. 23.

#### V. CONCLUSION

In this paper, a bidirectional, closed-loop brain machine interface system has been reported. The system includes a 16-channel custom chip, integrated low-noise neural amplifiers, neural feature extraction units, neural stimulators, ADCs, and PID controllers. A channel-level energy efficient neural feature extraction module has been proposed, including a natural logdomain tuning filter bank, and a current-mode action potential detection. The system is highly programmable and energy efficient. A prototype chip has been fabricated in 180 nm CMOS technology. General purpose wireless modules, memory media, inductive charging and power management units were also integrated in the system. Bench testing and *in-vivo* experimental results are shown in this paper. The system has been used in neuroscience research. A comparison with recent reported designs of bidirectional neural interface is listed in Table III. The proposed system provides a promising solution for bidirectional brain machine interface applications, especially for closed-loop experiments with freely behaving animals.

## ACKNOWLEDGMENT

The authors would like to thank the MOSIS Education Program for fabricating the chip.

#### REFERENCES

- J. P. Donoghue, "Bridging the brain to the world: A perspective on neural interface systems," *Neuron*, vol. 60, no. 3, pp. 511–521, 2008.

- [2] J. L. Collinger, B. Wodlinger, J. E. Downey, W. Wang, E. C. Tyler-Kabara, D. J. Weber, A. J. C. McMorland, M. Velliste, M. L. Boninger, and A. B. Schwartz, "High-performance neuroprosthetic control by an individual with tetraplegia," *Lancet*, vol. 381, no. 9866, pp. 557–564, 2013.

- [3] L. R. Hochberg, D. Bacher, B. Jarosiewicz, N. Y. Masse, J. D. Simeral, J. Vogel, S. Haddadin, J. Liu, S. S. Cash, P. van der Smagt, and J. P. Donoghue, "Reach and grasp by people with tetraplegia using a

neurally controlled robotic arm," *Nature*, vol. 485, no. 7398, pp. 372–375, 2012.

- [4] L. A. Johnson, J. D. Wander, D. Sarma, D. K. Su, E. E. Fetz, and J. G. Ojemann, "Direct electrical stimulation of the somatosensory cortex in humans using electrocorticography electrodes: A qualitative and quantitative report," *J. Neural Eng.*, vol. 10, no. 3, 2013.

- [5] D. J. Weber, R. Friesen, and L. E. Miller, "Interfacing the somatosensory system to restore touch and proprioception: Essential considerations.," J. Mot. Behav., vol. 44, no. 6, pp. 403-18, 2012.

- [6] V. Gilja, C. A. Chestek, I. Diester, J. M. Henderson, K. Deisseroth, and K. V. Shenoy, "Challenges and opportunities for next-generation intracortically based neural prostheses," *IEEE Trans. Biomed. Eng.*, vol. 58, no. 7, pp. 1891–1899, 2011.

- [7] S. J. Bensmaia and L. E. Miller, "Restoring sensorimotor function through intracortical interfaces: progress and looming challenges," *Nat. Rev. Neurosci.*, vol. 15, no. 5, pp. 313–325, 2014.

- [8] X. Liu, M. Zhang, B. Subei, A. G. Richardson, T. H. Lucas, and J. Van Der Spiegel, "The PennBMBI: Design of a general purpose wireless brain-machine-brain interface system," *IEEE Trans. Biomed. Circuits Syst.*, vol. 9, no. 2, pp. 248–258, 2015.

- [9] F. Zhang, A. Mishra, A. G. Richardson, and B. Otis, "A low-power ECoG/EEG processing IC with integrated multiband energy extractor," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 9, pp. 2069–2082, 2011.

- [10] H. Rhew, et al., "A fully self-contained logarithmic closed-loop deep brain stimulation SoC with wireless telemetry and wireless power management," *IEEE J. Solid-State Circuits*, vol. 49, pp. 2213–2227, Oct. 2014.

- [11] P. Cong, et al., "A 32-channel modular bidirectional neural interface system with embedded DSP for closed-loop operation," in Proc. Eur. Solid State Circuits Conf., 2014.

- [12] K. Limnuson, et al., "A bidirectional neural interface SoC with an integrated spike recorder, microstimulator, and low-power processor for real-time stimulus artifact rejection," in Proc. IEEE Custom Integrated Circuits Conf., 2014.

- [13] M. Spler, A. Walter, A. R. Murguialday, G. Naros, N. Birbaumer, A. Gharabaghi, W. Rosenstiel, and M. Bogdan, "Decoding of motor intentions from epidural ECoG recordings in severely paralyzed chronic stroke patients.," *J. Neural Eng.*, vol. 11, no. 6, 2014.

- [14] H. Scherberger, M. R. Jarvis, and R. A. Andersen, "Cortical local field potential encodes movement intentions in the posterior parietal cortex," *Neuron*, vol. 46, no. 2, pp. 347–354, 2005.

- [15] G. Buzsaki and A. Draguhn, "Neuronal oscillations in cortical networks," *Science*, vol. 304, pp. 1926–1930, 2004.

- [16] M. Penttonen and G. Buzsaki, "Natural logarithmic relationship between brain oscillators," *Thalamus Relat. Syst.*, vol. 2, no. 2, pp. 145–152, 2003.

- [17] J. Liu, H. K. Khalil, and K. G. Oweiss, "Neural feedback for instantaneous spatiotemporal modulation of afferent pathways in bidirectional brainmachine interfaces," *IEEE Trans. Neural. Syst. Rehabil. Eng.*, vol. 19, pp. 521–533, Oct. 2011.

- [18] J. Daly, J. Liu, M. Aghagolzadeh, and K. Oweiss, "Optimal space-time precoding of artificial sensory feedback through mutichannel microstimulation in bidirectional brain-machine interfaces," *J. Neural. Eng.*, vol. 9, p. 065004, Nov. 27 2012.

- [19] C. T. Moritz, S. I. Perlmutter, and E. E. Fetz, "Direct control of paralysed muscles by cortical neurons," *Nature*, vol. 456, pp. 639–642, Dec. 4 2008.

- [20] C. Ethier, E. R. Oby, M. J. Bauman, and L. E. Miller, "Restoration of grasp following paralysis through brain-controlled stimulation of muscles," *Nature*, vol. 485, pp. 368–71, May 17 2012.

- [21] C. E. Bouton, A. Shaikhouni, N. V. Annetta, M. A. Bockbrader, D. A. Friedenberg, D. M. Nielson, *et al.*, "Restoring cortical control of functional movement in a human with quadriplegia," *Nature*, vol. 533, pp. 247–250, May 12 2016.

- [22] S. Musallam, B. D. Corneil, B. Greger, H. Scherberger, and R. A. Andersen, "Cognitive control signals for neural prosthetics," *Science*, vol. 305, pp. 258–262, Jul. 9 2004.

- [23] G. Santhanam, S. I. Ryu, B. M. Yu, A. Afshar, and K. V. Shenoy, "A highperformance brain-computer interface," *Nature*, vol. 442, pp. 195–198, Jul. 13 2006.

- [24] K. Kurosawa, R. Futami, T. Watanabe, and N. Hoshimiya, "Joint angle control by FES using a feedback error learning controller," *IEEE Trans. Neural. Syst. Rehabil. Eng.*, vol. 13, pp. 359–371, Sep. 2005.

- [25] H.-V. V. Ngo, T. Martinetz, J. Born, and M. Mlle, "Auditory closed-loop stimulation of the sleep slow oscillation enhances memory.," *Neuron*, vol. 78, no. 3, pp. 545–553, May 2013.

- [26] S. Stanslaski, P. Afshar, P. Cong, J. Giftakis, P. Stypulkowski, D. Carlson, D. Linde, D. Ullestad, A.-T. Avestruz, and T. Denison, "Design and validation of a fully implantable, chronic, closed-loop neuromodulation device with concurrent sensing and stimulation," *IEEE Trans. Neural Syst. Rehabil. Eng.*, vol. 20, no. 4, pp. 410–21, Jul. 2012.

- [27] M. Arsiero, H.-R. Lscher, and M. Giugliano, "Real-time closed-loop electrophysiology: Towards new frontiers in in vitro investigations in the neurosciences," *Arch. Ital. Biol.*, vol. 145, no. 3–4, pp. 193–209, Nov. 2007.

- [28] A. Wallach, D. Eytan, A. Gal, C. Zrenner, and S. Marom, "Neuronal response clamp," *Front. Neuroeng.*, vol. 4, no. Apr., p. 3, Jan. 2011.

- [29] X. Liu, M. Zhang, H. Zhu, A. G. Richardson, T. H. Lucas, and J. Van der Spiegel, "Design of a low-noise, high power efficiency neural recording front-end with an integrated real-time compressed sensing unit," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 24–27, 2015.

- [30] R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 958–965, 2003.

- [31] E. A. Brown, J. D. Ross, R. A. Blum, Y. Nam, B. C. Wheeler, and S. P. DeWeerth, "Stimulus-artifact elimination in a multi-electrode system," *IEEE Trans. Biomed. Circuits Syst.*, vol. 2, no. 1, pp. 10–21, 2008.

- [32] X. Liu, M. Zhang, A. G. Richardson, T. H. Lucas, and J. Van Der Spiegel, "A 12-channel bidirectional neural interface chip with integrated channellevel feature extraction and PID controller for closed-loop operation," in *Proc. Biomed. Circuits Syst. Conf.*, 2015, pp. 8–11.

- [33] W. Wattanapanitch, M. Fee, and R. Sarpeshkar, "An energy-efficient micropower neural recording amplifier," *IEEE Trans. Biomed. Circuits Syst.*, vol. 1, no. 2, pp. 136–47, Jun. 2007.

- [34] R. Geiger, et al. "Active filter design using operational transconductance amplifiers: A tutorial," *IEEE Circuits Devices Mag.*, vol. 1, pp. 20–32. Mar. 1985.

- [35] R. Harrison, et al. "Local field potential measurement with low-power analog integrated circuit," in Proc. 26th Annu. Int. Conf. IEEE Engineering in Medicine and Biology Soc., 2004.

- [36] R. R. Harrison, "The design of integrated circuits to observe brain activity," *Proc. IEEE*, vol. 96, no. 7, pp. 1203–1216, Jul. 2008.

[37] P. M. Furth and H. A. Ommani, "Low-voltage highly-linear transconductor

- [37] P. M. Furth and H. A. Ommani, "Low-voltage highly-linear transconductor design in subthreshold CMOS," in *Proc. IEEE Int. Midwest Symp. Circuits Syst.*, vol. 1, pp. 156–159, 1997.

- [38] R. Sarpeshkar, Ultra Low Power Bioelectronics: Fundamentals, Biomedical Applications, and Bio-Inspired Systems, Cambridge, U.K.: Cambridge Univ. Press, 2010.

- [39] R. Torrance, T. Viswanathan, and J. Hanson, "CMOS voltage to current transducers," *IEEE Trans. Circuits Syst.*, vol. 32, no. 11, pp. 1097–1104, 1985.

- [40] J. Gak, M. R. Miguez, and A. Arnaud, "Nanopower OTAs with improved linearity and low input offset using bulk degeneration," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 3, pp. 689–698, 2014.

- [41] C. D. Salthouse and R. Sarpeshkar, "A practical micropower programmable bandpass filter for use in bionic ears," *IEEE J. Solid-State Circuits*, vol. 38, no. 1, pp. 63–70, Jan. 2003.

- [42] A. Kumar, "A wide dynamic range high-q high-frequency bandpass filter with an automatic quality factor tuning scheme," Georgia Inst. Technol., Atlanta, GA, USA, 2008.

- [43] K. H. Ang, G. Chong and Y. Li, "PID control system analysis, design, and technology," *IEEE Trans. Control Syst. Technol.*, vol. 13, no. 4, pp. 559–576, Jul. 2005.

- [44] V. Gilja, et al. "A high-performance neural prosthesis enabled by control algorithm design," *Nature Neurosci.*, vol. 15, no. 12, pp. 1752–1757. 2012.

- [45] W. K. Ho, C. C. Hang and J. H. Zhou, "Performance and gain and phase margins of well-known PI tuning formulas," *IEEE Trans. Control Syst. Technol.*, vol. 3, no. 2, pp. 245–248, Jun. 1995.

- [46] B. Haaheim and T. G. Constandinou, "A sub-1 uQ, 16 kHz current-mode SAR-ADC for single-neuron spike recording," in *Proc. IEEE Int. Symp. Circuits Syst.*, no. 1, pp. 2957–2960, May 2012.

- [47] L. Chen, B. Shi, and C. Lu, "A robust high-speed and low-power CMOS current comparator circuit," in *Proc. IEEE Asia-Pacific Conf. Circuits Syst. Electron. Commun. Syst.*, pp. 174–177, 2000.

- [48] C. Liu, et al. "A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure". IEEE J. Solid-State Circuits, vol. 45, no. 4, pp. 731– 740, 2010.

- [49] NXP Semiconductors, http://www.nxp.com/documents/application note/AN10216.pdf.

- [50] P. Dayan and L. F. Abbott, "Theoretical Neuroscience, Computational and Mathematical Modeling of Neural Systems," Cambridge, MA, USA: MIT Press, 2001.

- [51] W. Chen, H. Chiueh, T. Chen, C. Ho, C. Jeng, M. Ker, C. Lin, Y. Huang, C. Chou, T. Fan, M. Cheng, Y. Hsin, S. Liang, Y. Wang, F. Shaw, Y. Huang, C. Yang, and C. Wu, "A fully integrated 8-channel closed-loop epileptic seizure control," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 232–247, 2014.

- [52] R. Shulyzki, K. Abdelhalim, A. Bagheri, M. T. Salam, C. M. Florez, J. L. P. Velazquez, P. L. Carlen, and R. Genov, "320-channel active probe for high-resolution neuromonitoring and responsive neurostimulation," *IEEE Trans. Biomed. Circuits Syst.*, vol. 9, no. 1, pp. 1–1, 2015.

- [53] W. Biederman, D. J. Yeager, N. Narevsky, S. Member, J. Leverett, R. Neely, J. M. Carmena, S. Member, E. Alon, S. Member, and J. M. Rabaey, "A 4.78 mm<sup>2</sup> fully-integrated neuromodulation SoC combining 64 acquisition channels with digital compression and simultaneous dual stimulation," *IEEE J. Solid-State Circuits*, vol. 50, no. 4, pp. 1038–1047, 2015.

Xilin Liu (S'13) received the B.S. degree in electrical engineering from the Harbin Institute of Technology, Harbin, China, and the M.S. degree in electrical engineering from the University of Pennsylvania, Philadelphia, PA, USA in 2011 and 2013, respectively.

Currently, he is working toward the Ph.D. degree at the University of Pennsylvania. His research interests include analog and mixed-signal integrated circuits and systems design for medical applications, brain-machine interface, low-power data converters, high-speed DAC for telecommunications, and CMOS image sensors.

Mr. Liu received the IEEE Solid-State Circuits Society (SSCS) 2015–2016 Predoctoral Achievement Award. He authored papers that received the Best Paper Award (1st place) of the 2015 Biomedical Circuits and Systems Conference (BioCAS) and the Best Paper Award of the BioCAS Track of the 2014 International Symposium on Circuits and Systems (ISCAS). Also, he was the recipient of the Student-Research Preview Award (honorable mention) of the 2014 IEEE International Solid-State Circuits Conference (ISSCC).

Milin Zhang (S'06–M'11) received the B.S. and M.S. degrees in electronic engineering from Tsinghua University, Beijing, China, in 2004 and 2006, respectively, and the Ph.D. degree from the Electronic and Computer Engineering Department, Hong Kong University of Science and Technology (HKUST), Hong Kong.

After finishing her doctoral studies, she worked as a Postdoctoral Researcher at the University of Pennsylvania, Philadelphia, PA, USA. She joined Tsinghua University as an Assistant Professor in the

Department of Electronic Engineering in 2016. Her research interests include designing of traditional and various non-traditional imaging sensors, such as polarization imaging sensors and focal-plane compressive acquisition image sensors. She is also interested in brain-machine-interface and relative biomedical sensing applications and new sensor designs.

Dr. Zhang has received the Best Paper Award of the BioCAS Track of the 2014 International Symposium on Circuits and Systems (ISCAS), and the Best Paper Award (1st place) of the 2015 Biomedical Circuits and Systems Conference (BioCAS).

Andrew G. Richardson (M'14) received the B.S.E. degree in biomedical engineering from Case Western Reserve University, Cleveland, OH, USA, in 2000, and the S.M. degree in mechanical engineering and the Ph.D. degree in biomedical engineering from the Massachusetts Institute of Technology (MIT), Cambridge, MA, USA, in 2003 and 2007, respectively.

Currently, he is Co-Director of the Translational Neuromodulation Laboratory, Department of Neurosurgery, University of Pennsylvania, Philadelphia, PA, USA. His research interests include neural pros-

theses for restoring sensory, motor, and memory function.

**Jan Van der Spiegel** (S'73–M'79–SM'90–F'02) received the M.S. degree in electromechanical engineering and the Ph.D. degree in electrical engineering from the University of Leuven, Belgium, in 1974 and 1979, respectively

He is a Professor of the Electrical and Systems Engineering, the Director of the Center for Sensor Technologies, and Associate Dean for Professional Program at the School of Engineering and Applied Science at the University of Pennsylvania, Philadelphia, PA, USA. He is the former chair of the Electrical

Engineering and interim chair of the Electrical and Systems Engineering Departments. His primary research interests are in mixed-mode VLSI design, CMOS vision sensors for polarization imaging, biologically based image sensors and sensory information processing systems, and brain-machine interface electronics. He has authored more than 250 journal and conference papers, and is the coauthor of eight U.S. patents.

Dr. Van der Spiegel received the IEEE Major Educational Innovation Award, and is the recipient of the IEEE Third Millennium Medal, the UPS Foundation Distinguished Education Chair and the Bicentennial Class of 1940 Term Chair. He received the Christian and Mary Lindback Foundation, and the S. Reid Warren Award for Distinguished Teaching, the IBM Young Faculty Development Award and the Presidential Young Investigator Award. He has served on several IEEE program committees (IEDM, ICCD, ISCAS and ISSCC) and was the technical program chair of the 2007 International SolidState Circuit Conference (ISSCC 2007). He is an Associate Editor of IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS, and Section Editor of Electrical and Electronic Engineering of the Journal of Engineering of the IET, and former Editor of Sensors and Actuators A for North and South America. He was the chair of the IEEE SSCS Chapters committee from 1998 to 2015. Currently, he is the President of the IEEE Solid-State Circuits Society. He is a member of Phi Beta Delta and Tau Beta Pi.

**Timothy H. Lucas** (M'12) completed his neurosurgery and doctoral training in physiology and biophysics at the University of Washington, Seattle, WA, USA in 2009, followed by subspecialty fellowships at the University of California, San Francisco, San Francisco, CA, USA.

He also served as Senior Registrar in the Atkinson Moreley Wing of St. George's Health Care Trust in London, U.K. As Assistant Professor of Neurosurgery, he directs the Translational Neuromodulation Lab and Co-Directs the Center for Neuroengi-

neering and Therapeutics at the University of Pennsylvania. Philadelphia, PA, USA. His research focuses on the developing novel neuromodulation strategies to restore function to patients with paralysis. Clinically, he performs craniotomies for tumor and epilepsy in eloquent brain regions using minimally invasive laser and endoscopic techniques.