# LC-2

# Programmer's Reference and

# User Guide

University of Michigan EECS 100

Copyright (C) Matt Postiff 1995-1999. All rights reserved. Written permission of the author is required for duplication of this document.

# **Table of Contents**

| Table of Contents                                 |    |

|---------------------------------------------------|----|

| List of Tables                                    |    |

| List of Figures                                   | V  |

| Chapter 1 Introduction to the LC-2                | 1  |

| 1.1 Notational Conventions                        | 3  |

| Chapter 2 LC-2 Programmer's Reference             | 7  |

| 2.1 LC-2 Programming Model                        | 9  |

| 2.2 Instruction Set                               |    |

| 2.3 Summary of Instruction Formats and Semantics  | 28 |

| 2.4 Addressing Modes                              | 31 |

| 2.5 Branching Modes                               |    |

| 2.6 The LC-2 System Calls                         |    |

| 2.7 The LC-2 Hardware Registers                   |    |

| 2.8 The LC-2 Memory Map                           | 35 |

| Chapter 3 LC-2 Machine- and Assembly-Programming  | 37 |

| 3.1 Introduction to Program Execution in the LC-2 | 39 |

| 3.2 The LC-2 Instruction Encoding                 | 40 |

| 3.3 Condition Codes in the LC-2 Processor         | 41 |

| 3.3.1 Condition Field in the Instruction Encoding |    |

| 3.4 Keyboard Input and Console Output             |    |

| 3.5 Programming the LC-2 in Machine Language      |    |

| 3.5.1 Machine-Language File Formats               |    |

| 3.6 Programming the LC-2 in Assembly Language     |    |

| 3.6.1 Introduction                                |    |

| 3.6.2 LC-2 Assembly Language                      |    |

| 3.6.3 The Assembly Process                        |    |

| 3.6.4 Some Examples                               | 49 |

| Chapter 4 LC-2 Programming Tools Guide            | 51 |

| 4.1 The convert Program                           | 53 |

| 4.2 The assemble Program                          | 54 |

| 4.2.1 The Listing File                            | 54 |

| 4.3 The Simulator                                 |    |

| 4.3.1 The Simulator Menu Bar                      | 56 |

| Chapter 5 Appendices                              | 61 |

| Appendix A ASCII Reference                        | 63 |

| Appendix B Simulator Script Reference   | 65 |

|-----------------------------------------|----|

| Appendix C Installing the LC-2 Software | 67 |

# **List of Tables**

| Table 1. Notational Conventions                                                      | 3           |

|--------------------------------------------------------------------------------------|-------------|

| Table 2. The Logical Operators                                                       | 5           |

| Table 3. Specifying when a branch occurs by the relationship between the instruction | 's nzp bits |

| and the condition codes                                                              | 14          |

| Table 4. LC-2 Instruction Format Summary                                             | 28          |

| Table 5. LC-2 addressing modes                                                       | 31          |

| Table 6. LC-2 branching modes                                                        | 32          |

| Table 7. LC-2 System Calls                                                           | 33          |

| Table 8. LC-2 Hardware Registers                                                     | 34          |

| Table 9. Condition Codes in the LC-2 Processor                                       | 41          |

| Table 10. The Possibilities for the Condition Field in the Instruction (nzp)         | 41          |

| Table 11. The elements of a line of an LC-2 assembly language program                | 46          |

| Table 12. LC-2 Assembler reserved characters                                         | 47          |

| Table 13. LC-2 assembler pseudo-ops                                                  | 48          |

| Table 14. LC-2 assembler output files                                                | 54          |

| Table 15. ASCII Code Reference                                                       | 63          |

# **List of Figures**

| Figure 1. LC-2 Memory Map                                                                   | 35 |

|---------------------------------------------------------------------------------------------|----|

| Figure 2. The binary representation of an LC-2 program (left) and its equivalent hexadecima | 1  |

| representation (right)                                                                      | 43 |

| Figure 3. A more complicated LC-2 program                                                   | 44 |

| Figure 4. The program of Figure 2 shown in assembly language                                | 49 |

| Figure 5. The program of Figure 3 shown in assembly language                                | 50 |

| Figure 6. Assembler-produced listing file for dumbadd.asm                                   | 54 |

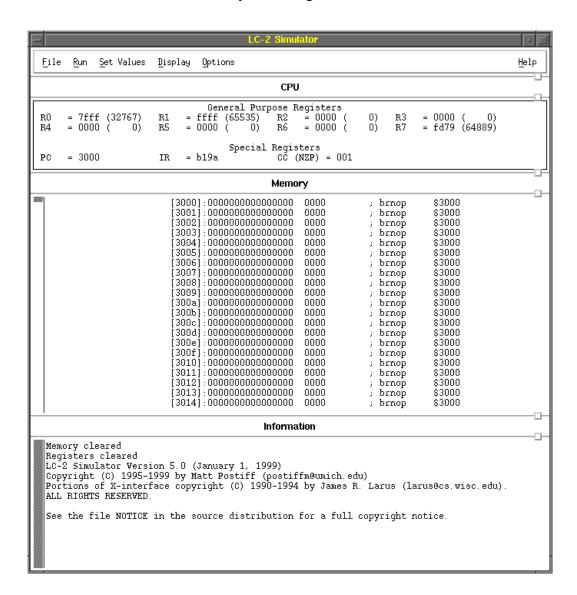

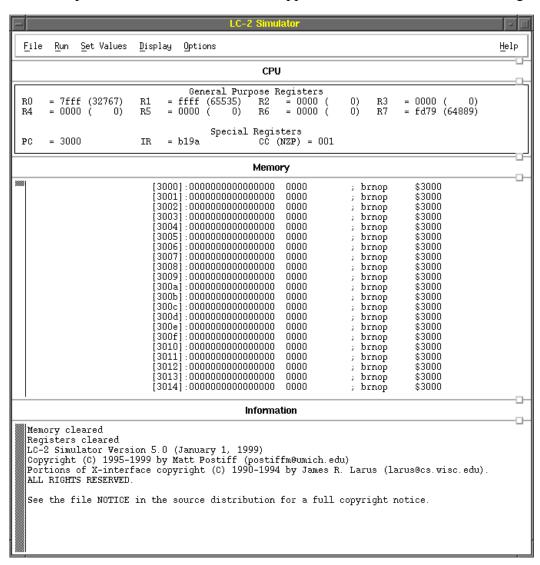

| Figure 7. The LC-2 simulator                                                                | 55 |

| Figure 8. The LC-2 console window                                                           | 56 |

| Figure 9. The LC-2 Simulator menu bar                                                       | 57 |

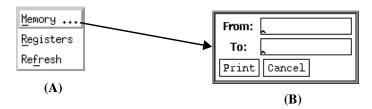

| Figure 10. The LC-2 Simulator File menu (A) and associated dialog boxes (B-D)               | 57 |

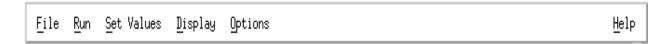

| Figure 11. The LC-2 Simulator Run menu (A) and associated dialog boxes (B-D)                | 58 |

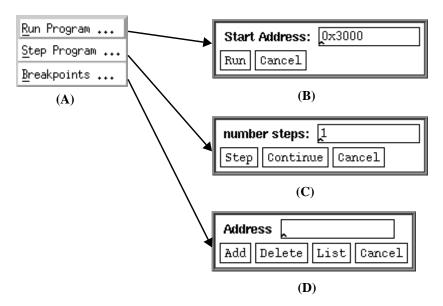

| Figure 12. The LC-2 Simulator Set Values menu (A) and an associated dialog box (B)          | 59 |

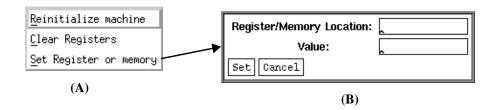

| Figure 13. The LC-2 Simulator Display menu (A) and an associated dialog box (B)             | 59 |

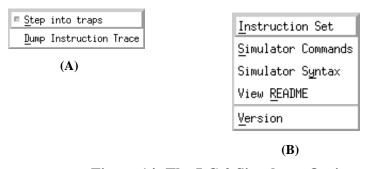

| Figure 14. The LC-2 Simulator Options (A) and Help menus (B)                                | 60 |

| Figure 15. The LC-2 Simulator Popup menu                                                    | 60 |

# CHAPTER 1 Introduction to the LC-2

The Little Computer 2 (LC-2) is a simple computer used to introduce general-purpose computing devices to first-year engineering students with no previous background in computer architecture or logic design. This document introduces the use and programming of the LC-2. The remainder of this chapter defines notation used throughout this manual. The LC-2 Programmer's Reference in Chapter 2 is a detailed reference manual for students who will write several programming assignments on the machine. Chapter 3 details LC-2 machine-language and assembly-language programming. The LC-2 Programming Tools Guide in Chapter 4 provides information concerning use of the assembler and simulator. The appendices provide an ASCII character reference and some detail about the simulation tools.

The LC-2 and accompanying materials have been used for the introductory computing course (EECS 100) at the University of Michigan since the Fall of 1995. Winter 1999 is the eighth semester in which the LC-2 has been used.

The course lectures, the textbook, and this document complement each other, and neither in isolation will cover the whole LC-2.

#### 1.1. Notational Conventions

This section summarizes the notational conventions used throughout this manual.

A word is a 16-bit quantity with bit order increasing from right to left, so that the left bit is numbered 15 and the right bit is numbered 0. Bit 15 is the *most significant bit*, while bit 0 is the *least significant bit*. The following figure illustrates:

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

Table 1 lists the symbols and terms used throughout the manual.

**Table 1: Notational Conventions**

| Notation                                 | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| \$Number, XNumber,<br>0XNumber, 0xNumber | The number is specified in base-16 (hexadecimal).                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| #Number                                  | The number is specified in base-10 (decimal).                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| A <l:r></l:r>                            | Denotes part of a value, specifically, the bits in positions I through r of value A (usually a register or memory location). Fe example, if the value in the PC is (hex) \$301A = (binary) 0011 0000 0001 1010, then PC<15:9> refers to the 7 bits 0011 000. only one bit needs to be denoted, the notation is usually abbrev ated as A<1>, the :r part being left off. For example, PC<2:2> i the same as PC<2>, which is the single bit found at bit position of the PC (0 in this case). |  |

| A @ B                                    | Concatenation of A and B. For example, if A is 0011 01 and B is 00 1100 1000, A @ $B = 0011\ 0100\ 1100\ 1000$ .                                                                                                                                                                                                                                                                                                                                                                            |  |

| BaseR                                    | Base Register. one of R0R7 whose contents specify the base address of a memory structure.                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| COND                                     | Condition upon which a branch occurs. These are based on the processor status bits N, Z, and P. See the BR instruction.                                                                                                                                                                                                                                                                                                                                                                     |  |

| page                                     | The set of $2^9$ consecutive memory locations which share the same high 7 address bits (bits <15:9> of the address).                                                                                                                                                                                                                                                                                                                                                                        |  |

| current page                             | The page where the currently executing instruction resides.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| DR                                       | Destination Register; one of R0R7 which specifies where the result of an instruction should be written                                                                                                                                                                                                                                                                                                                                                                                      |  |

| general purpose register                 | Any register R0R7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

**Table 1: Notational Conventions**

| Notation     | Meaning                                                                                                                                                                                                                                                                                   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| imm5         | 5-bit immediate value; 5 bits in an instruction used as a literal (immediate) value; sign extended to 16 bits. Range {-1615}.                                                                                                                                                             |

| index6       | 6-bit immediate value; These 6 bits are zero extended and added to a base register to form a memory address. Range {063}. Note that index6 is always zero or positive.                                                                                                                    |

| LABEL        | An assembler construct that identifies a location on the current page. It is translated into a pgoffset9 (see below).                                                                                                                                                                     |

| L            | Link bit; specifies whether a JSR instruction will save the value of the next PC in R7. If $L == 1$ , the next PC is saved in R7. If $L == 0$ , the next PC is <i>not</i> saved in R7.                                                                                                    |

| MB1          | Must Be One. In an instruction encoding, bits shown as MB1 must be set to 1 by the programmer or assembler. Zeroes in these bit positions may result in unexpected behavior.                                                                                                              |

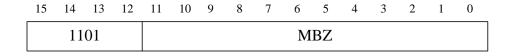

| MBZ          | Must Be Zero. In an instruction encoding, bits shown as MBZ must be set to 0 by the programmer or assembler. Non-zero values in these bit positions may result in unexpected behavior.                                                                                                    |

| mem[address] | Denotes the contents of memory at the given address.                                                                                                                                                                                                                                      |

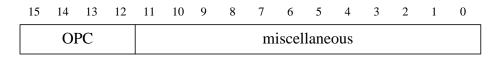

| OPC          | Opcode field of instruction; 4 bits which specify the instruction to be executed by the processor.                                                                                                                                                                                        |

| PC           | Program Counter; 16-bit, processor-internal register which contains the memory address of the <i>next</i> instruction to be fetched. For example, during execution of the instruction at address A, the PC contains address A+1. The PC is sometimes called the Instruction Pointer (IP). |

| pgoffset9    | 9 bits of offset on a page (a page address). PC<15:9> is concatenated with pgoffset9 to form a 16-bit memory address. Range {0511}.                                                                                                                                                       |

| setcc(X)     | Indicates that condition codes N, Z and P are set based on the value of X. If X is negative, N=1, Z=0, P=0. If X is zero, N=0, Z=1, P=0. If X is positive, N=0, Z=0, P=1.                                                                                                                 |

| SEXT(A)      | Sign extension of A. The most significant bit position of A is duplicated as many times as necessary to extend A to 16 bits. For example, if $A = 1100\ 00$ , then $SEXT(A) = 1111\ 1111\ 1111\ 0000$ .                                                                                   |

| SR, SR1, SR2 | Source Register (1 or 2); one of R0R7 which specifies from where an instruction operand is taken.                                                                                                                                                                                         |

**Table 1: Notational Conventions**

| Notation  | Meaning                                                                                                                                                                                                                                                 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| trapvect8 | 8-bit trap number used in the TRAP instruction. Range {0255}.                                                                                                                                                                                           |

| unix%     | The Unix command prompt.                                                                                                                                                                                                                                |

| ZEXT(A)   | Zero extension of A. Enough zero bits are added to the most significant end of A to extend it to 16 bits. For example, if $A = 1100$ 00, then $ZEXT(A) = 0000\ 0000\ 0011\ 0000$ . Note that $ZEXT(A) = SEXT(A)$ if the most significant bit of A is 0. |

Table 2 shows the truth tables of the logical operators used in this manual.

**Table 2: The Logical Operators**

| X | Y                                              | X AND Y                               |

|---|------------------------------------------------|---------------------------------------|

| 0 | 0                                              | 0                                     |

| 0 | 1                                              | 0                                     |

| 1 | 0                                              | 0                                     |

| 1 | 1                                              | 1                                     |

| X | Y                                              | X OR Y                                |

| 0 | 0                                              | 0                                     |

| 0 | 1                                              | 1                                     |

| 1 | 0                                              | 1                                     |

| 1 | 1                                              | 1                                     |

| X |                                                | NOT X                                 |

| 0 |                                                | 1                                     |

| 1 |                                                | 0                                     |

|   | 0<br>0<br>1<br>1<br>X<br>0<br>0<br>1<br>1<br>X | 0 0 0 1 1 1 X Y 0 0 0 1 1 1 X 0 1 X 0 |

# CHAPTER 2 LC-2 Programmer's Reference

This chapter, the **LC-2 Programmer's Reference**, is a detailed reference manual for the LC-2 architecture. This chapter is divided into 8 sections. Section 1 gives an overview of LC-2 programming; 2 details the instruction set of the LC-2; 3 is an instruction summary; and 4 and 5 contain descriptions of addressing and branching modes. Section 6 lists the trap routines provided with the simulator; 7 lists the hardware registers for accessing video, keyboard, and machine control functions of the LC-2; and 8 shows a memory map of the machine.

#### 2.1. LC-2 Programming Model

The LC-2 has 8 general purpose registers, each of which is 16 bits wide. The arithmetic and logic units operate on 16 bit words. Addresses are 16 bits wide, so the machine has  $2^{16}$  (65, 536 or 64K) words, or 128 KB of memory.

The instruction set contains 16 basic instructions. There are operates (ADD, AND, and NOT), data movement instructions (LD, LDI, LDR, ST, STI, STR, LEA), flow control instructions (BR, JSR, JMP, JSRR, JMPR, RET), and control instructions (RTI and TRAP).

The simplest addressing scheme, direct, forms addresses by concatenating the top 7 bits of the program counter with 9 bits of page address specified in the instruction. This means that the memory space can be viewed as divided into  $2^7 = 128$  pages, each of  $2^9 = 512$  words. The other addressing modes of the LC-2 are indirect, base+index, and immediate. See "Addressing Modes" on page 31 for more information.

Input and output devices are mapped as part of the memory address space. See "The LC-2 Hardware Registers" on page 34 for more details.

#### 2.2. Instruction Set

Each of the following pages describes an LC-2 instruction. The descriptions are laid out as follows:

#### **INSTRUCTION**

**Short description**

#### **Assembler Format(s):**

mnemonic [arguments]

This is the assembly language format of the instruction.

#### **Encoding(s):**

Machine code equivalent to the assembly language format.

#### **Operation:**

A formal description of the instruction.

#### **Description:**

English description of the action of the instruction, including any side effects. Includes special notes and references to related instructions. Includes a note about which, if any, of the condition codes are modified by the instruction. If an instruction modifies a condition code, the condition code is set or cleared depending on the result of the operation performed by the instruction. So,

if the result of the operation is negative, then N = 1, Z = 0, P = 0.

if the result of the operation is zero, then N = 0, Z = 1, P = 0.

if the result of the operation is positive, then N = 0, Z = 0, P = 1.

#### **Example(s):**

Some example uses of the instruction.

ADD

#### **Assembler Formats:**

```

ADD DR, SR1, SR2

ADD DR, SR1, imm5

```

#### **Encodings:**

| 15 | 14      | 13 | 12 | 11 | 10 | 9   | 8 | 7   | 6 | 5 | 4   | 3  | 2 | 1   | 0 |

|----|---------|----|----|----|----|-----|---|-----|---|---|-----|----|---|-----|---|

|    | 00      | 01 |    |    | DR |     |   | SR1 |   | 0 | M   | BZ |   | SR2 | 2 |

|    | 0001 DR |    |    |    |    | SR1 |   | 1   |   | j | imm | 5  |   |     |   |

#### **Operation:**

```

if (bit<5> == 0) {

DR = SR1 + SR2

}

else if (bit<5> == 1) {

DR = SR1 + SEXT(imm5)

}

setcc(DR)

```

#### **Description:**

If bit<5> == 0, then add the contents of SR1 and SR2. If bit<5> == 1, then add the contents of SR1 and the sign extended immediate value. The result in both cases is placed in DR and sets the condition codes.

Any carry generated at the most significant bit of the addition is discarded, and overflow is not signalled.

```

ADD R2, R3, R4 ; R2 = R3 + R4

ADD R2, R3, \#7 ; R2 = R3 + 7

```

#### **Assembler Formats:**

```

AND DR, SR1, SR2

AND DR, SR1, imm5

```

#### **Encodings:**

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6 | 5 | 4 | 3  | 2  | 1   | 0 |

|----|----|----|----|----|----|---|---|-----|---|---|---|----|----|-----|---|

|    | 01 | 01 |    |    | DR |   |   | SR1 |   | 0 | M | ΒZ |    | SR2 | 2 |

|    | 01 | 01 |    |    | DR |   |   | SR1 |   | 1 |   | i  | mm | 5   |   |

#### **Operation:**

```

if (bit<5> == 0) {

DR = SR1 AND SR2

}

else if (bit<5> == 1) {

DR = SR1 AND SEXT(imm5)

}

setcc(DR)

```

#### **Description:**

If bit<5> == 0, then perform the bitwise AND of the contents of SR1 and SR2. If bit<5> == 1, then perform the bitwise AND of the contents of SR1 and the sign extended immediate value. The result in both cases is placed in DR and sets the condition codes.

```

AND R2, R3, R4 ; R2 = R3 AND R4

AND R2, R3, #7 ; R2 = R3 AND 7

```

#### BR

# **Branch to Location on Current Page**

#### **Assembler Formats:**

| _     |        |      | 3.6   | •         |

|-------|--------|------|-------|-----------|

| $H_0$ | 1111VA | lent | Mine  | monics    |

|       | ai va  | LOIL | 11110 | 111011100 |

| BRn LABEL   | BRlt LABEL |

|-------------|------------|

| BRz LABEL   | BReq LABEL |

| BRp LABEL   | BRgt LABEL |

| BRnz LABEL  | BRle LABEL |

| BRnp LABEL  | BRne LABEL |

| BRzp LABEL  | BRge LABEL |

| BRnzp LABEL | BR LABEL   |

| BRNOP       | NOP        |

#### **Encoding:**

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4     | 3   | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|----|-------|-----|---|---|---|

|    | 00 | 00 |    | n  | Z  | p |   |   |   | pg | goffs | et9 |   |   |   |

#### **Operation:**

```

if ((n \ AND \ N) \ OR \ (z \ AND \ Z) \ OR \ (p \ AND \ P)) \ \{ \\ PC = PC < 15:9 > @ \ pgoffset9 \\ \}

```

#### **Description:**

If the condition is true, branch to the specified location on the current page. The top 7 bits of the current program counter are concatenated with the pgoffset9 field to form the new 16-bit PC value, which is written to the PC only if the condition is true. The condition codes are not modified.

The nzp bits specify how to compute the condition under which the processor should take the branch. Table 3 explains the nzp encodings.

Table 3: Specifying when a branch occurs by the relationship between the instruction's nzp bits and the condition codes.

| nzp | Condition<br>Codes Set | Condition                                 | nzp | Condition<br>Codes Set | Condition                                    |

|-----|------------------------|-------------------------------------------|-----|------------------------|----------------------------------------------|

| 000 | NA                     | Do not branch under any condition         | 100 | N                      | Negative<br>Less Than                        |

| 001 | P                      | Positive<br>Greater Than                  | 101 | N or P                 | Negative or Positive<br>Not Equal            |

| 010 | Z                      | Zero<br>Equal                             | 110 | N or Z                 | Negative or Zero<br>Less than or Equal       |

| 011 | Z or P                 | Zero or Positive<br>Greater than or Equal | 111 | N, Z, or<br>P          | Negative, Zero, or Positive<br>Unconditional |

The processor examines the n, z, and p bits in the instruction to determine which LC-2 condition codes to test. If n is set, test N; if n is not set, ignore N. If z is set, test Z, etc. If any of the condition codes tested in this way is set, the branch is taken. If none of n, z, or p are set in the instruction, the processor treats the branch instruction as it would treat a NOP. If n, z, and p are all set, the processor branches unconditionally, regardless of the condition code setting.

JSR/JMP and JSRR/JMPR also control program flow.

Zero is neither positive nor negative.

#### **Example:**

BRzp LOOP; Branch to LOOP if last result was zero or positive

# JSR JMP

# Jump to Subroutine Jump

#### **Assembler Format:**

#### **Encoding:**

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5  | 4     | 3   | 2 | 1 | 0 |

|----|----|----|----|----|----|----|---|---|---|----|-------|-----|---|---|---|

|    | 01 | 00 |    | L  | M  | BZ |   |   |   | pg | goffs | et9 |   |   |   |

#### **Operation:**

```

if (L == 1) {

R7 = PC

}

PC = PC<15:9> @ pgoffset9

```

# **Description:**

Unconditionally jump to the specified location on the current page. If the link bit L is set, the PC is saved in R7, allowing a later return. The top 7 bits of the current program counter are concatenated with the pgoffset9 field to form the new 16-bit PC value. The condition codes are not modified.

```

JSR FOO ; Jump to FOO, put return PC into R7 JMP FOO ; Jump to FOO

```

# JSRR JMPR

# Jump to Subroutine through Register Jump through Register

#### **Assembler Format:**

```

JSRR BaseR, index6 (L = 1)

JMPR BaseR, index6 (L = 0)

```

#### **Encoding:**

| 15 | 5 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7    | 6 | 5 | 4 | 3   | 2    | 1 | 0 |

|----|---|----|----|----|----|----|----|---|------|---|---|---|-----|------|---|---|

|    |   | 11 | 00 |    | L  | M  | ΒZ | ] | Base | R |   |   | ind | lex6 |   |   |

#### **Operation:**

```

if (L == 1) {

R7 = PC

}

PC = BaseR + ZEXT(index6)

```

# **Description:**

If the link bit L is set, the PC is saved in R7, allowing a later return. The index is zero extended to 16 bits and added to the contents of BaseR to form the new PC value. The condition codes are not modified.

```

JSRR R2, \#10 ; Jump to R2 + 10, put return PC into R7 JMPR R2, \#10 ; Jump to R2 + 10

```

#### LD

# **Load Direct from Memory to Register**

#### **Assembler Format:**

LD DR, LABEL

#### **Encoding:**

| 15 14 | 13 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4     | 3   | 2 | 1 | 0 |

|-------|-------|----|----|---|---|---|---|----|-------|-----|---|---|---|

| 0010  | 0     |    | DR |   |   |   |   | pg | goffs | et9 |   |   |   |

#### **Operation:**

#### **Description:**

Load a register from the specified location on the current page. The top 7 bits of the current program counter are concatenated with the pgoffset9 field to form a 16-bit memory address. The contents of memory at this address is loaded into DR and is used to set the condition codes.

LD R4, COUNT; R4 =

$$mem[COUNT]$$

#### LDI

# **Load Indirect from Memory to Register**

#### **Assembler Format:**

LDI DR, LABEL

#### **Encoding:**

| 15 14 1 | 13 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4     | 3   | 2 | 1 | 0 |

|---------|-------|----|----|---|---|---|---|----|-------|-----|---|---|---|

| 1010    | 0     |    | DR |   |   |   |   | pg | goffs | et9 |   |   |   |

#### **Operation:**

```

DR = mem[ mem[ PC<15:9> @ pgoffset9 ] ] setcc(DR)

```

#### **Description:**

Load a register indirectly from the specified location. The top 7 bits of the current program counter are concatenated with the pgoffset9 field to form a 16-bit memory address. The contents of memory at this location is used as the address of the data that is loaded into DR. The data loaded into DR sets the condition codes.

```

LDI R4, POINTER ; R4 = mem[mem[POINTER]]

```

#### LDR

# **Load from mem[Base + Index] to Register**

#### **Assembler Format:**

LDR DR, BaseR, index6

#### **Encoding:**

| 15 | 5    | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7    | 6 | 5 | 4 | 3   | 2    | 1 | 0 |

|----|------|----|----|----|----|----|---|---|------|---|---|---|-----|------|---|---|

|    | 0110 |    |    |    |    | DR |   | I | 3ase | R |   |   | ind | lex6 |   |   |

#### **Operation:**

$$DR = mem[BaseR + ZEXT(index6)]$$

setcc(DR)

#### **Description:**

Load a register using a base register and index. The index is zero extended to 16 bits and added to the contents of BaseR to form a memory address. The contents of memory at this address is loaded into DR and sets the condition codes. Note that index6 is a positive offset.

```

LDR R4, R2, \#10; R4 = contents of mem[R2 + 10]

```

#### **LEA**

#### **Load Effective Address**

#### **Assembler Format:**

LEA DR, LABEL

#### **Encoding:**

| 15 | 14   | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4     | 3   | 2 | 1 | 0 |

|----|------|----|----|----|----|---|---|---|---|----|-------|-----|---|---|---|

|    | 1110 |    |    |    | DR |   |   |   |   | pg | goffs | et9 |   |   |   |

#### **Operation:**

#### **Description:**

The top 7 bits of the current program counter are concatenated with the pgoffset9 field to form a 16-bit memory address. This address is placed into DR and sets the condition codes.

# **NOT**

# **Bitwise NOT (invert or complement)**

#### **Assembler Format:**

NOT DR, SR

#### **Encoding:**

| 15 14 | 13   | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|-------|------|----|----|----|---|---|----|---|---|---|---|----|---|---|

| 100   | 1001 |    |    | DR |   |   | SR |   |   |   | M | B1 |   |   |

#### **Operation:**

DR = NOT(SR)setcc(DR)

#### **Description:**

Perform the bitwise complement operation on the contents of SR and place the result in DR. The result sets the condition codes.

### **Example:**

NOT R4, R2 ; R4 = NOT(R2)

# **RET**

# **Return from Subroutine**

#### **Assembler Format:**

**RET**

#### **Encoding:**

#### **Operation:**

$$PC = R7$$

#### **Description:**

Load the PC with the value in R7, thus allowing a return from a previous JSR or JSRR instruction. The condition codes are not modified.

RET ;

$$PC = R7$$

#### RTI

# **Return from Interrupt**

#### **Assembler Format:**

RTI

#### **Encoding:**

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|----|---|---|---|---|---|

|    | 10 | 00 |    |    |    |   |   |   | M | ΒZ |   |   |   |   |   |

#### **Operation:**

```

setcc(mem[R6])

R6 = R6 - 1

PC = mem[R6]

R6 = R6 - 1

```

#### **Description:**

Pop the top of the stack, and load the value into PC. The condition codes are not modified.

#### **Example:**

```

RTI ; first pop condition codes ; then pop PC

```

#### **Notes:**

On an external interrupt, the initiating sequence pushes the PC onto the stack, then pushes the current condition codes onto the stack, then loads the PC with the starting address of the service routine. The last instruction in the service routine is RTI, which returns control to the interrupted program by popping the stack and loading the value popped into the condition codes, then popping the stack again and loading the value popped into the PC.

#### ST

# **Store Direct from Register to Memory**

#### **Assembler Format:**

ST SR, LABEL

#### **Encoding:**

| 15 | 14   | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4     | 3   | 2 | 1 | 0 |

|----|------|----|----|----|----|---|---|---|---|----|-------|-----|---|---|---|

|    | 0011 |    |    |    | SR |   |   |   |   | pg | goffs | et9 |   |   |   |

#### **Operation:**

mem[ PC<15:9> @ pgoffset9 ] = SR

#### **Description:**

Store from the specified register to the specified location on the current page. The top 7 bits of the current program counter are concatenated with the pgoffset9 field to form a 16-bit memory address. The contents of SR are copied into memory at this address. The condition codes are not modified.

#### **Example:**

ST R4, COUNT ; mem[COUNT] = R4

#### STI

# **Store Indirect from Register to Memory**

#### **Assembler Format:**

STI SR, LABEL

#### **Encoding:**

| 15 | 14   | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4     | 3   | 2 | 1 | 0 |

|----|------|----|----|----|----|---|---|---|---|----|-------|-----|---|---|---|

|    | 1011 |    |    |    | SR |   |   |   |   | pg | goffs | et9 |   |   |   |

#### **Operation:**

mem[ mem[ PC<15:9> @ pgoffset9 ] ] = SR

#### **Description:**

Store from the specified register to the indirectly specified location. The top 7 bits of the current program counter are concatenated with the pgoffset9 field to form a 16-bit memory address. The contents of memory at this address are used as the address where the contents of SR are to be copied. The condition codes are not modified.

#### **Example:**

STI R4, POINTER ; mem[mem[POINTER]] = R4

#### STR

# **Store from Register to mem[Base + Index]**

#### **Assembler Format:**

STR SR, BaseR, index6

#### **Encoding:**

| 1 | 5    | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7    | 6 | 5 | 4 | 3   | 2    | 1 | 0 |

|---|------|----|----|----|----|----|---|---|------|---|---|---|-----|------|---|---|

|   | 0111 |    |    |    |    | SR |   | ] | Base | R |   |   | ind | lex6 |   |   |

#### **Operation:**

$$mem[(BaseR + ZEXT(index6))] = SR$$

#### **Description:**

Store from the specified register to the specified location. The offset is zero extended to 16 bits and added to the contents of BaseR to form a memory address. The contents of SR are copied into memory at this address. The condition codes are not modified.

STR R4, R2,

$$\#10$$

;  $mem[R2 + 10] = R4$

#### **TRAP**

# **Call System Routine**

#### **Assembler Format:**

TRAP trapvect8

#### **Encoding:**

| 15 | 14   | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |

|----|------|----|----|----|----|----|---|---|---|---|------|------|---|---|---|

|    | 1111 |    |    |    | M  | ΒZ |   |   |   |   | trap | vect | 3 |   |   |

#### **Operation:**

R7 = PC

PC = mem[ ZEXT(trapvect8) ]

#### **Description:**

Execute the system call specified by the trap number. The PC is saved in R7, allowing a later return. The trapvect8 field is zero extended to 16 bits. The contents of this memory location are placed into the PC. The condition codes are not modified.

Each of the first  $2^8 = 256$  memory locations contains the starting address for the system call specified by its corresponding trap number. This area of memory is called the trap vector table. See "The LC-2 System Calls" on page 33 for more information.

### **Example:**

TRAP x23

; Execute the IN system call

# 2.3. Summary of Instruction Formats and Semantics

**Table 4: LC-2 Instruction Format Summary**

| Mnemonic | 15   | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7     | 6 | 5  | 4     | 3     | 2   | 1   | 0 |

|----------|------|----|----|----|----|----|----|---|-------|---|----|-------|-------|-----|-----|---|

| *ADD     |      | 00 | 01 |    |    | DR | •  |   | SR1   |   | 0  | M     | ΒZ    |     | SR2 |   |

| *ADD     |      | 00 | 01 |    |    | DR |    |   | SR1   |   | 1  |       | j     | imm | 5   |   |

| *AND     |      | 01 | 01 |    |    | DR |    |   | SR1   |   | 0  | M     | BZ    |     | SR2 |   |

| *AND     |      | 01 | 01 |    |    | DR |    |   | SR1   |   | 1  |       | i     | imm | 5   |   |

| BR       |      | 00 | 00 |    | n  | Z  | p  |   |       |   | pg | offse | et9   |     |     |   |

| JSR      |      | 01 | 00 |    | L  | M  | BZ |   |       |   | pg | offse | et9   |     |     |   |

| JSRR     |      | 11 | 00 |    | L  | M  | ΒZ | ] | Basel | R |    |       | ind   | ex6 |     |   |

| *LD      |      | 00 | 10 |    |    | DR |    |   |       |   | pg | offse | et9   |     |     |   |

| *LDI     |      | 10 | 10 |    |    | DR |    |   |       |   | pg | offse | et9   |     |     |   |

| *LDR     |      | 01 | 10 |    |    | DR |    | ] | Basel | R |    |       | ind   | ex6 |     |   |

| *LEA     |      | 11 | 10 |    |    | DR |    |   |       |   | pg | offse | et9   |     |     |   |

| *NOT     |      | 10 | 01 |    |    | DR |    |   | SR    |   |    |       | M     | B1  |     |   |

| RET      |      | 11 | 01 |    |    |    |    | • |       | M | BZ |       |       |     |     |   |

| RTI      |      | 10 | 00 |    |    |    |    |   |       | M | BZ |       |       |     |     |   |

| ST       |      | 00 | 11 |    |    | SR |    |   |       |   | pg | offse | et9   |     |     |   |

| STI      |      | 10 | 11 |    |    | SR |    |   |       |   | pg | offse | et9   |     |     |   |

| STR      | 0111 |    |    |    |    | SR |    | ] | Basel | R |    |       | ind   | ex6 |     |   |

| TRAP     |      | 11 | 11 |    |    | M  | ΒZ |   |       |   |    | trapy | vect8 | 3   |     |   |

<sup>\*</sup>Indicates instructions that modify the condition codes.

The following Verilog summarizes the behavior of each instruction. The Verilog variable containing the instruction is called inst. Symbols such as DR, ZEXT, trapvect8, etc. are used as defined earlier in this document. The register file is a memory array called R[].

```

// Memory State

reg [15:0] mem [65535:0];

// primary memory

// Processor State

reg [15:0] PC;

// program counter

reg [15:0] R [7:0];

// register file

reg N, Z, P;

// condition codes

// Instruction Format

reg [15:0] i;

// instruction

reg [3:0] opc = i[15:12];

// opcode

req [4:0] imm5 = i[4:0];

// immediate data

reg [8:0] pgoffset9 = i[8:0]; // page address

reg [5:0] index6 = i[5:0];

// immediate index

reg [7:0] trapvect8 = i[7:0]; // trap vector

reg [2:0] DR = i[11:9];

// destination register

reg [2:0] SR = i[11:9];

// source registers

req [2:0] SR1 = i[8:6];

reg [2:0] SR2 = i[2:0];

reg [2:0] BaseR = i[8:6];

reg L = i[11];

// link bit

// Interpret the instruction stream

task interpret begin

repeat begin

i = MP[PC];

PC = PC + 1;

execute;

end

end // task interpret

// Execute an instruction

task execute begin

case (i[15:12])

`ADD: begin

if (i[5] == 0) R[DR] = R[SR1] + R[SR2];

if (i[5] == 1) R[DR] = R[SR1] + SEXT(imm5);

set_condition_codes(R[DR]);

end

`LD: begin

```

```

R[DR] = mem[ \{PC[15:9], pgoffset9\} ];

set_condition_codes(R[DR]);

end

`ST: mem[ {PC[15:9], pgoffset9} ] = R[SR];

`JSR: begin // also called `JMP

if (L == 1) R[7] = PC;

PC = \{PC[15:9], pgoffset9\};

end

`AND: begin

if (i[5] == 0) R[DR] = R[SR1] & R[SR2];

if (i[5] == 1) R[DR] = R[SR1] \& SEXT(imm5);

set_condition_codes(R[DR]);

end

`LDR: begin

R[DR] = mem[ R[BaseR] + ZEXT(index6) ];

set_condition_codes(R[DR]);

end

`STR: mem[ R[BaseR] + ZEXT(index6) ] = R[SR];

`BR: begin

if ((i[11] & N) | (i[10] & Z) | (i[9] & P))

PC = \{PC[15:9], pgoffset9\};

end

`NOT: begin

R[DR] = \sim R[SR1];

set_condition_codes(R[DR]);

end

`LDI: begin

R[DR] = mem[mem[PC[15:9], pgoffset9]];

set_condition_codes(R[DR]);

end

`STI: mem[ mem[ {PC[15:9], pgoffset9} ] ] = R[SR];

`JSRR: begin // also called `JMPR

if (L == 1) R[7] = PC;

PC = R[SR1] + ZEXT(index6);

end

`RET: PC = R[7];

'RTI: begin

PC = mem[R[6]];

R[6] = R[6] - 1;

end

`LEA: begin

R[DR] = \{PC[15:9], pgoffset9\};

set_condition_codes(R[DR]);

end

`TRAP: begin

R[7] = PC;

```

```

PC = mem[ ZEXT(trapvect8) ];

end

endcase

end // task execute

// Computing condition codes

task set_condition_codes;

input [15:0] a;

begin

N = Z = P = 0;

if (a[15] == 1) N = 1;

else if (a == 16'b0) Z = 1;

else P = 1;

end // task set_condition_codes

endtask

```

# 2.4. Addressing Modes

An addressing mode defines the way in which data is accessed. The LC-2 has five addressing modes which are summarized in the table below.

Table 5: LC-2 addressing modes

| Name of<br>Addressing<br>Mode | Meaning                                                                                                                            | Example        |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------|

| register                      | The data is in the specified register.                                                                                             | add r1, r2, r3 |

| immediate<br>(literal)        | The data is in the instruction. In the example, the #5 is the immediate data.                                                      | add r1, r2, #5 |

|                               | The data to be loaded is the <b>literally</b> -specified address on the current page.                                              | lea r1, LABEL  |

|                               | (This addressing mode is often referred to as <i>literal mode</i> since the bits in the instruction "literally" are used as data.) |                |

| direct                        | The data is at the specified address on the current page.                                                                          | ld r1, LABEL   |

| indirect                      | The address of the data is contained in the location specified on the current page.                                                | ldi r1, LABEL  |

| base+index                    | Data is at the address formed by adding the zero-extended index (#3 in the example) to the base register (r2 in the example).      | ldr r1, r2, #3 |

Direct addressing is provided in the pgoffset9 field (INST<8:0>) of the LD and ST instructions. The 9 bits directly identify the memory address on the current page. PC<15:9> specifies the current page. Since there are 7 bits to identify the current page, there can be  $2^7 = 128$  pages. A complete 16-bit address is formed by concatenating the page number PC<15:9> and the pgoffset9 (i.e., PC<15:9> @ INST<8:0>). This address is used as the adddress of the 16-bit data element.

The indirect addressing mode allows the contents of a memory location to contain the address of the data element. [You will see when we get to programming in C that this is a very useful concept, and has a special name. That is, a location that contains the address of the data is referred to as a "pointer" because it points to the data.] It is implemented with the LDI and STI instructions. INST<8:0> are used exactly as they are in the direct addressing mode to form an address. However, the resulting address contains the address of the data element to be fetched (in the case of LDI) or stored (in the case of STI).

The base+index addressing mode allows the programmer to specify a memory location as an offset from some particular starting address. The starting address is contained in a base register BaseR. The offset is specified as the index in the instruction. A memory address is formed by adding the contents of the base register with the zero-extended offset. This address is then used for the LDR or STR operation. It is convenient to use the base+index addressing mode to process sequential data structures such as strings, records (e.g. activation records), arrays of structures, etc. Supposing that the base register points to the beginning of an array of items, it must be incremented by the size of each element to traverse through the array. The index can specify a field in each item.

# 2.5. Branching Modes

A branching mode defines the way in which a branch or jump takes place. The LC-2 has two basic modes which are summarized below.

Examples

Meaning

BR LABEL

JSR LABEL

JSR BaseR, index6

The target of the branch or jump is the specified address on the current page.

The target of the jump is the sum of the contents of the register BaseR and the zero-extended 6-bit index encoded in the instruction.

**Table 6: LC-2 branching modes**

Direct branches are provided by the BR and JSR instructions. INST<8:0> directly identify the target address on the current page. PC<15:9> specifies the current page. A complete 16-bit address is formed by concatenating the page number PC<15:9> and the pgoffset9 (that is, PC<15:9> @ INST<8:0>). This is the target address placed into the PC.

Jumps to locations not on the current page can be implemented with the JSRR instruction. The new PC is formed by adding the contents of the BaseR with the 6-bit index.

The L (link) field in the JSR instructions distinguish them from the BR instruction. If L is set (L == 1), the current PC is copied to R7 before the jump takes place. This action forms a *link* to the calling subroutine for a later return. If L is clear (L == 0), the current PC is discarded.

# 2.6. The LC-2 System Calls

The LC-2 provides several trap routines for the programmer's convenience. They are as follows.

**Table 7: LC-2 System Calls**

| Trap<br>Number | Assembler<br>Name | Description                                                                                                                                                                                 |

|----------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$20           | GETC              | Read a single character from the keyboard. The character is not echoed onto the console. Its ASCII code is copied into R0. The high 8 bits of R0 are cleared.                               |

| \$21           | OUT               | Write a character in R0<7:0> to the console.                                                                                                                                                |

| \$22           | PUTS              | Write a string pointed to by R0 to the console.                                                                                                                                             |

| \$23           | IN                | Print a prompt on the screen and read a single character from the keyboard. The character is echoed onto the console, and its ASCII code copied into R0. The high 8 bits of R0 are cleared. |

| \$24           | PUTSP             | Write a packed string pointed to by R0 to the console.                                                                                                                                      |

| \$25           | HALT              | Prints a message on the console and halts execution.                                                                                                                                        |

| Others         |                   | All other trap vectors point to a routine which prints a message on the console indicating that a trap was executed for which no other routine was defined.                                 |

# 2.7. The LC-2 Hardware Registers

Certain memory addresses specify registers which have special meanings to the LC-2.

**Table 8: LC-2 Hardware Registers**

| Location | I/O Register Name          | I/O Register Function                                                                                                                                                      |

|----------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$F3FC   | Video Status Register      | Bit<15>, the ready bit, indicates whether the video device is ready to receive another character to print on the screen. Also known as CRTSR.                              |

| \$F3FD   | Horizontal Screen Position | Not implemented.                                                                                                                                                           |

| \$F3FE   | Vertical Screen Position   | Not implemented.                                                                                                                                                           |

| \$F3FF   | Video Data Register        | A character written in the low byte of this register will be displayed on screen. If the high byte is not 0, it too will be written (packed strings). Also known as CRTDR. |

| \$F400   | Keyboard Status Register   | Bit<15>, the ready bit, indicates whether the keyboard has received a new character. Also known as KBSR.                                                                   |

| \$F401   | Keyboard Data Register     | Bits<7:0> contain the last character typed on the keyboard. Also known as KBDR.                                                                                            |

| \$FFFF   | Machine Control Register   | Bit<15> is the clock enable bit. When cleared, instruction processing stops because the clock signal stops pulsing. Also known as MCR.                                     |

# 2.8. The LC-2 Memory Map

The LC-2's complete 16-bit, 64 KW memory space is shown below. There are  $2^7 = 128$  pages with 512 words each. Memory between \$3000 and \$CFFF (40 KW) is available for user programs. Each block represents two pages.

Figure 1: LC-2 Memory Map

|      | X000-X3FF                     | X400-X7FF                | X800-XBFF             | XC00-XFFF             |

|------|-------------------------------|--------------------------|-----------------------|-----------------------|

| 0000 | Vector Table                  | Operating System Code    | Operating System Code | Operating System Code |

| 1000 | Reserved                      | Reserved                 | Reserved              | Reserved              |

| 2000 | Reserved                      | Reserved                 | Reserved              | Reserved              |

| 3000 |                               |                          |                       |                       |

| 4000 |                               |                          |                       |                       |

| 5000 |                               |                          |                       |                       |

| 6000 |                               |                          |                       |                       |

| 7000 |                               |                          |                       |                       |

| 8000 |                               |                          |                       |                       |

| 9000 |                               |                          |                       |                       |

| A000 |                               |                          |                       |                       |

| B000 |                               |                          |                       |                       |

| C000 |                               |                          |                       |                       |

| D000 | Reserved                      | Reserved                 | Reserved              | Reserved              |

| E000 | Reserved                      | Reserved                 | Reserved              | Reserved              |

| F000 | Video RAM*<br>Video registers | Keyboard<br>System RAM** | System RAM**          | Boot ROM              |

<sup>\*</sup> packed memory: 2 characters are stored in each word

<sup>\*\*</sup> memory mapped I/O devices

# CHAPTER 3 LC-2 Machine- and Assembly-Programming

This chapter discusses programming the LC-2 in machine- and assembly-language.

# 3.1. Introduction to Program Execution in the LC-2

The LC-2's memory is logically laid out in a linear array. Each entry in the array is identified by a unique 16-bit number (its *address*). Each entry contains 16 bits of information.

LC-2 instructions are stored in its memory. Each instruction is 16 bits long. To begin execution of an instruction, the processor first retrieves (*fetches*) the instruction from the memory location which contains the instruction. The instruction is then *decoded* and *executed*.

As part of the execution, many instructions also record whether the result of execution is negative, zero, or positive. This is done by setting or clearing the three corresponding condition codes (N, Z, and P).

After finishing execution, whatever results the instruction produces are recorded, and the next instruction is processed. The processor keeps track of the next instruction with a special register called the *program counter* (PC). The program counter specifies the address from which the next instruction is to be retrieved.

From the programmer's perspective, a *machine instruction* is the most basic operation that a computer can carry out. In the case of the LC-2, there are 16 basic instructions, each 16 bits long, which the processor knows how to execute directly. These include operate instructions (which process information), data movement instructions, and control instructions (which modify the normal sequential flow of the program).

# 3.2. The LC-2 Instruction Encoding

Consider an arbitrary LC-2 instruction which we will call INST. When the LC-2 executes INST, it examines bits <15:12>, the opcode, to figure out what the instruction is telling it to do. For example, the opcode may represent "add." The rest of the bits in the instruction tell the LC-2 what quantities to add and where to put the result.

INST<11:9> usually specifies a destination register or condition codes. The destination register (DR) is specified as 000, 001, 010, 011, 100, 101, 110, or 111, representing registers zero through seven (R0..R7). For instance, if bits  $<15:9> = 1001\ 010$ , the opcode is NOT and the result will be placed into R2.

One exception to this general rule is the st instruction, where INST<11:9> actually specify a *source* register.

In the case of and, add, and not, at least one source register (SR or SR1) is required. It is encoded in bits <8:6>. It is encoded in the same fashion as the DR field.

The add and instructions are different from not in that they need two source operands. It is also convenient to be able to literally specify in the instruction a number to add or and. To accomplish both in the same instruction format, the LC-2 supports the execution of the following instructions:

a) add R0, R1, R2 ; R0 = R1 + R2

b) add R0, R0, #1; R0 = R0 + 1 (increment R0)

c) and R0, R1, R2 ; R0 = R1 & R2

d) and R0, R0, #0 ; R0 = R0 & 0 (clear R0)

To specify a) and c), INST<5> is 0. This indicates that the last 3 bits of the instruction, INST<2:0> are encoded as the second source register (R2 in both cases above). The intervening bits INST<4:3> are 0. To specify b) and d), INST<5> is 1. The remaining 5 bits <4:0> designate a 5 bit number. This number is sign extended to 16 bits, which allows us to use positive as well as negative numbers in the 5-bit immediate field. The allowed values range from -16 to 15.

Some instructions require a nine-bit field which is a page offset. As will be explained shortly, this offset tells the processor where to fetch data from on the current page (defined by the program counter). This page offset field is contained in INST<8:0>.

# 3.3. Condition Codes in the LC-2 Processor

The hardware for an LC-2 computer (or in our case, the simulator) contains three flip flops which retain properties about the results computed by the processor. The flip flops, or more appropriately the signals that they store, are called the *condition codes* of the LC-2. Sometimes condition codes are referred to as *flags*. The instructions that may modify the contents of those flip flops are detailed in the **LC-2 Programmer's Reference Manual**. The three condition codes are described in Table 9.

Table 9: Condition Codes in the LC-2 Processor

| Name | Meaning                                                                                                                                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N    | Set if bit 15 of the instruction result is 1. That is, if the result is <i>negative</i> when interpreted as a two's complement number. Cleared otherwise.    |

| Z    | Set if the instruction result is <i>zero</i> (\$0000). Cleared otherwise.                                                                                    |

| P    | Set if the instruction result is <i>positive</i> , that is, neither negative nor zero. Note that \$0000 is neither positive nor negative. Cleared otherwise. |

### 3.3.1. Condition Field in the Instruction Encoding

To control the flow of a program, branch instructions are used to skip or repeat sequences of instructions. The LC-2 provides several ways to perform such *branches*. The programmer controls the conditions under which a branch may occur by using three bits in the branch instruction encoding which we call the 'nzp' bits. The 3 bits together form the *condition field* of the branch instruction. For the LC-2, these bits may be used in any combination to specify when a branch occurs. Table 10 shows all the combinations.

Table 10: The Possibilities for the Condition Field in the Instruction (nzp)

| nzp | Take the branch                                                                                                                                               |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000 | never                                                                                                                                                         |

| 100 | if N is set (only negative)                                                                                                                                   |

| 010 | if Z is set (only zero)                                                                                                                                       |

| 001 | if P is set (only positive)                                                                                                                                   |

| 110 | if N or Z is set (negative or zero, but not positive)                                                                                                         |

| 011 | if Z or P is set (zero or positive, but not negative)                                                                                                         |

| 101 | if N or P is set (negative or positive, but not zero)                                                                                                         |

| 111 | if any of N, Z, or P are set (after the processor sets the condition codes, at least one bit is always set, so the branch will always be taken <sup>a</sup> ) |

a. Note that upon machine startup, the contents of the condition codes are undefined. Using the condition codes in a branch instruction before setting them results in undefined operation.

### 3.4. Keyboard Input and Console Output

The trap instruction has an 8-bit field INST<7:0> which is a *trap number*. The trap number indexes a table at the start of the LC-2's memory which provides access to special operating system routines.

Two instances of the trap instruction are the in and out operations. To avoid explaining all of the details behind this instruction, we will simply say that it should be used "as is" until a more complete explanation can be given. When an in instruction is reached in a program, program execution stops until a key on the keyboard is pressed. The ASCII representation of the pressed key is placed into the low half of the R0 register and control is returned to the program. The upper half of the R0 register R<15:8>=00000000 after use of the in instruction. The out instruction works similarly. When encountered in a program, the character contained in the low half of R0 is written to the LC-2 console. The upper half of the register R0<15:8> must be 00000000 for the operation to work correctly.

42

<sup>1.</sup> Lectures in class will fully explain this. Bear with us as the textbook for the course is not yet written.

# 3.5. Programming the LC-2 in Machine Language

### 3.5.1. Machine-Language File Formats

An LC-2 program written in machine language is formatt5ed as a sequence of lines, one 16-bit instruction per line. The first line must indicate where the program should be loaded into the LC-2's memory. The load position is usually \$3000 (hex) or 00110000000000000 (binary) for a normal program. The remaining lines are machine instructions or data which will be loaded into contiguous locations of LC-2's memory.

The program can be written in your favorite text editor in bnary notation as in Figure 2. The spaces in the binary representation are for readability only.

Figure 2: The binary representation of an LC-2 program (left) and its equivalent hexadecimal representation (right).

| 0011 | 0000 | 0000 | 0000 | 3000 |

|------|------|------|------|------|

| 1111 | 0000 | 0010 | 0011 | F023 |

| 0001 | 0010 | 0010 | 0000 | 1220 |

| 1111 | 0000 | 0010 | 0011 | F023 |

| 0001 | 0000 | 0000 | 0001 | 1001 |

| 1111 | 0000 | 0010 | 0001 | F021 |

| 1111 | 0000 | 0010 | 0101 | F025 |

The program may also be written as hexadecimal notation (consisting of the characters 0 through 9 and A through F), as on the right of Figure 2.

These listings represent a very simple LC-2 program. To understand what this program does, simply decode each of the instructions using the information from the reference manual. The first line instructs the simulator where to load the program into the LC-2's memory. The second line is an input instruction which reads a character from the keyboard into R0. The third line adds R0 and 0 and places the result into R1 (which effectively copies<sup>2</sup> R0 into R1). The next instruction reads a second character into R0. The fifth line adds R0 and R1 and places the result into R0. The sixth line writes the character in R0 to the console. Finally, the last line is a HALT instruction which stops instruction processing.

LC-2 programs can also be stored in true binary format (*not* like that in Figure 2). This format is nearly impossible to read directly, unlike the textual forms shown above. It is similar to the format in which commercial software is distributed.

Incidentally, the program of Figure 1 is provided in the class examples directory in the file called dumbadd.obj. Try it using the simulator and see what happens.

<sup>2.</sup> This type of copy operation is often called a "move."

A more complicated example is shown in Figure 3.

Figure 3: A more complicated LC-2 program

| Page<br>Address<br>(hex) | Program<br>Hex | Function                                                                                                                                                                                                                                                                                         |  |

|--------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                          | 3000           | Program load address                                                                                                                                                                                                                                                                             |  |

| 000                      | E612           | Load the full address of a buffer at page address \$012 into register R3                                                                                                                                                                                                                         |  |

| 001                      | 54A0           | AND R2 with \$0 (produces \$0) and place result into R2.                                                                                                                                                                                                                                         |  |

| 002                      | F023           | Read a character from the keyboard                                                                                                                                                                                                                                                               |  |

| 003                      | 1236           | Add \$36 to the character read in and place result into R1 This is the same as subtracting \$0A. How? Consider that the value \$36 is sign extended before the addition and remember your two's complement arithmetic. Why? So that we can perform a comparison against the Enter key [newline]. |  |

| 004                      | 8409           | If the last result was zero, branch to location \$009                                                                                                                                                                                                                                            |  |

| 005                      | 70C0           | Store R0 into memory pointed to by R3+0                                                                                                                                                                                                                                                          |  |

| 006                      | 16E1           | Increment R3 (move pointer one word ahead)                                                                                                                                                                                                                                                       |  |

| 007                      | 14A1           | Increment R2 (add 1 to counter)                                                                                                                                                                                                                                                                  |  |

| 008                      | 4802           | Jump to location \$002 on this page                                                                                                                                                                                                                                                              |  |

| 009                      | 16FF           | Decrement the pointer to point to the last character read into the buffer                                                                                                                                                                                                                        |  |

| 00A                      | 5482           | AND R2 with itself and place result into R2. This action is to set the flag bits according to R2 (I am using it specifically for the side effect, just to make sure that the flags are set correctly).                                                                                           |  |

| 00B                      | 8411           | If R2 was zero, branch to location \$010 on this page                                                                                                                                                                                                                                            |  |

| 00C                      | 60C0           | Load a character into R0 from memory pointed to by R3+0                                                                                                                                                                                                                                          |  |

| 00D                      | F021           | Write the character to the console                                                                                                                                                                                                                                                               |  |

| 00E                      | 14BF           | Decrement R2 (subtract 1 from counter)                                                                                                                                                                                                                                                           |  |

| 00F                      | 16FF           | Decrement R3 (move pointer one word backward)                                                                                                                                                                                                                                                    |  |

| 010                      | 480A           | Jump to offset \$0A on this page                                                                                                                                                                                                                                                                 |  |

| 011                      | F025           | HALT service routine                                                                                                                                                                                                                                                                             |  |

Figure 3: A more complicated LC-2 program

| Page<br>Address<br>(hex) | Program<br>Hex | Function                                                          |

|--------------------------|----------------|-------------------------------------------------------------------|

| 012                      | 0000           | The next 10 locations are reserved to hold characters of an input |

| 013                      | 0000           | string.                                                           |

| 014                      | 0000           |                                                                   |

| 015                      | 0000           |                                                                   |

| 016                      | 0000           |                                                                   |

| 017                      | 0000           |                                                                   |

| 018                      | 0000           |                                                                   |

| 019                      | 0000           |                                                                   |