# Introduction to LEON3, GRLIB

Adi Katav

akatav@kaltech.co.il

6201129 4(0) 972+ Ext 101

## Few words about KAL:

- KAL provides professional ASIC consultancy for Digital/Analog ASIC Projects

- Silicon IP services

- Projects

- More info at our web site

## COMPANY INFORMATION

- Located in Gothenburg, Sweden

- Private Company

- Management team with 40 years combined experience in the

#### space sector:

Per Danielsson: CEO

Jiri Gaisler: Founder and CTOSandi Habinc: System Design

14 engineers with expertise within electronics, ASIC and software design

## GAISLER PRODUCT PORTFOLIO

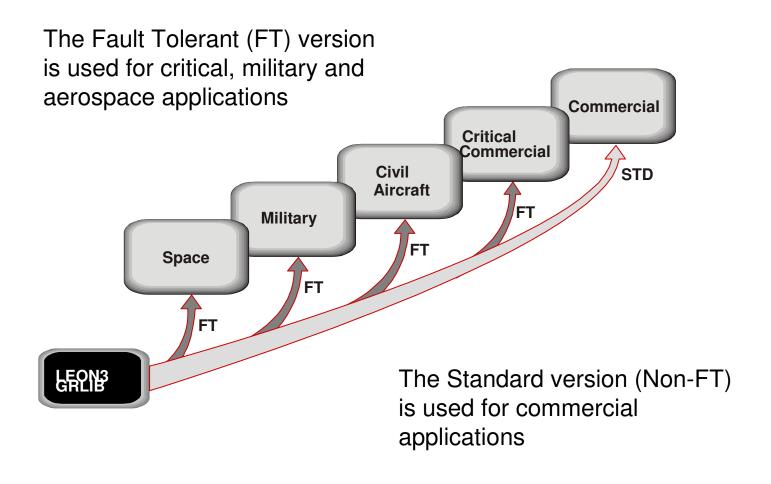

- LEON3 processor, STD/FT

- **LEON** compatible IP-blocks:

- GRFPU, Floating Point Unit

- Memory controllers

- PCI, CAN, USB, I2C, SPI

- 10/100/1000 Mbit Ethernet MAC

- SpaceWire, 1553

- **LEON** development boards

- **Test Systems**

- **Technical support and adaptations**

- Full software development environment based on open source tools

- TSIM, ERC32 and LEON simulator

- GRMON, LEON Debug monitor

- RTOS ports for VxWorks & ThreadX

## LEON3 FEATURES

## Open Source Standard SW Environment

- GNU C/C++ compiler

- RTEMS real-time kernel

- eCos real-time kernel

- SnapGear Linux

## Full Simulator and Debug Monitor

- Simulator for developing and debugging SW

- Monitor for HW and SW validation

#### **High Performance**

- 400 MHz on 0.13 μm ASIC (std-cell))

- 125 MHz on FPGA

### Customer Approval and Validation

- LEON is the standard processor of ESA

- Numerous commercial customers are using LEON

#### **Low Gate Count**

- 25 kgates for ASIC

- 3,500 LUT

- 4.000 Cells

## IP-Library of Cores for SOC Design

- Portable and Vendor independent

- Connection through standard AMBA bus

www.KALtech.co.il

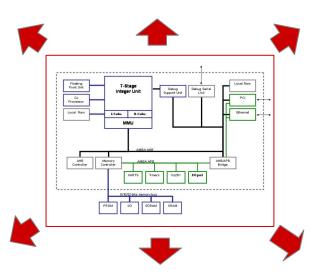

# LEON3 SPARC V8 PROCESSOR

- -7stage pipeline, multi-processor support

- Separate multi-set caches with LRU/LRR/RND

- On-chip debug support unit with trace buffer

- 250/400 MHz on 0.18/0.13 um, 250/400 MIPS, 25

Kgates

- 125 MHz on FPGA, 3500 LUT

- Highly configurable:

- Cache size 1-256 Kbyte, sets 1-4, LRU/LRR Random

- Mul/div options, FPU, MMU

- Pipeline optimisation for specific target technologies

- SEU tolerance by design for space applications, FT version

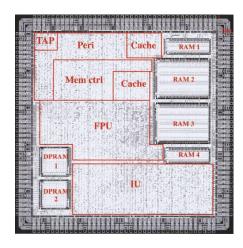

### **GRLIB IP-LIBRARY**

- GRLIB is a complete design environment:

- LEON3 / LEON3-FT

- Floating Point Unit, Mul/Div

- Timers, Interrupt Controller

- Memory controllers (SRAM, SDRAM, DDR)

- SpaceWire, CAN, Ethernet, PS2, UART,

PCI, MIL-STD-1553B, USB 2.0

- CCSDS Telemetry/Telecommand

- AMBA on-chip bus with Plug & Play support

- Support for many tools and prototyping boards

- Support for portability between technologies

## **GRLIB PLUG & PLAY**

- Fully compliant with AMBA 2.0 AHB/APB buses, with additional sideband signals

- Plug&Play information allows for distributed address decoding, interrupt steering, cachability information, etc.

- No modification of centralized resources, e.g. address decoder, arbiter or interrupt controller.

- Automatic generation of table including vendor and device identifier for each attached core, including version and interrupt information.

- Software can scan table and install the corresponding drivers etc.

- Hardware debuggers can use table for initializing

the various IP cores etc.

www.KALtech.co.il

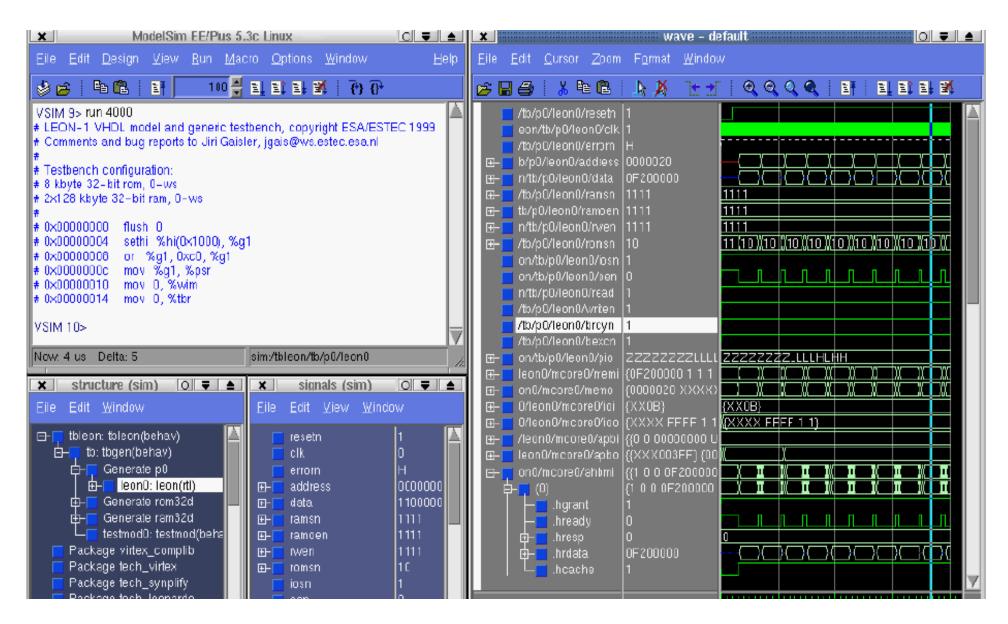

### TSIM SIMULATOR

- Emulates LEON3 system including memory

- Configurable cache size/org., PROM/SRAM size/width

- Break/watchpoints, trace buffer, stack backtrace

- Code coverage, check-pointing, profiling, GDB I/F

- Loadable modules (I/O and AHB) for extension, library version

- 20 MIPS, accuracy better than 5% (1% typical)

- Memory EDAC emulation

- SDRAM support up to 512 Mbyte

- GRFPU timing

- MMU emulation

- Used in many projects (space and consumer) www.KALtech.co.il

## **VHDL Simulation**

## GRGMON

- Debug monitor for LEON2 systems providing non-intrusive debug environment on real target hardware

- Read/write access to all LEON registers and memories

- Download and execution of applications

- Built-in disassembler and trace buffer

- Breakpoint and watchpoint management

- Command-line mode or graphical user interface

- Remote connection to GNU debugger (GDB)

- Supported debug interfaces: PCI, USB, Ethernet, JTAG, UART and SpaceWire

- Used in many projects (space and consumer)

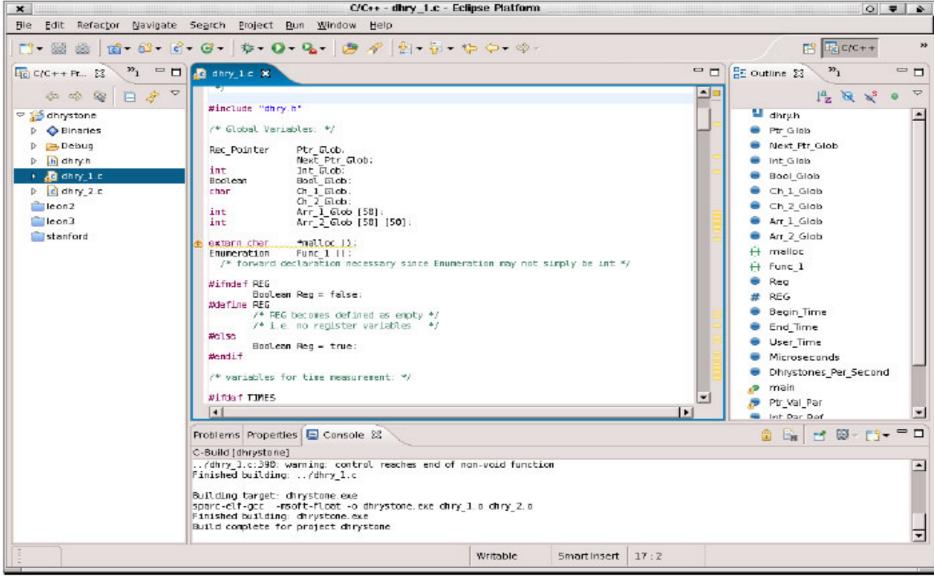

## **Eclipse**

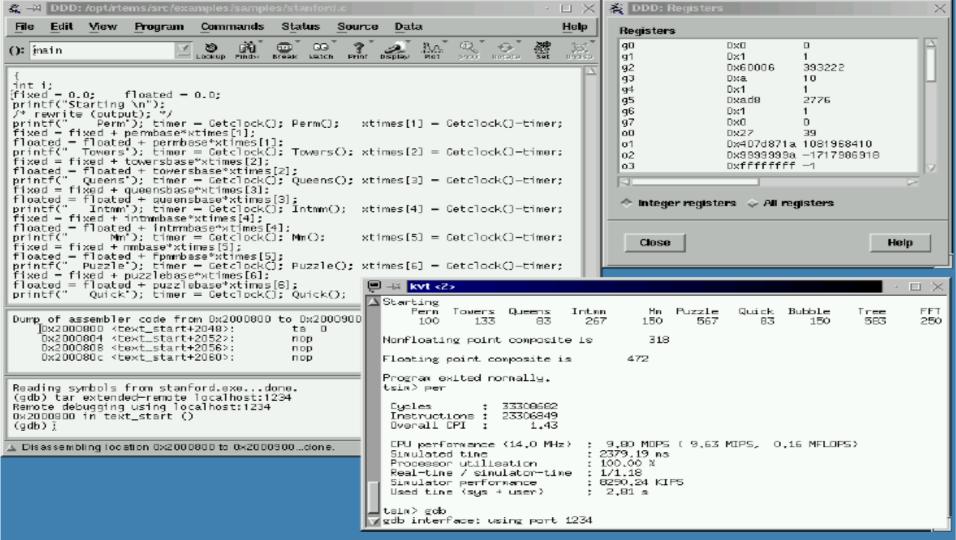

#### GDB/DDD

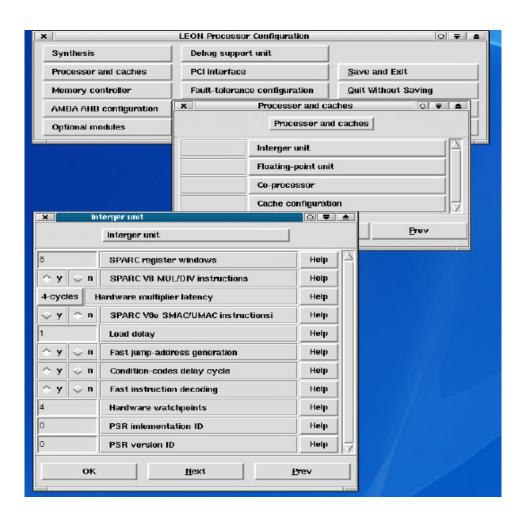

# **GRLIB SOC Config Tool**

## OPERATING SYSTEMS FOR LEON

## Available today

- RTEMS-4.6.5+

- VxWorks 5.4, 6.3, 6.4

- ThreadX

- eCos

- Linux-2.6.21, uClinux-2.0.x

## Under development

- Nucleus

- LynxOS

### RTEMS FOR LEON

- RCC tool-chain, based on RTEMS-4.6.5 with extensions

- Initially ported from ERC32 BSP, maintained by GR

- Updates are being merged with RTEMS CVS (4.8)

- Supports AT697 with standard peripherals and any LEON3FT configuration with plug&play

- GRLIB drivers: GRPCI, GRSPW, CANOC, 1553, GRETH

- New drivers added for RASTA and GR701

- InSilicon-PCI, GRSPW, HCAN, PCI-F

- LAN91C111 Ethernet MAC

#### **VXWORKS FOR LEON**

- Port and BSP available for VxWorks 5.4, 6.3 and 6.4

- Full source code for BSP and port (6.x) provided

- Compiled with DIAB or GCC (VxWorks-5.4)

- LEON2 Drivers:

- standard peripherals, LAN91C111

- Supports MMU in COLE

- GR701 support in development (PCI, SPW, 1553, CAN)

- LEON3 Drivers:

- GRLIB: standard peri. + GRETH, GRSPW, CAN, 1553BRM

- LEON3FT MMU support, LAN91C111

- Workbench support on Linux and Windows hosts

## THREADX FOR LEON

- Popular RTOS for deeply embedded systems

- LEON Port and BSP available for ThreadX-5.0

- Full source code for Kernel, BSP and port provided

- Small foot-print, GCC tool-chain

- Network stack (NetX) under testing

- USB stack (USBX) to be ported Q4-2007

- Has been used by NASA with ERC32 and Mongoose

- NASA Deep Impact Sensor

- Device driver development done by end-user

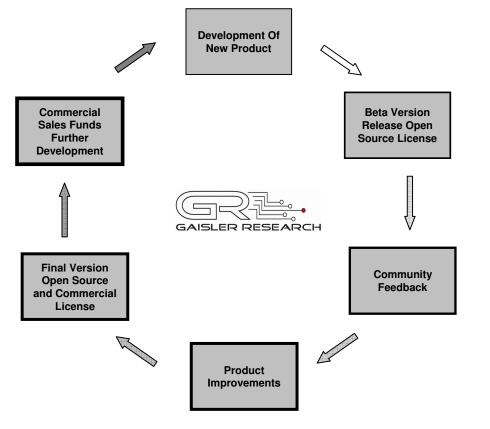

## LICENSING MODEL

Gaisler Research uses an open source business model based on Dual Licensing. Dual licensing allows to provide commercial licenses for a fee, while at the same time offering the source code under open source licenses.

- Free access for the academic research community

- Free evaluation possibilities for companies

- Large user base gives sizable and quick feedback

- Commercial licenses for IP cores to companies not willing to comply with the GPL license

- Commercial licenses for the LEON3 FT IP core library

- Provide technical support and development tools

# MARKET AND APPLICATIONS

## **CUSTOMERS AND APPLICATION**

#### Commercial examples

- GPS receiver

- Set top boxes

- Sensors

- RF-ID

- Printers

- Wireless

- Power transmission

- Video games

#### Space

- All European space companies

- US, China, Canada, Korea, Israel, India, Taiwan

#### Research and Universities

Used by hundreds of universities and research centres around the world

## Other processors vs. Leon

| PRODUCT                          | ARM 9     | ARM 11    | ARC 700 | Xtensa LX | LEON3  |

|----------------------------------|-----------|-----------|---------|-----------|--------|

| Clock frequency<br>(MHz)         | 250       | 400       | 400     | 350       | 400    |

| Pipe-line stages                 | 5         | 8         | 7       | 5         | 7      |

| Gate count                       | 000'100 < | 000'100 < | 000'100 | 000'28    | 000'25 |

| Synthesizable to FPGA            | No        | No        | Yes     | Yes       | Yes    |

| Third party SW development tools | Yes       | Yes       | No      | No        | Yes    |

| Open Source<br>VHDL              | No        | No        | No      | No        | Yes    |

| License Cost                     | High      | High      | Medium  | Medium    | Low    |

Clock frequency: Depends on process and technology, figures are approximate for 0.13 µm process

Gate count: Depends on processor configuration, figures are for bare processor

## **VERIFICATION STATUS**

- LEON3 independently certified by Sparc International

- Verified for space use according to the stringent requirements of the European Space Agency

- Used as reference design in the low power design package

- Used as reference design by major tool vendors: (Synopsis, Synplify, Mentor, Spirit)

- Promoted by Cadence through the open choice programme

- Partnership for military and space FPGA applications

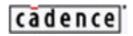

## **LEON3 Multi Processing**

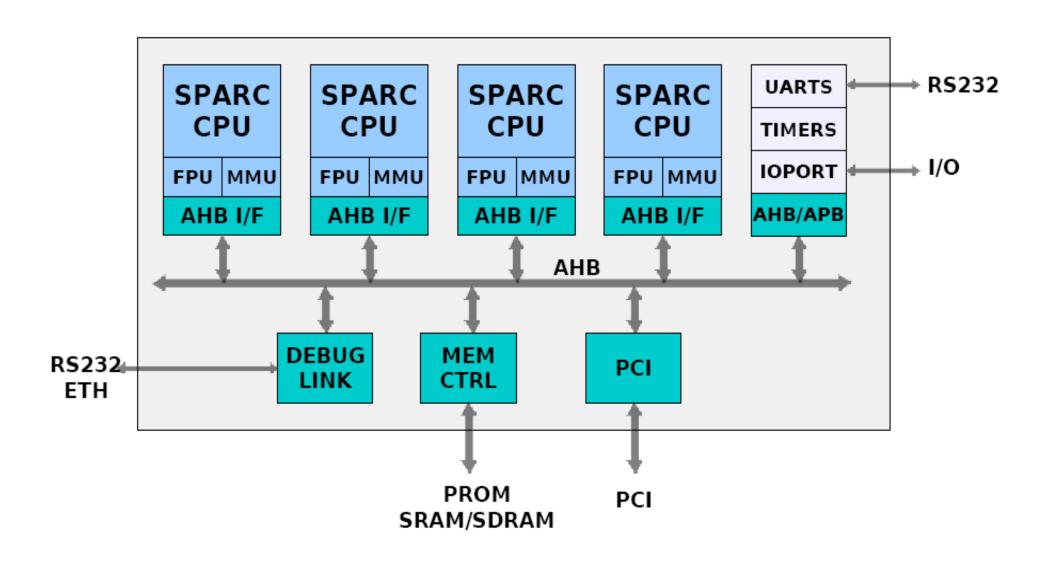

# **Example on the NX750LP**

www.KALtech.co.il