# Speedster22i 10/40/100 Gigabit Ethernet User Guide

UG029 - Jan 20, 2017

## **Copyright Info**

Copyright © 2013, 2014, 2016, 2017 Achronix Semiconductor Corporation. All rights reserved. Achronix is a trademark and Speedster is a registered trademark of Achronix Semiconductor Corporation. All other trademarks are the property of their prospective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, and disclaimers are listed at <u>http://www.achronix.com</u> and use of this document and the Information contained therein is subject to such terms.

## **Table of Contents**

| Copyright Info                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Overview                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |

| Functional Description                                                                                                                                                                                                                                                                                                                    |                                                                                                                      |

| Valid Interface Combinations                                                                                                                                                                                                                                                                                                              | 10                                                                                                                   |

| Detailed Architecture                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

| Ethernet MAC Frame Formats                                                                                                                                                                                                                                                                                                                |                                                                                                                      |

| MAC Receive<br>Preamble processing<br>MAC Address Check<br>Frame Length / Type Field Verification<br>VLAN Frames Processing<br>Pause/PFC Frame Processing<br>CRC Check<br>Frame Padding<br>Frame Truncation<br>RS Layer Fault Handling<br>MAC Transmit<br>Overview<br>Frame Payload Padding<br>MAC Address Overwrite                      | 15<br>16<br>18<br>18<br>18<br>18<br>19<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20 |

| CRC-32 Calculation<br>Preamble Generation and Insertion<br>Inter-Frame Gap                                                                                                                                                                                                                                                                |                                                                                                                      |

| -                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      |

| Interface Signal Descriptions<br>Global Signals<br>Receive FIFO Interface<br>Transmit FIFO Interface<br>PMA TX/RX Interface<br>Priority Flow Control Interface<br>Auto-Negotiation Control and Status<br>Serial Bus Interface<br>SerDes (off-chip) Interface<br>Transmitted Frame Status<br>Timestamp Timer<br>MAC/PCS Status Indications | 25<br>25<br>27<br>29<br>30<br>30<br>31<br>31<br>31<br>31<br>32                                                       |

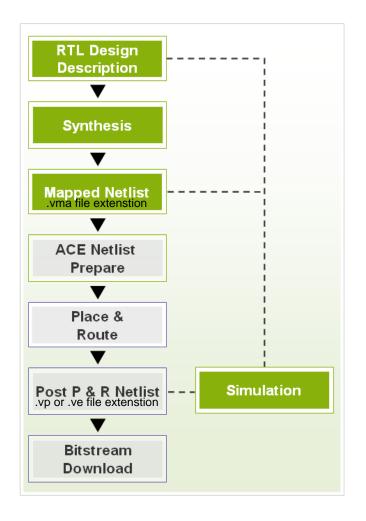

| Implementation with ACE                                                                                                                                                                                                                                                                                                                   |                                                                                                                      |

| •                                                                                                                                                                      | 33       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Creating an Ethernet Instance<br>Configuring the 10/40/100G Ethernet Core<br>FPGA Fabric Interface<br>PHY Interface                                                    |          |

| Interfacing the Ethernet Core to the FPGA Fabric<br>Data<br>Serial Bus Interface                                                                                       | 36       |

| Simulation                                                                                                                                                             | 36       |

| Clock Distribution                                                                                                                                                     | 38       |

| Reset Considerations                                                                                                                                                   | 40       |

| MAC Soft Reset                                                                                                                                                         | 40       |

| FIFO / Credit Counter Reset                                                                                                                                            | 40       |

| PCS Reset                                                                                                                                                              | 40       |

| FPGA I/O Ring Resets<br>MAC_ACX_SYNCHRONIZER_MODE<br>Other Shared Resets                                                                                               | 41       |

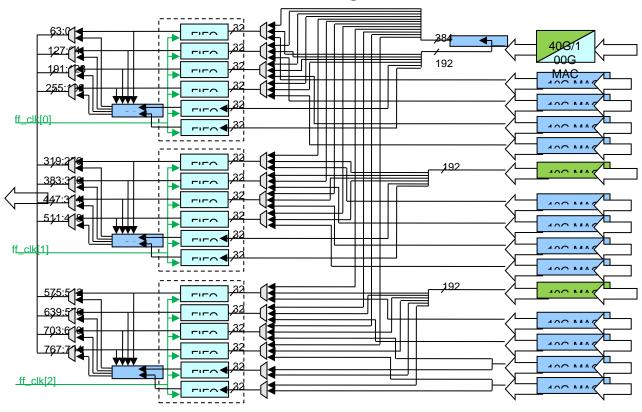

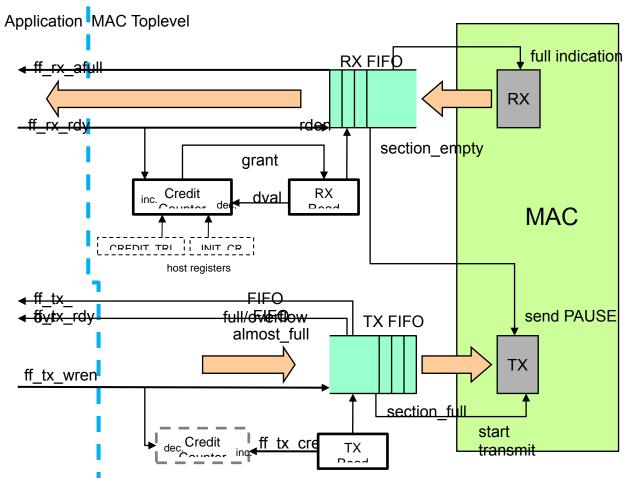

| Fabric FIFO Interface                                                                                                                                                  | 43       |

| Overview<br>Transmit FIFO Interface Block Diagram<br>Receive FIFO Interface Block Diagram                                                                              | 44       |

| Credit Handling<br>Receive Direction: FIFO to Application<br>Transmit Direction: Application to FIFO                                                                   |          |

| Data Structure                                                                                                                                                         |          |

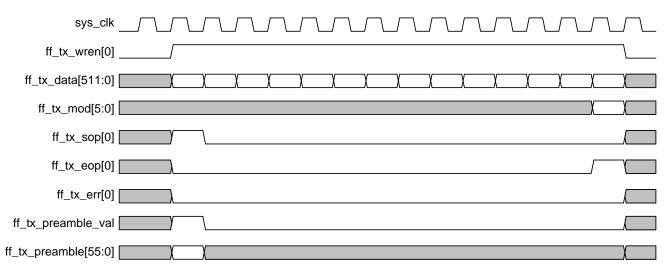

| FIFO Interfece Transmit Operation                                                                                                                                      | 51       |

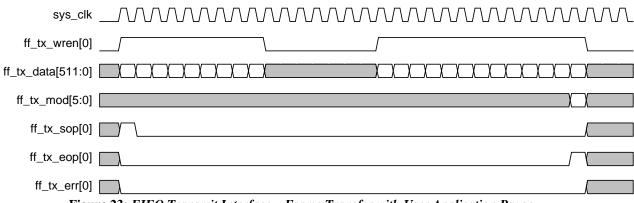

| FIFO Interface Transmit Operation                                                                                                                                      | 53       |

| FIFO Interface Transmit Operation                                                                                                                                      |          |

|                                                                                                                                                                        | 56       |

| FIFO Interface Receive Operation                                                                                                                                       |          |

| FIFO Interface Receive Operation<br>Frame Status<br>FIFO Thresholds                                                                                                    | 57<br>57 |

| FIFO Interface Receive Operation<br>Frame Status<br>FIFO Thresholds<br>FIFO Sections Behavior (Watermarks)                                                             | 57<br>   |

| FIFO Interface Receive Operation<br>Frame Status<br>FIFO Thresholds<br>FIFO Sections Behavior (Watermarks)<br>FIOW Control Interface                                   | 57<br>   |

| FIFO Interface Receive Operation<br>Frame Status<br>FIFO Thresholds<br>FIFO Sections Behavior (Watermarks)<br>Flow Control Interface<br>Link Pause Flow Control Frames | 57<br>   |

| Serial Bus Interface                                             |     |

|------------------------------------------------------------------|-----|

| Overview                                                         |     |

| Port List                                                        |     |

| Read Operation                                                   | -   |

| Write Operation                                                  |     |

|                                                                  |     |

| PMA Management Interface                                         |     |

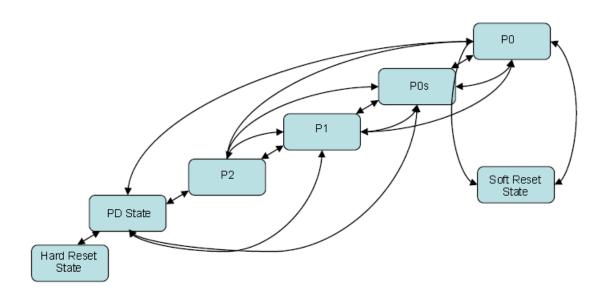

| Power State Descriptions                                         |     |

| Power State Sequencing                                           |     |

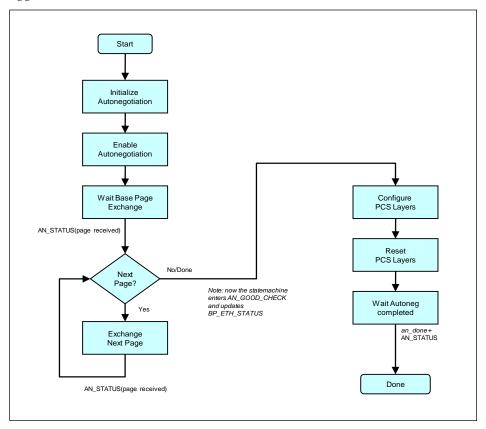

| Auto-Negotiation                                                 |     |

| Overview                                                         |     |

| Usage                                                            |     |

| Usage                                                            |     |

| IEEE 1588 Timestamping                                           |     |

| Receive Timestamping                                             |     |

| Transmit Timestamping                                            |     |

| Registers                                                        |     |

| •                                                                |     |

| MAC & PCS Configuration Registers<br>MAC & PCS Register Overview |     |

| Channelized MAC Registers                                        |     |

| COMMAND_CONFIG Register Bit Definitions                          |     |

| STATUS Register Bit Definitions                                  |     |

| 10G MAC SGMII PCS Register Map<br>1000Base-X / SGMII PCS         |     |

| Global Registers                                                 |     |

| Channelized PCS Registers                                        |     |

| Auto-Negotiation Registers                                       |     |

| PMA Registers                                                    |     |

| PMA State Control<br>PMA Receive Equalization Registers          |     |

| PMA Transmit Control Registers                                   |     |

| PMA Adaptive Equalizer Registers                                 |     |

| Statistics Data Registers                                        | 114 |

| Overview                                                         |     |

| IEEE 802.3 Management Package                                    |     |

| IETF Management Information Base (MIB, MIB-II) Objects           |     |

| IETF Remote Network Monitoring<br>Receive Statistics Vector      |     |

| Transmit Statistics Vector                                       |     |

| References                                                       |     |

| <b>Revision History</b> | ۲۲ . | 120 |

|-------------------------|------|-----|

|-------------------------|------|-----|

## **Table of Figures**

The hardened 10/40/100 Gigabit Ethernet controller available in Achronix Speedster22i FPGAs provides a flexible, high-performance, and power efficient networking interface.

The features include:

- Fully integrated 10/40/100 Gigabit Ethernet MAC

- Designed to the IEEE Std 802.3ba-2010 specification

- Configurable full-duplex for 10/40/100 Gigabit Ethernet operation

- 5 configurable modes of operation

- o 1-12 x 10 Gigabit Ethernet Channels

- o 1 x 100 Gigabit, 1-2 x 10 Gigabit Ethernet Channels

- 1-3 x 40 Gigabit Ethernet Channels

- 1-4 x 10 Gigabit, 1-2 x 40 Gigabit Ethernet Channels

- 1-8 x 10 Gigabit, 1 x 40 Gigabit Ethernet Channels

- User-accessible raw statistic vector outputs (IEEE 802.3 basic, mandatory and recommended Management Information packages (clause 30, MIB, MIB-II, IETF RFC 2665, SNMP, RMON in accordance with IETF RFC 2819))

- Provides counters to generate the applicable objects of the Management Information Base (MIB, MIB-II) according to IETF RFC 2665 (including its update to 10 Gbps) for SNMP (Simple Network Management Protocol) managed environments.

- Support for VLAN 802.1q VLAN Tag (VLAN Type and VLAN Info fields) frames

- Configurable in-band Frame Check Sequence (FCS) field passing on both transmit and receive paths

- Auto padding on transmit and stripping on receive paths

- Configured and monitored through a host interface

- Each PCS Layer implements a X/XL/CGMII side loopback to the MAC, which returns all data from the MAC transmit back to the MAC receive side without passing through any the PCS blocks.

- 10G Base-R: The PCS transmits the constant pattern of 0x00ff to the SerDes line interface.

- 40G/100G Base-R: The PCS transmits the MAC transmit data unchanged to the SerDes line interface (as defined by IEEE802.3ba).

- Hardware-selectable Device Control Register (DCR) bus or generic host bus interface

- Configurable flow control through Ethernet MAC Control PAUSE frames; symmetrically or asymmetrically enabled

- Configurable support for jumbo frames of any length

- Each PCS layer implements auto-negotiation, but does not include Parallel Detection. Parallel Detection must be implemented in user logic when the remote device does not support auto-negotiation or when auto-negotiation is disabled.

- When operating in 10G mode of operation, the 10G MAC can implement a configurable 10/100/1000 SGMII/1000Base-X PCS layer instead of the normal XGMII/10GBase-R PCS layer to allow operations below 10Gbps.

- Fully configurable Inter-Packet Gap (IPG) supports LAN and WAN with support for Deficit Idle Count (DIC) to reduce bandwidth loss. Configurable in full-duplex operation

- Optional Frame Check Sequence (FCS) checking (add and delete)

- PCS Lane Marker Insertion and deletion..

- MAC support for Link Pause Flow Control and Priority Flow Control (PFC) enables prioritization of up to 8 traffic classes.

- PCS layer timestamp support enables IEEE 1588 precision time protocol.

*Note: There are restrictions on which interface (10/40/100) can occupy which SerDes Lanes. See Valid Interface Combinations below.*

## **Functional Description**

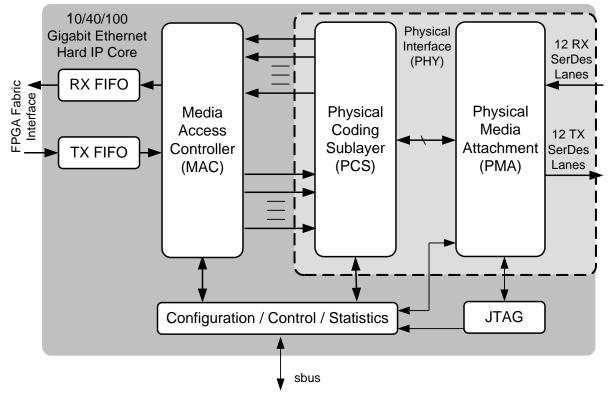

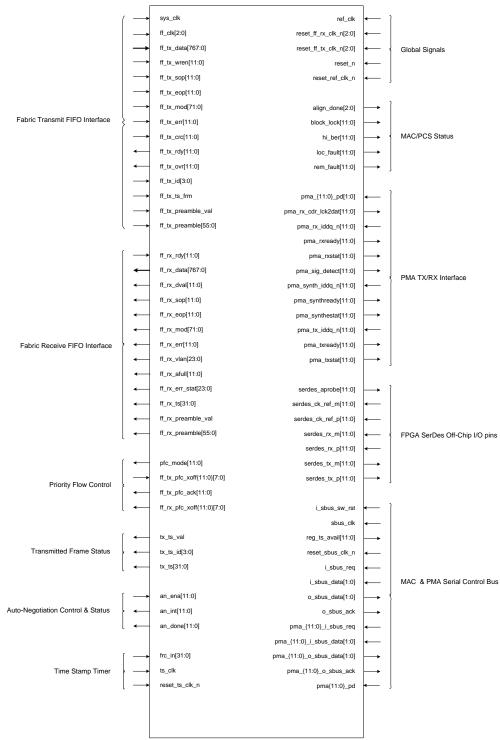

The block diagram for the 10/40/100 Gigabit Ethernet MAC and how it connects to the PHY is shown below.

Figure 1: 10/40/100 Gigabit Ethernet Block Diagram

On the FPGA Fabric interface, the 10/40/100 Gigabit Ethernet MAC and PCS Core implements a flexible FIFO interface that can be connected to a custom user application.

On the Ethernet line side, the Ethernet Core implements a 12 x 20-Bit line interface to the Physical Media Attachment (PMA) module which consists of 12 x 10G SerDes lanes directly connected to the FPGA I/O pins. The 12 SerDes lanes in the PMA module can be utilized independently of the 10/40/100G Ethernet MAC if the MAC IP is not being used. The physical interface between the MAC and SerDes is configured via the 10/40/100G Ethernet MAC IP configuration wizard. Details of the Achronix SerDes I/O are beyond the scope of the user guide. A separate user guide is available for the SerDes I/O functionality.

#### Valid Interface Combinations

The valid mapping of interfaces (10/40/100) onto SerDes Lanes is:

- 12 x 10G (lanes 0-11)

- 1 x 100G (lanes 0-9) 2x10 (lanes 10-11)

- 3 x 40G (lanes 0, 4, 8)

- 4 x 10G (lanes 0-3) 2x40G (lanes 4,8)

- 8 x 10G (lanes 0-7) 1x40G (lane 8)

For each of these configurations a subset may be used. i.e. you can have a 100G on lane 09 without 10G on lanes 10-11, likewise you can have a single 40G interface lane 0-3, 4-7 or 8-11, with the other lanes not occupied. (etc.)

## **Detailed Architecture**

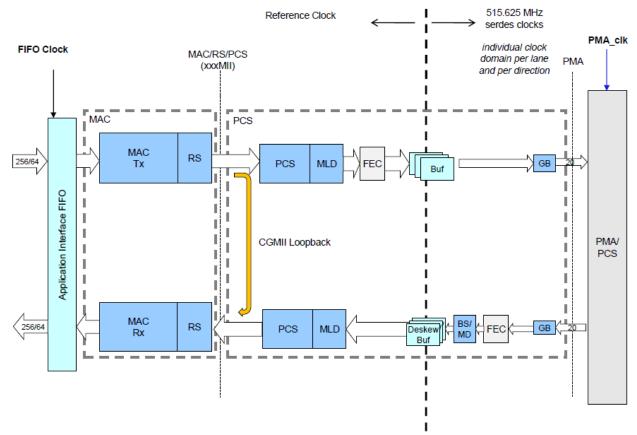

The figure below shows the internal architecture of the MAC block.

Figure 2 – Ethernet MAC Details

#### X/XL/CGMII Loopbacks

Each PCS Layer implements a X/XL/CGMII side loopback to the MAC, which returns all data from the MAC transmit back to the MAC receive side without passing through any of the PCS blocks.

When the loopback is enabled the transmitted data is treated depending on the mode of operation as follows:

- 10G Base-R: The PCS transmits the constant pattern of 0x00ff (8x'1' bits alternating with 8x'0' bits) to the SerDes line interface.

- 40G/100G Base-R: The PCS transmits the MAC transmit data unchanged to the SerDes line interface (as defined by IEEE802.3ba).

## **Ethernet MAC Frame Formats**

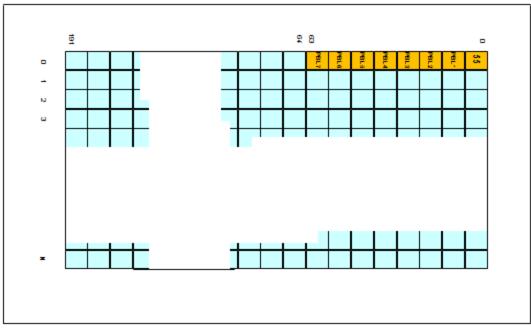

The IEEE 802.3 Standard defines the Ethernet Frame Format as follows: An Ethernet frame has a minimum length of 64 bytes and a maximum length of 1518 bytes, excluding the preamble and the SFD bytes. An Ethernet frame consists of the following fields:

- Seven bytes preamble

- Start frame delimiter (SFD)

- Two address fields

- Length or Type field

- Data field

- Frame check sequence (CRC value)

|              |          | 7 octets          | PREAMBLE             | T   |

|--------------|----------|-------------------|----------------------|-----|

|              |          | 1 octet           | SFD                  | Ţ   |

|              | (        | 6 octets          | DESTINATION ADDRESS  | Ţ   |

|              | 6 octets | SOURCE ADDRESS    | Ţ                    |     |

|              | 2 octets | LENGTH/TYPE       | Payload length       |     |

| Frame length | 1        | 01500/9000 octets | PAYLOAD DATA         | ]}₊ |

|              | 04       | 046 octets        | PAD                  |     |

|              | l        | 4 octets          | FRAME CHECK SEQUENCE | Ι   |

Figure 3 MAC Frame Format Overview

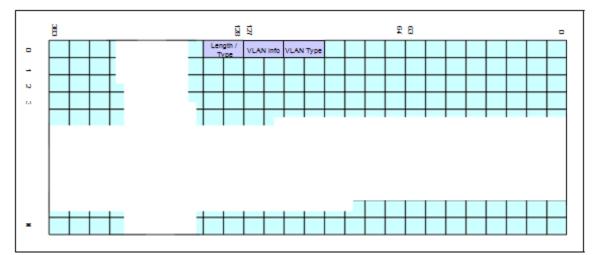

Optionally MAC frames can be VLAN tagged with an additional 4-Byte field (VLAN Tag and VLAN Info) inserted between the MAC Source Address and the Length/Type Field. VLAN tagging is defined by the IEEE P802.1q specification. VLAN tagged frames have a maximum length of 1522 bytes, excluding the preamble and the SFD bytes.

|              |          | Zastata           | DDCAMPLE             | 7                 |

|--------------|----------|-------------------|----------------------|-------------------|

|              |          | 7 octets          | PREAMBLE             | 4                 |

|              |          | 1 octet           | SFD                  |                   |

|              | (        | 6 octets          | DESTINATION ADDRESS  |                   |

|              |          | 6 octets          | SOURCE ADDRESS       |                   |

| Frame length | 2 octe   | 2 octets          | VLAN Tag (0x8100)    | length/type field |

|              |          | 2 octets          | VLAN info            |                   |

|              | 2 octets | LENGTH/TYPE       | Payload length       |                   |

|              |          | 01500/9000 octets | PAYLOAD DATA         | _}₊_              |

|              |          | 042 octets        | PAD                  |                   |

|              | L        | 4 octets          | FRAME CHECK SEQUENCE |                   |

Figure 4 VLAN Tagged MAC Frame Format Overview

| Term                              | Description                                                                                                                                                                                                              |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                   | The length, in octets, defines the length of the complete Frame without<br>preamble and SFD. Legal sizes are:                                                                                                            |  |  |

|                                   | <ul> <li>Standard Ethernet Frame: 64 1518 (payload 01500)</li> </ul>                                                                                                                                                     |  |  |

| Frame Length                      | <ul> <li>Jumbo Frame: 64 9022 (Payload 09000)</li> </ul>                                                                                                                                                                 |  |  |

|                                   | <ul> <li>VLAN Frame: 64 1522 (Payload 01500)</li> </ul>                                                                                                                                                                  |  |  |

|                                   | <ul> <li>Pause and PFC Frame: always 64</li> </ul>                                                                                                                                                                       |  |  |

| Payload Length                    | If the length / type field value is <0x600 it indicates a length information for the<br>frame's payload section. Otherwise the field is interpreted as a type.                                                           |  |  |

| Destination and<br>Source Address | 48-Bit MAC addresses. The least significant byte is sent/received first and the two first bits (Two Least Significant bits) of the MAC address are used to distinguish MAC frames as detailed in chapter 5.2 on page 23. |  |  |

#### Note:

Although the IEEE specification defines a maximum frame length, the MAC Core provides the flexibility to program any value for the Frame maximum length for example to support non-standard Jumbo frames.

Figure 5 MAC Frame Definition

## **MAC Receive**

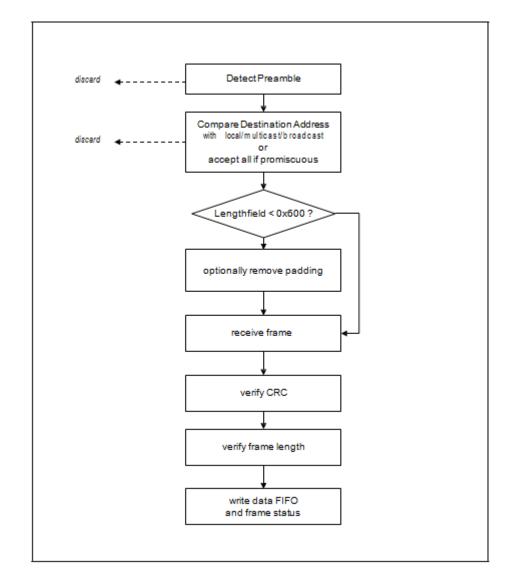

The MAC receive engine performs the following tasks:

- Check Frame Framing

- Remove Frame preamble and Frame SFD field

- Frame Discarding based on Frame Destination address field if not in promiscuous mode

- Process Pause and PFC Frames

- Check Frame Length

- Calculate and verify CRC-32

- Write received Frames in the Core Receive FIFO

**Figure 6: Receive Operation**

#### Preamble processing

The RS Layer removes all the preamble bytes and the SFD byte.

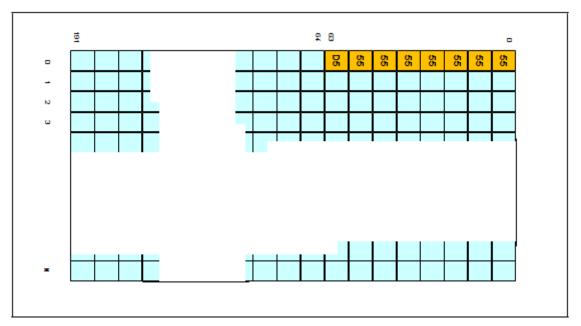

Although the IEEE standard specifies that Frames should be separated by at least 96-Bit times (Inter Packet Gap or IPG), the IEEE standard also specifies the optional Deficit Idle Count (DIC) mechanism that allows to optimize the IPG between 5 to 19 octets and 5 to 15 octets for 40/100G and 10G respectively. Hence, for 40/100G the next 64-Bit block following the final 64-Bit block of a frame can already contain a new preamble. For 10G a minimum of one XGMII column (4 octets) of IDLE must be present in between two frames.

Figure 7: Preamble and SFD Field Position (40/100G RS Layer)

Note that the PCS sub-layer (both 10G and 40/100G) cannot encode a Terminate and Start control character within the same 66-Bit block, therefore it is never possible to receive a preamble starting within the same 64-Bit block that contained the last data bits of a previous frame.

#### User Programmable Preamble Processing

If the Core is configured to insert and extract User specific non-standard preambles (synthesis option), the seven bytes (PBL1 to PBL7 in Figure 9) following the start control code are extracted from the Frame, stored with the frame data and then provided on the Client interface, along with the Frame data (PBL1 is provided in ff\_rx\_preamble(7:0)). Since the first byte of the preamble is converted from the CGMII Start control character (0xFB) to 0x55, it is considered not significant and is not extracted.

Figure 8: User Specific Preamble (40/100G RS Layer)

#### **MAC Address Check**

#### Overview

The destination address bit 0 is used to differentiate Multicast and Unicast Addresses: If bit 0 is set to "0", the MAC address is an individual address (Unicast Address).

If bit 0 is set to "1", the MAC address defines a group address (Multicast Address). If all 48 bits of the MAC address are set to '1', it indicates a broadcast address.

After reconciliation and preamble processing, the destination MAC address is available as the first 6 Bytes beginning at byte 0 of the first word forwarded to the MAC layer and eventually the client application.

#### Unicast Address Check

When used in non-promiscuous mode (Configuration register PROMIS\_EN set to "0"), when a Unicast frame is received, the frame destination MAC address is compared against the MAC address programmed in the Core registers MAC\_ADDR\_0 and MAC\_ADDR\_1. If the destination address matches the programmed MAC address, the frame is accepted; if the destination address does not match the programmed MAC address, the frame is rejected

If promiscuous mode is enabled (Configuration register PROMIS\_EN set to "1"), no address check is performed and the MAC Core accepts all Unicast frames.

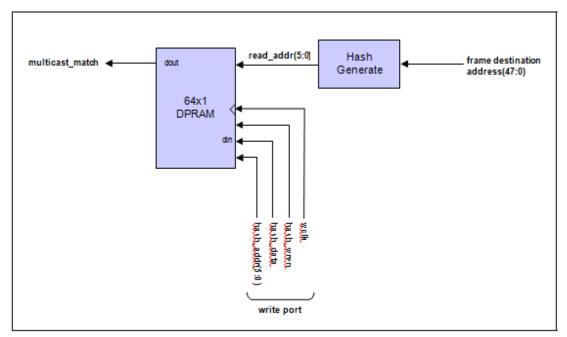

#### Multicast Address Resolution

Multicast addresses are, in typical implementations, resolved using a software task running on the system host processor. While the Multicast address resolution generates acceptable processor load for 10Mbps or 100Mbps Ethernet connections, with Multi-Gigabit Ethernet connections, this task can significantly load the host processor. To reduce processing load

from the host processor, the MAC Core implements a hardware Multicast address resolution engine.

A 64-entries table (Hash Table) is calculated and written by the host processor into a 64x1 look- up-table (DPRAM). When a Multicast frame is received, the MAC address decoding

#### Figure 9: Multicast Address Resolution Overview

*Note:* Each look-up-table entry is typically set to 0x00 after power-up and all Multicast frames are then subsequently rejected until the hash table is programmed.

To build the hash table, the host processor generates a 6-Bit code for each Multicast address by XOR "ing the MAC address bits as detailed in Table 3. The code is used to address the look- up-table. For each code (look-up address), writing a "1" indicates that all the multicast MAC addresses represented by the code should be accepted. Writing a '0' indicates that all the multicast MAC addresses represented by the code should be rejected.

#### Table 1 – Hash bits

| Hash Code Bit | Value                                             |  |

|---------------|---------------------------------------------------|--|

| 0             | XOR multicast MAC address bits 7:0 (first octet)  |  |

| 1             | XOR multicast MAC address bits 15:8               |  |

| 2             | XOR multicast MAC address bits 23:16              |  |

| 3             | XOR multicast MAC address bits 31:24              |  |

| 4             | XOR multicast MAC address bits 39:32              |  |

| 5             | XOR multicast MAC address bits 47:40 (last octet) |  |

If promiscuous mode is enabled (Configuration register PROMIS\_EN is set to ",1"), all Multicast frames are accepted.

#### **Broadcast Frames**

The Core always accepts frames with the destination MAC address set to the Broadcast address.

#### Frame Length / Type Field Verification

After reconciliation and preamble processing, the Length / Type field is located at byte offset 12 and 13 from a 16-Byte boundary within the MAC datapath word. The most-significant byte is byte 12 and the least-significant byte is byte 13.

If the Length / Type field has a value less than 1536 (0x0600), then the Core checks the payload length and reports any error in the frame status word (Bit '0' of Core signal ff\_rx\_err\_stat). If the Length / Type field has a value greater than 1535, then the Core interprets the field as a type and forwards the frame to the user application.

Control and VLAN frames (Type 0x8808 and 0x8100, respectively) are processed by the Core as described in the following two sections ("5.4" and "5.5").

## **VLAN Frames Processing**

Figure 10: VLAN Tagged Frame

#### **Pause/PFC Frame Processing**

Depending on the setting of COMMAND\_CONFIG(PFC\_MODE), either Pause frames or PFC frames are processed by the MAC Core. Only one mode can be active at a time: If a frame of the other mode is received it is treated as a regular command frame. Depending on COMMAND\_CONFIG(CMD\_FRM\_ENA) it is then either discarded or forwarded to the user application but has no effect within the MAC. See 9 page 48 for more details.

Pause frames are optionally terminated in the Core receive engine if the Core configuration register PAUSE\_FWD is set to '0' (default). Pause frames can also optionally be transferred to the receive FIFO interface if the Core configuration register PAUSE\_FWD is set to '1'.

If the configuration register PAUSE\_IGNORE is set to '0', the Quanta is extracted from the terminated Pause frame and sent to the MAC transmit path via a small internal clock decoupling logic. If a CRC or a length error is detected, the Quanta is ignored.

If the Core configuration register PAUSE\_IGNORE is set to '1', the Quanta is not extracted from the received Pause frames.

#### Table 2 – Pause/PFC Control Register

| Register      |           | Description                                                                                                                                                                                  |

|---------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLEASE_IGNORE | PAUSE_FWD | Description                                                                                                                                                                                  |

| 0             | 1         | <ul> <li>Pause frames terminated.</li> <li>Quanta extracted and sent to the<br/>Core transmit path.</li> <li>Pause frames not transferred to the<br/>Core FIFO interface.</li> </ul>         |

| 0             | 1         | <ul> <li>Pause Frames not terminated.</li> <li>Quanta extracted and sent to the<br/>Core transmit path. Pause frames<br/>transferred to the Core FIFO<br/>interface.</li> </ul>              |

| 1             | 0         | <ul> <li>Pause frames terminated.</li> <li>Quanta not extracted and not sent to<br/>the Core transmit path.</li> <li>Pause frames not transferred to the<br/>Core FIFO interface.</li> </ul> |

| 1             | 1         | <ul> <li>Pause Frames not terminated.</li> <li>Quanta not extracted and not sent to the Core transmit path.</li> <li>Pause frames transferred to the Core FIFO interface.</li> </ul>         |

When a Pause frame is received, the statistics counter (aPAUSEMACCtrlFramesReceived) is always incremented, independent from pause ignore or pause forward functions.

A Pause frame is considered valid only, if the following conditions are valid: Length / Type field is set to 0x8808

Opcode field, which is immediately following the Type, is 0x0001 (Pause) or 0x0101 (PFC)

MAC destination address is either the configured Unicast address (programmed in the Core registers MAC\_ADDR\_0 and MAC\_ADDR\_1) or the control frame Multicast address 01-80-c2-00-00-01

- the frame has a valid CRC

- the frame has a length of 64 octets

If any of the first three conditions fails (type, opcode, address), the frame is forwarded to the Client and the MAC takes no further action.

If a Pause frame is not 64 octets in length, it is ignored, even if all other conditions are valid. Depending on the pause-forwarding configuration setting (configuration register bit PAUSE\_FWD), such a frame is either discarded or forwarded to the user application.

#### **CRC Check**

The CRC-32 field is always checked and can optionally be discarded or forwarded to the Core FIFO interface if the Core configuration register bits CRC\_FWD and PAD\_EN are set to '1' and '0', respectively. The CRC polynomial, as specified in the IEEE 802.3 standard, is:

FCS(X) = X32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 + X8 + X7 + X5 + X4 + X2 + X1 + 1

The 32 bits of the CRC value are placed in the FCS field so that the X31 term is the right-most bit of the first octet. The CRC bits are thus received in the following order: X31, X30, ..., X1, X0.

If a CRC-32 error is detected, the frame is marked invalid and Bit '1' of the frame status word (Core signal ff\_rx\_err\_stat) indicating a CRC error is set to "1".

#### **Frame Padding**

When a frame is received with a payload length less than 46 Bytes (42 Bytes for VLAN tagged frames), the padding octets are written into the receive FIFO (i.e. no stripping occurs).

This is always the case for the 40/100G MAC datapath. The 10G MAC can optionally be configured to remove the padding octets when the CRC should be removed and the length field shows a value < 46.

#### **Frame Truncation**

In receive, the MAC is always checking the received frame length (total octets following the preamble and SFD) against the configured FRM\_LENGTH value. If the frame exceeds the programmed value, the frame is truncated and provided to the user application with a length error status (see 7.6 page 43).

When frame truncation happens, the receive FIFO write may stop prior to the actual truncation point. Hence the frame delivered to the client application can be shorter than the given FRM\_LENGTH, but the truncation is always executed only when the limit is reached exactly. In addition, the last octets of a truncated frame can contain arbitrary data.

Another cause of frame truncation can be a receive FIFO almost full condition during reception, which is reported accordingly in the frame's receive status.

#### **RS Layer Fault Handling**

#### Standard Fault Handling Behavior

When the RS Layer detects a fault sequence on it's receive interface, the transmitter is instructed to abort transmission, possibly truncating an outgoing frame. When a local fault sequence (9c-00- 00-01) is detected, the transmitter is instructed to permanently transmit remote fault sequences. When remote fault sequence (9c-00-00-02) is detected, the transmitter permanently transmits idle.

When a fault is reported by the RS receive, the MAC stops serving the transmit FIFO until the fault situation clears.

The fault status is indicated with the toplevel pins loc\_fault/rem\_fault for local and remote fault respectively. In addition, the MAC's STATUS register (see Table 29 page 77) provides latched information of fault occurrences.

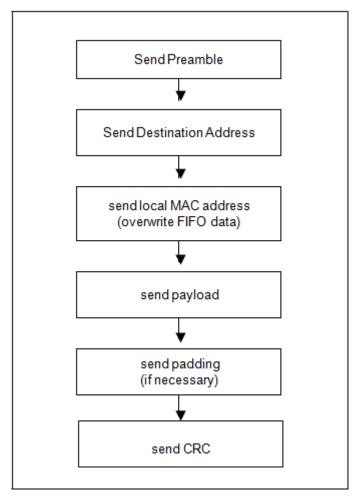

## **MAC Transmit**

#### Overview

Ethernet Frame transmission starts when the Transmit FIFO holds enough data or a pause condition should be reported to the remote (pause frame trigger event). Once a transfer has started, the transmit engine performs the following tasks:

- Generate Preamble and SFD field before Frame transmission

- Optional, when in Link Pause Mode, generate Pause frames if the receive FIFO reports a congestion or if the pause generation pin ff\_tx\_pfc\_xoff(0) is asserted

- When in PFC Mode, generate PFC frames if the pause generation pins

- ff\_tx\_pfc\_xoff(7:0) are asserted

- When in Link Pause Mode, suspend Ethernet Frame transfer (XOFF) if a non zero Pause Quanta is received from the MAC receive path (optional)

- Overwrite MAC source address (optional)

Figure 11 – MAC Transmit Overview

#### Frame Payload Padding

The IEEE specification defines a minimum frame length of 64 Bytes. It is the responsibility of the application to ensure frames with at least 60 octets if CRC should be appended, or 64 octets if it includes CRC, are written into the transmit FIFO.

If shorter frames are provided, they are padded automatically by the MAC to the minimum size of 60 octets before CRC. This will lead to correct minimum sized frames only if the MAC is instructed to append CRC (i.e. ff\_tx\_crc, is asserted). Otherwise the MAC may transmit a corrupt (short) frame.

Note that padding can append arbitrary data to the frame.

#### **MAC Address Overwrite**

On each frame transferred from the Core transmit FIFO interface, the source MAC address is optionally replaced by the address programmed on the configuration registers MAC\_ADDR\_0 and MAC\_ADDR\_1 (if COMMAND\_CONFIG(TX\_ADDR\_INS) set to '1') or is transparently forwarded to the Ethernet line (COMMAND\_CONFIG(TX\_ADDR\_INS) set to '0').

#### **CRC-32 Calculation**

The CRC-32 field is optionally generated and appended at the end of a frame if the frame is transmitted to the Core with the frame status bit ff\_tx\_crc set to '1'.

The CRC polynomial, as specified in the IEEE 802.3 standard, is:

FCS(X) = X32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 + X8 + X7 + X5 + X4 + X2 + X1 + 1

The 32 bits of the CRC value are placed in the FCS field so that the X31 term is the right-most bit of the first octet. The CRC bits are thus transmitted in the following order: X31, X30, ..., X1, X0.

#### **Preamble Generation and Insertion**

If the Core is configured to insert and extract User specific non-standard preambles, the Core inserts the preamble provided on the Core pins ff\_tx\_preamble(55:0) and adds a character in front to form the 8-Byte preamble block. The Reconciliation Sub-Layer eventually replaces that added character with the XGMII/CGMII Start control character. The first byte transmitted following the start character is ff\_tx\_preamble(7:0).

Note: Custom preambles are available for 10G modes or above only. When operating in 1G/SGMII the default preamble/SFD must be set always.

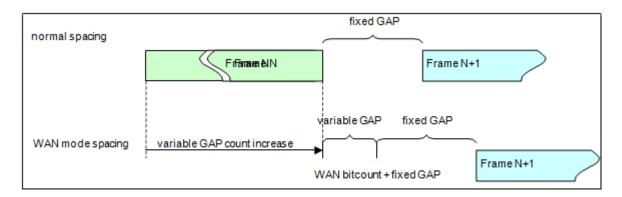

#### **Inter-Frame Gap**

#### Fixed Frame Gap and Deficit Idle Counter (DIC)

The IEEE standard specifies that between frames an inter-packet gap (IPG) of 96-Bit times (12 octets) is inserted. In addition, the frame Start character must always be aligned to an 8-Byte boundary (40/100G) or 4-Byte boundary (10G), starting with Lane 0.

To maintain the full throughput on the Ethernet line, the IEEE standard also specifies the optional Deficit Idle Count (DIC) mechanism. With DIC, the IPG can be optimized between 5

and 19 octets for 40/100G or 5 to 15 octets for 10G, to keep an average IPG of 12 octets and maintain the nominal maximum data rate.

The DIC mechanism sometimes inserts and deletes Idle characters to align the Start control character to a lane 0 boundary. The TX maintains a Deficit Idle Counter that represents the cumulative count of Idle characters deleted or inserted. The DIC is incremented for each Idle character deleted, decremented for each Idle character inserted, and the decision of whether to insert or delete Idle characters is constrained by bounding the DIC to a minimum value of zero and maximum value of 7 for 40/100G and 3 for 10G.

#### WAN Mode Variable Inter Frame Gap

For the 10G MAC only, a special WAN mode is available (see COMMAND\_CONFIG). In WAN mode, and to get an average bandwidth of 9.95328Gbps compatible with OC-192c streams, the MAC Core constantly adapts the gap between Frames. As for the LAN Mode, the minimum gap is 96-Bit time (Fixed Gap in "Figure 13") and the gap increases with the number of bits transmitted on the line.

The 96 bit-time (12 octets) gap is increased by one 8 bit-time (octet) for every 104 bits transmitted on the line. For example when a 64-Byte Frame is transmitted, the minimum gap with the next Frame is 19 octets (12 Fixed Gap + 7 Dynamic Gap calculated from the Frame length).

Additional gap is introduced to align the start-of-frame control character being sent always on the XGMII interface Lane 0. The DIC mechanism (see above) is used to compensate for adding too much IPG due to the lane 0 alignment.

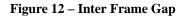

## **Interface Signal List**

Figure 13: Interface Signal List

## **Global Signals**

Table 3 – Global Signals

| Signal Name            | Mode | Description                                                                     |

|------------------------|------|---------------------------------------------------------------------------------|

| ref_clk                | In   | Reference Clock. Must be at least 652 MHz +/-<br>100ppm.                        |

| pma_rst_hard_n         | In   | Active low hard reset for all SerDes channels.                                  |

| reset_ref_clk_n        | In   | Active low reset signal for ref_clk clock domain.                               |

| reset_ts_clk_n         | In   | Active low reset signal for ts_clk clock domain (if ts_clk is used, see below). |

| reset_ff_tx_clk_n[2:0] | In   | Active low reset signal for ff_tx_clk[2:0] clock domains.                       |

| reset_ff_rx_clk_n[2:0] | In   | Active low reset signal for ff_rx_clk[2:0] clock domains.                       |

## **Receive FIFO Interface**

Table 4 - Receive FIFO Interface (All syncrounous to sys\_clk at user interface)

| Signal Name               | Mode | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sys_clk                   | In   | FPGA fabric System Clock. All the FIFO signals are<br>synchronized on sys_clk rising edge. The minimum<br>frequency for the system clock is a function of the<br>interface rate:<br>10G: at least 155 MHz<br>40G: at least 177 MHz<br>100G: at least 295 MHz                                                                                                                                         |

| ff_clk[2:0]               | In   | FIFO Reference Clocks per FIFO group. Can be set to<br>any value required to get the required bandwidth on the<br>FIFO 768-Bit interface. Can be independent from the<br>System clock, however the FIFO clock has to be at least<br>400.0 MHz to allow for the start of frame to be always<br>aligned on lane 0 for 40G mode and may be relaxed to at<br>least 320.51 MHz for the 10G or 100G modes. |

| ff_rx_data<br>[767:0]     | Out  | Receive Data. Refer to the 'Fabic FIFO Interface' for the details of how to map this 768-bit bus to the individual 10/40/100G channels.                                                                                                                                                                                                                                                              |

| ff_rx_dval[11:0]          | Out  | Receive Data Valid per segment. Asserted (set to 1) by<br>the MAC to indicate that data on ff_rx_data,<br>ff_rx_sop, ff_rx_eop, ff_rx_mod, ff_rx_err,<br>ff_rx_vlan, ff_rx_err_stat and ff_rx_ts is valid.                                                                                                                                                                                           |

| ff_rx_sop[11:0]           | Out  | Receive Start of Frame per segment. Set to 1 when the first data word of a frame is driven on ff_rx_data.                                                                                                                                                                                                                                                                                            |

| ff_rx_eop[11:0]           | Out  | Receive End of Frame per segment. Set to 1 when the final data word of a frame is driven on ff _rx_data.                                                                                                                                                                                                                                                                                             |

| ff_rx_mod<br>[(12*6)-1:0] | Out  | Receive Word Modulo per segment. Indicates which portion of<br>the final frame word is valid:<br><u>Bit 543210</u><br>000000: ff_rx_data[63:0]/[255:0]/[511:0] is valid (for<br>10/40/100G)<br>000001: ff_rx_data[7:0] is valid<br>000010: ff_rx_data[15:0] is valid<br>000011: ff_rx_data[23:0] is valid<br>000100: ff_rx_data[31:0] is valid<br>000101: ff_rx_data[39:0] is valid                  |

|                      |     | 000110: ff_rx_data[47:0] is valid                                                                                           |

|----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------|

|                      |     | 000111: ff_rx_data[55:0] is valid<br>001000: ff_rx_data[63:0] is valid (40/100G only)                                       |

|                      |     | 001001: ff rx data[71:0] is valid (40/100G only)                                                                            |

|                      |     |                                                                                                                             |

|                      |     |                                                                                                                             |

|                      |     | 011110: ff_rx_data[239:0] is valid (40/100G only)                                                                           |

|                      |     | <b>011111</b> : ff_rx_data[247:0] is valid (40/100G only)                                                                   |

|                      |     | 100000: ff_rx_data[255:0] is valid (100G only)                                                                              |

|                      |     | <b>100001:</b> ff_rx_data[263:0] is valid (100G only)                                                                       |

|                      |     |                                                                                                                             |

|                      |     | 111110: ff rx data[495:0] is valid (100G only)                                                                              |

|                      |     | 111111: ff rx data[503:0] is valid (100G only)                                                                              |

|                      |     | Receive Frame Error per segment. Asserted with the frame's                                                                  |

| ff_rx_err[11:0]      | Out | final data word to indicate that an error was detected when                                                                 |

| []                   |     | receiving the frame. The type of error is coded on the status                                                               |

|                      |     | word ff_rx_err_stat[23:0].<br>Receive Ready per segment. The ff_rx_rdy signal is asserted                                   |

|                      |     | high to indicate to the Receive FIFO that it may transmit                                                                   |

| ff_rx_rdy[11:0]      | In  | ff_rx_data. Deasserting the ff_rx_rdy signal allows the user to                                                             |

| ii_ix_iuy[11.0]      |     | pause the reception of ff_rx_data, but the Receive FIFO Almost                                                              |

|                      |     | Full flag, ff_rx_afull, must be monitored to prevent the Receive                                                            |

|                      |     | FIFO from overflowing, resulting is a loss of data.<br>Receive FIFO Almost Full flag per segment. The ff_rx_afull flag      |

| ff_rx_afull[11:0]    | Out | is asserted high when there are 15 or fewer empty locations                                                                 |

|                      | out | remaining in the Receive FIFO.                                                                                              |

|                      |     | Receive Frame VLAN Indication per segment. Asserted with the                                                                |

| ff_rx_vlan           | Out | frame's final data word to indicate that the current frame                                                                  |

| [(12*2)-1:0]         | Out | implements a VLAN Tag (bit 0 asserted) or a Stacked VLAN Tag                                                                |

|                      |     | (bit 1 asserted).<br>Receive Frame Status and Error Indications. A status word is                                           |

|                      |     | available for each received frame with the final word                                                                       |

|                      |     | (ff rx eop = 1). The receive frame status                                                                                   |

|                      |     | ff rx err stat[23:0] can be mapped to any segment of                                                                        |

|                      |     | FIFO group 0 (10G: SEG0-3, 40G: SEG0, 100G: SEG0).                                                                          |

|                      |     |                                                                                                                             |

|                      |     | _stat[0]: Set to 1 when the current frame has an invalid                                                                    |

|                      |     | length, i.e. less than 64 octets or more than the maximum value defined in register FRM_LENGTH, or a mismatch between the   |

|                      |     | payload received and the payload length given within the frame                                                              |

|                      |     | was detected.                                                                                                               |

|                      |     | _stat[1]: Set to 1 to indicate that the current frame was                                                                   |

|                      |     | received with a CRC-32 error.                                                                                               |

|                      |     | _stat[2]: Set to 1 to indicate that the current frame was                                                                   |

| ff_rx_err_stat[23:0] | Out | received with a wrong or unexpected code during frame<br>reception reported by the reconciliation sub-layer function.       |

|                      |     | stat[3]: Set to 1 to indicate that the current frame was                                                                    |

|                      |     | truncated because of a FIFO exception (Overflow).                                                                           |

|                      |     | _stat[4]: Set to 1 to indicate that a Sequence Error (Local or                                                              |

|                      |     | Remote) was received from the PHY device during frame                                                                       |

|                      |     | reception.                                                                                                                  |

|                      |     | _stat[5]: Set to 1 to indicate that the current Frame                                                                       |

|                      |     | <pre>implements a Stacked VLAN Tag. stat[6]: Set to 1 to indicate that the current frame was</pre>                          |

|                      |     | received with an Error control character on the XL/CGMII                                                                    |

|                      |     | interface.                                                                                                                  |

|                      |     | _stat[7]: Set to 1 to indicate that the current Frame                                                                       |

|                      |     | implements a VLAN Tag.                                                                                                      |

|                      |     | _stat[23:8]: Payload length of the frame. This is a copy of the length/type field as it is found within the frame. For VLAN |

|                      |     |                                                                                                                             |

|                      |     | frames it is a copy of the length/type field following the 4-octet VLAN tag.                                                                                                                                                                                                                     |

|----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ff_rx_ts[31:0]       | Out | Receive Timestamp Value. Time when the MAC detected<br>the SFD of the frame.<br>Valid with ff_rx_sop. The receive timestamp<br>ff_rx_ts[31:0] can be mapped to any segment of<br>FIFO group 0 (10G: SEG0-3, 40G: SEG0, 100G: SEG0).                                                              |

| ff_rx_preamble_val   | Out | Receive Frame Preamble Valid Indication. Asserted (set<br>to 1) to indicate that a valid preamble is available on pin<br>ff_rx_preamble[55:0].<br>Note: Since the signal ff_rx_preamble_val is not a<br>pulse, the application should sample<br>ff_rx_preamble[55:0] when ff_rx_sop is set to 1. |

| ff_rx_preamble[55:0] | Out | Receive Frame Preamble. 56-Bit preamble of the current frame, valid when ff_rx_preamble_val is set to 1. The receive frame preamble ff_rx_preamble[55:0] can be mapped to any segment of FIFO group 0 (10G: SEG0-3, 40G: SEG0, 100G: SEG0).                                                      |

|                      |     |                                                                                                                                                                                                                                                                                                  |

## **Transmit FIFO Interface**

#### Table 5 – Transmit FIFO Interface (all synchronous to ff\_tx\_clk[2:0])

|                           | Mode Description |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal Name               | woae             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| ff_tx_data<br>[767:0]     | In               | Transmit Data. Refer to the 'Fabic FIFO Interface' for the details of how to map this 768-bit bus to the individual 10/40/100G channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| ff_tx_wren[11:0]          | In               | Transmit Data Write Enable per segment. Asserted by the Transmit application to write data into the MAC Core FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| ff_tx_sop[11:0]           | In               | Transmit Start of Frame per segment. Set to 1 when the first data word of a frame is driven on $ff_tx_data$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| ff_tx_eop[11:0]           | In               | Transmit End of Frame per segment. Set to 1 when the final data word of a frame is driven on ff_tx_data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| ff_tx_mod<br>[(12*6)-1:0] | In               | Transmit Word Modulo per segment. Indicates which<br>portion of the final frame word is valid:<br><u>Bit 543210</u><br>000000: ff_tx_data[63:0]/[255:0]/[511:0] is<br>valid (for 10/40/100G)<br>000001: ff_tx_data[7:0] is valid<br>000010: ff_tx_data[7:0] is valid<br>000010: ff_tx_data[15:0] is valid<br>000100: ff_tx_data[23:0] is valid<br>000101: ff_tx_data[31:0] is valid<br>000101: ff_tx_data[39:0] is valid<br>000110: ff_tx_data[47:0] is valid<br>000110: ff_tx_data[55:0] is valid<br>000100: ff_tx_data[63:0] is valid<br>001000: ff_tx_data[71:0] is valid (40/100G only)<br>001001: ff_tx_data[239:0] is valid (40/100G only)<br><br>011110: ff_tx_data[247:0] is valid (40/100G only)<br>11111: ff_tx_data[255:0] is valid (40/100G only)<br>100000: ff_tx_data[255:0] is valid (100G only) |  |

|                      |     | 111110: ff tx data[495:0] is valid (100G only)                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      |     | 111111: ff tx data[503:0] is valid (100G only)                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| ff_tx_err[11:0]      | In  | Transmit Frame Error per segment. Asserted with the frame's final data word to indicate that the transmitted frame is invalid. When ff_tx_err is asserted, the frame is transmitted to the XL/CGMII interface with a transmit error.                                                                                                                                                                                                                                                  |  |

| ff_tx_crc[11:0]      | In  | Transmit CRC Append per segment. If set, a CRC field will be appended to the frame. If cleared, the MAC does not append a FCS to the frame. This signal must be valid during ff tx sop assertion.                                                                                                                                                                                                                                                                                     |  |

| ff_tx_rdy[11:0]      | Out | Transmit FIFO Ready per segment. When the ff_tx_rdy signal is high, the user may send ff_tx_data to the transmit FIFO of the addressed segment. When the ff_tx_rdy signal is low, the transmit interface FIFO is almost full and the user must stop sending data to the ff_tx_data port.                                                                                                                                                                                              |  |

| ff_tx_ovr[11:0]      | Out | Transmit Overflow Error per segment. Asserted (set to 1) as long as an overflow condition persists on the application FIFO per segment. This signal can be used to trigger an application interrupt.                                                                                                                                                                                                                                                                                  |  |

| ff_tx_id[3:0]        | In  | Frame Identifier. An arbitrary value that must be valid<br>during ff_tx_eop assertion that can be used to mark<br>specific frames. The frame identifier ff_tx_id[3:0]<br>can be mapped to any segment of FIFO group 0 (10G:<br>SEG0-3, 40G: SEG0, 100G: SEG0).<br>The value is available at the transmit status pins<br>$tx_ts_id[3:0]$ when the frame has been transmitted<br>to the PHY.<br>Has no further meaning inside the MAC besides the<br>forwarding to the transmit status. |  |

| ff_tx_ts_frm         | In  | IEEE 1588 Timing Frame Indication that must be valid<br>during ff_tx_eop assertion. The frame indication<br>ff_tx_ts_frm can be mapped to any segment of FIFO<br>group 0 (10G: SEG0-3, 40G: SEG0, 100G: SEG0).<br>Allows the application to mark specific 1588 event<br>frames. When set for a frame, its transmit timestamp will<br>be returned on tx_ts[31:0]                                                                                                                       |  |

| ff_tx_preamble_val   | In  | Transmit Frame Preamble Valid Indication. Should be asserted with $ff_tx_sop$ to indicate that the current frame should be sent with the preamble provided on $ff_tx_preamble[55:0]$ .                                                                                                                                                                                                                                                                                                |  |

| ff_tx_preamble[55:0] | In  | Transmit Frame Preamble. 56-Bit preamble inserted in<br>the current frame, must be valid when<br>ff_tx_preamble_val is set to 1. The transmit frame<br>preamble ff_tx_preamble[55:0] can be mapped to<br>any segment of FIFO group 0 (10G: SEG0-3, 40G:<br>SEG0, 100G: SEG0).                                                                                                                                                                                                         |  |

## PMA TX/RX Interface

#### Table 6 – PMA TX/RX Interface

| Signal Name                  | Mode   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pma_{11:0}_pd{1:0]           | Input  | Individual Lane power down state control:<br>11 – Coma Power State (P2) - Everything but receiver<br>detection + signal detect is disabled. Minimum power<br>consumption<br>10 – Slumber Power State (P1) - PLL is enabled. CDR<br>and Driver are disabled. Increased power consumption<br>01 – Doze Power State (P0s) - Everything but transmit<br>driver is enabled. Apprx. 20-30mW saved from the Wake<br>state.<br>00 – Wake Power State (P0) - Everything is Asserted.<br>Maximum power consumption. |

| pma_rx_cdr_lck2dat<br>[11:0] | Output | CDR Lock to Data status indicator<br>0 – CDR is locked to reference clock<br>1 – CDR is locked to data                                                                                                                                                                                                                                                                                                                                                                                                    |

| pma_rx_iddq_n[11:0<br>]      | Input  | Individual Receive Lane disable/power-down control 1 –<br>Non-PD State - all analog circuits are enabled 0 – PD<br>State - all analog circuits are disabled. Analog Receiver<br>impedance is placed into High Impedance mode.                                                                                                                                                                                                                                                                             |

| pma_rxready[11;0]            | Output | Receive Lane Ready Status Signal:<br>0 – RX Lane is not ready for data transmission<br>1 – RX Lane is ready for data transmission                                                                                                                                                                                                                                                                                                                                                                         |

| pma_rxstat[11:0]             | Output | Receive Lane State Transition Status. Indicates when the PMA has completed a requested state transition:<br>0 – RX Lane has not completed its state change<br>1 – RX Lane has completed its state change                                                                                                                                                                                                                                                                                                  |

| pma_sig_detect[11:<br>0]     | Output | Receiver Data Detection Status Signal.<br>0 – Indicates no/invalid data on receive pins<br>1 – Indicates valid data on receive pins                                                                                                                                                                                                                                                                                                                                                                       |

| pma_synth_iddq_n[<br>11:0]   | Input  | Individual Synthesizer disable/power-down control<br>1 – Non-PD State - all analog circuits are enabled<br>0 – PD State - all analog circuits are disabled                                                                                                                                                                                                                                                                                                                                                |

| pma_synthready[11:<br>0]     | Output | SYNTH Ready Status Signal:<br>0 – SYNTH is not ready for data transmission<br>1 – SYNTH is ready for data transmission                                                                                                                                                                                                                                                                                                                                                                                    |

| pma_synthstat[11:0]          | Output | <ul> <li>SYNTH state transition status. Indicates when the PMA has completed a requested state transition:</li> <li>0 – SYNTH has not completed its state change</li> <li>1 – SYNTH has completed its state change</li> </ul>                                                                                                                                                                                                                                                                             |

| pma_tx_iddq_n[11:0<br>]      | Input  | Individual Transmit Lane disable/power-down control:<br>1 – Non-PD State - all analog circuits are enabled<br>0 – PD State - all analog circuits are disabled                                                                                                                                                                                                                                                                                                                                             |

## **Priority Flow Control Interface**

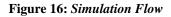

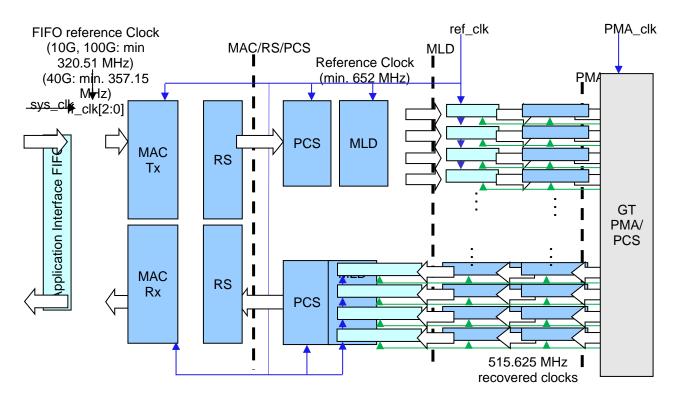

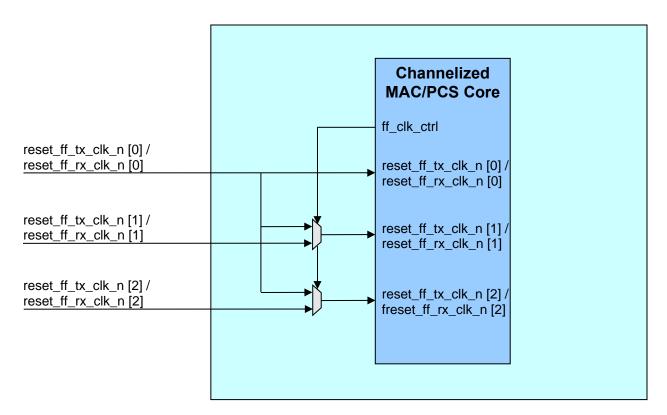

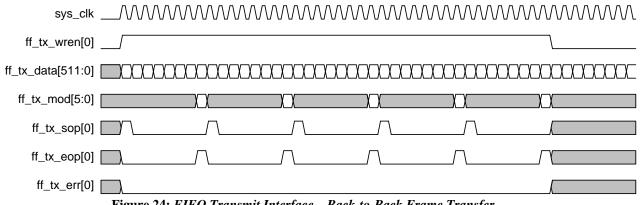

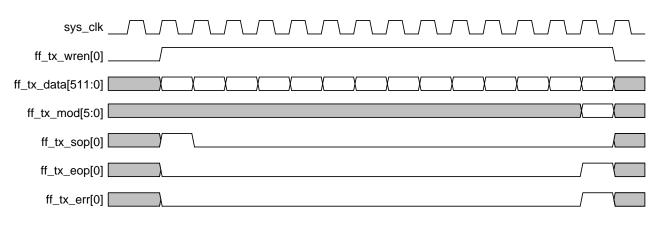

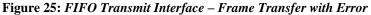

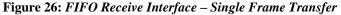

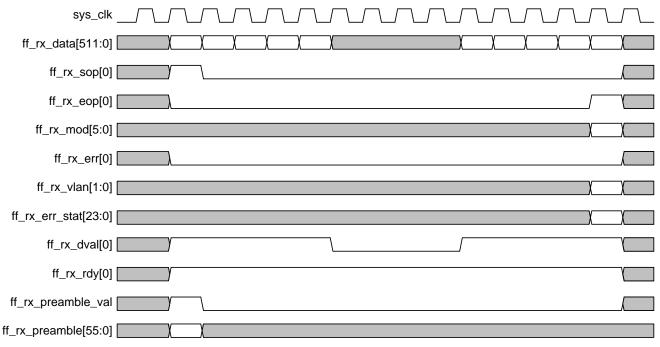

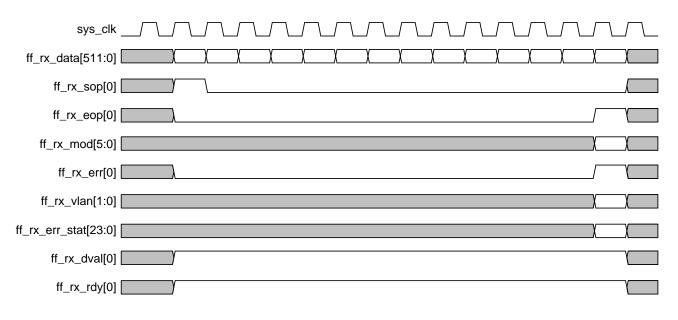

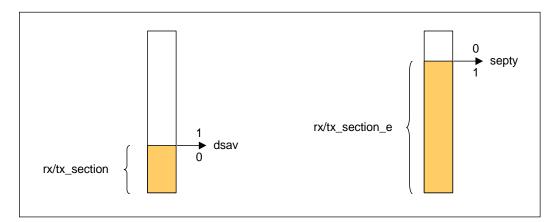

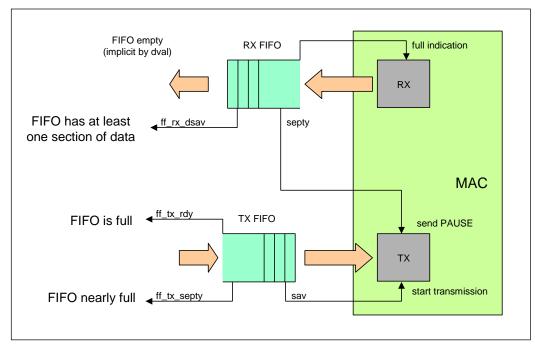

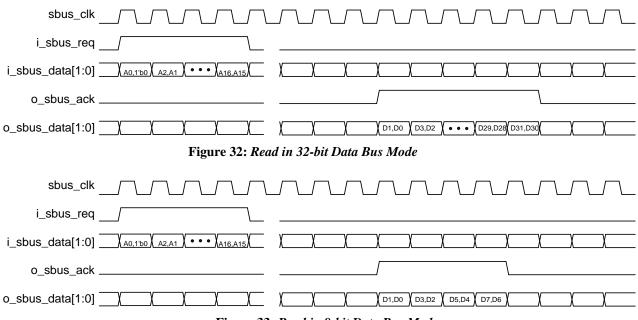

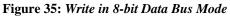

| Signal Name                    | Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |