# **VSC8489**

# Hardware Design Checklist

# 1.0 INTRODUCTION

This document provides a hardware design checklist for the Microchip VSC8489 product family. It is meant to help customers achieve first-pass design success.

There are several members of the VSC8489 family namely, VSC8489-17, VSC8489-16, and VSC8489-02. This document mostly covers VSC8489-17, which is the most full-featured device in the family. On the other hand, the VSC8489-16 is a one-channel device, and the channel 1 pins are unused (no-connects). The VSC8489 must be configured after power-up, even for basic bring-up purposes. Use the Microchip supplied API and reference the sample application for examples of API calls.

These checklist items should be followed when utilizing the VSC8489 in a new design. A summary of these items is provided in Section 9.0, "Hardware Checklist Summary". Detailed information on these subjects can be found in the corresponding sections:

- Section 2.0, "General Considerations"

- Section 3.0, "Power"

- Section 4.0, "Thermal Considerations"

- Section 5.0, "Media SerDes Interface"

- Section 6.0, "Host Interface (XAUI, RXAUI, and SGMII)"

- Section 7.0, "Reference Clocks"

- Section 8.0, "Miscellaneous"

# 2.0 GENERAL CONSIDERATIONS

#### 2.1 Required References

The VSC8489 implementor should have the following documents on hand:

- VSC8489-17 Dual Channel WAN/LAN/Backplane RXAUI/XAUI to SFP+/KR 10 GbE SerDes PHY with VeriTime™ Data Sheet

- VSC8489-16 Single Channel WAN/LAN/Backplane RXAUI/XAUI to SFP+/KR 10 GbE PHY with Optional Veri-Time™ Data Sheet

- VSC8489-02 Dual Channel WAN/LAN/Backplane RXAUI/XAUI to SFP+/KR 10 GbE SerDes PHY Data Sheet

#### 2.2 Pin Check

• Check the pinout of the part against the data sheet. Ensure that all pins match the data sheet and are configured as inputs, outputs, or bidirectional for error checking.

#### 2.3 Ground

• A single ground reference is used for all ground pins. Use one or more continuous ground planes to ensure a low impedance ground path and a continuous ground reference for all signals. Section 4.0, "Thermal Considerations" also explains the importance of grounds for thermal dissipation.

# 3.0 POWER

• Table 3-1 show the power supply pins for VSC8489.

| IADEE 5-1. |            |                                             |                          |  |  |  |  |  |

|------------|------------|---------------------------------------------|--------------------------|--|--|--|--|--|

| Name       | Pin Number | Description                                 | Comment                  |  |  |  |  |  |

| VDDAH      | G4         | 1.0V power supply for host-side analog      | Analog, use ferrite bead |  |  |  |  |  |

| VDDAH      | G5         | 1.0V power supply for host-side analog      |                          |  |  |  |  |  |

| VDDAH      | J4         | 1.0V power supply for host-side analog      |                          |  |  |  |  |  |

| VDDAH      | J5         | 1.0V power supply for host-side analog      |                          |  |  |  |  |  |

| VDDAL      | F7         | 1.0V power supply for line-side analog      | Analog, use ferrite bead |  |  |  |  |  |

| VDDAL      | G7         | 1.0V power supply for line-side analog      |                          |  |  |  |  |  |

| VDDAL      | G9         | 1.0V power supply for line-side analog      |                          |  |  |  |  |  |

| VDDAL      | H9         | 1.0V power supply for line-side analog      |                          |  |  |  |  |  |

| VDDAL      | J7         | 1.0V power supply for line-side analog      |                          |  |  |  |  |  |

| VDDHSL     | F9         | 1.2V power supply for line-side I/Os        | Analog, use ferrite bead |  |  |  |  |  |

| VDDHSL     | F10        | 1.2V power supply for line-side I/Os        |                          |  |  |  |  |  |

| VDDHSL     | G10        | 1.2V power supply for line-side I/Os        |                          |  |  |  |  |  |

| VDDHSL     | H10        | 1.2V power supply for line-side I/Os        |                          |  |  |  |  |  |

| VDDHSL     | J9         | 1.2V power supply for line-side I/Os        |                          |  |  |  |  |  |

| VDDHSL     | J10        | 1.2V power supply for line-side I/Os        |                          |  |  |  |  |  |

| VDDL       | H4         | 1.0V power supply for chip core             | Digital, no ferrite bead |  |  |  |  |  |

| VDDL       | H5         | 1.0V power supply for chip core             |                          |  |  |  |  |  |

| VDDL       | H7         | 1.0V power supply for chip core             |                          |  |  |  |  |  |

| VDDMDIO    | C7         | 2.5V power supply for MDIO I/Os             | Digital, no ferrite bead |  |  |  |  |  |

| VDDTTL     | C9         | 2.5V power supply for non-MDIO digital I/Os | Digital, no ferrite bead |  |  |  |  |  |

| VDDTTL     | M6         | 2.5V power supply for non-MDIO digital I/Os |                          |  |  |  |  |  |

#### TABLE 3-1: POWER SUPPLY PINS

#### 3.1 Current Requirements

• Ensure that the voltage regulators and power distribution are designed to adequately support these current requirements for each power rail. (See Table 3-2.) Note that the 1.0V maximum current values in this table include margins, so they sum to more than the maximum 1.0V current specification in the data sheet. The data sheet value is correct for overall power.

| Power Rail       | Voltage | Maximum Current |

|------------------|---------|-----------------|

| VDDAH            | 1.0V    | 1000 mA         |

| VDDAL            | 1.0V    | 900 mA          |

| VDDL             | 1.0V    | 2000 mA         |

| VDDHSL           | 1.2V    | 150 mA          |

| VDDMDIO + VDDTTL | 2.5V    | 50 mA           |

#### TABLE 3-2: MAXIMUM RAIL CURRENTS

#### 3.2 Power Supply Planes

- VSC8489 requires three power rails: 2.5V, 1.2V, and 1.0V. The filtered analog 1.0V and 1.2V supplies should not be shorted to any other digital supply at the package or PCB level. See Section 3.3, "Analog Power Plane Filter-ing".

- The most important PCB design and layout considerations are as follows:

- Ensure that the return plane is adjacent to the power plane (without a signal layer in between).

- Ensure that a single plane is used for voltage reference with splits for individual voltage rails within that plane. Try to maximize the area of each power split on the power plane based on corresponding via coordinates for each rail to maximize coupling between each voltage rail and the return plane.

- Minimize resistive drop while efficiently conducting away heat from the device using one-ounce copper cladding.

- Four-layer PCBs with only one designated power plane must adhere to proper design techniques to prevent random system events, such as CRC errors. Each power supply requires the lowest resistive drop possible to power pins of the device with correctly positioned local decoupling. For more information, see Section 3.4, "Decoupling Capacitors".

- Ferrite beads should be used over a series inductor filter whenever possible, particularly for high-density or high-power devices.

# 3.3 Analog Power Plane Filtering

- The analog power supplies are:

- VDDAH

- VDDAL

- VDDHSL

- A ferrite bead should be used to isolate each analog supply from the rest of the board. The bead should be placed in series between the bulk decoupling capacitors and local decoupling capacitors.

- Because all PCB designs yield unique noise coupling behavior, not all ferrite beads or decoupling capacitors may be needed for every design. It is recommended that system designers provide an option to replace the ferrite beads with 0Ω resistors once a thorough evaluation of system performance is completed.

- Ferrite beads are not recommended on the digital supplies VDDL, VDDTTL, and VDDMDIO.

- The chosen ferrite beads should have the impedance of 80Ω to 120Ω at 100 MHz, and the characteristics are specified in Table 3-3.

| VSC8489       | Ferrite Bead Requirements |                       |  |  |

|---------------|---------------------------|-----------------------|--|--|

| Analog Supply | Current                   | Maximum DC Resistance |  |  |

| VDDAH         | 1000 mA                   | 40 mΩ                 |  |  |

| VDDAL         | 1000 mA                   | 40 mΩ                 |  |  |

| VDDHSL        | 150 mA                    | 100 mΩ                |  |  |

#### TABLE 3-3: FERRITE BEAD PARAMETERS

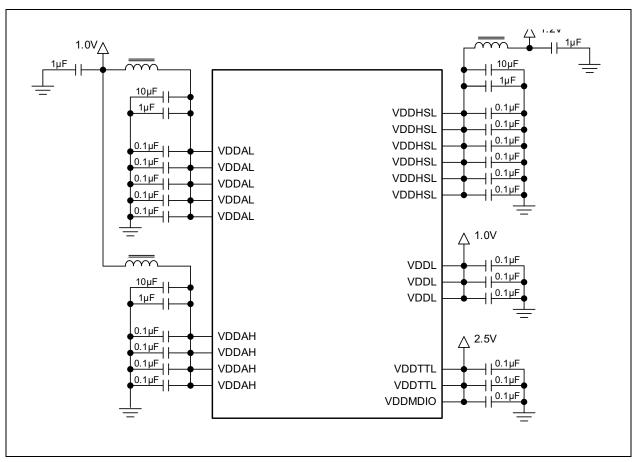

The power and ground connections are shown in Figure 3-1.

#### FIGURE 3-1: POWER SUPPLY CONNECTIONS AND LOCAL FILTERING

#### 3.4 Decoupling Capacitors

- Bulk decoupling capacitors can be placed at any convenient position on the board. Local decoupling capacitors should be X5R or X7R ceramic and placed as close to the VSC8489's power pins as possible for every pin.

- If the VSC8489 device is on the top-side of the printed circuit board (PCB), the best location for local decoupling capacitors is on the bottom or underside of the PCB, directly under the device.

# 4.0 THERMAL CONSIDERATIONS

- For proper cooling, ensure efficient thermal dissipation by maximizing the number of via connections to the ground plane. Additional ground planes will enhance thermal dissipation and signal integrity performance.

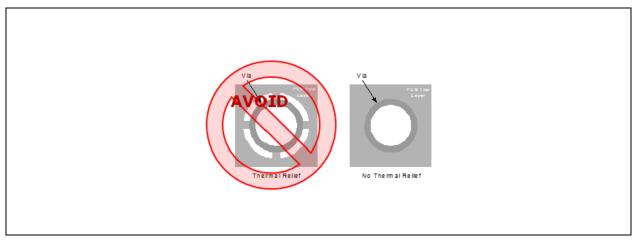

- When connecting the thermal vias to ground planes, it is advisable to avoid thermal relief connection traces as shown on the left-hand side of Figure 4-1 as these are designed to prevent the flow of heat through the PCB. Instead, the thermal vias should have a solid connection to the traces and planes on each layer as shown on the right-hand side of Figure 4-1.

- PCB thermal vias should connect to the solid ground planes within the board to dissipate heat below the package. A minimum of one-ounce copper cladding is recommended. Figure 4-2 shows a cross-section of the thermal via.

#### FIGURE 4-2: THERMAL GROUND PLANE CONNECTION

# 5.0 MEDIA SERDES INTERFACE

#### 5.1 Media SerDes Design Rules

- Table 5-1 shows information on Media SerDes Interface. Best performance is achieved when SerDes traces are placed using the following design rules:

- AC coupling capacitors are not needed for SFP+ and SFP applications because SFP+/SFP modules have AC coupling capacitors internally on both TX and RX signals.

- Use AC coupling with 0.1 µF capacitors on RXIN and TXOUT for chip-to-chip applications. Place the capacitors at the receiving end of the signals.

- Traces should be routed as 50Ω (100Ω differential) controlled impedance transmission lines (microstrip or stripline).

- Traces should be of equal length (within 10 mils) on each differential pair to minimize skew.

- Traces should be run adjacent to a single ground plane to match impedance and minimize noise.

- Spacing equal to five times the ground plane gap is recommended between adjacent tracks to reduce crosstalk between SerDes pairs. Minimum spacing of three times the ground plane gap is required.

- Traces should avoid vias and layer changes. If layer changes cannot be avoided, mode-suppression vias should be included next to the signal vias to reduce the strength of any radiating spurious fields.

- Guard vias should be placed no greater than one-quarter wavelength apart around the differential pair tracks.

- If a port is unused, both the RXIN and TXOUT pins can be left floating (no-connect).

- If the LOPC pins are not used, pull them to ground with a resistor.

| Pin Name | Pin Number | Туре | Level | Description                                                 |  |  |

|----------|------------|------|-------|-------------------------------------------------------------|--|--|

| RXIN0N   | B13        | Ι    | CML   | Receive channel 0 input data, complement                    |  |  |

| RXIN0P   | B14        | I    | CML   | Receive channel 0 input data, true                          |  |  |

| RXIN1N   | L14        | I    | CML   | Receive channel 1 input data, complement                    |  |  |

| RXIN1P   | L13        | I    | CML   | Receive channel 1 input data, true                          |  |  |

| TXOUTON  | D14        | 0    | CML   | Transmit channel 0 output data, complement                  |  |  |

| TXOUT0P  | D13        | 0    | CML   | Transmit channel 0 output data, true                        |  |  |

| TXOUT1N  | N13        | 0    | CML   | Transmit channel 1 output data, complement                  |  |  |

| TXOUT1P  | N14        | 0    | CML   | Transmit channel 1 output data, true                        |  |  |

| LOPC0    | D6         | Ι    | LVTTL | Loss of optical carrier, channel 0. Internally pulled high. |  |  |

| LOPC1    | M7         | l    | LVTTL | Loss of optical carrier, channel 1. Internally pulled high. |  |  |

#### TABLE 5-1: MEDIA SERDES INTERFACE PINS

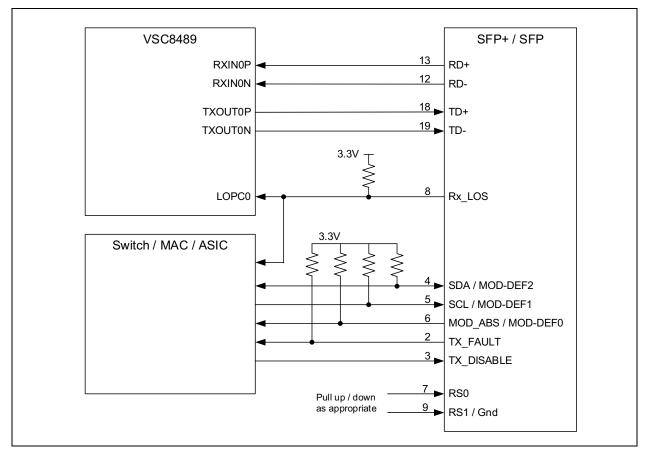

#### 5.2 Connecting to 10G SFP+ or 1G SFP

- Follow the succeeding guidelines for connecting the differential SerDes data pins to the SFP+/SFP (also referred to as SFP):

- Connect the VSC8489 TXOUT pins directly to the TD input pins of the SFP.

- Connect the VSC8489 RXIN pins directly to the RD output pins of the SFP.

- External termination resistors and AC coupling capacitors are not needed on the PCB.

- · Connection and use of the other SFP signals are at the discretion of the user.

- The RX LOS output of the SFP can drive the LOPC input of the VSC8489 and/or the host device.

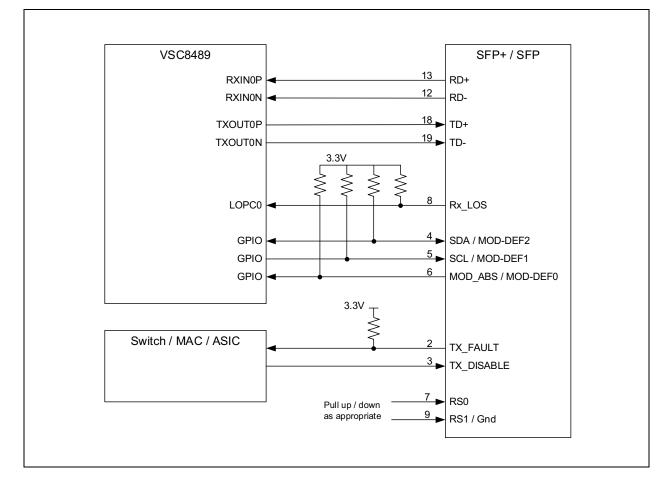

- VSC8489 GPIO pins can be configured as Two-Wire masters for accessing SFP registers via SDA and SCL. However, since this adds an additional layer of software complexity to manage these signals, it is extremely common for the SFP Two-Wire interface to be managed directly from the switch/MAC/ASIC host device. GPIO assignments are given in the table below.

- · VSC8489 GPIO pins can also be assigned as inputs for the MOD\_ABS (module absent) output of the SFP.

- All other SFP signals, if used, should be connected to the switch/MAC/ASIC host device and not to the VSC8489.

- All single-ended SFP outputs are open drain and require a pull-up resistor to 3.3V when used.

- · All VSC8489 GPIO outputs are open drain and require a pull-up resistor. When connected to an SFP, the pull-up

voltage must be 3.3V and not 2.5V.

GPIO pin assignments are specified in Table 5-2 and Table 5-3.

| Channel   | VSC8489 Pin      | SFP+ Pin   |  |  |  |  |  |

|-----------|------------------|------------|--|--|--|--|--|

| Channel 0 | GPIO_6 (pin K4)  | SDA, pin 4 |  |  |  |  |  |

| Channel 0 | GPIO_7 (pin K5)  | SCL, pin 5 |  |  |  |  |  |

| Channel 1 | GPIO_10 (pin L5) | SDA, pin4  |  |  |  |  |  |

| Channel 1 | GPIO_11 (pin L6) | SCL, pin 5 |  |  |  |  |  |

#### TABLE 5-2: GPIO ASSIGNMENTS FOR TWO-WIRE MASTER

#### TABLE 5-3:GPIO ASSIGNMENTS FOR MOD\_ABS INPUTS

| Channel   | VSC8489 Pin                            | SFP+ Pin       |

|-----------|----------------------------------------|----------------|

| Channel 0 | PHY GPIO_0 (pin D4) or GPIO_8 (pin K6) | MOD_ABS, pin 6 |

| Channel 1 | PHY GPIO_9 (pin L4)                    | MOD_ABS, pin 6 |

• Figure 5-1 and Figure 5-2 illustrate VSC8489 to SFP+ connections. Figure 5-1 shows a typical scenario wherein most SFP signals are connected to the Switch/MAC/ASIC host device rather than the VSC8489. Conversely, Figure 5-2 shows a less common scenario wherein the maximum number of SFP signals are connected to the VSC8489.

#### FIGURE 5-1: SFP+ CONNECTIONS WITH TWO-WIRE AND MOD\_ABS TO THE SWITCH/MAC/ ASIC

#### FIGURE 5-2: SFP+ CONNECTIONS WITH TWO-WIRE AND MOD\_ABS TO THE VSC8489

# 6.0 HOST INTERFACE (XAUI, RXAUI, AND SGMII)

• Table 6-1 shows information on Host SerDes Interface.

| Pin Name | Pin Number | Туре | Level | Description                                                                 |  |  |  |  |

|----------|------------|------|-------|-----------------------------------------------------------------------------|--|--|--|--|

| XRX0_0N  | C2         | Ι    | CML   | XAUI channel 0, RX path lane 0, serial data input, complement               |  |  |  |  |

| XRX0_0P  | C1         | I    | CML   | XAUI channel 0, $\mathbf{R}\mathbf{X}$ path lane 0, serial data input, true |  |  |  |  |

| XRX0_1N  | D2         | I    | CML   | XAUI channel 0, RX path lane 1, serial data input, complement               |  |  |  |  |

| XRX0_1P  | D1         | Ι    | CML   | XAUI channel 0, $\mathbf{R}\mathbf{X}$ path lane 1, serial data input, true |  |  |  |  |

| XRX0_2N  | E2         | Ι    | CML   | XAUI channel 0, RX path lane 2, serial data input, complement               |  |  |  |  |

| XRX0_2P  | E1         | I    | CML   | XAUI channel 0, RX path lane 2, serial data input, true                     |  |  |  |  |

| XRX0_3N  | F2         | Ι    | CML   | XAUI channel 0, RX path lane 3, serial data input, complement               |  |  |  |  |

| XRX0_3P  | F1         | Ι    | CML   | XAUI channel 1, RX path lane 3, serial data input, true                     |  |  |  |  |

| XRX1_0N  | P2         | Ι    | CML   | XAUI channel 1, RX path lane 0, serial data input, complement               |  |  |  |  |

| XRX1_0P  | N2         | Ι    | CML   | XAUI channel 1, RX path lane 0, serial data input, true                     |  |  |  |  |

| XRX1_1N  | P3         | Ι    | CML   | XAUI channel 1, RX path lane 1, serial data input, complement               |  |  |  |  |

| XRX1_1P  | N3         | Ι    | CML   | XAUI channel 1, RX path lane 1, serial data input, true                     |  |  |  |  |

| XRX1_2N  | P4         | Ι    | CML   | XAUI channel 1, RX path lane 2, serial data input, complement               |  |  |  |  |

| XRX1_2P  | N4         | Ι    | CML   | XAUI channel 1, $\mathbf{R}\mathbf{X}$ path lane 2, serial data input, true |  |  |  |  |

| XRX1_3N  | P5         | I    | CML   | XAUI channel 1, RX path lane 3, serial data input, complement               |  |  |  |  |

| XRX1_3P  | N5         | Ι    | CML   | XAUI channel 1, $\mathbf{R}\mathbf{X}$ path lane 3, serial data input, true |  |  |  |  |

| XTX0_0N  | B6         | 0    | CML   | XAUI channel 0, TX path lane 0, serial data input, complement               |  |  |  |  |

| XTX0_0P  | A6         | 0    | CML   | XAUI channel 0, TX path lane 0, serial data input, true                     |  |  |  |  |

| XTX0_1N  | B5         | 0    | CML   | XAUI channel 0, TX path lane 1, serial data input, complement               |  |  |  |  |

| XTX0_1P  | A5         | 0    | CML   | XAUI channel 0, TX path lane 1, serial data input, true                     |  |  |  |  |

| XTX0_2N  | B4         | 0    | CML   | XAUI channel 0, TX path lane 2, serial data input, complement               |  |  |  |  |

| XTX0_2P  | A4         | 0    | CML   | XAUI channel 0, TX path lane 2, serial data input, true                     |  |  |  |  |

| XTX0_3N  | B3         | 0    | CML   | XAUI channel 0, TX path lane 3, serial data input, complement               |  |  |  |  |

| XTX0_3P  | A3         | 0    | CML   | XAUI channel 0, TX path lane 3, serial data input, true                     |  |  |  |  |

| XTX1_0N  | H2         | 0    | CML   | XAUI channel 1, TX path lane 0, serial data input, complement               |  |  |  |  |

| XTX1_0P  | H1         | 0    | CML   | XAUI channel 1, TX path lane 0, serial data input, true                     |  |  |  |  |

| XTX1_1N  | J2         | 0    | CML   | XAUI channel 1, TX path lane 1, serial data input, complement               |  |  |  |  |

| XTX1_1P  | J1         | 0    | CML   | XAUI channel 1, TX path lane 1, serial data input, true                     |  |  |  |  |

| XTX1_2N  | K2         | 0    | CML   | XAUI channel 1, TX path lane 2, serial data input, complement               |  |  |  |  |

| XTX1_2P  | K1         | 0    | CML   | XAUI channel 1, TX path lane 2, serial data input, true                     |  |  |  |  |

| XTX1_3N  | L2         | 0    | CML   | XAUI channel 1, TX path lane 3, serial data input, complement               |  |  |  |  |

| XTX1_3P  | L1         | 0    | CML   | XAUI channel 1, TX path lane 3, serial data input, true                     |  |  |  |  |

TABLE 6-1: HOST SERDES INTERFACE PINS

#### 6.1 Host Serial Interface Design

- The host interface may be either XAUI, RXAUI, or 1GbE / SGMII. It is recommended to use the same configuration for both channels 0 and 1.

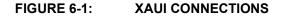

- XAUI (10G) uses all four TX path lanes and four RX path lanes per channel. (See Figure 6-1.)

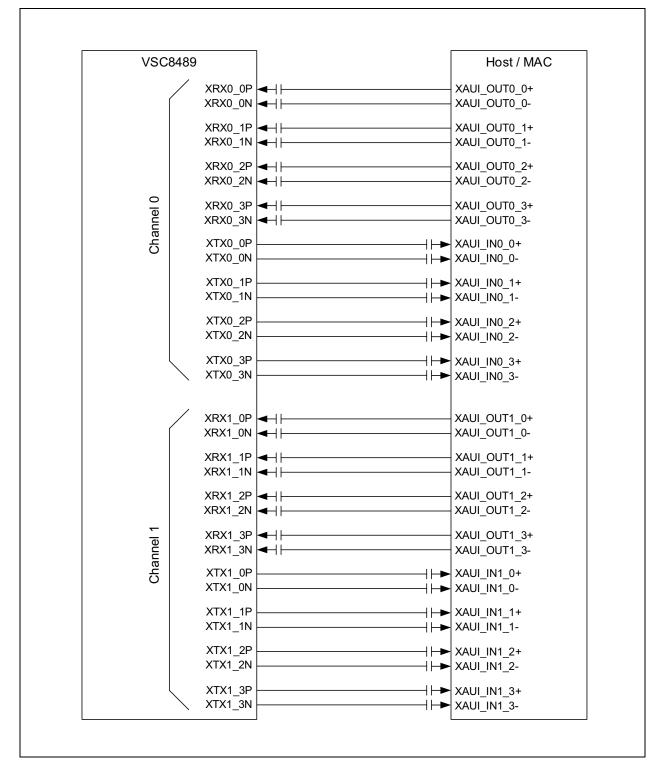

- RXAUI (10G) uses lanes 0 and 2. Lanes 1 and 3 can be left floating (no-connect). (See Figure 6-2.)

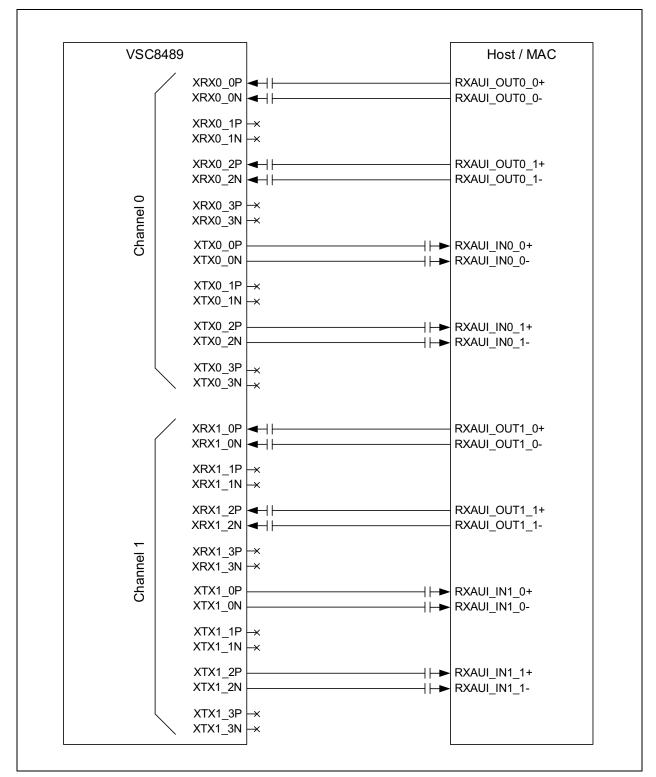

- 1GbE (1.25 Gbps) or SGMII uses either lane 0 or 3 only. The other three lanes can be left floating (no-connect). (See Figure 6-3.)

- · Check the signal directions, so that the outputs of one device connect to the inputs of the other device.

- Use AC coupling with 0.1 µF capacitors. Capacitors are best located close to the destination.

- The AC coupling capacitors are not required in cases wherein the driver satisfies the Common-mode voltage requirements of the receiver.

- The VSC8489 has internal termination on the XRX inputs, so external termination resistors are not needed. The host typically has internal termination also. If it does not, then 100Ω termination resistors may be needed on the XTX signals at the host's end.

- Best performance will result when SerDes traces are placed using the following design rules:

- Traces should be routed as 50Ω (100Ω differential) controlled impedance transmission lines (microstrip or stripline).

- Traces should be of equal length (within 30 mils) on each differential pair to minimize skew.

- Traces should be run adjacent to a single ground plane to match impedance and minimize noise.

- Spacing equal to five times the ground-plane gap between adjacent tracks is recommended to reduce crosstalk between SerDes pairs. A minimum spacing of three times the ground-plane gap is required.

- Traces should avoid vias and layer changes. If layer changes cannot be avoided, mode-suppression vias should be included next to the signal vias to attenuate any radiating spurious fields.

- Guard vias should be placed no greater than one-quarter wavelength apart around the differential pair tracks.

FIGURE 6-2: RXAUI CONNECTIONS

# 7.0 REFERENCE CLOCKS

• Table 7-1 shows information on reference clocks.

| Pin Name | Pin Number | Туре | Level | Description                             |  |  |  |

|----------|------------|------|-------|-----------------------------------------|--|--|--|

| WREFCKN  | J14        | I    | CML   | WAN reference clock input, complement   |  |  |  |

| WREFCKP  | H14        | ļ    | CML   | WAN reference clock input, true         |  |  |  |

| XREFCKN  | F14        | I    | CML   | Reference clock input, complement       |  |  |  |

| XREFCKP  | F13        | I    | CML   | Reference clock input, true             |  |  |  |

| SREFCKN  | J12        | ļ    | CML   | SyncE reference clock input, complement |  |  |  |

| SREFCKP  | H12        | I    | CML   | SyncE reference clock input, true       |  |  |  |

| MODE0    | K11        | I    | LVTTL | Mode select input bit 0                 |  |  |  |

| MODE1    | M9         | l    | LVTTL | Mode select input bit 1                 |  |  |  |

#### TABLE 7-1: REFERENCE CLOCKS

#### 7.1 Device Reference Clocks

The VSC8489 has three reference clock inputs, WREFCK, XREFCK, and SREFCK. SyncE applications may use either one or two clocks, while non-SyncE applications use only XREFCK. Using all three reference clocks is unnecessary.

- WREFCK\_P/N may be used for one configuration of WAN plus SyncE as shown in Table 7-2.

- XREFCK\_P/N is a required reference clock for all operating modes. The frequency may be either 125 MHz or 156.25 MHz. XREFCK may be an ordinary oscillator for non-SyncE applications or a hitless (DPLL) clock for SyncE applications. The clock speed is set by the MODE1 input. Users must take note of the following when setting the clock speed:

- Pull MODE1 low for 156.25 MHz.

- Pull MODE1 high for 125 MHz.

- MODE0 must always be pulled low.

- SREFCK\_P/N may be used for certain SyncE applications, but it is not required for SyncE. See Section 7.2, "Synchronous Ethernet" for more details.

Table 7-2 lists reference clock configurations for different modes:

| Mode                            | XREFCK                  | WREFCK     | SREFCK     | TX CMU REF | RX CMU REF |

|---------------------------------|-------------------------|------------|------------|------------|------------|

| 10.3125G LAN Single Ref.        | 156.25 MHz              | —          | —          | XREFCK     | XREFCK     |

| 9.95328G WAN Single Ref.        | 156.25 MHz              | —          | —          | XREFCK     | XREFCK     |

| 1.25G LAN Single Ref.           | 156.25 MHz              | —          | —          | XREFCK     | XREFCK     |

| 10.3125G LAN Single Ref.        | 125 MHz                 | —          | —          | XREFCK     | XREFCK     |

| 9.95328G WAN Single Ref.        | 125 MHz                 | —          | —          | XREFCK     | XREFCK     |

| 1.25G LAN Single Ref.           | 125 MHz                 | —          | —          | XREFCK     | XREFCK     |

| 10.3125G Sync-E LAN Single Ref. | 156.25 MHz<br>(Hitless) | —          | _          | XREFCK     | XREFCK     |

|                                 | 156.25 MHz              | —          | 161.13 MHz | SREFCK     | XREFCK     |

| 10.3125G Sync-E LAN Dual Ref.   | 156.25 MHz              | —          | 156.25 MHz | SREFCK     | XREFCK     |

|                                 | 156.25 MHz              | —          | 125 MHz    | SREFCK     | XREFCK     |

| 9.95328G Sync-E WAN Single Ref. | 156.25 MHz<br>(Hitless) | —          |            | XREFCK     | XREFCK     |

| 9.95328G Sync-E WAN Dual Ref.   | 156.25 MHz              | _          | 155.52 MHz | SREFCK     | XREFCK     |

| 9.95328G Sync-E WAN Dual Ref.   | 156.25 MHz              | 155.52 MHz | _          | WREFCK     | WREFCK     |

TABLE 7-2: REFERENCE CLOCK CONFIGURATIONS

| TABLE 7-2: | <b>REFERENCE CLOCK CONFIGURATIONS (CONTINUED)</b> |

|------------|---------------------------------------------------|

| IADLE /-Z: | REFERENCE CLOCK CONFIGURATIONS (CONTINUED)        |

| Mode                         | XREFCK                  | WREFCK | SREFCK | TX CMU REF | RX CMU REF |

|------------------------------|-------------------------|--------|--------|------------|------------|

| 1.25G Sync-E LAN Single Ref. | 156.25 MHz<br>(Hitless) | —      |        | XREFCK     | XREFCK     |

· Users must ensure that the following are executed when using reference clocks:

- Meet the jitter requirements from the data sheet.

- Meet the amplitude specifications given in the data sheet. Note that **XREFCK\_P/N** and **WREFCK\_P/N** are configurable for either high-swing or low-swing inputs. An API call is used to configure it. **SREFCK\_P/N** has a single amplitude range.

- Traces are routed as 50Ω (100Ω differential) controlled impedance transmission lines (microstrip or stripline).

- Use AC coupling with 0.1 µF capacitors. Capacitors are best placed close to the reference clock input pins.

- For some clock drivers, make sure that termination resistors are placed on the clock driver side. Termination resistors are not typically needed on the VSC8489 side of the capacitors.

- All reference clocks must be free from glitches or must be hitless.

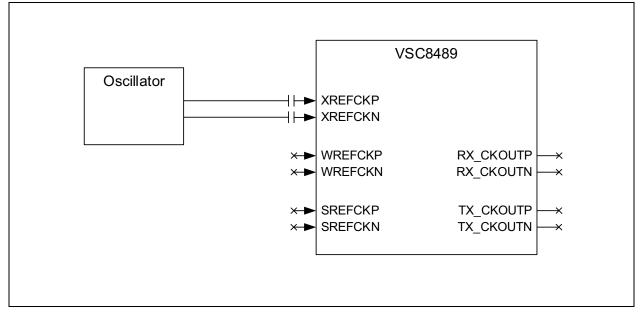

- Unused reference clocks can be left floating (no-connect). See Figure 7-1.

FIGURE 7-1: REFERENCE CLOCK FOR NON-SYNCE

#### 7.2 Synchronous Ethernet

There are multiple ways to implement clocking for Synchronous Ethernet. The two main ways are SyncE with Single Reference Clock and SyncE with non-hitless XREFCK, LAN Mode.

#### 7.2.1 SYNCE WITH SINGLE REFERENCE CLOCK

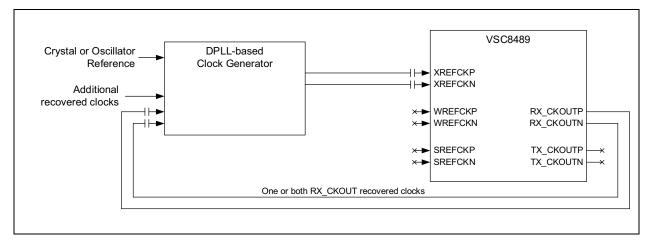

• Single clock LAN, external master: In this configuration, a hitless (DPLL) clock chip drives XREFCK. The clock changes gradually to match an externally referenced synchronous Ethernet clock. The change must be hitless to avoid data corruption. One of the port recovered clocks, output on the RXCKOUT pins, can be used as reference to the clock chip. WREFCK and SREFCK are not used. See Figure 7-2.

#### 7.2.2 SYNCE WITH NON-HITLESS XREFCK, LAN MODE

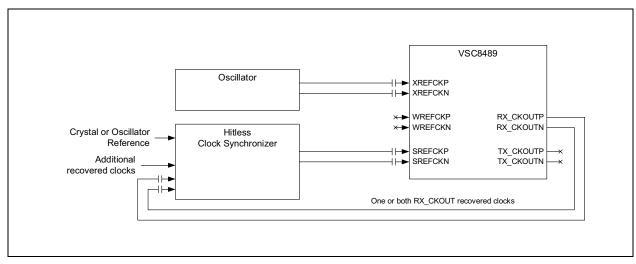

• Dual clock LAN, external master: In this configuration, the XREFCK remains connected to the stable 156.25 MHz system clock. All the line-side transmits are then synchronized to SREFCK. The F to delta F block accepts the SREFCK clock from external synchronous Ethernet master and generates the lane Sync signal to effectively synchronize all the line-side TX to this external clock. SREFCK must be 156.25 MHz. See Figure 7-3.

#### FIGURE 7-3: ALTERNATE SYNCE CLOCK CONFIGURATION

### 7.3 Output Clocks

• The output clocks of this device are specified in Table 7-3.

| Name      | Number | Туре | Level | Description                                                                         |

|-----------|--------|------|-------|-------------------------------------------------------------------------------------|

| RX0CKOUTN | A8     | 0    | CML   | Selectable clock output channel 0, complement. See register device 1, address A008. |

| RX0CKOUTP | B8     | 0    | CML   | Selectable clock output channel 0, true. See register device 1, address A008.       |

| RX1CKOUTN | P7     | 0    | CML   | Selectable clock output channel 1, complement. See register device 1, address A008. |

| RX1CKOUTP | N7     | 0    | CML   | Selectable clock output channel 1, true. See register device 1, address A008.       |

| TX0CKOUTN | A10    | 0    | CML   | Selectable clock output channel 0, complement. See register device 1, address A009. |

| TX0CKOUTP | B10    | 0    | CML   | Selectable clock output channel 0, true. See register device 1, address A009.       |

| TX1CKOUTN | P9     | 0    | CML   | Selectable clock output channel 1, complement. See register device 1, address A009. |

| TX1CKOUTP | N9     | 0    | CML   | Selectable clock output channel 1, true. See register device 1, address A009.       |

#### TABLE 7-3: OUTPUT CLOCKS

- RX0CKOUT and RX1CKOUT can be used to output the line-side RX recovered clock for each port. Alternatively, they can output the line-side TX clock or host-side RX recovered clock.

- TX0CKOUT and TX1CKOUT can be used to output the line-side TX clock for each port. Alternatively, they can output the line-side RX recovered clock or the host-side RX recovered clock.

- For 10G LAN mode, the only available output frequency is 161.1328125 MHz. For 10G WAN mode, the only available frequency is 155.52 MHz. For 1G mode, the only available output frequency is 125 MHz. Take note of the following guidelines:

- Traces should be routed as  $50\Omega$  ( $100\Omega$  differential) controlled impedance transmission lines (microstrip or stripline).

- Use AC coupling with 0.1 µF capacitors. Capacitors are best placed close to the reference clock input pins.

- Any unused output clocks can be left floating (no-connect).

# 8.0 MISCELLANEOUS

#### 8.1 Reset

• The VSC8489 must be reset at power-up. One option is to hold **RESETN** low for a minimum 1 ms after all power rails are up, control pins are stable, and clocks are active. Another option is to pulse **RESETN** low for a minimum 1 ms after power up. **RESETN** is typically driven by a voltage monitor device or by the management processor or FPGA. See Table 8-1 for more information on the reference clocks.

TABLE 8-1: RESET PIN

| Pin Name | Pin Number | Туре | Level | Description                                 |

|----------|------------|------|-------|---------------------------------------------|

| RESETN   | C6         | Ι    | LVTTL | Reset. Low = Reset. Internally pulled high. |

#### 8.2 Reference Resistor

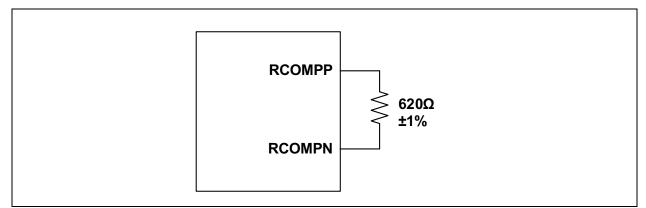

• Connect a  $620\Omega \pm 1\%$  resistor between **RCOMPN** and **RCOMPP** as shown in Figure 8-1. Refer to Table 8-2 for additional details on the pins.

TABLE 8-2:REFERENCE RESISTORS

| Pin Name | Pin Number | Туре | Level  | Description                     |

|----------|------------|------|--------|---------------------------------|

| RCOMPN   | M11        | _    | Analog | Resistor comparator, complement |

| RCOMPP   | L11        |      | Analog | Resistor comparator, true       |

#### FIGURE 8-1: RCOMP RESISTOR

#### 8.3 Serial Management Interfaces (SMI)

- The VSC8489 has SPI and MDIO management interfaces. Only one can be used at a time.

- SPI has the advantage of higher bandwidth and native addressing for 32-bit registers. (MDIO uses 16-bit data transfers, but the registers are 32 bits.)

- SPI is considered essential for MACSec or two-step 1588 due to performance reasons. MDIO performance is suitable for one-step 1588.

- · Make sure to wait at least 105 ms after the rising edge of RESETN before initiating an SMI activity.

- A Two-Wire (I<sup>2</sup>C) management interface is also available via GPIO\_2 and GPIO\_3 pins. However, it is not supported in the software API and is not recommended.

#### 8.3.1 SPI MANAGEMENT INTERFACE

- The SPI interface is the recommended interface for managing the VSC8489, especially for two-step IEEE 1588 and MACSec applications. See the Design Considerations section of the data sheets specified in Section 2.1, "Required References" for the maximum SPI frequency. This interface operates at 2.5V but is 3.3V tolerant. Refer to Table 8-3 for pin information.

- If the SPI interface is unused, pull the input pins to VDDTTL.

| Pin Name | Pin Number | Туре | Level | Description                 |

|----------|------------|------|-------|-----------------------------|

| MISO     | E11        | 0    | LVTTL | SPI slave data output       |

| MOSI     | E9         | I    | LVTTL | SPI slave data input        |

| SCK      | D11        | l    | LVTTL | SPI slave clock input       |

| SSN      | D9         |      | LVTTL | SPI slave chip select input |

#### TABLE 8-3: SPI MANAGEMENT PINS

#### 8.3.2 MDIO MANAGEMENT INTERFACE

- The maximum MDIO frequency is 2.5 MHz. This interface operates at 2.5V but is 3.3V tolerant.

- A pull-up resistor (~2 kΩ) is required on MDIO. Depending on the master device, a pull-up may also be needed on MDC.

- If multiple devices are on this bus, ensure that each device has a unique MDIO address as determined by the **PADDR[4:1]** pins.

- If the MDIO interface is unused, the pins can be left floating (no-connect). Refer to Table 8-4 for detailed information on MDIO pins.

| Pin Name | Pin Number | Туре | Level   | Description                                     |

|----------|------------|------|---------|-------------------------------------------------|

| MDC      | D7         | I    | LVTTL   | MDIO clock input                                |

| MDIO     | E7         | В    | LVTTLOD | MDIO data I/O                                   |

| PADDR1   | D10        | I    | LVTTL   | MDIO port address bit 1. Internally pulled low. |

| PADDR2   | C8         | I    | LVTTL   | MDIO port address bit 2. Internally pulled low. |

| PADDR3   | E10        | I    | LVTTL   | MDIO port address bit 2. Internally pulled low. |

| PADDR4   | E6         | I    | LVTTL   | MDIO port address bit 2. Internally pulled low. |

#### TABLE 8-4: MDIO MANAGEMENT

#### 8.4 IEEE 1588 Signals

• The VSC8489-17 and VSC8489-16 support IEEE 1588, while the VSC8489-02 does not. For the VSC8489-02, leave all these pins floating (no-connect). See Table 8-5 for pin information.

| Pin Name | Pin Number | Туре | Level | Description                                        |

|----------|------------|------|-------|----------------------------------------------------|

| CLK1588N | E8         | I    | CML   | 1588 logic clock input, complement                 |

| CLK1588P | D8         | I    | CML   | 1588 logic clock input, true                       |

| SPI_CLK  | K7         | 0    | LVTTL | Push-out SPI clock output for 1588 timestamp       |

| SPI_CS   | L10        | 0    | LVTTL | Push-out SPI chip select output for 1588 timestamp |

| SPI_DO   | L7         | 0    | LVTTL | Push-out SPI data output for 1588 timestamp        |

#### TABLE 8-5: IEEE 1588 SIGNALS

#### 8.4.1 1588 LOGIC CLOCK

- The CLK1588\_P/N input clock is used in most IEEE 1588 applications to clock the Local Time Counter (LTC). While it is also possible for the LTC to reference a data path clock or the host-side PLL instead of CLK1588\_P/N, these options are not typically used.

- Design guidelines for CLK1588\_P/N are as follows:

VSC8489

- CLK1588\_P/N supported frequencies are 125, 156.25, 200, and 250 MHz.

- For 1588 boundary clock applications, CLK1588 is typically supplied by a PLL-based reference.

- For 1588 transparent clock applications, CLK1588 should be sourced from a frequency locked clock that is common to all other timestamping interfaces

- Traces should be routed as 50Ω (100Ω differential) controlled impedance transmission lines (microstrip or stripline).

- Use AC coupling with 0.1 µF capacitors. Capacitors are best located close to the destination.

- The clock inputs are internally terminated, so external resistors are not needed.

- If CLK1588\_P/N are unused, they can be left floating (no-connect).

#### 8.4.2 PUSH OUT SPI MASTER INTERFACE

Serial time stamps can be pushed out on the SPI\_CLK, SPI\_CS, and SPI\_DO output pins. This interface is more

often used in two-step 1588 mode because of the higher rate of timestamps needing to be processed by the external processor or FPGA. For applications such as one-step transparent clock, it is typically not used. If unused,

these pins can be left floating (no-connect). The signals are 2.5V LVTTL.

#### 8.4.3 GPIO SIGNALS FOR 1588

• Several GPIO pins may be configured for 1588-specific functions as summarized in Table 8-6.

| Pin     | Function            | Requirements                                |

|---------|---------------------|---------------------------------------------|

| GPIO_0  | 1588-1PPS channel 0 | Open-drain output, pull-up required if used |

| GPIO_1  | 1588-load/save      | Input                                       |

| GPIO_4  | 1588-1PPS channel 1 | Open-drain output, pull-up required if used |

| GPIO_5  | 1588-PPS RI         | Input                                       |

| GPIO_9  | 1588-1PPS channel 1 | Open-drain output, pull-up required if used |

| GPIO_11 | 1588-1PPS channel 1 | Open-drain output, pull-up required if used |

#### TABLE 8-6: GPIO PINS FOR 1588 FUNCTIONS

#### 8.5 GPIO Pins

- The VSC8489 has 16 GPIO pins which may be used for general purpose I/O or for dedicated functions. Refer to Table 8-7 and Table 8-8.

- When used as outputs, these pins are open-drain and require a  $2-k\Omega$ -to-10-k $\Omega$  pull-up resistor.

- · Any unused GPIO pins can be left floating (no-connect).

- When configured to an LED mode, a GPIO output is active low. Power for LEDs should be 3.3V, with a load resistor in series.

| D4 | <b>Type</b><br>B                       |                                                                                                                   | Description                                                                      |

|----|----------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|    | В                                      |                                                                                                                   |                                                                                  |

| _  | _                                      | LVTTLOD                                                                                                           | General purpose I/O 0                                                            |

| D5 | В                                      | LVTTLOD                                                                                                           | General purpose I/O 1                                                            |

| E4 | В                                      | LVTTLOD                                                                                                           | General purpose I/O 2                                                            |

| E5 | В                                      | LVTTLOD                                                                                                           | General purpose I/O 3                                                            |

| F4 | В                                      | LVTTLOD                                                                                                           | General purpose I/O 4                                                            |

| F5 | В                                      | LVTTLOD                                                                                                           | General purpose I/O 5                                                            |

| K4 | В                                      | LVTTLOD                                                                                                           | General purpose I/O 6                                                            |

| K5 | В                                      | LVTTLOD                                                                                                           | General purpose I/O 7                                                            |

| K6 | В                                      | LVTTLOD                                                                                                           | General purpose I/O 8                                                            |

| L4 | В                                      | LVTTLOD                                                                                                           | General purpose I/O 9                                                            |

| L5 | В                                      | LVTTLOD                                                                                                           | General purpose I/O 10                                                           |

|    | E5<br>F4<br>F5<br>K4<br>K5<br>K6<br>L4 | E4     B       E5     B       F4     B       F5     B       K4     B       K5     B       K6     B       L4     B | E4BLVTTLODE5BLVTTLODF4BLVTTLODF5BLVTTLODK4BLVTTLODK5BLVTTLODK6BLVTTLODL4BLVTTLOD |

TABLE 8-7: GPIO PINS

| TADLE 0-7. |            |      |         |                        |

|------------|------------|------|---------|------------------------|

| Pin Name   | Pin Number | Туре | Level   | Description            |

| GPIO_11    | L6         | В    | LVTTLOD | General purpose I/O 11 |

| GPIO_12    | C10        | В    | LVTTLOD | General purpose I/O 12 |

| GPIO_13    | C11        | В    | LVTTLOD | General purpose I/O 13 |

| GPIO_14    | N11        | В    | LVTTLOD | General purpose I/O 14 |

| GPIO_15    | P11        | В    | LVTTLOD | General purpose I/O 15 |

# TABLE 8-7: GPIO PINS (CONTINUED)

#### TABLE 8-8:GPIO FUNCTIONS

| Pin    | Configuration Registers                | Function                                                                                                                                                                                              |

|--------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_0 | GPIO_0_Config_Status<br>GPIO_0_Config2 | Traditional I/O (default)<br>Observed internal signals<br>MOD_ABS_Channel_0<br>PMTICK<br>ROSI frame pulse 0<br>TX Activity LED<br>WIS_INTB<br>1588-1PPS channel 0<br>Leave unconnected when not used. |

| GPIO_1 | GPIO_1_Config_Status<br>GPIO_1_Config2 | Traditional I/O (default)<br>Observed internal signals<br>ROSI_CLK_0<br>RX Activity LED<br>WIS_INTA<br>1588-Load/Save<br>Leave unconnected when not used.                                             |

| GPIO_2 | GPIO_2_Config_Status<br>GPIO_2_Config2 | Traditional I/O<br>Observed internal signals<br>Slave Two-Wire serial – SDA (default)<br>ROSI_DATA_0<br>TX Activity LED<br>WIS_INTB                                                                   |

| GPIO_3 | GPIO_3_Config_Status<br>GPIO_3_Config2 | Traditional I/O<br>Observed internal signals<br>Slave Two-Wire serial – SCL (default)<br>TOSI_FRAME_PULSE_0<br>RX Activity LED<br>WIS_INTB                                                            |

| GPIO_4 | GPIO_4_Config_Status<br>GPIO_4_Config2 | Traditional I/O (default)<br>Observed internal signals<br>TOSI_CLK_0<br>TX Activity LED<br>WIS_INTB<br>1588-1PPS channel 1                                                                            |

| GPIO_5 | GPIO_5_Config_Status<br>GPIO_5_Config2 | Traditional I/O (default)<br>Observed internal signals<br>TOSI_INPUT_0<br>RX Activity LED<br>WIS_INTA<br>1588-PPS RI<br>Leave unconnected when not used.                                              |

| <b>TABLE 8-8:</b> | GPIO FUNCTIONS (CONTINUED)               |                                                                                                                                                                   |

|-------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_6            | GPIO_6_Config_Status<br>GPIO_6_Config2   | Traditional I/O (default)<br>Observed internal signals<br>Ch0 SFP 12C SDA<br>ROSI_FRAME_PULSE_1<br>TX Activity LED<br>WIS_INTB                                    |

| GPIO_7            | GPIO_7_Config_Status<br>GPIO_7_Config2   | Traditional I/O (default)<br>Observed internal signals<br>Ch0 SFP 12C SCL<br>ROSI_CLK_1<br>RX Activity LED<br>WIS_INTA                                            |

| GPIO_8            | GPIO_8_Config_Status<br>GPIO_8_Config2   | Traditional I/O (default)<br>Observed internal signals<br>MOD_ABS_Channel_0<br>PMTICK<br>ROSI_DATA_1<br>TX Activity LED<br>WIS_INTA                               |

| GPIO_9            | GPIO_9_Config_Status<br>GPIO_9_Config2   | Traditional I/O (default)<br>Observed internal signals<br>MOD_ABS_Channel_1<br>PMTICK<br>TOSI_FRAME_PULSE_1<br>RX Activity LED<br>WIS_INTA<br>1588-1PPS channel 1 |

| GPIO_10           | GPIO_10_Config_Status<br>GPIO_10_Config2 | Traditional I/O (default)<br>Observed internal signals<br>Ch1 SFP 12C SDA<br>TOSI_CLK_1<br>TX Activity LED<br>WIS_INTB                                            |

| GPIO_11           | GPIO_11_Config_Status<br>GPIO_11_Config2 | Traditional I/O (default)<br>Observed internal signals<br>Ch1 SFP 12C SCL<br>TOSI_INPUT_1<br>RX Activity LED<br>WIS_INTA<br>1588-1PPS channel 1                   |

| GPIO_12           | GPIO_12_Config_Status<br>GPIO_12_Config2 | Traditional I/O (default)<br>Observed internal signals<br>TX Activity LED<br>WIS_INTA                                                                             |

| GPIO_13           | GPIO_13_Config_Status<br>GPIO_13_Config2 | Traditional I/O (default)<br>Observed internal signals<br>RX Activity LED<br>WIS_INTA                                                                             |

| GPIO_14           | GPIO_14_Config_Status<br>GPIO_14_Config2 | Traditional I/O (default)<br>Observed internal signals<br>TX Activity LED<br>WIS_INTA                                                                             |

| GPIO_15           | GPIO_15_Config_Status<br>GPIO_15_Config2 | Traditional I/O (default)<br>Observed internal signals<br>RX Activity LED<br>WIS_INTA                                                                             |

# TABLE 8-8: GPIO FUNCTIONS (CONTINUED)

#### 8.6 JTAG

• If JTAG is not used, **TRSTB** should be pulled low. The other pins may be left floating (no connect). See Table 8-9 for JTAG pin information.

| Pin Name | Pin Number | Туре | Level | Description                                              |

|----------|------------|------|-------|----------------------------------------------------------|

| TCK      | K9         | I    | LVTTL | Boundary scan, test clock input. Internally pulled high. |

| TDI      | L8         | I    | LVTTL | Boundary scan, test data input. Internally pulled high.  |

| TDO      | K8         | 0    | LVTTL | Boundary scan, test data output                          |

| TMS      | M5         | I    | LVTTL | Boundary scan, test mode select. Internally pulled high. |

| TRSTB    | K10        | I    | LVTTL | Boundary scan, test Reset input. Internally pulled high. |

#### TABLE 8-9: JTAG PINS

#### 8.7 Temperature Sensor Diode

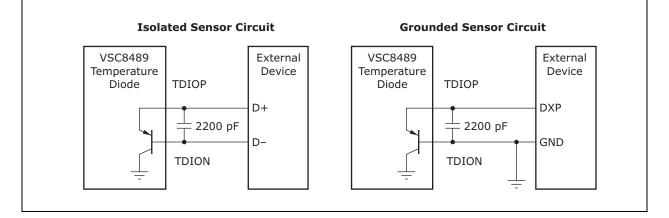

- The temperature sensor diode pins provide access to an on-die diode and internal circuitry for monitoring die temperature. (See Table 8-10.) To use it, connect an external thermal sensor, located on the board or in a stand-alone measurement kit.

- The cathode is connected internally to ground, so the temperature sensor must be chosen accordingly.

- Temperature measurement using a thermal diode is very sensitive to noise. Figure 8-2 illustrates a generic application design.

#### TABLE 8-10: TEMPERATURE SENSOR PINS

| Pin Name | Pin Number | Туре                                           | Level                                      | Description                           |

|----------|------------|------------------------------------------------|--------------------------------------------|---------------------------------------|

| TDION    | B7         | — Analog Temperature diode, negative (cathode) |                                            | Temperature diode, negative (cathode) |

| TDIOP    | A7         | _                                              | Analog Temperature diode, positive (anode) |                                       |

#### FIGURE 8-2: THERMAL DIODE CONNECTIONS

#### 8.8 Unused Pins

• Follow the instructions given for these unused pins in Table 8-11.

TABLE 8-11: UNUSED PINS

| Pin Name | Pin Number | Туре | Level | Description                                                              |  |

|----------|------------|------|-------|--------------------------------------------------------------------------|--|

| NC       | M8         | _    | _     | No connect (formerly labeled as ANATEST)                                 |  |

| SCAN_EN  | L9         | Ι    | LVTTL | Scan enable input, factory test purposes only. Keep connected to ground. |  |

# VSC8489

NOTES:

# 9.0 HARDWARE CHECKLIST SUMMARY

#### TABLE 9-1: HARDWARE DESIGN CHECKLIST

| Section                                                   | Check                                              | Explanation                                                                                                                                                                                                                                                                                                           | ٧ | Notes |

|-----------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|

| Section 2.0, "General Considerations"                     | Section 2.1, "Required References"                 | All necessary documents are on hand.                                                                                                                                                                                                                                                                                  |   |       |

|                                                           | Section 2.2, "Pin Check"                           | The pins match the data sheet.                                                                                                                                                                                                                                                                                        |   |       |

|                                                           | Section 2.3, "Ground"                              | All ground pins connect to a single ground. Solid ground planes should be used.                                                                                                                                                                                                                                       |   |       |

| Section 3.0, "Power"                                      | Section 3.1, "Current Requirements"                | Ensure that the power rails can supply adequate current.                                                                                                                                                                                                                                                              |   |       |

|                                                           | Section 3.2, "Power Supply Planes"                 | Make sure that the analog planes are filtered with ferrite beads,<br>while digital planes are not. Consider possible resistive voltage<br>drop in distribution.                                                                                                                                                       |   |       |

|                                                           | Section 3.3, "Analog Power Plane Filter-<br>ing"   | Check if each analog power rail has ferrite bead filtering, with<br>bulk capacitors on both sides of the bead and one capacitor<br>near each power pin. Ferrite beads must meet current and DC<br>resistance requirements. Consider DC voltage drop across the<br>ferrite beads.                                      |   |       |

|                                                           | Section 3.4, "Decoupling Capacitors"               | Ensure that there is one decoupling capacitor near each power pin and at least a 10 $\mu$ F bulk capacitor per rail. See Figure 3-1.                                                                                                                                                                                  |   |       |

| Section 4.0, "Thermal Consider                            | rations"                                           | Do not use thermal relief for ground vias.                                                                                                                                                                                                                                                                            |   |       |

| Section 5.0, "Media SerDes<br>Interface"                  | Section 5.1, "Media SerDes Design<br>Rules"        | Unless common mode voltages are compatible, make sure to<br>use AC coupling caps for non-SFP applications. SFP modules<br>include AC coupling. Follow good differential signal layout prac-<br>tices. Pull unused LOPC inputs low.                                                                                    |   |       |

|                                                           | Section 5.2, "Connecting to 10G SFP+ or<br>1G SFP" | Take note that AC coupling caps are not needed. Connect <b>TXOUT</b> to <b>TD</b> of SFP and <b>RXIN</b> to <b>RD</b> . SFP single-ended outputs need pull-ups. Consider connecting the SFP Two-Wire and other controls to a host rather than the VSC8489. Other SFP status and control may also connect to the host. |   |       |

| Section 6.0, "Host Interface<br>(XAUI, RXAUI, and SGMII)" | Section 6.1, "Host Serial Interface<br>Design"     | Verify if XAUI uses all four lanes and RXAUI uses lanes 0 and<br>2. Check if 1GbE uses lane 0 (or 3). Make sure to leave unused<br>lanes floating. Unless Common-mode voltage levels are com-<br>patible, use AC coupling. Follow good differential signal layout<br>practices.                                       |   |       |

# TABLE 9-1: HARDWARE DESIGN CHECKLIST (CONTINUED)

| Section                            | Check                                                  | Explanation                                                                                                                                                                                                                         | v | Notes |

|------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|

| Section 7.0, "Reference<br>Clocks" | Section 7.1, "Device Reference Clocks"                 | Check the table of clocking modes. <b>XREFCK</b> is required for all cases (125 MHz or 156.25 MHz). Usually <b>WREFCK</b> and <b>SREFCK</b> are not needed. Leave unused input clocks floating. Ensure jitter requirements are met. | - |       |

|                                    | Section 7.2, "Synchronous Ethernet"                    | Take note that the most common configurations use a hitless clock source for XREF. Recovered clocks on <b>RX_CKOUT</b> can be fed to the hitless clock source. Other configurations are possible and can use <b>SREFCK</b> .        |   |       |

|                                    | Section 7.3, "Output Clocks"                           | The external receiver of the recovered clock for SyncE must be<br>configured for the available output frequency: 10G LAN Mode =<br>161.1328125 MHz, 10G WAN mode = 155.52 MHz, and 1G<br>mode = 125 MHz.                            |   |       |

| Section 8.0, "Miscellaneous"       | Section 8.1, "Reset"                                   | Ensure that there is a rising edge on <b>RESETN</b> following power rails and clock being up.                                                                                                                                       |   |       |

|                                    | Section 8.2, "Reference Resistor"                      | Make sure to connect a $620\Omega \pm 1\%$ resistor between RCOMPN and RCOMPP.                                                                                                                                                      |   |       |

|                                    | Section 8.3, "Serial Management Inter-<br>faces (SMI)" | Remember that among the three options (SPI, Two-Wire, and MDIO), only one can be used at a time. SPI is strongly recommended. MDIO is suitable only if MACSec and two-step 1588 are not used.                                       |   |       |

|                                    | Section 8.4, "IEEE 1588 Signals"                       | Make sure to supply a quality clock for CLK1588 input clock.<br>The push-out SPI interface is only for outputting timestamps to<br>the host processor. Some 1588 functions are available on<br>GPIO pins.                           |   |       |

|                                    | Section 8.5, "GPIO Pins"                               | Take note that a variety of functions are available: interrupts, 1588, GPIO, etc. When output, they are open drain and require external pull-ups.                                                                                   |   |       |

|                                    | Section 8.6, "JTAG"                                    | If JTAG is unused, <b>TRSTB</b> should be pulled low and the other JTAG pins can be left unconnected.                                                                                                                               |   |       |

|                                    | Section 8.7, "Temperature Sensor Diode"                | If used, connect to an external temperature sensor device such<br>as the MCP9902, with <b>TDIOP</b> connected to the positive node<br>and <b>TDION</b> to the negative node.                                                        |   |       |

|                                    | Section 8.8, "Unused Pins"                             | Verify if pin L9 is connected to ground. Pin M8 should be left unconnected.                                                                                                                                                         |   |       |

# APPENDIX A: REVISION HISTORY

| Revision Level & Date     | Section/Figure/Entry | Correction |

|---------------------------|----------------------|------------|

| DS00003602A<br>(08-27-20) | Initial release      |            |

#### TABLE A-1: REVISION HISTORY

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

#### Technical support is available through the web site at: http://microchip.com/support

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- · Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are

committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection

feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or

other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet Iogo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified Iogo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-6666-6

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# Worldwide Sales and Service

#### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston** Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141 Japan - Osaka

Tel: 81-6-6152-7160

Japan - Tokyo Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore

Taiwan - Kaohsiung

Taiwan - Taipei

Thailand - Bangkok

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

Italy - Padova Tel: 39-049-7625286

EUROPE

Austria - Wels

Tel: 43-7242-2244-39

Tel: 45-4485-5910

Fax: 45-4485-2829

Tel: 358-9-4520-820

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

**Germany - Garching**

Tel: 49-2129-3766400

Germany - Heilbronn

Germany - Karlsruhe

Tel: 49-7131-72400

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Rosenheim

Tel: 49-8031-354-560

Israel - Ra'anana

Italy - Milan

Tel: 972-9-744-7705

Tel: 39-0331-742611

Fax: 39-0331-466781

Tel: 49-8931-9700

Germany - Haan

Finland - Espoo

France - Paris

Fax: 43-7242-2244-393

**Denmark - Copenhagen**

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

**Romania - Bucharest** Tel: 40-21-407-87-50

Spain - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

Tel: 65-6334-8870 Taiwan - Hsin Chu Tel: 886-3-577-8366

Tel: 886-7-213-7830

Tel: 886-2-2508-8600

Tel: 66-2-694-1351