# **RTG4 FPGA High-Speed Serial Interfaces User Guide**

# Introduction (Ask a Question)

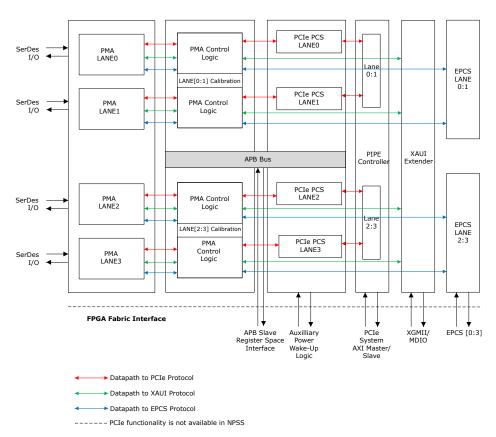

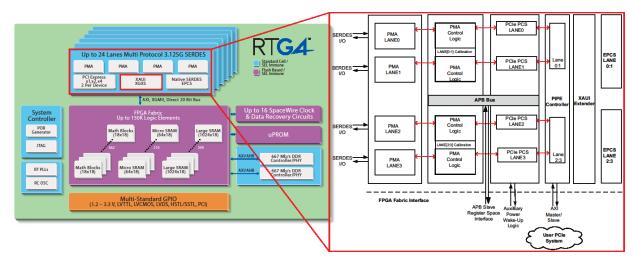

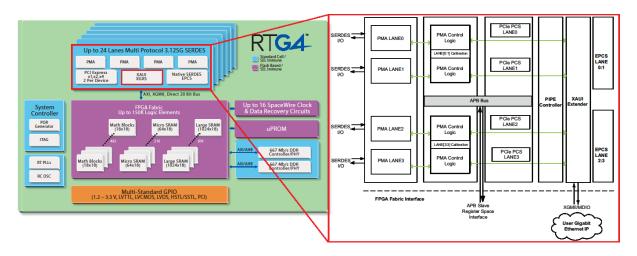

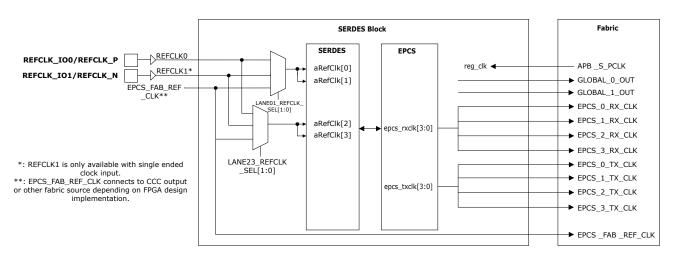

The RTG4<sup>™</sup> FPGA device includes a Serializer/De-serializer (SerDes) block that provides support for several serial communication standards. This module integrates several functional blocks to support multiple high-speed serial protocols within the device. The SerDes block has embedded functionality to integrate required features used with several protocols and is used with FPGA hosted application designs.

This user guide applies to part numbers starting with RT4G150 and 5962-1620.

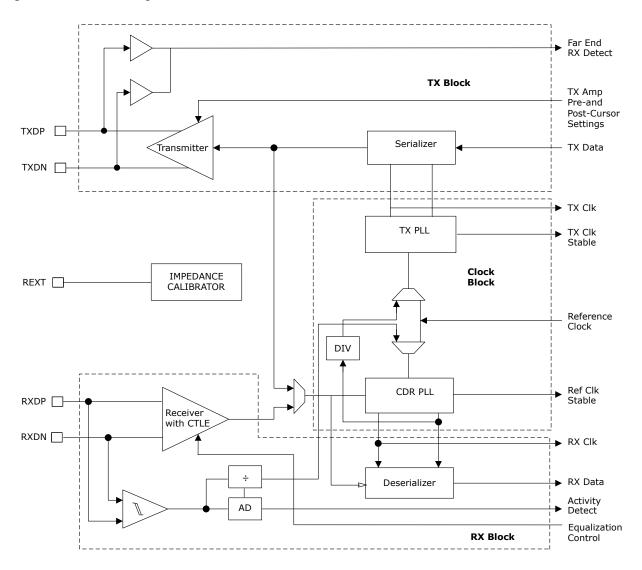

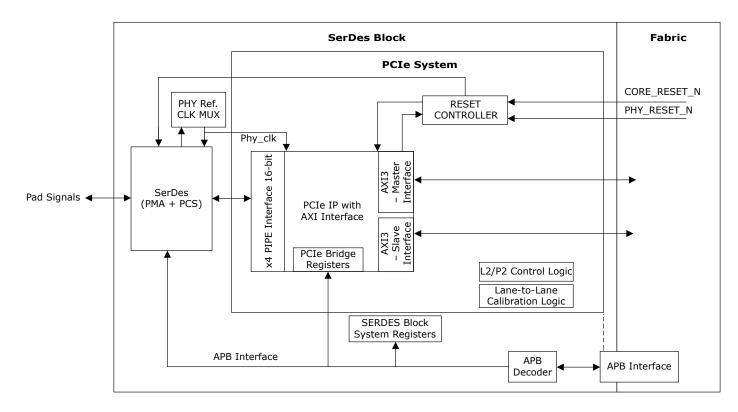

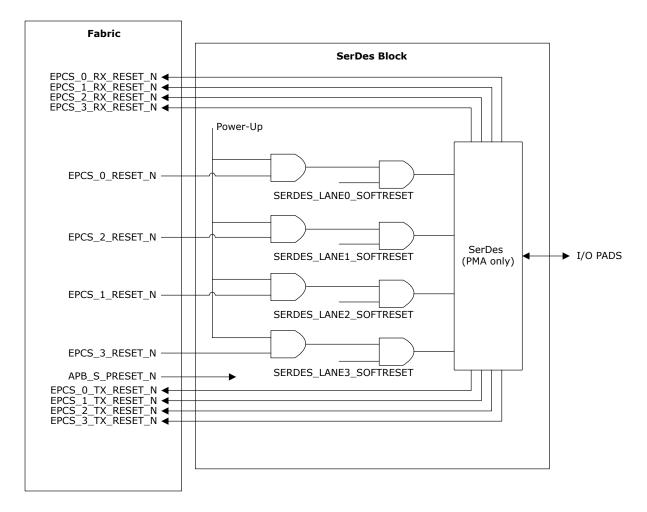

#### Figure 1. RTG4 SerDes Block Diagram

# Features (Ask a Question)

The SerDes block has the following features:

- 6 SerDes/PCS blocks (Quads/4x Lanes)—up to 24 total SerDes lanes

- x1, x2, and x4 PCIe endpoint protocol support

- PCIe is compliant with the PCIe base specification 1.1 for Gen1 and PCIe base specification 2.1 for Gen1 or Gen2—only supports the 2.5 Gbps variant of the Gen2 specification.

- 10 Gigabit attachment unit interface (XAUI) protocol supports four lanes of 3.125 Gbps (10 Gbps with overhead).

- External Physical Coding Sub-layer (EPCS) interface supports user defined high serial protocols, such as Serial Gigabit Media Independent Interface (SGMII) 1000-BaseX, and JESD204B protocol support up to 3 Gbps.

- Single-Event Upset (SEU) mitigation techniques including Triple-Module Redundancy (TMR) logic triplication and self-correcting latches.

- Single or multiple serial protocol modes of operation. In multiple serial protocol modes, two protocols can be implemented on the four physical lanes of the SerDes block.

- Arm<sup>®</sup> AMBA<sup>®</sup> Advanced Peripheral Bus (APB-3) compliant slave interface for SerDes block configuration register access.

For AC and DC specification, see the RTG4 FPGA Datasheet.

# Device Support (Ask a Question)

The following table lists the SerDes blocks available in each RTG4 device.

#### Table 1. Available SerDes Blocks in RTG4 Devices

| Blocks         | RT4G150 |

|----------------|---------|

| SerDes blocks  | 6       |

| SerDes lanes   | 24      |

| PCle endpoints | 2       |

**Note:** The specified number of SerDes blocks varies depending on the device package. PCIe endpoints support x1, x2, or x4 PCIe links.

# **Table of Contents**

| Inti | oductio  | on                                            | 1   |

|------|----------|-----------------------------------------------|-----|

|      | Feature  | es                                            | 1   |

|      | Device   | Support                                       | 2   |

| 1.   | Device   | Architecture                                  | 4   |

|      | 1.1.     | SerDes Block Serial Protocols Support         | 5   |

| 2.   | PMA      |                                               | 7   |

|      | 2.1.     | Features                                      | 7   |

|      | 2.2.     | Transmit Block                                | 8   |

|      | 2.3.     | Receive Block                                 | 11  |

|      | 2.4.     | Clock Block                                   | 15  |

|      | 2.5.     | Calibration Resource Sharing                  | 19  |

|      | 2.6.     | SerDes Block-I/O Signal Interface             | 20  |

| 3.   | PCB De   | esign                                         | 22  |

| 4.   | Physica  | al Coding Sublayers                           | 23  |

|      | -        | PCI Express                                   |     |

|      |          | XAUI                                          |     |

|      |          | EPCS                                          |     |

|      |          | Register Initialization                       |     |

|      |          |                                               |     |

| 5.   |          | s Block Register Access Map                   |     |

|      |          | Configuration of SerDes Block                 |     |

|      | 5.2.     | SerDes Register Lock Bits Configuration       | 167 |

| 6.   | Debug    |                                               | 170 |

|      | 6.1.     | Diagnostic Loopbacks                          | 170 |

|      | 6.2.     | Pseudo-Random Bit Sequences Pattern Generator |     |

|      | 6.3.     | Pseudo-Random Bit Sequences Pattern Checker   | 173 |

|      | 6.4.     | Custom Pattern Generator                      |     |

|      | 6.5.     | Using SmartDebug Utility for SerDes           |     |

| 7.   | Revisio  | on History                                    | 175 |

| Mic  | rochip F | FPGA Support                                  | 178 |

| Mic  | rochin I | Information                                   | 178 |

|      | -        | icrochip Website                              |     |

|      |          | ct Change Notification Service                |     |

|      |          | ner Support                                   |     |

|      |          | hip Devices Code Protection Feature           |     |

|      |          | Votice                                        |     |

|      | -        | narks                                         |     |

|      |          | y Management System                           |     |

|      | Worldv   | wide Sales and Service                        |     |

# 1. Device Architecture (Ask a Question)

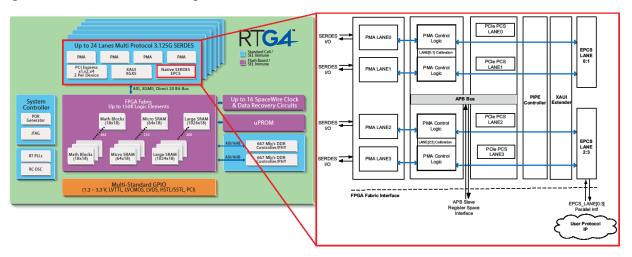

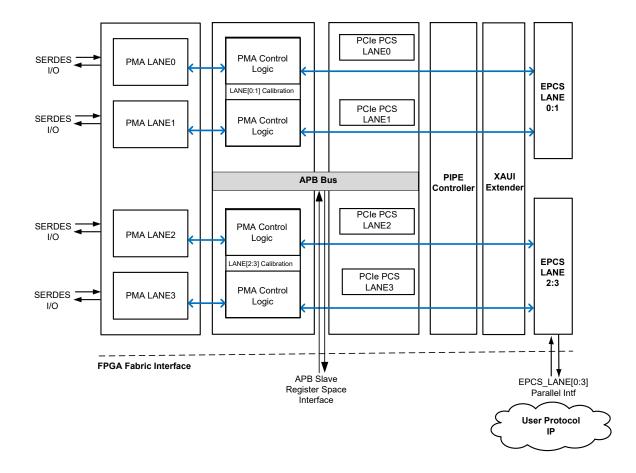

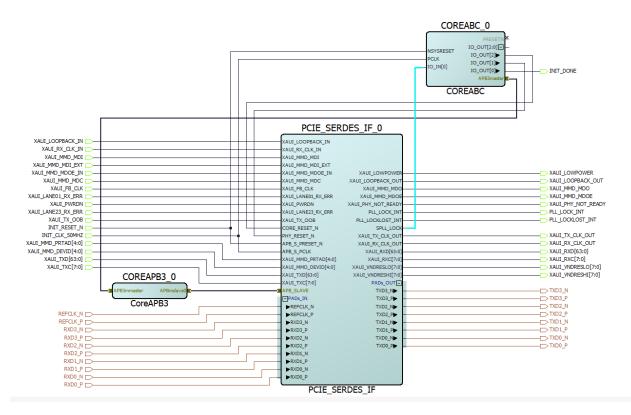

The RTG4 device family has up to six SerDes blocks. Each SerDes block interfaces with fabric, program control, and four duplex SerDes differential I/O pads known as SerDes Lanes. Individually, the SerDes block shows a high-level view of the RTG4 SerDes block. The SerDes block, which is dependent on the FPGA design implemented protocol, provides an AXI3 (PCIe), XGMII (XAUI), or native SerDes clock and data (EPCS) along with the control plane interface APB.

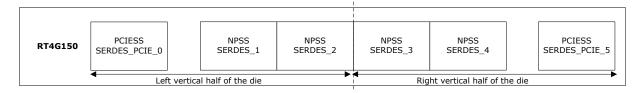

As shown in the following figure, two of the RTG4 SerDes block modules in each device contain PCIe endpoint functionality. These PCIe Sub-System (PCIESS) modules include PCIe functionality, whereas Non-PCIe Sub-System (NPSS) modules do not include PCIe logic.

The following figure shows the number of PCIESS and NPSS modules per device. PCIESS modules act as a superset, with all the capabilities of NPSS modules and PCIe functionality included. The north side of the device includes three SerDes blocks on the right and left vertical halves of the array.

#### Figure 1-1. SerDes Block Capability Per Device

Each of the SerDes blocks includes:

- **PMA**: This block implements up to four channels of high-speed I/O, the physical media attachment layer (PMA), and a physical coding sub-layer (PCS) of PCIe protocols. It also implements the PMA calibration and control logic. This PCS layer is compliant with the Intel PIPE 2.0 specification. The PCIe PCS functionality can be bypassed completely in order to use the SerDes lanes for protocols other than PCIe. This allows the use of the PMA in various PHY modes and the implementation of different protocols in the RTG4 device.

- **PCIe System**: This block implements the x1, x2, and x4 lanes PCIe endpoint (Regular and Reverse Lanes mode) with an AXI3 interface to the fabric.

**Important:** PCIe functionality is included only in the two PCIESS blocks.

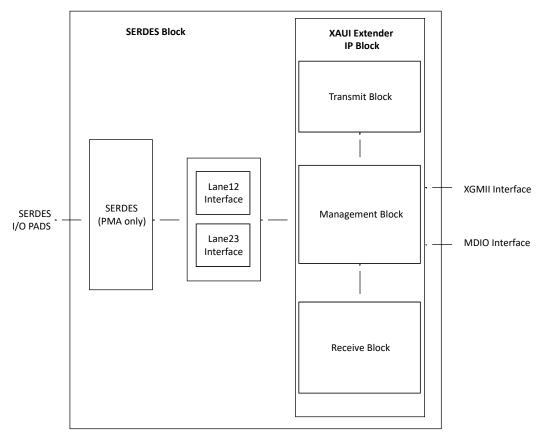

- **XAUI Extender**: This block is an XGMII extender to support the XAUI protocol through a FPGA IP MAC core in the FPGA fabric.

- **EPCS**: This block is a Basic mode used to extend the SerDes for custom support access to the FPGA fabric.

- SerDes Block System Register: The SerDes block system registers control the SerDes block module for single protocol or multi-protocol support implementation. These registers are accessible through the 32-bit APB interface, and the default values of these registers are configured using the Libero<sup>®</sup> System-on-Chip (SoC) software. The SerDes block is initially configured at power-up with parameters determined during the FPGA design flow using the Libero SoC software. The SerDes block configuration can be subsequently changed by writing the related control registers through the APB interface.

The following table lists single protocol usage for SerDes block module.

#### Table 1-1. SerDes Block Module—Single Protocol Usage Overview

| Protocol | SerDes Block Description                                                                                                                                                      | (Gbps)    | Reference Clock<br>(Typ.) lnput<br>Frequency |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------|

| PCle     | The SerDes block is configured to use PCIe Gen1/2 x4, x2, and x1 link modes.<br>The PCIe link can be configured in Regular or Reversed mode.                                  | 2.5       | 100 MHz                                      |

| XAUI     | The SerDes block is configured to use all four lanes. In XAUI mode, all lanes are used and the PCIe system is put in RESET state.                                             | 4 x 3.125 | 156.25 MHz                                   |

| EPCS     | In EPCS mode, any serial protocol can be run through the EPCS interface to the fabric. EPCS mode is used to implement many other standard protocol interfaces, such as SGMII. | 1-3.125   | 100–160 MHz                                  |

# 1.1 SerDes Block Serial Protocols Support (Ask a Question)

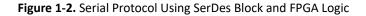

The SerDes block supports the implementation of multiple high-speed serial protocols. Although each of the serial protocols is unique, all of them are layered protocol stacks, and the implementation varies from one layer to the next layer. Typically, the physical layer consists of fixed functionality common to multiple packet-based protocols, while the upper layers tend to be more customizable.

The advantage of connecting the FPGA logic and SerDes blocks is that it allows multiple serial protocols in the RTG4 devices. The following figure shows the implementation of PCIe, XAUI, and EPCS protocols using the SerDes block and FPGA fabric and the fixed modules contained within the SerDes block per application. As shown in the example, PCIe applications include many functional blocks within the SerDes block, whereas EPCS requires more FPGA IP blocks for complete system implementation.

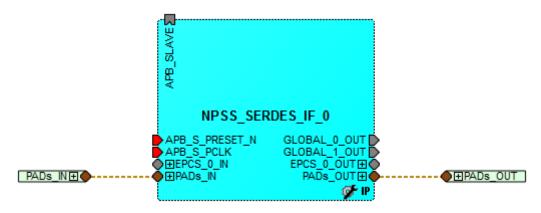

The RTG4 devices contain a mix of SerDes blocks with different embedded protocol support logic. The PCIe sub-system (PCIESS) within the SerDes blocks implements the PCIe EP specification for transaction, data link, and physical layers. The PCIESS SerDes block can also be used for XAUI and customized EPCS protocols such as SGMII and JESD204B. The RTG4 also includes similar SerDes blocks, which have the same XAUI and EPCS capabilities without embedded PCIe logic, known as NPSS. All RTG4 devices include two PCIESS blocks and various quantities of NPSS blocks based on the FPGA device and package sizes.

- SERDES BLOCK contained functionality

MDI – Media Dependent Interface

# 2. PMA (Ask a Question)

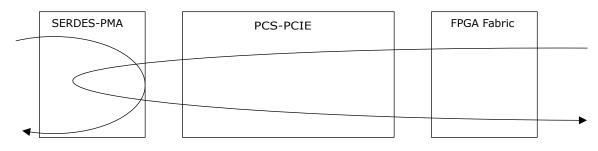

The physical media attachment (PMA) of the RTG4 FPGA family is included within the SerDes block module. This section describes the fixed hardware blocks and the physical hardware capabilities of PMA.

# 2.1 Features (Ask a Question)

The following are the main features of PMA:

- Transmit block includes differential impedance matching output buffers, serializer logic, transition de-emphasis, and receiver detection circuitry

- Receive block includes differential current mode logic (CML) input buffers, de-serializer logic, on-chip termination, and continuous-time linear equalization (CTLE)

- Clock block includes clock recovery circuitry and clock management logic

- Configuration control and status register access

The PMA block contains high-speed analog front-end logic, transmit PLL, clock and data recovery (CDR) PLL, calibration, and the voltage offset cancellation mechanism.

The following figure shows a simplified functional block diagram of the PMA block. Each of the PMA blocks includes three sub-functions—Transmit, Receive and Clock block. The three blocks have several primary inputs and outputs as well as control and status connections. The control and status nodes are either ports or registers used in conjunction with the implementation.

# 2.2 Transmit Block (Ask a Question)

The transmit macro includes a serializer, which receives a 20-bit (maximum) data-word synchronous with a transmit clock and serializes it into a single stream of differentially transmitted data to the lane. This macro supports multi-level output drive and multi-level transition (pre-and post-cursor) 3-tap de-emphasis while maintaining proper impedance. For information, see the 2.6. SerDes Block-I/O Signal Interface listed in Table 2-5. The transmit outputs do not support hot-swap.

# 2.2.1 Transmit Output Buffer (Ask a Question)

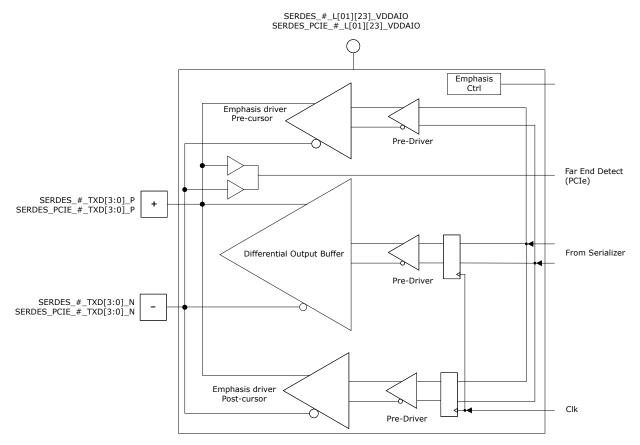

The following figure shows the transmit block with a high-speed and differential impedance matching output buffer. It supports multi-level drive, pre-cursor and post-cursor transition deemphasis, Multi-Level Common mode, and calibrated output impedance. The output driver utilizes the current diversion circuitry to maintain the programmable amplitude adjustments. These parameters are predefined by the Libero software but can be tuned by the designer. The transmitters are suitable for connections to systems using Low-Voltage Differential Signaling (LVDS) and High-Speed Current-Steering Logic (HCSL)type signaling. For information about the DC output specifications, see RTG4 FPGA Datasheet.

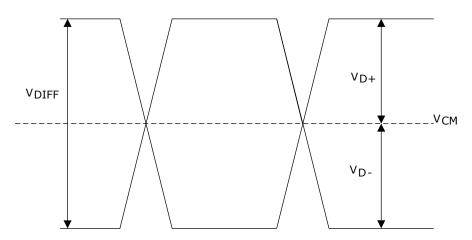

The transmit output voltage levels—VDIFFp-p and VCM, are nominally set by the Libero software based on key protocol parameters. The limits of these settings are dependent on the analog SerDes I/O supply. The output voltage parameters are defined by the following equations:

- VDIFFp-p = 2\*(VD+ VD-)

- VCM = 0.5\*(VD+ VD-)

The following figure shows the transmit output signal parameters.

Figure 2-3. Transmit Output Signal Parameters

The main tap of the transmit output block is programmable and controlled by the TX\_AMP\_RATIO setting. The amplitude is set as a ratio from 100% (full-swing) to 0%. The ratio is determined as a function of the initial lane calibration. Therefore, the device calibrates the link and determines an optimized impedance, and the ratio setting uses this calibration to baseline the needed amplitude. This allows flexibility to match receiver specifications on the far-end of the link. Valid settings for TX\_AMP\_RATIO are between 0 and 128, where 128 denotes 100% swing.

Figure 2-5. Transmit AMP RATIO Setting in Libero SoC

| LANE0_TX_AMP_RATIO | 0x1024 | read-write | 0x0 | 0x80 | 8     |

|--------------------|--------|------------|-----|------|-------|

| TX_AMP_RATIO       |        | read-write | 0x0 | 0x80 | [7:0] |

The transmit amplitude is adjusted by the TX\_AMP\_RATIO configuration settings. The TX\_AMP\_RATIO setting is controlled by Libero software that adjusts the amplitude in the hardware and includes four predefined settings as listed in the following table.

| TX_AMP_RATIO VALUE (HEX) | Minimum | Maximum | Unit |

|--------------------------|---------|---------|------|

| 0A                       | 110.00  | 130.00  | mV   |

| 2A                       | 360.00  | 430.00  | mV   |

| 55                       | 740.00  | 850.00  | mV   |

| 80                       | 1060.00 | 1270.00 | mV   |

Table 2-1. Predefined Transmit Amplitude

$\rightarrow$

**Important:** The ratio values in the preceding table can vary across devices. For lower limits of absolute TX\_AMP\_RATIO\_VALUE hx80, see RTG4 FPGA Datasheet.

# 2.2.2 Transmit De-Emphasis (Ask a Question)

The signal quality of a physical channel can be adjusted to match the interconnections and PCB using the integrated de-emphasis control. The post-cursor and pre-cursor nominally span from 0 dB to 20 dB. Adjustment of these controls in conjunction with the transmit amplitude allows the user to closely match the interconnect channel.

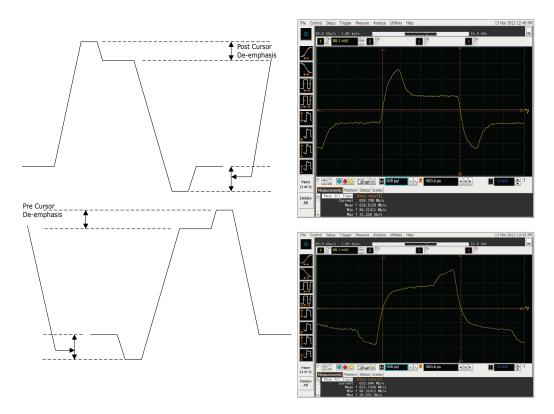

The pre-cursor and post-cursor de-emphasis adjust the magnitude of the output based on the prior bit values, effectively attenuating the successive bits. This transition emphasis compensates for the channel losses and opens the signal eye at the far-end receiver. The following figure shows the de-emphasis settings and pre-cursor and post-cursor responses of the transmit driver.

The pre-cursor and post-cursor attenuation is a function of the transmit amplitude ratio setting (see TX\_AMP\_RATIO) and the transmit pre-cursor and post-cursor ratio setting.

The pre-cursor attenuation (de-emphasis in dB) is calculated using the formula:

dB = 20 x log (1-2 x precursor ratio)

where pre-cursor ratio is simply the TX\_PRE\_RATIO divided by the TX\_AMP\_RATIO. Similarly, post-cursor attenuation (de-emphasis in dB) is calculated using the formula:

dB = 20 x log (1-2 x postcursor ratio)

where post-cursor ratio is simply the TX\_PST\_RATIO divided by the TX\_AMP\_RATIO.

For example, when TX\_AMP\_RATIO = 128 and TX\_PST\_RATIO = 21, Post Cursor Attenuation = 20 \* log(1-2 \* 21/128). This yields -3.5 dB attenuation.

Figure 2-6. Pre-Cursor and Post-Cursor De-Emphasis

The Libero configurators support TX de-emphasis for both the XAUI and EPCS protocols.

# 2.3 Receive Block (Ask a Question)

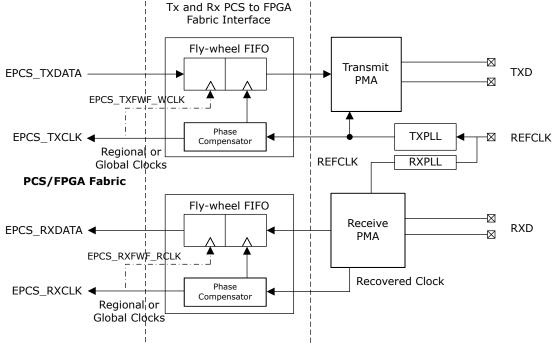

The receive block receives the serialized data from input receivers. The CDR circuit receives the signal and extracts a properly timed bit clock from the data stream. The data signal is deserialized down to a lower-speed parallel, 20-bit (maximum) digital data-word (receive data). The deserialized data is synchronous to the recovered link clock (receive clock).

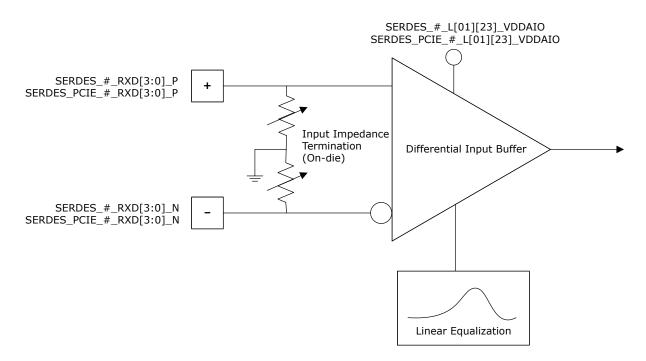

# 2.3.1 Receive Input Buffer (Ask a Question)

The receive block includes an analog front-end powered by the SerDes analog power supply. It contains a current mode input differential buffer with on-die input impedance control. The input buffer amplifier receives the incoming differential data signal and translates the differential signal to internal logic levels with no amplitude impairments. The input buffer amplifier rejects the common mode noise. The calibrated input impedance has a typical  $100\Omega$  differential impedance. The input impedance can be configured as per the system requirements. The receive inputs do not support hot-swap.

Jitter on the incoming data signal transfers through this stage. Therefore, care must be taken to ensure both the incoming timing and amplitude are free from impairments. The integrated linear equalizer filters extraneous noise from the incoming signals.

#### Figure 2-7. RX Input Diagram

# 2.3.2 Receive Equalization (Ask a Question)

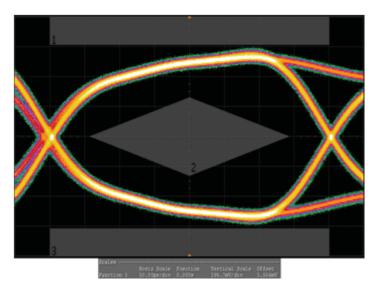

The receive block supports a programmable CTLE. The equalizer compensates the attenuated interconnections of the system PCB by effectively using a high-pass filter component, which attenuates the lower frequency components to a degree greater than the higher frequency components. The equalizer circuitry can be tuned to compensate for the signal distortion caused by the high frequency attenuation of the physical channel of PCB and interconnect.

The effective receiver equalization compensates for the channel loss of the board with the added frequency response of CTLE. The frequency response can be programmed to maximize the signal quality of the receiver to achieve the best possible Bit-Error Rate (BER). An under-equalized channel does not adequately open the eye, whereas over-equalization can produce a channel with high jitter. Correct equalization has optimal eye opening with low noise and low jitter.

The receive block has many features that can be tuned dynamically in operation mode. When changing the transmit control registers in real-time, the changes are not updated until the specific UPDATE\_SETTINGS register is written.

Figure 2-8. RX EQ RATIO Setting as shown in the Libero SoC

| ⊿ | LANE0_RE AMP RATIO | 0x101c | read-write | 0x0 | 0x00 | 8     |

|---|--------------------|--------|------------|-----|------|-------|

|   | RE_AMP_RATIO       |        | read-write | 0x0 | 0x00 | [7:0] |

| ⊿ | LANEO RE CUT RATIO | 0x1020 | read-write | 0x0 | 0x00 | 8     |

|   | RE CUT RATIO       |        | read-write | 0x0 | 0x00 | [7:0] |

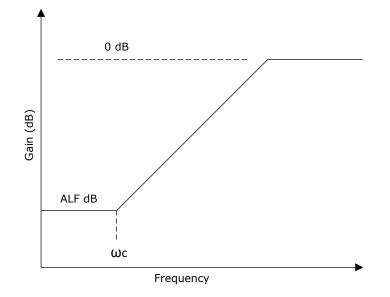

# 2.3.3 CTLE (Ask a Question)

As a FIR filter, the CTLE operates on the analog input signal and is intended to equalize the incoming transmitted signal and channel by removing the ISI at the receiver. The function of the filter uses both ALF (flat band low-frequency gain) and c (relative frequency of the flat band roll-off) which are set by the user to optimize the signal quality at the receiver. The Rx Macro sets the desired level of the filter response by setting the hardware registers RE\_AMP\_RATIO and RE\_CUT\_RATIO. The following figure shows the response of CTLE.

Figure 2-9. Receiver Equalization Frequency Response

The receiver equalization is adjusted by the RE\_AMP\_RATIO and RE\_CUT\_RATIO configuration settings. The receive equalization setting is controlled by Libero software that adjusts the settings accordingly in the hardware using predefined settings as listed in the following sections: 4.2. XAUI and 4.3. EPCS sections.

The following table lists the receiver equalization (CTLE) settings.

| rx_equalization_amp_ratio | rx_equalization_cut_frequency | High-Pass Cut-off Frequency | Low-frequency dB Loss of the<br>Filter |

|---------------------------|-------------------------------|-----------------------------|----------------------------------------|

| RE_AMP_RATIO Setting      | RE_CUT_RATIO Setting          | Wc (MHz)                    | ALF (dB) Round                         |

| 103                       | 12                            | 200.00                      | 9.54                                   |

| 74                        | 17                            | 200.00                      | 12.04                                  |

| 57                        | 22                            | 300.00                      | 13.98                                  |

| 47                        | 27                            | 400.00                      | 15.56                                  |

| 40                        | 31                            | 400.00                      | 16.90                                  |

Table 2-2. Receiver Equalization (CTLE) Settings

| continued                 |                               |                             |                                        |  |  |  |

|---------------------------|-------------------------------|-----------------------------|----------------------------------------|--|--|--|

| rx_equalization_amp_ratio | rx_equalization_cut_frequency | High-Pass Cut-off Frequency | Low-frequency dB Loss of the<br>Filter |  |  |  |

| RE_AMP_RATIO Setting      | RE_CUT_RATIO Setting          | Wc (MHz)                    | ALF (dB) Round                         |  |  |  |

| 119                       | 32                            | 400.00                      | 10.88                                  |  |  |  |

| 119                       | 31                            | 500.00                      | 8.52                                   |  |  |  |

| 103                       | 37                            | 500.00                      | 12.04                                  |  |  |  |

| 35                        | 36                            | 500.00                      | 18.06                                  |  |  |  |

| 103                       | 36                            | 500.00                      | 9.54                                   |  |  |  |

| 91                        | 42                            | 500.00                      | 13.06                                  |  |  |  |

| 31                        | 41                            | 500.00                      | 19.08                                  |  |  |  |

| 91                        | 41                            | 600.00                      | 10.46                                  |  |  |  |

| 81                        | 47                            | 600.00                      | 13.98                                  |  |  |  |

| 27                        | 46                            | 600.00                      | 20.00                                  |  |  |  |

| 81                        | 46                            | 600.00                      | 11.29                                  |  |  |  |

| 74                        | 52                            | 600.00                      | 14.81                                  |  |  |  |

| 25                        | 50                            | 600.00                      | 20.83                                  |  |  |  |

| 74                        | 50                            | 700.00                      | 12.04                                  |  |  |  |

| 70                        | 55                            | 700.00                      | 15.56                                  |  |  |  |

| 23                        | 55                            | 700.00                      | 21.58                                  |  |  |  |

| 67                        | 55                            | 800.00                      | 12.74                                  |  |  |  |

| 64                        | 60                            | 800.00                      | 16.26                                  |  |  |  |

| 21                        | 60                            | 800.00                      | 22.28                                  |  |  |  |

| 62                        | 60                            | 800.00                      | 13.38                                  |  |  |  |

| 60                        | 64                            | 800.00                      | 16.90                                  |  |  |  |

| 19                        | 64                            | 800.00                      | 22.92                                  |  |  |  |

| 128                       | 69                            | 900.00                      | 11.48                                  |  |  |  |

| 57                        | 64                            | 900.00                      | 13.98                                  |  |  |  |

| 55                        | 69                            | 900.00                      | 17.50                                  |  |  |  |

| 18                        | 69                            | 900.00                      | 23.52                                  |  |  |  |

| 120                       | 74                            | 900.00                      | 12.04                                  |  |  |  |

| 53                        | 69                            | 900.00                      | 14.54                                  |  |  |  |

| 52                        | 74                            | 900.00                      | 18.06                                  |  |  |  |

| 5                         | 245                           | 900.00                      | 24.08                                  |  |  |  |

| 112                       | 79                            | 1000.00                     | 12.57                                  |  |  |  |

| 50                        | 74                            | 1000.00                     | 15.07                                  |  |  |  |

| 15                        | 254                           | 1000.00                     | 18.59                                  |  |  |  |

| 124                       | 69                            | 1100.00                     | 8.20                                   |  |  |  |

| 106                       | 84                            | 1100.00                     | 13.06                                  |  |  |  |

| 15                        | 245                           | 1100.00                     | 15.56                                  |  |  |  |

| 116                       | 74                            | 1100.00                     | 8.67                                   |  |  |  |

| 125                       | 88                            | 1100.00                     | 11.60                                  |  |  |  |

| 35                        | 254                           | 1100.00                     | 13.53                                  |  |  |  |

| 109                       | 79                            | 1200.00                     | 9.12                                   |  |  |  |

| 44                        | 249                           | 1200.00                     | 12.04                                  |  |  |  |

| 103                       | 83                            | 1200.00                     | 9.54                                   |  |  |  |

| 55                        | 254                           | 1200.00                     | 10.88                                  |  |  |  |

continued

| continued                   | continued                     |                             |                                        |  |  |  |  |

|-----------------------------|-------------------------------|-----------------------------|----------------------------------------|--|--|--|--|

| rx_equalization_amp_ratio   | rx_equalization_cut_frequency | High-Pass Cut-off Frequency | Low-frequency dB Loss of the<br>Filter |  |  |  |  |

| <b>RE_AMP_RATIO Setting</b> | RE_CUT_RATIO Setting          | Wc (MHz)                    | ALF (dB) Round                         |  |  |  |  |

| 34                          | 252                           | 1300.00                     | 9.95                                   |  |  |  |  |

| 75                          | 254                           | 1400.00                     | 9.17                                   |  |  |  |  |

| 82                          | 254                           | 1400.00                     | 8.52                                   |  |  |  |  |

| 95                          | 254                           | 1500.00                     | 7.96                                   |  |  |  |  |

| 91                          | 254                           | 1500.00                     | 7.47                                   |  |  |  |  |

| 115                         | 254                           | 1600.00                     | 7.04                                   |  |  |  |  |

| 120                         | 254                           | 1700.00                     | 6.66                                   |  |  |  |  |

| 72                          | 254                           | 1800.00                     | 6.02                                   |  |  |  |  |

### 2.3.4 AC Coupling (Ask a Question)

Each lane must be AC-coupled to remove common mode dependencies. However, AC coupling generates baseline wander if the high-speed serial data transmission is not DC-balanced. 8b/10b encoded data is an example of DC-balanced signaling used with PCIe and XAUI protocols. The addition of external capacitors for AC coupling requires careful consideration. The designer must select a capacitor based on the system requirements. The pattern-dependent jitter associated with the low-frequency cutoff of the AC coupling network must be minimized. When non-return-to-zero (NRZ) data with long strings of identical 1's or 0's is applied to this high-pass filter, a voltage droop occurs that results in low-frequency, pattern-dependent jitter (PDJ). Off-chip AC coupling requires recommended capacitor values such as 10 nF for 8b/10b XAUI and 75–200 nF for PCIe. These example values need to be reviewed based on specific system requirements. For more information, see the AN4972: Board Design and Layout Guidelines for RTG4 FPGAs (Earlier AC439).

# 2.4 Clock Block (Ask a Question)

The Clock block in the PMA contains one transmit PLL and one CDR PLL. Figure 2-1 shows an overview of the clock block with some associated signals. The transmit PLL and receive CDR use a common input pin "RefClk". This clock signal is sourced from a reference clock input pin or from the FPGA fabric. The fabric clock is only available in EPCS modes. The power supply for the transmit PLL and CDR PLL is supplied from a dedicated 2.5V supply.

### 2.4.1 Transmit PLL and CDR PLL (Ask a Question)

Each of the PLLs (TX PLL and CDR PLL) contains the necessary dividers, output high-frequency (BIT\_CLK), and low frequency (TXClk and RXClk) clocks. The transmit clock (TXclk) and receive clock (RXClk) are divided into pipelined versions of the high-frequency clocks. The transmit and receive clocks are complementary. Within a PMA lane, the TX PLL and CDR PLL cannot be independent, that is, the TX and RX use the same REFCLK within their lane. Designs requiring separate RX and TX need to use RX from one lane and TX from another lane. The exact frequencies of the clocks are determined by the reference clock (RefClk) and divide ratio settings (M, N, and F). The divide ratio settings—M, N, and F are programmed from the APB interface on the SerDes block. For the RefClk operating ranges, see the RTG4 FPGA Datasheet.

The relationships between FREF (from RefClk clock input), FBaudClock, FBusClock, and bus width are as shown in the following equations:

$FCVO = (FREF) \times M \times N \times F$

FBaudClock = FCVO/M = FREF x M x N x F

FBusClock = FBaudClock/N = FREF x F

Bus Width = FBaudClock/FBusClock = N

**Important:** FBaudClock in transmit PLL and CDR PLL are the EPCS\_TX\_CLK and EPCS\_RX\_CLK, respectively, for EPCS mode, and bus width is the EPCS bus width.

The transmit clock is only present at the correct frequency if all the following conditions are true:

- Reference clock is present and at correct frequency

- M, N, and F are correctly set

- Transmit PLL is ON

- Transmit clock trees are ON (internal)

- Power-down mode is OFF and initialization is done

The receive clock is only present at the correct frequency if all of the following conditions are true:

- Reference clock is initially present and at the correct frequency

- M, N, and F are correctly set

- Receive PLL is ON, at correct frequency and transmit clock is present

- · Serial bitstream is present and valid

- De-serializer circuitry is ON

- Receivers are ON

Figure 2-10. M, N, and F Settings in the Libero SoC

| 4 L/ | ANEO PLL F PCLK RATIO | 0x1010 | read-write | 0x0 | 0x1 | 8     |

|------|-----------------------|--------|------------|-----|-----|-------|

|      | F                     |        | read-write | 0x0 | 0x1 | [3:0] |

|      | DIV_MODE0             |        | read-write | 0x0 | 0x0 | [5:4] |

|      | RESERVED              |        | read-write | 0x0 | 0x0 | [7:6] |

| 4 L/ | ANEO PLL M N          | 0x1014 | read-write | 0x0 | 0x9 | 8     |

|      | N_4_0                 |        | read-write | 0x0 | 0x9 | [4:0] |

|      | M_1_0                 |        | read-write | 0x0 | 0x0 | [6:5] |

|      | CNT250NS_MAX_8        |        | read-write | 0x0 | 0x0 | [7:7] |

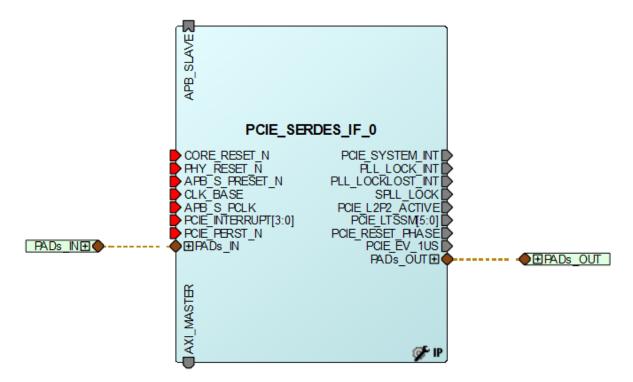

# 2.4.2 Reference Clock Inputs (Ask a Question)

Each SerDes block consists of reference clock input pads. The REFCLK is multiplexed in the clock block. It optionally allows the reference clock to be sourced to the transmit PLL and/or CDR PLL, which are the dedicated input buffers used for the reference clock input. The REFCLK inputs have a dedicated power supply. VDDI powers the SerDes reference clock, that is, 1.8V, 2.5V, or 3.3V. A common SERDES\_VDDI supply provides the required SerDes reference clocks to use the same voltage supply.

#### Table 2-3. Reference Clock Specifications (Typical)

|                 | Min | Max | Unit |

|-----------------|-----|-----|------|

| Ref Clock Speed | 100 | 160 | MHz  |

#### Note:

For detailed specifications, see the RTG4 FPGA Datasheet.

The best performance of the SerDes is based on the selection of a quality clock source. The SerDes reference clock phase noise contributes to the transmit output phase noise and can decrease receiver jitter tolerance. For more specific information, see the RTG4 FPGA Datasheet.

# 2.4.3 SerDes Reference Clock Inputs (Ask a Question)

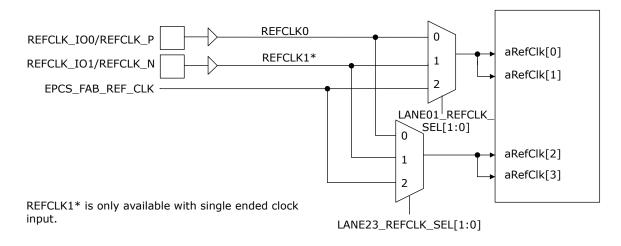

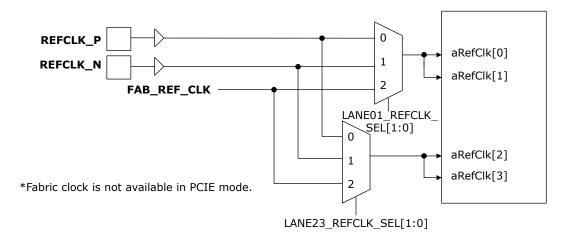

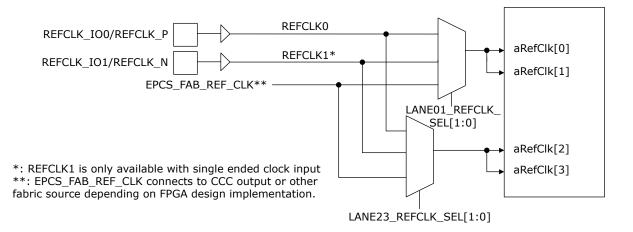

PMA in the SerDes block needs a reference clock on each of its lanes for transmit and receive clock generation through the PLLs. The reference clock input port (REFCLK) is optionally connected to I/O pads or an additional reference clock source, fab\_ref\_clk, coming from the fabric.

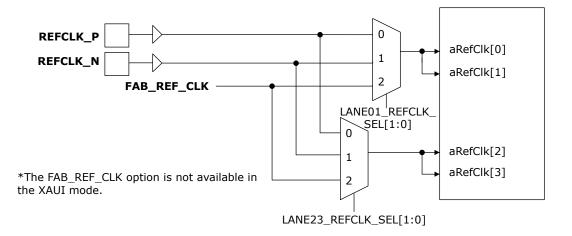

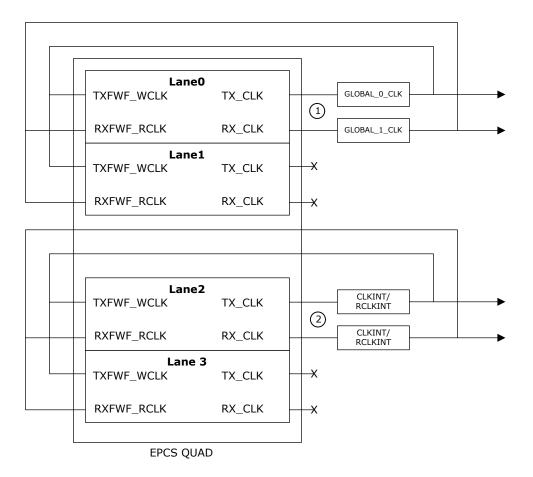

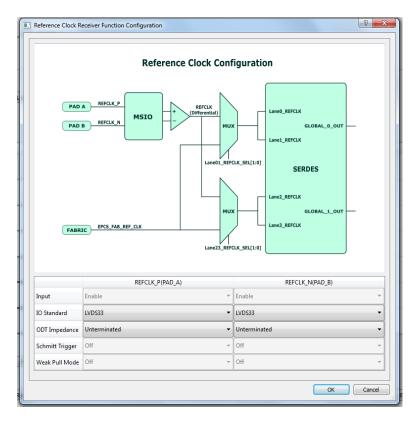

Each SerDes block includes four lanes (Lane[0:3]). A dedicated reference clock block (REFCLK) is available for each SerDes block. Two I/O pads are associated with the REFCLK block. The I/O pads can accept only one differential clock signal via the REFCLK\_P and REFCLK\_N pins. The REFCLK block uses both the I/O pads to supply a single REFCLK signal to all four lanes of the SerDes block. However, an optional feature is available to supply two individual single-ended clock signals to the REFCLK\_IO[0:1] I/O pads. This feature provides two REFCLKs to the SerDes block and permits independent clocking of two lanes. In this scenario, Lane 0 and Lane 1 share one of the clock inputs, and Lane 2 and Lane 3 share the other clock input. The REFCLK is controlled by the selection of the input multiplexer for the REFCLK input of the SerDes block. The Libero software correctly sets the input MUXes for the REFCLKs based on the SerDes block configurator settings.

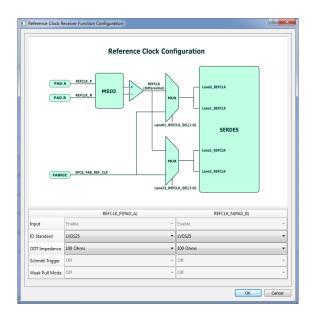

The RTG4 SerDes device includes a multi-standard input reference clock. The reference clock is configured through the Libero SoC software configurator to support differential or single-ended signaling standards. Based on the reference clock source selection, the supported I/O standards and other options such as impedance, receiver settings, and weak pull-up/pull-down settings are available.

| SERDES_VDDI Supply  | 3.3V                | 2.5V                | 1.8V           |

|---------------------|---------------------|---------------------|----------------|

| Supported Standards | LVTTL/LVCMOS33      | LVCMOS25            | LVCMOS18       |

|                     | LVDS33 <sup>1</sup> | LVDS25 <sup>1</sup> | SSTL18-Class 1 |

|                     | LVPECL              | RSDS                | SSTL18-Class 2 |

|                     | RSDS                | mini-LVDS           | HSTL18-Class 1 |

|                     | mini-LVDS           | SSTL25-Class 1      | -              |

|                     | -                   | SSTL25-Class 2      | -              |

#### Table 2-4. Support Reference Clock Input Standards

<sup>(1)</sup> For LVDS33 and LVDS25, designers must reference the RTG4 I/O Users Guide and RTG4 FPGA Datasheet for correct termination and common-mode recommendations to achieve optimal jitter performance. For more information about application solution, see Reference Clocks for RTG4 SerDes REFCLK Inputs and Interface Circuits Application Note.

**Important:** HCSL inputs are supported directly with LVDS I/O STD inputs from the Libero. There is no specific HCSL I/O STD available in Libero, and designs requiring HCSL are supported by using the LVDS25 I/O standard.

The dedicated clock input pins are recommended to achieve optimal performance. The fabric reference clock is only available in EPCS modes. The following figure shows the reference clock selection. The user-programmed clock selection is routed to the SerDes clock block RefClk input port.

The SerDes has four lanes, and the two adjacent SerDes lanes share the same reference clock, as shown in the following figure. In this scheme, lane0 and lane1 share the same reference clock input. Similarly, lane3 and lane4 share the same reference clock input.

#### Figure 2-11. SerDes Reference Clock Input Sources

When a SerDes REFCLK input PAD is disabled or unused, Libero SoC automatically configures it as follows:

- The I/O buffer is disabled.

- The internal on-die termination is disabled.

- The Schmitt Trigger input is disabled.

- The I/O standard is set to LVCMOS.

- The internal weak pull-down resistor is disabled.

- The internal weak pull-up resistor is enabled.

Important: Libero SoC reports the SerDes Reference Clock configuration used by the design in the project's Configuration Report for SERDES block(s), Fabric DDR, and Fabric CCC(s). This report is generated during the Generate FPGA Array Data design flow step. This report can be accessed using the Libero SoC Reports tab or by opening the file from the Libero project folder, /designer/<root>/ <root>\_init\_config.txt. The file is also available in .html format for easy viewing.

The following figure shows an example of the SerDes reference clock configuration information reported by Libero SoC in the configuration report.

Figure 2-12. Example of the SerDes Reference Clock Report Configuration Information Reported by Libero® SoC

| Port                       | Pin | 1 | IO Standard                             | ODT | [ Impedance (Ohm) | 1 | Schmitt Trigger                   | 1 1 | Weak Pull Moo     | de I |

|----------------------------|-----|---|-----------------------------------------|-----|-------------------|---|-----------------------------------|-----|-------------------|------|

| REFCLK_P_0  <br>REFCLK_N_0 |     |   | 300000000000000000000000000000000000000 |     | erminated         |   | On<br>Off                         |     | Up<br>Off         | 1    |

|                            |     |   |                                         |     |                   |   |                                   |     |                   |      |

| +                          |     |   |                                         |     |                   |   |                                   |     |                   |      |

|                            | +   | + |                                         | +-  | )/SERDESIF_INST/I |   | -+                                | 010 | -+                |      |

|                            | +   | + |                                         | +-  |                   |   | _NPSS_IP<br>++<br>  Schmitt Trigg | er  | -+<br>  Weak Pull | Mode |

|                            | Pin | 1 | IO Standard                             | 1   |                   |   | -+                                | er  | Weak Pull         | Mode |

# 2.5 Calibration Resource Sharing (Ask a Question)

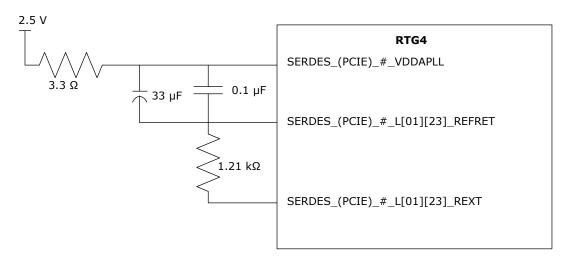

The SerDes PMA block calibration is performed to optimize the SerDes in the system. Calibration is done for the source impedance at the transmitter and at the termination of the receiver. The calibration circuitry is shared across channels. Each SerDes block contains two external reference resistor (REXT) signals—one for lane0 and lane1 and another for lane2 and lane3. The calibration interaction limits the combination of protocols/data rates per channel utilization since the adjacent channels are bonded to the same calibration circuitry. For example, if lane1 and lane0 operate and the PHY is reset on lane0, the recalibration function, which follows the reset disrupts lane1 due to the shared REXT calibration resistor.

REXT connections are required to calibrate transmit/receive termination value and internal elements. A 1.21 k-1% resistor must be connected on the PCB, as shown in the following figure. This resistor can be a 0201 or 0402 sized component, since the power dissipation through this resistor is less than 1 mW during calibration. For more details, see the AN4972: Board Design and Layout Guidelines for RTG4 FPGAs (Earlier AC439).

#### Figure 2-13. Calibration Resistor Connection

#### 2.5.1 SerDes Startup (Ask a Question)

For SerDes to lock at power-up, it is essential that the reference clock to the SerDes be at the target frequency and stable. If the clock frequency is lower or higher than the target, the SerDes

link acquisition is not guaranteed or reliable. SERDES\_VDDI of the reference clock must be at its minimum or higher. Any lower SERDES\_VDDI causes higher Jitter and unpredictable locking. At system startup, the user must hold the PCS/PMA in reset until the clock stabilizes at its target frequency. The reset signals are listed for PCIe, XAUI, and EPCS modes depending on target protocols. See 4. Physical Coding Sublayers for information about reset pin descriptions. If the PLL does not lock, a simple reset may not be sufficient, and a power down (using the protocol mode related SerDes power down pin) may be required.

In EPCS modes, after power-up, the fabric releases EPCS\_#\_RESET\_N, starting the Tx PLL locking process. The fabric output port, EPCS\_#\_TX\_CLK\_STABLE, is the Tx PLL lock flag. A rise on this flag begins the SerDes calibration operation. Calibration time is dependent on the transmit parallel clock. Calibration determines the PMA's optimized output impedance and receiver termination that best match the system. The end of calibration triggers the EPCS\_#\_READY output port to rise, indicating to the fabric that the transceiver is ready for operation. Serial port outputs are held in common-mode throughout calibration. Upon completion of calibration, the transmitter is taken out of electrical-idle. This is a serial shift operation, which adds 27 parallel transmit clock cycles to complete. After which, the serial outputs reflect the applied EPCS\_#\_TX\_DATA pattern. When the serializer sends out differential data, it takes some time for the line to charge up because of capacitive coupling.

In PCIE or XAUI modes, the protocol layer manages the health and proper sequencing of the startup requiring no user logic intervention.

# 2.6 SerDes Block-I/O Signal Interface (Ask a Question)

The RTG4 SerDes block interfaces with differential I/O pads, the PCIe system, and the FPGA. The following table lists these signals.

| Port Name                                              | Туре      | Connected to   | Description                                                                                                                                                                                |  |  |

|--------------------------------------------------------|-----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SERDES_(PCIE)_#_RXD0_P                                 | Input     | Input pads     | Receive data. SerDes differential positive input: Each SerDes                                                                                                                              |  |  |

| SERDES_(PCIE)_#_RXD1_P                                 |           |                | block consists of four RX+ signals.                                                                                                                                                        |  |  |

| SERDES_(PCIE)_#_RXD2_P                                 |           |                |                                                                                                                                                                                            |  |  |

| SERDES_(PCIE)_#_RXD3_P                                 |           |                |                                                                                                                                                                                            |  |  |

| SERDES_(PCIE)_#_RXD0_N                                 | Input     | Input pads     | Receive data. SerDes differential negative input: Each SerDes                                                                                                                              |  |  |

| SERDES_(PCIE)_#_RXD1_N                                 |           |                | block consists of four RX- signals.                                                                                                                                                        |  |  |

| SERDES_(PCIE)_#_RXD2_N                                 |           |                |                                                                                                                                                                                            |  |  |

| SERDES_(PCIE)_#_RXD3_N                                 |           |                |                                                                                                                                                                                            |  |  |

| SERDES_(PCIE)_#_TXD0_P                                 | Output    | Output pads    | Transmit data. SerDes differential positive output: Each SerDes                                                                                                                            |  |  |

| SERDES_(PCIE)_#_TXD1_P                                 |           |                | block consists of four TX+ signals.                                                                                                                                                        |  |  |

| SERDES_(PCIE)_#_TXD2_P                                 |           |                |                                                                                                                                                                                            |  |  |

| SERDES_(PCIE)_#_TXD3_P                                 |           |                |                                                                                                                                                                                            |  |  |

| SERDES_(PCIE)_#_TXD0_N                                 | Output    | Output pads    | Transmit data. SerDes differential negative output: Each SerDes                                                                                                                            |  |  |

| SERDES_(PCIE)_#_TXD1_N                                 |           |                | block consists of four TX- Signals.                                                                                                                                                        |  |  |

| SERDES_(PCIE)_#_TXD2_N                                 |           |                |                                                                                                                                                                                            |  |  |

| SERDES_(PCIE)_#_TXD3_N                                 |           |                |                                                                                                                                                                                            |  |  |

| SERDES_(PCIE)_#_L01_REXT                               | Reference | Reference pads | External reference resistor connection to calibrate TX/RX                                                                                                                                  |  |  |

| SERDES_(PCIE)_#_L23_REXT                               |           |                | termination value. Each SerDes block consists of two REXT signals<br>—one for lane0 and lane1, another for lane2 and lane3.                                                                |  |  |

| SERDES_(PCIE)_#_REFCLK_P<br>SERDES_(PCIE)_#_REFCLK_IO0 | Input     | Input pads     | This pin acts as the positive terminal when used with a differential clock source. It is limited to driving only one clock source to the SerDes block when differential (REFCLK0) is used. |  |  |

#### Table 2-5. SerDes Block I/O - PAD Interface

| continued                                              |       |              |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|--------------------------------------------------------|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Port Name                                              | Туре  | Connected to | Description                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| SERDES_(PCIE)_#_REFCLK_N<br>SERDES_(PCIE)_#_REFCLK_IO1 | Input | Input pads   | This pin acts as the negative terminal when used with a<br>differential clock source. It is limited to driving only one clock<br>source to the SerDes block when differential (REFCLK0) is used.<br>When used with a single ended clock source, this input pin<br>supplies a reference clock signal to the REFCLK1 input of the<br>SerDes block. |  |  |  |

**Important:** Here, x = the SerDes Block\_# where # varies from 0 through 5 based on the device size. The notation SERDES\_(PCIE) indicates the capability of a SerDes block to include PCIe functionality. SerDes without PCIe capability is represented without PCIe in the pin name. For example, SERDES\_3.

**Important:** For more information on SerDes pins and related power supplies, see RTG4 FPGA Pin Descriptions Datasheet.

PMA

# 3. PCB Design (Ask a Question)

Good board design practices are required to achieve the expected performance from the PCB and RTG4 devices. High-quality and reliable results depend on minimizing noise levels, preserving signal integrity, meeting impedance and power requirements, and using appropriate transceiver protocols. A good understanding of the RTG4 chip, experience in digital and analog board layout, knowledge of transmission line theory and signal integrity are essential to build high performance PCBs. See AN4972: Board Design and Layout Guidelines for RTG4 FPGAs (Earlier AC439), which describes the details of PCB design for RTG4 based designs.

IBIS-AMI models recommended to simulate serial links to predict a serial link performance with an eye diagram and bit error rate. IBIS-AMI models are available for download from the Microchip website. AC292 Application Note IBIS/IBIS-AMI Models: Background and Usage provides information for using the equalization models to optimize the design of PCB channels with the RTG4 SerDes blocks.

# 4. Physical Coding Sublayers (Ask a Question)

The RTG4 contains three embedded SerDes PCS blocks (PCIe, XAUI, and EPCS). These blocks are user-configured in the design. The embedded PCIe and XAUI blocks support protocol-required functions without the need for FPGA-hosted PCS logic. EPCS protocols require the user to include soft FPGA-hosted logic to perform PCS functions.

# 4.1 PCI Express (Ask a Question)

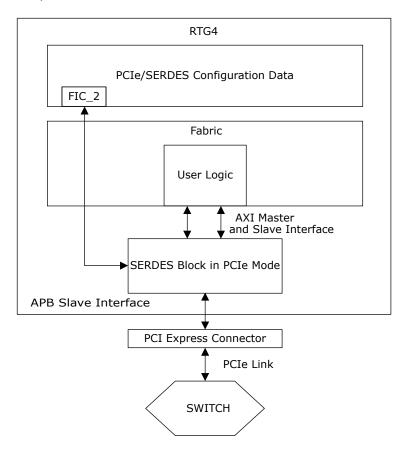

PCIe is a high-speed, packet-based, point-to-point, low-pin-count, and serial interconnect bus. RTG4 has a fully integrated PCIe EP implementation within the SerDes block. This section describes the architecture of the PCIe system that implements the main PCIe IP function.

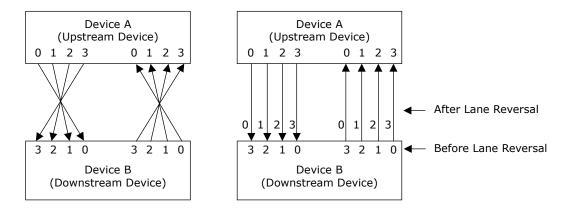

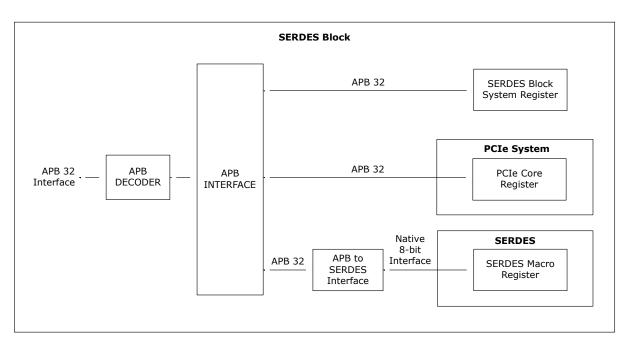

EP in PCIe refers to a type of function that can be the requester or the completer of a PCIe transaction. The PCIe sub-system (PCIESS) within the SerDes blocks implements the PCIe EP specification for transaction, data link, and physical layers. On the application side, it has one master interface and one slave interface. The master interface can be a 64-bit AXI3 master. The slave interface can be a 64-bit AXI3 slave. The PCIe link initiates transactions to the RTG4 fabric through the AXI3 master. RTG4 fabric initiates transactions to wards the PCIe link through the AXI3 slave. There is an APB interface that has access to the SerDes block system registers.

### 4.1.1 Features (Ask a Question)

The following are the main features of the PCIe EP implemented in RTG4:

- x1, x2, or x4 lane support

- Implements native endpoint

- Compliant with PCIe base specification revision 2.0 and 1.1 for 2.5 Gbps operation

- Single-function/Single virtual channel (VC)

- Receives, transmits, and retries buffer

- AXI3 master and slave interface to the RTG4 FPGA fabric

- AXI3 64-bit master and slave interfaces

- Advanced error reporting (AER) support

- End-to-end cyclic redundancy check (ECRC) generation and forward support

- Supports all base memory, configuration, and message transactions

- Implements type 0 configuration space for EP

- Supports three 64-bit BARs or six 32-bit BARs

- Native active state power management L0, L1, and L2 state support

- Power management event (PME) message

- Supports design time selection of the PCIe lane reversal for flexibility of lane assignments for board layout

# $\rightarrow$

**Important:** A PCIe endpoint refers to the location of the connection in the PCIe topology. A PCIe endpoint connects to switch downstream port or a root complex downstream port. As an endpoint, PCIe initiates and responds to transactions in the system.

### 4.1.2 Device Support (Ask a Question)

The following table lists the total number of PCIe endpoint blocks available in each RTG4 device that are configured to support PCIe.

#### Table 4-1. PCIe Endpoint Blocks Available in RTG4

|                   | RT4G150 |

|-------------------|---------|

| PCIe EP available | 2       |

The specified number of PCIe EP blocks vary depending on the device package. PCIESS can implement x1, x2, or x4 links.

Each RTG4 device has a minimum of two PCIESS endpoint blocks that allow two PCIe variations within an RTG4 device.

#### 4.1.3 RTG4 PCI Express Block (Ask a Question)

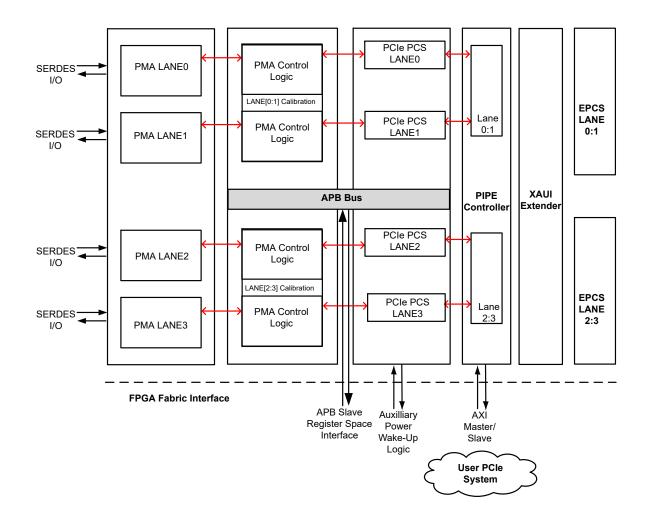

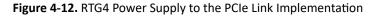

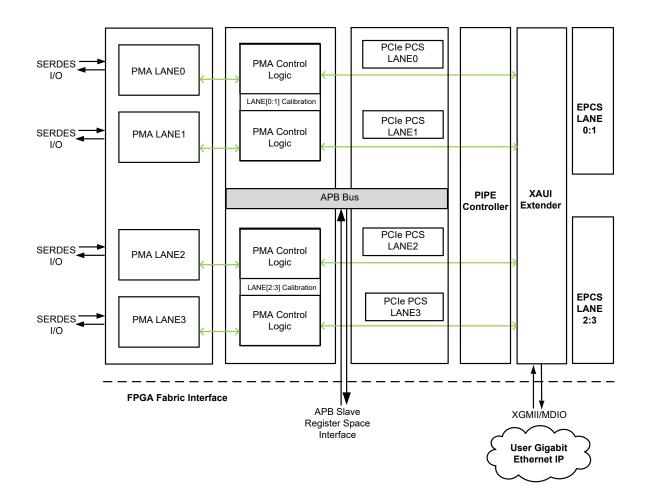

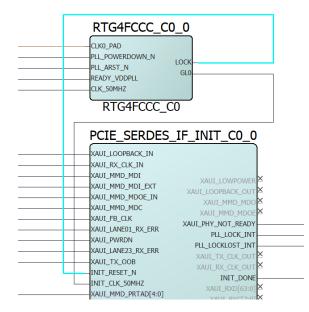

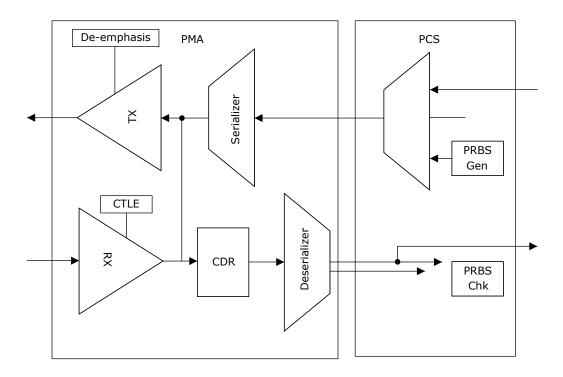

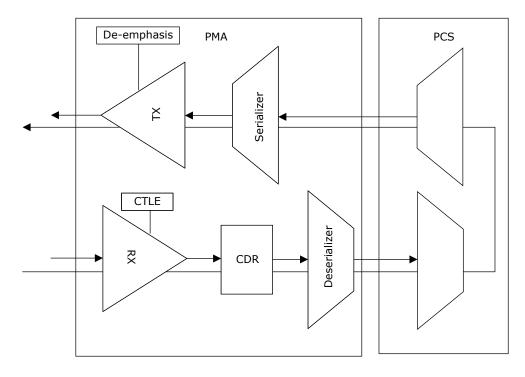

The RTG4 family supports up to six integrated SerDes blocks in one device, and each block supports up to four SerDes lanes, thus supporting up to 24 SerDes lanes. The following figure shows the RTG4 device block diagram with PCIe implementation. Each PCIESS block contains an integrated PCIe system block, also known as a PCIe system, which implements the PCIe transaction layer and data link layer. The PCIESS block also has a SerDes PMA block that implements the physical layer. The RTG4 family includes two PCIESS blocks per device. The PCIe system block along with the SerDes PMA block provides the complete PCIe EP solution in RTG4. The RTG4 PCIe implementation is compliant with PCIe Base Specification revisions 2.0 and 1.1.

Figure 4-1. RTG4 SerDes Block Diagram

The following figure shows a simplified view of a PCIe EP implementation in an RTG4 device. The PCIe system interfaces to the FPGA fabric on one side and the PCS/PMA SerDes block on the other side. The SerDes block interfaces to the dedicated I/O in the RTG4 device is called a SerDes I/O. For more information, see the 5-SerDes Block I/O - PAD Interface. The PCIe system interface to the FPGA fabric consists of an application interface and a configuration interface. In addition, it has several signals for clocking, reset, and power management.

#### Figure 4-2. SerDes Block Configuration for PCIe Single Protocol Mode

- **Application Interface**: The application interface transfers transaction layer packets (TLP). It is either AXI3 master only, AXI3 slave only, or AXI3 master plus slave interface.

- AXI3 Master Interface: The master interface is a 64-bit AXI3 master. A typical application

interface uses a master interface, which is used to respond to data read requests, and a slave

interface, which is used to initiate requests. It is also possible to use the master and/or slave

interfaces by themselves for specific applications.

- AXI3 Slave Interface: The slave interface is a 64-bit AXI3 slave interface. The RTG4 fabric initiates PCIe transactions using the slave interface (that is, memory write TLP and memory read TLP). The data on a read request comes back to the same interface.

- **Configuration Interface**: The configuration interface uses the APB slave interface.

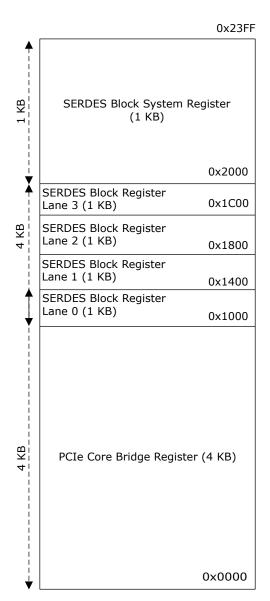

- APB Interface: The APB interface has access to various registers, including the PCIe configuration registers, the AXI3 bridge register, the SerDes block register and so on. The APB provides access to the memory map of the SerDes block, which includes a section for the PCIe controller.

- **Other Signals**: The PCIe system has several clocking signals, reset signals, phase-locked loop (PLL) signals, interrupts, and power management signals to the FPGA fabric.

The following figure shows a simple application with a switch port connected to a PCIe EP implemented in an RTG4 device.

Figure 4-3. RTG4 PCIe EP Implementation

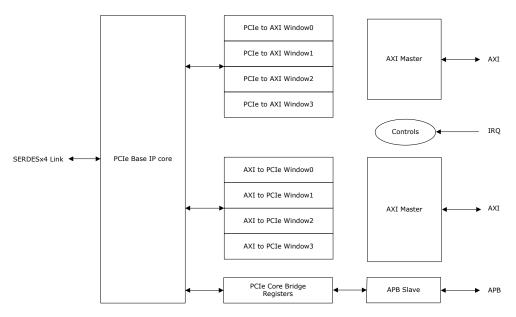

The PCIe system sub-block inside the SerDes block implements the PCIe physical layer, data link layer, and transaction layer of the PCIe specification. It interfaces with the SerDes block on one side and the FPGA fabric on the other side. The following figure shows the RTG4 SerDes block in PCIe mode and various sub-blocks for the PCIe system block.

#### Figure 4-4. Detailed PCIe System Block Diagram

#### 4.1.3.1 AXI Master Block (Ask a Question)

The AXI3 master only supports memory read and write transactions.

#### 4.1.3.1.1 AXI Master Write Transaction Handling (Ask a Question)

The AXI master write transactions handle the following operations:

- · The write transaction is handled in big-endian order

- PCIe transactions can be of any size up to the configurable maximum payload size (256 bytes)

- AXI3 transactions are limited to 128 bytes, a received TLP is divided into several AXI3 transactions

- AXI3 master receives a write transaction, it processes the transaction as 128-byte segments (aligned on a 128-byte address boundary) until the segments in the transaction have been processed

- TLP is de-constructed and sent to the AXI3 interface, and the data is presented as little endian

#### 4.1.3.1.2 AXI Master Read Transaction Handling (Ask a Question)

The AXI master read transactions handle the following operations:

- Read transactions are handled the same way as write transactions, except that before transferring the transaction to the AXI3 master read channel, the PCIe IP checks the transmit buffer for available space

- PCIe IP does not transfer the read transaction if there is no sufficient space in the transmit replay buffer to store PCIe completions

- The number of outstanding AXI3 master read transactions is therefore limited by the size of the Tx buffer

- The AXI3 master read channel can receive transactions in any order, and data can be completely interleaved. However, the PCIe IP generates completions in the order they are initiated on the link

#### 4.1.3.2 AXI Slave Block (Ask a Question)

The AXI3 slave interface forwards AXI3 read and write requests from the FPGA fabric to the PCIe link.

#### 4.1.3.2.1 AXI Slave Write Transaction Handling (Ask a Question)

The AXI slave write transactions handle the following operations:

- Minimum 128 bytes must be available for write transaction

- Data interleaving is not supported

- Wait states are used if buffer is full or has less than 128 Bytes of space available

- Write responses are generated as soon as the last data phase is over

- Maximum of 128 Bytes of data packet can be created

- Only four outstanding write transactions are supported

- Incrementing-address burst is supported

#### 4.1.3.2.2 AXI Slave Read Transaction Handling (Ask a Question)

The AXI slave read transactions handle the following operations:

- Minimum 128 Bytes must be available for read transaction

- PCIe IP generates a PCIe tag, arbitrates between write requests and completions, and then checks for available flow control (FC) credits

- · Response is generated if a time-out occurs or if a completion with error status is received

#### **Outstanding Requests**

The AXI3 interface supports the following outstanding requests as listed in the following table.

#### Table 4-2. AXI3 and Outstanding Transactions

| AXI3 Transaction | Outstanding Transactions |

|------------------|--------------------------|

| Master write     | Limited by Tx credits    |

| Master read      | 4                        |

| Slave write      | Limited by Rx credits    |

| Slave read       | 4                        |

#### 4.1.3.3 AXI3 Transaction and TLP Ordering Rules (Ask a Question)

This section describes the TLP ordering rules for sending and receiving TLPs. Both AXI3 interfaces, master and slave can multiplex the transmit buffer to send packets over the PCIe link. There are priority ordering rules in PCIe that mandate the scheduling of packets, and this is followed by the PCIe IP block in the case of a collision.

# 4.1.3.3.1 AXI3 Slave Interface (Ask a Question)

The slave path does not reorder transactions other than reordering using PCIe standard ordering rules, but does arbitrate between transactions when they occur simultaneously. The order of priority for arbitrations is master read completions, slave write requests, and then slave read requests.

# 4.1.3.3.2 AXI3 Master Interface (Ask a Question)

The master path does not reorder transactions other than reordering using PCIe standard ordering rules, but does arbitrate between transactions at the AXI3 master interface. If a transaction is currently waiting for a response phase, the transaction is completed before the read transaction is forwarded to the AXI3 master interface.

#### 4.1.3.4 APB Slave Interface (Ask a Question)

The APB slave interface provides APB interface to SerDes block system registers.

# 4.1.3.5 AXI3 to AHBL Bridge (Master/Slave) (Ask a Question)

In the Libero SoC catalog, there are two AHBLite IP cores which support AXI to AHBL (master) and AHBL to AXI (slave) between the SerDes block configured with an AXI3 interface and AHB hosted

within the FPGA fabric. The two Direct Cores from the Libero SoC catalog are specifically developed to bridge PCIe AXI3 to AHBL transactions. RTG4 designs requiring SerDes configured as PCIe with AHBLite master must use the CorePCIe\_AXItoAHBL DirectCore.

In addition, designs with both master and slave AHBLite interfaces are required to use the CorePCIe\_AXItoAHBL and CorePCIe\_AHBLtoAXI DirectCores. The Core IP handbooks provide implementation guidance.

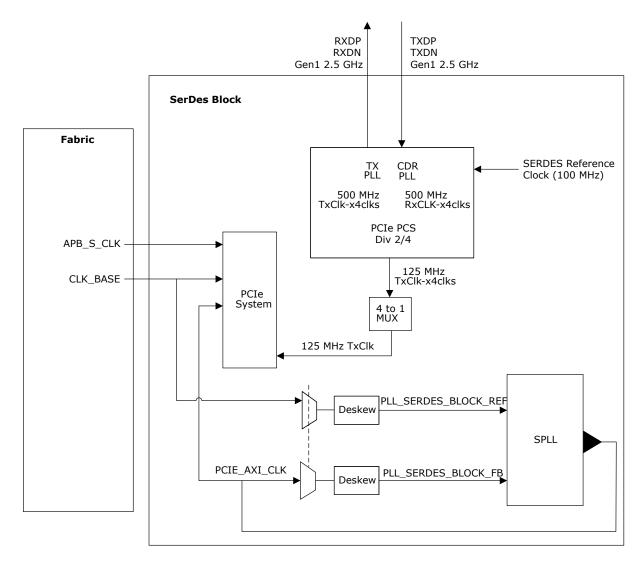

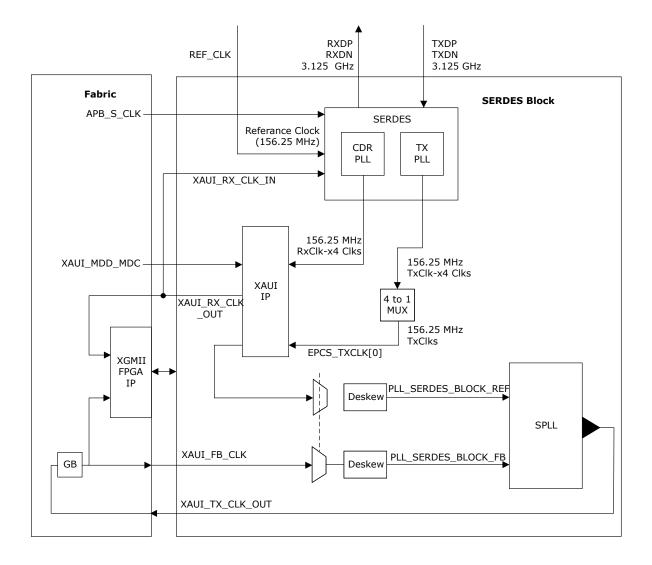

#### 4.1.3.6 PCIe Clocking Architecture (Ask a Question)

The RTG4 SerDes block, when configured in PCIe mode, uses multiple clocks inside the SerDes block. This sub-section describes the PCIe clocking architecture inside the SerDes block in PCIe mode. Figure 4-5 shows the PCIe clocking architecture in the RTG4 device. The two main clock inputs are a differential SerDes reference clock (100 MHz) for SerDes PMA and a CLK\_BASE input for SerDes block from the FPGA fabric. In addition, there is an APB clock input for the SerDes block from the FPGA fabric.

SerDes reference clock: The differential 100 MHz reference clock is used by SerDes (TX PLL and CDR PLL) to generate 125 MHz clock and is passed to PCIe System IP block. The settings for TX PLL and CDR PLL are calculated automatically by the Libero software. This 125 MHz clock output from SerDes is used by PCIe system.

The PCIe standard specifies a 100 MHz clock (Refclk) with greater than ±300 ppm frequency stability at both the transmitting and receiving devices. RTG4 supports two distinct clocking topologies: Common Refclk and Separate Refclk.

Common Refclk is the most widely supported clocking method in open systems where the host (switch or root) provides a clock to the end point. An advantage of this clocking architecture is that it supports spread spectrum clocking (SSC) which is useful in reducing electromagnetic interference (EMI). RTG4 supports SSC clocking in common clock systems.

Separate Refclk uses two independent clock sources. One clock for the host (switch or root) and another clock source for the endpoint. The clock sources must have ±300 ppm frequency accuracy and cannot use any SSC.

#### Figure 4-5. Clocks in PCIe Mode

The clocking architecture also uses SPLL to synchronize data between CLK\_BASE and the clock generated from SerDes (125 MHz clocks). The SPLL allows the reduction of the skew between the fabric and the RTG4 SerDes block module.

Figure 4-6. SerDes Reference Clock for PCIe Mode

### 4.1.3.6.1 SerDes Reference Clocks Selection (Ask a Question)

RTG4 accepts the PCIe reference clock. It is fully compliant with the PCIe add-in card specifications and can directly receive the 100 MHz reference clock from the PCIe connector. The differential PCIe clock is connected to the REFCLK\_P and REFCLK\_N pins and configured correctly by the Libero software.

Table 4-3. Reference Clock Signals for SerDes in PCIe Mode

| Clock Signal     | Description                                                                  |

|------------------|------------------------------------------------------------------------------|

| REFCLKP, REFCLKN | Reference clock input for SERDES_(PCIE)_#_REFCLK_P, SERDES_(PCIE)_#_REFCLK_N |

The reference clock needs to be compliant with the PCIe protocol. For specifications, see RTG4 FPGA Datasheet. The Libero software permits using only REFCLK\_P or REFCLK\_N for PCIe mode.

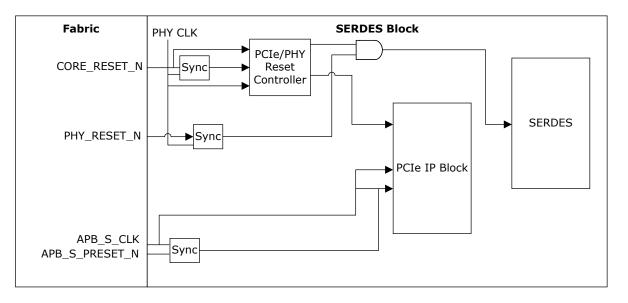

#### 4.1.3.7 PCIe Reset Network (Ask a Question)

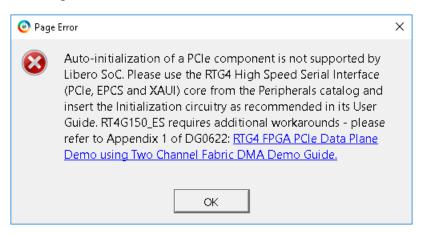

The SerDes block has different reset inputs when configured in the PCIe mode. The reset connections are required for a proper PCIe SerDes initialization solution. To build the initialization circuitry, see *RTG4 High-Speed Serial Interface (PCIe, EPCS, and XAUI) Configuration User Guide*. The pcie\_init component has a one-to-one connection for the fabric signals, as shown in the following figure.

#### Figure 4-7. Reset Signals in PCIe Mode

# 4.1.3.8 Fabric Interface for PCIe Block (Ask a Question)

The RTG4 PCIe block interfaces with the FPGA fabric using the following interface pins:

- PCIe system AXI3 master interface

- PCIe system AXI3 slave interface

- PCIe system APB slave interface

- PCIe system clock signals

- PCIe system reset signals

- PCle interrupt and power management interface

#### Table 4-4. PCIe System AXI3 Master Interface

| Port               | Туре   | Description                                                           |

|--------------------|--------|-----------------------------------------------------------------------|

| AXI_M_AWID[3:0]    | Output | AXI3 master mode: AWID (not supported)                                |

| AXI_M_AWADDR[31:0] | Output | AXI3 master mode: AWADDR                                              |

| AXI_M_AWLEN[3:0]   | Output | AXI3 master mode: AWLEN                                               |

| AXI_M_AWSIZE[1:0]  | Output | AXI3 master mode: AWSIZE                                              |

| AXI_M_AWBURST[1:0] | Output | AXI3 master mode: AWBURST                                             |

| AXI_M_AWVALID      | Output | AXI3 master mode: AWVALID                                             |

| AXI_M_AWREADY      | Input  | AXI3 master mode: AWREADY                                             |

| AXI_M_WID[3:0]     | Output | AXI3 master mode: WID (not supported)                                 |

| AXI_M_WSTRB[7:0]   | Output | AXI3 master mode: WSTRB                                               |

| AXI_M_WLAST        | Output | AXI3 master mode: WLAST                                               |

| AXI_M_WVALID       | Output | AXI3 master mode: WVALID                                              |

| AXI_M_WDATA[63:0]  | Output | AXI3 master mode: WDATA                                               |

| AXI_M_WREADY       | Input  | AXI3 master mode: WREADY                                              |

| AXI_M_BID[3:0]     | Input  | AXI3 master mode: BID                                                 |

| AXI_M_BRESP[1:0]   | Input  | AXI3 master mode: BRESP. In response to a write the value is ignored. |

| AXI_M_BVALID       | Input  | AXI3 master mode: BVALID                                              |

| AXI_M_BREADY       | Output | AXI3 master mode: BREADY                                              |

#### .....continued

| Port               | Туре   | Description                                                                                                                        |

|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------|

| AXI_M_ARID[3:0]    | Output | AXI3 master mode: ARID. Used to indicate the ID of the current outstanding read completion. Read completions can be interleaved.   |

| AXI_M_ARADDR[31:0] | Output | AXI3 master mode: ARADDR                                                                                                           |

| AXI_M_ARLEN[3:0]   | Output | AXI3 master mode: ARLEN                                                                                                            |

| AXI_M_ARSIZE[1:0]  | Output | AXI3 master mode: ARSIZE (tied to 11)                                                                                              |

| AXI_M_ARBURST[1:0] | Output | AXI3 master mode: ARBURST                                                                                                          |

| AXI_M_ARVALID      | Output | AXI3 master mode: ARVALID                                                                                                          |

| AXI_M_ARREADY      | Input  | AXI3 master mode: ARREADY                                                                                                          |

| AXI_M_RID[3:0]     | Input  | AXI3 master mode: RID. Used to indicate the ID of the current outstanding read completion.<br>Read completions can be interleaved. |

#### Table 4-5. PCIe System AXI3 Slave Interface

| Port               | Туре   | Description                                                                                                                                                      |

|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI_S_AWID[3:0]    | Input  | AXI3 slave mode: AWID (not supported)                                                                                                                            |

| AXI_S_AWADDR[31:0] | Input  | AXI3 slave mode: AWADDR                                                                                                                                          |

| AXI_S_AWLEN[3:0]   | Input  | AXI3 slave mode: AWLEN                                                                                                                                           |

| AXI_S_AWSIZE[1:0]  | Input  | AXI3 slave mode: AWSIZE                                                                                                                                          |

| AXI_S_AWBURST[1:0] | Input  | AXI3 slave mode: AWBURST                                                                                                                                         |

| AXI_S_AWVALID      | Input  | AXI3 slave mode: AWVALID                                                                                                                                         |

| AXI_S_AWREADY      | Output | AXI3 slave mode: AWREADY                                                                                                                                         |

| AXI_S_AWLOCK[1:0]  | Input  | AXI3 slave mode: AWLOCK                                                                                                                                          |

| AXI_S_WID[3:0]     | Input  | AXI3 slave mode: WID (not supported)                                                                                                                             |

| AXI_S_WSTRB[7:0]   | Input  | AXI3 slave mode: WSTRB                                                                                                                                           |

| AXI_S_WLAST        | Input  | AXI3 slave mode: WLAST                                                                                                                                           |

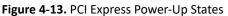

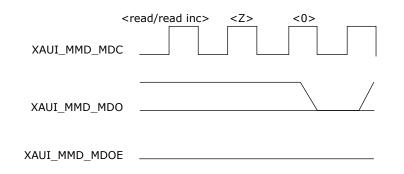

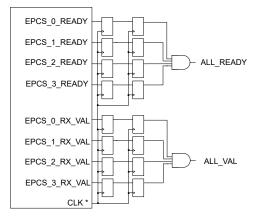

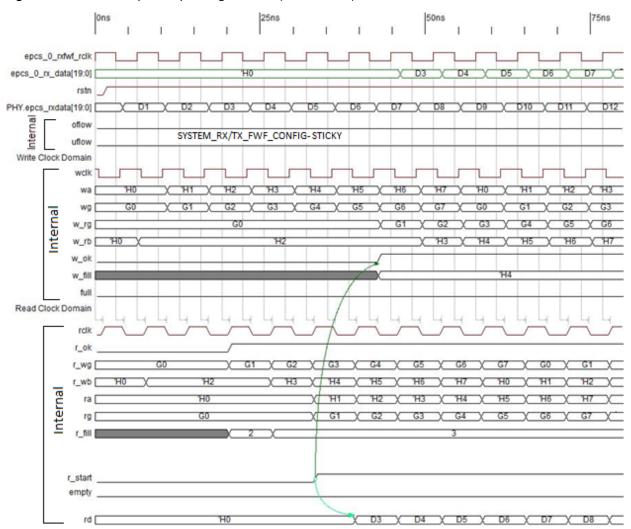

| AXI_S_WVALID       | Input  | AXI3 slave mode: WVALID                                                                                                                                          |