**SUMMER 1987** VOL 8 NO 1 AN ARGUS SPECIALIST PUBLICATION

and and one fair

MIS

£2.75

ACS

MrHamson

SHOOL

TODAY

From the publishers of

NAC Blog

H38.

HA MECNECONDER 3917

....

# DATA ISSUE DEDICATED DEVICES **SPECIAL PURPOSE ICs FOR:**

MUSIC **COMPUTERS** DOMESTIC **AUDIO** TIMING RADIO

Ó

amannin.

A Schlumberger Company

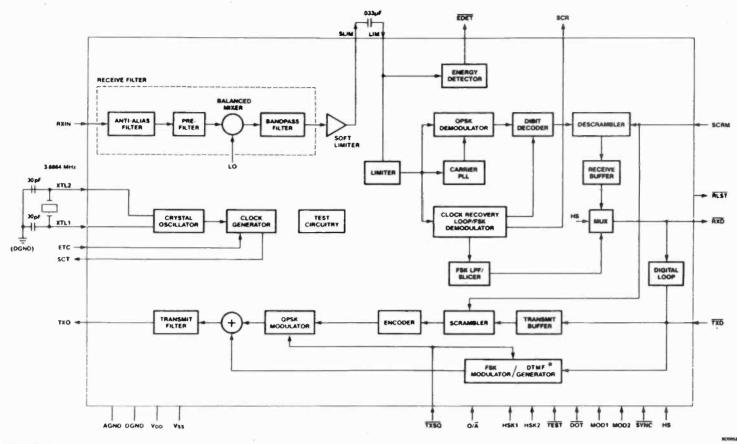

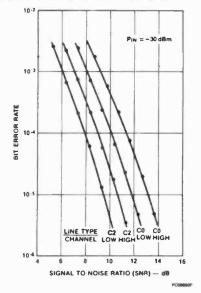

# μ**ΑV22**

# 1200 bps Full Duplex Modem

#### Description

The µAV22 1200 bps full duplex modes I.C. is fabricated in Fairchild's advanced Double-Poly Silicon-Gate CMOS process. The monolithic I.C. performs all the signal processing functions required of a CCITT V.22, alternative B compatible modern. Handshaking protocols, dialing control and mode control functions can be handled by a general purpose, single chip µC. The µAV22, µC and several components to perform the telephone line interface and control provide a high performance, cost effective and ultra-low power solution for V.22-compatible modern designs.

The modem chip performs the modulation, demodulation, filtering and certain control and self-test functions required for a CCITT V.22-compatible modern, as well as additional enhancements. Both 550 Hz and 1800 Hz guard tones and notch filters and DTMF tone generator are on-chip. Switched-capacitor filters provide channel isolation, spectral shaping and fixed compromise equalization. A novel switched-capacitor modulator and a digital coherent demodulator provide 1200 DPSK operation.

The receive filter and energy detector may be configured for call progress tone detection (dialtone, busy, ringback, voice) providing the front end for a smart dialer.

- Functions as a CCITT V.22-compatible modem

- Interfaces to Single Chip µC Which Handles Handshaking Protocols and Mode Control Functions

- e DTMF Tone Generation and Call Progress Tone

- **Detection for Smart Dialer Applications**

- e 1300 Hz Calling Tone Generator On Chip

- Pin and function compatible with the µA212A

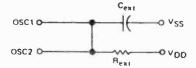

- On Chip Oscillator Uses 3.6864 MHz Crystal

- Few External Components Required

- Operates from +5 and -5 Volt Supplies

- Low Operating Power: 35 mW Typical • 550 Hz and 1200 Hz guard tones and notch filters are on-chip

#### **Absolute Maximum Ratings**

VDD to DGND or AGND Vss to DGND or AGND Voltage at any Input

Voltage at any Digital Output

Voltage at any Analog Output

Operating Temperature Range Storage Temperature Range Lead Temperature (soldering, 10 seconds)

70 V -7.0 V V<sub>DD</sub> + 0.3 to VSS -0.3 V V<sub>DD</sub> + 0.3 V to DGND -0.3V V<sub>DD</sub> + 0.3 V to V<sub>SS</sub> -0.3 V 0°C to 70°C -65°C to +150°C

300°C

**Connection Diagram** 28-Lead Dip (Top View)

|              | 1  | 5 | 28 | - V00  |

|--------------|----|---|----|--------|

|              | 2  |   | 27 | V88    |

|              | 3  |   | 26 | AGND   |

|              | 4  |   | 25 | D TXO  |

| ETC          | 5  |   | 24 | 0/Ā    |

| SYNC         |    |   | 23 | TXSO   |

| EDET         | ,  |   | 22 | SCT    |

| HS 🗖         | •  |   | 21 | MOD1   |

|              |    |   | 20 | MOD2   |

|              | 10 |   | 19 | TEST   |

| xTL2         | 11 |   | 18 | DGND   |

| <b>m</b> i 🗖 | 12 |   | 17 | HSK2   |

|              | 13 |   | 16 | HBK1   |

| AXD _        | 14 |   | 15 | RLST   |

|              |    |   |    | CDOP10 |

#### Order Information

| Device Code      | Package Code | Package De   |

|------------------|--------------|--------------|

| µAV22DC          | FM           | Ceramic DIP  |

| µAV22PC          |              | Molded DIP   |

| HAV22QC          |              | Molded Surfa |

| *Consult Factory |              |              |

scription ace Mount

Data supplied by Fairchild Semiconductor Ltd.

© Fairchild Semiconductor.

# Volume 8 No. 1

Edited by: Ron Keeley Group Editor: Dave Bradshaw Editorial Director: Ron Moulton Managing Director: Peter Welham

Typesetting by: KAMSET Typesetting, Brentwood, Essex Originated by: Argus Design Printed by: Garden City Press, Letchworth

#### © 1987

Subscription rates upon application to Electronics Digest, Subscriptions Dept., Infonet Ltd., Times House, 179 The Marlowes, Hemel Hempstead, Herts HP1 1BB

Published by: Argus Specialist Publications, 1 Golden Square, London W1R 3AB.

Distributed by: Argus Press Sales & Distribution Ltd., 12-18 Paul Street, London EC2A 4JS (British Isles)

© Argus Specialist Publications Ltd 1987. All material is subject to worldwide copyright protection. All reasonable care is taken in the preparation of the magazine content but the publishers cannot be held legally responsible for errors. Where mistakes do occur, a correction will normally be published as soon as possible afterwards. All prices and data contained in the advertisements are accepted by us as correct at time of going to press. Neither the advertisers not the publishers can be held responsible, however, for any variations which may occur after publication had closed for press.

Welcome to the Summer of 1987. In this issue of Electronics Digest we present full data sheets for more than a dozen selected ICs. They have only one thing in common: each is a complete electronic sub-system on a chip, performing multiple functions that, not too long ago, would have required a circuit board of discrete elements. The selection ranges from relatively simple devices such as smoke and fluid detectors, through single chip AM and FM radios to a universal timer employing a 4-bit computer. Audio circuits include a digitally controlled graphic equaliser IC, a programmable compandor, and a number of sound synthesisers. The datasheets reveal the inner working of the various devices and provide all the information needed by an adventurous constructor to design and build a simple radio, tunes synthesizer, DC motor controller etc.

Contents

| μAV22 V.22 Modem                             | 2  |

|----------------------------------------------|----|

| TDA7000 FM radio                             | 4  |

| $\mu$ A7392 DC motor speed controller        | 7  |

| M112 polyphonic sound generator              | 10 |

| NE572 programmable compandor                 | 20 |

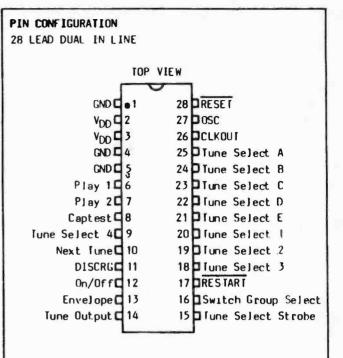

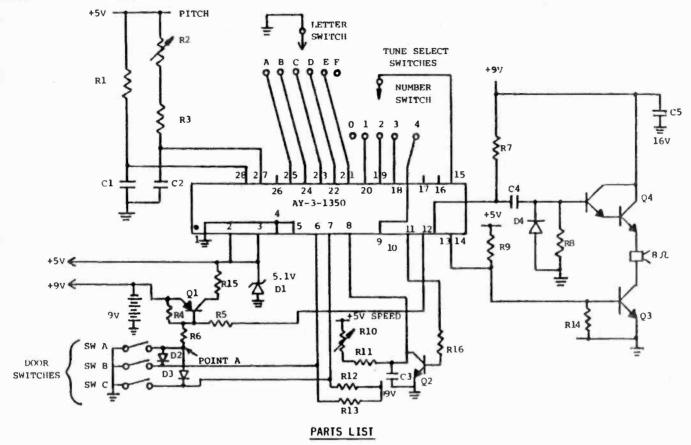

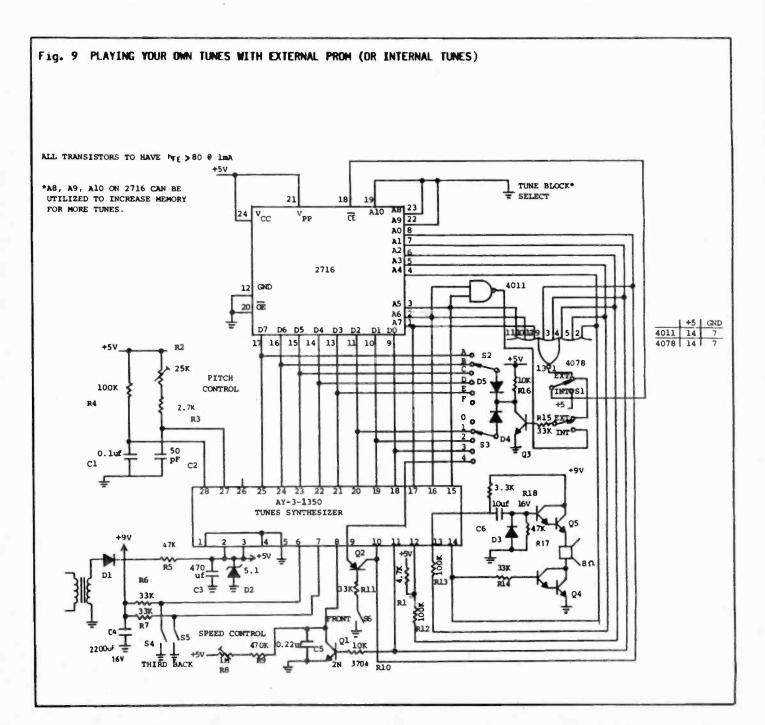

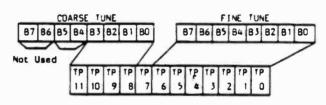

| AY-3-1350 tunes synthesizer                  | 24 |

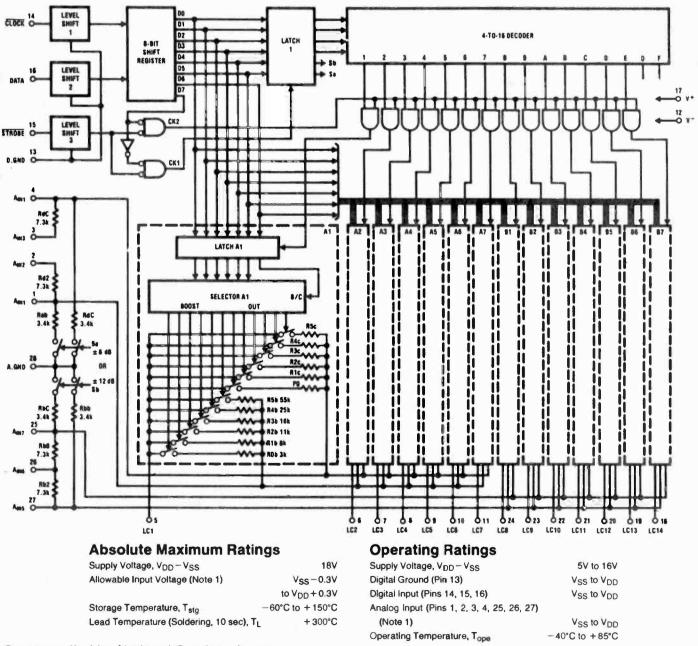

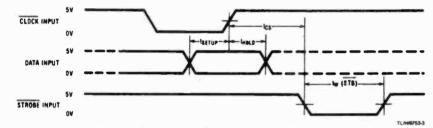

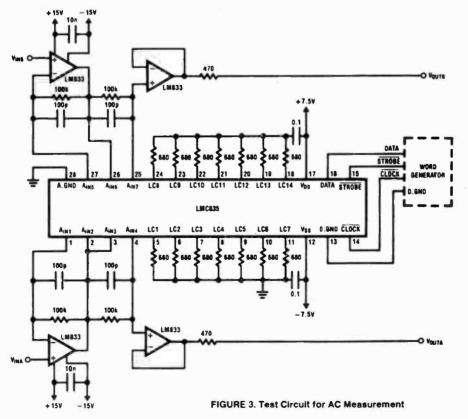

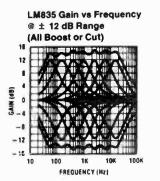

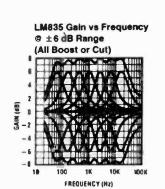

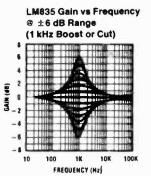

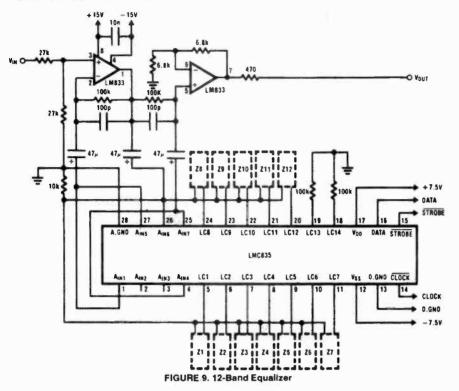

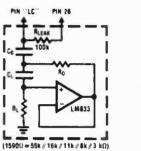

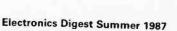

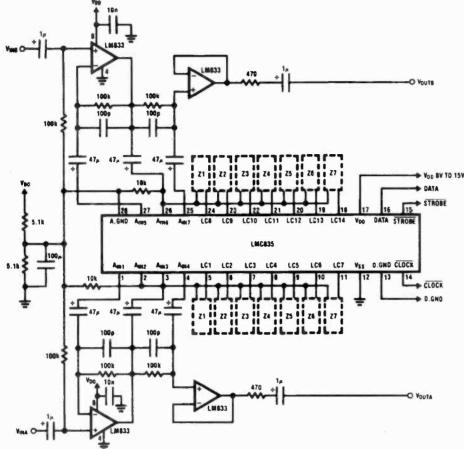

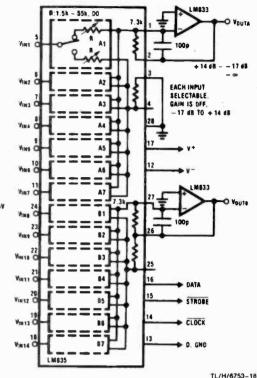

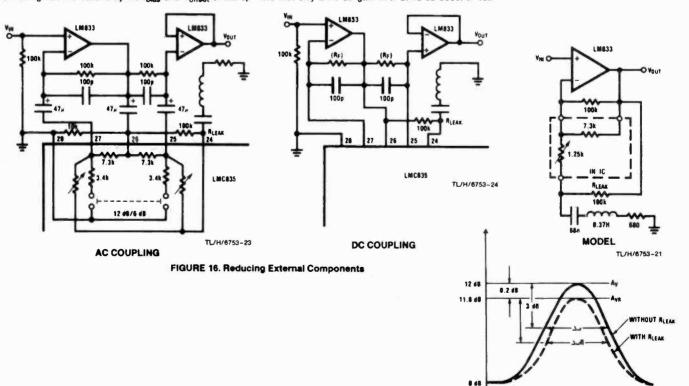

| LMC835 graphics equaliser                    | 34 |

| μA212 300/1200 board Modem                   | 43 |

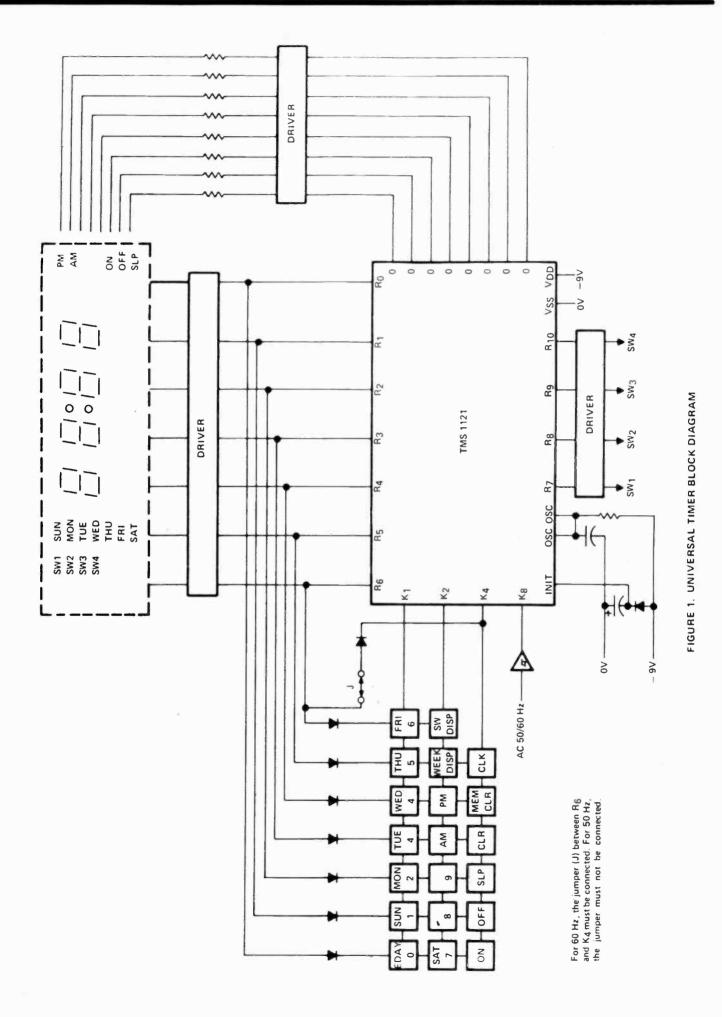

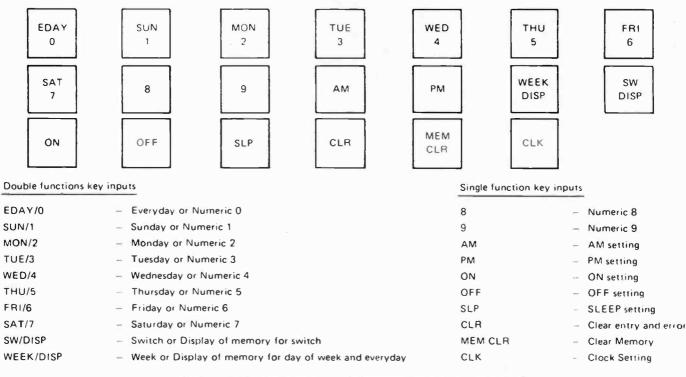

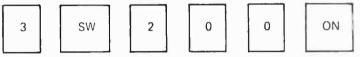

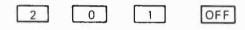

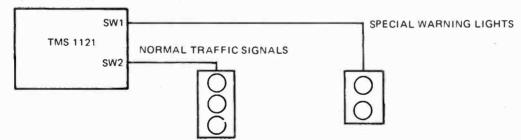

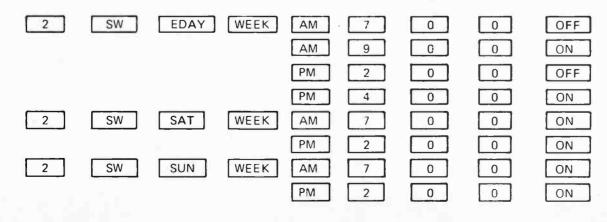

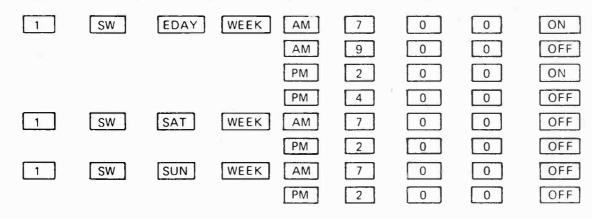

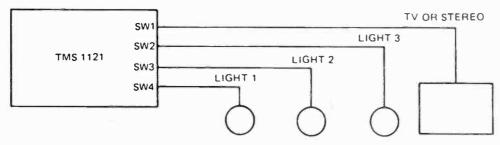

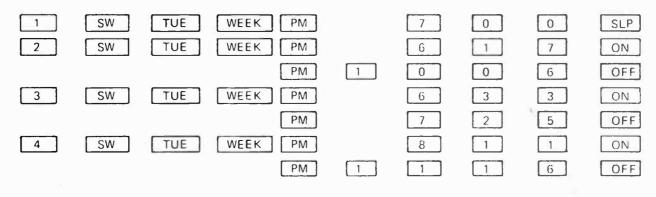

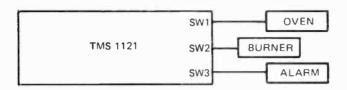

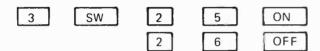

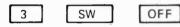

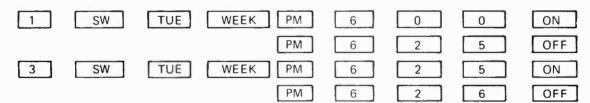

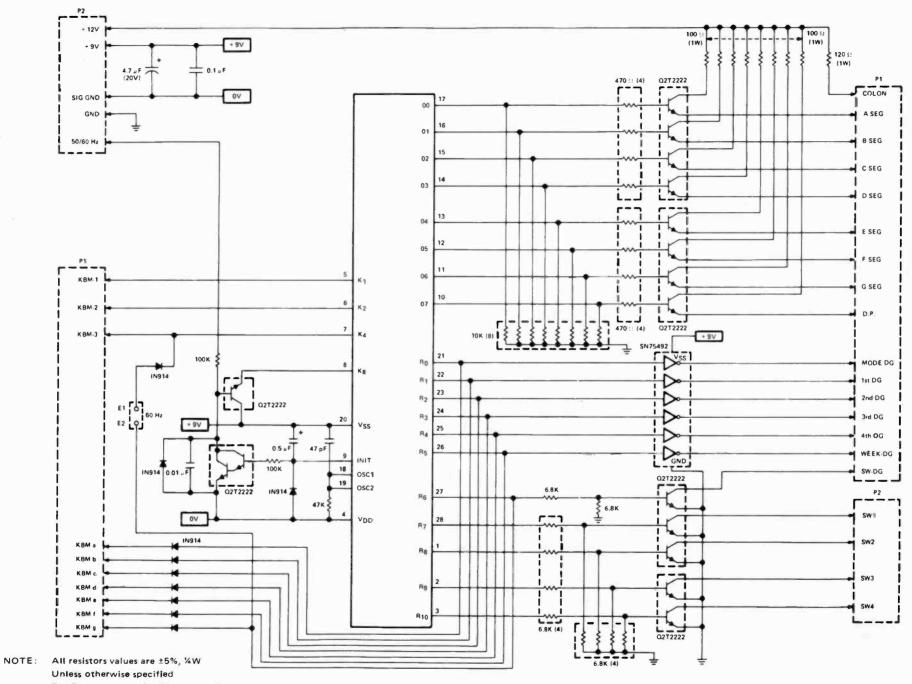

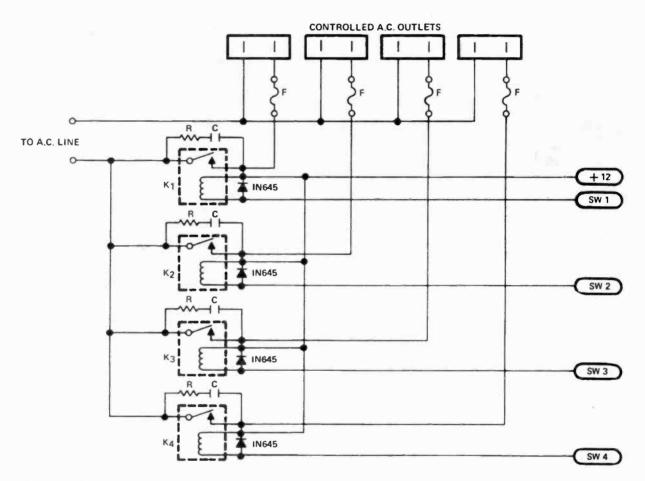

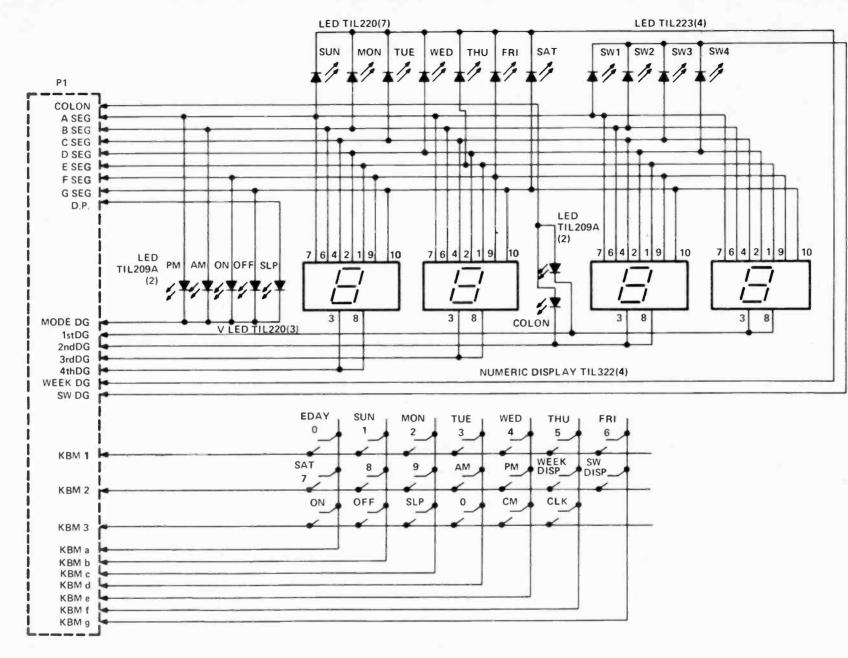

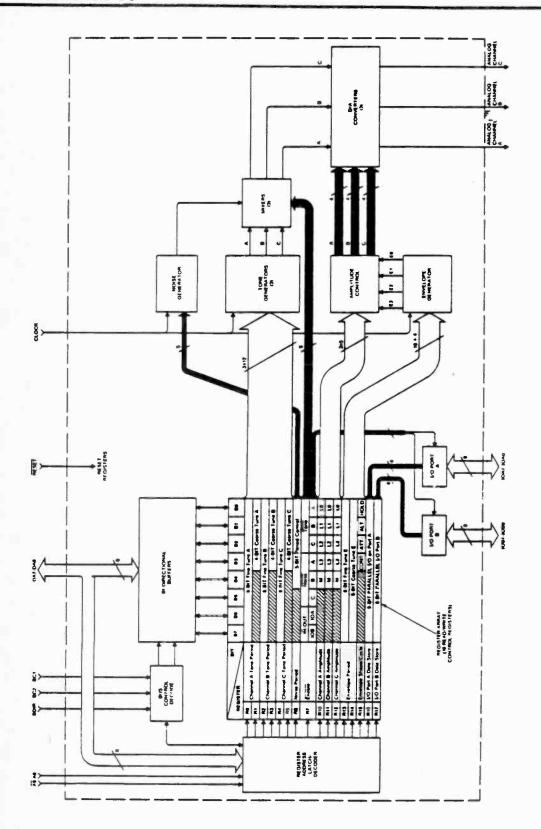

| TMS1121 universal timer controller           | 50 |

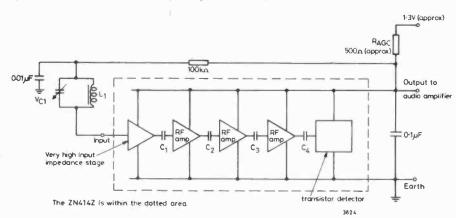

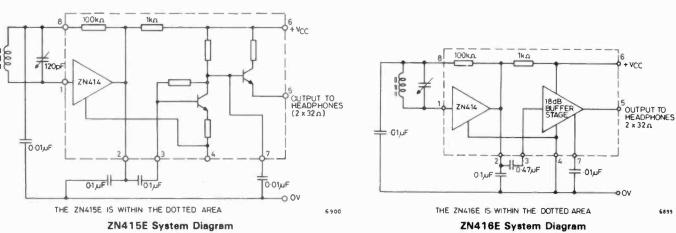

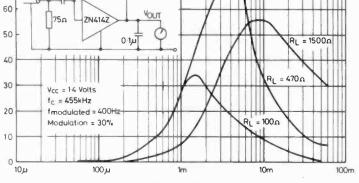

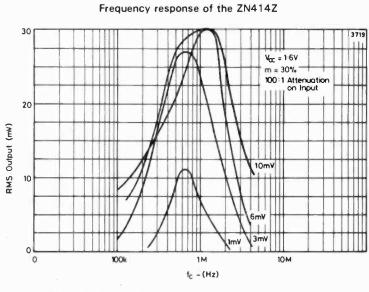

| ZN414 AM radio                               | 63 |

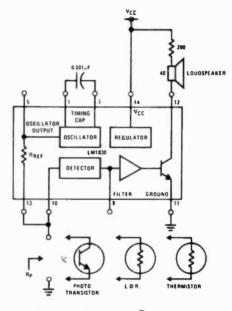

| LM1801 smoke detector                        | 69 |

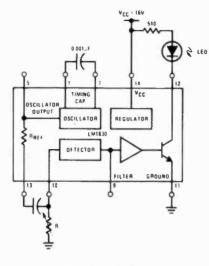

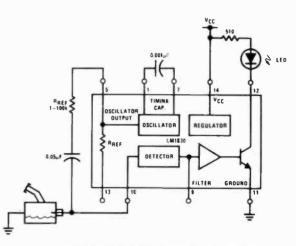

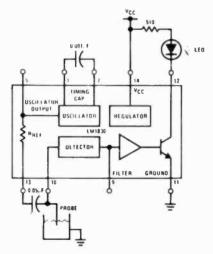

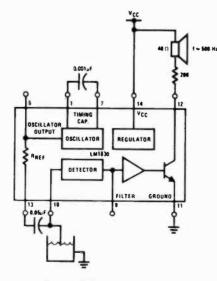

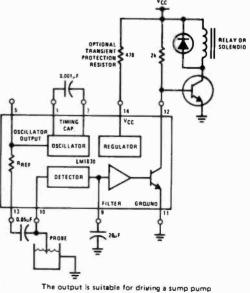

| LM1830 fluid detector                        | 71 |

| AY-3-8910/8912 programmable sound generators | 14 |

| $\mu$ A2240 universal timer                  |    |

Thanks to Mullard/Signetics, National Semiconductor, Fairchild, Texas Instruments, General Instrument, Ferranti, SGS-ATES, and Maplin, for their assistance in compiling this edition of Electronics Digest.

Note: While every effort has been made to ensure that the data contained in this issue of Electronics Digest is accurate, neither the Publisher nor the Manufacturer will accept any liability in respect of the use of the consequences of the use of any data published here. All data intermatication the manufacturer.

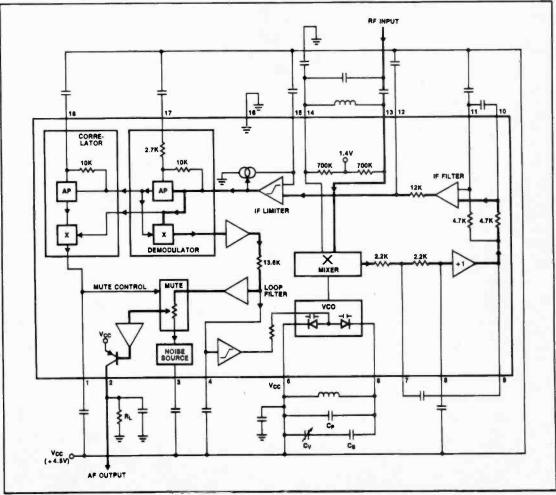

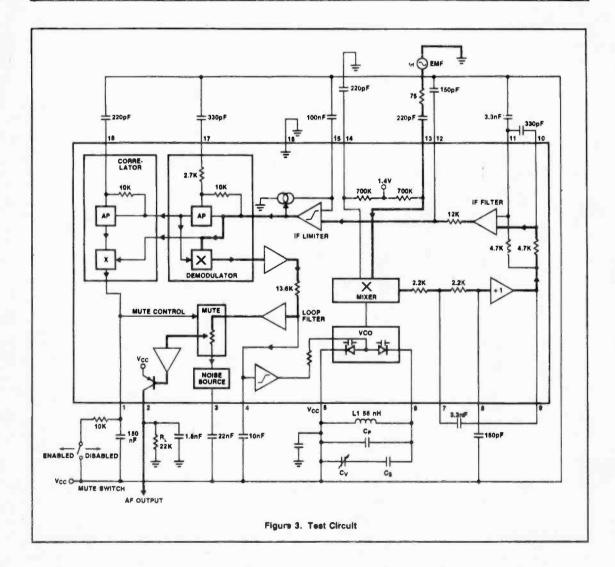

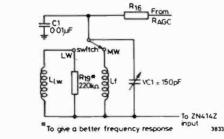

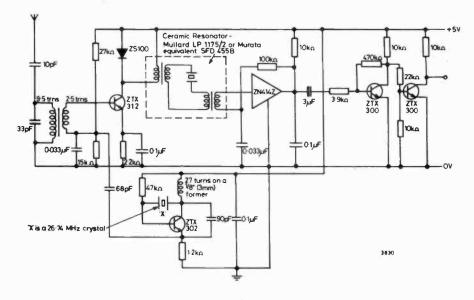

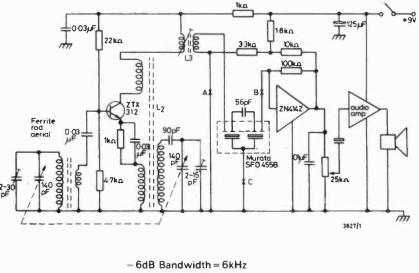

# **FM Radio Circuit**

# DESCRIPTION

The TDA7000 is a monolithic integrated circuit for mono FM portable radios where a minimum of peripheral components is important (small dimensions and low costs).

The IC has an FLL (Frequency-Locked-Loop) system with an intermediate frequency of 70 kHz. The I.F. selectivity is obtained by active RC filters. The only function which needs alignment is the resonant circuit for the oscillator, thus selecting the reception frequency. Spurious reception is avoided by means of a mute circuit, which also eliminates too-nolsy input signals. Special precautions are taken to meet the radiation requirements.

#### FEATURES

- R.F. input stage

- Mixer

- Local oscillator

I.F. amplifier/limiter

- Phase demodulator

- . Mute detector

- . Mute switch

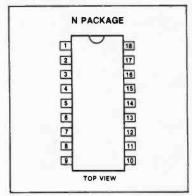

## PIN CONFIGURATION

# FUNCTIONAL PIN DESCRIPTION

NAME AND FUNCTION

PIN NO

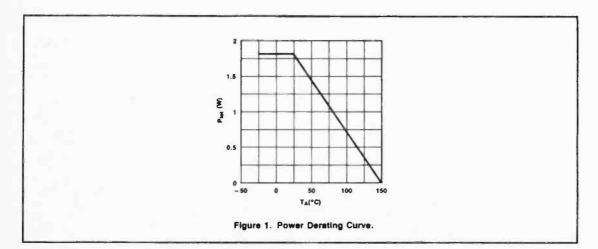

#### ABSOLUTE MAXIMUM RATINGS

|                  | SYMBOL AND PARAMETER                | RATING                                       | UNIT     |

|------------------|-------------------------------------|----------------------------------------------|----------|

| Vcc              | Supply voltage (pin 5)              | 12                                           | V        |

| V <sub>8-5</sub> | Oscillator voltage (pin 6)          | V <sub>CC</sub> -0.5 to V <sub>CC</sub> +0.5 | v        |

|                  | Total power dissipation             | See derating curve                           | Figure 2 |

| TSTG             | Storage temperature range           | -55 to +150                                  | •C       |

| TA               | Operating ambient temperature range | 0 to +60                                     | •C       |

| 1  | Muting capacitor                    |

|----|-------------------------------------|

| 2  | Audio frequency output              |

| 3  | Noise source                        |

| 4  | Loop filter capacitor               |

| 5  | Supply voltage                      |

| 6  | VCO                                 |

| 7  | 1st integrator capacitor (to pin 9) |

| 8  | 2nd integrator capacitor            |

| 9  | 1st integrator capacitor (to pin 7) |

| 10 | IF filter capacitor (to pin 11)     |

| 11 | IF filter capacitor                 |

| 12 | IF limiter capacitor                |

| 13 | RF input                            |

| 14 | Mixer                               |

| 15 | Current source capacitor            |

| 16 | Ground                              |

| 17 | Demodulator capacitor               |

| 18 | Correlator capacitor                |

#### BLOCK DIAGRAM

Data supplied by Mullard/Signetics.

4

© Mullard/Signetics.

# DC ELECTRICAL CHARACTERISTICS $V_{CC} = 4.5V$ ; $T_A = 25$ °C: measured in Figure 3; unless otherwise specified

| SYMBOL             | AND PARAMETER      | TEST CONDITION                 |     | TDA7000 |     | UNIT |

|--------------------|--------------------|--------------------------------|-----|---------|-----|------|

| STMOUL             | AND PANAMETER      | TEST CONDITION                 | Min | Тур     | Max |      |

| V <sub>cc</sub>    | Supply voltage     | (Pin 5)                        | 2.7 | 4.5     | 10  | v    |

| Icc                | Supply current     | $V_{\rm CC} = 4.5 V$           |     | 8       |     | mA   |

| I <sub>6</sub>     | Oscillator current | (Pin 6)                        |     | 280     |     | μА   |

| V <sub>14-16</sub> | Voltage            | (Pin 14)                       |     | 1.35    |     | v    |

| 1 <sub>2</sub>     | Output current     | (Pin 2)                        |     | 60      |     | μA   |

| V2.16              | Output voltage     | (Pin 2) R <sub>L</sub> = 22 kΩ |     | 1.3     |     | V    |

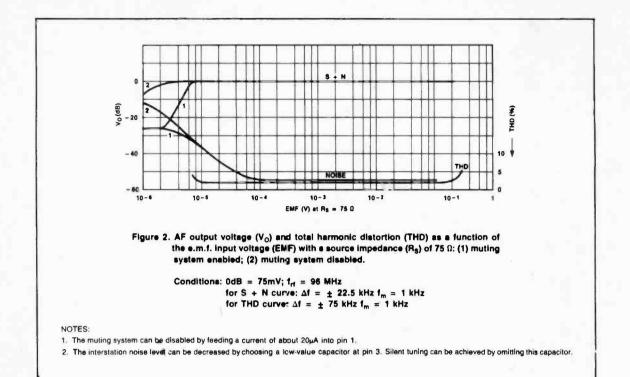

AC ELECTRICAL CHARACTERISTICS  $V_{CC} = 4.5 \text{ V}; T_A = 25^{\circ}\text{C}; \text{ measured in Figure 3 (mute switch open, enabled); } f_{rf} = 96$ MHz (tuned to max. signal at 5  $\mu$ V e.m.f.) modulated with  $\Delta f = \pm 22.5 \text{ kHz}; f_m = 1 \text{ kHz};$ EMF = 0.2 mV (e.m.f. voltage at a source impedance of 75  $\Omega$ ); r.m.s. noise voltage measured unweighted (f = 300 Hz to 20 kHz); unless otherwise specified.

| SYMBOL AND PARAMETER |                                                                                                                                                                                                       | ETER TEST CONDITION                                                        |     | TDA7000 |     |       |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|---------|-----|-------|--|

|                      |                                                                                                                                                                                                       | TEST CONDITION                                                             | Min | Тур     | Max | Max   |  |

|                      |                                                                                                                                                                                                       | -3 dB limiting; muting disabled                                            |     | 1.5     |     |       |  |

| EMF                  | Sensitivity (see Figure 2)<br>(e.m.f. voltage)                                                                                                                                                        | -3 dB muting                                                               |     | 6       |     | Vų    |  |

|                      |                                                                                                                                                                                                       | S/N = 26 dB                                                                |     | 5.5     |     | ]     |  |

| EMF                  | Signal handling (e.m.f. voltage)                                                                                                                                                                      | THD < 10%; $\Delta f = \pm 75$ kHz                                         |     | 200     |     | mV    |  |

| S/N                  | Signal-to-noise ratio                                                                                                                                                                                 |                                                                            |     | 60      |     | dB    |  |

| THD                  | Total harmonic distortion                                                                                                                                                                             | $\Delta f = \pm 22.5 \text{ kHz}$                                          |     | 0.7     |     | %     |  |

| THU                  | rotal narmonic distortion                                                                                                                                                                             | $\Delta f = \pm 75 \text{ kHz}$                                            |     | 2.3     |     | 7 90  |  |

| AMS                  | MS AM suppression of output voltage (ratio of the AM output signal referred to the FM output signal)<br>FM signal: f <sub>m</sub> = 1 kHz; Δf = ±75 kHz<br>AM signal: f <sub>m</sub> = 1 kHz; m = 80% |                                                                            |     | 50      |     | dB    |  |

| RR                   | Ripple rejection                                                                                                                                                                                      | $(\Delta V_{CC} = 100 \text{ mV}; f = 1 \text{ kHz})$                      |     | 10      |     | dB    |  |

| V6-5(rms)            | Oscillator voltage (r.m.s. value)                                                                                                                                                                     | (Pin 6)                                                                    |     | 250     |     | mV    |  |

| Δf <sub>osc</sub>    | Variation of oscillator frequency                                                                                                                                                                     | Supply voltage ( $\Delta V_{CC} = 1V$ )                                    |     | 80      |     | kHz/\ |  |

| S+300                | Colocities                                                                                                                                                                                            |                                                                            |     | 45      |     | dB    |  |

| S_300                | Selectivity                                                                                                                                                                                           |                                                                            |     | 35      |     |       |  |

| ∆f <sub>rt</sub>     | A.F.C. range                                                                                                                                                                                          |                                                                            |     | ±300    |     | kHz   |  |

| в                    | Audio bandwidth                                                                                                                                                                                       | $\Delta V_0 = 3 \text{ dB}$<br>measured with pre-emphasis (t = 50 $\mu$ s) |     | 10      |     | kHz   |  |

| V <sub>O(rms)</sub>  | A.F. output voltage (r.m.s. value)                                                                                                                                                                    | $R_{L} = 22 k\Omega$                                                       |     | 75      |     | mV    |  |

| RL                   | Load resistance                                                                                                                                                                                       | V <sub>CC</sub> = 4.5V                                                     |     |         | 22  | kΩ    |  |

|                      |                                                                                                                                                                                                       | V <sub>CC</sub> = 9.0V                                                     |     |         | 47  |       |  |

#### NOTES:

1. The muting system can be disabled by feeding a current of about 20  $\mu A$  into pin 1.

2. The Interstation noise level can be decreased by choosing a low-value capacitor at pin 3. Silent tuning can be achieved by omitting this capacitor.

# **TDA7000**

6

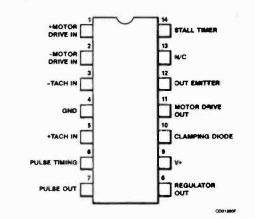

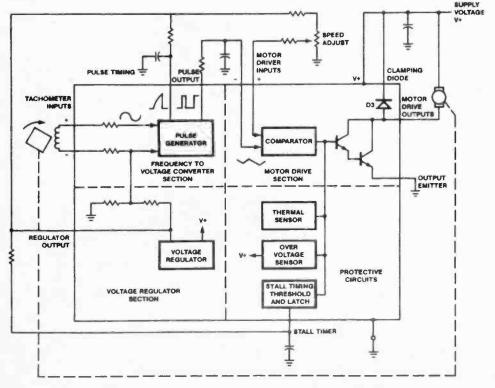

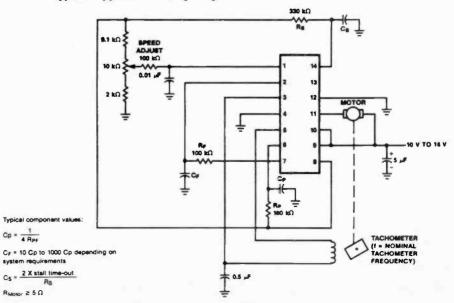

# **DC Motor Speed Control Circuit**

# Description

The µA7392 is designed for precision, closed loop, motor speed control systems. It regulates the speed of capstan drive motors in automotive and portable tape players and is useful in a variety of industrial and military control applications, e.g., floppy disc drive systems and data cartridge drive systems. The device is constructed using the Fairchild Planar Epitaxial process.

The µA7392 compares actual motor speed to an externally presettable reference voltage. The motor speed is determined by frequency to voltage conversion of the input signal provided by the tachometer generator. The result of the comparison controls the duty cycle of the pulse width modulated switching motor drive output stage to close the system's negative feedback loop.

Thermal and over voltage shutdown are included for selfprotection, and a stall-timer feature allows the motor to be protected from burn out during extended mechanical jams.

- Precision Performance

- High Current Performance

- Wide Range Tachometer Input

Thermal Shutdown, Over Voltage And Stall

- Protection

Internal Regulator

- Wide Supply Voltage Range 6.3 V To 16 V

- Absolute Maximum Ratings

#### Storage Temperature Range Ceramic DIP -65°C to +175°C Molded DIP -65°C to +150°C Operating Temperature Range -40°C to +85°C Lead Temperature Ceramic DIP (soldering, 60 s) 300°C Molded DIP (soldering, 10 s) Internal Power Dissipation<sup>1-3</sup> 265°C 14L-Ceramic DIP 1.36 W 14L-Molded DIP 1.04 W Supply Voltage (V+), V9, 24 V V10. V11 Regulator Output Current, I8 15 mA Voltage Applied to Lead 6 (Tachometer Pulse Timing) 7.0 V

Connection Diagram 14-Lead DiP (Top View)

| Order Inform | ation        |                     |

|--------------|--------------|---------------------|

| Device Code  | Package Code | Package Description |

| µA7392DV     | 6A           | Ceramic DIP         |

| µA7392PV     | 9A           | Molded DIP          |

| Voltage Applied Between Leads 3<br>and 5 (Tachometer Inputs) | ±6.0 V |

|--------------------------------------------------------------|--------|

| Continuous Current through                                   |        |

| Leads 11 and 12 Motor Drive                                  |        |

| Output ON                                                    | 0.3 A  |

| Repetitive Surge Current through                             |        |

| Leads 11 and 12 (Motor Drive ON)                             | 1.0 A  |

| Repetitive Surge Current through                             |        |

| Leads 10 and 11 (Motor Drive OFF)                            | 0.3 A  |

Notes

T<sub>J Max</sub> = 150°C for the Molded DIP, and 175°C for the Ceramic DIP.

Ratings apply to ambient temperature at 25°C. Above this temperature, derate the 14L-Ceramic DIP at 9.1 mW/°C, the 14L-Molded DIP at 8.3 mW/°C.

3. Internally Limited.

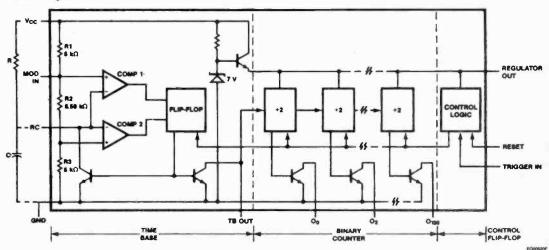

# Block Diagram

Data supplied by Fairchild Semiconductor Ltd. © Fairchild Semiconductor.

# μ**A**7392

Electrical Characteristics T<sub>A</sub> = 25°C, V+ = 14.5 V, unless otherwise specified.

| Symbol              | Characteristic                                                           | Condition                                                              | Min  | Тур  | Max   | Unit              |

|---------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------|------|------|-------|-------------------|

| Voltage Re          | gulator Section (Test Circuit 1)                                         |                                                                        |      |      |       |                   |

| lcc                 | Supply Current                                                           | Excluding Current into Lead 11                                         |      | 7.5  | 10    | mA                |

| VReg                | Regulator Output Voltage                                                 |                                                                        | 4.5  | 5.0  | 5.5   | v                 |

| LINEReg             | Regulator Output Line                                                    | V+ = 10 V to 16 V                                                      |      | 6.0  | 20    | ٣V                |

|                     | Regulation ( $\Delta V_8$ )                                              | V+ = 6.3 V to 16 V                                                     |      | 12   | 50    |                   |

| LOADReg             | Regulator Output Load<br>Regulation (ΔV <sub>8</sub> )                   | I <sub>8</sub> from 10 mA to 0                                         |      | 40   |       | mV                |

| Frequency           | to Voltage Converter Section (Test                                       | Circuit 2)                                                             |      |      |       |                   |

| VIN                 | Tachometer (-) Input Bias<br>Voltage                                     | A                                                                      |      | 2.4  |       | V                 |

| IIN                 | Tachometer (+) Input Bias<br>Current                                     | $V_5 = V_3$                                                            |      | 1.0  | 10    | μA                |

| VDIFF               | Tachometer Input Positive<br>Threshold                                   | (V <sub>5</sub> - V <sub>3</sub> )                                     | 10   | 25   | 50    | mV <sub>P−l</sub> |

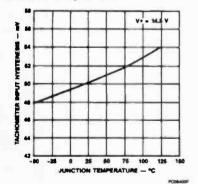

| V <sub>HY</sub>     | Tachometer Input Hysteresis                                              |                                                                        | 20   | 50   | 100   | mV <sub>P-1</sub> |

| R                   | Pulse Timing ON Resistance                                               | V <sub>6</sub> = 1.0 V                                                 |      | 300  | 500   | Ω                 |

| VTH                 | Pulse Timing Switch Threshold                                            |                                                                        | 45   | 50   | 55    | %V8               |

| t,                  | Output Pulse Rise Time                                                   |                                                                        |      | 0.3  |       | μs                |

| tr                  | Output Pulse Fall Time                                                   |                                                                        |      | 0.1  |       | μs                |

| VSat-LOW            | Pulse Output LOW Saturation<br>(V7)                                      |                                                                        |      | 0.13 | 0.25  | v                 |

| V <sub>Set-HI</sub> | Pulse Output HIGH Saturation $(V_8 - V_7)$                               |                                                                        |      | 0.12 | 0.2   | V                 |

| Source              | Pulse Output HIGH Source<br>Current                                      | V <sub>7</sub> = 1.0 V                                                 | -340 | -260 | - 180 | μA                |

| SVS                 | Frequency-to-Voltage Conversion<br>Supply Voltage Stability <sup>1</sup> | $V_{FV} = 0.25 V_8^2$<br>V <sub>+</sub> = 10 V to 16 V                 |      | 0.1  |       | %                 |

| TS                  | Frequency-to-Voltage Conversion<br>Temperature Stability <sup>3</sup>    | $V_{FV} = 0.25 V_8^2$<br>$T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      | 0.3  |       | %                 |

| Motor Drive         | e Section                                                                |                                                                        |      |      |       |                   |

| VIO                 | Input Offset Voltage                                                     |                                                                        |      |      | 20    | mV                |

| I <sub>IB</sub>     | Input Bias Current                                                       |                                                                        |      | 0.1  | 10    | μA                |

| CMR                 | Common Mode Range                                                        |                                                                        | 0.8  |      | 2.5   | V                 |

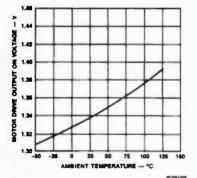

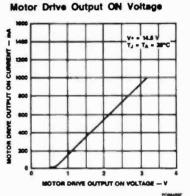

| VSAT                | Motor Drive Output Saturation                                            | i <sub>11</sub> = 300 mA                                               |      | 1.3  | 2.0   | V                 |

| LEAK                | Motor Drive Output Leakage                                               | V <sub>11</sub> = V <sub>10</sub> = 16 V                               |      |      | 5.0   | μA                |

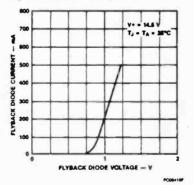

| io                  | Flyback Diode Leakage                                                    | $V_{10} = 16 V, V_{11} = 0 V$                                          |      |      | 30    | μA                |

| VD                  | Flyback Diode Clamp Voltage                                              | I <sub>11</sub> = 300 mA<br>Motor Drive Output OFF                     |      | 1.1  | 1.3   | v                 |

| Protective          | Circuits                                                                 |                                                                        |      |      |       |                   |

| J-T°C               | Thermal Shutdown<br>Junction Temperature <sup>4</sup>                    |                                                                        | -    | 160  |       | °C                |

| J-T°C           | Thermal Shutdown<br>Junction Temperature <sup>4</sup> |     | 160 |     |  |

|-----------------|-------------------------------------------------------|-----|-----|-----|--|

| Over Voltage    | Overvoltage Shutdown <sup>4</sup>                     | 18  | 21  | 24  |  |

| V <sub>TH</sub> | Stall Timer Threshold Voltage <sup>5</sup>            | 2.5 | 2.9 | 3.5 |  |

| ITH             | Stall Timer Threshold Current <sup>5</sup>            |     | 0.3 | 3.0 |  |

#### Notes

- 1. Frequency-to-voltage conversion, supply voltage stability is defined as:  $\frac{V_{FV}(16 V)}{V_{6}(16 V)} = \frac{V_{FV}(10 V)}{V_{6}(10 V)} \div \frac{V_{FV}(14.5 V)}{V_{6}(14.5 V)} \times 100\%$

- 2.  $V_{\rm FV}$  is the integrated DC output voltage from the pulse generator (Lead 7) 3. Frequency-to-voltage conversion temperature stability is defined as:

- $\frac{V_{FV}(85^{\circ}C)}{V_{8}(85^{\circ}C)} = \frac{V_{FV}(-40^{\circ}C)}{V_{8}(-40^{\circ}C)} + \frac{V_{FV}(25^{\circ}C)}{V_{8}(25^{\circ}C)} \times 100\%$

- 4. Motor Drive circuitry is disabled when these limits are exceeded. If the condition continues for the duration set by the external stall timer components, the circuit is latched off until reset by the onterial star unter the power supply input line. 5. If stall timer protection is not required, lead 14 should be grounded.

۷ V μA

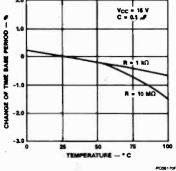

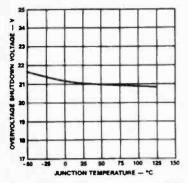

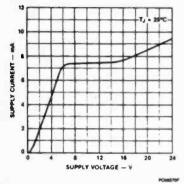

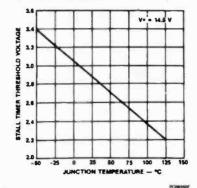

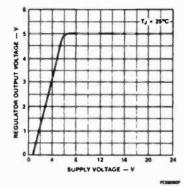

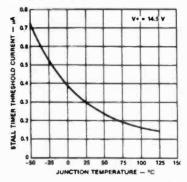

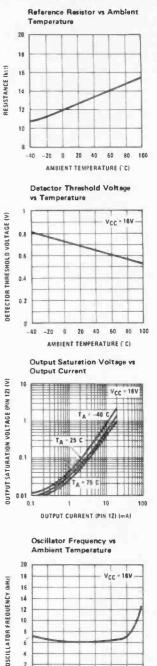

# **Typical Performance Curves**

Overvoltage Shutdown Voltage vs **Junction Temperature**

Supply Current vs Supply Voltage

Tachometer Input Hysteresis vs **Junction Temperature**

Motor Drive Output ON Voltage vs **Amblent Temperature**

#### Stall Timer Threshold Voltage vs **Junction Temperature**

Regulator Output Voltage vs Supply Voltage

Flyback Diode Current (D3) vs Flyback Diode Voltage

Motor Drive Output ON Current vs

60 75

100 125

BATURE - "C

#### Typical Application Using Magnetic Tachometer

## Stall Timer Threshold Current vs **Junction Temperature**

Regulator Output Voltage va **Junction Temperature**

V+ + 34.4 V

.

6. The form

ğ ı

545 .

IS OUT AT

-25 . 25

-

> 6

# **Polyphonic Sound Generator**

- 8 µP PROGRAMMABLE SOUND GENERATOR CHANNELS

- 2MHz CLOCK

- INTERNAL TOS WITH POSSIBILITY OF EXTERNAL SYNCHRONIZATION FOR MULTICHIP USE 6 COMPLETE OCTAVE KEYBOARDS (72 KEYS) FIVE HOMOGENEOUS FOOTAGES  $\mu$ P PROGRAMMABLE BY ADDING A CONSTANT K TO . THE KEYBOARD SITUATION

- SEVEN OCTAVE RELATED OUTPUTS ENVELOPED WITHOUT CONSTANT DC LEVEL (4 FOOTAGES)

- SEVEN FOOTAGE RELATED OUTPUTS WITH DIFFERENT CONFIGURATIONS FOR: FOOTAGES WITH ENVELOPE (WITHOUT CONSTANT DC LEVEL) AND FOOTAGES WITHOUT ENVELOPE (WITH CONSTANT DC LEVEL) AND

- VARIOUS SOUND CHANNEL DIVISIONS (SEE OPTION I, II AND III) POSSIBILITY OF EXCLUDING ONE OR MORE SOUND CHANNELS FROM THE NON ENVEL-OPED FOOTAGE OUTPUTS

- ONE MONOPHONIC OUTPUT NON ENVELOPED RELATED TO SOUND CHANNEL 1 WITH THE POSSIBILITY OF CHOOSING THE FOOTAGE (TWO ADDITIONAL MONOPHONIC OUT-PUTS ON OPTION II).

- 50% DUTY CYCLE ON ALL OUTPUTS

- **DIGITAL DRAWBAR CONTROL (32 LEVELS)**

- ATTACK-DECAY-SUSTAIN-RELEASE (ADSR) ENVELOPE DEFINITION WITH DIGITAL CON-TROL ON A.D.R. AND ANALOG CONTROL ON S ADDITIONAL ANALOG CONTROL ON RELEASE ANALOG PERCUSSION INPUT TO ENVELOPE ONE FOOTAGE (M2) ON THE OCTAVE RE-

- ATED OUTPUTS

- SPECIAL EXTERNAL ENVELOPE POSSIBILITY USING HOLD AND/OR RELEASE ∞. HOLD AND RELASE ∞ ARE DEDICATED TO DECAY AND PEDAL EFFECT. N-CHANNEL TECHNOLOGY 12V SINGLE SUPPLY.

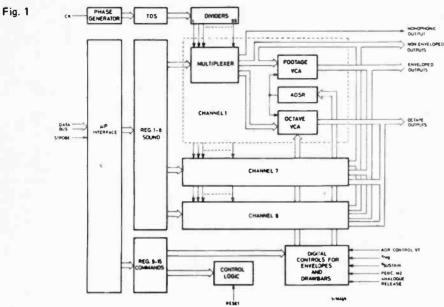

The M112 is a polyphonic sound generator that combines eight generators with envelope shapers and drawbar circuitry in a single package

This versatile circuit simplifies the design of a wide range of polyphonic instruments and, interfacing directly with a microcomputer chip, gives designers an unprecedented degree of flexibility. The M112 is realized on a single monolithic silicon chip using low threshold N-channel silicon gate MOS tecnology. It is available in a 40 lead plastic package.

#### ABSOLUTE MAXIMUM RATINGS

| V <sub>DD</sub> *   | Supply voltage                  | -0.3 to 20 V  |

|---------------------|---------------------------------|---------------|

| V,                  | Input voltage                   | -0.3 to Vpp   |

| V <sub>O(off)</sub> | Off state output voltage        | -0.3 to 20 V  |

| Ptot                | Total package power dissipation | 500 mW        |

| Tstg                | Storage temperature             | -65 to 150 °C |

| Top                 | Operating temperature           | 0 to 70 °C    |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

· All voltages are with respect to VSS

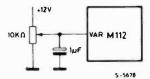

### **PIN CONNECTIONS**

# RECOMMENDED OPERATING CONDITIONS

|     | <ul> <li>A start stort</li> </ul> | -               | -    | Values |      |      |  |

|-----|-----------------------------------|-----------------|------|--------|------|------|--|

|     | Parameter                         | Test conditions | Min. | Typ.   | Max. | Unit |  |

| VDD | Highest Supply Voltage            |                 | 11.4 | 12     | 12.6 | V    |  |

© SGS-ATES.

# BLOCK DIAGRAM

# STATIC ELECTRICAL CHARACTERISTICS

$(V_{DD} = 12V \pm 5\%, V_{SS} = 0V, T_{amb} = 0$  to 50°C unless otherwise specified)

|          | Parameter                         | Test conditions                                 | Min. | Typ, | Max. | Unit |

|----------|-----------------------------------|-------------------------------------------------|------|------|------|------|

| INPUT S  | IGNALS                            |                                                 |      | 1    |      |      |

| VIH      | Input High Voltage                | Pins 3, 6 to 11                                 | 2.4  |      | VDD  | V    |

|          | the second second                 | All other inputs                                | 6    |      | VDD  | V    |

| VIL      | Input Low Voltage Pins 3, 6 to 11 |                                                 | -0.3 |      | 0.8  | V    |

|          |                                   | All other inputs                                | -0.3 |      | 1    | V    |

| VSA      | Analog Ground                     | $R < 10\Omega$ $C = 100\mu F$                   | 0    | 0    | 1    | V    |

| VT       | ADR Control Time                  | R = 1K C = 1µF                                  | 0    |      | VDD  | V    |

| VAR      | Analog Release                    | R = 10K C = 0.1µ                                | 0    |      | VDD  | V    |

| Vreg     | Control OFF Asymptote             | $R < 10\Omega$ $C = 100\mu$                     | 0    | 0    | 1    | V    |

| VSUST    | Control Level Sustain             | R = 1K C = 100µ                                 | 0    |      | VDD  | V    |

| Perc. M2 | Control Level Percussion          | R = 10K                                         | 0    |      | VDD  | V    |

| 161      | Input Leakage Current             | $V_i = V_{DD}$                                  |      |      | 1 *  | μA   |

| UTPUT    | SIGNALS (One key presse           | d)                                              |      |      |      |      |

| 1OL      | Output Low current                | VOL = VDD/2-1V (note 1)                         | 10   | 30   | 50   | μA   |

|          |                                   | V <sub>OH</sub> = V <sub>DD/2+1V</sub> (note 1) | 10   | 30   | 50   | μA   |

| Гон      | Output High Current               | V <sub>OH</sub> = 10V (note 2)                  | 100  | 300  | 500  | μA   |

|          |                                   | V <sub>OH</sub> = 10V                           | 10   | 30   | 50   | μA   |

|          |                                   |                                                 |      |      |      |      |

| OH                               | - Off                                                                        |    |    |   |

|----------------------------------|------------------------------------------------------------------------------|----|----|---|

|                                  | V <sub>OH</sub> = 10V                                                        | 10 | 30 | 3 |

| lo(off) Off state output current | $V_0 = V_{DD}$ (all output pins)                                             |    |    |   |

| .0(011)                          | V <sub>O</sub> = V <sub>SS</sub> (pins 14-15-20 in<br>3 <sup>rd</sup> state) |    |    |   |

| POWER DISSIPATION                |                                                                              |    |    |   |

| 100 | Supply current | T <sub>amb</sub> = 25°C | 50 | mA |

|-----|----------------|-------------------------|----|----|

|     |                |                         |    | -  |

1

-1

uA

μA

Notes: 1. Refers only to FL, FM1, FM2 (pins 20, 15, 14). 2. Refers only to octave outputs with drawbar max.

# DYNAMIC ELECTRICAL CHARACTERISTICS

|                                 | Parameter                      | Test conditions | Min. | Typ.    | Max,  | Uni |

|---------------------------------|--------------------------------|-----------------|------|---------|-------|-----|

| CLOCK                           |                                |                 |      |         |       |     |

| fj                              | Input Clock Frequency          |                 | 250  | 2000.24 | 2.300 | kHz |

| t <sub>r</sub> , t <sub>f</sub> | Rise and Fall Times 10% to 90% |                 |      |         | 30    | ns  |

| ton, toff                       | ON and OFF Times               |                 | 150  |         |       | ns  |

| RESET                           |                                |                 |      |         |       |     |

| tw                              | Pulse Width                    | Clock = 2 MHz   | 10   |         |       | μs  |

| tr                              | Fall Time                      |                 |      |         | 30    | ns  |

| OUTPUT                          | SIGNALS                        |                 |      |         |       |     |

|                                 | Outptu duty cycle              |                 | T    | 50      |       | %   |

# **Electronics Digest Summer 1987**

# GENERAL DESCRIPTION

The M112 contains a microprocessor interface, eight programmable sound generator channels, a top octave synthesiser, a divider chain and control circuitry, (see fig. 1). Each generator consists of logic to select the desired notes and harmonics from 96 frequencies obtained by division, an ADSR envelope generator and two voltage-controlled amplifiers. Programmable attenuators are included for drawbar control of the harmonic content of the sound.

To simplify system design the signals generated in each channel are directed to octave separated outputs and footage outputs. Two voltage-controlled amplifiers are provided for each channel to keep the octave and footage outputs separate.

The attack time, decay time, release time and sustain level are set for all eight channels by common controls. Tone selection, the attack, decay, release parameters, drawbars and special effects are all software controlled.

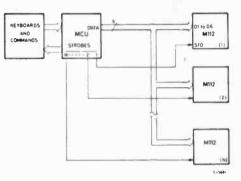

In a typical configuration (fig. 2), one or more M112s are connected to a microprocessor which scans the keyboard and front panel controls in a matrix arrangement. When the microprocessor detects a key depression it chooses one of the sound generators and allocates it to that note. If another key is pressed the microprocessor allocates another sound generator and so on. This process can be repeated until there are no more free channels, i.e. when 8N keys are pressed simultaneously where N is the number of M112s used.

When one of the keys is released the microprocessor resets a control bit in the appropriate generator channel which will then be re-allocated to another key when needed.

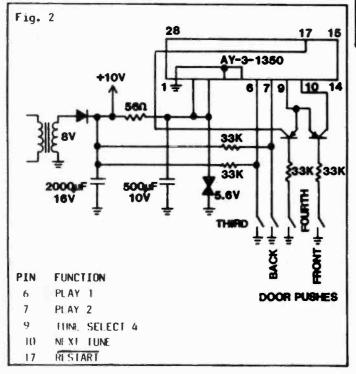

Fig. 2

#### OUTPUTS

The M112 has 15 music output pins. Seven of these are octave outputs, seven are footage outputs and the last is a monophonic output from channel one. This standard configuration can be changed under program control.

The octave outputs, which are enveloped, are so called because there is one output for each octave, i.e. output signals from all eight channels that fall within the same octave are routed to the same output. These outputs are provided to simplify the generation of sinewaves from the squarewaves generated by the M112s digital circuitry. Since each of these outputs handles a limited range of frequencies – exactly one octave – a simple low pass or bandpass filter will do the job. The blend of harmonics sent to the octave outputs is controlled by the drawbar attenuators.

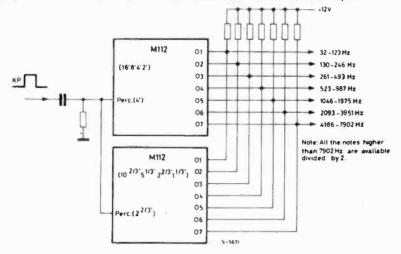

The footage outputs are related to the five footages generated by the M112. These are referred to as L, M1, M2, H1 and H2 (L = Low, M = mid, H = high) and can be programmed to give the three different ranges given in table 1, adding a constant K (number of half tones) to the keyboard information.

All five footages can be obtained from these outputs but only four are mixed by the drawbar circuitry and routed to the octave outputs.

|         | Enveloped footage outputs (option 2)     Octave outputs     Non Enveloped Footage Outputs |        |        |        |      |  |  |  |

|---------|-------------------------------------------------------------------------------------------|--------|--------|--------|------|--|--|--|

| Footage | L                                                                                         | M1     | M2     | H1     | H2   |  |  |  |

| 0       | 16'                                                                                       | 8'     | 4'     | 2'     | 1'   |  |  |  |

| 7       | 10 2/3'                                                                                   | 5 1/3' | 2 2/3' | 1 1/3' | 2/3' |  |  |  |

| 4       | 12 4/5'                                                                                   | 6 2/5' | 3 1/5' | 1 3/5' | 4/5' |  |  |  |

#### TABLE 1 - THE THREE FOOTAGE RANGES OF THE M112

Fig. 3 - Example of octave related output "EVEN" and "ODD" with Percussion input.

In no case will the maximum frequency be higher than 7902 Hz (with a 2 MHz clock). The output configuration for the octave and footage outputs can be changed under program control as mentioned above. There are three options, including the standard configuration, and these are:

- Option 1, the normal configuration gives four enveloped footage outputs, LE, M1E, M2E, H1E, and three non-enveloped outputs, L, M1 and M2. All eight channels are present on each output.

- Option 2 is a special configuration for sawtooth generation (sawtooth waveforms are frequently used in sound synthesis). In this case channels two and three appear only on the outputs FM1 and FM2 (footages M1 and M2) and are excluded from the rest. All five footages are available as enveloped outputs.

- Option 3 is intended for sophisticated automatic accompaniment circuits. All the channels appear on three non-enveloped outputs (FL, FM1, FM2) for chord generation and can be disconnected or command. Channels 4, 5, 6 and 7 appear on four enveloped outputs for arpeggi. The octave outputs are used for the bass and include only channel 8.

| Pin                  | 0                               | ption I    | C                 | Option II               | Option III               |                              | Option IV                          |                               |   |

|----------------------|---------------------------------|------------|-------------------|-------------------------|--------------------------|------------------------------|------------------------------------|-------------------------------|---|

| 15<br>14<br>20<br>18 | FM2<br>FM1<br>FL<br>FH1E        |            |                   | hannel 3)<br>hannel 2}  | FM2<br>FM1<br>FL<br>FH1E | All channels<br>(see note 3) | FM2 (0<br>FM1 (0<br>FH2E (<br>FH1E |                               |   |

| 16<br>17             | FM2E<br>FM1E                    |            | FM2E<br>FM1E      |                         | FM2E<br>FM1E             | only channels<br>4-5-6-7     | FM2E<br>FM1E                       | only channel                  |   |

| 19                   | FLE                             | For the    | FLE               |                         | FLE .                    |                              | FLE                                | ]                             |   |

| 40                   | O1E                             | 8 channels | 01E<br>02E<br>03E | O2E                     | Only channels            | O1E                          |                                    | OIE                           | ) |

| 36                   | O2E                             |            |                   |                         | 1-4-5-6-7-8              | O2E                          |                                    | 02E                           |   |

| 35                   | O3E                             |            |                   |                         | O3E                      |                              | O3E                                | a shu shannal (               |   |

| 38                   | O4E                             |            | 04E               |                         | O4E                      | only channel 8               | 04E                                | only channel 8                |   |

| 39                   | O5E                             |            | O5E               |                         | O5E                      |                              | 05E                                |                               |   |

| 37                   | O6E                             | 1          | O6E               |                         | O6E                      |                              | 06E                                |                               |   |

| 34                   | 07E                             | 1          | 07E               | )                       | O7E .                    | )                            | 07E                                | ļ                             |   |

| 21                   | 1 Monophonic out<br>(channel 1) |            | Mono<br>(channe   | Mono<br>(channel 1)     |                          | ± 1)                         | Mono<br>(channel 1)                |                               |   |

|                      | Standard                        | USB        | Special           | for sawtooth<br>on etc. |                          | for high class<br>animent    |                                    | or information sical meaning) |   |

#### **TABLE 2 - OUTPUT CONFIGURATIONS**

FL, FM1, FM2 are footage outputs not enveloped (with constant DC level) FLE, FM1E, FM2E, FH1E, FH2E are enveloped (without constant DC level).

- Notes: 1) H2 is available only in option 2 on FH2 enveloped outputs. It is not available on octave related outputs. 2) In the option 2 the Sound channels 2 and 3 are available only on pins 14 and 15 and consequently are excluded from the other outputs.

- 3) Each channel can be disconnected with commands NC1 to NC8 (register 10).

### DRAWBARS AND EFFECTS

One of the significant features of the M112 is the implementation of drawbar control circuitry. This consists of four programmable attenuators, one for each of the footages routed to the octave outputs, which are used to blend harmonics to produce the desired sound.

Other features of the M112 include hold, pedal and percussion effects, all of which are enabled/disabled under software control. Hold, when active, interrupts the decay of the ADSR envelope and Pedal interrupts the release curve. Hold and pedal permit external control of the envelope. This feature can be used, for example, to synthesize very realistic piano and harpisichord sounds.

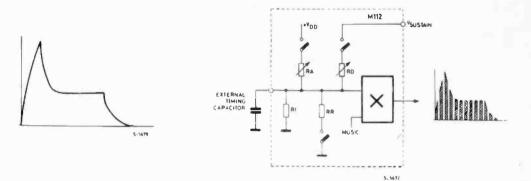

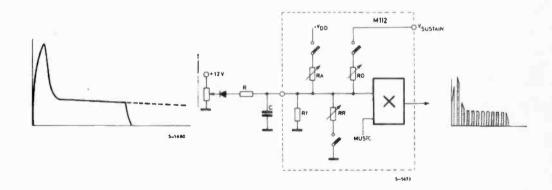

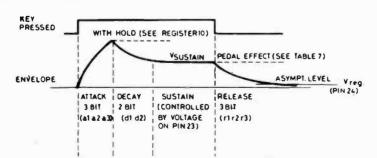

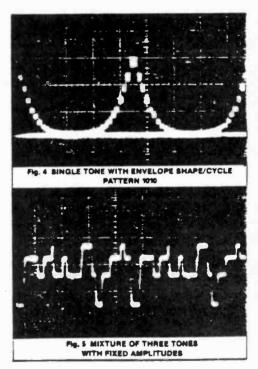

A piano effect can be produced by suitably programming the envelope shapers but by using the hold and pedal controls and a few external components much greater realism can be obtained. Fig. 4 shows a simplified schematic of one of the envelope shapers together with the type of envelope generated. The envelope parameters are controlled by RA, RD, RR and  $V_{SUS}$  (RA, RD and RR are programmed resistors controlling attack, decay and release). Disabling the natural decay and release and adding a handful of components a close approximation to the ideal waveform can be produced (fig. 5). R1 is a very large resistance (typically  $3M\Omega$ ) to give the long (several seconds) time constant for the second decay.

Fig. 4 - With an external capacitor the M112's envelope shapers produce the standard ADSR envelope,

Fig. 5 - Disabling the normal decay and release and adding a few external components a realistic piano envelope can be produced.

#### INPUTS

Eight pins on the M112 are used to define the elementary time interval of the ADSR envelope shapers (Pins 26 to 33). Capacitors, nominally  $1\mu$ F, are connected to these pins. Eight separate capacitors are necessary because the envelope shapers are independently triggered. Analog inputs are also provided to adjust the asymptotic release level (V<sub>reg</sub> pin 24) and the charge/discharge current for attack, decay and release (VT pin 12) in order to compensate the differences of ADR time constant between several M112s used in the same instrument.

The sustain level is fixed by the voltage at pin 23.

The release time constant, digitally controlled by software, can also be fine adjusted by a trimmer connected at pin 25.

#### PROGRAMMING

The M112 is programmed using five basic commands:

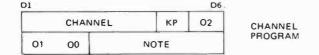

- CHANNEL PROGRAM

- ADSR PROGRAM

- NON-ENVELOPED OUTPUT MASK

- LOAD CONTROL REGISTER

- DRAWBAR PROGRAM

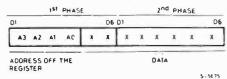

These commands all consist of 12 bits transferred to the M112 (or one of the M112s) in two six-bit bytes through six data lines. Data is latched into the M112 synchronously by a strobe signal. The M112 can be connected directly to an M387X series microcomputer.

Each command contains the address of the Register in which data is to be memorized (there are 16 registers) and the data.

Channel program commands consist of the channel code (4 bits), octave code (3 bits), note code (4 bits) and a control bit, KP (key pressed). KP must be set if the key has just been pressed and reset if the note has just been released.

Resetting KP does not necessarily silence the channel because the sound continues after the key has been released if the release time is non-zero. To stop a channel completely the unused note and octave codes are used.

If an unused note code is programmed the channel is turned off with the output transistor in the ON state and if an unused octave code is used the channel is turned off with the output transistor in the OFF state. Six octave codes and twelve note codes are recognized, giving a keyboard span of 72 keys.

For example, to tell an M112 that channel three is to play  $F^{\#}$  in the third octave the command is:

| D1 |   |   |   |   | D6 |                                               |

|----|---|---|---|---|----|-----------------------------------------------|

| 0  | 0 | 1 | 0 | 1 | 0  | CHANNEL 3 CODE IS 001<br>OCTAVE 3 CODE IS 011 |

| 1  | 1 | 0 | 1 | 1 | 0  | F # NOTE CODE IS 0110<br>KP IS SET            |

The ADSR Program command sets the attack, decay and release times for all the envelope shapers. This command takes the form:

| 1 | D1 |    |    |    |    | D6 |         |

|---|----|----|----|----|----|----|---------|

| į | 1  | 0  | 0  | 0  | r3 | r2 | ADSR    |

| 1 | r1 | d2 | d1 | a3 | a2 | a1 | PROGRAM |

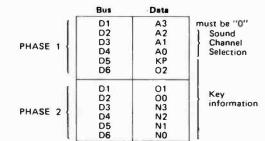

The code 1000 selects the ADSR control register, a3/a2/a1 is the attack time, d2/d1 is the decay time and r3/r2/r1 is the relase time. These times are all multiples of the time interval set by external capacitors. With the suggested 1µF values this time interval is 15ms. The release code 000 is used to enable the pedal effect.

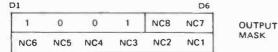

The Non-Enveloped Output Mask command is used to select which channels are to be routed to the non-enveloped footage outputs. Any or all of the eight channels can be excluded by setting the appropriate bit.

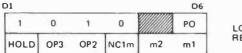

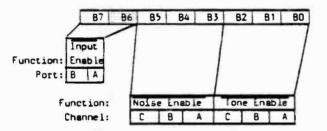

The Load Control Register command selects the footage and output options and enables/disables the hold and percussion facilities.

LOAD CONTROL REGISTER

"NC1m" is a control bit that excludes channel one from all outputs except the three non-enveloped footages outputs. PO is the percussion disable bit, m2/m1 is the footage option select code for the monophonic output and OP2/OP1 the output configuration select code.

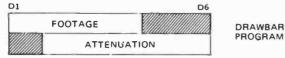

The drawbar-controlled attenuators are set independently for each footage using the Drawbar Program Command which has the form:

Footage is selected by addressing registers R12 to R15.

Attenuation is controlled in 32 linear steps which can be conveniently reduced to the conventional 16 or 8-step logarithmic scale using a lookup table.

# APPLICATIONS

The M112 is intended for a wide range of applications ranging from simple single-keyboard organs to 2-3 manual instruments with sophisticated synthesis and accompaniment facilities. It can also be used in electronic pianos, harpsichords, string synthesizers etc.

# DESCRIPTION

#### Pin 1 - VSA Analog ground

Ground connection of all outputs. It is typically connected to  $V_{SS}$ . By adjusting its value with respect to  $V_{SS}$  (plus/minus) it is possible to modify the output current and compensate the differences in current between several M112s used in the same applications.

# Pins 2 and 13 - VSS, VDD

Power supply connections. V<sub>DD</sub> is hominally 12V; V<sub>SS</sub> is to be connected to GND.

#### Pin 4 - Reset input

It is used to synchronize various M112s in multichip use. The reset is activated when the input is at H Level. In this condition the chip is blocked.

#### Pin 5 - Clock input

It has to be connected to an external oscillator of 2 MHz.

#### Pin 6 to 11 - D1, D6 Data bus input Pin 3 - STD Data Strobe input

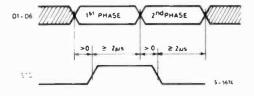

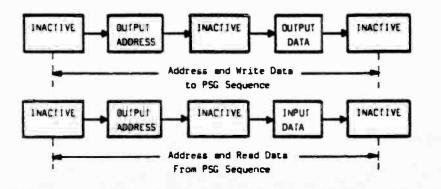

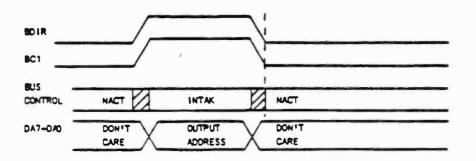

These pins are used to transfer the 12 bits of data from the microprocessor to the registers of various M112s using a two phase procedure.

The first six bits of data are latched on the positive edge of STD, while the other six bits are latched on the negative edge of STD.

Each  $2 \times 6$  bit of information contains the address of the register (4 bit/16 registers) and the data up to 8 bits to be memorized in the selected register.

#### **TABLE 3 - REGISTER SELECTION**

| A0 | 0 A1 A2 |     | A3 | Register n° | Register function |

|----|---------|-----|----|-------------|-------------------|

| 0  | 0       | 0   | 0  | 1           | 1                 |

| 1  | 0       | 0   | 0  | 2           |                   |

| 0  | 1       | 0   | 0  | 3           |                   |

| 1  | 1       | 0   | 0  | 4           | Note-octave etc.  |

| 0  | 0       | 1   | 0  | 5           | For Sound channel |

| 1  | 0       | 1   | 0  | 6           |                   |

| 0  | 1       | 1 1 | 0  | 7           |                   |

| 1  | 1       | 1   | ۵  | 8           |                   |

| 0  | 0       | 0   | 1  | 9           | 1                 |

| 1  | 0       | 0   | 1  | 10          | 11                |

| 0  | 1       | 0   | 1  | 11          |                   |

| 1  | 1       | 0   | 1  | 12          | Control Commands  |

| 0  | -0      | 1   | 1  | 13          |                   |

| 1  | 0       | 1   | 1  | 14          |                   |

| 0  | 1       | 1   | 1  | 15          | J                 |

| 1  | 1       | 1 1 | 1  | 16          | Used for test*    |

\* This address sets the Ic in a test condition that can only be modified by a Reset command on pin 4.

#### **Registers 1 to 8**

There registers are related to the sound channels

A0-A2: Sound channel selection with reference to table 3, register 1 is related to channel 1, register 2 to channel 2 and so on up to channel 8.

TABLE 4

|                     |          | Octave | Code | 02 | 01 | 00 |

|---------------------|----------|--------|------|----|----|----|

| ].                  | Note OFF |        | 0    | 0  | 0  | 0  |

| 1\                  |          | 1      | 1    | 0  | 0  | 1  |

|                     |          | 2      | 2    | 0  | 1  | 0  |

| Output              |          | 3      | 3    | 0  | 1  | 1  |

| transistor<br>"OFF" |          | 4      | 4    | 1  | 0  | 0  |

|                     |          | 5      | 5    | 1  | 0  | 1  |

| 17                  |          | 5      | 6    | 1  | 1  | 0  |

| 1/                  | Note OFF |        | 7    | 1  | 1  | 1  |

# N0-N1-N2-N3 = Note Code (Table 5)

| ABLE 5 | NO | N1 | N2 | N3 | Code | Note       |           |

|--------|----|----|----|----|------|------------|-----------|

|        | 0  | 0  | 0  | 0  | 0    | DO         |           |

|        | 1  | 0  | 0  | 0  | 1    | DO#        |           |

|        | 0  | 1  | 0  | 0  | 2    | RE         |           |

|        | 1  | 1  | 0  | 0  | 3    | RE#        |           |

|        | 0  | 0  | 1  | 0  | 4    | MI         |           |

|        | 1  | 0  | 1  | 0  | 5    | FA         |           |

|        | 0  | 1  | 1  | 0  | 6    | FA#        |           |

|        | 1  | 1  | 1  | 0  | 7    | SOL        |           |

|        | 0  | 0  | 0  | 1  | 8    | SOL#       |           |

|        | 1  | 0  | 0  | 1  | 9    | LA         |           |

|        | 0  | 1  | 0  | 1  | 10   | LA#        |           |

|        | 1  | 1  | 0  | 1  | 11   | SI         |           |

|        | 0  | 0  | 1  | 1  | 12   | Note "OFF" | 1         |

|        | 1  | 0  | 1  | 1  | 13   | Note "OFF" | Output    |

|        | 0  | 1  | 1  | 1  | 14   | Note "OFF" | transisto |

|        | 1  | 1  | 1  | 1  | 15   | Note "OFF" | "ON"      |

#### Register 9 to 15

These registers are related to the various control commands

#### TABLE 6

|        | Register<br>Data<br>Bus | R9       | R10            | R11     | R12 | R13                    | R14  | R 15 | R 16 |

|--------|-------------------------|----------|----------------|---------|-----|------------------------|------|------|------|

|        | [ D1                    | 21       | 1              | 1       | 1   | 1                      | 1    | 1    | 1    |

|        | D2                      | 0        | 0              | 0       | 0   | 1                      | 1    | 1    | 1    |

|        | D3                      | 0        | 0              | 1       | 1   | 0                      | 0    | 1    | 1    |

| HASE 1 | ] D4                    | 0        | 1              | 0       | 1   | 0                      | 1    | 0    | 1    |

|        | D5                      | r3       | NC8            | X       | x   | x                      | X    | x    | ×    |

|        | D6                      | r2       | NC7            | PO      | x   | ×                      | ×    | ×    | ×    |

|        | [ D1                    | r1       | NC6            | HOLD    | x   | ×                      | ×    | ×    | x    |

|        | D2                      | d2       | NC5            | OP3     | L5  | M1 5                   | M2 5 | H1 5 | ×    |

|        | D3                      | d1       | NC4            | OP2     | L4  | M1 4                   | M2 4 | H1 4 | ×    |

| HASE 2 | D4                      | a3       | NC3            | NC1m    | L3  | M1 3                   | M2 3 | H1 3 | ×    |

|        | D5                      | a2       | NC2            | m2      | L2  | M1 2                   | M2 2 | H1 2 | ×    |

|        | D6                      | a1       | NC1            | m1      | L1  | M1 1                   | M2 1 | H1 1 | ×    |

|        |                         | Envelope | Channel<br>off | Various |     | Drawbar le<br>footages |      | i    | Test |

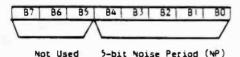

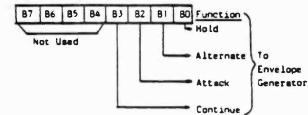

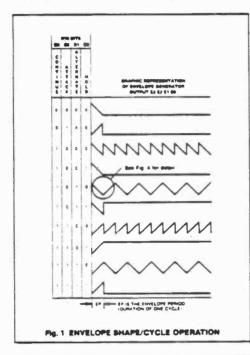

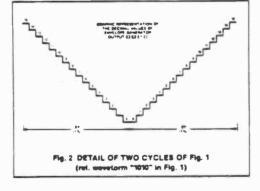

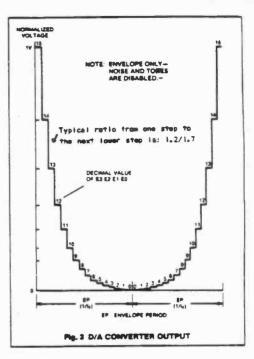

Register 9 - R9 selects the ADR envelope parameters for ADSR control (see fig. 6)

Fig. 6 - ADSR envelope control

Table 7 shows the various time constants for Attack, Decay and Release.

| TA | BL | F | 7 |

|----|----|---|---|

|    |    | - |   |

| <b>a</b> 3 | 82 | a1 | Attack |       |         |

|------------|----|----|--------|-------|---------|

|            | d2 | d1 |        | Decay |         |

| r3         | r2 | r1 |        |       | Release |

| 0          | 0  | 0  | T/2    | 41    | * 00    |

| 0          | 0  | 1  | т      | 8T    | Т       |

| 0          | 1  | 0  | 2T     | 16T   | 2Т      |

| 0          | 1  | 1  | 4T     | 32T   | 4T      |

| 1          | 0  | 0  | 8T     |       | 8т      |

| 1          | 0  | 1  | 16T    |       | 16T     |

| 1          | 1  | 0  | 32T    |       | 32T     |

| 1          | 1  | 1  | 64T    |       | 64T     |

$^*$  In this case it is possible to obtain the pedal effect. T = 3 ms is the typical time constant unit with 8 external capacitors of

1 = 3 ms is the typical time constant unit wit 1  $\mu$ F connected to pins 26 to 33.

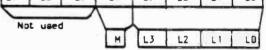

Register 10 - Contains 8 commands to exclude the corresponding sound channel from the non-enveloped footage outputs (FL-FM1-FM2)

0 = ON 1 = OFF

Register 11 - Contains the following 8 commands: m1 and m2 select one of the four footages available for the monophonic output (C1m) according to table 8.

TABLE 8

| m1<br>m2 |   | 0       | 1      | 0      | 1      |

|----------|---|---------|--------|--------|--------|

|          |   | 0       | 0      | 1      | 1      |

|          | 0 | 16'     | 8′     | 4'     | 2'     |

| ĸ        | 7 | 10 2/3' | 5 1/3' | 2 2/3' | 1 1/3  |

|          | 4 | 12 4/5' | 6 2/5' | 3 1/5  | 1 3/5' |

OP2-OP3 - Select the four output options described in table 1 according to table 9.

#### TABLE 9

| OPTION | OP2 | OP3 |

|--------|-----|-----|

| 1      | 0   | 0   |

| 0      | 1   | 0   |

|        | 0   | 1   |

| IV     | 1   | 1   |

HOLD - If 0, disconnects the external 8 capacitors of envelope (1  $\mu F$ ) and the V<sub>SUSTAIN</sub> pin (pin 23) in the decay phase.

PO (Percussion Off) - If 1, the percussion input is inhibited (see pin 22 description).

NC1m-If1, eliminates channel 1 from all outputs except the 3 footage outputs not enveloped (it can be eliminated from these outputs through the command NC1 of register 10).

N.B. NC1m command is inoperative on the monophonic output (C1m) where channel 1 is always present.

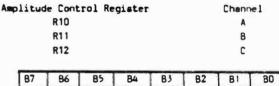

#### Registers 12-13-14-15

These registers contain the drawbar control for 4 footages on the octave related output.

Footages L, M1, M2 and H1 are controlled in 32 linear levels or for example, using conversion table in the microprocessor in 8 or 16 logarithmic levels.

Table 10 shows an example of footage L with 32, 16 and 8 step control in dB.

### Pin 12 - VT - ADR Control

It is used to adjust the ADR time constant for several M112s used in the same application. Using a single M112 it has to be connected to  $V_{DD}$ .

#### TABLE 10

| L | L | L | L. | L   |          | Attenuation in dE | 5       |

|---|---|---|----|-----|----------|-------------------|---------|

| 5 | 4 | 3 | 2  | 1   | 32 steps | 16 steps          | 8 steps |

| 0 | 0 | 0 | 0  | 0 ' | OFF      | OFF               | OFF     |

| 0 | 0 | 0 | 0  | 1   | -29.8    | -29.8             | -29.8   |

| 0 | 0 | 0 | 1  | 0   | -23.8    | -23.8             | -23.8   |

| 0 | 0 | 0 | 1  | 1   | -20.3    | -20.3             | -20.3   |

| 0 | 0 | 1 | 0  | 0   | -17.8    | -17.8             |         |

| 0 | 0 | 1 | 0  | 1   | -15.8    | -15.8             |         |

| 0 | 0 | 1 | 1  | 0   | -14.3    | -14.3             | -14.3   |

| 0 | 0 | 1 | 1  | 1   | -12.9    |                   |         |

| 0 | 1 | 0 | 0  | 0   | -11.8    | -11.8             |         |

| 0 | 1 | 0 | 0  | 1   | -10.7    |                   |         |

| 0 | 1 | 0 | 1  | 0   | -9.8     | -9.8              |         |

| 0 | 1 | 0 | 1  | 1   | -9.0     |                   | -9.0    |

| 0 | 1 | 1 | 0  | 0   | -8.2     | -8.2              |         |

| 0 | 1 | 1 | 0  | 1   | -7.5     |                   |         |

| 0 | 1 | 1 | 1  | 0   | -6.9     | -6.9              |         |

| 0 | 1 | 1 | 1  | 1   | -6.3     |                   |         |

| 1 | 0 | 0 | 0  | 0   | -5.7     | -5.7              |         |

| 1 | 0 | 0 | 0  | 1   | -5.2     |                   |         |

| 1 | 0 | 0 | 1  | 0   | -4.7     |                   |         |

| 1 | 0 | 0 | 1  | 1   | -4.2     | -4.2              | -4.2    |

| 1 | 0 | 1 | 0  | 0   | -3.8     |                   |         |

| 1 | 0 | 1 | 0  | 1   | -3.4     |                   |         |

| 1 | 0 | 1 | 1  | 0   | -3.0     | -3.0              |         |

| 1 | 0 | 1 | 1  | 1   | -2.6     |                   |         |

| 1 | 1 | 0 | 0  | 0   | -2.2     |                   |         |

| 1 | 1 | 0 | 0  | 1   | -1.9     |                   |         |

| 1 | 1 | 0 | 1  | 0   | -1.5     | -1.5              |         |

| 1 | 1 | 0 | 1  | 1   | -1.2     |                   |         |

| 1 | 1 | 1 | 0  | 0   | -0.9     |                   |         |

| 1 | 1 | 1 | 0  | 1   | -0.58    |                   |         |

| 1 | 1 | 1 | 1  | 0   | ~0.29    |                   |         |

| 1 | 1 | 1 | 1  | 1   | 0        | 0                 | 0       |

# Pin 14 to 20 - FM1, FM2, FM2E, FM1E, FH1E, FLE, FL (Footages output)

The "wired-or" function is possible on all outputs.

The non enveloped outputs (with constant DC level) are push-pull current generators.

The enveloped outputs (with non constant DC level) are open drain sink current generators. Output duty cycle is 50%.

#### Pin 21 - C1m

Monophonic output of channel 1 (always present). Duty cycle of the waveform is 50%.

#### Pin 22 - Percussion M2

Using a specific signal on this input it is possible to have a percussion effect on M2 footage for the octave related output.

# Pin 23 - V SUSTAIN

This input defines the level of sustain (see fig. 6).

# Pin 24 - V reg

This pin controls the asymptote of V<sub>RELEASE</sub> through the gate of a transistor which discharges the envelope capacitor. If the performance at the end of release time is considered satisfactory, this pin must be connected to V<sub>SS</sub>. Otherwise this input can be connected to a voltage not higher than 1V.

#### Pin 25 - VAR Analog release

This pin is intended for analog control of the release time constant when it is required in addition to the digital one controlled by software.

It allows intermediate values not included in table 7 (see explanation of register 9). In the case of pedal effect connect this input to  $V_{\rm SS}$ .

### Pin 26 to 33 - CH1, CH8 Envelope capacitor inputs

8 capacitors (typical value =  $1\mu$ F) have to be connected for the ADSR envelopes.

# Pin 34 to 40 - O1E, O7E Octave Outputs

Octave related outputs. Duty cycle is 50%.

# Programmable Analog Compandor

#### DESCRIPTION

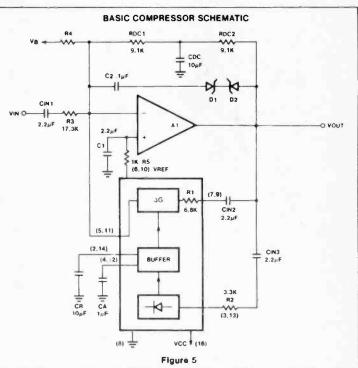

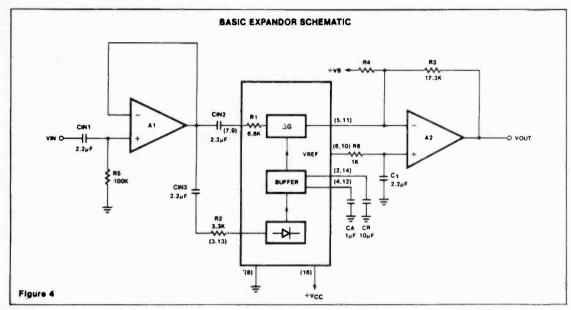

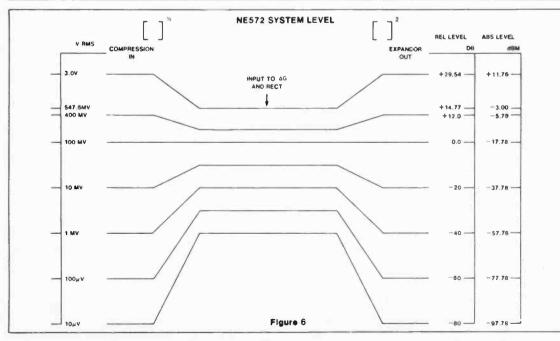

The NE572 is a dual channel, high performance gain control circuit in which either channel may be used for dynamic range compression or expansion. Each channel has a full wave rectifier to detect the average value of input signal; a linearized, temperature compensated variable gain cell (AG) and a dynamic time constant buffer. The buffer permits independent control of dynamic attack and recovery time with minimum external components and improved low frequency gain control ripple distortion over previous compandors.

The NE572 is intended for noise reduction in high performance audio systems. It can also be used in a wide range of communication systems and video recording applications.

#### FEATURES

- Independent control of attack and recovery time.

- Improved low frequency gain control rippie

- Complementary gain compression and expansion with external Op Amp

- Wide dynamic range-greater than 110dB

- Temperature compensated gain control

- Low distortion gain cell

- Low noise 6µV typical

- Wide supply voltage range-6V-22V System level adjustable with external components.

#### APPLICATIONS

- **Dynamic noise reduction system**

- **Voltage control amplifier**

- Stereo expandor

- Automatic level control High level limiter

- Low level noise gate

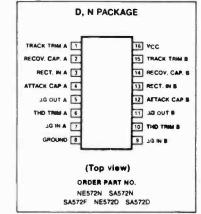

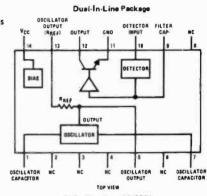

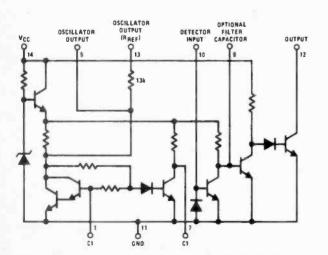

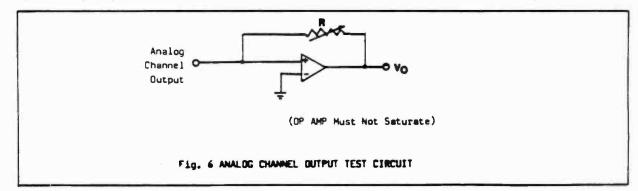

# BLOCK DIAGRAM

1. Supplied only in large SO (Small Outline) package

#### ABSOLUTE MAXIMUM RATINGS

| PARAMETER                   | RATING  | UNIT |

|-----------------------------|---------|------|

| Supply voltage              | 22      | VDC. |

| Operating temperature range | 0 to 70 | °C   |

| Power dissipation           | 500     | mW   |

#### AUDIO SIGNAL PROCESSING IC COMBINES VCA AND FAST AT-TACK-SLOW RECOVERY LEVEL SENSOR

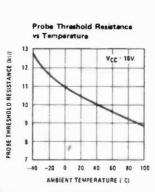

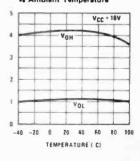

In high performance audio gain control applications it is desirable to independently control the attack and recovery time of the gain control signal. This is true, for example, in compandor applications for noise reduction. In high end systems the input signal is usually split into two or more frequency bands to optimize the dynamic behavior for each band. This reduces low frequency distortion due to control signal ripple, phase distortion, high frequency channel overload and noise modulation. Because of the expense in hardware, multiple band signal processing up to now was limited to professional audio applications.

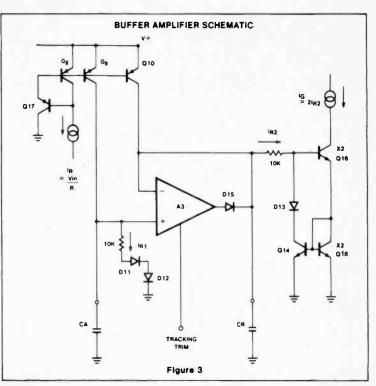

With the introduction of the Signetics NE572 this high performance noise reduction concept becomes feasible for consumer hl fi applications. The NE572 is a dual channel gain control IC. Each channel has a linearized, temperature compensated gain cell and an improved level sensor. In conjunction with an external low noise op amp for current to voltage conversion, the VCA features low distortion, low noise and wide dynamic range. The novel level sensor which provides gain control current for the VCA gives lower gain control ripple and independent control of fast attack, slow recovery dynamic response. An attack capacitor CA with an internal 10K resistor RA defines the attack time TA. The recovery time TR of a tone burst is defined by a recovery capacitor CR and an internal 10K resistor RR. Typical attack time of 4MS for the high frequency spectrum and 40MS for the low frequency band can be obtained with .1µF and 1.0µF attack capacitors respectively. Recovery time of 200MS can be obtained with a 4.7 µF external capacitor. With the recovery capacitor added in the level sensor, the gain control ripple for low frequency signals is much lower than that of a simple RC ripple filter. As a result the residual third harmonic distortion of low frequency signal in a two quad transconductance amplifier is greatly improved. With the 1.0µF attack capacitor and 4.7µF recovery capacitor for a 100HZ signal the third harmonic distortion is improved by more than 10db over the simple RC ripple filter with a single 1.0µF attack and recovery capacitor, while the attack time remains the same.

The NE572 is assembled in a standard 16 pin dual in line plastic package and in oversized SO (Small Outline) package. It operates over wide supply range from 6V to 22V. Supply current is less than 6mA. The NE572 is designed for consumer application over a temperature range 0-70°C. The SA572 is intended for applications from - 40°C to + 85°C.

#### **NE572 BASIC APPLICATIONS**

#### Description

The NE572 consists of two linearized, temperature compensated gain cells (AG) each with a full-wave rectifier and a buffer amplifier as shown in the block dlagram. The two channels share a 2.5V common bias reference derived from the power supply but otherwise operate independently. Because of inherent low distortion, low noise and the capability to linearize large signals, a wide dynamic range can be obtained. The buffer amplifiers are provided to permit control of attack time and recovery time independent of each other. Partitioned as shown in the block diagram, the IC allows flexibility in the design of system levels that optimize DC shift, ripple distortion, tracking accuracy and noise floor for a wide range of application requirements.

#### **Gain Cell**

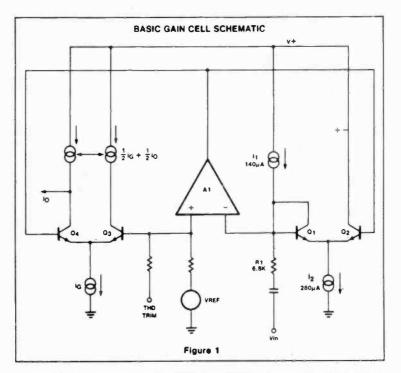

Figure 1 shows the circuit configuration of the gain cell. Bases of the differential pairs

Signetics

$Q_1 = Q_2$  and  $Q_3 = Q_4$  are both tied to the output and inputs of OPA A<sub>1</sub>. The negative feedback through  $Q_1$  holds the V<sub>BE</sub> of  $Q_1 = Q_2$  and the V<sub>BE</sub> of  $Q_3 = Q_4$  equal. The following relationship can be derived from the transistor model equation in the forward active region.

$$\begin{split} & \Delta V_{\mathsf{BE}}_{\mathsf{Q}_3-\mathsf{Q}_4} = \Delta_{\mathsf{BE}}_{\mathsf{Q}_1-\mathsf{Q}_2} \\ (\mathsf{V}_{\mathsf{BE}} = \mathsf{V}_\mathsf{T} \mathsf{I}_\mathsf{n} \mathsf{IC}/\mathsf{IS}) \\ & \mathsf{V}_\mathsf{T} \mathsf{I}_\mathsf{n} \left( \frac{\frac{1}{2} \mathsf{I}_\mathsf{G} + \frac{1}{2} \mathsf{I}_\mathsf{Q}}{\mathsf{I}_\mathsf{S}} \right) = \mathsf{V}_\mathsf{T} \mathsf{I}_\mathsf{n} \left( \frac{\frac{1}{2} \mathsf{I}_\mathsf{G} - \frac{1}{2} \mathsf{I}_\mathsf{Q}}{\mathsf{I}_\mathsf{S}} \right) \\ & = \mathsf{V}_\mathsf{T} \mathsf{I}_\mathsf{n} \left( \frac{\mathsf{I}_1 + \mathsf{Iin}}{\mathsf{I}_\mathsf{S}} \right) = \mathsf{V}_\mathsf{T} \mathsf{I}_\mathsf{n} \left( \frac{\mathsf{I}_2 - \mathsf{I}_1 - \mathsf{Iin}}{\mathsf{I}_\mathsf{S}} \right) \\ & \text{where IIn} = \frac{\mathsf{VIn}}{\mathsf{R}_1} \\ & \mathsf{R}_1 = 6.8\mathsf{K} \\ & \mathsf{I}_1 = \mathsf{I40}_\mathsf{M} \\ & \mathsf{I}_2 = \mathsf{280}_\mathsf{M} \mathsf{A} \end{split}$$

$I_{\mbox{O}}$  is the differential output current of the gain cell and  $J_{\mbox{G}}$  is the gain control current of the gain cell.

If all transistors  $Q_1$  through  $Q_4$  are of the same size, equation (2) can be simplified to:

$$I_0 = \frac{2}{I_2} \cdot lin \cdot I_G - \frac{1}{I_2} (I_2 - 2I_1) \cdot I_G$$

(3)

The first term of eqn. (3) shows the multiplier relationship of a linearized two quadrant transconductance amplifier. The second term is the gain control feed through due to the mismatch of devices. In the design this has been minimized by large matched devices and careful layout. Offset voltage is caused by the device mismatch and it leads to even harmonic distortion. The offset voltage can be trimmed out by feeding a current source within  $\pm 25\mu A$  into the THD trim pin. The residual distortion is third harmonic distortion and is caused by gain control ripple. In a compandor system, available control of fast attack and slow recovery improves ripple distortion significantly. At the unity gain level of 100mV, the gain cell gives THD (total harmonic distortion) of . 17% TYP. Output noise with no input signals is only 6µV in the audio spectrum (10HZ-20KHZ). The output current IO must feed the virtual ground input of an operational amplifier with a resistor from output to inverting input. The non-inverting input of the operational amplifier has to be biased at VREF If the output current IO is dc coupled.

#### Rectifier

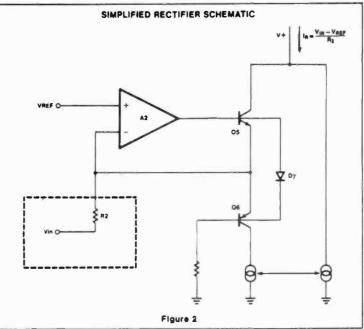

The rectifier is a full-wave design as shown in Figure 2. The input voltage is converted to current through the input resistor R2 and turns on either Q5 or Q6 depending on the signal polarity. Deadband of the voltage to current converter is reduced by the loop gain of the gain block A2. If AC coupling is used, the rectifier error comes only from input bias current of gain block A2. The input bias current is typically about 70nA. Frequency response of the gain block A2 also causes second order error at high frequency. The collector current of Q6 is mirrored and summed at the collector of Q5 to form the full wave rectified output current IR. The rectifier transfer function is

VIN-VREF

R<sub>2</sub> (4) If Vin is A.C. coupled, then the equation will be reduced to:

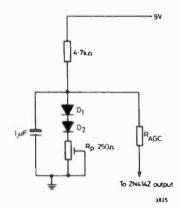

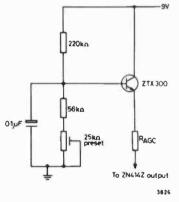

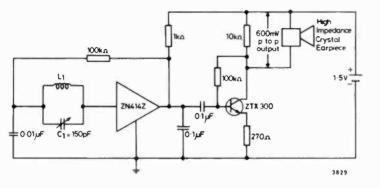

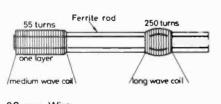

RAC = R2