| 1  | <b>Technical Specification</b>              |

|----|---------------------------------------------|

| 2  |                                             |

| 3  |                                             |

| 4  | ATLAS Level-1 Calorimeter Trigger Upgrade   |

| 5  |                                             |

| 6  | FEX System Switch Module (FEX Hub)          |

| 7  | Prototype                                   |

| 8  |                                             |

| 9  | Dan Edmunds, Yuri Ermoline, Brian Ferguson  |

| 10 | Wade Fisher, Philippe Laurens, Spencer Lee, |

| 11 | Pawel Plucinski                             |

| 12 |                                             |

| 13 | Draft for Review                            |

| 14 | Version: 1.1                                |

| 15 | 12 March 2018                               |

| 16 |                                             |

# Contents

| 18       | 1 Conventions                                                                 |    |

|----------|-------------------------------------------------------------------------------|----|

| 19       | 2 Related Documents                                                           | 9  |

| 20       | 3 Introduction                                                                | 11 |

| 21       | 3.1 L1Calo Overview                                                           | 11 |

| 22       | 3.1.1 Overview of the L1Calo System in Phase I (Run 3)                        | 11 |

| 23       | 3.1.2 Overview of the L1Calo System in Phase-II (Run 4)                       | 14 |

| 24       | 3.2 FEX-Hub Module Overview                                                   | 14 |

| 25       | 4 FEX-Hub Module Functionality                                                | 17 |

| 26       | 4.1 Support of the ROD Mezzanine Card                                         |    |

| 27       | 4.2 FEX and FEX-Hub Readout Data Distribution                                 |    |

| 28       | 4.3 TTC Clock and Data Stream Distribution                                    |    |

| 29       | 4.4 Ethernet Network Switch                                                   |    |

| 30       | 4.5 Slow Control                                                              |    |

| 31       | 4.6 Connections to the IPMB                                                   |    |

| 32       | 4.7 Power Supplies                                                            | 19 |

| 33       | 4.8 Extended Use Cases                                                        |    |

| 34       | 4.9 Commissioning and Diagnostic Facilities                                   |    |

| 35       | 4.10 Environment Monitoring                                                   |    |

| 36       | 4.11 ATCA Form Factor                                                         |    |

| 37       | 5 Interfaces to Other L1Calo Modules                                          |    |

| 38       | 5.1 TTC Clock and Data Stream Interfaces                                      |    |

| 39       | 5.2 High-Speed Readout Data Interfaces                                        |    |

| 40       | 5.3 Ethernet Network Interfaces                                               |    |

| 41       | 5.4 Hub Interfaces to FEX Modules                                             |    |

| 42       | 5.4.1 Interface with Hub-1                                                    |    |

| 43       | 5.4.2 Interface with Hub-2                                                    |    |

| 44       | 5.5 Hub Interface to the ROD Mezzanine                                        |    |

| 45       | 5.5.1 MGT Differential Inputs to ROD from Hub                                 |    |

| 46       | 5.5.2 MGT Differential Outputs from ROD to Hub                                |    |

| 47       | 5.5.3 Other signals between ROD and Hub                                       |    |

| 48       | 5.6 Hub Interfaces to Second Hub Modules                                      |    |

| 49<br>50 | 5.6.1 Base Interface                                                          |    |

| 50       | 5.6.2 Fabric Interface                                                        |    |

| 51       | 5.6.3 Hub-2 usage of the Fabric Interface connection to Hub-1                 |    |

| 52<br>52 | 5.6.4 Update Channel Interface                                                |    |

| 53<br>54 | 6 Hub Implementation Details                                                  |    |

| 54       | <ul><li>6.1 Physical Layout</li><li>6.2 Readout Signal Distribution</li></ul> |    |

| 55<br>56 | 6.3 Timing and Trigger Control Distribution                                   |    |

| 50<br>57 | 6.3.1 Clock Distribution                                                      |    |

| 58       | 6.3.2 Control Signal Distribution                                             |    |

| 59       | 6.4 Base Interface Switch                                                     |    |

| 59<br>60 | 6.5 Hub FPGA                                                                  |    |

| 61       | 6.6 The IPM Controller                                                        |    |

| 62       | 6.7 Power Supplies and Management                                             |    |

| 63       | 6.8 Thermal Management                                                        |    |

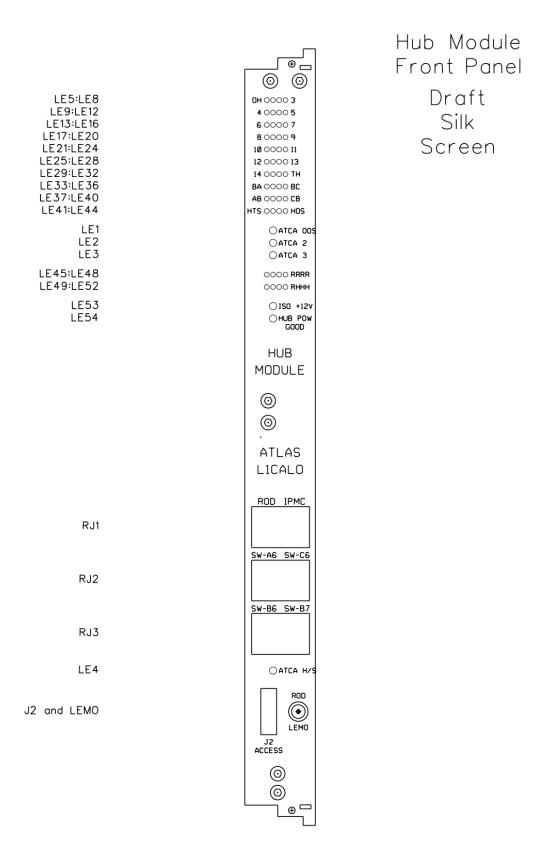

| 64       | 6.9 Front-Panel Layout                                                        |    |

| 65       | 6.9.1 Front Panel LEDs                                                        |    |

| 66       | 6.10 Rear Inputs and Outputs                                                  |    |

| $\sim$   | 0.10 11941 111941 4114 Output                                                 |    |

| 67                   | 6.10.1 ATCA Zone 1                                                                 |  |

|----------------------|------------------------------------------------------------------------------------|--|

| 68                   | 6.10.2 ATCA Zone 2                                                                 |  |

| 69                   | 6.10.3 ATCA Zone 3                                                                 |  |

| 70                   | 6.11 FEX-Hub PCB                                                                   |  |

| 71                   | 7 Programming Model                                                                |  |

| 72                   | 7.1 Guidelines                                                                     |  |

| 73                   | 7.2 Register Map & Controllable Functions                                          |  |

| 74                   | 8 Testing and Commissioning                                                        |  |

| 75                   | 8.1 Standalone and FEX System Tests                                                |  |

| 76                   | 8.2 Full Bandwidth Tests                                                           |  |

| 77<br><b>-</b> 0     | 9 FEX-Hub Prototype Tests                                                          |  |

| 78<br>70             | 9.1 Overview                                                                       |  |

| 79                   | 9.2 Power and Cooling Tests                                                        |  |

| 80                   | 9.2.1 Power Consumption                                                            |  |

| 81                   | 9.2.2 MGT Rail Power Supply Capacity                                               |  |

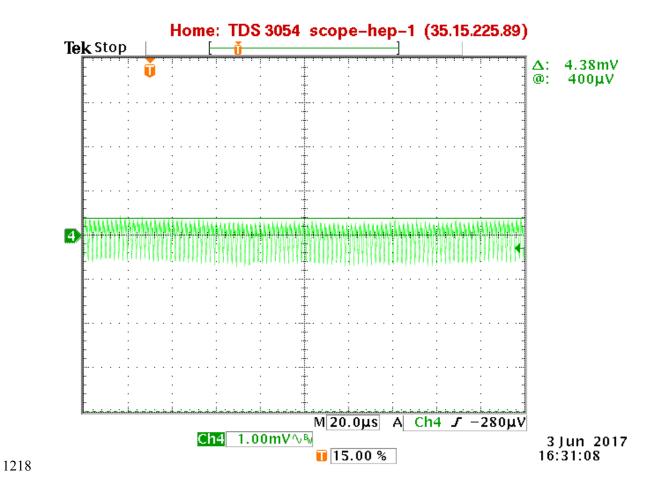

| 82                   | 9.2.3 MGT Rail Supply Noise                                                        |  |

| 83                   | 9.2.4 FPGA Silicon Temp                                                            |  |

| 84                   | 9.3 Clock Tests                                                                    |  |

| 85                   | 9.3.1 Clock Generation and Distribution                                            |  |

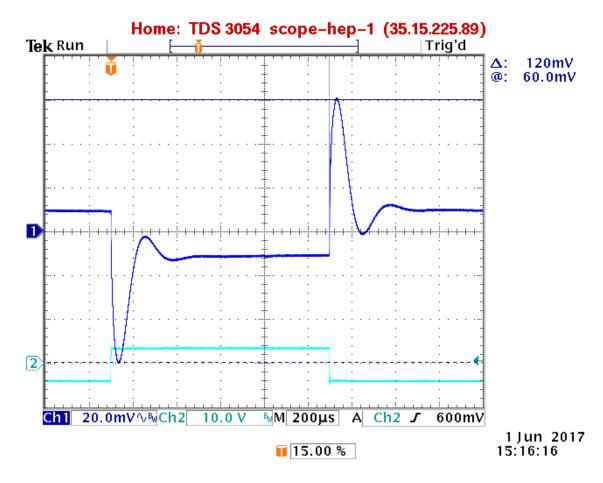

| 86                   | 9.3.2 Hub PLL Relock                                                               |  |

| 87                   | 9.4 High-Speed Link Tests                                                          |  |

| 88                   | 9.5 Gigabit Ethernet Tests                                                         |  |

| 89                   | 9.6 IPMC, Slow Control and Monitoring Tests                                        |  |

| 90                   | 9.7 Miscellaneous tests                                                            |  |

| 91                   | 9.8 Conclusions                                                                    |  |

| 92<br>93             | <ul><li>10 Planned Hub Module Production Yields</li><li>11 Special Notes</li></ul> |  |

| 93<br>94             | 12 Glossary                                                                        |  |

| 9 <del>4</del><br>95 | 13 Document Revision History                                                       |  |

| 95<br>96             | 14 Appendix 1: Backplane Connector/Pin Tables                                      |  |

| 90<br>97             | 14.1 Connector and Signal Usage for a HUB Slot                                     |  |

| 98                   | 14.1 Connector and Signal Usage for a FEX Slot                                     |  |

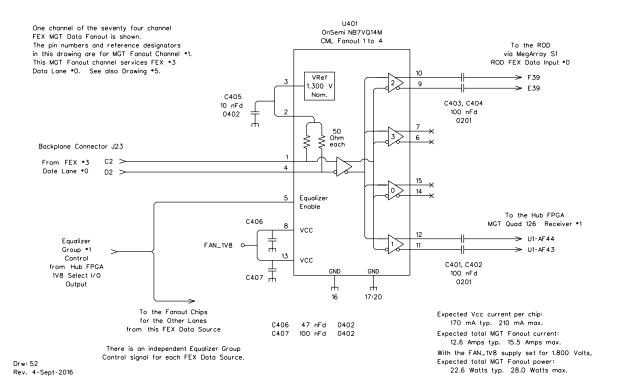

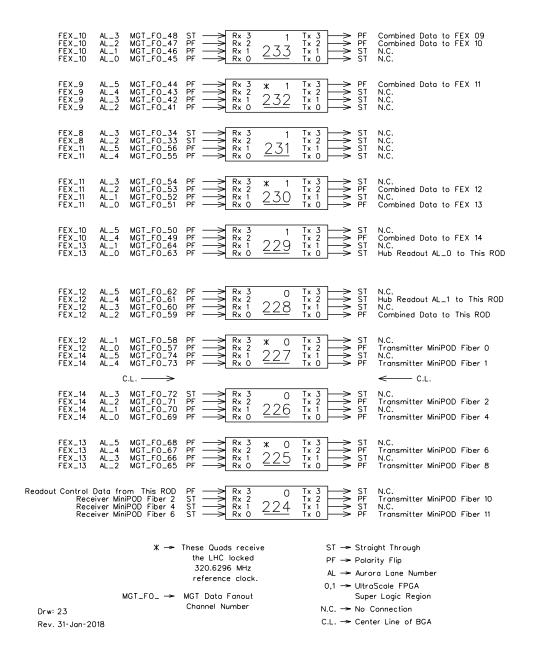

| 99                   | 15 Appendix 2: Hub Module FEX MGT Data Fanout                                      |  |

| 100                  | 15.1 AC Coupling                                                                   |  |

| 101                  | 15.1 AC Coupling                                                                   |  |

| 102                  | 15.3 Input Termination                                                             |  |

| 103                  | 15.4 Equalizer Enable                                                              |  |

| 104                  | 15.5 Reference Designators                                                         |  |

| 105                  | 15.6 Fanout Vcc Supply                                                             |  |

| 106                  | 15.7 Routing Challenges                                                            |  |

| 107                  | 15.8 Fanout Name                                                                   |  |

| 108                  | 15.9 Hub-Module FEX MGT Data Fanout Map                                            |  |

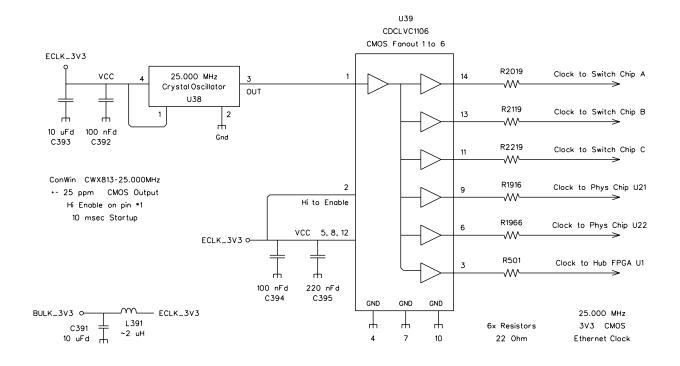

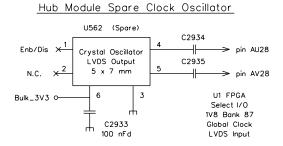

| 109                  | 16 Appendix 3: Hub-Module Clock Generation and Distribution                        |  |

| 110                  | 16.1 Ethernet 25.000 MHz Clock                                                     |  |

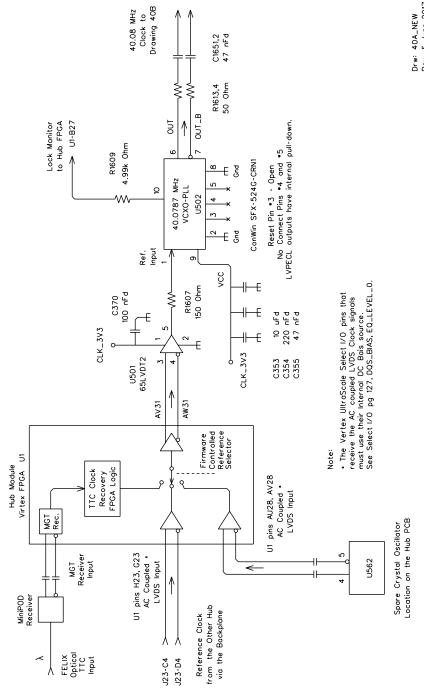

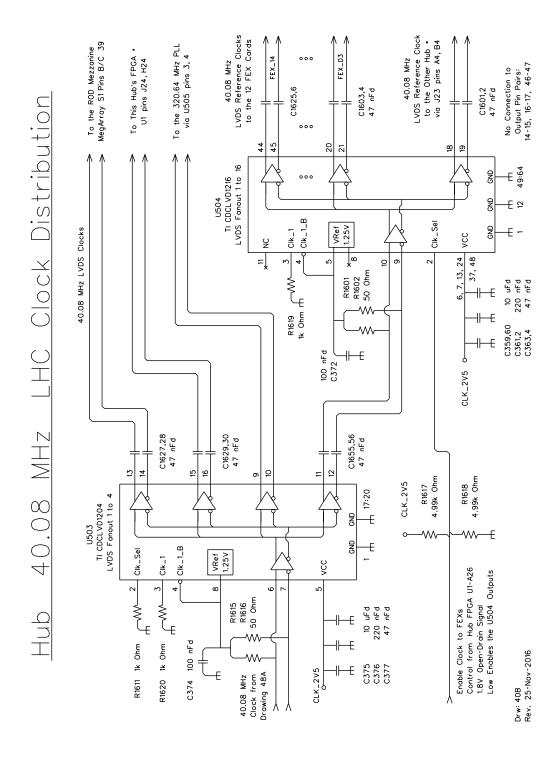

| 111                  | 16.2 40.08 MHz LHC Locked Clock                                                    |  |

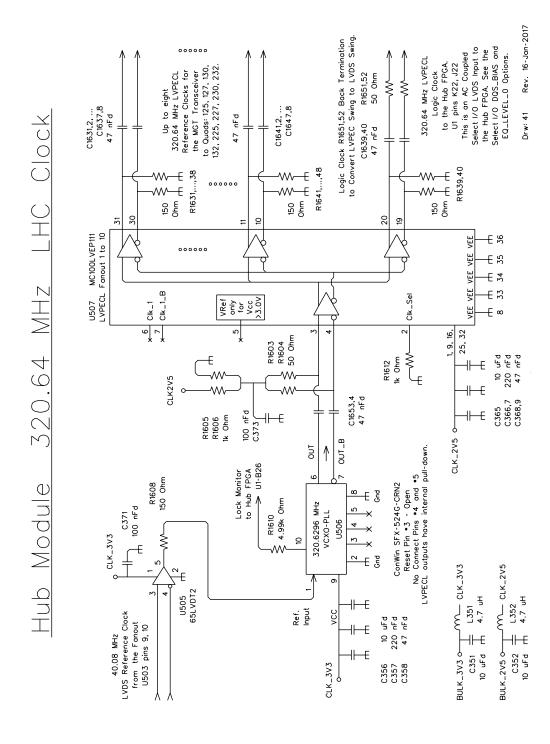

| 112                  | 16.3 320.64 MHz LHC Locked Clock for MGT Reference and FPGA Logic                  |  |

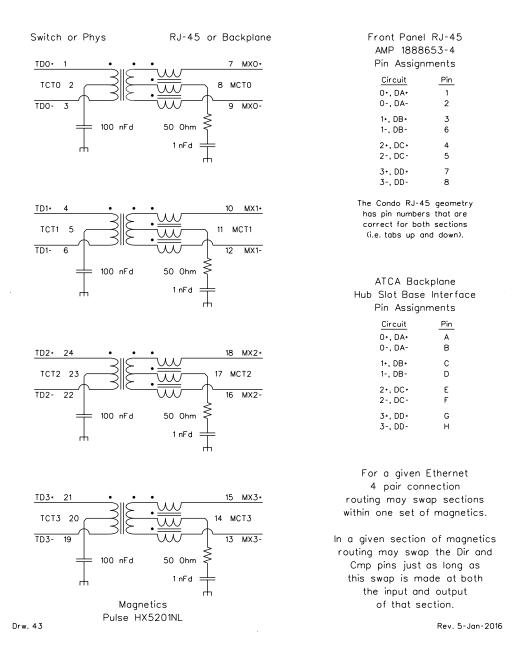

| 113                  | 17 Appendix 4: Hub-Module Ethernet Line Circuits                                   |  |

| 114                  | 17.1 Transformer Coupled Ethernet Line Circuits                                    |  |

| 115                  | 17.2 Phys Side Connections                                                         |  |

| 116                  | 17.3 Line Side Connections                                                         |  |

| 117                  | 17.4 Ethernet Magnetics Connection Summary                                         |  |

| 118 | 17.5 Front Panel RJ-45s                                     | 89  |

|-----|-------------------------------------------------------------|-----|

| 119 | 17.6 Capacitor Coupled Ethernet Line Circuits               | 89  |

| 120 | 17.7 Assignment of Ethernet "Magnetics"                     | 90  |

| 121 | 17.8 Assignment of Front Panel RJ-45 Connectors             | 91  |

| 122 | 17.9 Document / Verify the ROD's RJ45 Ethernet Connection   | 91  |

| 123 | 17.10 Document / Verify the IPMC's RJ45 Ethernet Connection | 92  |

| 124 | 18 Appendix 5: Hub Virtex FPGA MGT Transceiver Usage        |     |

| 125 | 19 Appendix 6: Hub Virtex FPGA Select I/O Usage             | 109 |

| 126 | 20 Appendix 7: Hub FPGA Signal Types                        |     |

| 127 | 20.1 Select I/O Signals:                                    | 115 |

| 128 | 20.1.1 Clock and Clock Management Signals                   | 115 |

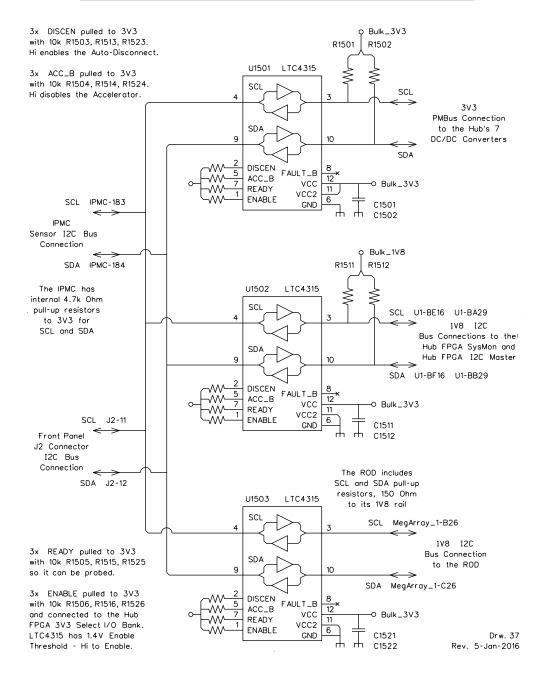

| 129 | 20.1.2 Ethernet Switch Chip Management Signals              | 116 |

| 130 | 20.1.3 Hardware Address Signals                             | 117 |

| 131 | 20.1.4 I2C Bus Signals                                      | 117 |

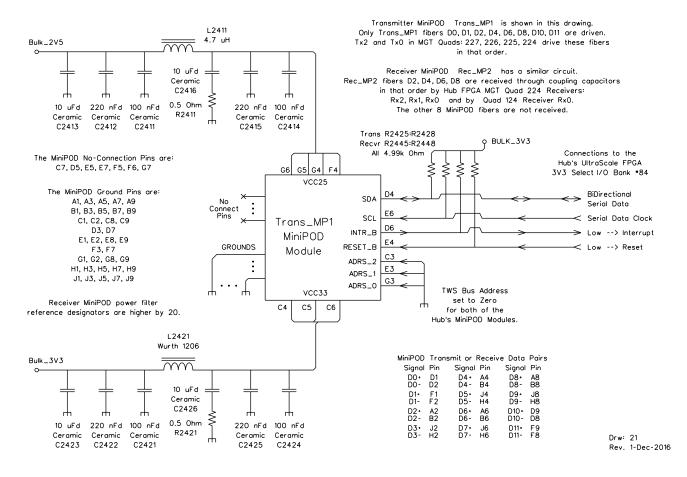

| 132 | 20.1.5 MiniPOD Management Signals                           |     |

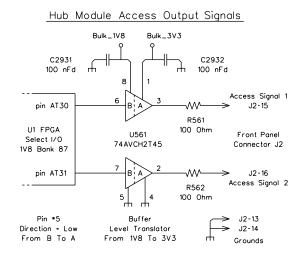

| 133 | 20.1.6 Miscellaneous Select I/O Signals                     |     |

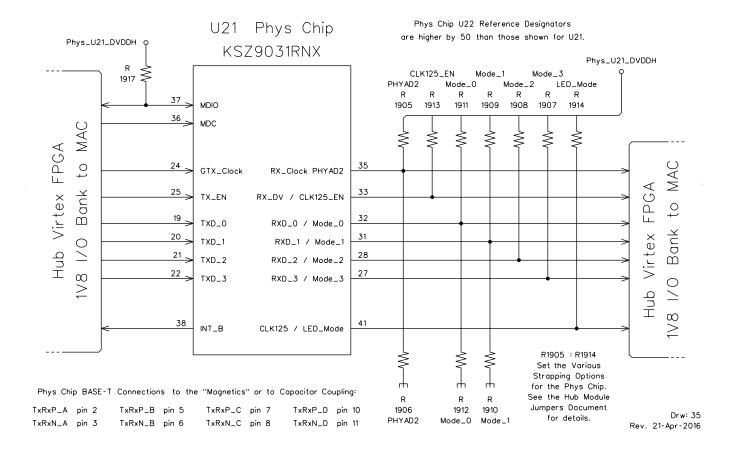

| 134 | 20.1.7 Phys U21 and Phys U22 signals                        |     |

| 135 | 20.1.8 ROD Present and ROD Power Control Signals            |     |

| 136 | 20.2 MGT Transceiver Signals                                |     |

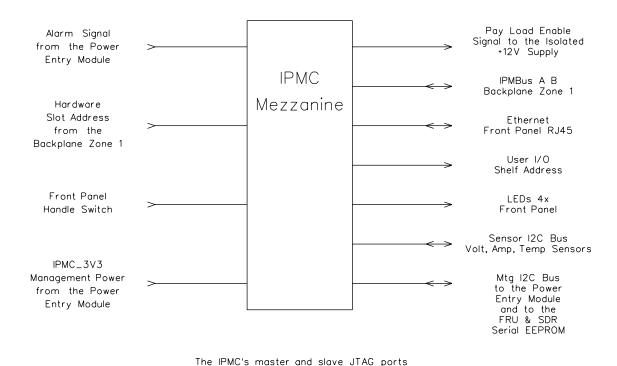

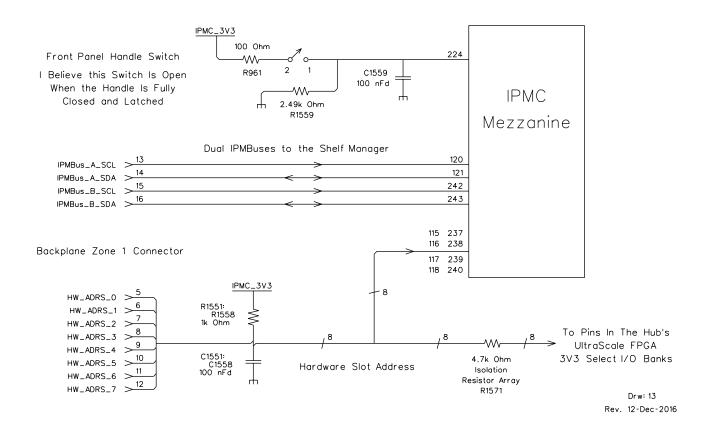

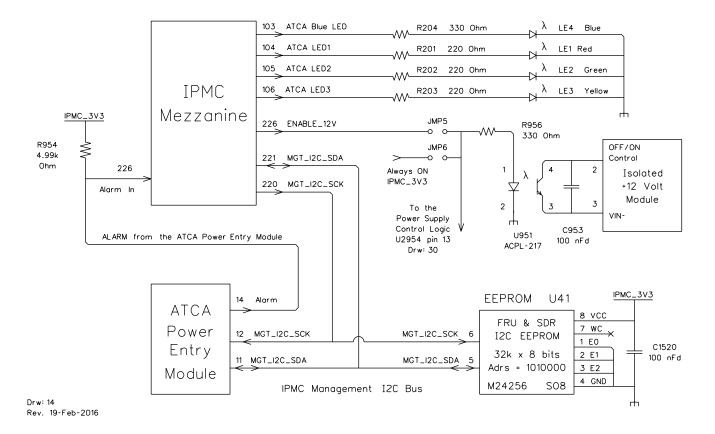

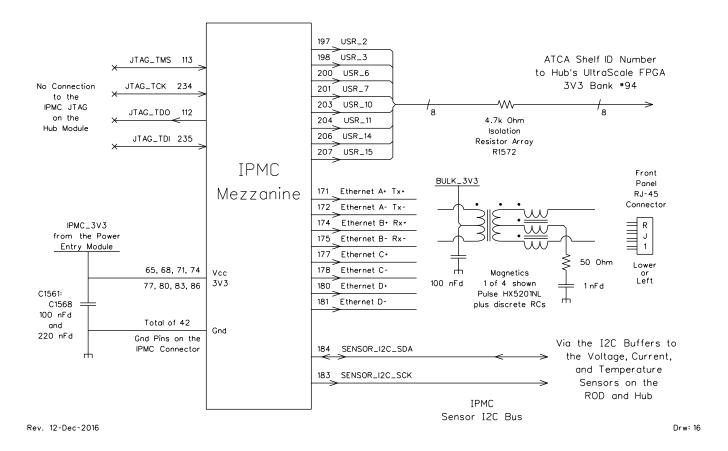

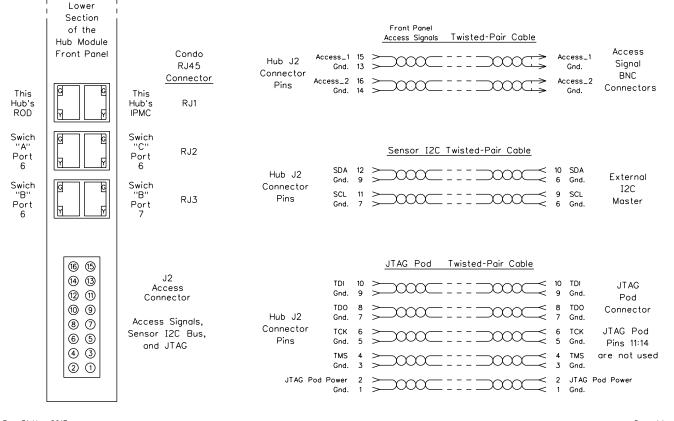

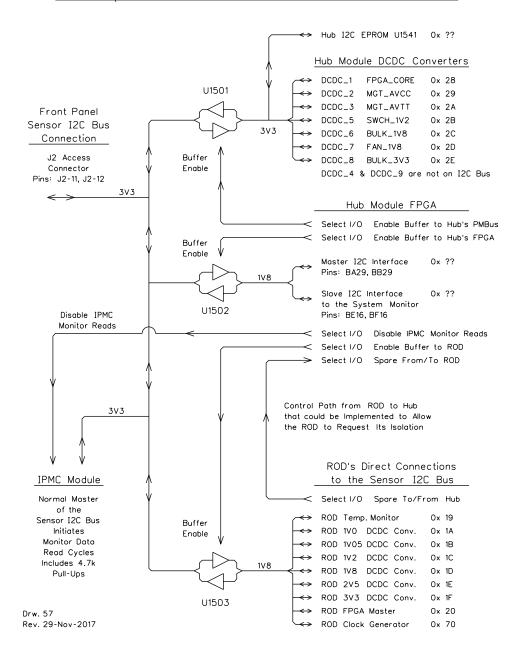

| 137 | 21 Appendix 8: Hub-Module IPMC Connections                  |     |

| 138 | 21.1 Connections Shown in Figure 33                         |     |

| 139 | 21.2 Connections Shown in Figure 34                         |     |

| 140 | 21.3 Connections Shown in Figure 35                         |     |

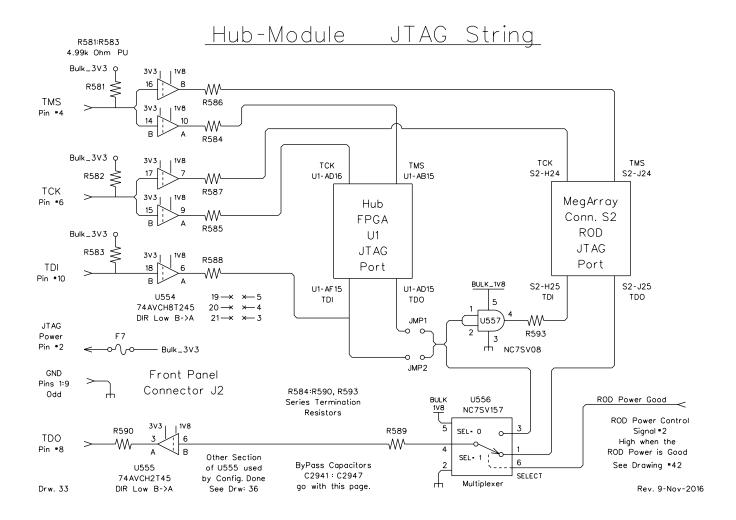

| 141 | 22 Appendix 9: Hub-Module JTAG String                       |     |

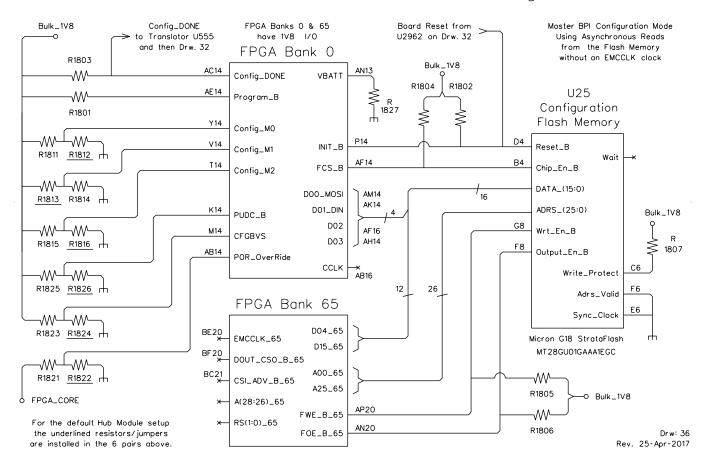

| 142 | 23 Appendix 10: Hub-Module Jumpers                          |     |

| 143 | 23.1 IPMC Ethernet A/Tx, B/Rx, Mag CT to 3V3, R1405 & R1410 |     |

| 144 | 23.2 Virtex FPGA Configuration Mode R1811 through R1816     |     |

| 145 | 23.3 Power On Reset Delay Override R1821 and R1822          |     |

| 146 | 23.4 Configuration Bank Voltage Select R1823 and R1824      |     |

| 147 | 23.5 Pull-Ups During Configuration R1825 and R1826          |     |

| 148 | 23.6 VBATT R1827                                            |     |

| 149 | 23.7 JTAG Skip the Hub FPGA JMP1 and JMP2                   |     |

| 150 | 23.8 DONE Included in ROD Power Control JMP3 and JMP4       |     |

| 151 | 23.9 Wait for IPMC Payload Enable Signal JMP5 and JMP6      |     |

| 152 | 23.10 Hub Phys Chip Jumpers R1901:R1914, R1951:R1964        |     |

| 153 | 23.11 DCDC Converter with LC Output Filter Feedback Jumpers |     |

| 154 | 23.12 ATCA "Shelf Ground" to "Logic Ground" Connection R959 |     |

| 155 | 23.13 Jumper on the Sensor I2C Bus EEPROM                   |     |

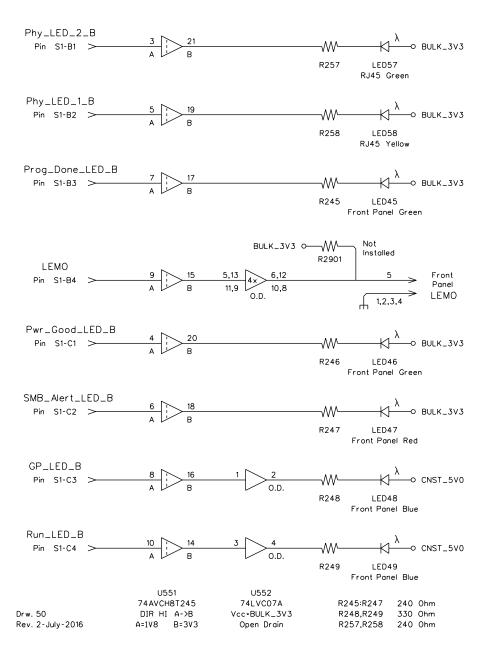

| 156 | 24 Appendix 11: Hub-Module Front Panel LEDs                 |     |

| 157 | 24.1 LEDs Driven by the IPMC Mezzanine                      |     |

| 158 | 24.2 LEDs Driven by the Switch Chips                        |     |

| 159 | 24.3 LEDs Driven by the Phys Chips on the Hub Module        |     |

| 160 | 24.4 LEDs Driven by the ROD Mezzanine Card                  |     |

| 161 | 24.5 LEDs Driven by the Hub Module's FPGA                   |     |

| 162 | 24.6 LEDs NOT Driven by the IPMC Card's Ethernet Connection |     |

| 163 | 24.7 Two Rationality LEDs                                   |     |

| 164 | 25 Appendix 12: Hub-Module MiniPOD Connections              |     |

| 165 | 26 Appendix 13: Non-MGT Rod-Hub Connections                 |     |

| 166 | 26.1 JTAG                                                   |     |

| 167 | 26.2 Sensor I2C Bus                                         |     |

| 168 | 26.3 ROD Front Panel Signals                                |     |

| 100 | 20.3 ROD Tituit i anci bighais                              | 133 |

| 169 | 26.4   | Clock 40.08 MHz                                            | 156 |

|-----|--------|------------------------------------------------------------|-----|

| 170 | 26.5   | Geographic Address                                         | 156 |

| 171 | 26.6   | Ethernet Connection                                        | 157 |

| 172 | 26.7   | Module Present                                             | 157 |

| 173 | 26.8   | ROD-Hub Power Control Signals                              | 157 |

| 174 | 26.9   | Spare Unused ROD-Hub HP IO Signals                         | 158 |

| 175 | 26.10  | Power from the Hub to the ROD                              |     |

| 176 | 26.11  | ROD-Hub MGT Signals                                        | 159 |

| 177 | 27 App | pendix 14: Phys Chip Usage on the Hub Module               | 161 |

| 178 | 27.1   | Power Supply, ByPass, Power Up, and Reset Requirements     | 161 |

| 179 | 27.2   | RGMII Interface Port                                       | 163 |

| 180 | 27.3   | MDC/MIIM/MDIO Interface Port                               |     |

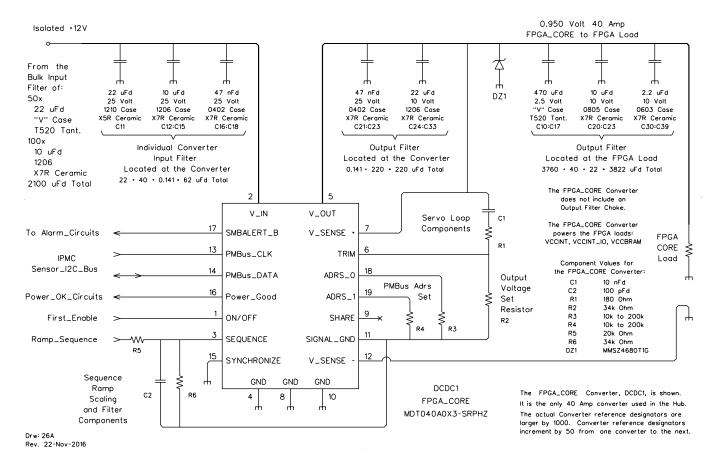

| 181 | 27.4   | Jumpers for the KSZ9031RNX (aka Strapping Pins)            | 163 |

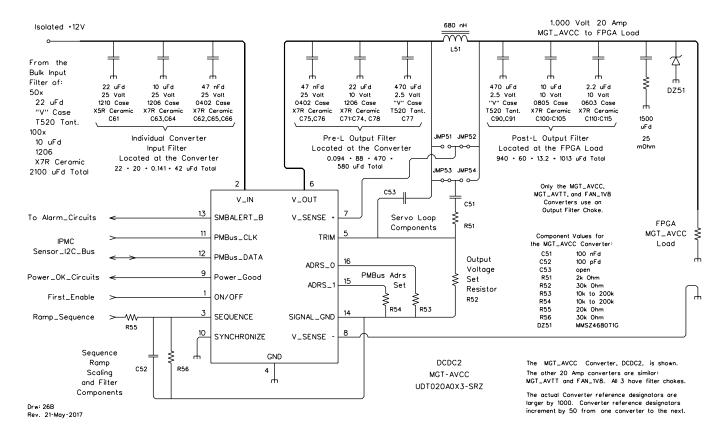

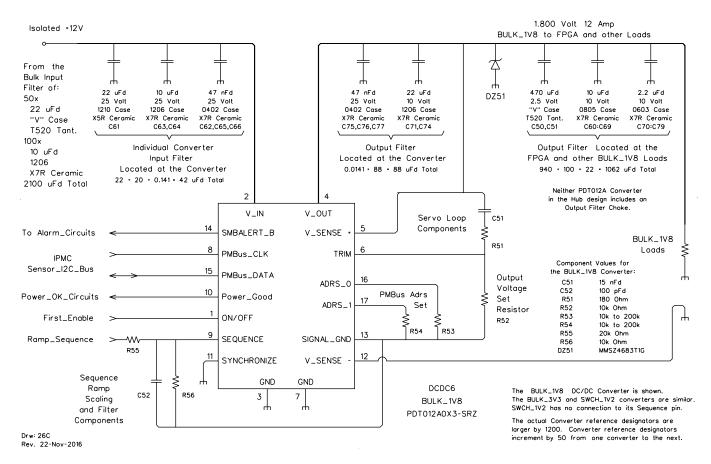

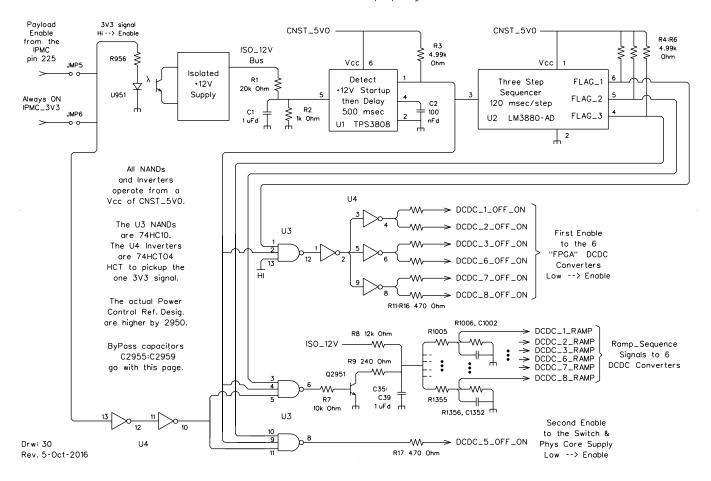

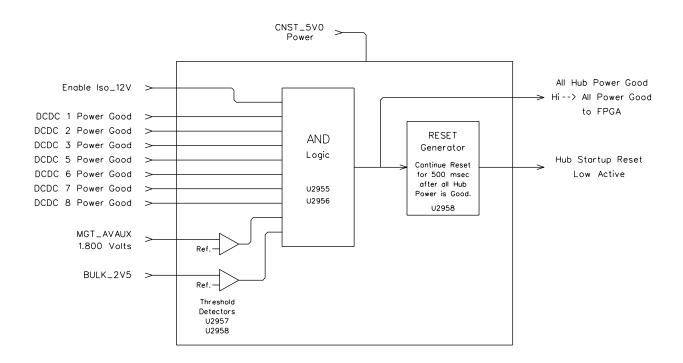

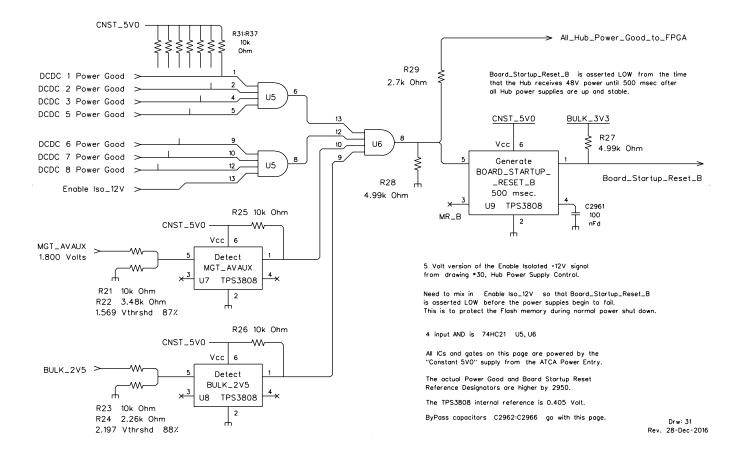

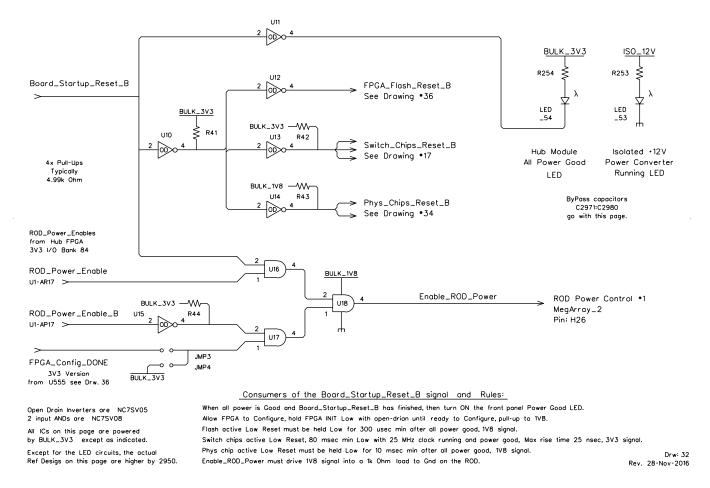

| 182 | 28 App | pendix 15: Hub-Module Power System                         | 167 |

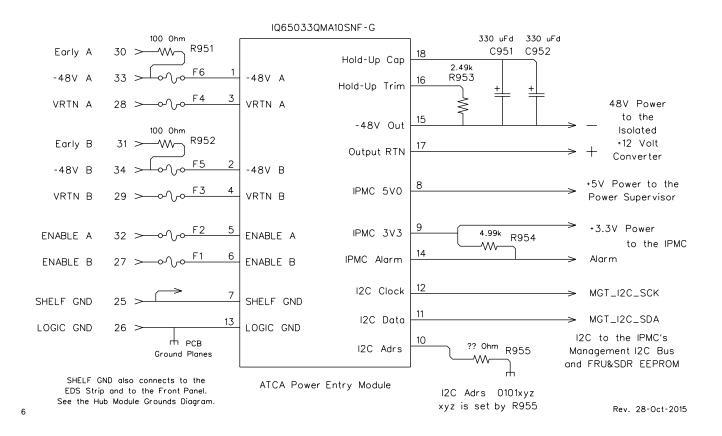

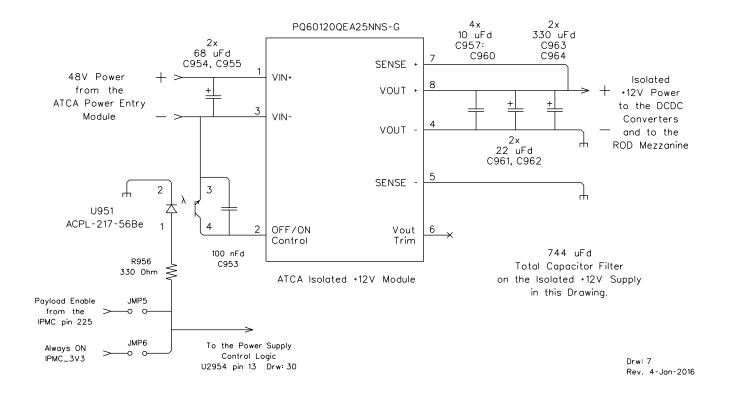

| 183 | 28.1   | ATCA Power Entry and Isolated +12V Supply                  | 167 |

| 184 | 28.2   | Hub Module Power Bus Table                                 | 168 |

| 185 | 28.3   | DCDC Converters                                            | 168 |

| 186 | 28.4   | DCDC Converter Input Filter Capacitors                     | 170 |

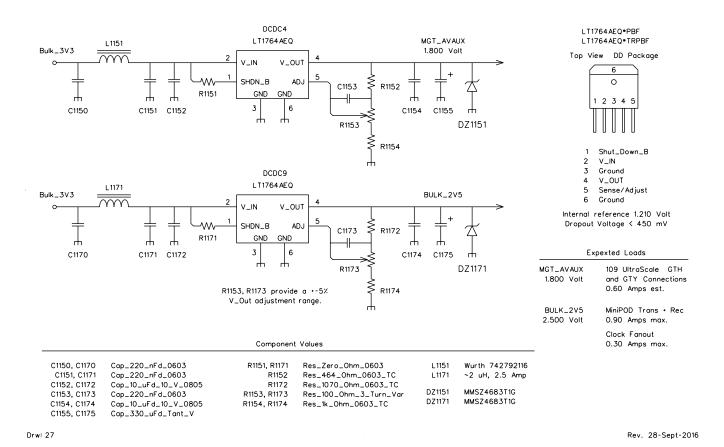

| 187 | 28.5   | DCDC Linear Supplies                                       | 170 |

| 188 | 28.6   | DCDC Converter Supervision                                 | 171 |

| 189 | 28.7   | DCDC Converters with an LC Output Filter                   | 172 |

| 190 | 28.8   | Power Requirements Information for each Section of the Hub | 173 |

| 191 | 28.9   | Final best Estimate on FPGA MGT Power from Xilinx Tools    | 175 |

| 192 | 29 App | pendix 16: Hub-Module Base Interface Ethernet Switch       | 193 |

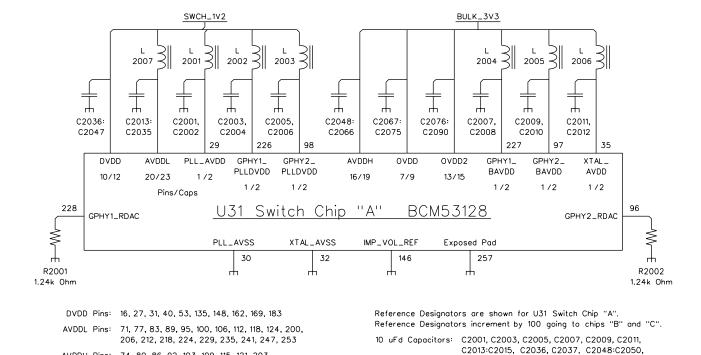

| 193 | 29.1   | Power Supply for the BCM53128 Switch Chip                  | 194 |

| 194 | 29.2   | Power-Up Supply Sequencing                                 | 196 |

| 195 | 29.3   | Hub Module Power Supply Design for Its Switch Chips        | 196 |

| 196 | 29.4   | Switch Chip Bypass Capacitors and Filter Chokes            | 197 |

| 197 | 29.5   | The BCM53128 Switch Capacitive Coupling                    |     |

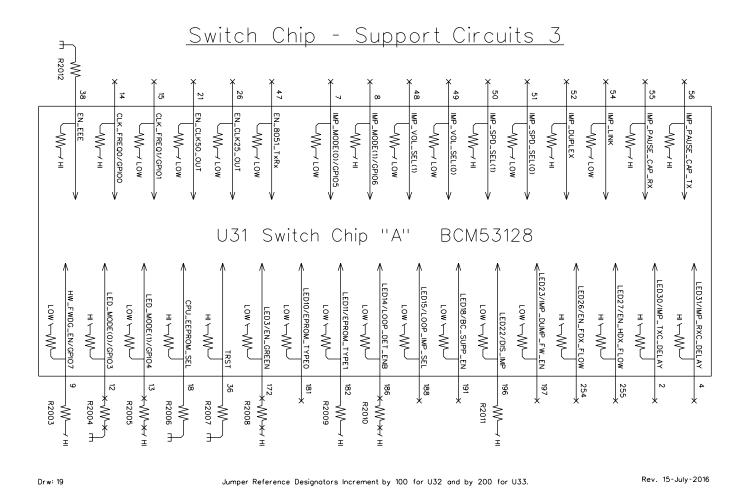

| 198 | 29.6   | Switch Chip Orientation and Port Connections               | 199 |

| 199 | 29.7   | Assignment of Ethernet "Magnetics"                         | 201 |

| 200 | 29.8   | Assignment of Front Panel RJ-45 Connectors                 | 201 |

| 201 | 29.9   | Resistor Set Pin                                           | 201 |

| 202 | 29.10  | Unused Tie Hi, Tie Low, Float Pins                         | 201 |

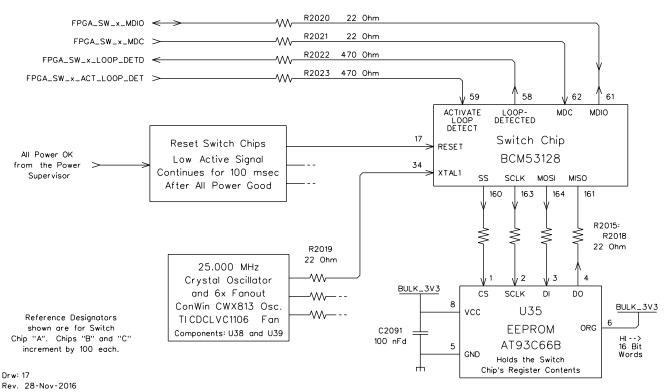

| 203 | 29.11  | EEPROM Connection to the Switch Chip                       | 202 |

| 204 | 29.12  | SPI Bus Connection                                         | 203 |

| 205 | 29.13  | MDC MDIO Connection to the Hub's Virtex FPGA               | 203 |

| 206 |        | Switch Chip Reset                                          |     |

| 207 | 29.15  | Clock to the Switch Chip                                   | 204 |

| 208 | 29.16  | Switch Chip Functions That Are Not Used on the Hub         | 204 |

| 209 | 29.17  | Switch Chip Bypass Capacitor and Filter Update             | 205 |

| 210 | 30 App | pendix 17: Switch Chip Associated Jumpers                  | 210 |

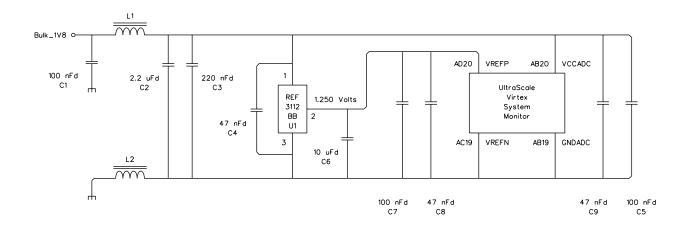

| 211 | 30.1   | Enumeration of All Strapping Options on the BCM53128       | 210 |

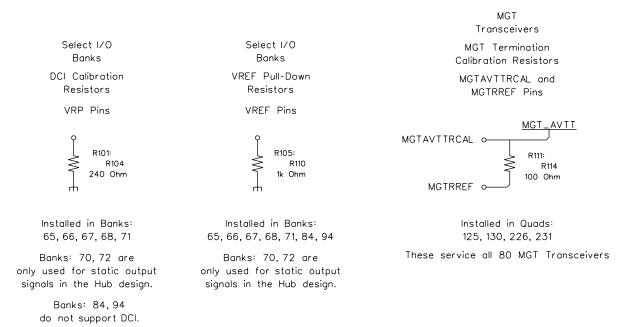

| 212 | 31 App | pendix 18: Hub-Module Xilinx FPGA                          | 212 |

| 213 | 31.1   | FPGA Configuration:                                        | 212 |

| 214 | 31.2   | FPGA JTAG Connection                                       |     |

| 215 | 31.3   | FPGA System Monitor Reference and Connections              | 212 |

| 216 | 31.4   | FPGA MGT Transceivers                                      |     |

| 217 | 31.5   | FPGA RGMII Ethernet Base Interface Connection              | 213 |

| 218 | 31.6   | FPGA Clock Sources                                         |     |

| 219 | 31.7   | The Select I/O Signals                                     | 213 |

| 220 | 31.8 | FPGA Power Supply Requirements                 | 213 |

|-----|------|------------------------------------------------|-----|

| 221 |      | opendix 19: Hub Commissioning Test Plan        |     |

| 222 | 32.1 | Power Supplies and Hub Component Cooling Tests | 218 |

| 223 | 32.2 | IPMC and Slow Control & Monitoring Bus Tests   | 219 |

| 224 |      | MGT Link Tests                                 |     |

| 225 | 32.4 | Clock Tests                                    | 220 |

| 226 | 32.5 | Ethernet Connection and Ethernet Switch Tests  | 220 |

| 227 | 32.6 | Miscellaneous Tests                            | 220 |

| 228 |      |                                                |     |

|     |      |                                                |     |

### 1 Conventions

230

240

241

242

243244

245

246

247

248

249

252

- The following conventions are used in this document:

- The term "Hub" or "FEX-Hub" is used to refer to the Phase-I L1Calo FEX system ATCA switch (hub) module in the rest of this document.

- The L1Calo FEX system Readout Driver (ROD) mezzanine is referred to as the "Hub-ROD" or just "ROD" in this document.

- FEX-Hub modules can be physically located in logical slots 1 or 2. The convention for the remainder of this document is to refer to these different modules as Hub-1 and Hub-2, respectively. Likewise the ROD modules in logical slots 1 or 2 are referred to as ROD-1 and ROD-2.

- The convention in this document will be that Hub-1 is the receiver of the TTC signal from the upstream FELIX system, and thus is responsible for distributing these signals to the FEX, ROD and Hub-2 recipients.

- A programmable parameter is defined as one that can be altered under computer control, for example between runs, not on an event-by-event basis. Changing such a parameter does not require a re-configuration of any firmware.

- Where multiple options are given for a link speed, for example, the readout links of the FEX modules are specified as running ≤6.4 Gb/s, this indicates that the link speed has not yet been fully defined. Once it is defined, that link will run at a single speed.

- In accordance with the ATCA convention, a crate of electronics is here referred to as a shelf.

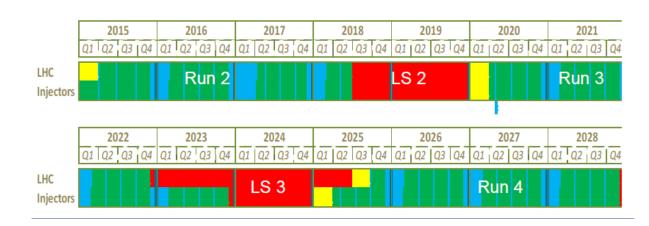

- Figure 1 explains the timeline for ATLAS running and shutdowns: Phase-I upgrades will be installed before the end of long shutdown LS 2; Phase-II upgrades will be installed before the end of LS 3.

- The term "buffer" is used to mean electrical reception and re-transmission of signals (possibly with fan-out), but without any storage or memory function. The terms "storage buffer", "FIFO", "Dual Port RAM" et al. are used where storage is involved.

Figure 1: LHC shutdown and run schedule.

| 262                      | 2     | Related Documents                                                                                                                                                                                                                                                                     |

|--------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 263<br>264<br>265        | [1.1] | ATLAS TDAQ System Phase-I Upgrade Technical Design Report, CERN-LHCC-2013-018, <a href="http://cds.cern.ch/record/1602235/files/ATLAS-TDR-023.pdf">http://cds.cern.ch/record/1602235/files/ATLAS-TDR-023.pdf</a>                                                                      |

| 266<br>267               | [1.2] | L1Calo Phase-I eFEX Specification, <a href="https://twiki.cern.ch/twiki/pub/Atlas/LevelOneCaloUpgradeModules/">https://twiki.cern.ch/twiki/pub/Atlas/LevelOneCaloUpgradeModules/</a>                                                                                                  |

| 268<br>269               | [1.3] | L1Calo Phase-I jFEX Specification, <a href="https://twiki.cern.ch/twiki/pub/Atlas/LevelOneCaloUpgradeModules/">https://twiki.cern.ch/twiki/pub/Atlas/LevelOneCaloUpgradeModules/</a>                                                                                                  |

| 270<br>271               | [1.4] | L1Calo gFEX Specification,<br>https://twiki.cern.ch/twiki/pub/Atlas/LevelOneCaloUpgradeModules/                                                                                                                                                                                       |

| 272<br>273               | [1.5] | L1Calo Phase-1 ROD Specification , <a href="https://twiki.cern.ch/twiki/pub/Atlas/LevelOneCaloUpgradeModules/">https://twiki.cern.ch/twiki/pub/Atlas/LevelOneCaloUpgradeModules/</a>                                                                                                  |

| 274<br>275               | [1.6] | L1Calo Phase-I Optical plant Specification, <a href="https://twiki.cern.ch/twiki/pub/Atlas/LevelOneCaloUpgradeModules/">https://twiki.cern.ch/twiki/pub/Atlas/LevelOneCaloUpgradeModules/</a>                                                                                         |

| 276<br>277               | [1.7] | ATCA Short Form Specification, <a href="http://www.picmg.org/pdf/picmg_3_0_shortform.pdf">http://www.picmg.org/pdf/picmg_3_0_shortform.pdf</a>                                                                                                                                        |

| 278<br>279               | [1.8] | PICMG 3.0 Revision 3.0 AdvancedTCA Base Specification, <i>access controlled</i> , <a href="http://www.picmg.com/">http://www.picmg.com/</a>                                                                                                                                           |

| 280<br>281<br>282        | [1.9] | P. Moreira, A. Marchioro, and K. Kloukinas, The GBT, a Proposed Architecture for Multi-Gb/s Data Transmission in High Energy Physics, 2007. <a href="https://espace.cern.ch/GBT-Project/Papers/paperMoreiraGBT.doc">https://espace.cern.ch/GBT-Project/Papers/paperMoreiraGBT.doc</a> |

| 283<br>284<br>285        | [1.10 | Development of an ATCA IPMI controller mezzanine board to be used in the ATCA developments for the ATLAS Liquid Argon upgrade, <a href="http://cds.cern.ch/record/1395495/files/ATL-LARG-PROC-2011-008.pdf">http://cds.cern.ch/record/1395495/files/ATL-LARG-PROC-2011-008.pdf</a>    |

| 286<br>287               | [1.11 | ] IPbus Protocol,<br>https://svnweb.cern.ch/trac/cactus/export/trunk/doc/ipbus_protocol_v2_0.pdf                                                                                                                                                                                      |

| 288<br>289               | [1.12 | P] Front-End Link Exchange (Felix),<br>https://edms.cern.ch/document/13111772/1                                                                                                                                                                                                       |

| 290<br>291<br>292<br>293 | [1.13 | MEG-Array Connectors, <a href="https://cdn.amphenol-icc.com/media/wysiwyg/files/documentation/datasheet/boardwiretoboard/bwb_megarray_mezzanine.pdf">https://cdn.amphenol-icc.com/media/wysiwyg/files/documentation/datasheet/boardwiretoboard/bwb_megarray_mezzanine.pdf</a>         |

| 294<br>295               | [1.14 | ATLAS L1Calo System-Level Specifications,<br>https://edms.cern.ch/document/1492098/1                                                                                                                                                                                                  |

| 296<br>297<br>298 | [1.15] Spencer Lee, Hub Gigabit Ethernet test description,  https://web.pa.msu.edu/hep/atlas/l1calo/hub/specification/2_final_design_review/Fub_GbE_Test_Report_v0_1.pdf  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 299<br>300        | [1.16] Hub firmware specification, <pre>https://web.pa.msu.edu/hep/atlas/l1calo/hub/specification/2_final_design_review/F</pre> <pre>LIP_FW_Spec_FDP_02_12_2018_pdf</pre> |

| 301               | UB_FW_Spec_FDR_03_12_2018.pdf                                                                                                                                             |

### 3 Introduction

302

- This document describes the ATCA switch module (FEX-Hub) of the ATLAS Level-1

- Calorimeter Trigger Processor (L1Calo) system [1.1]. The FEX-Hub is one of several

- modules being designed to upgrade L1Calo, providing the increased discriminatory

- 306 power necessary to maintain trigger efficiency as the LHC luminosity is increased

- beyond that for which ATLAS was originally designed.

- The function of the FEX-Hub module is to provide common communications functions

- for the FEX ATCA shelves including the routing of FEX readout data, network

- communications to and from FEX modules and distribution of clock and control signals.

- The FEX-Hub modules will be installed in L1Calo during the long shutdown LS2, as part

- of the Phase-1 upgrade, and will operate during Run 3. They will remain in the system

- after the Phase-2 upgrade in LS3, and will operate during Run 4, at which time they will

- form part of L0Calo. The following sections provide overviews of L1Calo in Run 3 and

- 315 L0Calo in Run 4.

- This is a specification for the production FEX-Hub module. This final version will

- deliver the required functionality for the L1Calo FEX system. This specification further

- describes possible use cases not critical to the core Hub functionality that represent

- fallback options for the L1Calo (L0Calo) readout system if needed.

- This document is arranged as follows. The front portion of the document introduces the

- L1Calo system, the plans for its upgrade and the upgrade evolutions. Next, a descriptive

- overview of the FEX-Hub module is provided, describing the primary specifications for

- its functionality within the L1Calo trigger system, including system interfaces and the

- implementation of the FEX-Hub itself. Finally, there are two appendices that enter into

- 325 the details of how the FEX-Hub module has been designed and built, which provide an

- official reference on the "as built" FEX-Hub specification.

### 3.1 L1Calo Overview

## 328 3.1.1 Overview of the L1Calo System in Phase I (Run 3)

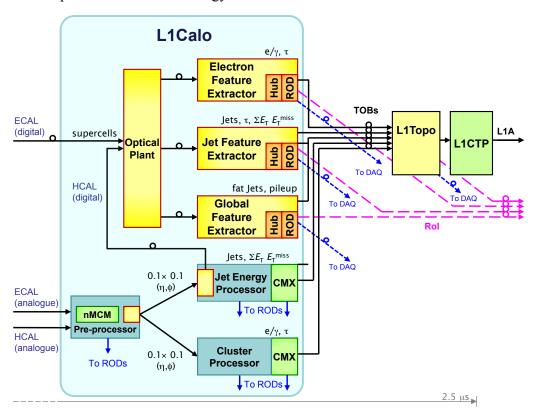

- In Run 3, L1Calo contains three subsystems installed prior to LS2, as shown in Figure 2

- 330 (see document [1.1]):

- The Pre-processor, which receives shaped analog pulses from the ATLAS

- calorimeters, digitises and synchronises them, identifies the bunch-crossing from

- which each pulse originated, scales the digital values to yield transverse energy  $(E_{\rm T})$ ,

- and prepares and transmits the data to the following processor stages:

• The Cluster Processor (CP) subsystem (comprising Cluster Processing Modules (CPMs) and Common Merger Extended Modules (CMXs)) which identifies isolated e/γ and τ candidates;

• The Jet/Energy Processor (JEP) subsystem (comprising Jet-Energy Modules (JEMs) and Common Merger Extended Modules (CMXs)) which identifies energetic jets and computes various local energy sums.

**Figure 2**: The L1Calo system in Run 3. *Components installed during LS2 are shown in yellow/orange*

- Additionally, L1Calo contains the following three subsystems installed as part of the Phase-I upgrade in LS2:

- The electromagnetic Feature Extractor eFEX subsystem, comprising eFEX modules and FEX-Hub modules, the latter carrying Readout Driver (ROD) daughter cards. The eFEX subsystem identifies isolated  $e/\gamma$  and  $\tau$  candidates, using data of finer granularity than is available to the CP subsystem.

- The jet Feature Extractor (jFEX) subsystem, comprising jFEX modules, and Hub modules with ROD daughter cards. The jFEX subsystem identifies energetic jets and computes various local energy sums, using data of finer granularity than that available to the JEP subsystem.

- The global Feature Extractor (gFEX) subsystem, which is a single, stand-alone module. The gFEX subsystem identifies calorimeter trigger features requiring the complete calorimeter data.

• An updated Level-1 Topological Processing subsystem (L1Topo), comprising L1Topo modules, and Hub modules with ROD daughter cards. The L1Topo subsystem applies topological selection and threshold criteria on trigger objects derived from the calorimeter and muon detector systems.

360361

357

358

- In Run 3, the Liquid Argon Calorimeter provides L1Calo both with analog signals (for

- the CP and JEP subsystems) and with digitized data (for the FEX subsystems). From the

- hadronic calorimeters, only analog signals are received. These are digitized on the Pre-

- processor, transmitted electrically to the JEP, and then transmitted optically to the FEX

- subsystems. Initially at least, the eFEX and jFEX subsystems will operate in parallel with

- 367 the CP and JEP subsystems. Once the performance of the FEX subsystems has been

- validated, the CP sub system will be removed, and the JEP used only to provide hadronic

- data to the FEX subsystems.

- The optical signals from the JEP and LDPS electronics are sent to the FEX subsystems

- via an optical plant. This performs two functions. First, it separates and reforms the fibre

- bundles, changing the mapping from that employed by the LDPS and JEP electronics to

- that required by the FEX subsystems. Second, it provides any additional fan-out of the

- signals necessary to map them into the FEX modules where this cannot be provided by

- 375 the calorimeter electronics.

- The outputs of the FEX subsystems (plus CP and JEP) comprise Trigger Objects (TOBs):

- data structures which describe the location and characteristics of candidate trigger

- objects. The TOBs are transmitted optically to the Level-1 Topological Processor

- (L1Topo), which merges them over the system and executes topological algorithms, the

- results of which are transmitted to the Level-1 Central Trigger Processor (CTP).

- The eFEX, jFEX, gFEX and L1Topo subsystems comply with the ATCA standard. The

- 382 eFEX subsystem comprises two shelves each of 12 eFEX modules. The jFEX subsystem

- comprises a single ATCA shelf holding 6 jFEX modules. The gFEX subsystem

- comprises a single ATCA shelf holding a single gFEX module. The L1Topo subsystem

- comprises a single ATCA shelf housing up to four L1Topo modules, each of which

- receives a copy of all data from all FEX modules. All L1Calo processing modules

- produce Region of Interest (RoI) and DAQ readout on receipt of a Level-1 Accept signal

- from the CTP. RoI information is sent both to the High-Level Trigger (HLT) and the

- DAO system, while the DAO data goes only to the DAO system. In the FEX and L1Topo

- subsystems, these data are transmitted by each FEX or L1Topo module via the shelf

- backplane to two Hub modules (with the exception of the gFEX, which requires no

- Hub/ROD). Each of these buffers the data and passes a copy to their ROD daughter

- board. The RODs perform the processing needed to select and transmit the RoI and DAQ

- data in the appropriate formats; it is likely that the required tasks will be partitioned

between the two RODs. Additionally, the Hub modules provide distribution and switching of the TTC signals and control and monitoring networks.

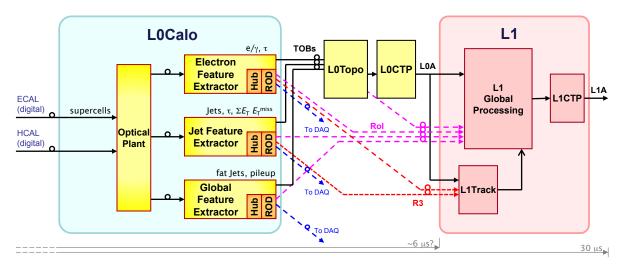

## 3.1.2 Overview of the L1Calo System in Phase-II (Run 4)

The Phase-II upgrade will be installed in ATLAS during LS3. At this point, substantial changes will be made to the trigger electronics. All calorimeter input to L1Calo from the electromagnetic and hadronic calorimeters will migrate to digital format, the structure of the hardware trigger will change to consist of two levels, and a Level-1 Track Trigger (L1Track) will be introduced and will require TOB seeding. The Pre-processor, CP and JEP subsystems will be removed, and the FEX subsystems, with modified firmware, will be relabelled to form the L0Calo system in a two stage (Level-0/Level-1) real-time trigger, as shown in Figure 3. Hence, the FEX subsystems must be designed to meet both the Phase-I and Phase-II upgrade requirements. The main additional requirements are to provide real-time TOB data to L1Track, and to accept Phase-II timing and control signals including Level-0 Accept (L0A) and Level-1 Accept. Additional calorimeter trigger processing will be provided by a new L1Calo trigger stage.

**Figure 3**: The L0/L1Calo system in Run 4. *The new Level-1 system is shown in red and pink. Other modules (yellow /orange) are adapted from the previous system to form the new L0Calo.*

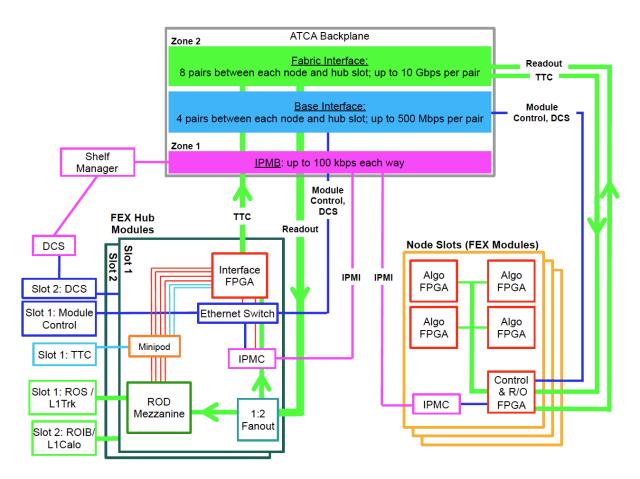

## 3.2 FEX-Hub Module Overview

The FEX-Hub module is an integral part of the L1Calo system. Its primary functions are to support FEX system readout, provide switching functionality for module control and DCS IPbus networks and to distribute timing and control signals to the FEX modules. **Figure 4** shows a sketch of the Hub modules within the FEX ATCA shelves. There are to be two Hub modules per shelf. Both Hub modules will receive multi-gigabit FEX data over the ATCA Fabric Interface, which will be fanned out to a ROD mezzanine on the

- Hub and to the Hub's own FPGA. This high-speed data path will include two data

- channels from the other Hub module. The Hub module in logical slot 1 will provide

- switching capability for a network that routes module control signals on the base

- interface, while the Hub in logical slot 2 will provide switching for a network that routes

- DCS information. The Hub module in slot 1 will further receive TTC information from

- 425 the FELIX system, and these signals will be decoded and fanned out to the FEX modules,

- 426 ROD modules and also to the Hub in slot 2. The fanned-out TTC control data stream will

- be interleaved with ROD-to-FEX communications including, for example, back-pressure

- 428 signals.

- The Hub module has connections to the other slots in the ATCA shelf over three distinct

- electrical interfaces, as illustrated in **Figure 4**. ATCA backplane Zone-2 consists of the

- Fabric Interface and the Base Interface. The Fabric Interface provides 8 differential pairs

- (channels) from each node slot to each Hub slot (8 to Hub-1 and 8 to Hub-2). There are a

- 433 total of 8 Fabric Interface channels between Hub-1 and Hub-2 (not 16 total). The Fabric

- Interface pairs have a nominal bandwidth specification of 10 Gbps / channel. The Base

- Interface provides 4 differential pairs between each node slot and each Hub slot. There

- are a total of 4 Base Interface channels between Hub-1 and Hub-2. The Base Interface

- lines have a nominal bandwidth specification of 500 Mbps / channel, suitable for Gbps

- Ethernet protocol. Finally, ATCA backplane Zone-1 provides each node and Hub slot

- with a connection to the Intelligent Platform Management Bus (IPMB) with a total

- bandwidth of 100 kbps. The Hub module will provide MPO connectors in the ATCA

- Zone-3 region, which will allow for the routing of fiber-optic cables to/from the

- 442 MiniPODs on the Hub and ROD modules.

- The L1Calo FEX-Hub system will consist of eight modules. There will be two eFEX

- shelves, one jFEX shelf and one L1Topo shelf, each hosting two Hub modules.

**Figure 4:** Illustration of the functions of FEX-Hub modules within the FEX trigger system, emphasizing the data paths through the ATCA backplane.

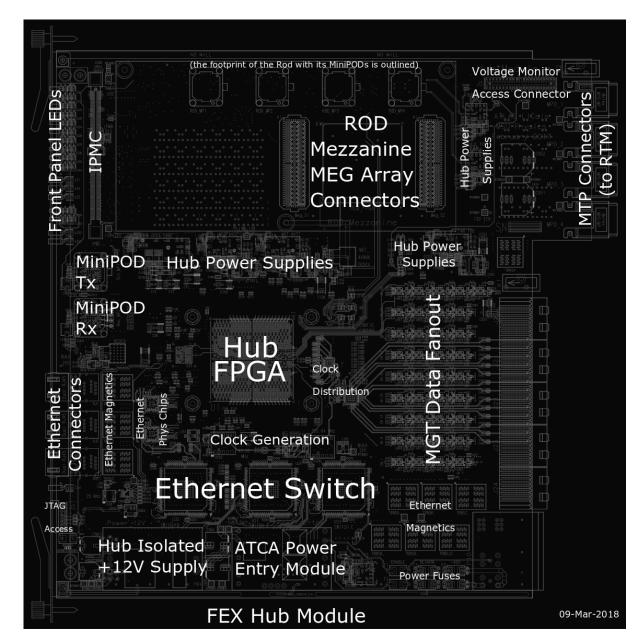

# 449 4 FEX-Hub Module Functionality

- 450 This section describes the functionality required for the FEX-Hub module within the

- L1Calo FEX trigger system. Details of the implementation of these functions will be

- described in Section 6 of this document. Figure 5 illustrates the overall layout of the Hub

- 453 module, including the outline of the ROD mezzanine card. In this figure, all of the

- primary functions and features of the Hub module are annotated for reference.

# 4.1 Support of the ROD Mezzanine Card

- 456 The FEX-Hub physically holds the ROD Mezzanine Card and provides electrical

- connections to it through two 400 pin MEG-Array connectors [1.13].

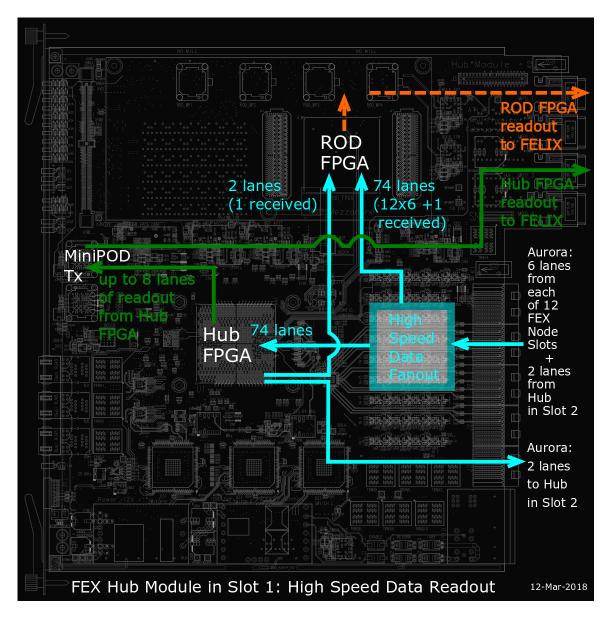

### 4.2 FEX and FEX-Hub Readout Data Distribution

- 459 The FEX-Hub receives over the Fabric Interface 6 serial streams of Readout Data from

- 460 each FEX Module. Each FEX-Hub also receives over the Fabric Interface 2 serial

- streams of Readout Data from the other FEX-Hub in the ATCA shelf. These 74 high-

- speed serial streams pass through a 1:2 fan-out on the FEX-Hub. One copy of each

- stream is sent to the ROD mezzanine and one copy is sent to the Hub's own FPGA. The

- Hub FPGA also sends 2 serial streams with its own Readout Data to its own ROD. Each

- ROD thus receives a total of 76 high speed Readout Data streams: 6 streams from each

- 466 FEX, 2 streams from the local Hub FPGA and 2 streams from the other Hub's Hub

- FPGA. The data rate per readout stream will be 10 Gbps or less.

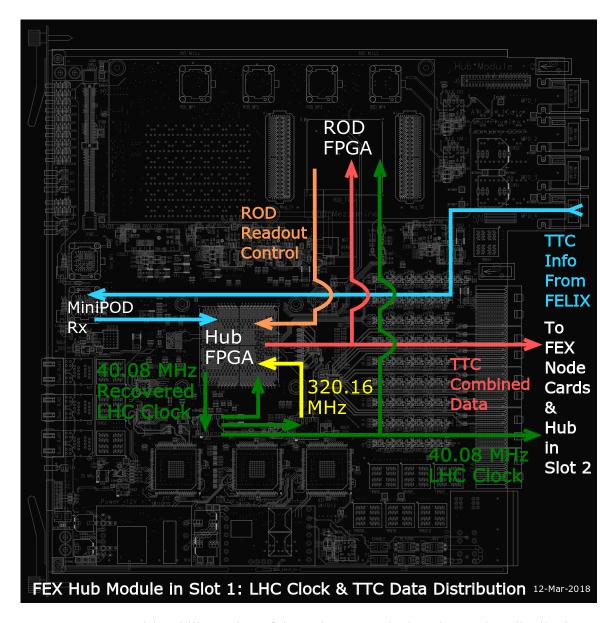

#### 4.3 TTC Clock and Data Stream Distribution

- The FEX-Hub in Slot 1 uses a 12-channel MiniPOD optical receiver to receive TTC

- signals from the upstream FELIX system. The FEX-Hub receives two types of TTC

- signals: a copy of the LHC clock and TTC control data. These signals are fanned out to

- each FEX module, to the local ROD, to the local Hub FPGA and to the FEX-Hub in Slot

- 2 (including its ROD). The LHC clock is directly forwarded without any processing on

- 474 the FEX-Hub. The TTC control data will be merged with additional control information

- coming from the ROD module from each FEX-Hub before being fanned out. The FEX-

- Hub uses two ports from the Fabric Interface Channel to each Node Slot to fan out these

- 477 two signals to each FEX. These two TTC and control signals sent to the FEX plus the 6

- 478 Readout Data streams received from each FEX use all 8 signals pairs of each Fabric

- Channel connecting one FEX to the FEX-Hub, albeit with an unconventional port

- 480 direction usage.

455

458

- The FEX-Hub in Slot 2 does receive the TTC information from FELIX directly, but

- 482 receives the TTC Clock and the TTC/ROD readout control stream from the FEX-Hub in

Slot 1. The FEX-Hub in Slot 2 sends any required ROD readout control data generated

by its own ROD to the FEX-Hub in Slot 1 for inclusion in the combined TCC/ROD

485 readout control data stream.

483

484

486

487

488

489

490

491

Figure 5: Annotated layout of Hub (+ROD outline) with primary functions noted.

### 4.4 Ethernet Network Switch

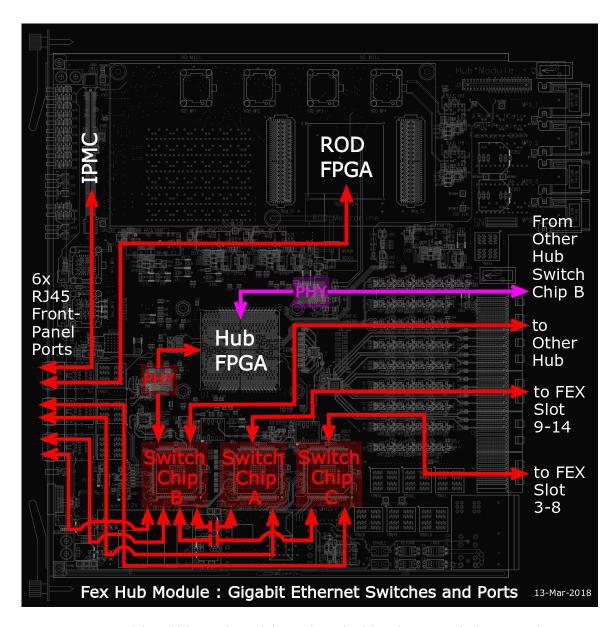

The FEX-Hub hosts an un-managed 10/100/1000 Base-T switch to provide the following 18 Gigabit Ethernet connections:

- Backplane: 12 connections to the "FEX Node" modules in this crate via the Base Channel Fabric;

- Backplane: 1 connection to the Ultrascale FPGA on the other Hub via the Update Channel Interface;

- Direct: 1 connection to the Ultrascale FPGA on this Hub;

- Front-Panel: 1 connection for an "up-link";

- Front-Panel: 1 connection for the ROD on this Hub (or IPMC on the other Hub);

- Front-Panel: 1 connection for the ROD on the other Hub (or IPMC on this Hub);

- Front-Panel: 1 spare connection;

501

506

496

498

- 502 This Ethernet switch functionality is implemented in hardware with three interconnected

- 503 8-port switch chips.

- The FEX-Hub module circuit board can be modified to disconnect these three switch

- 505 chips and provide a higher aggregate bandwidth capacity as described in Section 5.

### 4.5 Slow Control

- An IPBus interface is provided for high-level, functional control of the FEX-Hub module.

- This allows, for example, any firmware parameters to be set, modes of operation to be

- 509 controlled and monitoring data to be read.

### **4.6 Connections to the IPMB**

- 511 The FEX-Hub maintains a connection to the Intelligent Platform Management Bus

- 512 (IPMB) via an IPM Controller (IPMC) located on the Hub module. Communications

- between monitorable targets on the Hub, including the ROD mezzanine, are managed via

- an I2C Bus on the Hub module.

# 515 **4.7 Power Supplies**

- The FEX-Hub provides all of the normal ATCA redundant power input, power isolation,

- and power control from the Shelf Manager via an IPMC card. Bulk +12 Volt power is

- 518 provided to the ROD Mezzanine Card. Control signals are sent from the Hub to the ROD

- and Status signals are returned from the ROD to manage the ROD's own power up

- sequence. DC/DC converters are used to provide the power rails for the Hub itself.

### 521 4.8 Extended Use Cases

- 522 The FEX-Hub module is intended to be used in the L1Calo and L0Calo trigger systems

- through Run 4. As such, future use cases in which the Hub may need to augment the

- 524 capacity of the FEX-Hub-ROD readout path have been identified. This extra

- functionality is being implemented on the FEX-Hub so long as it does not complicate the

- 526 core Hub functions and design. These extra Hub functions are as follows:

| 527 • | Τ | he Hub ı | nain | <b>FPGA</b> | receives a | afanne | d-out | copy | of all | high-s | peed I | FEX | data l | being |

|-------|---|----------|------|-------------|------------|--------|-------|------|--------|--------|--------|-----|--------|-------|

|       |   |          |      |             |            |        |       |      |        |        |        |     |        |       |

- sent to the ROD mezzanine card, allowing at a minimum the monitoring of FEX data.

- This feature can also support Hub commissioning and diagnostics, as it further

- provides a Fabric Interface connection to the other Hub module.

- The Hub main FPGA provides additional MGT links to the ROD mezzanine, which

- will be instrumented on the ROD if sufficient input MGT links are available.

- Similarly, MGT links from the ROD to the Hub main FPGA are defined on the HUB-

- ROD interface.

- External data output paths from the Hub main FPGA are provided electrically via

- Ethernet and optically via one MiniPOD transmitter. The MiniPOD socket and

- routings are implemented by default, but the MiniPOD transmitter is only installed if

- 538 required.

542

551

- Together, this Hub functionality can provide supplemental trigger processing if required.

- However, all of this functionality could instead be ignored or disabled with no negative

- impact on the Hub core functions.

## 4.9 Commissioning and Diagnostic Facilities

- 543 The FEX-Hub module provides sufficient Hub-to-Hub electrical connections over the

- Fabric Interface, Base Interface and front-panel connections to commission and perform

- standalone diagnostic tests of the Ethernet switching functions, a subset of Fabric

- Interface high-speed data paths and TTC clock/data distribution using either one or two

- 547 FEX-Hub modules.

- Full commissioning and diagnostics will require a mated Hub+ROD, as well as a data

- source/sink for the node slots (eg., the FEX Test Module or Hub Test Module). The Hub

- testing and commissioning plan is discussed in greater detail in Section 8.

# 4.10 Environment Monitoring

- The Hub monitors the voltage and current of every power rail on the board. It also

- monitors the temperatures of FPGAs, of the MiniPOD transmitters (if installed), and of

- other areas of dense logic. Where possible, this is done using sensors embedded in the

- relevant devices themselves. Where this is not possible, discrete sensors are used. The

- voltage and temperature data are collected by the IPMC, via an I2C bus. From there, they

- are transmitted via Ethernet to the ATLAS DCS system. The Hub hardware also allows

- these data to be transmitted to the DCS via IPMB and the ATCA Shelf Controller, but it

- is not foreseen that ATLAS will support this route.

# 4.11 ATCA Form Factor

- The FEX-Hub module is an ATCA module, conforming to the PICMG® 3.0 Revision 3.0

- specification. The FEX-Hub is only capable of supporting a Dual-Star 14-slot (not 16)

- ATCA shelf. Within the L1calo system some of the Fabric Interface and Update

- Interface Channel ports are not used according to their conventional ATCA manner, as

- described in the technical detail appendices, see Sections 15 and 17.

## 5 Interfaces to Other L1Calo Modules

- The FEX-Hub module has mechanical and electrical connections to three other module

- 568 types within the L1Calo trigger system: the Hub-ROD Mezzanine card, the

- eFEX/jFEX/L1Topo modules and the other Hub module when used in a shelf with two

- Hubs. This section describes and illustrates the electrical connections between these

- 571 modules.

566

572

586

### 5.1 TTC Clock and Data Stream Interfaces

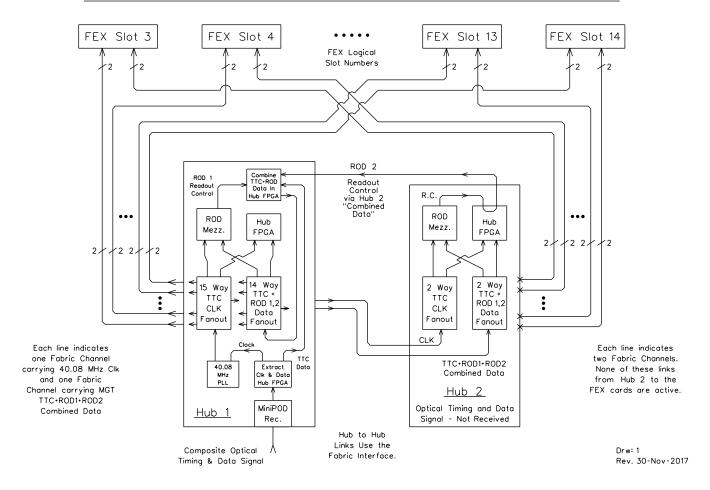

- Figure 6 shows the Hub's distribution of the TTC Clock and Data signals in the context

- of the other cards in the ATCA shelf. The composite TTC signal is received by a

- 575 MiniPOD receiver on the Hub-1 card. The TTC Clock is fanned out from the Hub-1 card

- 576 to all other modules in the shelf (including Hub-2) over the Fabric Interface. The TTC

- Data is combined with the back data from both ROD-1 and ROD-2 on Hub-1 and this

- 578 combined data stream is also fanned out from the Hub-1 module over the Fabric

- Interface. When a second Hub is used as shown in **Figure 6**, no TTC information is sent

- from Hub-2 to any of the Node slots, as the corresponding Fabric Interface ports are not

- driven on Hub-2. The Hub-1 and Hub-2 cards are identical printed circuit boards and

- could support independent fan-out of clock and data streams from both Hubs if that were

- desired in the future. Each Node slot has access to both the Hub-1 and the Hub-2 TTC

- clock and data streams. L1calo shelves are however currently explicitly defined to

- provide and use the TTC clock and data information fanned out from Hub-1 only.

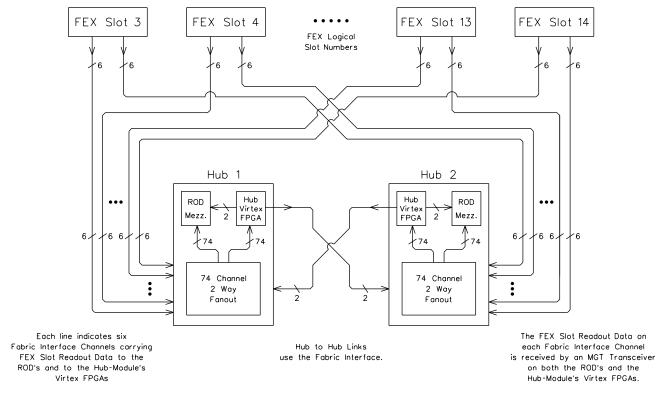

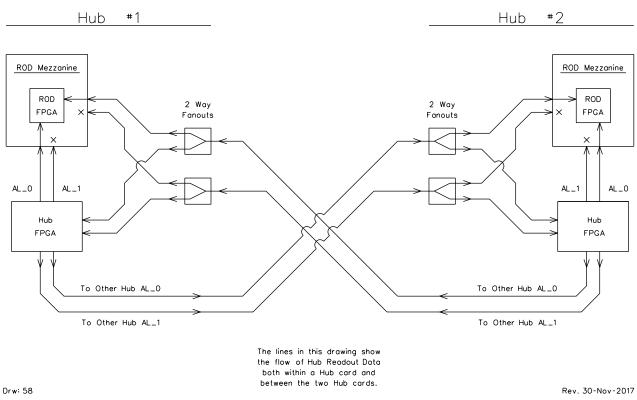

# 5.2 High-Speed Readout Data Interfaces

- Figure 7 shows the Hub's distribution of readout data in the context of the cards in the

- ATCA shelf. The readout data comes from the Node slots and from the FPGA on each

- Hub module. All of this data flows to both the ROD and to the FPGA on each Hub. The

- arrangement shown in **Figure 7** supports 2 independent streams of readout data. That is,

- the readout stream processed by the ROD and Hub FPGA on Hub-1 can be

- independent of the readout stream flowing into Hub-2.

- The Hub's high-speed readout data path as described at the level of the Hub board is

- illustrated in **Figure 19**, which can be found in the section describing the Hub PCB

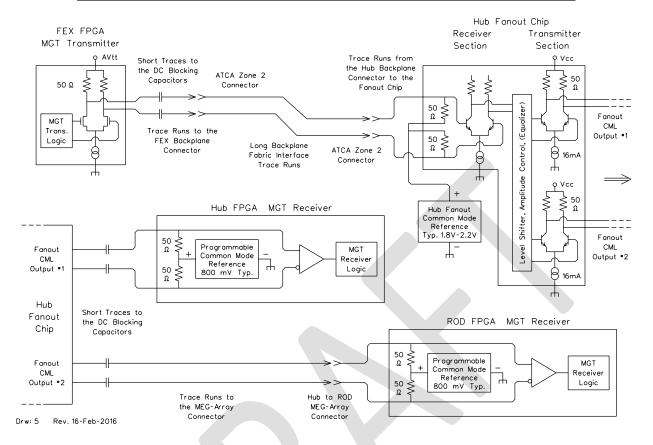

- layout (Section 6.11) and in greater detail in the technical detail appendices (Section 15).

# <u>Hub</u> <u>Clock and Combined Data Distribution</u>

**Figure 6:** Illustration of FEX-Hub distribution of TTC clock and control data stream signals.

596

# <u>Hub-Module Readout Data Distribution</u>

Drw: 2 Rev. 15-Feb-2016

**Figure 7:** Illustration of FEX-Hub distribution of high-speed readout data signals.

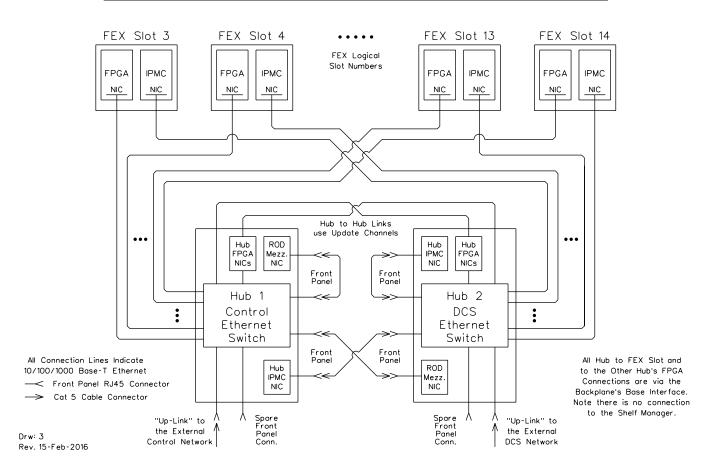

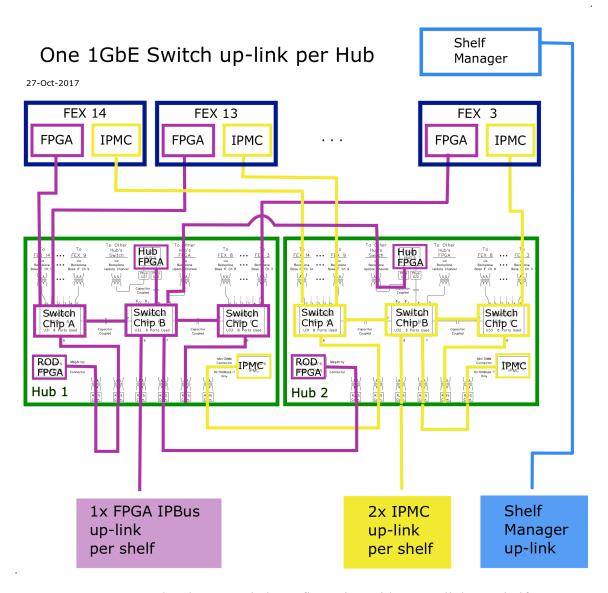

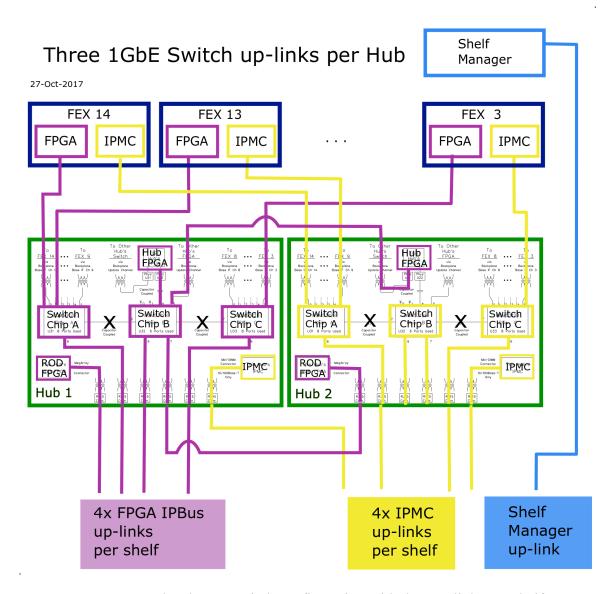

### **5.3** Ethernet Network Interfaces

**Figure 8** shows the Hub's Base Interface Ethernet Switch in the context of the other cards in the ATCA shelf. As shown in **Figure 8** the switch on Hub-1 is used to handle all connections to the IPbus Control network and the switch on Hub-2 is used to handle all connections to the IPMC/DCS network. Operation with only a Hub-1 in the shelf is possible but does not provide a Base Interface Ethernet connection to the IPMCs in the

- Node slots. In this situation the Node slot IPMCs can use their IPMB connection to the

- Shelf Manager and pass monitoring data to the DCS network.

- The Gigabit Ethernet switch functionality is implemented in hardware with three

- interconnected Broadcom BCM53128 8-port switch chips.

- When these three switch Chips are left interconnected one up-link connection per Hub is

- used to connect the L1calo crate to the rest of the network. The available aggregate

- bandwidth for the whole shelf is 1 Gbps over each of the Hub1 and Hub 2 networks. The

- corresponding connectivity at the level of one typical L1Calo shelf is depicted in **Figure**

- **6**17 **9**

- The FEX-Hub module circuit board can be modified to severe the inter-connections

- between these three switch chips. This modification increases the aggregate bandwidth

# Hub-Module Ethernet Switch Connections

**Figure 8:** Circuit diagram for the Hub Ethernet switch.

capacity. In particular, the aggregate bandwidth is then doubled for the FEX node slots. Four up-link connections per Hub are then required to connect the L1calo crate to the rest of the network. The corresponding connectivity at the level of one typical 11calo crate is depicted in **Figure 10**.

Figure 9: Hub Ethernet switch configuration with one uplink per shelf.

**Figure 10:** Hub Ethernet switch configuration with three uplinks per shelf.

### 5.4 Hub Interfaces to FEX Modules

- This subsection summarizes the Hub electrical interfaces to the FEX modules. A more

- complete specification of the connector/pin assignments is illustrated in Appendix 1

- 632 (Section 14). Please refer there for more details.

## 5.4.1 Interface with Hub-1

627

628

629

- Hub-1 resides in logical slot 1 and receives the TTC information from FELIX optically

- via MiniPOD. It thus distributes the TTC clock and control data signals. Hub-1 also

- 636 hosts the slow control IPbus network.

- 637 *5.4.1.1 Base Interface*

- The 2 ports of Base Channel 1 (4 pairs of differential signals) of the base interface are

- used to provide a Gigabit Ethernet connection to be used by the FEX module for its IPbus

- 640 port.

- The usage of the ports on this channel follows the ATCA PICMG 3.0 specification for

- 642 1000BASE-T Ethernet.

- 643 5.4.1.2 Fabric Interface

- The ports of the Fabric Interface Channel 1 are not used according to the ATCA

- 645 convention and notation.

- The 4 ports of Fabric Channel 1 (8 pairs of differential signals) are defined by ATCA as 4

- transmitting and 4 receiving pairs.

- Hub-1 is instead transmitting on only 2 of these pairs and receiving readout data from the

- FEX on the other 6 pairs

- 650 5.4.1.3 Hub-1 Module signals as Seen from a FEX Module

- The FEX modules receive the LHC clock on the receive signal pair of Fabric Interface

- Channel 1 port 0. (Note: this clock is received via MiniPOD on Hub-1). This signal is

- 653 meant to be received as a logic clock and not as data stream. It is not driven by an FPGA

- 654 MGT Transceiver on the HUB and is not meant to be received by an MGT on a FEX.

- 655 The FEX modules receive the combined TTC and ROD control data stream on the

- receive signal pair of Fabric Interface Channel 1 port 1. Note: the TTC control

- information is provided via the TTC signals sent by FELIX and received on Hub-1. The

- 658 two RODs on Hub-1 and Hub-2 may need to also send control information to the FEXs.

- This optional ROD control is merged with the TTC control data stream according to a

- 660 format to be determined.

- The FEX modules send their primary readout data streams 0-3 destined to the ROD on

- Hub-1 on the transmit signal pair of Fabric Interface Channel 1 port 0-3. The FEX

- module is SENDING its secondary readout data streams 4-5 destined to the ROD on

- Hub-1 on the RECEIVE signal pair of Fabric Interface Channel 1 port 2-3 which means it

- is using these two ports in the opposite direction from their conventional usage and

- 666 ATCA naming.

### **5.4.2** *Interface with Hub-2*

- Hub-2 resides in logical slot 2 and hosts the IPMC network. Hub-2 does not receive the

- TTC signal from FELIX via its MiniPOD receiver.

- 670 *5.4.2.1 Base Interface*

- The 2 ports of Base Channel 2 (4 pairs of differential signals) of the base interface are

- used to provide a Gigabit Ethernet connection to be used by the FEX module for its

- 673 IPMC.

- The usage of the ports on this channel follows the ATCA PICMG 3.0 specification for

- 675 1000BASE-T Ethernet.

- 676 5.4.2.2 Fabric Interface

- The ports of Fabric Interface channel 2 are not used according to the ATCA convention

- and notation.

- The 4 ports of Fabric Channel 2 (8 pairs of differential signal) are defined by ATCA as 4

- transmitting and 4 receiving pairs.

- Hub-2 is instead transmitting nothing on 2 of these pairs and receiving readout data from

- the FEX on the other 6 pairs.

- 683 5.4.2.3 Hub-2 Module Signals as Seen from a FEX Module

- The receive signal pair of Fabric Interface Channel 2 port 0 is unused on FEX modules.

- The receive signal pair of Fabric Interface Channel 2 port 1 is also unused on FEX

- 686 modules.

- The FEX modules send their primary readout data streams 0-3 destined to the ROD on

- 688 Hub-2 on the transmit signal pair of Fabric Interface Channel 2 port 0-3.

- The FEX module is SENDING its secondary readout data streams 4-5 destined to the

- 690 ROD on Hub-2 on the RECEIVE signal pair of Fabric Interface Channel 2 port 2-33

- which means it is using these two ports in the opposite direction from their conventional

- usage and ATCA naming.

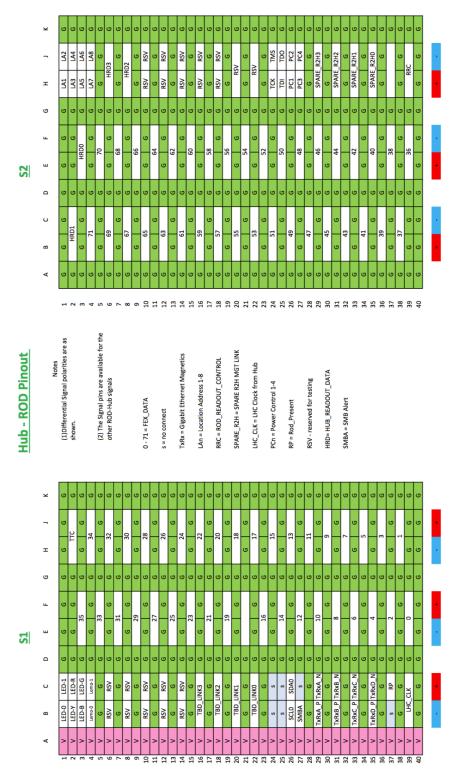

### 693 5.5 Hub Interface to the ROD Mezzanine

- Two 400 pin MEG-Array connectors interface the ROD Mezzanine to the FEX-Hub.

- This section identifies the signals carried through these connectors. A more detailed

- description of these HUB-ROD connections is given in the technical appendices,

- Sections 26, 19 and 18. An illustration of how the signals are organized in the MEG-

- Array connectors is shown in **Figure 11**, which emphasizes the relative use of ground

- and signal pins for the high-speed data lines. This figure is for illustration only and the

- technical specification appendices should be used for the mapping.

- Note: both the Ultrascale FPGA used on the FEX-Hub and the Virtex-7 FPGA used on

- the ROD offer a maximum of 80 MultiGigabit Transceivers (MGT) i.e. 80 Transmitter

| 704<br>705               | the main limiting factor in the compromises reached in the design of both the Hub-FEX and the ROD.                                                                                                                                                      |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 706                      | 5.5.1 MGT Differential Inputs to ROD from Hub                                                                                                                                                                                                           |

| 707                      | These differential signals are connected to MGT Receiver on the ROD FPGA.                                                                                                                                                                               |

| 708                      | • $12x6 = 72$ serial streams of Readout Data from the FEX modules                                                                                                                                                                                       |

| 709                      | • 2x serial streams of Readout Data from the local HUB FPGA                                                                                                                                                                                             |

| 710                      | • 2x serial streams of Readout Data from the other HUB FPGA                                                                                                                                                                                             |

| 711                      | • 1x serial stream of combined TTC and ROD control data stream                                                                                                                                                                                          |

| 712                      | 5.5.2 MGT Differential Outputs from ROD to Hub                                                                                                                                                                                                          |

| 713                      | • 1x serial stream of ROD Readout Control information                                                                                                                                                                                                   |

| 714<br>715               | This signal needs to be merged with the TTC control data stream by the HUB FPGA of the FEX-Hub in slot 1.                                                                                                                                               |

| 716<br>717               | A copy of this combined TTC and ROD control data stream is sent to the ROD FPGA from both FEX-Hub in Slot 1 and Slot 2.                                                                                                                                 |

| 718                      | 5.5.3 Other signals between ROD and Hub                                                                                                                                                                                                                 |

| 719                      | • LHC Clock                                                                                                                                                                                                                                             |

| 720                      | o 1x Differential signal pair                                                                                                                                                                                                                           |

| 721                      | Geographic Address                                                                                                                                                                                                                                      |

| 722                      | <ul> <li>8x signals coming from the Hub FPGA</li> </ul>                                                                                                                                                                                                 |

| 723<br>724<br>725<br>726 | The HUB FPGA determines this System Geographic Address by combining the J10 Hardware Address pins with the Shelf Address retrieved from the Shelf Manager by the IPMC. The shelf and slot addressing scheme for this 8 bit address needs to be defined. |

| 727                      | • IPbus port                                                                                                                                                                                                                                            |

| 728<br>729               | <ul> <li>4x Bi-directional Signal Pairs forming a 1000BASE-T Gigabit Ethernet<br/>connection.</li> </ul>                                                                                                                                                |

| 730                      | Sensor I2C Bi-directional Bus                                                                                                                                                                                                                           |

ports and 80 MGT Receiver ports. The limit on the number of MGT Receivers has been

| 731 | 0        | 2x I2C Signals (Clock and Data) connected to the IPMC                   |

|-----|----------|-------------------------------------------------------------------------|

| 732 | • JTAG   | access                                                                  |

| 733 | 0        | 4x JTAG Signals                                                         |

| 734 | • Power  | Supply Connections                                                      |

| 735 | 0        | +12V bulk power is made available to the ROD                            |

| 736 | • Power  | Control signals: 4 single-ended bidirectional signals nominally used as |

| 737 | 0        | 2x Power Control Signals to the ROD                                     |

| 738 | 0        | 2x Power Status Signals from the ROD                                    |

| 739 | • Contro | l and Status                                                            |

| 740 | 0        | 5x ROD-specified LEDs                                                   |

| 741 | 0        | 2x Phy LEDs                                                             |

| 742 | 0        | 1x Lemo                                                                 |

| 743 | 0        | 4x spare bidirectional differential pairs                               |

| 744 | 0        | 1x ROD present                                                          |

**Figure 11:** Illustration of the ROD/Hub MEG-Array connector pin usage, illustrating signal and ground designations. This diagram is not intended for signal mapping, and the final mapping is provided in the technical appendices.

### 746 **5.6 Hub Interfaces to Second Hub Modules**

- **747 5.6.1 Base Interface**

- The Base Channel 1 is reserved for the Shelf Manager Controller and is unused.

- The Base Channel 2 port (4 pairs of differential signals) is not currently allocated.

- 750 **5.6.2 Fabric Interface**

- 751 The Fabric Interface channel 1 is used according to the ATCA convention and notation

- with one caveat for Hub-2: Hub-2 is transmitting nothing on 2 of its transmitter pairs.

- 753 **5.6.3 Hub-2** usage of the Fabric Interface connection to Hub-1

- Hub-2 is receiving the LHC clock on the receiving signal pair of Fabric Interface Channel

- 755 1 port 0.

- 756 Hub-2 is receiving the combined TTC and ROD control data stream on the receiving

- signal pair of Fabric Interface Channel 1 port 1.

- Hub-2 is sending on the transmitting signal pair of Fabric Interface Channel 1 port 0-1 its

- readout data streams 1-2 destined to the ROD on Hub-1.

- 760 5.6.3.1 Hub-1 usage of the Fabric Interface connection to Hub-2

- 761 The receiving signal pair of Fabric Interface Channel 1 port 0 is unused on Hub-1.

- Hub-1 is receiving on the receive signal pair of Fabric Interface Channel 1 port 1 the

- ROD Readout control information from the ROD on Hub-2.

- Hub-1 is sending on the transmit signal pair of Fabric Interface Channel 1 port 0-1 its

- readout data streams 1-2 destined to the ROD on Hub-2.

### 766 **5.6.4 Update Channel Interface**

- 767 The 5 ports of the Update Channel (10 pairs of differential signal) are defined by ATCA

- as 5 transmitting and 5 receiving pairs. The first 4 ports of the Update Channel Interface

- are not used according to this ATCA convention and notation. The 5th port of the Update

- 770 Channel Interface is not currently allocated.

- The 4 Transmit pairs of Update Channel port 0-4 form one Gigabit Ethernet link and are

- connected to a Switch port of the local Hub. The 4 Receive pairs of Update Channel port

- 773 0-4 form another Gigabit Ethernet link and are connected to the Hub FPGA on the local

- 774 Hub.

- Note: the exact pin assignment of each port to the four 1000BASE-T signal pairs will be

- specified later while this assignment is internal to Hub operation only (no other L1Calo

- modules are affected).

- 778 This Hub-to-Hub connection allows the Hub FPGA on Hub-2 to connect to the IPbus

- Network serviced by the Ethernet switch on Hub-1.

- 780 The Hub FPGA on Hub-1 is directly connected to the IPbus Network switch on Hub-1

- and can simply ignore this additional Ethernet port that would connect it to the IPMC

- Network serviced by the Ethernet switch on Hub-2.

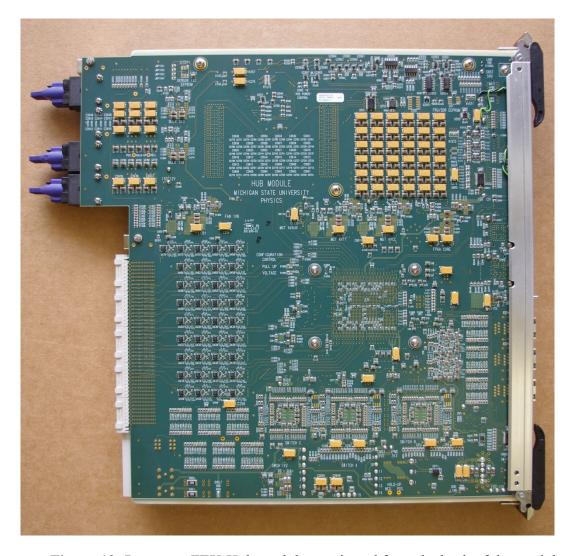

# 6 Hub Implementation Details

- 784 This section describes the details of how the FEX-Hub functionality has been

- 785 implemented for the prototype module, which is also the intended implementation for the

- final production module. The prototype FEX-Hub module is shown in **Figure 12** and

- Figure 13, wherein the ROD mezzanine card has been mounted to illustrate the

- anticipated final form of the Hub+ROD pairing.

**Figure 12:** Prototype FEX-Hub module with ROD mezzanine mounted, as viewed from the front of the module.

**Figure 13:** Prototype FEX-Hub module, as viewed from the back of the module.

# 6.1 Physical Layout

789

790

- The FEX-Hub module is implemented as a size 6 HP ATCA card, with the L1Calo-

- specified bump-out in Zone 3 to accommodate the L1Calo RTM. An annotated

- 794 illustration of the physical layout can be found in **Figure 5**.

- The Hub holds the ROD mezzanine card. The ROD is located near the top edge of the

- Hub and runs from the Hub's front panel edge for 200 mm towards the Hub's backplane

- edge. In the direction along the front panel the ROD runs for 100 mm.

- The Hub and ROD are electrically connected by two 400 pin MEG-Array connectors. A

- short 4mm stack height is used so that the Hub and ROD PCBs are quite close to each

- other. The component sides of the Hub and ROD both face in the same direction. The

- intent is to keep the path of the high-speed differential signals from the Hub to the ROD

- as short as possible and to give the maximum available height for the MiniPODs and

- other components on the ROD.

- The Hub and ROD are mechanically connected to each other using standoffs. The Hub

- holds the fiber-optic pig-tail cables and connectors that run from Zone 3 on the Hub to

- the MiniPOD devices on the ROD.

- The primary components on the Hub card are a Xilinx Ultrascale FPGA, three Broadcom

- GbE switches (with associated PHY chips and RJ45 connectors), 74 ON-Semi 1:2 fanout

- 809 chips.

832

- The Hub includes heat sinks for its FPGA, and for it MiniPODs. Along its backplane

- edge the FEX-Hub uses the Zone 1 P10 connector, the full complement of Zone 2

- connectors (J20 through J24), and 4 MPO connectors in Zone 3.

### 6.2 Readout Signal Distribution

- The FEX-Hub receives readout data on 6 channels of the Fabric Interface from each of

- the 12 node slots in the shelf. This is 72 channels of high-speed readout data from the

- FEX node slots. In addition the Ultrascale FPGA on the other FEX-Hub provides 2

- Fabric Interface channels of readout data. This makes a total of 74 channels of readout

- data from other slots in the shelf. The FPGA on the FEX-Hub holding the ROD also

- provides 2 GTH channels of readout data. Thus a total of 74 GTH receivers on the ROD

- are required to field the readout data from all sources in the shelf.

- The readout data from the backplane is received by the Hub with On-Semi 2-way fan-out

- chips that have built-in termination.

- One output from these fan-out chips runs to 74 MGT inputs on the FEX-Hub's Ultrascale

- FPGA. The other output from these fan-out chips is routed through the 2 Meg-Array

- connectors to the ROD mezzanine card.

- The pinout of the Meg-Array connectors to the ROD has been designed to provide

- optimum signal fidelity for these high-speed differential signals. The intent is to provide

- a clean, uniform, and short route for the traces on the ROD that connect the Meg-Array

- pins to its GTH transceiver inputs. On the ROD the Meg-Array connectors are located

- adjacent to the edges of its Ultrascale FPGA that hold the MGT transceivers.

- Additional details can be found in the technical appendices (Section 15).

### 6.3 Timing and Trigger Control Distribution

- In normal operation Hub #1 uses a MiniPOD to receive an optical link from FELIX that

- contains the LHC Reference Clock and the TTC Data Stream. Logic in the Hub's FPGA

- separates the LHC Reference Clock from this composite signal and sends it to the

- reference input of a 40.0787 MHz quartz crystal based Phase Locked Loop. The

- composite control information is combined with data flow control signals from the two

- 838 ROD modules in the shelf.

- The FEX-Hub distributes the TTC Clock and the TCC Data Stream to 15 different

- objects that use these signals. The objects that use these TTC signals are: 12 ATCA

- Node Slots, the ROD mezzanine card on this Hub, this Hub's own Ultrascale FPGA, and

- finally distribution of these TTC signals to the other Hub module.

#### 6.3.1 Clock Distribution

- Distribution of the TTC Clock by the Hub is purely by fan-out. Note that the Hub will

- provide a 40.08 MHz clock signal even when it is not receiving a composite TTC input

- 846 signal.

- The specified "pull range" of of this PLL is +- 40 ppm minimum which gives them an

- operating range of 40.077097 MHz to 40.080303 MHz. This operating range covers all

- conditions of operating temperature, supply voltage, and aging. The operating range of

- these PLLs is wider than the frequency range specified in FELIX Requirement

- 2.3.5: "The FE systems shall operate in the BC clock frequency range 40.078886 MHz to

- 40.078973 MHz during proton runs (at 6.5 TeV) and in the range 40.078422 MHz to

- 853 40.078970 MHz during heavy ion runs (at 6.5 TeV)".

- The clean output of the Hub's 40.0787 MHz PLL is fanned out to the following loads:

- as an AC coupled LVDS reference clock to the ROD on this Hub,

- as a logic clock to the FPGA on this Hub,

- as a reference clock to the 320.6296 MHz PLL on this Hub,

- as an AC coupled LVDS reference clock over the backplane to the Hub Module #2 in this shelf,

- as an AC coupled LVDS reference clock over the backplane to the 12 FEX cards in this shelf

- In normal operation Hub Module #2 receives its reference clock over the backplane just

- like the 12 FEX cards. Hub Module #2 does not receive an optical link from FELIX with

- the LHC Reference Clock. In Hub Module #2 the backplane reference clock is sent to

- the reference input of its 40.0787 MHz PLL. From there the clean 40 MHz clock signal is

- 866 fanned out to the following loads:

- as an AC coupled LVDS reference clock to the ROD on this Hub,

- as a logic clock to the FPGA on this Hub,

- as a reference clock to the 320.6296 MHz PLL on this Hub

### 6.3.2 Control Signal Distribution

- Distribution of the TTC Data Stream by the Hub is more complicated than what's

- required for the clock signal. As shown in the TTC Distribution drawing the TTC Data

- Stream is mixed with the "back data" coming from both the ROD on Hub-1 and the ROD

- on Hub-2. A small part of the logic available in the Hub-1 Virtex FPGA is used to

- combine these 3 data streams.

870

- Fabric Interface Channels are used to carry the TTC Clock and the combined Data

- Stream from Hub-1 to the Node Slots and from Hub-1 to Hub-2. When the Hubs are

- used this way all Node slots receive both their TTC Clock and the combined Data Stream

- from the Fabric Interface channels to Hub-1. Note that the PCB traces on both Hubs are

- the same so that distribution of TTC Data combined with back data from the ROD on

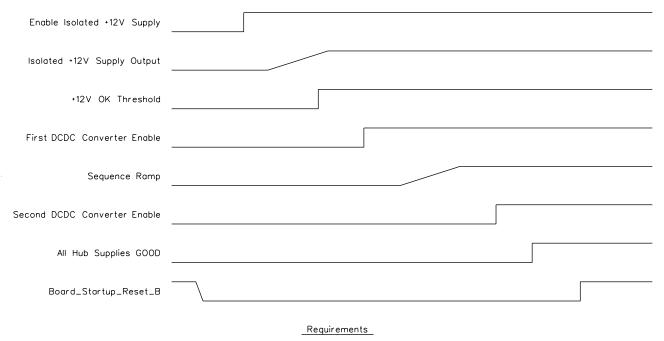

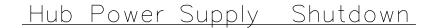

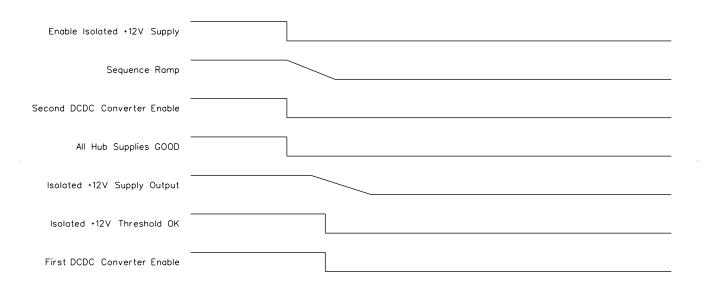

- Hub-1 on one set of Fabric channels while separately distributing TTC Data combined