# SIEMENS

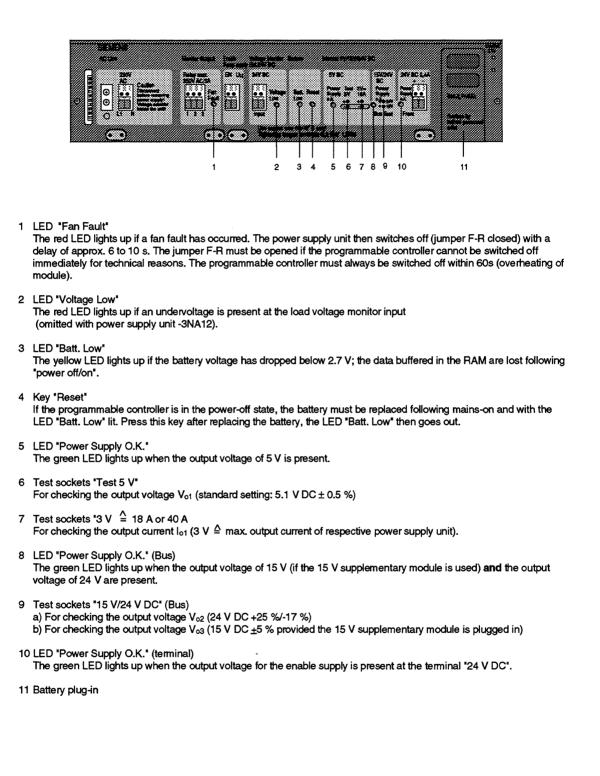

## **SIMATIC S5**

## S5-155U Programmable Controller (CPU 946/947)

Manual

Order No. 6ES5998-0UM22 Release 07

| Contents                                                       |                      |    |

|----------------------------------------------------------------|----------------------|----|

| Warnings<br>Information<br>Suggestions/Corrections             | C79000-R8576-C647    |    |

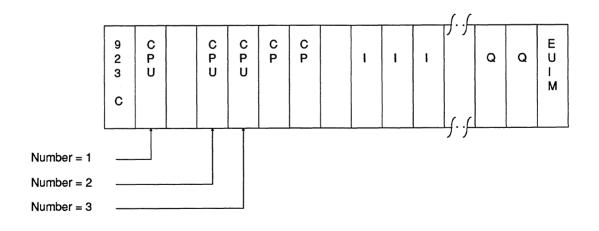

| Product Summary<br>CPU 946/947                                 | C79000-T8576-C647-01 | 1  |

| Installation Guide<br>Programmable Controllers of the U Series | C79000-B8576-C452-04 | 2  |

| S5-155U/S5-155H Central Controller<br>Instructions             | C79000-B8576-C380-05 | 3  |

| CPU 946/947<br>Instructions                                    | C79000-B8576-C532-06 | 4  |

| 355 Memory Module<br>Instructions                              | C79000-B8576-C382-06 | 5  |

| 923 C Coordinator<br>Instructions                              | C79000-B8576-C349-06 | 6  |

| Multiprocessor Operation<br>Instructions                       | C79000-B8576-C500-02 | 7  |

| Multiprocessor Communication<br>User's Guide                   | C79000-B8576-C468-05 | 8  |

| CPU 946/947<br>Programming Guide                               | C79000-B8576-C637-03 | 9  |

| <b>Space</b> for Pocket Guide<br>CPU 946/947, CPU 946R/947R    | C79000-B8576-C054-01 | 10 |

| Appendix                                                       | C79000-A8576-C647-01 | 11 |

|                                                                |                      | 12 |

The Pocket Guide CPU 946/947, CPU 946R/947R (C79000-B8576-C111-02) is included in the front pocket of this Manual.

## Summary of Product Number and Corresponding Documentation for the S5-155U Programmable Controller

The following table shows the assignment of the product documentation to the individual products. The listed sections of the documentation relate to the manual S5-155U (CPU 946/947) with the order no. 6ES5 998-0UM22, release 07.

| Product                                                              |                               | Product Documentation                                                                                                                                                                     |

|----------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Order No.                                                            | Title                         |                                                                                                                                                                                           |

| 6ES5 155-3UA11<br>6ES5 155-3UA21                                     | Central Controller<br>S5-155U | Instructions:<br>(Part 3): Central Controller S5-155U/155H<br>C79000-B8576-C380-05<br>(Part 7): Multiprocessor Operation in the                                                           |

|                                                                      |                               | Central Controllers S5-135U/155U<br>C79000-B8576-C500-02                                                                                                                                  |

|                                                                      |                               | <b>User's Guide</b><br>(Part 8): Multiprocessor Communication S5-135U<br>Programmable Controller, CPU 922 and 928<br>S5-155U Programmable Controller, CPU 946/947<br>C79000-B8576-C468-05 |

|                                                                      |                               | Installation Guide<br>(Part 2): Programmable Controllers of the<br>U Series<br>C79000-B8576-C452-04                                                                                       |

| 6ES5 946-3UA11<br>6ES5 946-3UA12<br>6ES5 946-3UA21<br>6ES5 946-3UA21 | CPU 946/947                   | Instructions<br>(Part 4): CPU 946/947<br>C79000-B8576-C532-06                                                                                                                             |

| 6ES5 947-3UA21                                                       |                               | Programming Guide<br>(Part 9): S5-155U Programmable Controller, CPU<br>946/947 and S5-155H Programmable Controller,<br>CPU 946R/947R<br>C79000-B8576-C637-03                              |

|                                                                      |                               | List of Operations (in the front pocket)<br>CPU 946/947, CPU 946R/947R<br>C79000-B8576-C111-02                                                                                            |

| 6ES5 355-3UA11                                                       | 355 Memory Module             | Instructions<br>(Part 5): 355 Memory Module<br>C79000-B8576-C382-06                                                                                                                       |

| 6ES5 923-3UC11                                                       | 923 C Coordinator             | Instructions<br>(Part 6): 923 C Coordinator<br>C79000-B8576-C349-06                                                                                                                       |

#### Preface

This manual provides an overview of the structure and functions of the programmable logical controller S5-155U. It explains how you configure, program, test and start your programmable controller.

This manual is intended as a guide for you to learn to use the PLC and to make optimum use of the features of the device.

This manual is intended for engineers, programmers and maintenance personnel who have a general knowledge of programmable controller concepts.

If you have any questions which have not been answered in this manual, please contact your local Siemens representative.

### How To Use This Manual

The following information is intended to make it easier for you to use the S5-155U manual, (order no. 6ES5 998-0UM22).

#### **Overview of Contents**

#### • Part 1 : Product Summary

This part provides an overview of the structure of the S5-155U programmable controller with CPU 946R/947R. This overview provides you with the basic information to aid your understanding of the following chapters.

#### • Part 2 : Programmable Controllers of the U Series - Installation Guide

This part provides the information about how the programmable controllers of the U series must be structured. Different configurations, power supply, wiring, fans, temperature monitoring, safety measures and interference suppression are described.

#### • Part 3 : 155U Central Controller - Instructions

This part provides the instructions to the S5-155U central controller. Both the hardware as well as the installation procedure, start-up procedure and the maintenance of the central controller are described. After installation is complete, you will find the information in this section that you need to guarantee trouble free operation of the central controller.

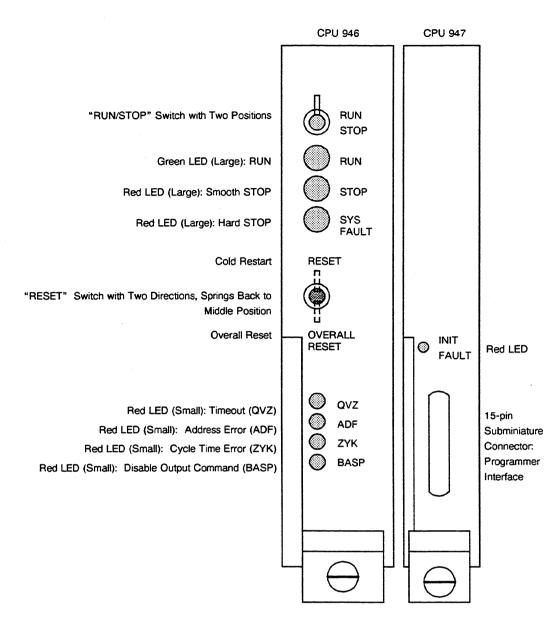

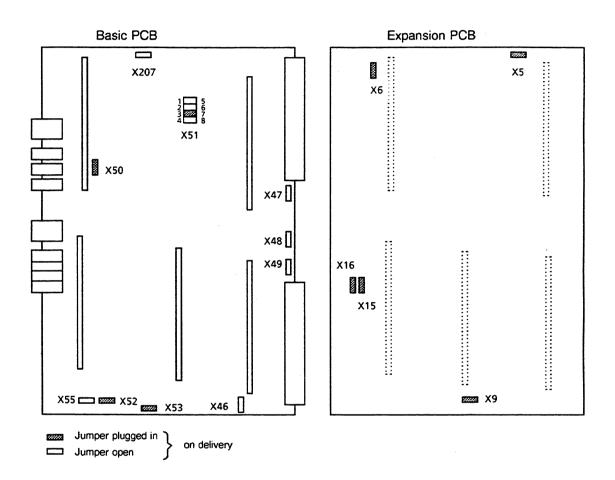

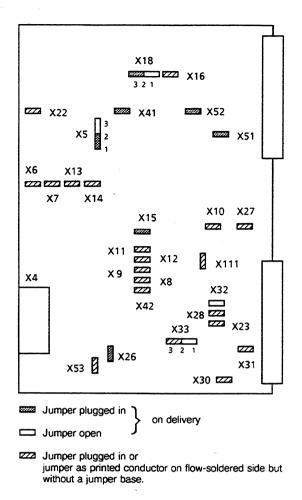

#### • Part 4 : CPU 946/947 - Instructions

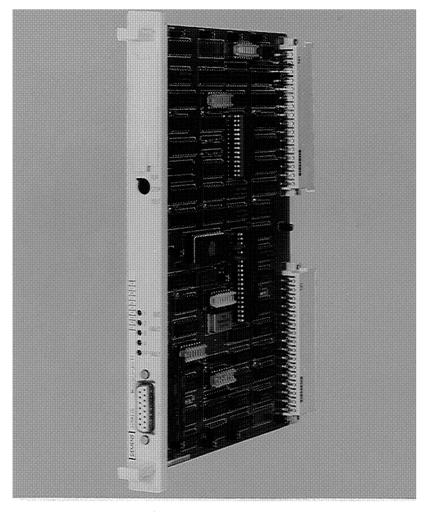

This part provides the instructions with a technical description and information about the installation procedure and use of the CPU 946/947; the standard central unit of the SIMATIC S5-155U programmable controller.

#### • Part 5 : 355 Memory Module - Instructions

This part provides the instructions on the memory module The instructions describe which modules you can use and what you must note about the installation and operation of the individual modules.

#### • Part 6 : 923C Coordinator - Instructions

Here you will find a description of how the modules function and what you must know about operating the coordinator.

#### • Part 9 : STEP 5 Programming Instructions for the S5-155U

The mode of operation and application of the CPU 946/947 are described in this section. Comprehensive information is available so that you can make optimum use of the S5-155U programmable controller.

#### • Part 11 : Appendix

The order numbers of all the components and spare parts mentioned in this manual are listed here.

## Index

Each part of this manual has its own index.

## Training

For information about training courses in connection with this device, please contact your local Siemens representative.

## Warning

#### Risks involved in the use of so-called SIMATIC-compatible modules of non-Siemens manufacture

"The manufacturer of a product (SIMATIC in this case) is under the general obligation to give warning of possible risks attached to his product. This obligation has been extended in recent court rulings to include parts supplied by other vendors. Accordingly, the manufacturer is obliged to observe and recognize such hazards as may arise when a product is combined with products of other manufacture.

# For this reason, we feel obliged to warn our customers who use SIMATIC products not to install so-called SIMATIC-compatible modules of other manufacture in the form of replacement or add-on modules in SIMATIC systems.

Our products undergo a strict quality assurance procedure. We have no knowledge as to whether outside manufacturers of so-called SIMATIC-compatible modules have any quality assurance at all or one that is nearly equivalent to ours. These so-called SIMATIC- compatible modules are not marketed in agreement with Siemens; we have never recommended the use of so-called SIMATIC-compatible modules of other manufacture. The advertising of these other manufacturers for so-called SIMATIC-compatible modules wrongly creates the impression that the subject advertised in periodicals, catalogues or at exhibitions had been agreed with us. Where so-called SIMATIC-compatible modules of non-Siemens manufacture are combined with our SIMATIC automation systems, we have a case of our product being used contrary to recommendations. Because of the variety of applications of our SIMATIC automation systems and the large number of these products marketed worldwide, we cannot give a concrete description specifically analyzing the hazards created by these so-called SIMATIC-compatible modules. It is beyond the manufacturer's capabilities to have all these so-called SIMATICcompatible modules checked for their effect on our SIMATIC products. If the use of so-called SIMATIC-compatible modules leads to defects in a SIMATIC automation system, no warranty for such systems will be given by Siemens.

In the event of product liability damages due to the use of so-called SIMATIC-compatible modules, Siemens are not liable since we took timely action in warning users of the potential hazards involved in so-called SIMATIC-compatible modules."

## Safety-Related Guidelines for the User

## 1 General

This manual provides the information required for the intended use of the particular product. The documentation is written for technically qualified personnel such as engineers, programmers or maintenance specialists who have been specially trained and who have the specialized knowledge required in the field of instrumentation and control.

A knowledge of the safety instructions and warnings contained in this manual and their appropriate application are prerequisites for safe installation and commissioning as well as safety in operation and maintenance of the product described. Only qualified personnel as defined in section 2 have the specialized knowledge that is necessary to correctly interpret the general guidelines relating to the safety instructions and warnings and implement them in each particular case.

This manual is an inherent part of the scope of supply even if, for logistic reasons, it has to be ordered separately. For the sake of clarity, not all details of all versions of the product are described in the documentation, nor can it cover all conceivable cases regarding installation, operation and maintenance. Should you require further information or face special problems that have not been dealt with in sufficient detail in this documentation, please contact your local Siemens office.

We would also point out that the contents of this product documentation shall not become a part of or modify any prior or existing agreement, commitment or legal relationship. The Purchase Agreement contains the complete and exclusive obligations of Siemens. Any statements contained in this documentation do not create new warranties or restrict the existing warranty.

## 2 Qualified Personnel

Persons who are **not qualified** should not be allowed to handle the equipment/system. Noncompliance with the warnings contained in this manual or appearing on the equipment itself can result in severe personal injury or damage to property. Only **qualified personnel** should be allowed to work on this equipment/system.

Qualified persons as referred to in the safety guidelines in this manual as well as on the product itself are defined as follows:

- System planning and design engineers who are familiar with the safety concepts of automation equipment;

- Operating personnel who have been trained to work with automation equipment and are conversant with the contents of the manual in as far as it is connected with the actual operation of the plant;

- Commissioning and service personnel who are trained to repair such automation equipment and who are authorized to energize, deenergize, clear, ground and tag circuits, equipment and systems in accordance with established safety practices.

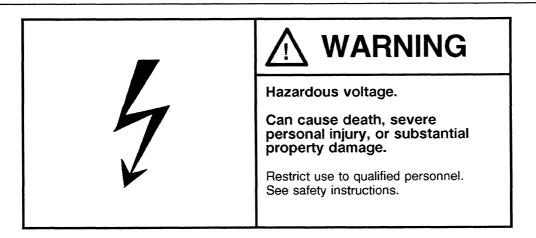

## 3 Danger Notices

The notices and guidelines that follow are intended to ensure personal safety, as well as protecting the product and connected equipment against damage.

The safety notices and warnings for protection against loss of life (the users or service personnel) or for protection against damage to property are highlighted in this manual by the terms and pictograms defined here. The terms used in this manual and marked on the equipment itself have the following significance:

#### Danger

indicates that death, severe personal injury or substantial property damage <u>will</u> result if proper precautions are not taken.

## Warning

indicates that death, severe personal injury or substantial property damage <u>can</u> result if proper precautions are not taken.

#### Caution

indicates that minor personal injury or property damage <u>can</u> result if proper precautions are not taken.

## Note

is an important information about the product, its operation or a part of the manual to which special attention is drawn.

### Important

If in this manual "Important" should appear in bold type, drawing attention to any particularly information, the definition corresponds to that of "Warning", "Caution" or "Note".

## 4 Proper Usage

- The equipment/system or the system components may only be used for the applications described in the catalog or the technical description, and only in combination with the equipment, components and devices of other manufacturers as far as this is recommended or permitted by Siemens.

- The product described has been developed, manufactured, tested and the documentation compiled in keeping with the relevant safety standards. Consequently, if the described handling instructions and safety guidelines described for planning, installation, proper operation and maintenance are adhered to, the product, under normal conditions, will not be a source of danger to property or life.

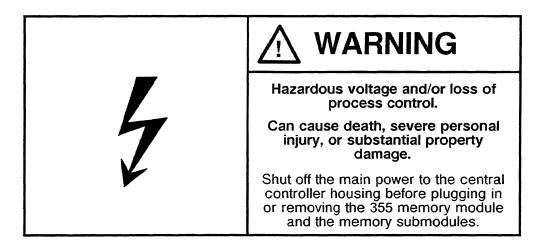

#### Warning

- After opening the housing or the protective cover or after opening the system cabinet. certain parts of this equipment/system will be accessible, which could have a dangerously high voltage level.

- Only suitably qualified personnel should be allowed access to this equipment/system.

- These persons must be fully conversant with any potential sources of danger and maintenance measures as set out in this manual.

- It is assumed that this product be transported, stored and installed as intended, and maintained and operated with care to ensure that the product functions correctly and safely.

## 5 Guidelines for the Planning and Installation of the Product

The product generally forms a part of larger systems or plants. These guidelines are intended to help integrate the product into its environment without it constituting a source of danger.

The following facts require particular attention:

## Note

Even when a high degree of safety has been designed into an item of automation equipment by means of multichannel configuration, it is still imperative that the instructions contained in this manual be exactly adhered to. Incorrect handling can render ineffective the preventive measures incorporated into the system to protect it against dangerous faults, and even create new sources of danger.

The following advice regarding installation and commissioning of the product should - in specific cases - also be noted.

## Caution

- Install the power supply and signal cables in such a manner as to prevent inductive and capacitive interference voltages from affecting the automation functions.

- Automation equipment and its operating elements must be installed in such a manner as to prevent unintentional operation.

- Automation equipment can assume an undefined state in the case of a wire break in the signal lines. To prevent this, suitable hardware and software measures must be taken when interfacing the inputs and outputs of the automation equipment.

## 6 Active and Passive Faults in Automation Equipment

- Depending on the particular task for which the electronic automation equipment is used, both active as well as passive faults can result in a dangerous situation. For example, in drive control, an active fault is generally dangerous because it can result in an unauthorized startup of the drive. On the other hand, a passive fault in a signalling function can result in a dangerous operating state not being reported to the operator.

- This differentiation of the possible faults and their classification into dangerous and nondangerous faults, depending on the particular task, is important for all safety considerations in respect of the product supplied.

#### Warning

In all cases where a fault in an automation equipment can result in severe personal injury or substantial damage to property, ie. where a dangerous fault can occur, additional external measures must be taken or equipment provided to ensure or force safe operating conditions even in the event of a fault (e.g. by means of independent limit monitors, mechanical interlocks etc.).

## 7 Procedures for Maintenance and Repair

If measurement or testing work is to be carried out on an active unit, the rules and regulations contained in the "VBG 4.0 Accident prevention regulations" of the German employers liability assurance association (Berufsgenossenschaften) must be observed. Particular attention is drawn to paragraph 8 "Permissible exceptions when working on live parts". Use only suitable electrical tools.

The information in this manual is checked regularly for updating and correctness and may be modified without prior notice. The information contained in this manual is protected by copyright. Photocopying and translation into other languages is not permitted without express permission from Siemens.

## Guidelines for Handling Electrostatically Sensitive Devices (ESD)

#### 1 What is ESD?

VSLI chips (MOS technology) are used in practically all SIMATIC S5 and TELEPERM M modules. These VLSI components are, by their nature, very sensitive to overvoltages and thus to electrostatic discharge:

They are therefore defined as

"Electrostatically Sensitive Devices"

"ESD" is the abbreviation used internationally.

The following warning label on the cabinets, subracks and packing indicates that electrostatically sensitive components have been used and that the modules concerned are susceptible to touch:

**ESDs** can be destroyed by voltage and energy levels which are far below the level perceptible to human beings. Such voltages already occur when a component or a module is touched by a person who has not been electrostatically discharged. Components which have been subjected to such overvoltages cannot, in most cases, be immediately detected as faulty; the fault occurs only after a long period in operation.

An electrostatic discharge

- of 3500 V can be felt

- of 4500 V can be heard

- must take place at a minimum of 5000 V to be seen.

But just a fraction of this voltage can already damage or destroy an electronic component.

The typical data of a component can suffer due to damage, overstressing or weakening caused by electrostatic discharge; this can result in temporary fault behavior, e.g. in the case of

- temperature variations,

- mechanical shocks,

- vibrations,

- change of load.

Only the consequent use of protective equipment and careful observance of the precautions for handling such components can effectively prevent functional disturbances and failures of ESD modules.

© Siemens AG C79000-D8076-C333-01

### 2 When is a Static Charge Formed?

One can never be sure whether the human body or the material and tools which one is using are not electrostatically charged.

Small charges of 100 V are very common; these can, however, very quickly rise up to 35 000 V.

Examples of static charge:

| - | Walking on a carpet                | up to | 35 000 V |

|---|------------------------------------|-------|----------|

| - | Walking on a PVC flooring          | up to | 12 000 V |

| - | Sitting on a cushioned chair       | up to | 18 000 V |

|   | Plastic desoldering unit           | up to | 8 000 V  |

| - | Plastic coffee cup                 | up to | 5000 V   |

| - | Plastic bags                       | up to | 5000 V   |

| - | Books, etc. with a plastic binding | up to | 8 000 V  |

#### 3 Important Protective Measures against Static Charge

- Most plastic materials are highly susceptible to static charge and must therefore be kept as far away as possible from ESDs.

- Personnel who handle ESDs, the work table and the packing must all be carefully grounded.

#### 4 Handling of ESD Modules

- One basic rule to be observed is that electronic modules should be touched by hand only if this is necessary for any work required to be done on them. Do not touch the component pins or the conductors.

- Touch components only if

- the person is grounded at all times by means of a wrist strap

or

- the person is wearing special anti-static shoes or shoes with a grounding strip.

- Before touching an electronic module, the person concerned must ensure that (s)he is not carrying any static charge. The simplest way is to touch a conductive, grounded item of equipment (e.g. a blank metallic cabinet part, water pipe, etc.) before touching the module.

- Modules should not be brought into contact with insulating materials or materials which take up a static charge, e.g. plastic foil, insulating table tops, synthetic clothing, etc.

- Modules should only be placed on conductive surfaces (table with anti-static table top, conductive foam material, anti-static plastic bag, anti-static transport container).

- Modules should not be placed in the vicinity of monitors, TV sets (minimum distance from screen > 10 cm).

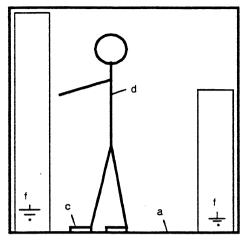

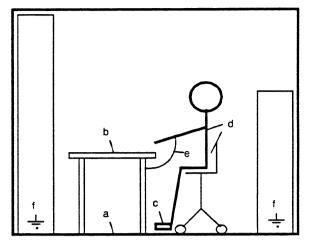

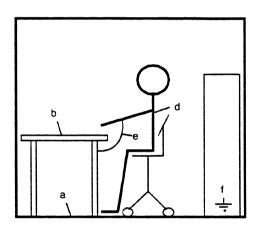

The diagram below shows the required protective measures against electrostatic discharge.

Standing position

Standing/sitting position

- a Conductive flooring

- b Anti-static table

- c Anti-static shoes

- d Anti-static coat e Grounding wrist s

- Grounding wrist strap

- Grounding connection of the cabinets

Sitting position

#### 5 Measurements and Modification to ESD Modules

- Measurements on modules may only be carried out under the following conditions:

- The measuring equipment is grounded (e.g. via the PE conductor of the power supply system) or

- when electrically isolated measuring equipment is used, the probe must be discharged (e.g. by touching the metallic casing of the equipment) before beginning measurements.

- Only grounded soldering irons may be used.

#### 6 Shipping of ESD Modules

Anti-static packing material must always be used for modules and components, e.g. metalized plastic boxes, metal boxes, etc. for storing and dispatch of modules and components.

If the container itself is not conductive, the modules must be wrapped in a conductive material such as conductive foam, anti-static plastic bag, aluminium foil or paper. Normal plastic bags or foils should not be used under any circumstances.

For modules with built-in batteries ensure that the conductive packing does not touch or shortcircuit the battery connections; if necessary cover the connections with insulating tape or material.

© Siemens AG C79000-D8076-C333-01

# SIEMENS

## **SIMATIC S5**

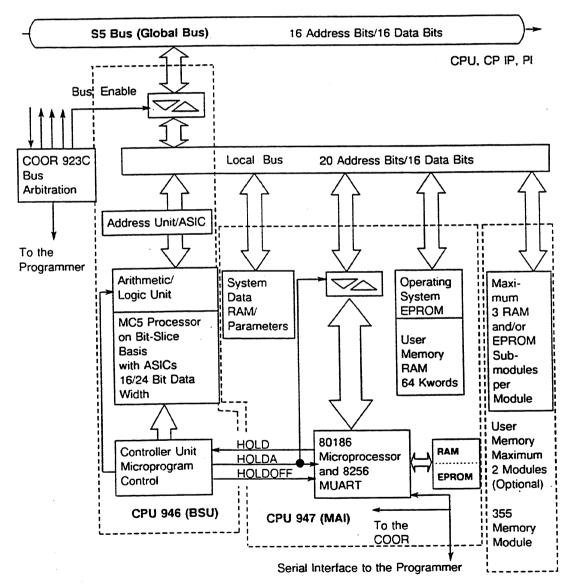

CPU 946/947 Product Summary

C79000-T8576-C647-01

#### CPU 946/947 Product Summary

The product summary provides an overview of the functions and characteristics of the CPU 946/947. It briefly describes general performance features and fields of application; the programming languages used are also mentioned.

#### Performance features

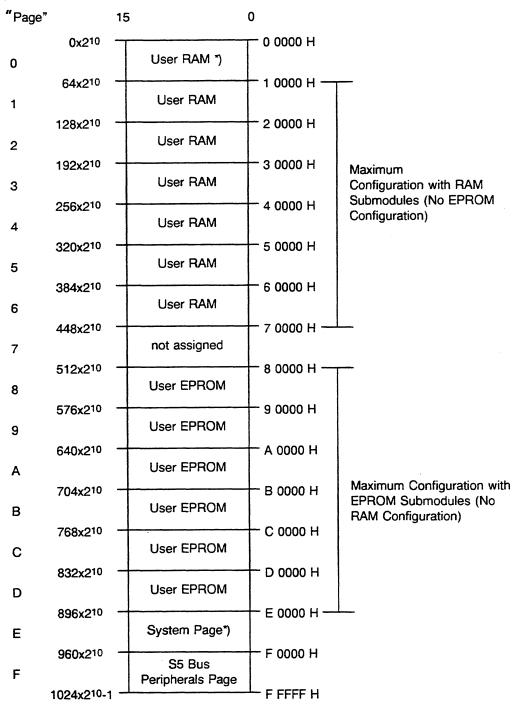

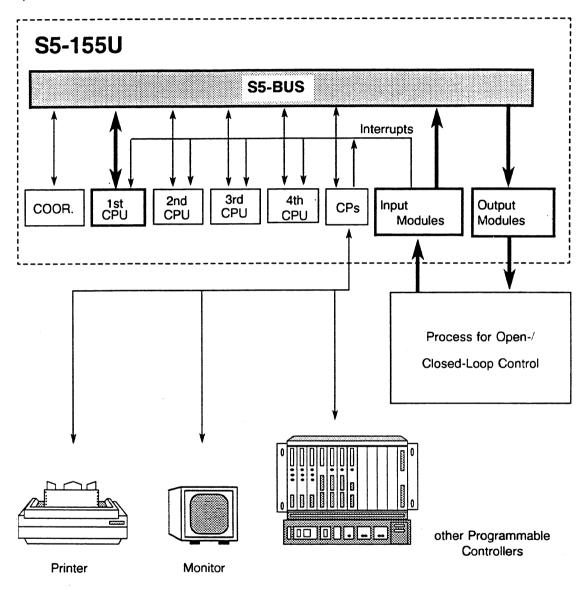

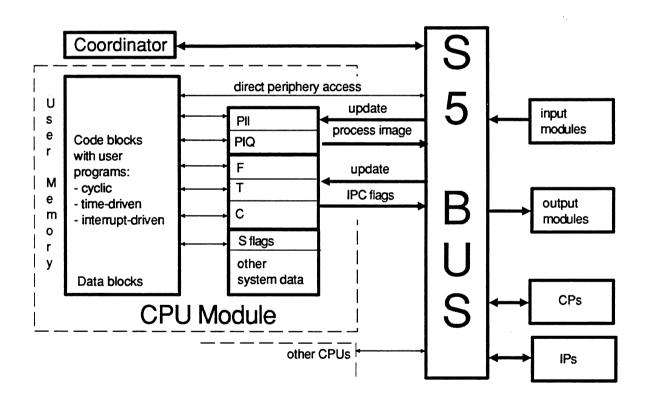

In the S5-155U programmable controller the CPU 946/947 can be used in single and in multiprocessor mode. It is designed for fast processing of all STEP 5 operations. With a maximum of 896 kbytes this CPU offers a large memory capacity.

The most outstanding features are:

Max. 896 kbyte memory for data and user programs, as RAM and/or EPROM. 128 kbyte RAMs are already integrated in the CPU.

| • |  | - | 2048  | flags    |

|---|--|---|-------|----------|

|   |  | - | 32768 | S flags  |

|   |  | - | 256   | timers   |

|   |  | - | 256   | counters |

| • | Processing from up to               | 4096                     | binary inputs/outputs                                                    | each                    |

|---|-------------------------------------|--------------------------|--------------------------------------------------------------------------|-------------------------|

|   | Via special interface modules up to | 192<br>520 000<br>32 000 | analog inputs/outputs<br>digital inputs/outputs<br>analog inputs/outputs | each<br>each or<br>each |

is possible.

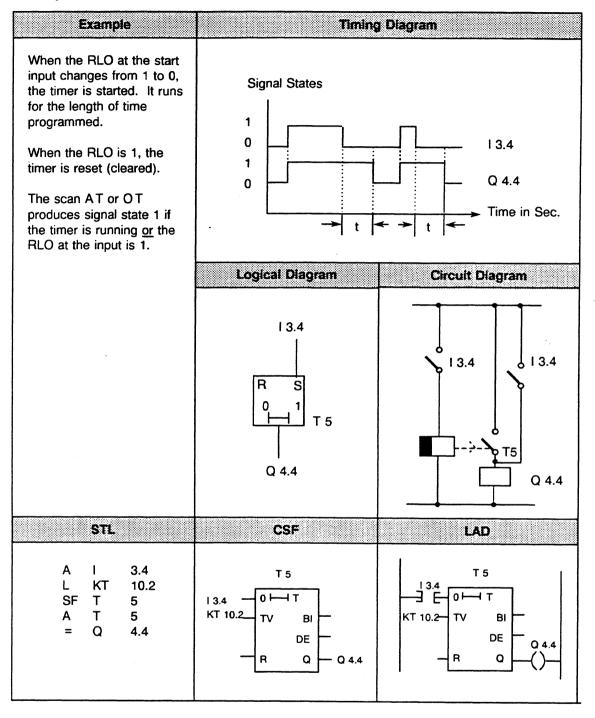

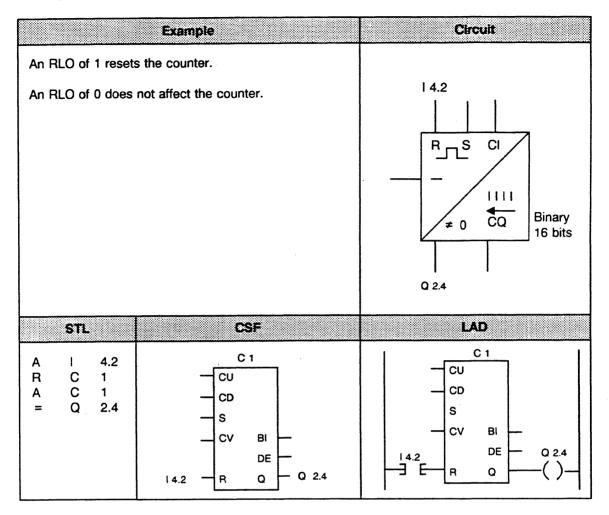

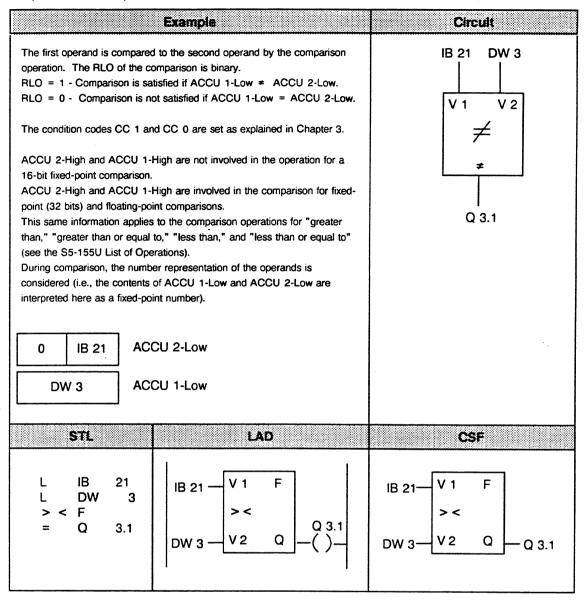

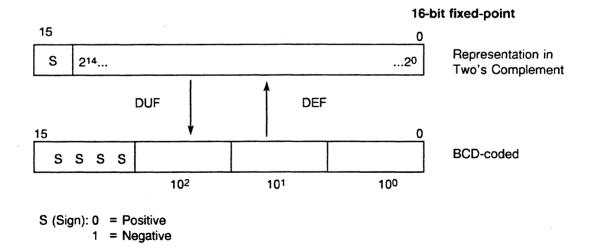

#### Programming language and program processing

Use the STEP 5 programming language /1/ to program the CPU 946/947. The types of representation for STEP 5 are the ladder diagram (LAD), control system flow chart (CSF) and statement list (STL). Furthermore GRAPH 5 is available which is used to program sequential controls (step sequences).

The CPU 946/947 allows user programs which are

- cyclic

- alarm-controlled

- time-controlled (max. 9 clock grids).

A hardware clock is also integrated.

The average processing time of 1K instructions is

- 1.4 ms for binary instructions

- 1.7 ms for command mix (60 % bits, 40 % words)

In the Programming Instructions in Part 9 of this manual you will find detailed information on programming the CPU 946/947. All operations and their running times are described in the Pocket Guide in Part 10 of this manual.

# SIEMENS

## **SIMATIC S5**

Programmable Controllers of the U Series

Installation Guide

C79000-B8576-C452-04

|                | Page                                                                                                                          |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| 1              | Introduction to Use of Installation Guidelines                                                                                |

| 2              | Fundamentals of EMC4                                                                                                          |

| 3              | Selection and Design of Cabinets 6                                                                                            |

| 3.1            | Selection Criteria                                                                                                            |

| 3.2            | Types of Cabinets                                                                                                             |

| 3.3            | Specifications When Designing a Cabinet8                                                                                      |

| 3.4            | Power Loss 10                                                                                                                 |

| 3.4.1<br>3.4.2 | Power Loss in Cabinet and Cabinet Cooling                                                                                     |

| 3.5            | Example of a Cabinet Design 12                                                                                                |

| 4              | Design and Connection of Power Supplies15                                                                                     |

| 4.1            | Internal Power Supply for Central Controllers and Expansion Units                                                             |

| 4.2            | Load Power Supply16                                                                                                           |

| 4.3            | Electrical Design with Process Peripherals17                                                                                  |

| 4.3.1          | Power Supply for CCs, EUs and Process Peripherals from Grounded Battery<br>or Grounded Power Supply Units                     |

| 4.3.2          | Power Supply for CCs, EUs and Process Peripherals from Centrally<br>Grounded Battery or Centrally Grounded Power Supply Units |

| 4.3.3          | Power Supply for CCs, EUs and Process Peripherals from Non-Grounded<br>Battery or Non-Grounded Power Supply Units             |

| 4.4            | Load Power Supply from Two Power Supply Units                                                                                 |

| 4.4.1<br>4.4.2 | Non-floating Modules                                                                                                          |

| 5              | Wiring Layout 23                                                                                                              |

| 5.1            | Wiring Layout Inside a Cabinet23                                                                                              |

| 5.2            | Wiring Layout Outside Cabinets24                                                                                              |

| 5.3            | Wiring Layout Outside Buildings 25                                                                                            |

| 5.4            | Equipotential Bonding                                                                                                         |

| 6   | Cabinet Wiring and Design with Respect to EMC         |

|-----|-------------------------------------------------------|

| 6.1 | Grounding of Inactive Metal Components                |

| 6.2 | Shielding of Devices and Cables                       |

| 6.3 | Use of Special Noise Suppression Measures             |

| 6.4 | Example of an EMC-compatible Cabinet Design           |

| 6.5 | Checklist for EMC-compatible Cabinet Design           |

| 7   | Framework and Wall Mounting of SIMATIC S5 Controllers |

| 8   | Lightning Protection Measures                         |

| 9   | Safety Measures                                       |

| 9.1 | Protection against Indirect Contact                   |

## **1** Introduction to Use of Installation Guidelines

This document is intended for planning, installation and commissioning engineers.

The installation guidelines are divided into the following sections:

- Chapter 1 Introduction to Use of Installation Guidelines

- Chapter 2 Fundamentals of EMC

This section provides a summary of the rules you must observe to ensure

electromagnetic compatibility.

- Chapter 3 Selection and Design of Cabinets This section lists criteria which must be considered when selecting the cabinet. The conditions resulting from the power loss of the modules used and the ambient temperature are considered in particular. The power losses of SIMATIC modules are listed.

- **Chapter 4** Design and Connection of Power Supplies This section provides information you must observe for the electrical connection of the power supply to CCs, EUs and process peripherals.

- **Chapter 5** Wiring Layout This section describes how you can achieve a high interference-resistance of your programmable controller by using a correct wiring layout.

- **Chapter 6** Cabinet Wiring and Design with Respect to EMC This section describes the measures required to ensure EMC of your programmable controller. It shows how you can prevent fundamental errors when designing and wiring cabinets. A checklist is provided to check the EMC-compatible cabinet design.

- Chapter 7 Framework and Wall Mounting This section describes what you must observe if you fit your SIMATIC controller in a framework or on a wall.

- Chapter 8 Lightning Protection Measures

This section provides information about the measures you should take to protect outdoor

cables and lines for SIMATIC devices from lightning strikes.

- Chapter 9 Safety Measures

This section provides a summary of the measures you must always take when planning

the use of programmable controllers in order to prevent danger during operation. The

regulations CENELEC HD 384.4.41 (IEC 364-4-41) (VDE 0100) and EN 60 204

(IEC 204-1) (VDE 0113) must be applied in order to carry out these measures.

We recommend that users who are using a SIMATIC S5 controller for the first time follow the installation guidelines right from the beginning when planning the control system. We strongly recommend that all users particularly observe the sections and paragraphs concerned with preventing danger (especially Chapter 9) and protection from sources of error (especially Chapter 6). Even if you are an experienced user, check your design using the checklist in Chapter 6.

## 2 Fundamentals of EMC

#### Definition of EMC

# Electromagnetic compatability (EMC) means that an electrical device is able to function correctly in a defined electromagnetic environment without disturbing other devices in its vicinity.

It is frequently sufficient to observe a few elementary rules to achieve electromagnetic compatibility (EMC). It is essential for you to observe the following four rules when installing your programmable controller.

## Rule 1: Make sure there is a perfectly functioning reference ground (central grounding point)

- Connect the central controller and expansion units to the central grounding point in a star-shaped configuration without loops.

- Protect the PLC from external influences by installing it in a cabinet or housing. Incorporate the cabinet or housing into the ground system.

- Shield electromagnetic fields resulting from inductors (transformers, motors, contactor coils) from the PLC using barriers (steel, highly permeable material).

- Use metal plug housings (not plastic) for screened data transmission lines.

#### Rule 2: Use a large-area ground.

- Connect all inactive metal components with a large-area contact and a low impedance.

- Establish a central connection between the inactive metal components and the central grounding point.

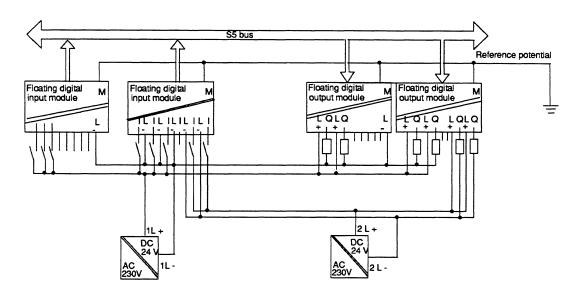

- The screw connections on inactive, painted metal components should be made using NOMEL contact washers <sup>1)</sup>.

- Do not forget to incorporate the screen bar into the ground system. This means that the screen bar itself must be connected to ground via a large-area contact.

- Aluminium components are unsuitable for grounding.

<sup>&</sup>lt;sup>1)</sup> Contact washer Siemens standard 70093 available from

<sup>-</sup> Siemens ANL A443 Werkzeug 8520 Erlangen

<sup>-</sup> Teckentrup GmbH und Co. KG, Postfach 120, D-5974 Herscheid 2,

<sup>-</sup> NOMEL S.A. Tour Franklin, Cedex 11, F-92081 Paris.

<sup>-</sup> or from your local Siemens representative

#### Rule 3: Plan the wiring layout and ensure that the plan is kept to

- Divide the cables into groups and route them separately. (power cables, power supply cables, signal lines, data lines)

- Always route power cables and signal cables in separate ducts or bundles.

- All the cables should only be fed into the cabinet from one side.

- Route the signal cables as close as possible to grounded components (e.g. cabinet members).

- We recommend the twisting of the forward and return lines of individually routed cables.

#### Rule 4: Ensure that your cables are well shielded

- Data transmission cables should be screened and connected at both ends.

- Analog cables should be screened and the screen connected at one or both ends.

- The cable screens must be connected at the cabinet inlet to the screen bar using a large-area contact and secured with clamps.

- Route the screen up to the module without interruptions.

## 3 Selection and Design of Cabinets

#### 3.1 Selection Criteria

The following criteria must be observed when selecting and dimensioning a cabinet:

- (i) Ambient conditions

- (ii) Quantity and type of power supplies and subracks to be used

- (iii) Total power loss of components present in the cabinet.

The ambient conditions present where the cabinet is located (temperature, humidity, dust, chemical influences) define the required degree of protection of the cabinet (IP XX) as shown in Fig. 1. Further information on degrees of protection can be found in IEC 529 and DIN 40050.

The required design of the cabinet is described in Section 3.3. Make sure that the maximum ambient temperature for the modules is not exceeded.

This involves both the ambient temperature outside the cabinet and the power loss in the cabinet.

It may be necessary to provide a fan or heat exchanger if the power loss is too high. A typical cabinet design is shown using an example at the end of the section.

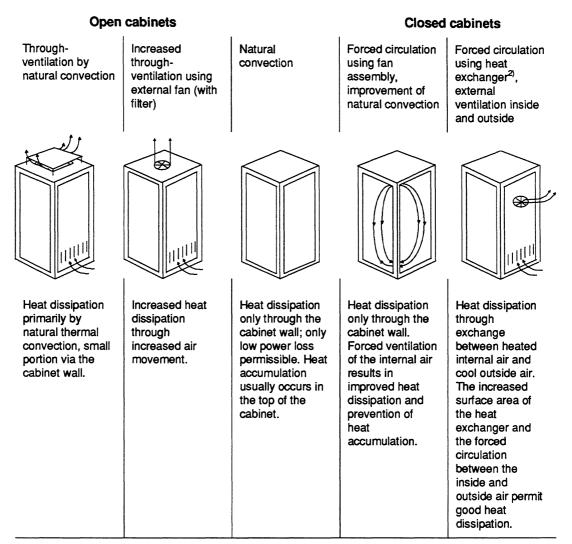

#### 3.2 Types of Cabinets

The following diagram shows a summary of the most common types of cabinet. It also shows the principle of heat dissipation used, the maximum achievable heat dissipation and the degree of protection.

Temperature difference between ambient temperature and cabinet temperature (measured at top in the cabinet): 20  $^{\circ}C^{4)}$

Power loss P<sup>3)</sup> with cabinet dimensions of 2200 mm x 600 mm x 600 mm

Installation as single unit:

| Up to approx.<br>700 W                   | Up to approx.<br>2700 W (approx.<br>1400 W with very<br>fine filter) | Up to approx.<br>260 W                   | Up to approx.<br>360 W                   | Up to approx.<br>1700 W                  |

|------------------------------------------|----------------------------------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| Degree of protection IP 20 <sup>1)</sup> | Degree of protection IP 20 <sup>1)</sup>                             | Degree of protection IP 54 <sup>1)</sup> | Degree of protection IP 54 <sup>1)</sup> | Degree of protection IP 54 <sup>1)</sup> |

#### Fig. 1 Types of cabinets

<sup>1)</sup> The location and the ambient conditions present there are decisive for selection of the type of cabinet protection (see IEC 529 and DIN 40050).

<sup>2)</sup> See Catalog NV21 for heat exchangers.

<sup>3)</sup> The values only apply if the guidelines for installation are adhered to (for further details refer to the following section).

4) If other temperature differences are present, refer to the temperature characteristics of the cabinet manufacturer.

### 3.3 Specifications When Designing a Cabinet

You must first define the components to be fitted in the cabinet. Then calculate the total power loss of the individual components. The following specifications must be observed:

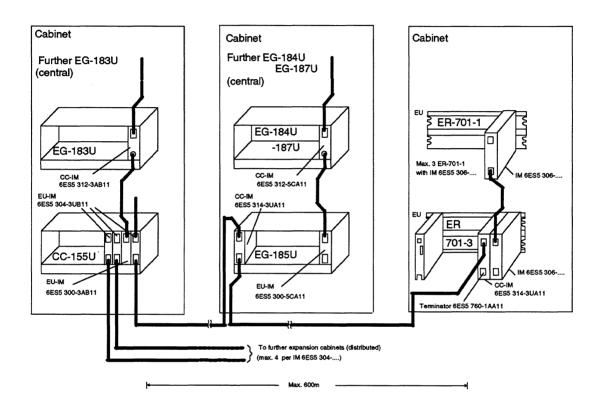

- The expansion units can be accommodated together with the respective central controller in one cabinet, or also in several cabinets (centralized or distributed). See Section 2 for the installation dimensions of the subracks.

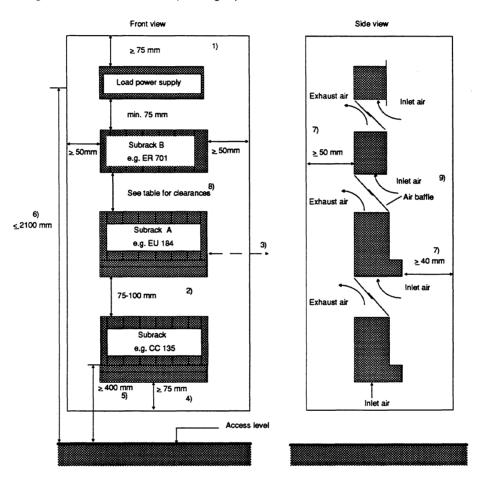

- As a result of the required spacing between devices and the maximum permissible installation height for control elements, a maximum of three U-type devices can be arranged one above the other (see Fig. 2).

Fig. 2 Installation dimensions for SIMATIC controllers in cabinet

- <sup>1)</sup> Min. 75 mm with closed cabinet roof. Smaller distances are possible with a perforated cabinet roof and an additional, separate ventilation roof.

- <sup>2)</sup> Min. 75 mm space for inlet air and exhaust air, max. 100 mm because of cable length between the CC/EU interface modules.

- <sup>3)</sup> Max. spacing of 400 mm possible (min. 50 mm) when connecting devices next to one another (with IM 312).

- <sup>4)</sup> Min. 75 mm from obstructions (large equipment) in the inlet air area.

- <sup>5)</sup> Min. installation height above access level 400 mm for control elements, 200 mm for connections.

- Max. installation height for control elements: 2100 mm to VDE 0106, Part 100, 2000 mm to EN 60 204 (IEC 204-1) (VDE 0113).

Reserve for single single time (400 mm does exhibit to an exhibit to a shift to an exhibit to an exhibit

- <sup>7)</sup> Space for air circulation (400 mm deep cabinets are sufficient).

- <sup>8)</sup> See Table 2-1 for the distances between subracks A and B.

- <sup>9)</sup> The installation of air baffles is recommended to provide a better air supply.

## Note:

$\Box$

The expansion unit with the largest power loss should be positioned as the top unit.

If subracks are combined (CC and EU), the clearances listed in Table 1 must be observed.

| Subrack A 1)  | Subrack B <sup>1)</sup> | Minimum<br>clearance | Maximum clearance                              |

|---------------|-------------------------|----------------------|------------------------------------------------|

| S5-135U/155U  | S5-135U                 | 75 mm                | Limited by the length of                       |

| or<br>S5-115U | S5-115U with fan        | 60 mm                | the connection cables to the interface modules |

| or<br>S5-100U | S5-115U without fan     | 100 mm               |                                                |

|               | S5-100U                 | 75 mm                |                                                |

#### Table 1 Required clearance between subracks

<sup>1)</sup> See Fig. 2, Installation dimensions for SIMATIC controllers in cabinet

If subracks from the S5-135U/155U series are used together with subracks of the S5-115U in the same cabinet, ensure that the rear panels of the subracks have the same clearance to the rear panel of the cabinet. This results in improved air circulation.

## 3.4 Power Loss

## 3.4.1 Power Loss in Cabinet and Cabinet Cooling

The power loss that can be dissipated from a cabinet depends on the cabinet design, its ambient temperature and the arrangement of units in the cabinet.

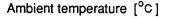

Fig. 3 shows the permissible ambient temperature of a cabinet with dimensions of 600 mm x 600 mm x 2200 mm depending on the power loss. The values indicated only apply to the arrangement of units in the cabinet as shown in Fig. 2. You can obtain more information from Catalogs NV21 and ET1.

Curve 1 Cabinet (open) with through-ventilation by natural convection. Curve 2 Closed cabinet with natural convection and internal forced circulation using fan.

Curve 3 Closed cabinet with heat exchanger. Heat exchanger size 11/6 (920 mm x 460 mm x 111 mm).

Fig. 3 Maximum cabinet environment temperature depending on the power loss

## Note:

When fitting the subracks of the S5-135U/155U series, the maximum power loss which can be dissipated by the fans must not be exceeded. The max. dissipated power loss per unit with an inlet temperature of 55 °C is

250 W. This value is increased by 20 W for each reduction in the inlet temperature by 1  $^{\circ}$ C.

#### Caution:

Modules with a hard disk drive can only be used up to an ambient temperature of 50  $^{\circ}$ C.

## 3.4.2 Example of Calculating Cabinet Type

The following example shows the maximum permissible ambient temperature for different types of cabinet with the same power loss.

Example:

The following configuration is present:

| Total power loss:                                          | 900 W |

|------------------------------------------------------------|-------|

| 1 load power supply, 24 V/40 A, 6EV1 362-5BK00 (full load) | 200 W |

| 2 expansion units, each with 250 W power loss              | 500 W |

| 1 central controller                                       | 200 W |

Fig. 3 shows the max. ambient temperatures for a total power loss of 900 W:

| Cabinet design (see Fig. 1)                            | Max. ambient temperature |

|--------------------------------------------------------|--------------------------|

| Closed, with natural convection and forced circulation | (use not possible)       |

| Open with through-ventilation                          | Approx. 33 °C            |

| Closed, with heat exchanger                            | Approx. 42 °C            |

| Framework/wall                                         | Max. 55 °C               |

The power losses of the modules can be found in the technical data in the catalogs or in the manuals.

If these values are not listed in the technical data, they can be calculated easily from the power consumption. To do this, multiply the value of the power consuption by the appropriate voltage.

#### Examples:

| ٠ | CPU 928B: | power consumption | 4 A/5 V                              | ······   | power loss = 20 W         |

|---|-----------|-------------------|--------------------------------------|----------|---------------------------|

| • | CP 143:   | power consumption | 4 A/5 V<br>0.5 A/15 V<br>0.04 A/24 V | <b>-</b> | power loss approx. 21 V   |

| ٠ | IM 304    | power consumption | 1.5 A/5 V                            |          | power consumption = 7.5 W |

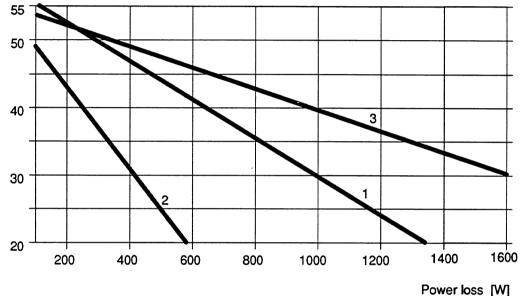

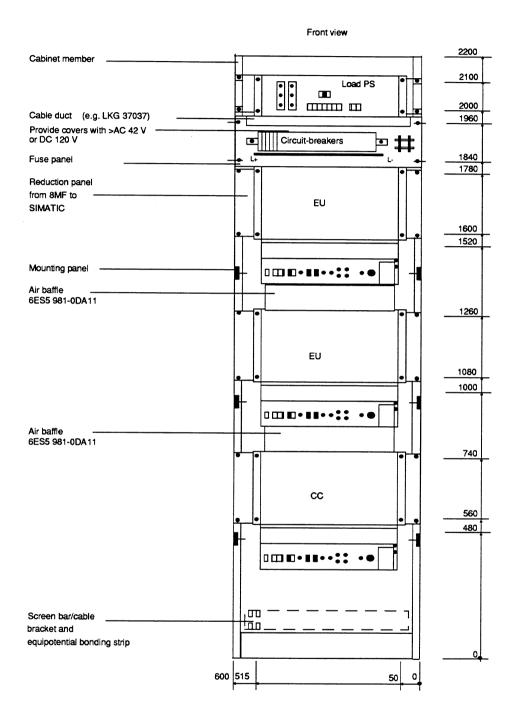

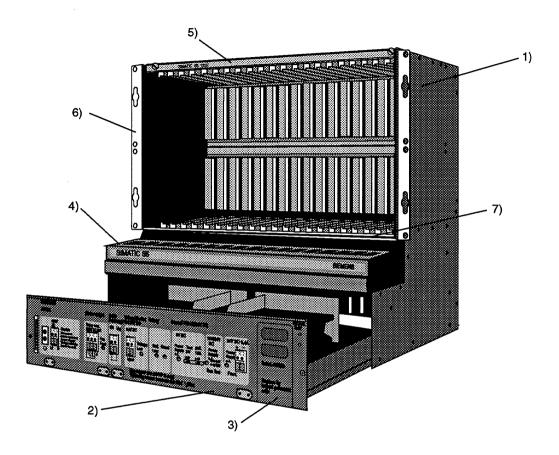

#### 3.5 Example of a Cabinet Design

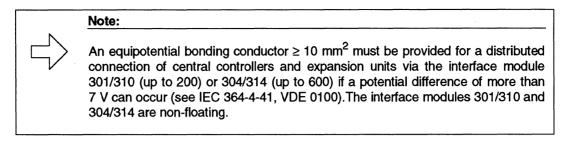

Figs. 4 and 5 show a design using the example of a metric 8MF cabinet (2200 mm x 600 mm x 600 mm). This design has a number of advantages:

- Universal application

- Independent of the cabinet width (550 to 1200 mm possible)

- The units can be installed asymmetrically; you thus gain more space on one side for routing signal cables.

- All devices can be installed and removed from the front, even after initial installation. The M6 screws must be premounted on the 19-inch cabinet member at the correct mounting height. You can then hook in the subrack and tighten the screws (one-man installation)

- The separate cable routing for analog, digital and power supply lines in cable ducts increases the resistance to mutual interferences between the signals.

Fig. 4 Front view of 8MF cabinet

C79000-B8576-C452-04

Side view from left

Side view from right

.

Fig. 5 Side views of 8MF cabinet

## 4 Design and Connection of Power Supplies

The following section provides information you must observe for the electrical connection of the power supply.

Different power supplies are required for SIMATIC S5 systems:

• Internal power supply for central controllers and expansion units

The internal power supply of the SIMATIC modules is obtained from power supply units in the form of plug-ins. These power supply units are fixed components of the CC and the EU. You can find their technical data in the Instructions of the respective units and in the catalogs.

• Load power supply for the I/O modules as well as sensors and actuators.

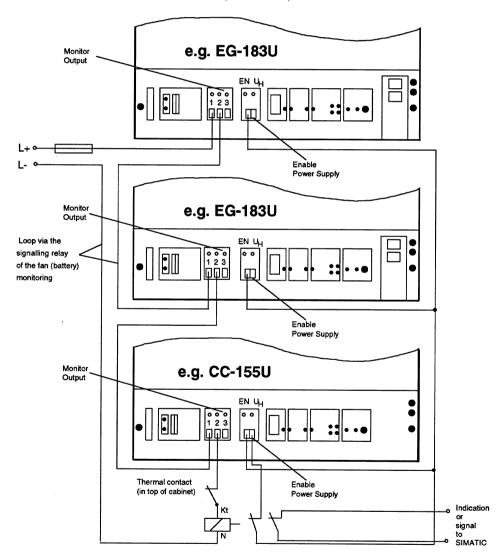

#### 4.1 Internal Power Supply for Central Controllers and Expansion Units

The power supplies fitted in the CCs and EUs deliver the internal DC voltages of 5 V, 15 V and 24 V from the input voltage of 120/230 V AC or 24 V DC.

When equipping the CCs and EUs, ensure that the rated current of the respective power supply is not exceeded. You can find the current consumption of the individual modules with the 5 V supply e.g. in the catalogs and the Instructions of the respective module (Technical Data).

Floating and non-floating power supplies are available for the input voltage of 24 V DC.

The permissible input voltage for power supplies with a rated input voltage of 24 V DC is:

• Static DC 20 to 30 V.

The permissible input voltage is as follows for power supplies with a rated input voltage of 230/120 V AC:

- With rated voltage 230 V: 187 to 253 V AC

- With rated voltage 120 V: 93 to 127 V AC.

#### 4.2 Load Power Supply

The series 6EV 13.. power supply units from Siemens (output currents 20 and 40 A) can be used to supply the I/O modules as well as the CC and EU power supplies with the input voltage of 24 V DC. Detailed information can be found in Catalog ET1.

The following must be observed when dimensioning load power supplies for digital output modules (S5-135U/155U series):

- To protect the cables and lines from overcurrents and to protect the modules from short-circuits, additional fuses are present on the modules in addition to the electronic short-circuit protection (in the power supply). The fuses also serve as protection if the power supply connections are reversed.

- The electronic short-circuit protection for digital outputs only responds when 2-3 times the rated current is exceeded. You should therefore make sure that the load power supply can supply the current required to trigger the short-circuit protection of an output.

- Note when selecting the load power supply, and taking into consideration all connected output loads, that two to three times the rated output current can flow briefly at the output in the event of a short-circuit before the pulsed electronic short-circuit protection takes effect. This excess current is generally present with non-regulated load power supply units.

- In the case of regulated load power supply units, especially with small output currents up to 20 A, the rated output current of the load power supply must be dimensioned such that several times the rated current can flow in the event of a short-circuit.

### Caution:

Safe electrical isolation according to CENELEC HD 384.4.41 (IEC 364-4-41) Part 4 (VDE 0100) or VDE 0160 must be guaranteed with all power supply units used for SIMATIC S5 devices and modules. All electrically-isolated Siemens power supplies of the 6EV13... series satisfy this condition.

### 4.3 Electrical Design with Process Peripherals

The following section shows various designs of power supplies for CCs, EUs and process peripherals.

The following are possible:

- Grounded power supply

- Centrally grounded power supply

- Non-grounded power supply.

You must observe the following fundamental points when designing the electrical configuration of the process peripherals:

- A master switch (to VDE 0113)<sup>1)</sup> or a disconnection facility (to VDE 0100)<sup>2)</sup> must be provided for the CC, EU and load power supply.

- For DC 24 V load circuits you require a load power supply with guaranteed electrical isolation. Non-regulated load power supplies must be provided with a capacitor (dimensioning: 250 μF per 1 A load current). This means you must connect a capacitor in parallel to the output terminals.

- Electrical isolation by means of a transformer (to VDE 0113<sup>1)</sup> Section 6.1.1 and VDE 0100<sup>2)</sup>) is recommended for load circuits for supplying external control devices with electromagnetic operating coils (e.g. more than 5).

- The circuits for the sensors and actuators can be used in groups.

- To protect against parasitic voltages, the subracks must be connected together with a large-area contact and low impedance.

1) VDE 0113 is equivalent to EN 60 204, IEC 204-1

2) VDE 0100 is equivalent to CENELEC HD 384.4.31 (IEC 364-4-41).

#### 4.3.1 Power Supply for CCs, EUs and Process Peripherals from Grounded Battery or Grounded Power Supply Units

The ground of the internal supply voltages is connected to the subrack housing. Grounded operation provides the best noise immunity.

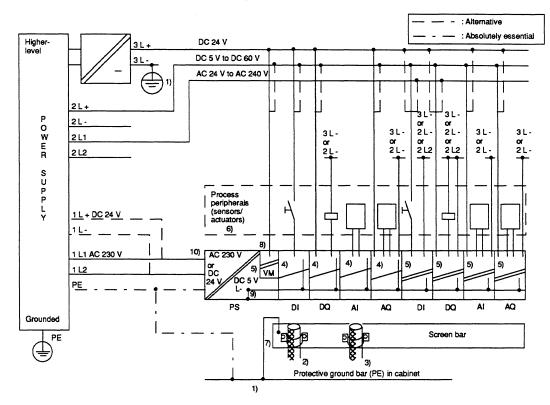

Fig. 6 Possible connections for sensors/actuators of the process peripherals to grounded power supply units

- Housing potential (cabinet potential) = protective ground conductor. 1)

- Use cable screen, if available, for digital modules. Provide screening with longer cables; connect at one end 2) to cabinet inlet or connect at both ends.

- 3) Connect cable screen at one end to cabinet inlet with analog modules or also at both ends; lead on up to module.

- 4) Non-floating module.

- 5) Floating module.

- 6) 7) Protective ground conductor required to housings of sensors and actuators.

- Connection cable with as large a cross-section as possible (black) > 16 mm<sup>2</sup>; if the screen is used as the protective ground conductor (green/yellow), connect at both ends.

- 8) Only with S5-135U/155U series: monitoring of load voltage L+ (24 V DC).

- Non-removable connection between the internal ground of the supply voltages and the housing. 9) Particularly important:

- Electrical isolation is not available with the power supply unit 24 V/10 A (order no. 10)

- 6ES5 955-3NA12); operation is only possible without problems on grounded power supply unit.

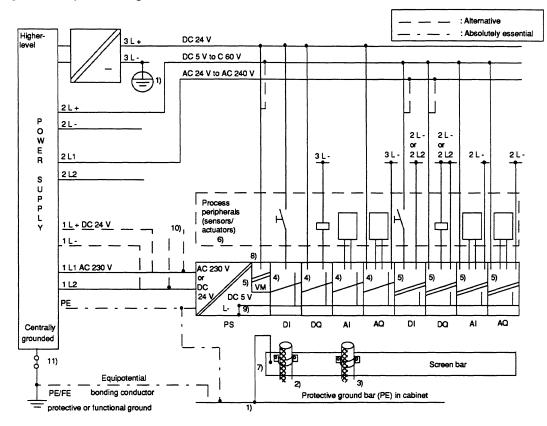

## 4.3.2 Power Supply for CCs, EUs and Process Peripherals from Centrally Grounded Battery or Centrally Grounded Power Supply Units

If SIMATIC S5 programmable controllers are to be installed where a central grounding is available, then proceed as shown in Fig. 7. This is, however, not as immune to noise as the grounded system in Fig. 6.

- 1) Housing potential (cabinet potential) = protective ground conductor.

- Use cable screen, if available, for digital modules. Provide screening with longer cables; connect at one end to cabinet inlet or connect at both ends.

- Connect cable screen at one end to cabinet inlet with analog modules or also at both ends; lead on up to module.

- 4) Non-floating module.

- 5) Floating module.

- 6) Protective ground conductor required to housings of sensors and actuators; can be omitted for safely generated functional extra-low voltages.

- Connection cable with as large a cross-section as possible (black) > 16 mm<sup>2</sup>.

- 8) Only with S5-135U/155U series: monitoring of load voltage L+ (24 V DC).

- 9) Non-removable connection between the internal ground of the supply voltages and the housing.

Particularly important:

- Electrical isolation is not available with the power supply unit 24 V/10 A (order no. 6ESS 955-3NA12); operation on a centrally grounded power supply unit is therefore not directly possible. Voltage supply required via 3L+/-.

- 11) Removable connection for test purposes.

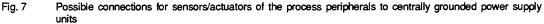

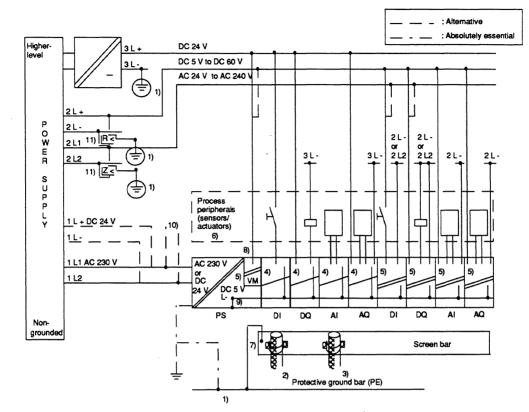

#### 4.3.3 Power Supply for CCs, EUs and Process Peripherals from Non-Grounded Battery or Non-Grounded Power Supply Units

Possible connections for sensors/actuators of the process peripherals to non-grounded power supply units Fig. 8

- 1) Housing potential (cabinet potential) = protective ground conductor.

- Use cable screen, if available, for digital modules. Provide screening with longer cables; connect at one end 2) to cabinet inlet or connect at both ends.

- 3) Connect cable screen at one end to cabinet inlet with analog modules or also at both ends; lead on up to module.

- 4) Non-floating module.

- 5) Floating module.

- Protective ground conductor required to housings of sensors and actuators; can be omitted for safely 6) generated functional extra-low voltages.

- 7) Connection cable with as large a cross-section as possible (black); if the screen is used as the protective ground conductor (green/yellow), connect at both ends. Only with S5-135U/155U series: monitoring of load voltage L+ (24 V DC).

- 8)

- Non-removable connection between the internal ground of the supply voltages and the housing. 9) Particularly important:

- Electrical isolation is not available with the power supply unit 24 V/10 A (order no. 10) 6ES5 955-3NA12); operation on a centrally grounded power supply unit is therefore not directly possible. Voltage supply required via 3L+/-.

- Insulation monitoring equipment is required if dangerous conditions could result through double 11) faults and/or with voltages > 42 V AC or 120 V DC. Only one insulation monitor is required per supply unit (to VDE 0113 Section 6.2.2).

## 4.4 Load Power Supply from Two Power Supply Units

The design of the load power supply using two power supply units enables you to specifically disconnect parts of the process peripherals. The inputs and outputs of different modules can be assigned as a group to one power supply unit.

The supply to inputs and outputs of different modules from two power supply units is indicated below using two examples.

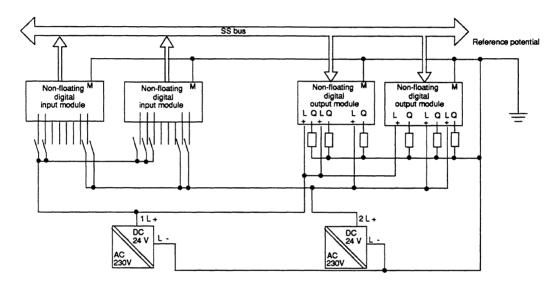

#### 4.4.1 Non-floating Modules

In the case of non-floating input/output modules it must be ensured that the negative poles (L-) of the power supply units are connected to the reference potential (SIMATIC device/cabinet housing). This is necessary since the inputs are referred to ground.

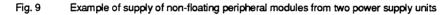

## 4.4.2 Floating Modules

In the case of floating modules, the inputs or outputs can be supplied from two power supply units by dividing into isolated groups.

Note that electrical isolation between the groups is lost as a result of the connection of inputs or outputs of two floating groups to one power supply unit.

Fig. 10 Supply of floating peripheral modules from two power supply units

When using CCs and EUs with a mains connection, we recommend a Siemens power supply unit from the 6EV13.. series with electrical isolation as the power supply for the process peripherals (load voltage).

## 5 Wiring Layout

You can achieve a high noise immunity for your programmable controller by using a correct wiring layout. The measures required are described in the following sections.

#### 5.1 Wiring Layout Inside a Cabinet

To ensure a correct layout of wiring inside cabinets, the wiring must be divided into the following groups:

- Group A: screened data lines (for PG, OP, SINEC L1, CP 525 etc.) screened analog lines screened signal lines for DC and AC voltages  $\leq$  400 V non-screened lines for DC and AC voltages  $\leq$  60 V

- Group B: non-screened lines for DC and AC voltages > 60 V and  $\leq$  400 V

Group C: non-screened lines for DC and AC voltages > 400 V and  $\leq$  1 kV

Route all wiring groups separately in the cabinet. Separately means that the wiring is routed in

- separate cable ducts

- separate wiring bundles with approx. 10 cm clearance.

When laying screened lines (e.g. analog lines) make a large-area contact of the screen to a cable clamping rail at the inlet to the cabinet and connect the screen further to the final point without an interruption (see Section 6.4).

## 5.2 Wiring Layout Outside Cabinets

• Route the cables outside cabinets and within buildings on metal cable trays. Make a conductive connection between the ends of two adjacent cable trays and connect these to ground at distances of 20 to 30 m.

The following may be routed on the same cable trays (cable routes, gutters, channels):

- cables from group A and

- cables from group B with approx. 10 cm clearance.

Route cables in group C on separate cable trays (cable routes, conduit).

- Always screen analog lines.

- Non-screened cables (e.g. signal lines, power supply lines) must be routed with as large a clearance from sources of interference (contactor, transformer, motor, electric welding unit) as possible.

- Signal lines and associated equipotential bonding lines should be routed with the smallest possible distance from one another and on the shortest path.

- Lines between the programmable controller and sensors/load should be installed whenever possible without breaks. If a break in the line is unavoidable, screen the terminal block e.g. with a metal box making large-area contact to a screen bar.

- Route associated single lines (e.g. forward and return lines, power supply cables) as close as possible to one another. If possible these lines should be twisted.

Signal lines and power cables up to 1 kV must be routed separately but can be routed in parallel. A minimum clearance of 10 cm must be observed. The clearance should be increased proportionally with higher voltages, and the safety regulations must be observed (e.g. IEC 664/664A).

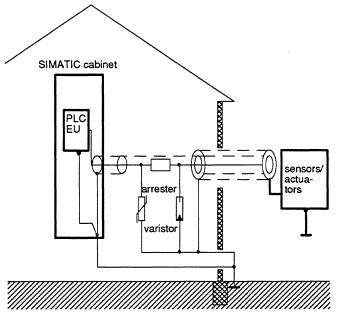

#### 5.3 Wiring Layout Outside Buildings

- If you route cables outside buildings, a double-screened cable must always be used for analog and data signal transmissions.

- The following must be observed when routing double-screened cables:

- connect the outer screen to ground at both ends

- only connect the inner screen at one end to the receiver side.

- Ensure that the equipotential bonding is sufficient. Connect an equipotential bonding conductor if necessary.

- The lightning protection and grounding regulations must be observed.

## 5.4 Equipotential Bonding

Different potentials can occur between different parts of your plant (e.g. different power supplies). These differences can be reduced by laying equipotential bonding lines to ensure the correct functioning of electronic components.

Keep the following points in mind when laying an equipotential bonding line:

- The effectiveness of equipotential bonding is directly related to the impedance of the line (less impedance greater effectiveness). This means that the connection required for equipotential bonding must have not only a low ohmic resistance but also as small an inductance as possible (achieved by keeping line lengths short).

- If screened signal lines with the screens grounded at both ends are required between parts of the plant, the impedance of the additional equipotential bonding line must not exceed a maximum of 10% of the screen impedance.

- The cross-sectional area of the equipotential bonding line must be selected for the max. equalizing currents.

- The equipotential bonding line must be laid so that loops (e.g. between equipotential bonding line and signal lines) cover as small an area as possible.

- The equipotential bonding line must make large-area contact with ground or chassis (see Section 6.4)

## 6 Cabinet Wiring and Design with Respect to EMC

EMC: electromagnetic compatibility (EMC) is understood to be the ability of an electric device to function without faults in a defined electromagnetic environment without influencing other devices in the environment.

Measures to guarantee EMC must already be made when designing and wiring the individual components in cabinets. The interfering environment must not be ignored if fault-free functioning of the programmable controller and wiring is to be obtained.

The measures required to guarantee EMC, as well as an example of a cabinet design as concerns EMC, are described in the following sections. The check list at the end of this section serves as an aid for checking the EMC-compatible design of your cabinet.

The following section as well as Section 5.1, Wiring Layout Inside a Cabinet, must be observed when designing your cabinet to guarantee EMC. These sections handle the subjects:

- Grounding of all inactive metal components

- Wiring layout in the cabinet

- Shielding of devices and cables

- Use of special interference-suppression measures.

### 6.1 Grounding of Inactive Metal Components

An important factor which contributes towards interference-free operation is consistent grounding. Grounding is understood to be the electrical connection of all inactive metal components (VDE 0160). Large-area grounding must always be used.

Large-area grounding means:

• Ground all conducting parts. These include subracks, cabinet members, cabinet panels, cabinet doors, screen bars, filter housings.

Measures to be observed when grounding:

- Make all ground connections with a low impedance.

- Connect all metal parts with a large-area contact.

- Use ground straps for the connection. Metallic wire mesh made of tin-plated copper strands is suitable as the ground strap. It should be kept as short as possible. The surface area of the ground straps is decisive, and not the cross-section, because of the high-frequency noise pulses discharged.

- Make the screw connections using NOMEL contact washers<sup>1)</sup>.

- <sup>1)</sup> Contact washer Siemens standard 70093 available from

- Siemens ANL A443 Werkzeug 8520 Erlangen

- Teckentrup GmbH und Co. KG, Postfach 120, D-5974 Herscheid 2,

- NOMEL S.A. Tour Franklin, Cedex 11, F-92081 Paris.

- or from your local Siemens representative

## 6.2 Shielding of Devices and Cables

Shielding is a way of attenuating (dampening) magnetic, electric or electromagnetic interferences. Shielding can be divided into:

#### **Device shielding**

Cabinets and housings must be incorporated into the measures for shielding the programmable controllers. The following must be observed:

- Cabinet enclosures such as side panels, rear walls, roof and floor panels must be connected sufficiently often with a low impedance in the case of an overlapping arrangement (connection interval e.g. 50 mm).

- Doors must additionally be connected to the cabinet ground. Use at least 2 ground straps.

- If sources of strong interference are present in the cabinet (transformers, cables to motors etc.), these must be isolated from sensitive electronics areas by metal partitions (steel, highly permeable material, e.g. mu-metal). The panels must be screwed several times to the cabinet ground with a low impedance.

The central grounding point must be connected to the protective ground conductor (grounding bar) with a low impedance and a Cu conductor  $\ge 16 \text{ mm}^2$  as short as possible.

#### Cable screening

Screened cables must be connected at both ends to the grounding bar with a large-area contact and if possible directly at the cabinet inlet. Good attenuation of all conducted frequencies can only be achieved by connecting at both ends.

The following must be observed when handling the screen:

- Use metal cable clamps to secure the braided screens with a large-area contact.

- Avoid the use of cables with foil screens since the foil can be easily damaged by tension or pressure when fitting, thus leading to a poorer screening effect.

#### Note:

An equalizing current may flow via the screen connected at both ends in the case of variations in the ground potential. Use an additional equipotential bonding conductor in this case (see Section 5.4 Equipotential Bonding).

In certain cases the screen can also be connected at only one end. Only the lower frequencies are then attenuated. Connection of the screen at one end may be more favorable if:

- An equipotential bonding conductor cannot be laid

- Analog signals (several mV or μA) are transmitted.

Interferences on cable screens are discharged to ground via the grounding bar and the equipotential bonding conductor. A low-impedance path to ground for the interfering currents must be provided so that these discharged currents do not produce a source of interference themselves:

- Tightly connect the screws of cable plugs, modules and equipotential bonding conductors.

- Protect the contact surfaces of equipotential bonding conductors and ground lines from corrosion.

## 6.3 Use of Special Noise Suppression Measures

#### **Connection of inductors**

Provide suppression (e.g. using RC elements, varistors or free-wheeling diodes) for inductors installed in the same cabinet (e.g. contactor and relay coils) not activated by SIMATIC S5 modules.

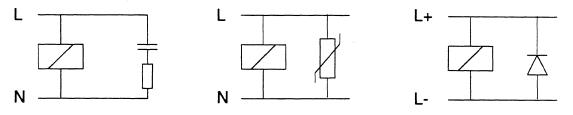

Fig. 12 Wiring inductors (example)

If further contacts are connected in series to SIMATIC outputs, the SIMATIC internal fusing is not effective. In such cases the inductor must be fused directly.

#### Protection against electrostatic discharge

Use metal housings or cabinets that are closed in at all sides to protect devices and modules against electrostatic discharge. Connect these housings or cabinets to the grounding point where you set them up so as to form a good contact.

Caution:

If you must work on the system with the cabinet open, follow the guidelines to protect electrostatically sensitive devices and modules (ESD).

The interference resistance is always reduced when the cabinet is open.

#### Mains power connection for programmers

Provide a grounded socket in each cabinet to supply power for a programmer. The sockets should be connected to the distribution board to which the protective ground conductor of the cabinet is also connected.

#### **Cabinet illumination**

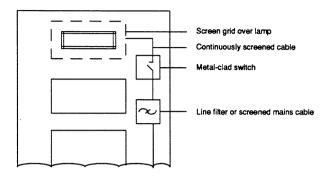

Do not use fluorescent lamps for the cabinet illumination since these generate interferences. If you must use fluorescent lamps, take the precautions shown in Fig. 13 LINESTRA<sup>®</sup> lamps are more suitable.

Fig. 13 Measures to suppress noise from fluorescent lamps in a cabinet

## 6.4 Example of an EMC-compatible Cabinet Design

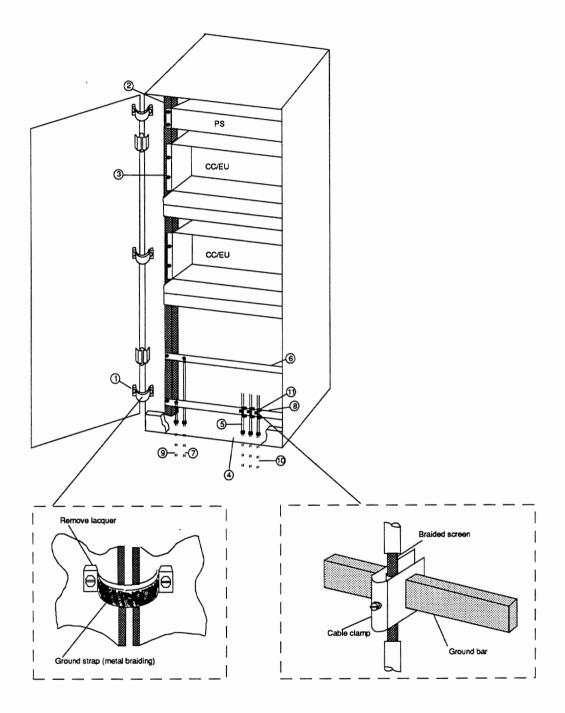

The example of a cabinet design shown in Fig. 14 - taking into consideration EMC - shows the grounding of all inactive metal components and the connection of screened cables. This example only applies to grounded operation. Observe the points listed in Fig. 14 during installation.

Fig. 14 Example of an EMC-compatible cabinet design

#### Re 1. Ground straps

All inactive metal components (e.g. cabinet doors and supporting panels) must be connected using ground straps if large-area metal-metal connections are not present. Metallic wire mesh made of tin-plated copper strands is suitable as the ground strap. It should be kept as short as possible, with a ratio between the length and width of less than 3 to 1.

#### Re 2. Cabinet members

The cabinet members must be connected to the cabinet housing with a large-area contact (metal-metal connection).

#### Re 3. Mounting bracket

A large-area metal-metal connection must be made between the cabinet member and mounting bracket.

#### Re 4. Base panel

A large-area metal-metal connection to the cabinet housing must be guaranteed.

#### Re 5. Cable screwed glands

Unused cable screwed glands must be closed using blanking plates in the case of closed cabinets with heat exchangers.

#### Re 6. Equipotential bonding bar

The bar must be connected to the cabinet members with a large-area contact (metal-metal connection).

#### Re 7. Equipotential bonding conductor

The conductors must be connected to the equipotential bonding bar.

#### Re 8. Ground bar

This serves as the central grounding point of the cabinet and must be connected to the cabinet members with a large-area contact (metal-metal connection). The ground bars must be connected to the external central grounding point to guarantee discharging of interfering and fault currents. It can additionally be used to connect screened cables.

#### Re 9. Cable from central grounding point

The cable must be connected to the grounding bar with a large-area contact.

#### Re 10. Signal cables

The screen of screened signal cables must be connected to the grounding bar with a large-area contact using cable clamps or to an additional screen bar connected with a large-area contact, and then routed further to the end point (e.g. I/O module) without interruption.

#### Re 11. Cable clamp

The cable clamp must enclose the braided screen over a large area.

# 6.5 Checklist for EMC-compatible Cabinet Design

| EMC measures                                                                                                   |                          | Remarks |

|----------------------------------------------------------------------------------------------------------------|--------------------------|---------|

| Connection of inactive components                                                                              | (Section 6.1)            |         |

| Are all inactive metal components connected t<br>large-area contact and low impedance, and gr                  |                          |         |

| Is there a sufficient connection to the central g                                                              |                          |         |

| Screw connections made using NOMEL conta                                                                       |                          |         |

| Particularly check the connections to:<br>• Subracks<br>• Cabinet members<br>• Cabinet bar<br>• Filter housing |                          |         |

| Equipotential bonding                                                                                          | (Section 5)              |         |

| With a spacially separated design, check the r<br>equipotential bonding conductor                              | outing of the            |         |

| Device screening                                                                                               | (Section 6.2)            |         |

| All cabinet components provided with contacts                                                                  | at sufficient intervals? |         |

| Doors connected to the cabinet body using gro                                                                  | ound straps?             |         |

| Are only metallic device plugs used?                                                                           |                          |         |

| Cable screening                                                                                                | (Section 6.2)            |         |

| Are all analog cables screened?<br>Are screens connected at both ends?                                         |                          |         |

| Are cable screens connected to ground bar or inlet?                                                            | screen bar at cabinet    |         |

| Are cable screens connected via cable clamps<br>contact, completely enclosed and with a low in                 |                          |         |

| Inductors                                                                                                      | (Section 6.3)            |         |

| Are isolating panels used in event of magnetic inductors?                                                      | influences from          |         |

| Are all coils of contactors connected to RC ele                                                                | ements?                  |         |

Table 2 Checklist for EMC-compatible cabinet design

| EMC measures                                          | Remarks                         |

|-------------------------------------------------------|---------------------------------|

| Cable routing                                         | (Section 5)                     |

| Cabling divided into groups?                          |                                 |

| Power supply cables (230 V) and sig ducts or bundles? | nal cables routed in separate   |

| Complete cabling introduced into cab                  | inet at one position?           |

| Signal cables routed close to ground                  | ed surface?                     |

| Forward and return lines of individua possible?       | ly routed conductors twisted if |

Table 2 Checklist for EMC-compatible cabinet design (continued)

C79000-B8576-C452-04

## 7 Framework and Wall Mounting of SIMATIC S5 Controllers

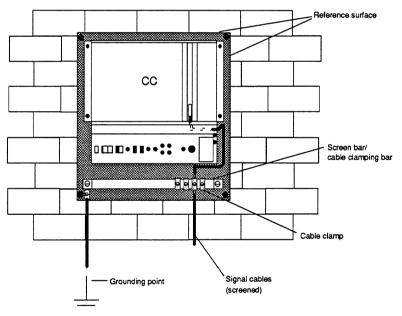

If you operate your SIMATIC controllers in a environment which is free from interferences to the greatest possible extent, you can fit the central controllers and expansion units on a framework or directly on a wall.

The following must be observed:

- A reference surface made of sheet-steel should be provided to improve the deviation of interfering currents conducted via the inlet cables. This reference surface must be at least 480 mm x 250 mm large and connected to the central grounding point. If you use screening or cable clamping rails, space must be provided for these on the reference surface. In the case of framework mounting, the metal frame serves as the reference surface.

- Fit the screen bar or cable clamping bar to this reference surface or to the framework. Ensure that the connection between the rails and the reference surface or framework is made with a large-area contact and low impedance (metal-metal connection).

- Connect all inactive metal components together with a large-area contact and low impedance. Inactive metal components are: subrack, power supply, reference surface, screen bar, protective ground bar.

- Also observe the points for the wiring layout (see Section 5).

Fig. 15 Wall mounting

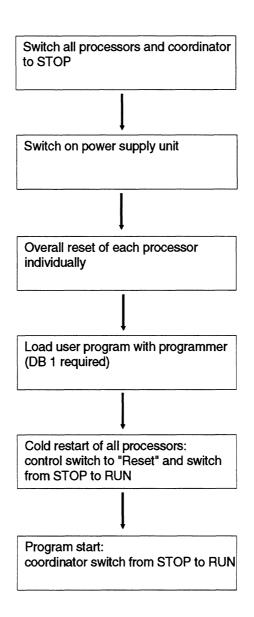

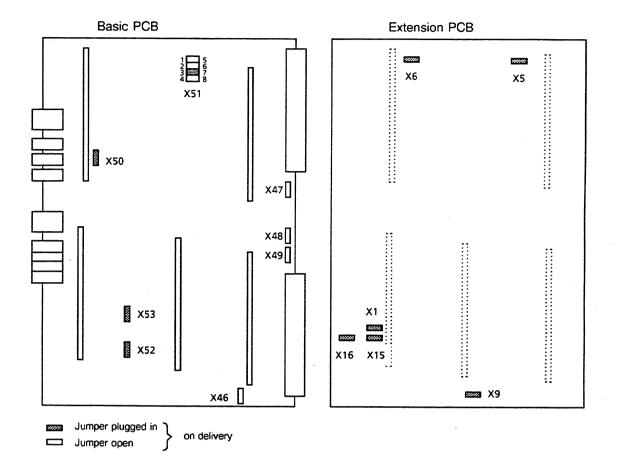

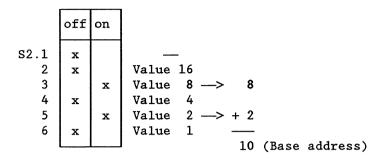

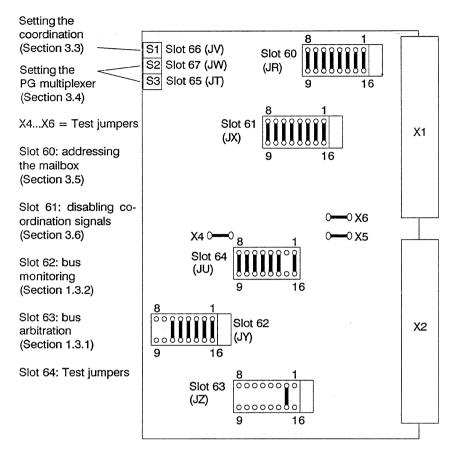

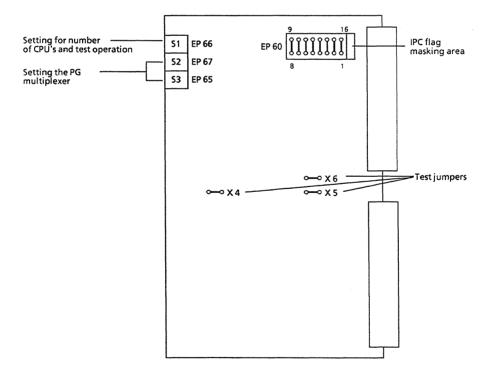

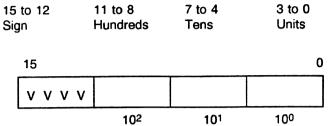

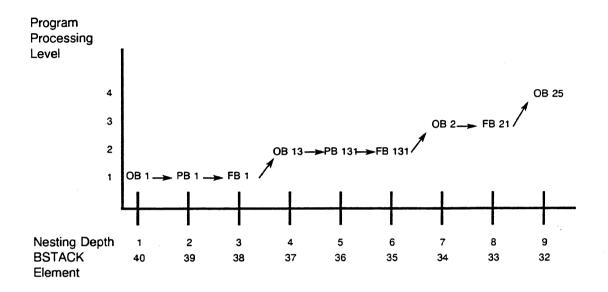

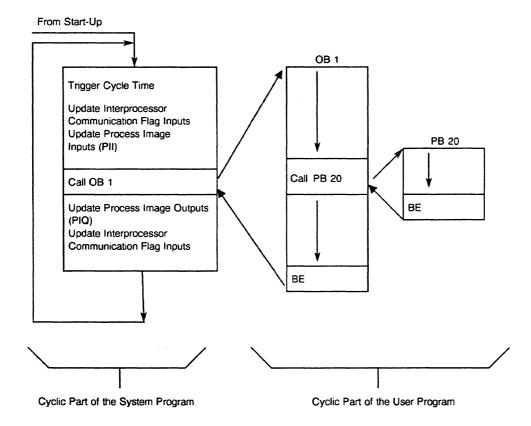

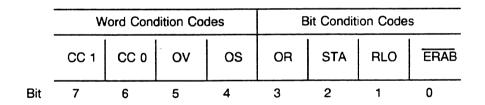

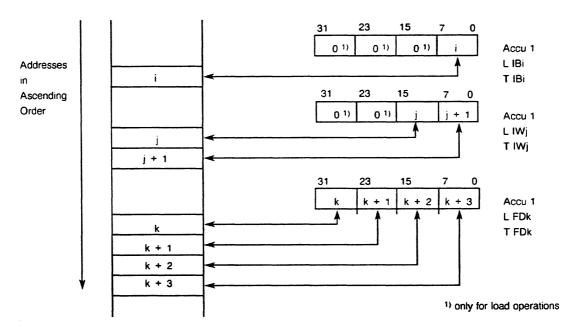

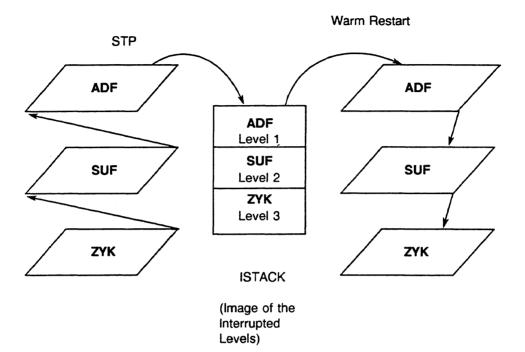

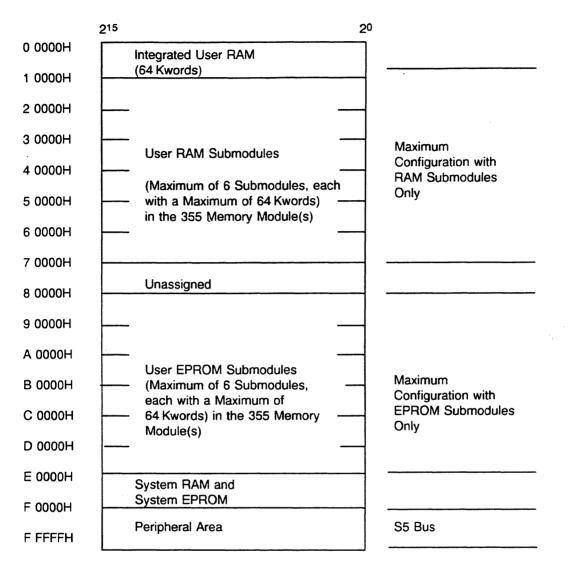

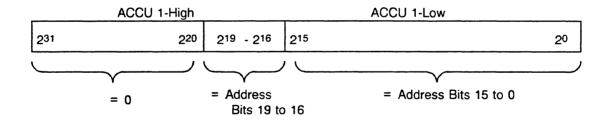

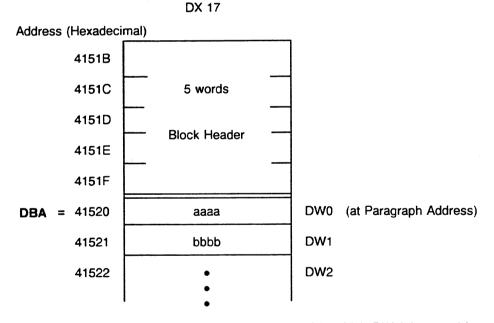

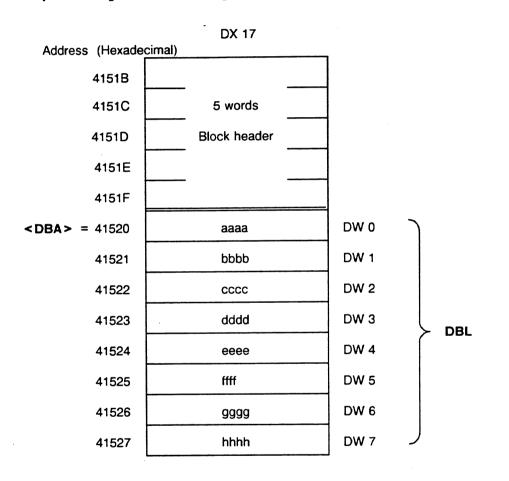

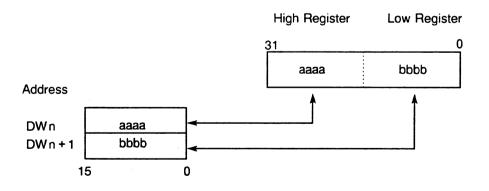

#### Note: