## NASA Electronic Parts and Packaging (NEPP) Program

NEPP Task: Guidelines for Selection of Ceramic Capacitors for Space Applications

# Cracking Problems in Low-Voltage Chip Ceramic Capacitors

**Alexander Teverovsky**

ASRC Federal Space and Defense Alexander.A.Teverovsky@nasa.gov

Worked performed at NASA Goddard Space Flight Center

2018

### Cracking Problems in Low-Voltage Chip Ceramic Capacitors

#### **Abstract**

Cracking remains the major reason of failures in multilayer ceramic capacitors (MLCCs) used in space electronics. Due to a tight quality control of space-grade components, the probability that as manufactured capacitors have cracks is relatively low, and cracking is often occurs during assembly, handling and the following testing of the systems. Majority of capacitors with cracks are revealed during the integration and testing period, but although extremely rarely, defective parts remain undetected and result in failures during the mission. Manual soldering and rework that are often used during low volume production of circuit boards for space aggravate this situation. Although failures of MLCCs are often attributed to the post-manufacturing stresses, in many cases they are due to a combination of certain deviations in the manufacturing processes that result in hidden defects in the parts and excessive stresses during assembly and use. This report gives an overview of design, manufacturing and testing processes of MLCCs focusing on elements related to cracking problems. The existing and new screening and qualification procedures and techniques are briefly described and assessed by their effectiveness in revealing cracks. The capability of different test methods to simulate stresses resulting in cracking, mechanisms of failures in capacitors with cracks, and possible methods of selecting capacitors the most robust to manual soldering stresses are discussed.

#### Contents

| 1. IN | TRODUCTION                                                               | 5   |

|-------|--------------------------------------------------------------------------|-----|

| 2. M  | ANUFACTURING PROCESSES AND TYPES OF MLCCS                                | 8   |

| 2.1.  | DIELECTRIC MATERIALS                                                     | 10  |

| 2.2.  | ELECTRODE MATERIALS                                                      | 11  |

| 2.3.  | TERMINATION MATERIALS                                                    | 12  |

| •     | Flexible terminations                                                    | 14  |

| 2.4.  | Design                                                                   | 15  |

| •     | Laser marking                                                            | 18  |

| 3. TE | STING AND QUALITY ASSURANCE                                              | 19  |

| 3.1.  | COMPARATIVE ANALYSIS OF SPECIFICATIONS                                   | 19  |

| •     | Military specifications                                                  | 20  |

| •     | NASA/GSFC specifications                                                 | 22  |

| •     | ESA and JAXA specifications                                              | 24  |

| •     | Automotive industry specifications                                       | 25  |

| 3.2.  | QUALIFICATION PROCEDURES AND CRACKING PROBLEMS IN MLCCS                  | 25  |

| •     | Thermal shock                                                            | 26  |

| •     | Life testing                                                             | 27  |

| •     | Humidity testing                                                         | 27  |

| •     | Resistance to soldering heat                                             | 28  |

| •     | Flex testing                                                             | 30  |

| •     | Sample size                                                              | 31  |

| 4. CH | IARACTERISTICS OF MLCCS                                                  | 32  |

| •     | Rated voltage                                                            | 32  |

| 4.1.  | CAPACITANCE AND DISSIPATION FACTOR                                       |     |

| 4.2.  | Insulation resistance and leakage currents                               | 34  |

| •     | Specified IR values                                                      | 35  |

| •     | Absorption and intrinsic leakage currents                                |     |

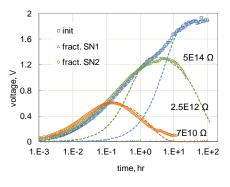

| •     | Effect of cracking on IR                                                 | 38  |

| 4.3.  | Breakdown voltage                                                        |     |

| 4.4.  | MECHANICAL CHARACTERISTICS                                               | 40  |

| •     | Flexural strength                                                        | 41  |

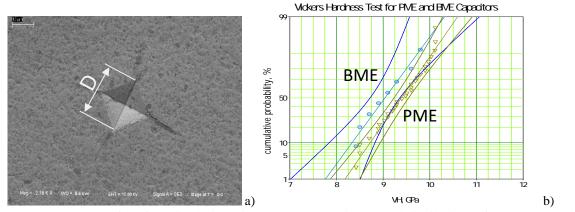

| •     | Vickers hardness                                                         | 43  |

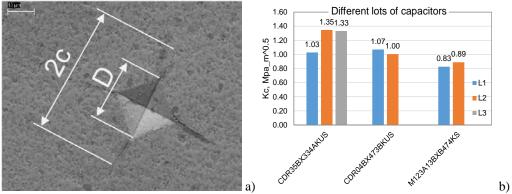

| •     | Indentation fracture toughness                                           | 43  |

| 5. FA | ILURE MECHANISMS IN MLCCS WITH CRACKS                                    | 44  |

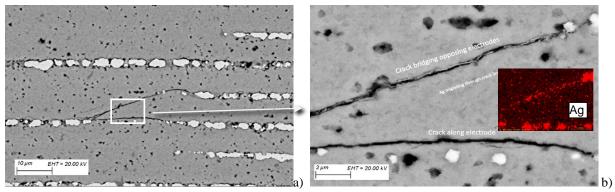

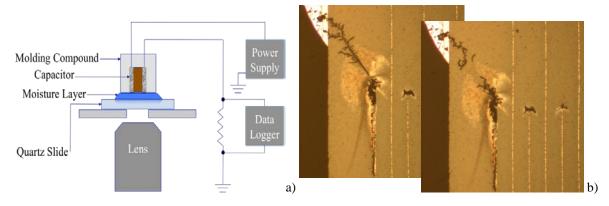

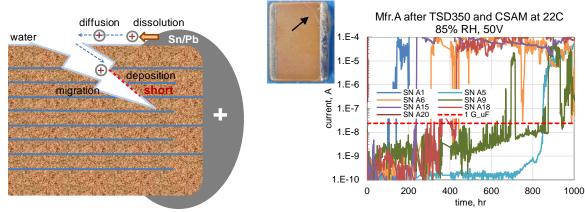

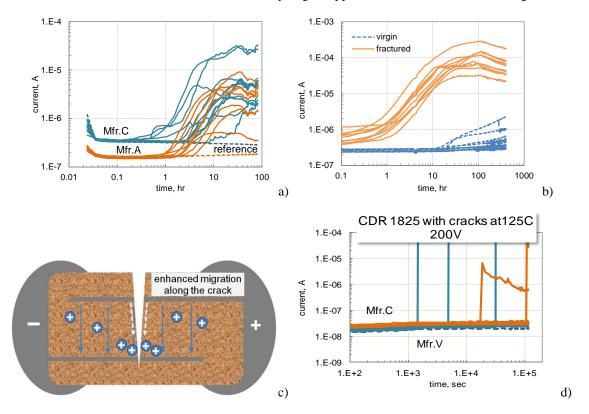

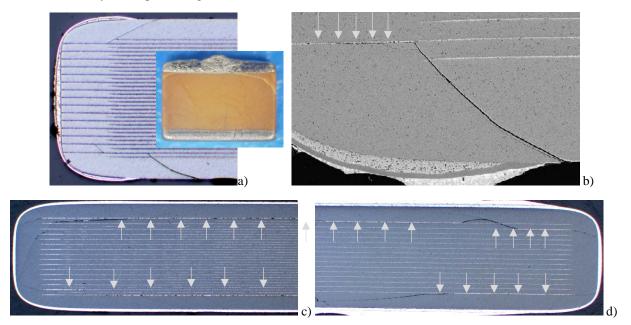

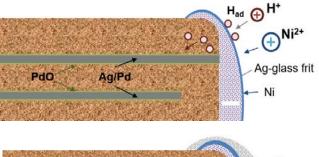

| 5.1.  | DEGRADATION OF PME AND BME CAPACITORS IN THE PRESENCE OF MOISTURE        | 45  |

| 5.2.  | DEGRADATION IN DRY ENVIRONMENTS                                          | 51  |

| 6. SP | ECIAL CASES OF MLCC CRACKING DURING MANUFACTURING, ASSEMBLY, AND TESTING | 52  |

| 6.1.  | Hydrogen-related cracking                                                | 53  |

| 6.2.  | EFFECT OF PICK AND PLACE MACHINE                                         |     |

| 6.3.  | ELECTRO-MECHANICAL RESONANCE                                             |     |

| 7. RE | VEALING CRACKS                                                           | E-1 |

| , ne  | V LALINU LIALIJ                                                          |     |

| 7.1.   | OPTICAL EXAMINATIONS                                      | 57 |

|--------|-----------------------------------------------------------|----|

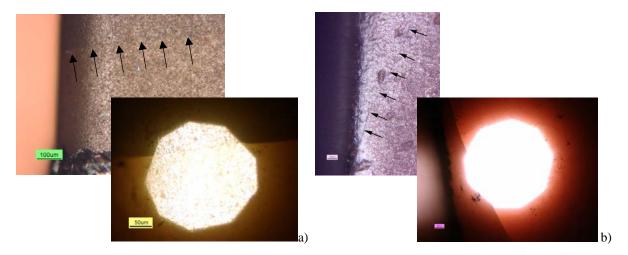

| •      | Vicinal illumination                                      | 57 |

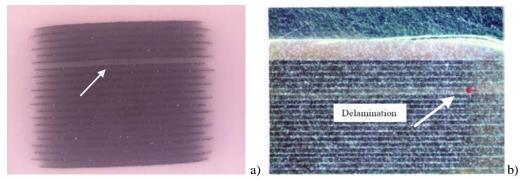

| •      | Revealing delamination by discoloration of ceramic layers | 58 |

| 7.2.   | ELECTRICAL MEASUREMENTS                                   | 58 |

| •      | Methanol test                                             | 59 |

| •      | Temperature dependence of capacitance                     | 59 |

| •      | Time Domain Reflectometry (TDR)                           | 59 |

| •      | Absorption voltage                                        | 59 |

| 7.3.   | ELECTRO-MECHANICAL EFFECTS                                | 60 |

| •      | Variations of the electro-mechanical resonance spectrum   | 60 |

| •      | Resonant ultrasound spectroscopy (RUS)                    | 60 |

| •      | Tone-burst excitation                                     | 61 |

| •      | Acoustic emission                                         | 61 |

| •      | Laser interferometry                                      | 61 |

| 8. CR. | ACKING CAUSED BY MANUAL SOLDERING                         | 62 |

| 8.1.   | WORKMANSHIP RECOMMENDATIONS FOR MANUAL SOLDERING          | 63 |

| •      | Effect of touch-up                                        | 64 |

| 8.2.   | SELECTING CAPACITORS ROBUST TO MANUAL SOLDERING           | 65 |

| •      | Terminal solder dip testing                               | 65 |

| •      | Assessment of the susceptibility to cracking              | 66 |

| 9. CO  | nclusion                                                  | 67 |

| 10.    | REFERENCES                                                | 68 |

#### 1. Introduction

Multilayer ceramic capacitors (MLCCs) constitute the majority of components used in electronic assemblies, mostly as filtering, bypass or decoupling devices. Since 2010 more than a trillion of MLCCs is manufactured every year in the world and consumed mostly by smart phones, PCs, TVs, and automotive industry [1, 2]. This makes MLCCs the most widely used passive component. Early generations of mobile phones used several dozens of MLCCs but modern smartphones have more than 600. A significant growth in consumption of electronics occurs within the automotive sector. Many vehicles today use more than 300 MLCCs in both 'under the hood' (engine management) applications and in the 'passenger compartment'. However, the latest Tesla models of electric cars have over 10,000 MLCCs per vehicle. Most commercial applications require cheaper and smaller size MLCCs. In 2018 almost 50% of the market share were size 0402 devices, but their production is declining and size 0201 capacitors are growing much faster. It is expected that in the near future the predominance of the 0201 case size will decline in favor of the size 01005, which already has 10% market share. Further, the designers should consider the 008004, a device that is taking off rapidly and is already outselling the 1206 size capacitors. Advancement of small size, high CV value, low-voltage MLCCs in commercial systems raised concerns regarding insulation resistance, IR, degradation and parametric failures in capacitors related to migration of oxygen vacancies [3, 4].

Compared to commercial, hi-rel and especially space systems are using a more conservative approach for selection of components and a substantial proportion of MLCCs used in high-level space projects has size 1206 and larger. However, the trend for using smaller size, high volumetric efficiency capacitors exists, and the use of advanced technology capacitors in newly design space instruments and systems is increasing.

Considering the amount of MLCCs used, the overall probability of their failures is extremely low. Still, because they are failing typically in a short circuit mode, failures might cause catastrophic consequences to the whole system, cease some system functions, or result in intermittent failures that can be misgauged as a software problem. Capacitors are typically responsible for up to 30% of the field failures in commercial systems, and until recently, approximately half of these failures were due to cracking in the parts [5].

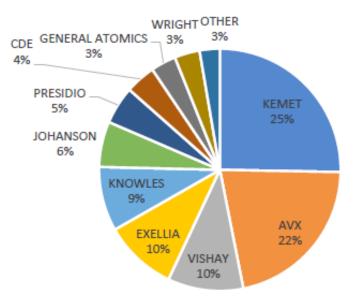

The proportion of MLCCs in space instruments is similar to commercial assemblies and varies from 10 to 20% of all electronic components. According to Paumanok Publications [6] the cost of capacitors procured by aerospace industry is 73% of the whole cost of passive components. The major vendors that produce 57% of all capacitors procured by aerospace companies are AVX Corporation, Vishay Intertechnology, and Kemet Electronics (see Fig.1.1). Japanese vendors who dominate commercial market (TDK Corporation, Murata Manufacturing, Matsushita, Rubycon) do not sell directly to the global defense markets; however, capacitors produced in Japan find their way into defense electronics through distribution.

Figure 1.1. Top manufacturers of capacitors for defense and aerospace electronics in 2017 [6]

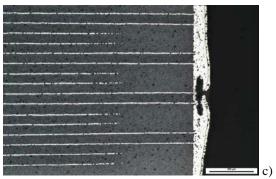

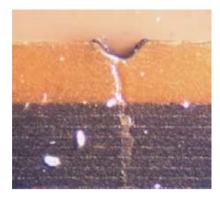

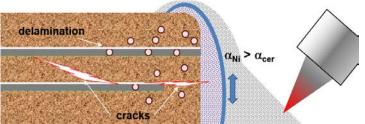

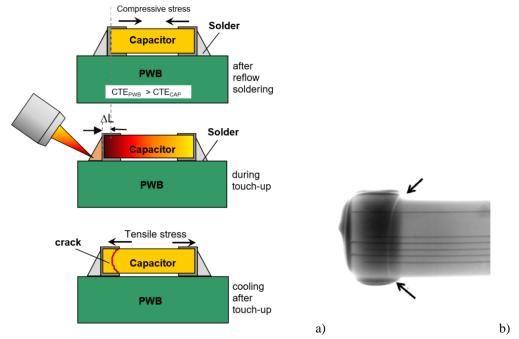

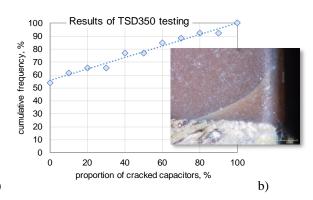

Cracks and delamination in MLCCs might originate from manufacturing processes or be introduced during assembly or the following handling and testing of the boards (flex cracks or thermal shock cracks). Examples of different types of cracks are shown in Fig. 1.2.

a) Manufacturing defect: CDR 0.1 μF 100 V capacitor that failed due to delamination at ~1.5 kohm during board-level testing

b) Manufacturing defect: voids and delaminations (knit line cracks).

c) Assembly-related defect: flex crack.

d) Assembly-related defect: thermal shock cracking.

e) Cracking caused by manual soldering.

f) Cracking caused by touch-up after reflow soldering.

Figure 1.2. Different types of cracks in MLCCs.

A brief description of different causes of cracking is given below.

1. Manufacturing defects.

Note that some defects might not result in formation of visual cracks, but rather weaken the part and make them more susceptible to cracking during assembly and applications. For example, thermal cracks caused by soldering might initiate at the internal flaws such as voids and delaminations.

- 1.1. Rapid cooling of the laminates can cause so-called firing cracks that typically propagate perpendicular to the plane at the terminals.

- 1.2. Insufficient binding strength and/or the presence of foreign materials might result in knit-line cracks that typically extend parallel to the electrodes.

- 1.3. Delaminations and knit line defects were a rather common defects in early ceramic capacitors, but are rare in contemporary MLCCs, especially those manufactured to military specification. Formation of the electrodeceramic delaminations during manufacturing can be attributed to variety of reasons. C. Hodgkins [7] identified nine principal causes for interlayer ceramic-metal separation that include outgassing of the solvent binder

(removal of the vaporized binder during pre-sintering processes that occurs along the ceramic/metal electrode interfaces), trapped air during lamination, and surface contamination. Another possible reason for delaminations of PME capacitors is oxidation of palladium electrodes in air that is accompanied with volume expansion.

#### 2. Assembly.

- 2.1. Pick-and-place machines can damage parts by excessive stresses created by centering jaws or vacuum picks.

- 2.2. Thermal shock cracks are due to a sharp temperature increase during soldering. These stresses might form large, visible U-shaped cracks on the surface of capacitors.

- 2.3. Thermal shock cracks might also occur when liquid cleaners are applied to a board that has not sufficiently cooled after soldering reflow. The effect is due to a much higher sensitivity of MLCCs to the cold (from hot to cold) compared to hot (from hot to cold) thermal shocks [8]. To prevent this type of cracking the boards should be cooled slowly, preferably by natural cooling, or at a rate not exceeding 2 °C to 3 °C/sec., to temperatures below 60 °C.

- 2.4. Tensile stresses and cracking might develop in MLCCs after soldering them onto alumina boards, which is due to the differences in CTEs between the ceramic material and substrate, with the latter having lower CTEs. These stresses were responsible for many observed failures in the first ceramic chip capacitors mounted on alumina substrates in hybrids [9].

#### 3. Board-level handling.

Due to the lack of stress relief in mounted chip capacitors, deformation and flexing of the PWB might create significant tensile stresses resulting in so-called flex cracking. These cracks mostly originate at the bottom surface near the edge of the termination margin and propagate inside at angles close to 45° [10]. Typical sources of the flex cracking are de-paneling, test probing, handling during visual examinations, attachment of standoff elements and connectors, etc.

#### 4 Application.

- 4.1. Deformation of the board caused by temperature cycling, vibration or mechanical shocks that occur during the ground phase testing and integration or launch of the spacecraft might cause flexing of the board sufficient for cracking of MLCCs. Multiple guidelines for design and board layout have been developed to reduce the probability of this type of failures [11].

- 4.2. Due to electrostriction in ceramic materials, voltage cycling might create mechanical stresses that would further develop preexisting microcracks, resulting in failures. This mechanism might be especially important for high-voltage ceramic capacitors [12, 13].

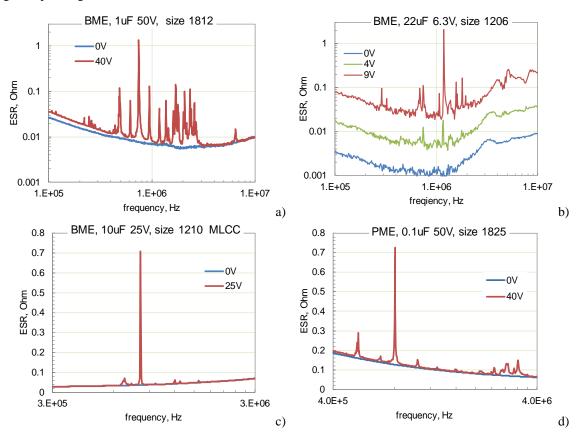

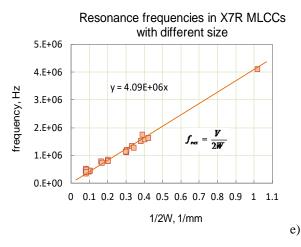

- 4.3. Electro-mechanical resonances in class II dielectric capacitors due to the reverse piezoelectric effect in ceramics (see section 6.3).

Although soldering-induced damage might not lead to immediate failures and damaged capacitors may endure weeks or months of service use, it can cause degradation of characteristics with time resulting eventually in field failures. In this regard, microcracks in capacitors generated during assembly can be considered as a "time bomb" [14] that causes increased leakage currents, shorts, opens, or intermittent contacts as degradation develops or cracks propagate with time during application.

Cracking in ceramic capacitors is an old problem. It appeared in the 1970s when first surface mount technology (SMT) chip capacitors were introduced to the market and their employment in NASA applications begun [9, 15]. According to J. Maxwell [11] this problem will continue to be with us in the foreseeable future. Two main factors contribute to the problem: brittleness of ceramic materials and thermal and mechanical stresses associated with the assembly process and/or post assembly handling and testing. Both factors are intrinsic to chip ceramic capacitors and explain the persistence of the problem.

Due to a relatively large size of military and space-grade capacitors used in space systems and use of manual soldering, a substantial proportion of MLCC cracking failures is attributed to the assembly process. Experience shows that the propensity to cracking is lot-related, which means that cracking is often due to a combination of the weakness in the part caused by flaws introduced during manufacturing and assembly-related stresses. A proper screening or qualification testing could have revealed lots with defects and reduced the probability of failures.

Historically, majority of defects in MLCCs were due to the manufacturing processes, and the screening and qualification (S&Q) system used in military specifications was focused on revealing and removing this type of defects. Currently, the proportion of manufacturing defects have been reduced substantially, and most problems with MLCCs are due to the post-manufacturing stresses. However, the requirements in military specifications remain mostly unchanged and do not address sufficiently post-manufacturing stresses.

One of the most powerful means used by hi-rel OEMs to improve reliability of components is derating that limits the level of stress (typically, voltage and temperature) compared to the operating conditions specified for the part. However, due to the low-voltage failure phenomena in MLCCs (see section 5.1) derating might be not effective in reducing risks associated with cracking in the parts.

In this report, we will first give an overview of manufacturing processes and types of MLCCs and consider to what degree the existing S&Q system assures safe assembly and reliable operation of the part. Techniques used to reveal capacitors with cracks, failure modes and mechanisms related to cracking will be reviewed and possible risk mitigating measures to reduce failures associated with manual soldering discussed.

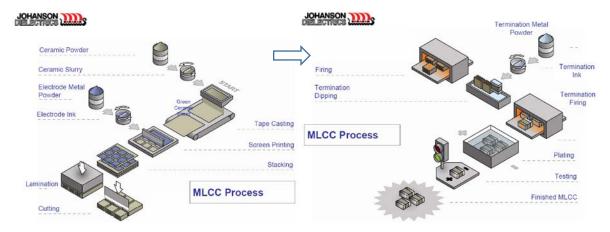

#### 2. Manufacturing processes and types of MLCCs

All MLCCs are manufactured using a ceramic slurry (a mixture of ceramic powder, dispersant, solvent, and organic binder) and a paste for metal electrodes (see Fig.2.1). The dielectric layers are formed by the casting process and then electrodes are formed by applying the paste by screen printing. Dry or wet stacking processes are used depending on conditions of the layers used for lamination. During the wet process, the next layer of the ceramic slurry and electrode paste are laid down on the top of the previous layer and then the stack is dried out to remove the binder (at  $\sim 400$  °C). During the dry process the layers are casted on a Mylar or stainless steel belt, then dried out, removed from the belt, stacked, and laminated at elevated temperature under pressure. It is considered that the wet process that is typically used to manufacture precious metal electrode (PME) capacitors allows for a better interlayer bonding that results in less delamination.

The dry process that is mostly used for the base metal electrode (BME) technology allows for thinner dielectric layers and larger number of electrodes. Maximum number of layers for dry technology is ~1000 layers with the thickness of the dielectric down to submicrometers, whereas for the wet technology the number of layers typically is less than 200 and the thickness is more than ~5 µm. However, experience shows that the type of the process is not a significant factor affecting the probability of cracking in MLCCs and both methods, when optimized, are capable of producing high-quality, defect free microstructure of MLCCs.

After cutting and presintering, the parts go through the tumbling process (not shown in Fig.2.1) to smooth and round the corners and help to obtain good coverage of the termination ink and subsequent barrier layer plating. The tumbling occurs in rotating barrels filled with water and zirconium balls. Tumbling also minimizes mechanical stresses at the corners of the part and reduces breakages during pick and place operations [16].

After tumbling and drying, the parts are sintered/fired in kilns at high (typically above 1000 °C) and tightly controlled temperatures. The following processes include application of the base termination to make contacts to the internal electrodes, electroplating and finishing.

Figure 2.1. Schematic of the processes of MLCCs manufacturing [17].

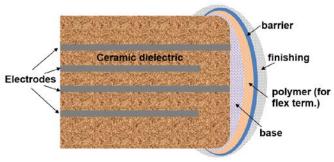

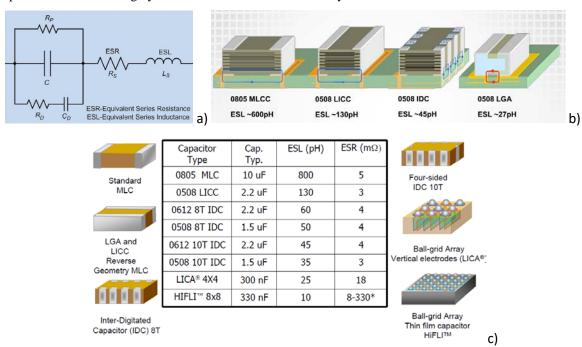

Fig.2.2 shows a typical construction of a low-voltage (below 200 V) MLCC. The major elements of the part are ceramic dielectric, metal electrodes, and terminations. Respectively, the type of capacitors depends on materials used in these elements (see Table 2.1). Different types of ceramic materials can be used with different types of metal electrodes and terminations resulting in a large variety of types of MLCCs. This variety further increases considering different sizes and outlines of the parts. Standard design low-voltage MLCCs have two terminals, but for some applications, in particular, for decoupling in microcircuits (e.g. FPGA), a design is changed to reduce inductance of the parts.

Figure 2.2. Schematic of a low-voltage MLCC.

Table 2.1. Classification of low-voltage MLCCs

| Ceramic dielectric                                                                                                                                                                                                                                                                                                                               | Electrode                                      | Termination                                                                                                                                                                                                                                  | Design (size and olutline)                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| <ul> <li>Class I (C0G, NP0, BP, BG)         High stability, low loss</li> <li>Class II (e.g. X7R, BX) High         volumetric efficiency with         variations of cap. ±15% in temp.         range from -55°C to +125°C.</li> <li>Class III (e.g. Y5V) Higher         volumetric efficiency than class         II, but less stable.</li> </ul> | <ul><li>Ag/Pd (PME)</li><li>Ni (BME)</li></ul> | Base termination: silver glass frit (for PME) copper glass frit (for BME) Barrier layer: Ni Cu (non-magnetic) Polymer (flex term. only) Silver epoxy Finish plating Sn/Pb Ag-Pd (non-magnetic) Au (wire bond attachment) Sn (ROHS compliant) | <ul><li>Standard, two terminals.</li><li>Low inductance.</li></ul> |

#### 2.1. Dielectric materials

Materials used in MLCCs have polycrystalline structure that is based on barium titanate (BaTiO3) ceramics with different doping for different areas of application and a few percent of glass to interconnect crystal grains. Based on temperature stability of the dielectric constant, K, capacitors are divided into three classes of materials (see Table 2.2). Per EIA-198 [18] classification, the level of temperature stability is characterized by a three-character alphanumeric code (see Table 2.3) indicating the minimal low temperature, maximum high temperature, and maximum capacitance change over the temperature range.

| EIA class<br>dielectric* | Dielectric<br>class | Low Temp.<br>rating, ºC | High Temp<br>rating, ⁰C | Maximum<br>Temp shift | Maximum<br>loss of C, %<br>per decade<br>hour ** |

|--------------------------|---------------------|-------------------------|-------------------------|-----------------------|--------------------------------------------------|

| C0G                      | 1                   | -55                     | 125                     | ± 30 ppm/°C           | 0                                                |

| X7R                      | II                  | -55                     | 125                     | ± 15%                 | 2.5                                              |

| Y5V                      | III                 | -30                     | 85                      | +22% -82%             | 7                                                |

Table 2.2. Characteristics of dielectric materials in MLCCs per EIA 198

Characteristics of class III ceramic capacitors vary substantially with temperature, voltage and time under bias or duration of storage. Due to a limited temperature range of class III capacitors, they cannot be tested and stressed to the level that is typically used for high-reliability parts and are not recommended for space applications.

Class I ceramic capacitors are the most temperature stable, have minimal dielectric losses and are typically used in RF systems. Thermal stability codes for this type of dielectrics are described in EIA-198, but the most commonly used is C0G type that is also known as NP0-type or BP/BG in MIL specifications. These materials are paraelectrics and have a relatively low dielectric constant (K < 100) that does not vary with voltage. Class I ceramic capacitors have a relatively small concentration of barium titanate, below 50%, and are composed of a mixture of finely ground materials such as Titanium dioxide (rutile, TiO2) or CaTiO3 modified by different additives (Zn, Zr, Nb, Mg, Ta, at al.). KEMET is using calcium zirconate (CaZrO3) ceramics with  $K \sim 32$  for class I dielectrics that allows for expanding capacitance values in U2J type BME capacitors into the range previously available only in Class II dielectric materials such as X5R and X7R.

| Low Temp.,<br>⁰C | Symbol | High Temp.,<br>⁰C | Symbol | Max. capacitance change over temp range, % | Symbol |

|------------------|--------|-------------------|--------|--------------------------------------------|--------|

| +10              | Z      | +45               | 2      | ±1                                         | Α      |

| -30              | Υ      | +65               | 4      | ±1.5                                       | В      |

| -55              | Χ      | +85               | 5      | ±2.2                                       | С      |

|                  |        | +105              | 6      | ±3.3                                       | D      |

|                  |        | +125              | 7      | ±4.7                                       | Е      |

|                  |        | +150              | 8      | ±7.5                                       | F      |

|                  |        | +200              | 9      | ±10                                        | Р      |

|                  |        |                   |        | ±15                                        | R      |

|                  |        |                   |        | ±22                                        | S      |

|                  |        |                   |        | +22 to -33                                 | Т      |

|                  |        |                   |        | +22 to -56                                 | U      |

|                  |        |                   |        | +22 to -82                                 | V      |

Table 2.3. Temperature characteristic codes for class II and III dielectrics

Examples. X7R: X=>-55C, 7=>+125C,  $R=>\pm15\%$ .

Z5U: Z=>+10C, 5=>+85C, U=>+22% to -56%

Class II and III dielectrics are based on ceramics with barium titanate concentration exceeding 90% that is doped with different elements (e.g. rare earth elements La, Nd, Sm, Gd, Dy, Ho, Er, Yt, Mg, Va) and behave as ferroelectrics at temperatures below ~ 125 °C (Curie point) and as paraelectrics at higher temperatures. Their dielectric constant is high, in the range from 200 to more than 10,000 for class II and more than 10,000 for class III capacitors, but the value

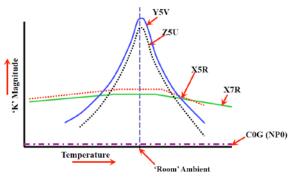

of *K* is temperature dependent and varies substantially with applied voltage. Comparative temperature dependencies of dielectric constant for different types of dielectrics are shown in Fig. 2.3.

Polycrystals in barium titanate ceramics are comprised of micrometer size grains that have glassy grain boundaries and a crystalline core-shell structure that determines performance and reliability of capacitors [19]. A high-resistive shell doped with rare elements is formed around the grain of the barium titanate ceramic during sintering. At temperatures below the Curie point, the grains are divided into randomly oriented domains that have the same spontaneous polarization (see Fig. 2.4). AC electric field changes the direction of polarization resulting in high values of the dielectric constants. Under DC bias the reversal of polarization caused by AC signal is limited that is reflected in a reduction of the dielectric constant with DC voltage in class II and III dielectrics.

Core

Shell Domain

Figure 2.3. Comparative temperature dependencies of dielectric constant in different types of materials J. Prymak, KEMET tutorial [20].

Figure 2.4. TEM image of a BaTiO3 ceramic showing core-sell structure of a grain [21].

Low-voltage PME MLCCs manufactured to military specifications have typically a relatively thick dielectric layers, in the range from 20 to 30  $\mu$ m, and the number of layers below 100. Stacking of large size MLCCs is used to produce large, microfarad range capacitors. Similar values of capacitance in BME MLCCs are reached in a smaller size parts by reducing the thickness of the dielectric layers and increasing their number. Contemporary BME capacitors can have dielectric thickness as low as 0.5 - 0.7  $\mu$ m and have up to 400 layers in case size 0402. Production of this type of capacitors require a very small grain size that is getting closer to the dimensional limit [22]. Reduction of the grain size below a certain optimum (~1  $\mu$ m) decreases room temperature dielectric constant and temperature stability of capacitors. Until recently, maximum operation temperature of capacitors was 150 °C (X8R, X8S, and X8T types), which is likely a limit for barium titanate ceramics. Development of new types of materials, e.g. tungsten-bronze type ferroelectrics, allows increasing further operating temperatures and development of X9R BME capacitors that can operate in the range from -55 °C to +200 °C.

#### 2.2. Electrode materials

Historically, MLCCs used in space application had electrodes made of precious metals, typically silver/palladium alloys (PME capacitors), but starting 2017 capacitors with nickel electrodes, or base metal electrode (BME) capacitors manufactured per MIL-PRF-32535 are qualified for space applications. BME capacitors have been widely employed in commercial and automotive industry applications since mid-90th mostly due to a lower price of materials. Table 2.4 shows characteristics of different types of metals used to form electrodes in MLCCs including the atmosphere for the metal paste firing.

| Metal | Melting<br>point, ⁰C | Resistivity,<br>mohm | Firing<br>atmosphere | Price ratio |

|-------|----------------------|----------------------|----------------------|-------------|

| Ag    | 961                  | 1.62                 | Air                  | 3           |

| Cu    | 1080                 | 1.72                 | Reducing             | 1           |

| Ni    | 1453                 | 6.9                  | Reducing             | 1           |

| Pd    | 1552                 | 10.4                 | Air                  | 80          |

Table 2.4. Physical properties and price ratio of electrode materials [21]

The paste that is typically used for PME capacitors has relatively large particle sizes, from 900 to 1000 nm, whereas BME technology uses pasts with smaller particles, from 300 to 500 nm. This allows formation of relatively thin nickel electrode layers. Typically, a composition of 70% Ag and 30% Pd is used for PME capacitors; however, depending on design, manufacturing process, and type of ceramic, the Ag/Pd ratio can vary substantially.

Silver/palladium alloys do not react with ceramic and do not oxidize significantly, which allows for sintering in air atmosphere. Although PME technology has been used for decades, some challenges during firing of capacitors with Ag/Pd electrodes still exist [2]. These challenges include catalyzation of the binder burn-out that might accelerate gas generation and cause delaminations and volumetric changes in the electrodes that can also facilitate delaminations. Volumetric changes are due to increasing Pd volume up to 68% when it is oxidized at ~500 °C and reduces back at ~800 °C. A low melting temperature glassy components should be used to limit the firing temperature for 70Ag/30Pd alloy to ~1,100°C, which results in reduction of the dielectric constant of ceramics. Silver evaporation during firing requires using special measures to increase Ag vapor pressure during sintering. Diffusion of silver into ceramic (mostly along the grain boundaries) limits the minimal thickness of the dielectric layers resulting in decreasing of volumetric efficiency of capacitors.

The major challenge for the BME technology is nickel oxidation in air during sintering that results in a substantial increase of resistance of electrodes. To reduce oxidation, high temperature operations (at ~1200 °C) are carried out in reduced atmospheres. This results in generation of positively charged oxygen vacancies in the ceramic, increases conductivity of the dielectric and causes IR degradation in capacitors with time of operation. To avoid the effects of reducing environments and stabilize ceramic, a special dopants e.g. rare earth oxides Y2O3, Dy2O3, Ho2O3, and Er2O3, are used. The dopans reduce concentration of oxygen vacancies and improve stability of capacitors during life testing [2]. In addition, stability of BME MLCCs is improved by re-oxidation at temperatures below sintering (~1000 °C) after firing of the parts. It is assumed that reoxidation of BME MLCCs is controlled by oxygen diffusion along the Ni inner electrodes [23].

Diffusion and migration of Ag into dielectric layers from inner Ag or Ag/Pd electrodes might pose a problem for long-term reliability. Silver is a material that is most susceptible to electromigration in the presence of moisture, and for this reason, cracking of PME capacitors creates a higher risk of electrical failures compared to BME capacitors (see section 5 of this report).

#### 2.3. Termination materials

After sintering, the end of a capacitor with exposed electrodes is dipped in a metal glass frit (thick film ink) consisting of metal particles or flakes and doped borosilicate glass. This ink is then dried and sintered/fired to the ceramic body allowing glass particles to fuse along contacts creating a sponge like structure and diffusing into ceramic to assure adhesion between ceramic body and terminal metallization [24]. If manufacturing process is not optimized, the interface boundary amorphous layer might crack during capacitors' manufacturing or assembly thus increasing the risk of failure. If termination firing temperature is below the optimal, not all internal electrodes form good metallurgical contacts with terminations. Under environmental stresses during application, this might cause intermittent electrical contacts resulting in sporadic changes in the value of capacitance and malfunctions of the electronic system. The type and optimal amount of glass frit used in termination depends on the type of ceramic and design of the capacitor.

The thickness and material of the glass frit affect the probability of cracking caused by thermal stresses associated with soldering and/or temperature cycling [25]. Insufficient thickness of the base termination might increase the proportion of MLCCs' failures during wave soldering by several times. Experience shows that optimization of the base terminal materials and processes improves substantially the robustness of capacitors and reduces risks of failures during high humidity operations. The type of paste used might also affect the probability of IR failures in COG BME capacitors after storage at normal conditions [26].

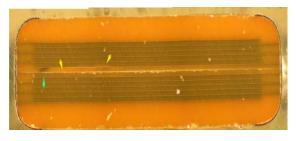

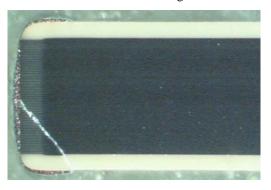

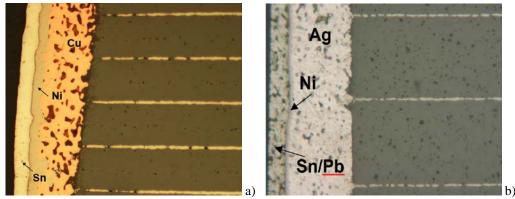

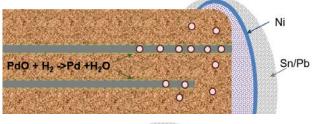

A silver-based frit is used for PME and a copper-based (sometimes nickel-based) frit is used for BME technology. The copper-based frit is fired in oxygen-free atmosphere to avoid oxidation. Fig. 2.5 shows typical cross-sections of terminations in PME and BME capacitors.

After the termination has been sintered it is electroplated with a nickel layer to form a barrier and minimize dissolution of electrodes and base metallization during soldering. A final step in forming terminations is plating with a tin/lead solder for military or tin layer for commercial capacitors to assure solderability of the part.

Figure 2.5. Terminations in BME (a) and PME (b) 50 V capacitors.

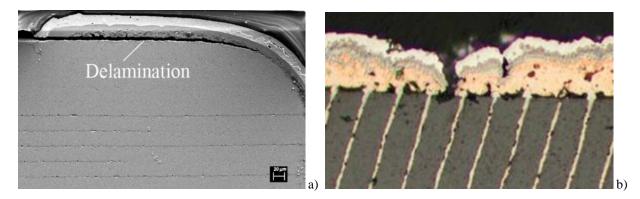

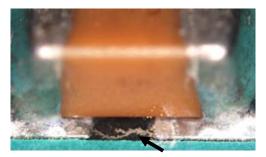

The porosity of the base termination and the presence of pinholes allow penetration of moisture through the terminals of the part [24]. This can cause corrosion of copper or degradation of insulation resistance of the capacitor in the presence of cracks that might create a path for moisture to short opposite electrodes. This degradation process might accelerate in the presence of defects in the termination such as terminal-ceramic delamination or pinholes shown in Fig. 2.6. Note, that MIL-PRF-123 considers acceptable pinholes of less than 130 µm and MIL-PRF-32535 reduces these requirements to 80 µm for capacitors with sizes smaller than 0805. These pinholes not only transparent for moisture, but can also trap contaminations and moisture for a long time thus enhancing the risk of corrosion.

Calculations have shown that the size of terminations affects the maximum principal stress in MLCCs [27]. Mechanical stresses in capacitors also depend on the thickness of nickel plating and process conditions [28]. Considering that CTE of nickel (13.4 ppm/K) is greater than that of ceramics ( $\sim$ 9.6 ppm/K) and for both materials the Young's modulus is rather large, from  $\sim$  100 GPa to 200 GPa, substantial tensile stresses might develop during soldering conditions, thus enhancing metal/ceramic separation close to terminals. In some cases, failures of MLCCs during temperature cycling have been attributed to increased stresses caused by nickel plating. The optimal thickness of Ni barrier layers at the terminations is considered to be in the range from 2 to 6  $\mu$ m. Thicker layers might increase risks of cracking and delaminations and seal moisture and contaminations that could have penetrated inside the part during initial stages of the plating process. Termination materials and geometry are important elements of capacitors' design that affects the probability of cracking and failures [29]. The susceptibility to thermal shock failures is greater for terminations with Ni barrier compared to Pd/Ag terminated chips.

Figure 2.6. Example of termination defects. a) delamination in a PME capacitor and pinholes in BME (b) and PME (c) capacitors.

For non-magnetic capacitors that are often required by medical or special RF applications, nickel cannot be used as the barrier layer and terminations are manufactured using Ag/Pd finishing. Capacitors with this type of terminations are not recommended for soldering due to the leaching of silver into molten solder and should be attached by silver epoxy. Also, a Cu barrier can be used instead of Ni on the top of Ag or Ag/Pd glass for the non-magnetic devices.

MLCCs with gold finishing are assembled using wire bonding at terminals. Gold electroplating might result in excessive hydrogen generation, and reactions of hydrogen with palladium in PME MLCCs might cause delaminations and cracking. The risk of hydrogen related delaminations is greater for PME compared to BME capacitors. A detailed description of different types of terminations and acceptable methods of assembly can be found in manufacturers' recommendations, e.g. [30, 31].

Commercial capacitors are typically compliant with the Restriction of Hazardous Substances (ROHS) regulations and their terminations are manufactured using lead-free metals (typically pure tin) that are susceptible to growing whiskers. For military and space applications, termination finishing with a Sn/Pb alloy having 3% lead minimum is required. Replacement of pure tin with Sn/Pb finishing in commercial MLCCs can be achieved either by solder dipping into Pb containing solder or by plating Sn/Pb layer on the top of the existing finishing and the following fusion (e.g., AEM Inc. refinishing process). The latter process is less risky because avoids thermal shock stresses to the parts.

#### Flexible terminations

Flexible terminations that are formed by addition of a conductive polymer layer between the base and Ni barrier (see Fig.2.2) have been used for electronic boards' assembly for more than a decade. What started as a commercial technology to reduce failures related to flex cracking of MLCCs, is currently used for the advanced military and space grade capacitors manufactured per MIL-PRF-55681 and MIL-PRF-32535. The major reason for popularity of this technology is that flexible terminations reduce the stress that is transferred from the board to the ceramic body, and possible cracks instead of propagating to the active area of capacitors are contained within the polymer [32]. Experience and testing show that introduction of flex terminations decreases substantially cracking of MLCCs during soldering, handling, and field operations. Manufacturing experience shows that introduction of flexible terminations practically eliminated field returns caused by flex cracking.

Temperature cycling tests of capacitors with flex terminations in comparison with regular termination parts soldered onto PWBs showed a substantial improvement in reliability. Regular termination MLCCs started failing after 1000 cycles, whereas there was no failures detected in the flexterm capacitors after 3000 cycles.

Using conductive polymers in terminations improves substantially results of the drop testing. TDK data [33] show that capacitors with soft terminations had no cracking failures after 10,000 drops (dropping from 1 m at a frequency of 16 times per min), whereas a regular product had 30% failures after 2000 drops. In addition, after the drop testing the parts passed humidity load test (1000 hours at 85 °C and 85% RH under rated voltage) thus indicating absence of hidden cracks.

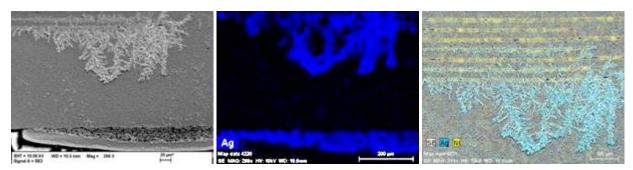

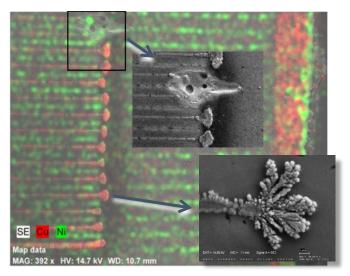

In BME capacitors with flex terminations operating in humid environments silver dendrites can grow along the surface of ceramics (see Fig. 2.7). Although the risk of increased metal migration along the cracks and failures caused by the growth of dendrites associated with silver-epoxy terminations exists, the benefits of reducing the probability of

cracking apparently prevail. As a result, the overall quality and reliability of BME capacitors with soft terminations is increased and field failures reduced.

Figure 2.7. Silver dendrites on the surface of a cross-sectioned BME flex-termination capacitor after low-voltage humidity testing at 1.5 V (HSSLV).

#### 2.4. Design

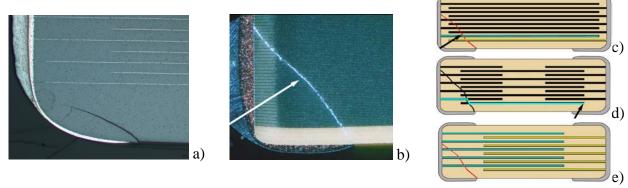

Most cracks in MLCCs caused by deformation of PWBs during assembly, handling or testing are initiated at the surface close to the terminal areas of capacitors (see Fig.2.8). These cracks might affect reliability of the parts if they are reaching active area of capacitors and cross opposite electrodes. For these reasons, parts with thicker cover plates and larger end margins are more resilient to cracking-related failures [34].

Existing requirements for margins in military specifications are similar to EIA-469 DPA standard [35] that has different margin and cover plate thickness limits for different groups of capacitors. The EIA-469 requirements for the margins are designed to provide sufficient electrical insulation, address mostly quality of the as-manufactured parts and do not consider cracking-related issues.

Thin dielectric MIL-PRF-32535 follows EIA-469 and specifies different limits for parts with VR above 50 V, below 6.3 V, 16 V and 25 V. For example, the thickness of cover plates should exceed 0.003" (75  $\mu$ m) for capacitors rated to more than 50 V and can be as low as 0.001" (25  $\mu$ m) for capacitors with VR  $\leq$  6.3 V. However, for capacitors intended for automotive industry, manufacturers have stricter requirements for the margins. A minimal size for margins and cover plates for commercial MLCCs manufactured by AVX is 75  $\mu$ m, it is 100 to 125  $\mu$ m for automotive grade capacitors and 110 to170  $\mu$ m for space application [36, 37].

To mitigate risks of cracking-related failures, special designs of MLCCs have been developed. For low capacitance values, KEMET, similar to other manufacturers, offers the Floating Electrode (FE-CAP) capacitors (see Fig. 2.8.d). This design is also known as a Serial Cap design [38]. For mid capacitance values, the Open Mode solution that has enlarged end margins that create safe zones on both ends of the capacitor (see Fig.2.8.e). Other manufacturers, e.g. TDK [33], are using similar design approaches to reduce failures caused by cracking (see Fig. 2.9).

Various designs of MLCCs that have been suggested by manufacturers to decrease the probability of flex cracking can be summarize as following:

- Flexible termination.

- Application of relatively soft and/or tear-away termination layers made of conductive polymers (see Fig. 2.2) reduces the stress in ceramic and restricts flex cracks within a safe zone away from the body of the MLCC.

- Fail open design (Fig.2.8.e).

- End margins are widened, so if a crack occurs, it does not cross electrodes with opposite polarity, and thus prevents short-circuit failures.

- Floating electrodes (Fig. 2.8.d).

- Two capacitors connected in series within an individual case size, so the probability of shorting cracks is reduced substantially.

- Clip-on lead frame.

- Attachment of J-shaped leads see Fig. 2.9) mechanically decouples the MLCC from the PWB and allows for some stress relief.

Figure 2.8. Soldering related cracks in MLCCs and schematics of a standard part (c), floating electrode capacitor (d), and Open Mode design (e) [38]. Yellow and blue lines in (c-e) represent electrodes with different polarity.

|                                                                        | image | Flex stress | Large capacity | Cost | Applications                                                                                                                       |

|------------------------------------------------------------------------|-------|-------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| 1) MEGACAP                                                             |       | ***         | ***            | *    | Circuits requiring especially<br>high reliability and large<br>capacitance                                                         |

| 2) Soft termination                                                    |       | **          | **             | **   | Circuits in which flex stress<br>or thermal shock can<br>become an issue                                                           |

| 3) Serial design, the CEU series (resin electrode s+ safety structure) |       | **          | *              | **   | Circuits in which flex stress<br>or thermal shock can<br>become an issue and a<br>serial connection of<br>capacitors is considered |

| 4) Open mode                                                           |       | **          | *              | ***  | Circuits that do no require<br>very big capacitance but flex<br>stress can be an issue                                             |

Figure 2.9. MLCC designs with flex crack countermeasures used by TDK [33].

A combination of floating electrode and flex termination design (e.g. a TDK Dual-Fail-Safe, Mega Cap design [39]) allows to reduce the risk of failures even further. This design has been proven highly reliable, and no cracks developed in the parts after 3000 thermal shock cycles.

Obviously, the cost of improved reliability of MLCCs with increased margins or floating electrodes is a lesser volumetric efficiency. For this reason, flex termination is likely the most efficient cracking mitigating measure.

Typically, capacitors having maximum capacitance values for a given case size and rated voltage have smaller margins and hence, pose a higher risk of failures. For this reason, for a given rated voltage and case size, the use of parts with maximum available value of capacitance is not recommended.

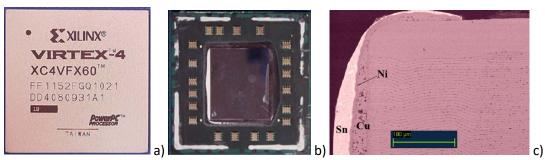

Since operating frequencies of contemporary microcircuits have increased substantially, new designs of MLCCs that are used in a close proximity to the microcircuits to improve their performance, suppress noise, and stabilize operation, have been developed. Fig. 2.10. shows an example of low-inductance capacitors used in a package of XILINX FPGA.

Figure 2.10. Overall external (a) and internal, after lid removal, (b) views of a XILINX VIRTEX-4 FPCA showing IDC-type ceramic capacitors mounted inside the package. Figure c) shows a cross-section of the termination area of IDC capacitors with dielectric thickness of ~2 µm.

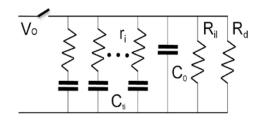

The equivalent series inductance, ESL, is an important parameter of capacitors that determines their efficiency during operation at high frequencies. Fig.2.11.a shows an equivalent circuit of MLCCs operating in the RF range. The idea of low ESL designs of MLCCs is in reduction of the length of the effective AC current flow path (see. Fig. 2.11.b).

ESL values can be decreased several times simply by reversing the width and length of capacitors. This change in the design might potentially increase the susceptibility of the parts to cracking, first, by creating of a more rigid solder connections, and second, because ceramic areas close to terminals have a higher level of internal mechanical stresses and the larger this area is, the greater the probability of having a crack.

A more drastic reduction of ESL, to the picohenry levels is achieved by IDC and ball grid array vertical electrode designs. Figure 2.11.c shows examples of designs of low-ESL MLCCs. The effect of design changes on the susceptibility to cracking requires additional analysis; however, some part types, and in particular, IDC capacitors, have passed extensive testing by XILINX and has been successfully used for more than a decade in FPGAs.

Figure 2.11. Equivalent circuit of a capacitor at high frequency(a) a schematic of the AC current flow in capacitors (b), J.Marshall [37], and types of low inductance MLCCs, R.Demko (c), [20].

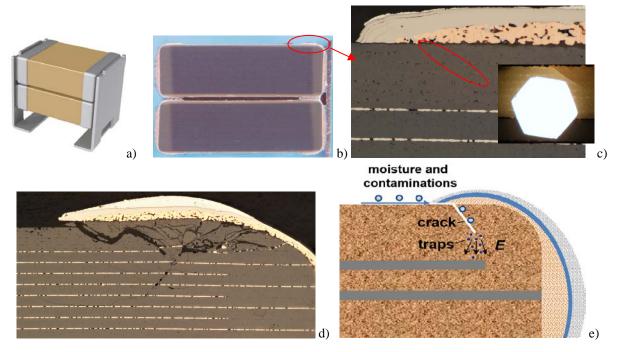

Stacked capacitors are manufactured by attaching leads to several MLCCs connected in parallel and arranged vertically one on the top of other (see for example Fig. 2.12a). This design allows for a substantial increase of capacitance at the same footprint and reduces the size of the circuit board. The lead-frame decouples mechanically capacitors from the board thus reducing microphonic noise and destructive effects of board flexing. Although the

lead-frame is attached using a high-temperature solder, the process is thoroughly controlled by the manufacturers that reduces the risk of cracking. However, shallow cracks under the terminations that are typical for most MLCCs occur also in stacked capacitors (Fig. 2.12b and c) and when the thickness of the cover plate is not sufficient, these cracks can cause life test failures as shown in Fig. 2.12d. When moisture and contaminations penetrate inside the crack, the electric field between the tip of the crack and top electrode is increased, and with time, this might cause failures according to the time dependent dielectric breakdown (TDDB) mechanism (see Fig. 12.2e).

Figure 2.12. An overall view of a stacked capacitor (a), cross-sectioning showing a thin cover plate (b) and a shallow crack under the termination (c). Fig. d shows cross-sectioning of a capacitor that failed during life testing and (e) is a schematic of the TDDB mechanism of failure.

#### Laser marking

Due to a small size, MLCCs are usually unmarked. However, some customers, prefer marked capacitors, so that they can have assurance that the correct component has been used [40]. A laser marking that is often used for plastic parts might cause damage to a ceramic capacitor in case the laser power level is above optimal (see Fig. 2.13.). Different types of capacitors use different materials and have different thickness of the cover layers and require different levels of the power setting to avoid cracking.

Figure 2.13. A capacitor damaged due to excessive power of laser marking machine.

#### 3. Testing and quality assurance

All MLCCs are manufactured using similar technological processes and materials and the difference between commercial and military or space grade capacitors is mostly in the design rules, the level of consistency of used materials and processes, and in the approach to quality assurance (QA) or amount of testing. For example, the thickness of the dielectric layers is typically much greater for military capacitors, and types of materials that are fixed for military can be changed for commercial capacitors. Stability of design and materials is important to assure consistency of characteristics and reliability of the parts, but retards innovations and improvements of performance.

Approaches for quality assurance of commercial and military capacitors are substantially different. Quality assurance of mass production commercial capacitors is based on the build-in-design approach and extensive use of the Statistical Process Control (SPC) system [41, 42]. SPC is a data-driven methodology for quality analysis and improvement that is essentially a preventive activity performed in real-time during the manufacturing process. Military specifications also require SPC system to be used, but it is not considered a major element of QA, and inability to make in-process improvements reduces substantially its efficiency. Instead, QA for military capacitors is based on extensive inspections and testing of the parts. As stated by Dan Friedlander [42] "SPC targets failures prevention, burn-in (testing) targets failures detection".

The first military specifications had been developed before the mass production era that was driven by commercial electronics market, and historically played an important role in improving quality of electronic components. Obviously, statistics was not effective without automotive process control and for low production volumes, so QA in military specifications relied heavily on testing and inspection.

Historically, majority of MLCCs used in space applications by NASA have been manufactured and tested according to MIL-PRF-123 (CKS-style) and MIL-PRF-55681 (CDR-style). In 2017 a specification for thin dielectric ceramic capacitors that includes BME-type capacitors, MIL-PRF-32535 (M32535-style) has been developed. In addition, USA, EU, and Japan space agencies have developed their own specifications (source control drawing, SCD) that extended the range of capacitors suitable for space applications: S-311-P-828, S-311-P-838 by NASA/GSFC [43, 44], ESCC-3009 by ESA [45], and QTS-2040 by JAXA [46, 47].

Capacitors developed for automotive industry are used sometimes in low-level space projects because these parts are manufactured to a higher quality standards compared to a general use commercial capacitors. Quality of these parts should be in compliance with AEC-Q200 requirements [48]. However, this document describes only general specifications for passive components, and the parts that are actually used by car manufacturers might have additional requirements detailed in non-disclosed documents.

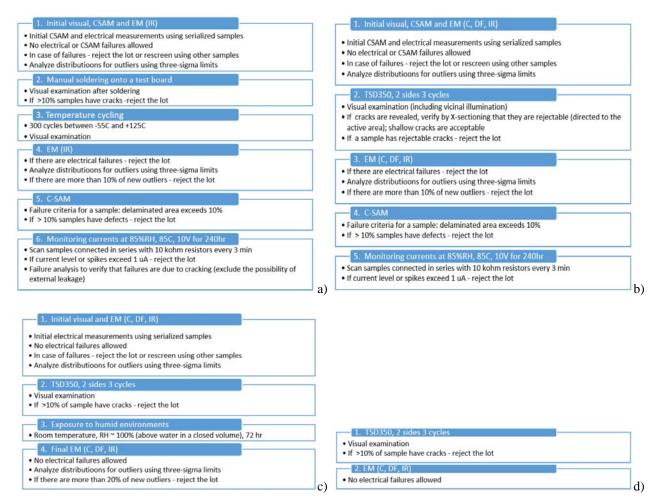

All mentioned above documents use a variety of tests and inspection procedures that generally can be divided into three groups: (i) screening gr.A, (ii) screening gr.B and (iii) qualification. Screening gr.A inspections and testing is carried out for 100% of samples in each lot and have a purpose of removing parts with manufacturing defects from the population. Burning-in is considered a major element of the screening because it supposed to prevent early, defect related (infant mortality) failures.

Screening gr.B is carried out using samples from each lot (sometimes called lot acceptance testing, LAT), and its purpose is to ensure that the manufacturer continue production of parts that conform to the specification. Qualification testing is carried out periodically using samples from some lots to confirm the required quality level for a given type of production. Obviously, gr.A screening can reveal manufacturing defects only, and the robustness of the parts towards assembly, and post-assembly stresses should be addressed by gr.B screening and qualification tests.

Note that the notion of the lot of parts for commercial components is not defined as strictly as for military components. However, considering that MLCCs are produced by huge batches and the amount of a certain type of capacitors used in a space project is relatively small, the probability of having parts from different batches is low.

#### 3.1. Comparative analysis of specifications

Tables 3.1 and 3.2 give a comparison of screening and qualification tests used in different specifications. In all documents, except for MIL-PRF-55681, there is a ban on use of pure tin for terminals' finishing. MIL-PRF-55681 has an option with pure tin, but warns against the possibility of whiskers growth. Some specifications limit the

thickness and dielectric constant of the ceramic layers and types of electrodes. For example, MIL-PRF-123 does not allow nickel electrodes and flexible terminations, limits dielectric thickness (d) to 0.8 mil, and the dielectric constant to 3000. In NASA/GSFC requirements, the values of d depend on the type of capacitors and can be as low as 0.28 mil (~7  $\mu$ m), whereas JAXA specification QTS-2040 limits d to 3  $\mu$ m. The latest military specification, MIL-PRF-32535, does not have limits for the dielectric thickness at all. Destructive physical analysis (DPA) is required by all specifications except for MIL-PRF-55681.

#### • Military specifications

Ultrasonic inspection when used for fully manufactured capacitors is limited to areas not covered by terminations, and likely for this reason, MIL-PRF-123 requires this inspection before the terminations are formed. However, formation of terminations might create a substantial stress to the capacitors and result in cracking, so the latest specification, MIL-PRF-32535, requires acoustic examinations before and after formation of terminations. Note that MIL-PRF-55681 (CDR-style capacitors) does not require ultrasonic inspection that might be the reason of several recent failures in space projects that were attributed to the presence of delaminations and cracks.

Every lot manufactured per MIL-PRF-123 and MIL-PRF-32535 specifications requires voltage conditioning or burning-in (BI) at two times rated voltage and 125 °C for 168 hours minimum. BI requirements in MIL-PRF-55681 are somewhat relaxed: (i) the duration of testing is 100 hr, and (ii) the temperature might be less than 125 °C and depends on the maximum operation temperature specified for the part. MIL-PRF-55681 also does not require DPA and thermal shock prior to BI. Considering high temperature processes during formation of terminations, the efficiency of temperature cycling before BI for unmounted capacitors is not clear.

Reliability of military grade capacitors is determined during accelerated life testing, typically at 2VR and 125 °C. The failure rate (FR) for MLCCs is usually expressed as percent failures per thousand hours of test and indicates a maximum failure rate at operating conditions that is determined in the assumption of random failures (exponential distribution) [49]. To verify reliability level of 0.001%/1000hr with 60% confidence 91.6×10<sup>6</sup> unit-hours of testing at operating conditions (125 °C and rated voltage) should be accumulated without failures (e.g. 91,600 samples during 1000 hours). The same FR level at 90% confidence would require testing of 230×10<sup>6</sup> unit-hours. To accelerate the testing, MIL-PRF-123 and MIL-PRF-55681 allow increasing test voltage two times that assumes 8X acceleration. However, even with this acceleration the testing might last more than half a year.

Capacitors manufactured to M32535 specification are not established reliability parts. Instead, two product quality levels are defined: standard reliability (M level) and high reliability (T level) that is intended for space applications. Both types are manufactured and tested similarly and the quality level is determined by (i) duration of life testing, and (ii) most importantly, by carrying out life testing on each lot of capacitors. Test duration for the T-level products is 4,000 hours for qualification and 1000 hours during gr. B screening testing, whereas qualification test for M-level capacitors requires 1,000 hours.

A sample size that is used for life testing varies from 123 for MIL-PRF-123 and MIL-PRF-32535 to 25 for MIL-PRF-5681. Also, some lots might not be tested at all (e.g. CDR capacitors manufactured to MIL-PRF-55681 specification) and they are qualified by similarity with samples from other lots representing manufacturing process over a certain period. Considering that only a small proportion of capacitors might have defects that pose reliability risks, the efficiency of life testing to reveal lots with defects, and cracks in particular is limited. This efficiency is even lower when parts are tested in fixtures or soldered onto boards at conditions that are different compared to the actual assembly of flight cards.

Table 3.1. Requirements for screening of low-voltage MLCCs

| Type<br>of      | Test                                  | MIL-<br>PRF-                                                  | MIL-<br>PRF-                          | MIL-<br>PRF-                                       | S-311-P-                                                                         | S-311-P-                                                                                | ESA<br>ESCC                       | JAXA<br>QTS-                                                             |

|-----------------|---------------------------------------|---------------------------------------------------------------|---------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------|

| test            |                                       | 123, T                                                        | 55681                                 | 32535, T                                           | 829                                                                              | 838                                                                                     | #3009                             | 2040/M                                                                   |

| Sco             | ope/limit                             | PME,<br>d $\leq$ 0.8 mil,<br>no pure tin,<br>$K_{max}$ = 3000 |                                       | No pure tin                                        | PME, no<br>pure tin,<br>d(PN), K <sub>max</sub><br>=4000,<br>X7R; 100<br>for NPO | BME, X7R,<br>d ≥ 0.28<br>mil, N ≤<br>300, Sn/Pb<br>plated                               | Type I and II dielectrics         | Sn/Pb by<br>solder dip,<br>d ≥ 3um<br>2000 < K <<br>4000                 |

|                 | C, DF                                 | 100%                                                          | 100%                                  | 100%                                               | 100%                                                                             | 100%                                                                                    | 100%                              | 100%                                                                     |

|                 | IR @25C                               | 100%                                                          | 100%                                  | 100%                                               | 100%                                                                             | 100%                                                                                    | 100%                              | 100%                                                                     |

|                 | IR@125C                               | 100%                                                          | Sample                                | 100%                                               | 100%                                                                             | 100%                                                                                    | sample                            | 100%                                                                     |

|                 | DWV/voltag<br>e proof                 | 2.5 to<br>4×VR                                                | 2.5×VR                                | 2.5 to<br>4×VR                                     | 2.5×VR                                                                           | 2.5×VR                                                                                  | 2.5×VR                            | 2.5×VR                                                                   |

| Screening, gr.A | TS and<br>Voltage<br>conditionin<br>g | 20c -55 to<br>+125C,<br>168-264hr<br>2×VR,<br>125C            | 100hr<br>2×VR, at<br>T <sub>max</sub> | 20c -55 to<br>+125C,<br>168-264hr<br>2×VR,<br>125C | 20c -55 to<br>+125C,<br>168-264hr<br>2×VR,<br>125C                               | 20c -55 to<br>+125C,<br>168-264hr<br>2×VR,<br>125C                                      | 96hr at<br>2×VR, T <sub>max</sub> | 4hr/2VR/85<br>(in-process)<br>20c -55 to<br>+125C,<br>21hr@ 3VR,<br>125C |

| 5               | PDA*                                  | 3%                                                            | 8%                                    | 5%                                                 | 5%                                                                               | 5%                                                                                      | 5%                                | -                                                                        |

| Ň               | Ultrasonic inspection                 | 100%<br>before<br>termination                                 | -                                     | Before and<br>after<br>termin. for<br>size ≥0805   | 100%<br>before or<br>after<br>termination                                        | 100%<br>before or<br>after<br>termination                                               | -                                 | 100%                                                                     |

|                 | Visual exam.                          | 100%                                                          | sample                                | 100%                                               | 100%                                                                             | 100%                                                                                    | 100%                              | 20 pcs                                                                   |

|                 | DPA                                   | ✓                                                             | -                                     | ✓                                                  | ✓                                                                                | ✓                                                                                       | ✓                                 | ✓                                                                        |

|                 | TS and Life test                      | 100c.,1000<br>hr, 2×VR,<br>125C                               | -                                     | 100c,<br>1000hr<br>2×VR,<br>125C                   | 100c,<br>1000hr<br>2×VR,<br>125C                                                 | 20c, 1000hr<br>2xVR,<br>125C                                                            | 1                                 | 25(0) pcs,<br>per JAXA-<br>QTS-2040                                      |

| gr.B            | THB/moistu<br>re<br>resistance        | 20c per<br>M202<br>TM106, 10c<br>at 50V                       | -                                     | 12(0) pcs.,<br>85C, 85%<br>RH, 96hr,<br>VR         | 20c per<br>M202<br>TM106                                                         | 85C, 85%<br>RH, 96hr,<br>VR                                                             | -                                 | 12 pcs, 20c<br>per M202<br>TM106                                         |

| Screening, gr.B | Breakdown voltage                     | -                                                             | -                                     | VBR ≥<br>6×VR or<br>1200V                          | 1                                                                                | 30(0) pcs,<br>VBR ≥<br>6xVR                                                             | 1                                 | As a part of evaluation                                                  |

| Scree           | Resistance<br>to soldering<br>heat    | -                                                             | -                                     | -                                                  | -                                                                                | 6(0) pcs,<br>M202<br>TM210, J,<br>Infared/con<br>vection but<br>1 cycle,<br>within gr.B | -                                 | 4 pcs.<br>Solder dip:<br>+260°C,<br>10s. M202<br>TM210, B.               |

|                 | HSSLV**                               | <b>✓</b>                                                      | -                                     | -                                                  | ✓                                                                                | -                                                                                       | ✓                                 | ✓                                                                        |

|                 | PRVT***                               | -                                                             | -                                     | -                                                  | -                                                                                | <b>✓</b>                                                                                | -                                 | -                                                                        |

| *PD 4 -         | percent defec                         | tives allowah                                                 | le le                                 |                                                    |                                                                                  | ,                                                                                       |                                   |                                                                          |

<sup>\*</sup>PDA = percent defectives allowable

<sup>\*\*</sup>HSSLV = humidity steady state low voltage test that is carried out at 1.3V for 240h at +85°C and 85%RH, typically using 12 samples.

<sup>\*\*\*</sup>PRVT = Process Reliability Verification Test.

Table 3.2. Requirements for qualification testing

| Test                               | MIL-PRF-<br>123, T                                                  | MIL-PRF-<br>55681                                                                 | MIL-PRF-<br>32535, T                                                                  | ESA ESCC<br>#3009                                      | JAXA QTS-<br>2040/M                                           | AEC-Q200                                                         |

|------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|

| TS                                 | -55C to<br>+125C, 100 c,<br>186 pcs                                 | -55C to<br>+125C, 5 c, 18<br>pcs                                                  | -55C to +125C<br>mounted, 100<br>c (T) and 5c<br>(M), 123 pcs                         | 10 cycles T <sub>min</sub> to T <sub>max</sub>         | 18 pcs on<br>alumina or<br>FR4, -30 to<br>+100°C x<br>1,000cy | 77(0) 1000c -<br>55 to +125C                                     |

| Life testing                       | 123(1) 1000hr<br>2xVR, 125C                                         | 25(1), 2000hr<br>at T <sub>max</sub> , 2xVR                                       | 123(1) 4000hr<br>2xVR, 125C                                                           | (20 or 40)<br>2000hr 2×VR,<br>125C                     | 123pcs.<br>1.5VR,<br>4,000h@+125°<br>C                        | 77(0), 1000hr<br>125C, VR                                        |

| HSSLV                              | <b>√</b>                                                            | <b>√</b>                                                                          | -                                                                                     | Within gr.B (10<br>TS cucles<br>before the<br>testing) | Within gr.B                                                   | ✓ (for PME only)                                                 |

| THB/moistu<br>re<br>resistance     | 20c per M202<br>TM106                                               | 20c per M202<br>TM106                                                             | 22(0), 85C,<br>85% RH,<br>1000hr, VR                                                  | -                                                      | -                                                             | 77(0), ), 85C,<br>85% RH,<br>1000hr, VR                          |

| Resistance<br>to soldering<br>heat | 12(1) pcs,<br>M202 TM210,<br>B, solder dip,<br>230C, 10sec,<br>gr.C | 9(1) pcs, M202<br>TM210, J,<br>Infared/convec<br>tion reflow but<br>1 cycle, gr.C | 22(0) pcs,<br>M202 TM210,<br>J,<br>Infared/convec<br>tion reflow but<br>1 cycle, gr.C | -                                                      | 4(0), M202<br>TM210,<br>cond.B Solder<br>dip: +260°C,<br>10s. | 30(0), M202,<br>TM210, D.<br>Wave solder,<br>260C, no<br>preheat |

| Flex testing                       | -                                                                   | 12 pcs.<br>2mm<br>deflection                                                      | 12 pcs, 2mm<br>deflection                                                             | -                                                      | 1 mm<br>deflection                                            | 2mm<br>deflection                                                |

<sup>\*</sup>The combination of the mounting process and 1 heat cycle is considered to be equivalent to 2 heat cycles.

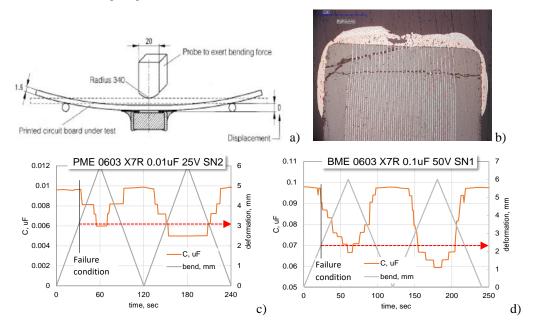

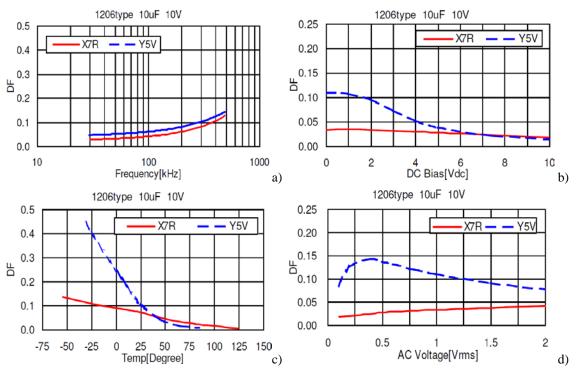

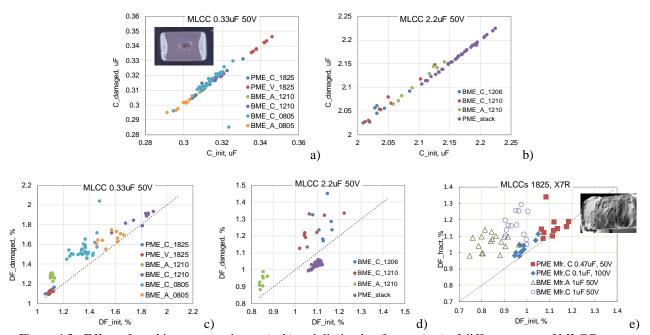

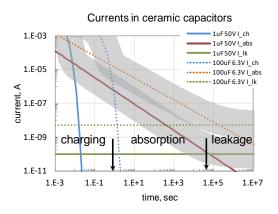

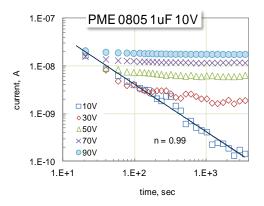

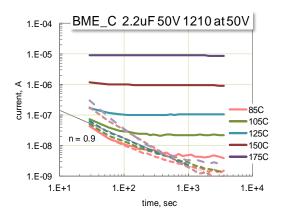

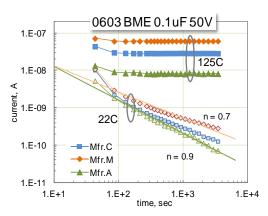

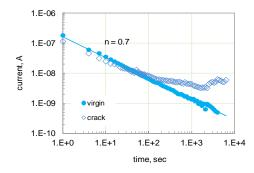

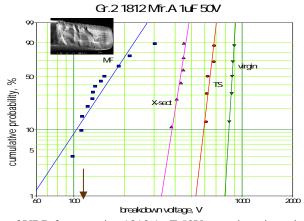

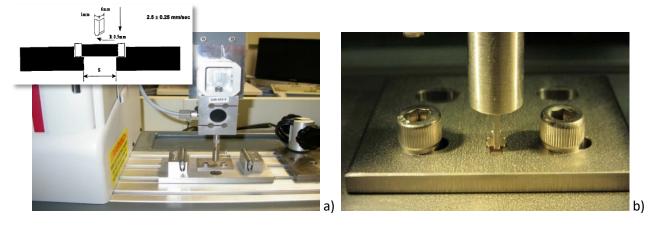

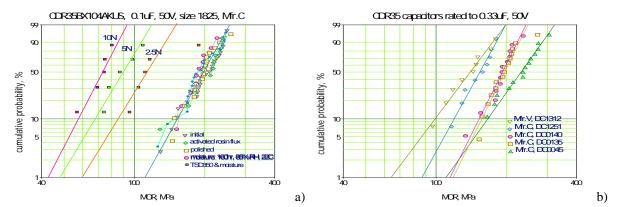

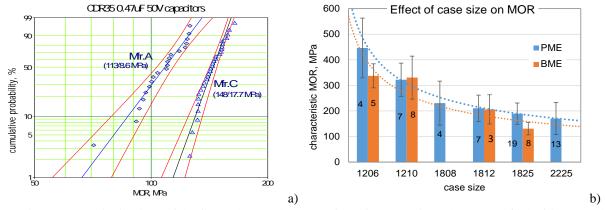

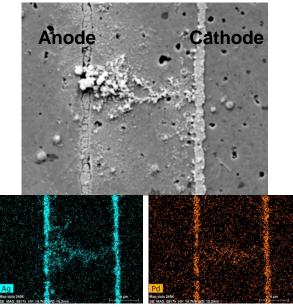

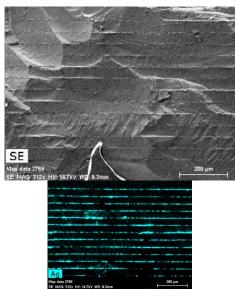

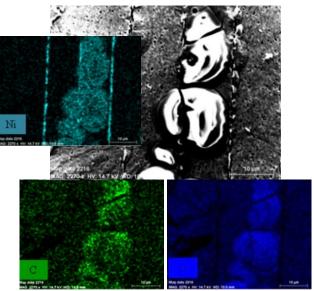

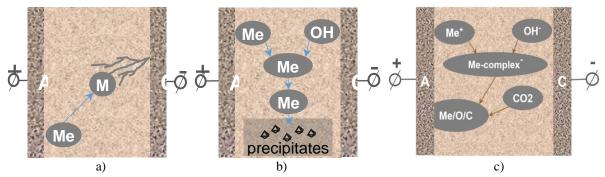

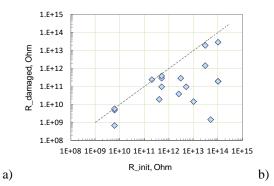

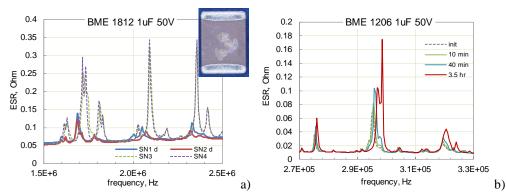

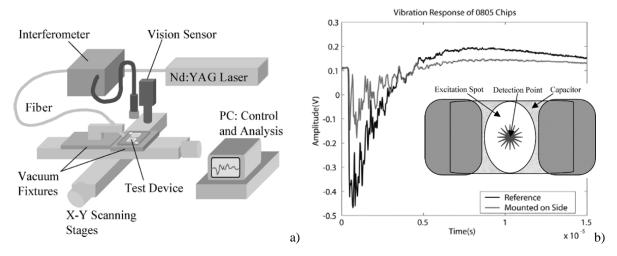

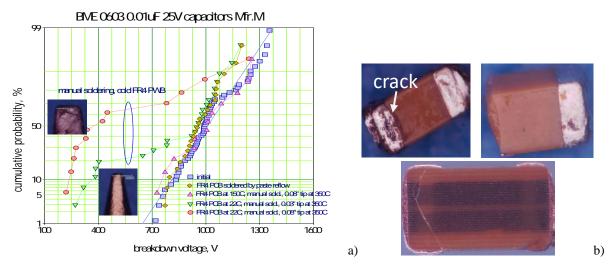

Life testing of small size thin dielectric IDC style X7S BME capacitors manufactured to MIL-PRF-32535 showed that these parts couldn't pass testing and fail after 4000 hr at 125 °C, 2VR. This was attributed to a higher acceleration factors compared to X7R capacitors with thicker dielectrics. For these parts, the exponent n in the Prokopowicz and Vaskas equation is in the range from 4.4 to 4.9 and  $E_a$  is between 1.2 and 1.6 eV, which is greater than what is usually assumed for PME capacitors ( $n \sim 3$ ). For this reason, life testing for IDC capacitors is carried out at 1.5VR [37], which is consistent with conditions used for thin dielectric capacitors by JAXA [47].