Welcome to the first annual NASA Symposium on VLSI Design. NASA's involvement in this event demonstrates a need for research and development in the area of high performance computing. High performance computing addresses problems faced by the scientific as well as industrial communities. High performance computing is needed in:

- Manipulating large quantities of data in real time

- Sophisticated digital control of space craft systems

- Digital data transmission, error correction and image compression

- Expert system control of space craft

In addition to requiring high performance computing, NASA imposes the constraint of zero power, weight and space. Clearly, a valuable technology in meeting these needs is Very Large Scale Integration.

This conference addresses important issues of VLSI design.

- Digital System Architectures

- Electronics

- Algorithms

- CAD tools

It is clear that solutions to problems faced by NASA have commercial applications. One goal of this conference is to share technology advances with the industrial community and encourage interaction between industry and NASA.

This symposium is organized by the NASA Space Engineering Research Center at the University of Idaho and is held in conjunction with a quarterly meeting of the NASA Data System Technology Working Group (DSTWG). One task of the DSTWG is to develop new electronic technologies that will meet next generation data system handling needs.

The NASA SERC is proud to offer, at its first symposium on VLSI design, presentations by an outstanding set of individuals from national laboratories and the electronics industry. These featured speakers share insights into next generation advances that will serve as a basis for future VLSI design.

Clearly there are individuals whose assistance was critical to the success of this symposium. Barbara Martin worked long hours with every single manuscript to place into proper LATEX form. Judy Wood did an excellent job at coordinating the many conference activities. The efforts of these professionals were vital and are greatly appreciated.

Our goal is to build upon this symposium in years to come and suggestions are encouraged that would allow a better symposium next year. I hope you enjoy your stay in Moscow, Idaho and I extend an invitation to visit the research laboratories during the symposium.

Gary K. Maki

880638

# Table of Contents

| Automating Analog Design: Taming the Shrew<br>A. Barlow                                                                        | 1    |

|--------------------------------------------------------------------------------------------------------------------------------|------|

| Next Generation VLSI Tools<br>J. Gibson                                                                                        | 9    |

| CCSDS Reed Solomon VLSI Chip Set<br>K. Cameron, S. Whitaker, N. Liu, K. Liu, J. Canaris                                        | 20   |

| Reed Solomon Error Correction for the Space Telescope<br>S. Whitaker, K. Cameron, J. Canaris, P. Vincent, N. Liu and P. Owsley | 32   |

| VLSI Chip-set for Data Compression Using the Rice Algorithm<br>J. Venbrux and N. Liu                                           | 41   |

| Optimal Digital Control of a Stirling Cycle Cooler<br>J. Feeley, P. Feeley and S. Langford                                     | 52   |

| Semiautomated Switched Capacitor Filter Design System<br>D. Thelen                                                             | 55   |

| Integrated CMOS RF Amplifier<br>C. Charity, S. Whitaker, J. Purviance and M. Canaris                                           | 64   |

| A Comparison of Two Fast Binary Adder Configurations<br>J. Canaris and K. Cameron                                              | - 78 |

| Self Arbitrated VLSI Asynchronous Sequential Circuits<br>S. Whitaker and G. Maki                                               | 87   |

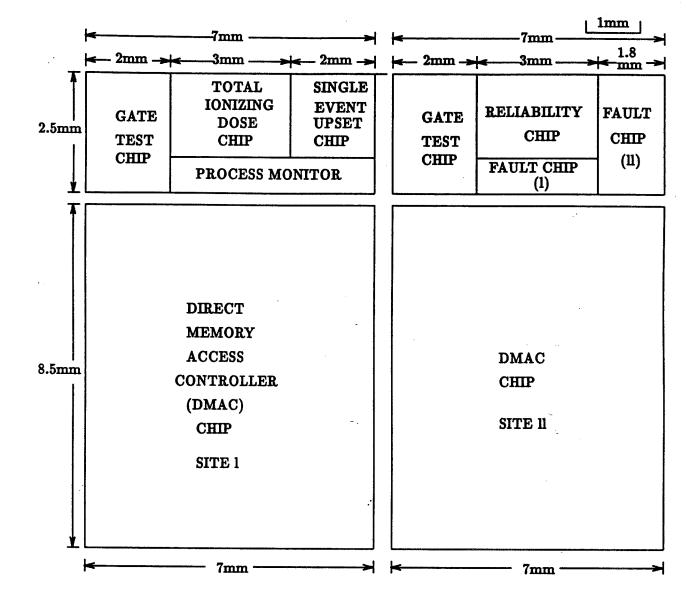

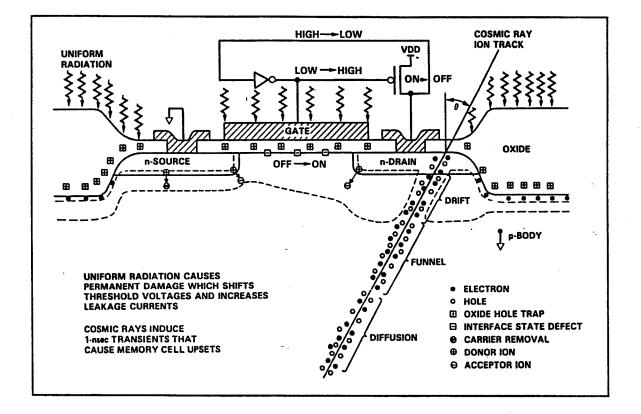

| Using Advanced Microelectronic Test Chips to<br>Qualify ASIC's for Space<br>M. Buehler, B. Blaes and Y-S. Lin                  | 105  |

| Real Time SAR Processing<br>A. Premkumar and J. Purviance                                                                      | 117  |

.

| NASA SERC 1990 Symposium on VLSI Design                                                                                    | iii |

|----------------------------------------------------------------------------------------------------------------------------|-----|

| Using Algebra for Massively Parallel Processor<br>Design and Utilization<br>L. Campbell and M. Fellows                     | 140 |

| On Well-Partial-Order Theory and Its Application to<br>Combinatorial Problems of VLSI Design<br>M. Fellows and M. Langston | 151 |

| Burst Error Correction Extensions for<br>LARGE Reed Solomon Codes<br>P. Owsley                                             | 163 |

| Performance Comparison of Combined ECC/RLL Codes<br>C. French and Y. Lin                                                   | 186 |

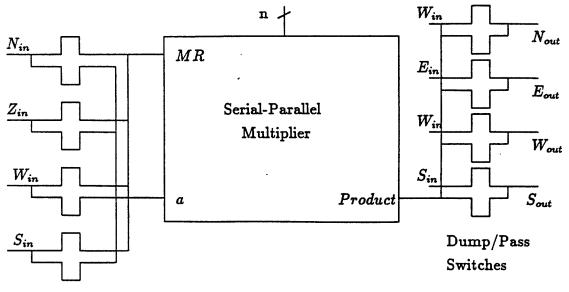

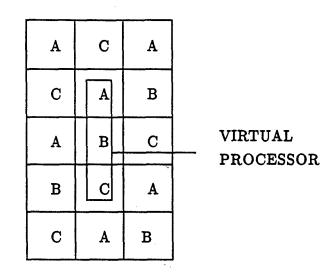

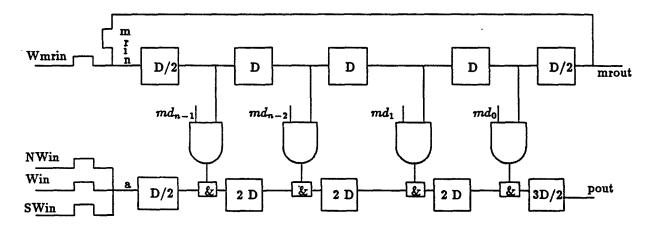

| Serial Multiplier Arrays for Parallel Computation<br>K. Winters                                                            | 197 |

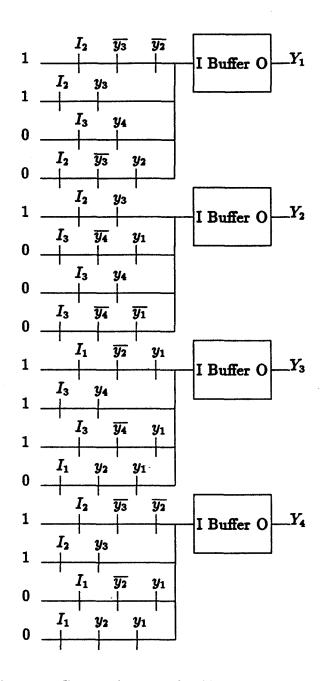

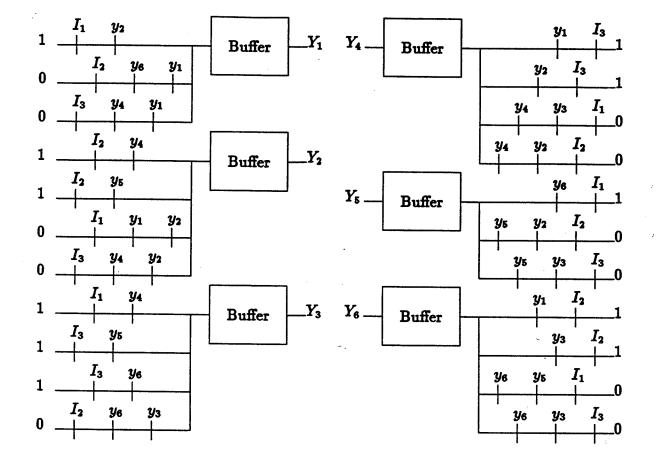

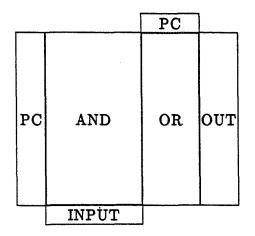

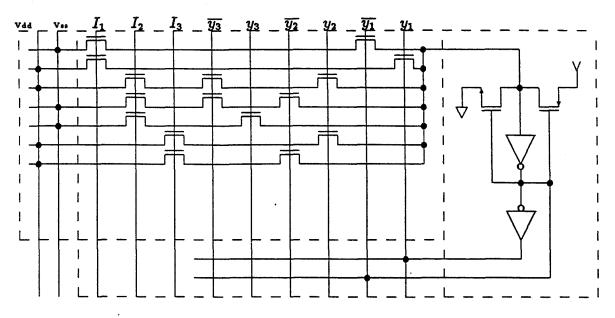

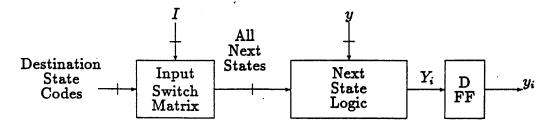

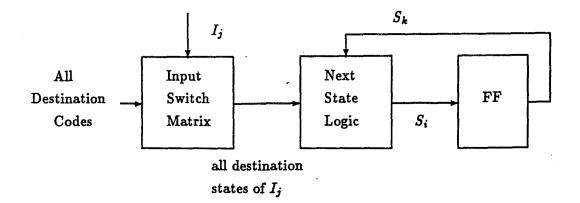

| PLA Realizations for VLSI State Machines<br>S. Gopalakrishnan, S. Whitaker, G. Maki and K. Liu                             | 213 |

| A Programmable Architecture for CMOS Sequential Circuits<br>S. Whitaker, G. Maki and M. Canaris                            | 223 |

| A Bit Serial Sequential Circuit<br>S. Hu and S. Whitaker                                                                   | 231 |

| Sequence Invariant State Machines<br>S. Whitaker and S. Manjunath                                                          | 241 |

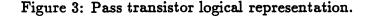

| Pass transistor Implementations of Multivalued Logic<br>G. Maki and S. Whitaker                                            | 253 |

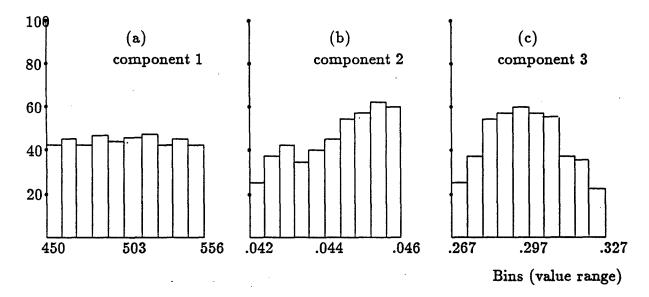

| Statistical Circuit Design for Yield Improvement in CMOS Circuits                                                          | 260 |

H. Kamath, J. Purviance and S. Whitaker

. . • • . . . . --\_\_\_\_\_ --... •

NASA SERC 1990 Symposium on VLSI Design

# Automating Analog Design: Taming the Shrew

A. Barlow Asahi Kasei Microsystems Tokyo, Japan

# 1 Introduction

The march, or rather, the sprint of progress in integrated circuits continues to amaze observers both within and without the industry. Three decades ago, a 50 transistor chip was a technological wonder. Fifteen years later, a 5000 transistor device would "wow" the crowds. Today, 50,000 transistor chips will earn a "not too bad" assessment, but it takes 500,000 to really leave an impression.

In 1975 a typical ASIC device had 1000 transistors, took one year to first samples (and two years to production) and sold for about 5 cents per transistor. Today's 50,000 transistor gate array takes about 4 months from spec to silicon, works the first time, and sells for about 0.02 cents per transistor.

Fifteen years ago, the single most laborious and error prone step in IC design was the physical layout. Today, most IC's never see the hand of a layout designer: an automatic place and route tool converts the engineer's computer captured schematic to a complete physical design using a gate array or a library of standard cells also created by software rather than by designers. CAD has also been a generous benefactor to the digital design process. The architect of today's digital systems creates his design using an RTL or other high level simulator. Then he pushes a button to invoke his logic synthesizer-optimizer tool. A fault analyzer checks the result for testability and suggests where scan based cells will improve test coverage. One obstinate holdout amidst this parade of progress is the automation of analog design, and its reduction to semi-custom techniques. While the variety and power of architectural options available to the analog designer has mushroomed, his methods remain largely unchanged from two decades ago. Synthesis by repeated trialand- error SPICE simulations is still the norm. The layout is still painstakingly handcrafted, transistor by transistor. Unlike their digital counterparts, analog first silicon that does not perform to spec is yet the rule rather than the exception. Analog design has stubbornly refused to be tamed by the array and cell methodologies that have overwhelmed the digital world. While analog cell libraries are widely advertised, in practice they find very little use [1].

# 2 What's the Problem ?

The comparatively stunted growth of analog CAD has multiple causes. Some are natural consequences of macroeconomics and of the general state of the computing industry. Others

are intrinsic to the nature of the analog problem. Still others appear to be rooted in quirks of human nature. I will focus on three of the more significant barriers.

## 2.1 Help Wanted (Semicustom need not apply)

Gate array vendors quickly learned that like the memory product business, their's is basically a simple two dimensional problem: the trade off between speed and chip area. The definition of next year's new product line is ever so predictable: more speed, higher gate count, lower cost. And they can feel confident that their's is a reasonably broad and complete product line if it includes a half dozen arrays that span the range from 1k to 50k gates. Analog, by contrast is a multi- dimensional nightmare. If we try to offer a semi-custom, structured product line containing reconfigurable analog elements, in what ratio should we include amplifiers, capacitors, resistors, switches, free transistors, matched pairs, etc. How many different combinations constitute a complete family of such analog arrays? In our amplifier cell library, what combinations of DC gain, bandwidth, noise, PSRR+, PSRR-, common- mode input range, offset voltage, settling time etc. are required? In a phase-locked- loop, what combinations of center frequency, capture range, hold range, jitter immunity, no signal frequency drift, output phase angle, etc. will suffice? Do next year's improvements target lower power, noise, matching accuracy, higher speed or something else?

#### 2.2 Where are the experts?

While digital design is as exciting and challenging, and even more economically rewarding, it differs from analog in a very fundamental way: it is not conceptually taxing. Digital systems may be mathematically sophisticated, but given a system design, the logic synthesis and layout is not mathematically challenging. We teach digital theory in its entirety to college freshmen. Digital's complexity and challenge is more akin to that of a large and involved cost accounting system than it is to analog design.

This essential difference in the nature of the problem has a very natural and interesting consequence: the digital world is readily comprehended by computer scientists and programmers who lack explicit training in electronic theory and its prerequisite mathematics. Thus those who best know how to create computerized automation can (and do) address themselves to the digital problem.

Analog automation on the other hand, demands a marriage of a circuit design expert and a design automation (computer) expert. As a species, analog designers still think of themselves, perhaps correctly, as artists, and are wary of the inevitable degradation and inelegance of an automated version of their craft. And as artists, they tend to enjoy the challenge of specific design situations, and the creation of entirely new architectures more than the broad, accountant-like thought process that must reduce a range of previously invented possibilities to fixed design procedures. The result of this incompatibility is that few really excellent analog designers, who are scarce breed to begin with, have found their way into the design automation field.

#### 2.3 An expert is not enough

Even given the mathematical prowess of expert designers, the fact remains that many analog design problems are too involved to be reduced by manual methods to tractable solutions. Traditionally much of the designers' skill has been the paring of the problem to a manageable essence. And despite his best efforts, a large dose of trial and error remains. Can we automate trial and error? The answer is certainly "yes", but only at the price of enormous computing power. Computerized search algorithms rarely have the same degree of intelligence guiding the sequence of trials, and must make a far greater number of poor choices before arriving at a suitable solution.

To summarize then, pivotal barriers to progress in analog design automation include the lack a suitable methodology, and the lack of experts willing to take on the task of automation. Given capable people and plausible methodologies, a further problem remains: the algorithm maker needs tools to help him do previously unmanageably complex mathematics. Finally, even given that tool, the task demands access to fabulously large computing power. The good news: all of these barriers are beginning to crumble.

## **3** A Light at the End of the Tunnel

While arrays and standard cells have proven ineffectual in the analog domain, a slight variation on the concept, standard generators, holds excellent promise. This is not a novel concept: it has been applied to the physical design of standard cell libraries for 6-7 years. In this discussion, I expand the usual definition of a generator to include the design process as well as the layout, and propose that we think of them not only as tools for library generation, but also as custom design aids.

Like standard cells, generators are usually based on fixed circuit schematics, (though algorithmic arraying can also be included under this same label). But unlike standard cells, the component sizes are not predetermined and the layout is not fixed. Generators can have either of two distinct functions: component size determination based on performance specifications, and physical layout. By introducing the flexibility of variable device sizes, a vastly broader range of specifications can be addressed. The concept is hierarchically extensible: macro generators can call lower level generators to create their subcomponents.

Aiding the design automator's modeling efforts, a viable first generation of symbolic mathematics software has appeared in the last several years. These are as yet immature and require a good deal of training to use. And quite properly, they have not attempted to supplant the need for mathematical understanding by the user. But even in this infant stage they offer significant benefit in addressing very complex math problems. One aspect in which they prove particularly useful is in keeping track of the signs and coefficients of problems with many variables. For example, the algebraic (not numeric) solution of a ten by ten determinant would be a year's work by manual methods. These new tools compute the twenty-something page result in an hour on a personal computer.

Lastly, it should be apparent to the most skeptical observer that the age of boundless computing power is upon us. Five years ago, thirty engineers time-shared a 5 MIPs, 4

4

Meg RAM minicomputer. Today each has a 10 MIPs, 16 Meg machine sitting on his desk for his personal use. Within 5 years it will be a 100 MIP, 64 Meg superworkstation. In a single decade we will have transitioned from a world where CPU time was a dominant resource limitation to a time where it is a non-issue. Automated trial and error will be both wonderfully rapid and virtually free.

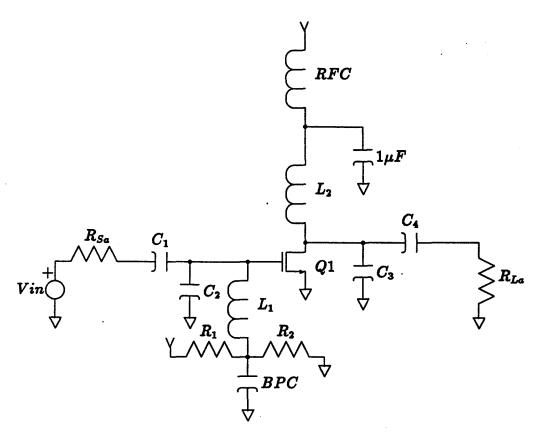

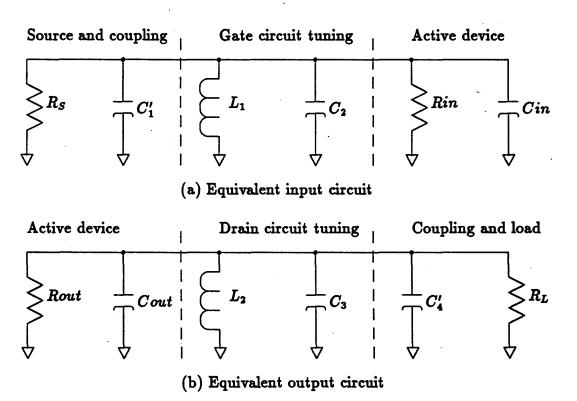

Exploiting this new computing muscle, a viable first generation of analog synthesis tools has begun to emerge. Carnegie-Mellon University researchers have created an op amp synthesizer capable of creating a very broad range of high performance custom amplifiers [2]. It hierarchically builds on generator submodules as small as matched transistor pairs and complementary drivers. Keying on various specification criteria, the system makes repeated educated guesses in determining both the device configuration and the device sizes. Based more, but not entirely on fixed amplifier schematics, CSEM (Switzerland) has created a tool that algorithmically sizes op amps, comparators, and even a few larger analog blocks such as sigma-delta converters [3]. It follows the design with a high quality automatic layout that is sensitive to analog design issues, and is interactively changeable by the user. Adding switched capacitor filter synthesis and layout to the CSEM tool, Silicon Compiler Systems is introducing the first fully featured commercial analog synthesis tools. The overall system behaves very similarly to a switched capacitor synthesis system previously reported by Asahi Kasei Microsystems (Japan) [4].

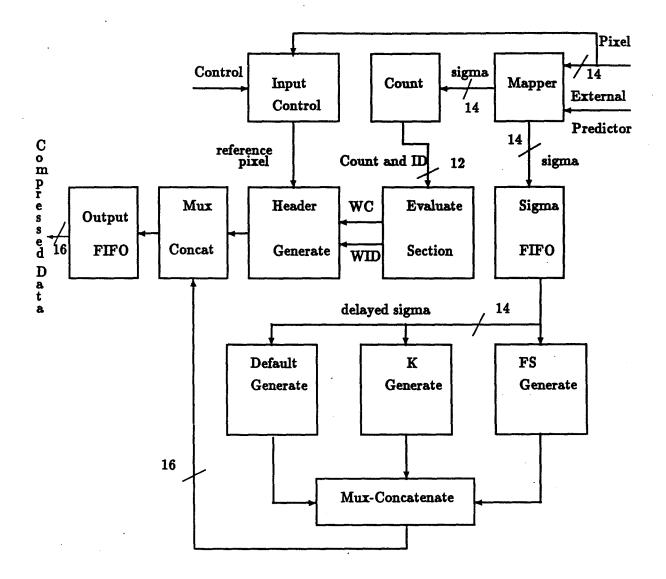

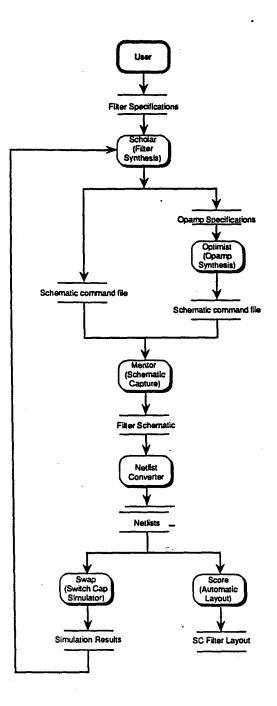

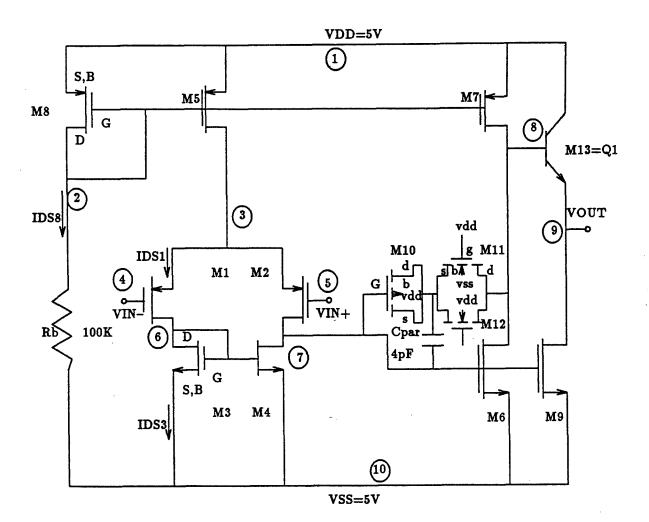

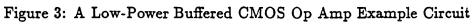

# 4 An Example: Asahi Kasei Microsystems' SCF Design System

Harnessing the power of recent workstations to implement the algorithmic guesswork of a non-linear programming numerical optimizer, and drawing on the modeling potential of symbolic mathematics tools, the Asahi Kasei system well illustrates the current stateof-the-art in analog design automation. The system integrates three new design modules into the design environment: a filter synthesizer (SCULPTOR), an op amp synthesizer (OPTIMIST), and a switched capacitor circuit layout synthesizer (SCARLET). A fourth required capability, op amp layout generation, has been implemented using a cell layout generation system similar to commercially available generator tools.

### 4.1 Automated Filter Design: SCULPTOR

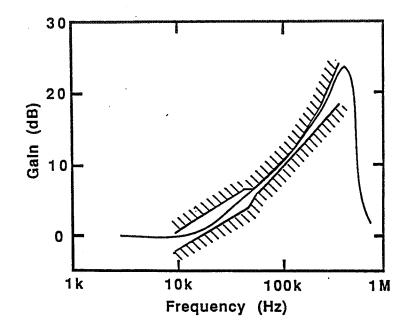

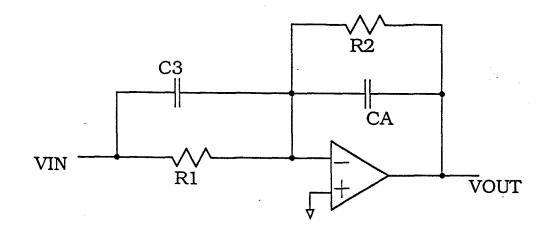

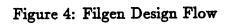

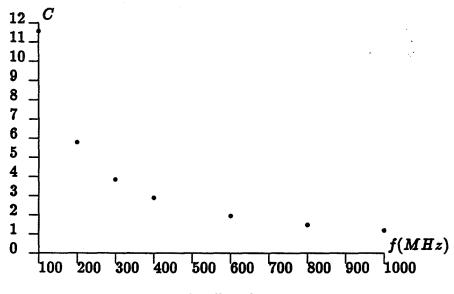

The filter synthesizer is employed for both gain and delay designs. Filter order and coefficients may be determined either by classical approximations or by the numerical optimizer. This later choice allows optimization of particular specs. For example, the user may choose to minimize Q, and hence noise and sensitivity. Delay equalization filters are also designed using the numerical optimizer. The optimizer is particularly valuable in the design of nonstandard filter functions. In telecommunication applications, gain equalization filters that compensate for frequency dependent line attenuation are often required. Since no formal mathematical solutions to these functions exist, designing them manually is a long and tedious trial-and-error process. SCULPTOR's optimizer created a filter with the transfer characteristic of Figure 1 in five minutes on a SUN4-260.

SCULPTOR's analysis includes all key non-ideal effects: capacitor mismatch, both amp and switch noise and amplifier finite gain. Filters are implemented as composites of single stage, biquad, interpolator and cosine filter sections. Programmable gain functions can also be automatically included in the design, thanks to SCULPTOR's embedded mixedmode switched capacitor / logic simulator. Filter sections may be analyzed separately or as cascaded composites. SCULPTOR outputs a captured schematic, op amp specifications to the amplifier generator and a netlist to the filter layout synthesizer.

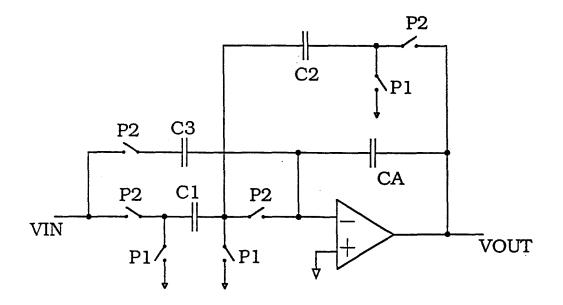

#### 4.2 Automated Amplifier Design: OPTIMIST

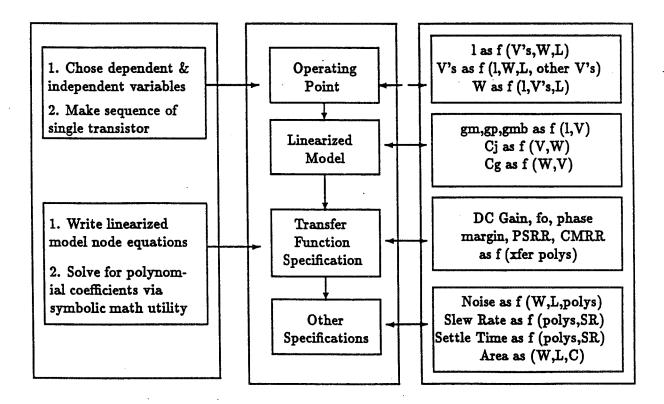

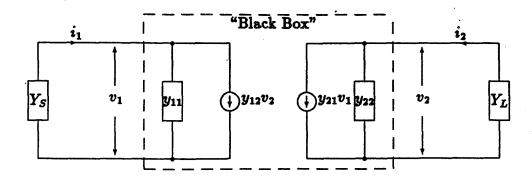

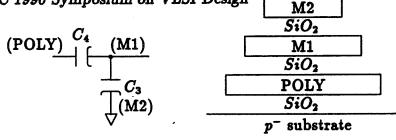

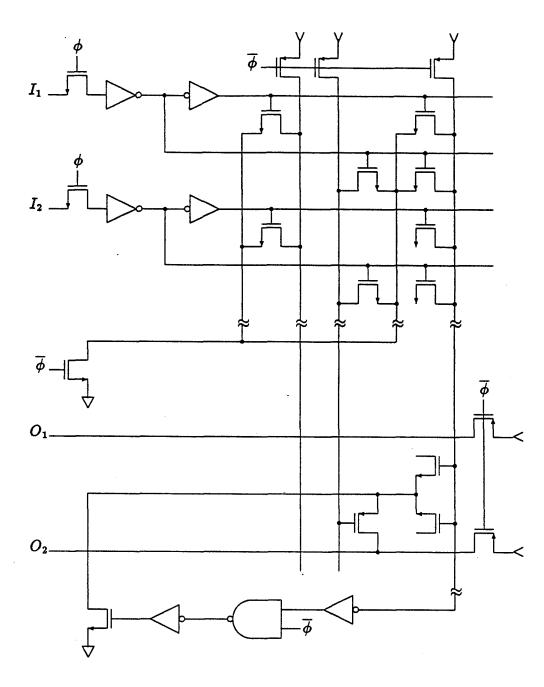

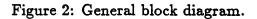

Also based on numerical optimization methods, OPTIMIST sizes the devices of amplifiers and switches to meet a specification received from SCULPTOR. Min/max limits on gain, bandwidth, noise, PSRR, etc. are inputs; device sizes and actual performance to spec are outputs. Using analytic models based on SPICE-like IV equations, and by including high order poles and zeros in the analysis, the result matches full conventional simulation very closely - within a fraction of a decibel for gain functions, and within 1 degree for phase. The creation of analytic models of this complexity is an entirely impractical task by manual methods. For OPTIMIST, the modeler employs a symbolic math modeling tool to create the transfer functions. Input is a set of node equations. Output is the transfer function polynomial coefficient expressions. Figure 2 summarizes the nature of OPTIMIST's modeling structure.

Each of OPTIMIST's design generators has a corresponding cell layout generator. The design and layout generators are correlated to have matching diffusion areas, etc., thus assuring correct modeling of parasitics.

While it has proven very helpful for amplifier design, and greatly accelerated a user defined trial-and-error process, OPTIMIST is a prime example of the need for still more computation speed in workstations. A full optimization search in OPTIMIST can take up to 30 minutes on a SUN4-260. This is acceptable in some instances, but detracts from the interactive feel that such tools should ideally have.

#### 4.3 Automated Switched Capacitor Circuit Layout: SCARLET

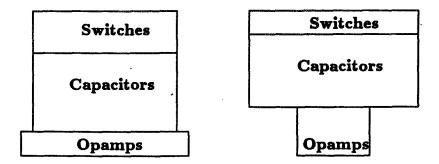

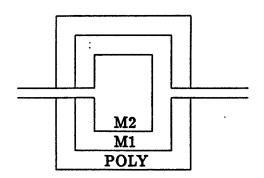

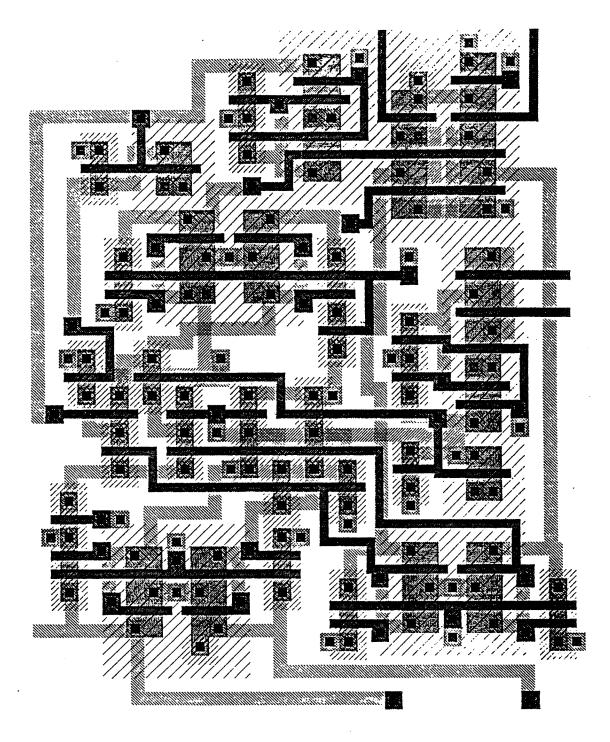

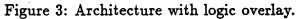

SCARLET's layout capability is not limited to SCFs: it compiles any circuit comprised of op amps, switches and capacitors. It's ability to draw circuits, properly considering noise and crosstalk, stems from an intelligent preanalysis of the netlist to be drawn. Prior to layout, SCARLET decomposes the network into clusters of elements connected to charge sensitive nodes. Having thus analyzed the circuit, SCARLET can create the physical layout with the same attention to signal crossing of critical nodes as would a human layout expert. The resultant physical design is of comparable quality and density to hand drawn filters. Figure 3 is an example of a SCARLET layout for a 6th order bandpass filter. It took 7 minutes on a VAX 8650.

## 5 On the Horizon

The wealth of existing analyses of amplifiers and filters as well as the pervasiveness of their use made them ideal candidates for automation in this first generation. But many other common functional blocks also hold promise for reduction to automated techniques. ADCs, DACs and PLLs all seem amenable to automation via the principles described above. The computational problem will be more severe, but well within the capabilities of the coming generation of workstations. The mathematics to model these is also more difficult, but they can be attacked by an ever more potent arsenal of analysis aids. And the proliferation of CASE tools is beginning to relieve the tedium of many programming tasks, leaving algorithm creation as the dominant task of the CAD developer. This may incline more analog artists to take up the challenge of analog CAD.

The shrew now has a tamer, and the tamer has a whip.

# References

- [1] In a panel discussion about analog design methodologies at the 1989 IEEE CICC, representatives of three leading ASIC vendors, Sierra Semiconductor, IMP and AMI all admitted that while they have created analog cell libraries and actively market them, in actual practice, the cells are rarely reused without modification to fit each new application's requirements.

- [2] R. Harjani et. al, "A Prototype Framework for Knowledge-Based Analog Circuit Synthesis", IEEE DAC, pp. 42-49, 1987

- [3] M. Degrauwe et al, "IDAC: An Interactive Design Tool for Analog CMOS Circuits", IEEE JSSC, vol SC-22, no. 6, Dec. 1987.

- [4] A. Barlow et al, "An Integrated Switched Capacitor Filter Design System", IEEE CICC, 4.5.1, 1989.

Figure 1: Gain Equalization

Figure 3: Generated layout for a 6th order SCF. Opamps and switches are represented by shaded bounding boxes

NASA SERC 1990 Symposium on VLSI Design

# **Next Generation VLSI Tools**

J. Gibson Hewlett Packard Company Disk Mechanism Division Boise, Idaho

Abstract – This paper focuses on what features would be useful in VLSI Computer Aided Design Tools and Systems to be used in the next five to ten years. Examples of current design tasks will be used to emphasize the areas where new or expanded VLSI CAD tools are needed.

To provide a basis for projecting the future of VLSI tools, a brief history of the evolution of VLSI design software and hardware platforms is presented. The role of design methodology is considered, with respect to the anticipated scale of future VLSI design projects. Future requirements of design verification and manufacturing testing are projected, based on the challenge of surviving in a competitive market.

Examples of VLSI design and related issues are centered primarily on cell library based structured custom design. Structured custom design implies the use of a hierarchical block organization in the implementation of a complex IC. The perspectives of what capabilities are needed in future VLSI tools reflect the author's involvement on VLSI design teams developing integrated circuits for disk memory and other computer peripherals, in the last eight years.

## **1** Introduction.

The transition from nicely manageable, fully synchronous structured custom designs to mixed synchronous/asynchronous digital designs, coupled with analog and digital functions on the same die, will require considerable investment in tools and engineering skills. More engineers will become involved in high speed digital designs, requiring more analog circuit expertise.

The requirements of new products will determine the methodology necessary to produce cost effective and timely VLSI designs. The increasingly difficult demands on design verification will require simulation capability well beyond the limits of current tools. The manufacturability of complex integrated circuits becomes even more important as computer peripheral product volumes go from a few thousand units per month to tens of thousands or hundreds of thousands of units per month.

The capability of tools available to VLSI designers is increasing rapidly, but the management of large complex projects still requires considerable investment. Marketplace pressures are requiring shorter IC development times, with the need for perfect first pass parts growing dramatically. Cost issues are pushing chip architectures towards the most efficient and cost effective chip layouts, involving more custom design. Full custom design or library cell based structured custom design requires the best possible tool environments

to support a skilled design team. Future VLSI tools will need to effectively address the needs of full custom IC designers, to help provide a competitive edge in the marketplace.

The following discussion highlights VLSI CAD tool issues in the design capture, verification and testing processes of integrated circuit development, as encountered in several product development cycles at Hewlett Packard's Disk Mechanism Division. The requirements for next generation VLSI tools will be projected, at least from one organization's point of view.

## 2 History.

It is difficult to imagine a more dynamic area of technological development than computer aided design, with VLSI design being at the forefront of the CAD evolutionary process. Every VLSI chip project since the early 1980's has been accompanied by a new generation of computers, graphics tools and peripherals, usually a new operating system, and new VLSI software tools that often required a change in the design methodology used by the IC development teams. The rapidly changing tools made it difficult to anticipate technical issues and almost impossible to accurately predict project completion dates. VLSI manufacturing processes and design parameters were changing at an equally fast rate. The growth rate of most electronics companies has been very high in the last ten years. Consequently, many new engineers have been introduced into this complex, dynamic environment. The only thing different between the early 1980's and the late 1980's, is that the rate of change of IC technology, software tools and systems has further quickened. This rate of technological change appears to be permanently increasing, a bit more rapidly each year. It is the product of an amazingly competitive marketplace and a very diverse range of applications of VLSI technology.

Just ten years ago, many IC's, some of significant complexity, were still composed by hand, using tape and mylar film and requiring several years to be completed. The work was exhausting, tedious and very error prone, regardless of the methodology. The first CAD systems were minicomputer or mainframe systems with a rudimentary graphics capability. A typical collection of software included not much more than a layout rule checker, an analog simulator (SPICE) and a unit delay switch type digital simulator and possibly a graphics based schematics editor. No tools existed to compare a schematic netlist verified by simulation to the netlist extracted from a layout. Huge plots of chips were generated, spread on the floor, and sometimes four or five manual checking cycles, involving different people for each cycle, were necessary to find mismatches between schematics and layouts. Manual artwork verification of digital designs continued into the early 1980's, and is still important in analog designs.

The early minicomputer and mainframe based CAD systems generally cost \$250,000 or much more, permitting only large corporations to participate in VLSI design. The systems would support only a few users, and the tasks had to be kept small, since the CPU's could easily be overloaded. Disk memory storage devices were expensive and not as reliable as today's products. One CPU handled all tasks and the only way to communicate with other remote systems was with expensive modems on costly leased phone lines. Cost limited the number of graphics terminals, as most engineers used RS-232 terminals. Early computer aided design methodologies were developed primarily by experienced designers who learned integrated circuit design in the 1970's, using calculators and second generation minicomputers with limited software. The VLSI tool limitations caused the development of a rigorous and efficient design methodology which was, and still is, the best way to achieve success.

CAD really started to be a factor when machines that could be called workstations finally began to appear on the market. These machines combined a sharply reduced cost of computing power with a mix of features that fit naturally with engineering groups designing ICs. Workstations began to provide a hardware and software system of interactive desktop machines, of affordable cost, connected to a local area network to provide transparent access to data and programs in real time. This development gradually eliminated the need to go through time-consuming departmental minicomputers or to use mainframes for batch processing. Providing each engineer with a graphics terminal quickly became affordable, and greatly improved productivity. Additional processing power could be added incrementally. Although it could be debated in some respects, probably the first 32bit graphics workstation to be shipped was the Apollo DN 100, the first of which was shipped in 1981. This was the earliest machine on the market that had most of the features of today's workstations. Some of the earlier proprietary machines changed so much between generations, that the older hardware was obsoleted at the end of a project, which was not unusual up to about 1987. UNIX became more common, providing a multiuser, multitasking environment ideal for engineering tasks. Software from several vendors slowly became available on most workstations. Networking allowed the sharing of computer and peripheral resources, which made it possible to apply every machine on a network to a time critical set of tasks.

VLSI CAD technology is hardly ten years old, but several revolutions have already taken place. The tremendous rate of hardware development, however, seems to have outpaced the development of software tools. The productivity of one engineer has probably increased several hundred to a thousand times the rate possible just one decade earlier. There is a good chance that the rate of productivity could increase nearly as much in the next ten years. Most of the VLSI CAD tool vendors are still enhancing their first generation products or are just beginning to introduce second generation products. Even large, diversified electronics companies are recognizing that the continuing investment in VLSI CAD tools is too large to justify only in-house use.

## **3** Platforms.

In 1980, a minicomputer with a quarter of a megabyte of random access memory was considered a powerful machine. This larger than average minicomputer may have had 50 to 100 megabytes of disk memory. The CPU was probably a sixteen bit machine, with no cache, some DMA, and moderate I/O data transfer rates, with a generalized performance rating of about 500,000 instructions per second. The graphics screens may have had about 535 by 390 pixels of display capability, with a slow re-windowing rate. All hardware attached to the minicomputer probably was designed for that particular machine. IC's designed for disk memory devices in the early 1980's ranged in complexity from 5000 to 35,000 FETs.

The slightly above average workstation in 1990 will probably have 16 to 32 megabytes of RAM, one or more 700 megabyte disk drives, 64 to 256 thousand bytes of cache, a 32 bit CISC CPU with 20 MIPS performance or a RISC CPU of about 35 MIPS, and 5 megabyte per second I/O data rates. Most graphics terminals will have 1280 by 1024 pixel display capability, with the top end at 2048 by 2048 pixels. The graphics display will be handled by a separate processor system. In addition, industry standard interface busses permit the attachment of peripherals and specialized processors from a number of vendors. The integrated circuits designed in the late 1980's for disk memory devices ranged from 30,000 to 70,000 FETs for most designs, with one close to 380,000 FETs. Other organizations have developed designs of about 750,000 FETs.

What might the fairly well loaded workstation look like in the year 2000? Some of the possibilities include maybe a gigabyte of RAM, 10 gigabytes of solid state disk, 100 or more gigabytes of disk memory, two or more CPU's, each providing 300 to 400 MIPS, plus several processors facilitating communications with peripherals. Fiberoptic I/O should be much less expensive than it is today and should make possible I/O rates to peripherals of 50 to 100 megabytes per second, the limit being the rate that the peripherals can accept data. Inexpensive multiscreen graphics systems that allow the viewing of artwork, schematics, and textual simulation data simultaneously might be possible. Each screen may be able to display 4096 by 4096 pixels, and almost certainly will provide integrated video capability. Some of these projections may actually be on the conservative side, given the current rate of progress in the computer industry. Disk memory peripherals may not require IC's of greater than 200,000 to 300,000 FETs, but the shorter development times possible with more powerful VLSI tools and computers will be needed. Such workstations could easily support the development of IC's of greater than 1,000,000 FETs.

The future use of networks could contribute as much to productivity as will the increasing power of workstations. Network computing will require much more sophisticated software to effectively utilize multi-CPU workstations in a LAN environment. The network will likely contain several types of specialized processors that are very effective in processing some of the VLSI design tasks, especially compute intensive tasks such as artwork design rule verification. It will be difficult for software technology to keep up with hardware technology. Software technology will probably set the pace of productivity improvements in the next ten years.

The continual improvement of workstations will force most design groups to consider new equipment every three or four years. The issues of obsolescence and return on investment will probably not diminish in the next ten years. Competitive pressures will continue to shrink product lifetimes, making it mandatory to keep design productivity as high as possible.

# 4 Methodology.

Many large, complex designs have been entirely synchronous, since the cost and performance has been acceptable. Synchronous designs generally involve considerably less risk than asynchronous designs and are much easier to test. The methodology of synchronous structured custom IC design involves defining a set of specifications for a cell library that will allow the product performance and cost goals to be met. Then a cell library is constructed, so that each cell can be used in a design as a building block, with known limits for it's use. System designers generally work at the cell level and above, leaving cell circuit design to one or two experts. Individual cells are designed to specification by a FET circuit expert, using an analog simulation tool such as SPICE. Within a synchronous system, the cell design is fairly straightforward, since a fixed period of time is available for budgeting delays in the implementation of a cell. Cell loading is fairly predictable, since each type of cell is used in a regular structure. The types of cells are divided into four general groups: datapath (registers and arithmetic functions); programmable logic arrays (state machines); input/output (I/O pads); and testability circuits. For synchronous design, this basic methodology is not anticipated to change very much for future designs. Improvements are anticipated in the areas of test coverage, test time and overall cost per function.

The need for lower cost and large product volumes are making higher levels of integration more attractive each year. The smaller physical size of each generation of disk drive is requiring much smaller printed circuit assemblies. Where the 20 to 50 megabyte 14 inch disk drives of 1980 contained electronics on about 400 square inches on several circuit boards, 1989's 380 to 760 megabyte 5.25 inch disk drives are limited to 44 square inches on one board. The 3.5 inch and 2.5 inch drives of the future will require about the same amount of electronic functionality on printed circuit boards of well under 10 square inches. Rather than build disk drives with essentially perfect read/write heads and media, error correcting circuits are making possible lower cost means of achieving demanding error rate limits for disk products.

Nearly all of the digital functions in disk drive electronics, other than memory devices and microprocessors, have already been integrated in gate array, standard cell and structured custom circuits. Some performance and cost advantages can be obtained by merging some of these circuits together, but many of the benefits of digital integration have already been gained. The next step in the integration of disk electronics involves either more analog integration, or the conversion of currently analog circuit techniques into an acceptable digital form. Large complex analog circuits are still difficult and time consuming projects, which are very hard to fit into the short development times permitted for new disk products. The number of expert analog IC developers is very small. It is likely that few analog IC experts are also expert analog read/write or servo control designers. Servo control has been largely moved into the digital domain, by using commercial digital signal processor circuits. DSP architectures allow the flexibility needed to optimize servo performance, but are still somewhat expensive. Analog servo control IC's are available, but are limited to certain types of mechanisms and performance ranges. In order to reduce the number of components on disk drive circuit boards, integrated circuits involving synchronous and asynchronous timing with some analog functions on chip, will be necessary in the next five years. Some examples of these complex designs are beginning to appear, mostly from analog circuit vendors. In order to continue to be successful in the development of complex mixed-methodology custom IC's, engineers will have to identify a methodology that partitions asynchronous and analog design into manageable sections. Managing the complexity of asynchronous designs will involve testing the boundaries of asynchronous and synchronous circuits, along with understanding the limits of the internal design of the asynchronous circuits. The main issues facing the mixing of analog and digital design on the same chip involve testability of the analog functions and overall yield or cost, due to the large number of processing steps for such IC's.

The implications for designers of mixed-methodology IC's include possibly larger design teams of people with a wider range of skills. The need for digital systems designers will continue, since pure digital design will continue to have the lowest cost per function and the widest range of application. Designers will have to know both synchronous and asynchronous (or timing) simulators to adequately verify future designs. Analog designers will be needed for the interfaces to mechanical devices that can't be handled digitally. Each of the above trends will require more investment in cell libraries used for structured design.

Analog effects will become more significant as overall system clock rates continue to increase. Where the 3 micron circuits of 1980 could be designed to operate at 10 mega-Hertz, today's 1.0 micron circuits are being designed for 30 to 40 megaHertz operation. In 1990, most circuits could be designed in .8 micron processes that will support 60 to 70 megaHertz system clocks. The .5 micron circuits of the mid-1990's will probably support 100 megaHertz system clock speeds. In the area above 30 megaHertz, secondary analog effects are already significant in most circuits. Inductance, parasitic capacitance, signal cross-coupling and other effects can have serious influence on circuits. More complicated analytical techniques, such as transmission line analysis, and more use of analog simulators could become common. Digital simulators that are aware of secondary analog effects may be needed for the higher speed designs.

The challenge for IC design teams in the next five to ten years will be to carefully identify the kind of IC's that will be needed in a particular kind of product, and then develop a strong methodology around the chosen technologies and design tools. It appears that the analog content of future designs will increase, unless good digital algorithms can be found to replace currently analog functions. Several vendors have tools that can provide the proper design environments, but choosing a tool set is only the start of the process of building an integrated circuit design methodology.

The future development of computers and peripherals is much easier to project than the future development of software tools and environments. The effort put into software in the next ten years will become an even larger portion of VLSI design system development costs. But, just as the hardware developers have drifted toward somewhat standardized architectures and interfaces, VLSI software tool developers are defining standards for interfacing some of the tools used for VLSI design. Frameworks or platforms upon which tools of various capabilities can be attached, with a reasonable investment, appears to be the path to the future. As long as the interfaces between the platforms and the tools are fairly simple, and the connections fairly loose, then considerable flexibility could be gained. Some past attempts at large tightly coupled VLSI design tool sets either lost all performance advantages or became too large to manage. If a design tool platform is to be effective, most of the bandwidth of the workstation involved should be handed over to the specific tool currently being used, keeping platform overhead processing low. It seems inevitable that VLSI design software tools are going to grow in size as more services are provided, and overall productivity should gain accordingly.

## 5 Verification.

Efficient verification of integrated circuit design is made possible by having many strengths and few weaknesses in the design methodology used to implement an IC. The random logic design of the early microprocessors have given way to the highly structured RISC processors of today. The use of pin level high speed testers has been complemented with scan path circuitry on chip. The synchronous unit delay digital simulators used for much of the 1980's are gradually being replaced with event wheel timing simulators, using rise and fall time delays, and several levels of drive strengths. Fet level only simulators are being supplemented with simulators that can mix FET, gate, and functional or behavioral models in one simulation.

How will design verification be improved in the 1990's? It is likely that one answer will involve the efficient management of even more complex designs. The structure of future integrated circuits will need to be partitioned to whatever level is needed to keep each circuit blocks small enough for an engineer to work with efficiently. Too many blocks can become a file system nightmare, and too few blocks can cause tools to be slow processing blocks that are too large. It's a matter of knowing the design, hardware platform, and software tool practical limitations. Hierarchical design is fairly well developed now, and should improve with higher speed networks and file servers.

Just as the logical structure of an IC is partitioned into hierarchical blocks, the verification effort can be similarly structured. Behavioral modeling can be used in the top down analysis to help determine how the functions of an IC are to be implemented, before all of the lower level circuit detail is invented. During the bottom-up implementation phase, FET level modeling is generally used to make sure that the performance of the lowest level blocks is exactly as desired. As the major blocks of a chip come together, the opportunity exists for using a functional representation of a block rather than the FET representation, to increase simulation speed. In order to insure that a functional block exactly matches the operation of a FET level representation, it should be easy to switch representations. If extensive testing is necessary to verify the design, more higher level functional modeling may be feasible, depending on the project schedule, the simulation execution time, and engineer workloads. Each level of logical representation requires additional verification, so much in some cases, that functional modeling may not reduce overall design verification time. High performance workstations on a network can greatly extend the utility of a low level simulation environment, if the simulation task can be shared between machines. Given personal preference, most design groups will find different paths to efficient design verification.

One of the growing needs for verification is the modeling of functions external to an IC. For example, if an IC has a Small Computer Systems Interface (SCSI), which has several asynchronous control lines, how is verification accomplished? One of the present techniques is to write vectors that cover all of the SCSI command and data operations. Such an approach can be made to work, but is fairly inflexible, since only one sequence of events is provided. Another approach is to interface the simulator to other workstations via the network and sockets, so that vectors can be computed based on previous simulation results. The use of sockets is flexible enough, but the performance can be slow. Another option that holds promise is to write functional models within the simulation environment that represent the SCSI operations. If a flexible language is used, such as "C", then almost any operation can be synthesized. This approach appears to have promise for representing the disk drive features necessary for the complete operation of an interface, formatting, and error correcting integrated circuit.

Going one more level up from the integrated circuit verification effort, the process of developing the drive electronics microprocessor firmware has become one of the more schedule critical tasks on recent projects. Quite often, firmware development is dependent on all of the drive electronics being functional. Firmware is usually developed using the real disk electronics, including any custom IC's and a functioning disk mechanism. Building breadboard prototypes is no longer practical, as breadboards have become too complex to build quickly, and the function of breadboards rarely matched that of the IC's. But, if the firmware development team could interact with a model that exactly represents the function of a custom interface IC, after the IC functionality has been frozen, but before IC silicon is available, firmware development may be able to start several months earlier than possible now. The IC model simulation performance has to be sufficient to allow the firmware developers to make reasonable progress on a daily basis. As high a level model as possible of a chip will be needed to have any possibility of being fast enough for firmware development. High level simulations may be able to take advantage of multiprocessor workstation architectures, where independent IC functions can be implemented in different processors, to emulate the parallel processing inherent in the IC itself. Such a verification environment would mean using much the same software techniques used now, but partitioning that software between several processors. Interprocess communication would have to be very efficient. Some VLSI tool environments that allow firmware developers to access IC models are beginning to be marketed at this time. Tools that allow firmware and IC design to interact will improve the ability of product development teams to reach optimal software/hardware partitioning in system designs.

More detailed extraction of layout capacitance will be needed to use timing simulators effectively, especially as system operating speeds increase. A delay calculator that considers the fan-in and fan-out for all cells in asynchronous circuits should be based on detailed layout and interconnect capacitances, and provide data that can be easily inserted into a simulation model of an IC. Such a tool will be needed for the accurate verification of unclocked standard cell blocks, included in a largely synchronous chip, that provide fast asynchronous control response. Pieces of such delay calculation and simulation capability exist now in some tool environments, but the process is not completely automated at this time.

One of the major problem areas of current IC design involves still requiring the engineer to invent a set of vectors that prove that a given circuit performs exactly as intended. As circuits become more and more complex, the possibility of undiscovered functional flaws increases. The need exists for tools that will help the engineer understand the bounds of a design, by asking questions that the engineer may not have considered. The most vulnerable areas of a design are on block or system boundaries, where specifications may be imprecise or incomplete. Expert systems tied to automatic vector generators that can be directed to part or all of a design may be an effective way of improving circuit quality.

Only in the last year or two has the time required to define and verify a simulation model of an integrated circuit been shorter than the time to build and verify the circuit layout. For a completely new IC design of the type used in disk drives, the definition phase is about 8 months and the implementation phase about 5 months. It seems likely that in the future, the implementation phase will become shorter, especially for largely synchronous designs, as VLSI tools improve and workstations gain in performance. Very soon, the length of the definition phase will need to be reduced. Some improvement can be made through better use of existing tools, such as functional simulators. But the opportunity for entirely new tools, using the computational power that will be available in the 1990's, that manage most of the details of a model, so that the engineer can concentrate on the function of a design, should be welcome. Considerable software tool help will be needed to maintain short schedules if large amounts of asynchronous logic or analog circuits are added to designs.

## 6 Testing.

From 1980 to about 1987, integrated circuit test cost was a small fraction of the total manufactured cost of most custom IC's used in disk drives. For most of the \$100 NMOS circuits, a test cost of \$6 to \$8 was not unusual. As the total IC cost was brought down, the test cost remained somewhat constant, and now is about 30% of the price of some custom IC's. The overhead expenses associated with IC testing are increasing gradually, making it difficult to achieve further IC cost reductions. At the same time, the much larger production volumes of recent years have added more emphasis on test coverage, tending to increase tests costs further. The issues of having synchronous, asynchronous, and analog circuits on the same chip could easily increase test costs even more.

Higher production volumes have focused attention on the rate of line scrap, which involves parts that fail to work at the final stage of assembly of a printed circuit board. Where a rate of 1% to 2% was once at least tolerable, when production volumes were about 1000 units per month, goals now are set at a few hundred parts per million, about .03%. Production volumes greater than 100,000 units per month will require line scrap rates of less than .01%. The higher production volumes make it easier to purchase faster test equipment, but much more engineering effort is still required to improve test coverage.

One high production volume part has shown that just one test methodology may not be enough to achieve 100 ppm line scrap rates. This standard cell part was designed with scan circuitry access to almost all nodes, with automatic test vector generation used to achieve greater than 99.7% node coverage. When run on production lots, the scan path vectors produced about a 5% test escape rate. In a simultaneous effort, pin level parallel testing was implemented on the same chip, with somewhat better than 70% node coverage. When run at the normal operating speed of the chip, the parallel vectors also produced a test escape rate of nearly 5%. The conclusions derived from these tests indicated that, since the scan testing was based on stuck-at faults, and was not run at the full operating speed of the chip, several high impedance shorts and some open circuits were probably missed. In the parallel testing, incomplete node coverage allowed some faults to slip through. Running both tests has, in fact, nearly reached the design goal of 100 ppm line scrap rate, with a reasonable overall test cost. The overlap of the two test methodologies appears effective in catching more of the failure modes of CMOS IC's. It also shows that going from 99.7% node coverage to 99.999% node coverage for scan testing is probably not worth the effort. Similarly, going from 70% to 90% or higher for parallel test node coverage may not reduce the test escapes by very much.

Fault simulators are very effective in reducing line scrap rates of IC's but the use of only the stuck-at models misses shorts and opens, which can be some of the more significant fabrication problems in CMOS today. Fault simulators need to be provided, for example, with pairs of signals that are close together in routing channels for a 100 microns or more, so that tests can be generated for signals that may be shorted together by metal stringers or other flaws. The problem is that signals that are in routing channels may come from distant blocks that have no relation to each other, and have lengthy initialization sequences. Such lengthy tests can raise test costs quickly. One alternative is to avoid the use of layouts that require the use of long routing channels. Another choice may be to back further away from minimum design rules in routing channels, which could easily increase the silicon cost.

Board level scan testing, based on the IEEE 1149 standard, will no doubt see considerable development in the 1990's. Board testing that involves complex custom IC's can be difficult. If a test fixture cannot report which part has failed, the printed circuit manufacturing line tends to remove the most complex IC on a board first, in the hope that a test failure can be quickly fixed. The problem is that the removed part doesn't get a second chance, and goes into the line scrap bin, accompanied with very little or no diagnostic data. The proposals for an industry standard printed circuit board boundary scan methodology could help manufacturing lines, by providing more tools to identify when a complex IC has failed. With surface mount parts preventing as many board tester contact points as were possible with through-hole parts, boundary scan may be a big help towards improving printed circuit diagnostic capability. In theory, the boundary scan protocol of a printed circuit board could permit scan access to some blocks within the complex IC's, which could further improve the location of failure mechanisms. The use of built-in self testing and firmware that is downloaded into RAM may add more flexibility to printed circuit board testing in the future.

Another diagnostic tool that could see considerable use in the future is the phase contrast scanning electron microscope. This equipment is capable of displaying a video interpretation of the surface of a portion of a chip on one screen, and a symbolic layout of the same portion of the chip in a second screen. A virtual probe can be used on the SEM display to see the voltage at any point on the surface of a passivated or non-passivated chip. A high speed parallel tester drives the pins of the chip with a repeating pattern. Even the voltage profile along interconnect can be observed. Delay times can be measured, so that new circuits could be characterized in considerable detail. The symbolic layout is used to locate noncontact probes on specific circuit nodes on the actual chip surface. A particular net of the circuit can be selected and highlighted in the layout, and the SEM processor will find and magnify the same area on the actual chip. Defects could be found by comparing voltage levels on the test chip with reference levels. This kind of capability suggests a common data base between the test and the design environments. Integrated design, test and manufacturing support tools will be increasingly valuable in the future.

## 7 Summary.

The VLSI tools developed in the next decade could easily increase one engineer's productivity by two or three orders of magnitude. The measurement of that productivity increase will probably not be solely in terms of FETs per day, but more likely in the ability to set and meet schedules, create highly manufacturable designs, and to produce manufacturable parts on the first pass through the fab. The VLSI design engineer may well be part of a small team, consisting of engineers that are specialists in using one or more VLSI software tools. More analog design skills will probably be needed.

The path to the most cost effective designs will very likely continue to be full custom or structured custom design, with the use of logic synthesis tools or function generators at the block level. Mixed asynchronous, synchronous and analog circuits will appear on more IC's. Higher speed designs will certainly require more attention to be placed on secondary analog effects in digital circuits.

In the next decade, the potential exists for single chip designs to replace almost all of the electronic components of present disk memory devices, at all levels of performance. The intensely competitive disk drive market suggests that shorter development schedules are most important, with cost and manufacturability following closely. Technology choices are going to be influenced heavily by potentially very large production volumes. These issues will no doubt be true for much of the electronics industry.

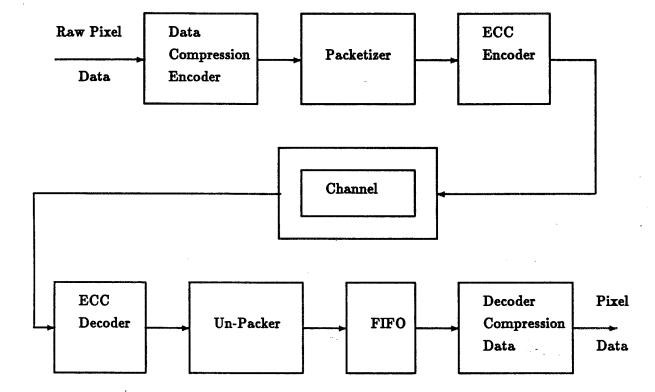

# N94- 71077

# **CCSDS Reed Solomon VLSI Chip Set**

K. Cameron, S. Whitaker, N. Liu, K. Liu and J. Canaris

NASA Engineering Research Center for VLSI System Design University of Idaho Moscow, Idaho 83843

Abstract – A highly efficient error correcting code has been selected by NASA as a CCSDS standard: the 16 symbol error correcting Reed Solomon code. A VLSI implementation of this decoder is described in this paper. A total of 4 full custom VLSI chips are needed that correct data in real time at an sustained rate up to 80 Mbits/second.

## 1 Introduction

A Reed Solomon (RS) code has been selected by both the European Space Agency (ESA) and NASA [1] as the outer code in a concatenated coding scheme for CCSDS space communications. This Reed Solomon code is a (n, n-32) block code of 8-bit symbols capable of correcting up to 16 symbol errors; n assumes values less than or equal to 255. When n < 255, a shortened code is generated which is desirable for certain applications.

Several VLSI implementations of the decoder have been presented in the literature. The first by Liu [2] required 40 VLSI chips with 100 support chips and operated at a 2.5 Mbit/second rate. Another VLSI implementation was suggested by Shao et. al. [3] with no performance data given. Both of these designs utilized systolic arrays. The design presented in this paper does not utilize systolic arrays but rather is a set of custom VLSI chips. Moreover, the architecture is invariant for any RS code defined over  $GF(2^8)$ .

The VLSI architecture requires a small chip count and guarantees real time decoding for data rates up to 80 Mbits/second. The design presented in this paper achieves the data rate with 4 VLSI chips.

## **2** Code Specification

The RS code used can be described with the following parameters and notation:

| Symbol           | Definition                                                         |

|------------------|--------------------------------------------------------------------|

| q                | the number of bits in each symbol                                  |

| $n \leq 2^{q-1}$ | the number of symbols per RS codeword                              |

| t                | the number of correctable symbol errors                            |

| 2 <i>t</i>       | the number of check symbols                                        |

| k = n - 2t       | the number of information symbols                                  |

| c(x)             | the code block represented as an order $n-1$ polynomial            |

| m(x)             | the k information symbols represented as an order $k-1$ polynomial |

| g(x)             | the order $n - k$ generator polynomial                             |

For the code under consideration, q = 8 and t = 16.

### 2.1 Code Description

The RS code word is defined as:

$$c(x) = x^{2t}m(x) + m(x) \mod g(x).$$

(1)

Simply stated, every valid code word is a multiple of the generator polynomial g(x). In its simplest form, the generator polynomial is defined as

$$g(x) = \prod_{i=0}^{2t-1} (x - \alpha^i) = \sum_{j=0}^{2t} g_j x^i$$

(2)

where  $\alpha$  is a primitive element of the field.

A more general form of the generator polynomial is defined as:

$$g(x) = \prod_{i=s+1}^{s+2t-1} (x - \beta^i) = \sum_{j=0}^{2t} g_i x^i$$

(3)

where s is an offset and  $\beta$  is a primitive field element equal to  $\alpha^h$ . This form is the one used by NASA and ESA, where  $\beta = \alpha^{11}$  and s = 112. Symmetrical coefficients of g(x) result in an offset of 112 [1].

#### 2.2 Decoding Algorithm

During transmission, errors can occur due to noise in the channel which is equivalent to an error polynomial being added to the code polynomial c(x). Let the received polynomial be:

$$R(x) = c(x) + E(x) = R_{n-1}x^{n-1} + \dots + R_1x + R_0$$

(4)

where E(x) is the error polynomial, n < 255 and each  $R_i$  is a field element. Symbols  $R_i, i < 32$ , are the check symbols. The first step in the decoding algorithm is to calculate the syndromes. The syndrome polynomial is defined as:

$$S(x) = R(x) \mod g(x) \tag{5}$$

and contains the information needed to correct errors and/or detect the presence of an uncorrectable error. Each byte  $S_k$  of the syndrome polynomial is defined as:

$$S_{k} = \sum_{i=0}^{n-1} R_{i} \beta^{i(k+1)}, \qquad (6)$$

where  $0 \le k \le 2t - 1$ . The syndrome polynomial can be expressed as:

$$S(x) = \sum_{k=0}^{2t-1} S_k x^k.$$

(7)

The next step is to obtain the error location  $\lambda(x)$  and error magnitude  $\Omega(x)$  polynomials. These polynomials have the following relationship with the syndrome polynomial:

$$S(x)\lambda(x) = \Omega(x) \mod x^{2t}$$

(8)

The error location and error magnitude polynomials can be obtained by using Euclid's greatest common divisor algorithm [4], which is a recursive operation. The algorithm is described later.

Once the two polynomials are known, the location and magnitude of a given error is found as follows:

Let  $\beta^i$  be a zero of  $\lambda(x)$  (i.e.  $\lambda(\beta^i) = 0$ ), then the error magnitude at location n - i - 1 is:

$$\frac{\Omega(\beta^i)}{\lambda'(\beta^i)}\beta^{112i} \tag{9}$$

where  $\lambda'(x)$  is the first derivative of  $\lambda(x)$  with respect to x.

For more details and examples, the reader is referred to Clark and Cain [4].

#### **2.3** Mathematical Considerations

Each of the 255 8 bit symbols of the code polynomial are members of the finite Galois Field GF(2<sup>8</sup>). A Galois Field can be defined by an irreducible polynomial p(x) [4]. For the field under consideration,  $p(x) = x^8 + x^7 + x^2 + x + 1$ . Addition of field elements is accomplished by bit-wise modulo 2 addition (exclusive-or).

Multiplication of field elements is a bit more complicated. If each of the two field elements is represented as a polynomial of order 7, then the product is accomplished by multiplying each of the polynomials modulo p(x). The result is an order 7 polynomial, which represents a field element.

Multiplication by a constant is a special case which is used frequently in the implementation of the encoder/decoder. Multiplication by a constant is a unary operator that operates on a polynomial representation of the field element. The operator can be represented by an 8 by 8 matrix that maps the polynomial onto its final representation [5,6].

Moreover, it is possible to allow the code to be described in a dual basis [7]. A dual basis is actually just another representation of the original field. If v is a q bit symbol in

the original representation of the field, it can be represented by the vector v' in the dual basis. The relationship between v and v' is

$$v' = Tv$$

and  $v = T^{-1}v'$

where T is a linear operator in the field. Any operator L in the original representation of the field can be used in the normal representation by transforming it as follows:

$$L_{dual} = T L_{original} T^{-1}.$$

(10)

A single chip implementation of the encoder that produces RS block codes in the dual basis has been implemented [5]. The decoder described here operates in either the dual basis or regular representation.

### **3** Architecture

The architecture and cell design are crucial factors in efficient use of silicon area. Cell interconnect is the most important issue in efficient chip design. Interconnect can consume major portions of a chip and greatly limit the amount of circuitry that can be placed on a chip. The objective in the design here was to minimize the amount of cell interconnect.

One of the major problems to overcome in using a Reed Solomon code is the large number of operations that must be executed to perform error correction. The operations that must be performed for each message are:

| Syndrome   | evaluation of 32 equations of order 254                      |  |

|------------|--------------------------------------------------------------|--|

| Euclid     | recursive evaluation between polynomials of degree 32 and 31 |  |

| Polynomial | 256 evaluations of polynomial of degree 16                   |  |

|            | 256 evaluations of polynomial of degree 15                   |  |

|            | 256 evaluations of polynomial of degree 15                   |  |

| Correct    | 256 divisions and additions of field elements                |  |

The number of operations for each of the above modules is:

| Module     | Number of Operations |

|------------|----------------------|

| Syndrome   | 16,320               |

| Euclid     | 693                  |

| Polynomial | 20,736               |

| Correct    | 1023                 |

| Total      | 38,772               |

Table 1: Number of Operations per Module

The number of calculations per message in the CCSDS code is 38,772. Operating at 80 Mbits/second, the number of operations per second is 1.5 billion. Clearly, this operation rate cannot be realized with a stored program computer.

| Module     | Gate Equivalents | Transistors |

|------------|------------------|-------------|

| Syndrome   | 35,860           | 143,442     |

| Euclid     | 29,400           | 117,600     |

| Polynomial | 61,040           | 244,160     |

| Correction | 5,236            | 20,944      |

Table 2: Standard Cell gate Equivalents

| Module     | Transistors |

|------------|-------------|

| Syndrome   | 26,100      |

| Euclid     | 61,900      |

| Polynomial | 27,600      |

| Correct    | 23,200      |

Table 3: Custom Transistor Count

VLSI is one approach to implementing high performance Reed Solomon decoders. There are three technologies for realizing VLSI: Gate arrays, standard cells and full custom. The first two approaches are relatively easy to implement but are limited in both performance and complexity. The CCSDS decoder would require approximately 131,000 gate equivalents, not counting necessary ROM and RAM. Clearly, it is impossible to realize the entire decoder on a single chip using standard cells or gate arrays. The next step would be to try to partition the decoder into separate modules. Shown below are the gate equivalents and number of transistors using standard cell logic needed to realize the CCSDS decoder:

Full custom VLSI yields higher performance and greater density. Shown below are the number of transistors required to realized the CCSDS decoder with full custom VLSI.

Notice that the full custom approach requires only 138,800 transistors compared to 526,146 using standard cells.

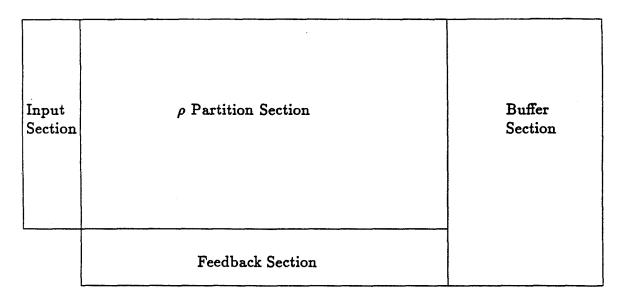

The above system resides on 4 full custom CMOS VLSI circuits. The critical element in achieving high level integration is to implement a custom architecture that produces highly dense circuits. Approaches that are effective using discrete MSI or SSI logic do not result in similar saving in full custom VLSI. One such example involves selecting the generator polynomial. In discrete logic, selecting a symmetric generator polynomial results in major savings [7]. However, in VLSI, this savings does not materialize [5,6,8]. Reducing interconnect is a major concern and therefore it is often more efficient to replicate a functional unit like a multiplier than it is to attempt to share it. Sharing a multiplier will greatly increase interconnect which consumes more area and also increases the capacitance values thereby reducing speed.

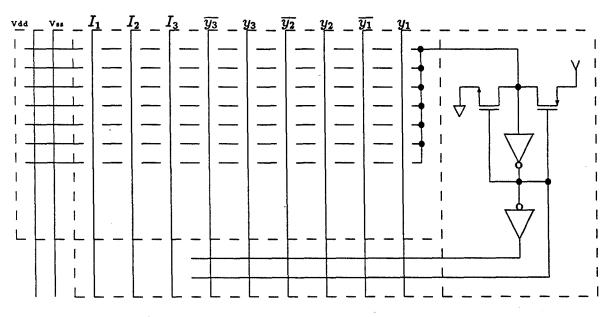

The VLSI cells used throughout the decoder consists of the following Galois Field

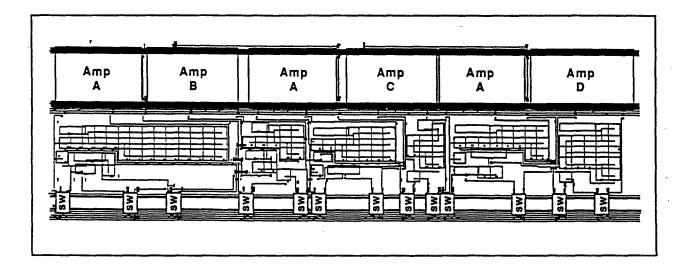

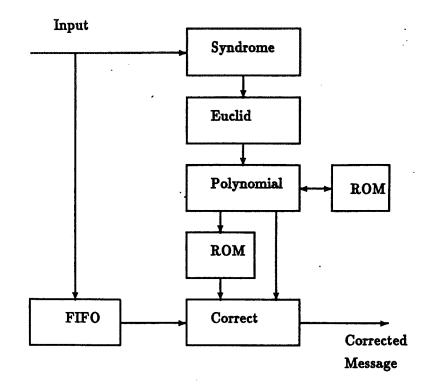

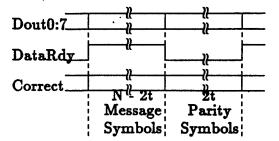

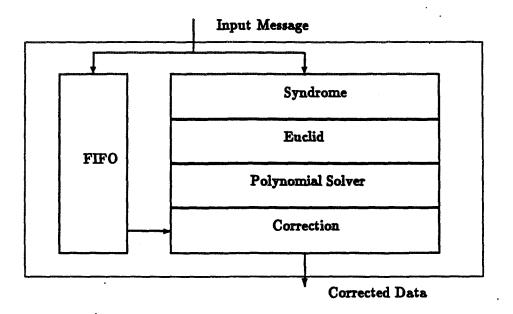

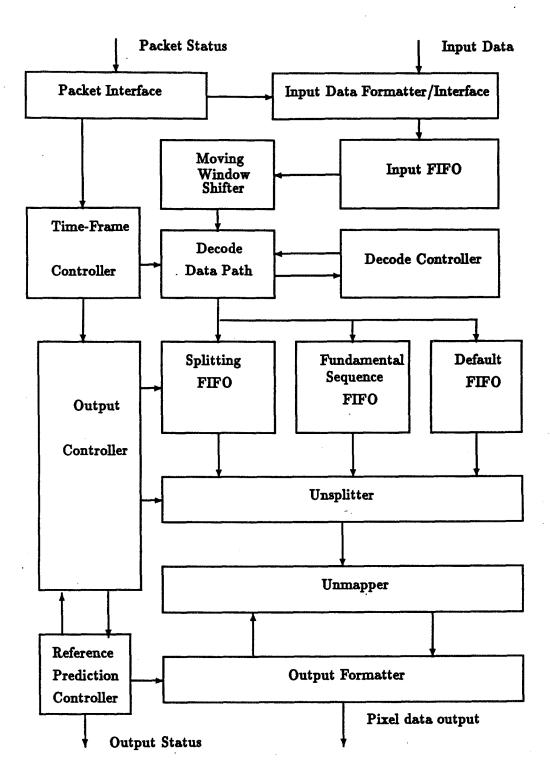

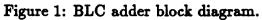

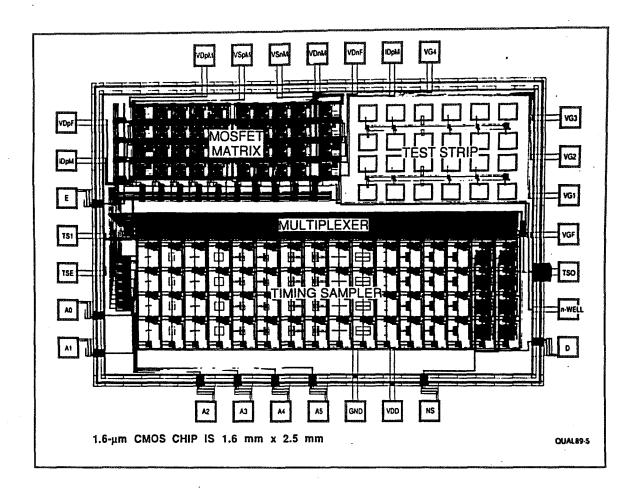

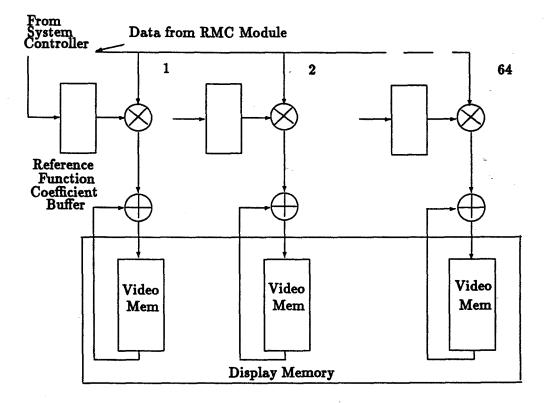

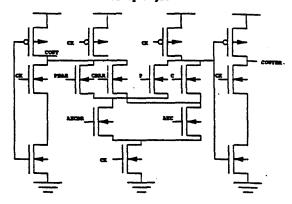

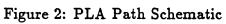

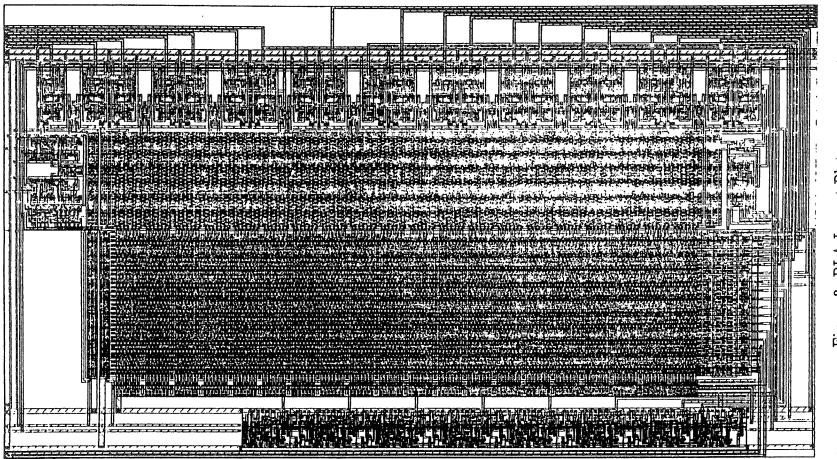

Figure 1: Reed Solomon VLSI System

processing elements: adder, constant multiplier, general multipler, and field inverse. The constant multipler performs the operation c x, where c is a constant and x is a variable; the general multiplier performs the operation  $x_1x_2$  on variables  $x_1$  and  $x_2$ .

## **4** System Architecture

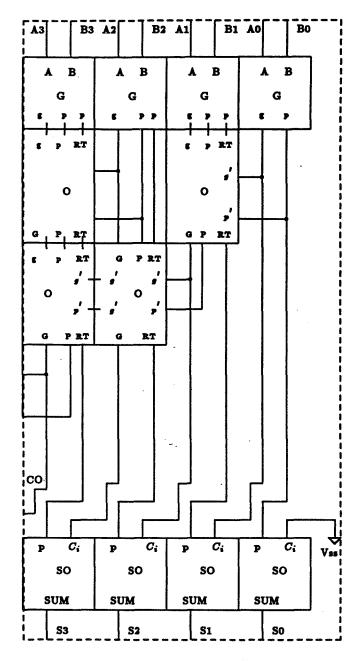

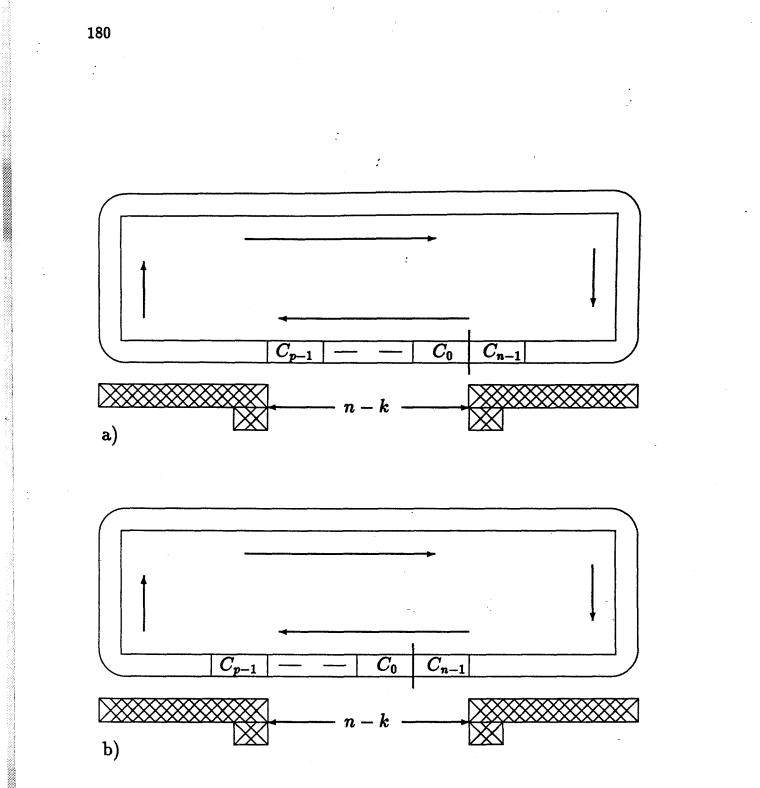

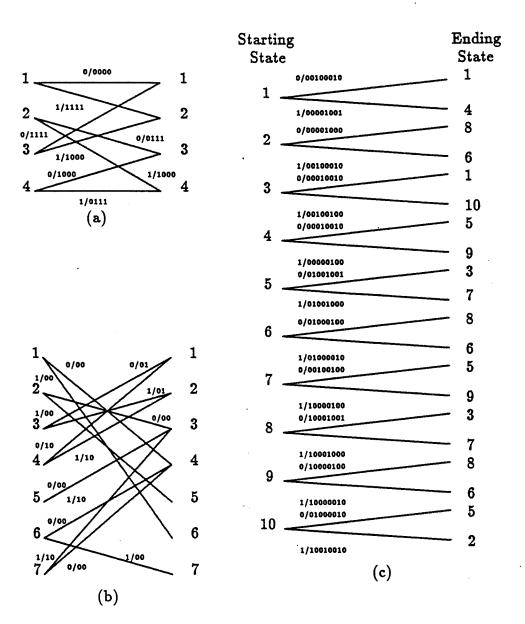

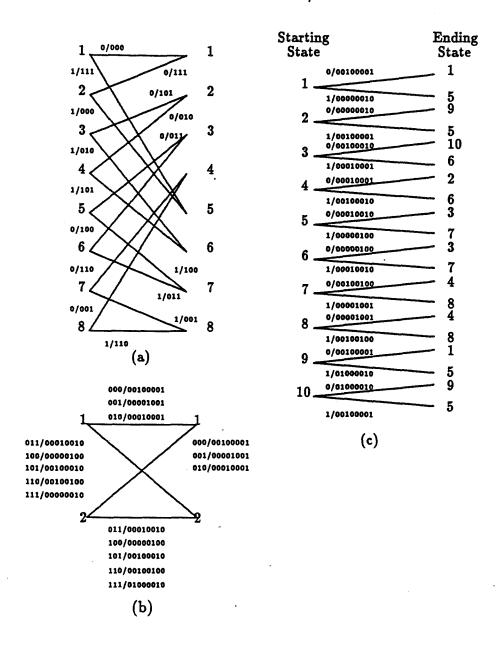

The decoder consists of 4 VLSI chips as depicted in Figure 1. The system is configured to perform in a pipelined manner where several messages are being processed simultaneously as depicted next:

| Message i:   | Syndrome Generator                       |

|--------------|------------------------------------------|

| Message i-1: | <b>Euclid Multiply and Euclid Divide</b> |

| Message i-2: | <b>Polynomial Solver and Correction</b>  |

| Message i-3: | Data Output                              |

Therefore, the latency of this system is 4.

The general operation can described as follows: A serial data stream is input into the serial-to-parallel converter from which the received message polynomial R(x) is generated. R(x) is stored in a buffer RAM for temporary storage. The syndrome generator produces the 32 symbol syndrome polynomial that is received by Euclid. The Euclid chip perform the division and multiply portions of Euclid's algorithm. A ROM is attached to Euclid

to calculate the inverse of a given field element. The Euclid produces the error location polynomial and the error magnitude polynomial. Polynomial Solver receives these polynomials from Euclid and performs the following simultaneous operations. The error location polynomial is evaluated for each element in the field generated by the primitive element  $\beta$ . If  $\beta^i$  is a root of  $\lambda(x)$ , then a signal Zero-Found is passed to the Error Correction Module. Both  $\lambda'(x)$  and  $\Omega(x)$  are evaluated for  $x = \beta^i$  and these results are also presented to Error Correction. Error Correction determines the error magnitudes; if Zero Found is true for  $x = \beta^i$ , then the magnitude for location n - i - 1 is given by Equation 9; otherwise the magnitude for location n - i is 0 (no error). Since the Polynomial Solver calculates both  $\Omega(x)$  and  $\lambda'(x)$ , Error Correction only has to divide these two values. Finally, the error magnitudes are exclusive-ored with the original information.

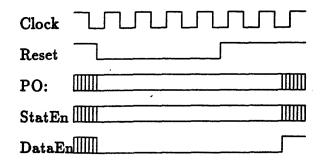

Real time decoding is achieved. The system clock being the symbol clock is a very important feature. Therefore, this decoder can decode symbols at the same rate message symbols are presented. Decoders that cannot use the symbol clock as the system clock must utilize a more complex clock system where the decoder operates at a higher clock rate than the symbol clock. Therefore, for a given technology, this decoder can operate faster than other designs which require a system clock that operates at a higher rate than the symbol clock. Moreover, operating at the symbol clock rate reduces the amount of message buffering.

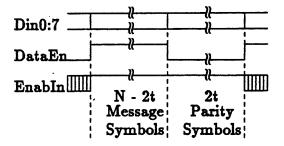

#### 4.1 Syndrome Generator

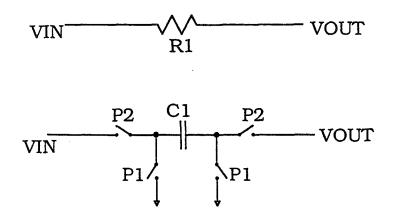

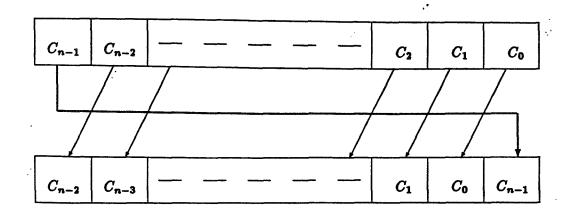

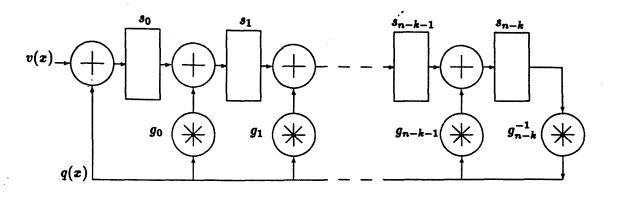

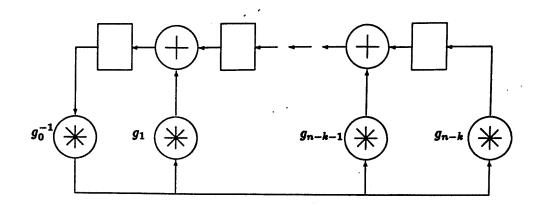

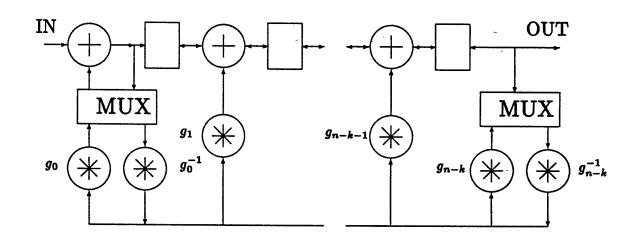

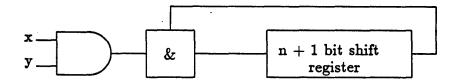

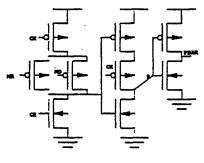

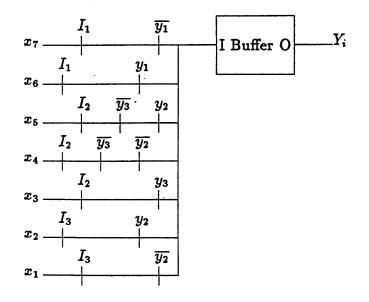

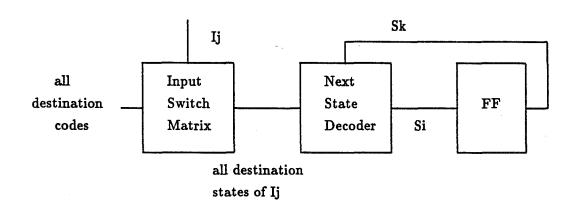

The calculation of the syndromes is given in Equation 6. The calculation  $R_i\beta^{i(k+s)}$  for syndrome byte is evaluated for all  $R_i$  and each k in  $\{0,1,2,\ldots,2t-1\}$  and i in  $\{0,1,2,\ldots,n-1\}$  (the number of input symbols in the message). A well known logic circuit for calculating syndrome  $S_j$  is shown in Fig. 2 [4]. The multiplier is a constant multiplier with the constant  $\beta^{1+j}$ . A CMOS version of this circuit is implemented here with a constant multiplier. With n input  $R_i$  symbols, a total of n clock pulses are needed to calculate a syndrome. All 32 syndromes are calculated simultaneously with 32 circuits operating in parallel.

Since one of the design constraints placed on the syndrome generator is that the system clock be equal to the symbol clock, it is necessary to calculate 32 syndromes in n clock pulses. A common means to configure 32 circuits depicted in Figure 2 is to first calculate 32 syndromes and then reconfigure the registers into a shift register and shift the syndromes out. However, this would require n + 32 clock pulses to calculate and shift out the syndromes, which is unacceptable.

Let the registers depicted in Figure 2 be called Syndrome registers. Let another register be defined as part of the register stack be called Shift and serve as a shift register. With the system clock being the symbol clock, if the contents of Syndrome are transferred to Shift after n clock pulses (n input symbols), the contents of Shift can be shifted out while the next set of syndromes are being calculated.

The NASA specification requires that decoder be capable of decoding dual basis RS code words. It is necessary to transform the dual basis code words into regular field code words; this is accomplished by operating on each received word by T' as defined

Figure 2: Syndrome generator

above. Operating on T' is equivalent to multiplying by a constant and therefore can be implemented in a similar manner as a constant multiplier. An extra feature is added to the syndrome generator to operate in either the regular field or the dual basis. An input signal DUAL is provided such that if DUAL is 1, then each input symbol is multiplied by T' (translation into regular field); if DUAL = 0, then the input symbols are not affected.

The Syndrome engine is implemented on a single, 3 micron CMOS chip  $4800 \ge 5140$  microns. There are approximately 26,000 transistors with only 5% of the area devoted to interconnect. With 32 additions and 32 multiplications occurring every 100 nano seconds, the equivalent instruction rate is 640 MOPS for a classical processor with a Galois Field ALU.

### 4.2 Euclid Divide and Multiply

The syndrome polynomial is shifted serially into the Euclid chip from the syndrome chip. The Euclid multiply and divide circuits recursively apply Euclid's Algorithm to find the error location and magnitude polynomials. The Euclid module uses the following algorithm to recursively obtain  $\lambda(x)$  and  $\Omega(x)$ .

$$\Omega_i(x) = \Omega_{i-2}(x) \mod \Omega_{i-1}(x) \tag{11}$$

$$\lambda_i(x) = -q_i(x)\lambda_{i-1}(x) + \lambda_{i-2}(x)$$

(12)

where  $q_i(x)$  are the non-negative powers of the division of  $\Omega_{i-2}(x)$  and  $\Omega_{i-1}(x)$ . The initial conditions are:

$$1.\Omega_{i-1}(x) = x^{2i} 2. \lambda_{-1} = 0 3. \Omega_0(x) = S(x) 4. \lambda_0(x) = 1$$

The algorithm continues until the order of  $\Omega_i(x)$  is less than t.

The organization of Euclid minimizes interconnect, and when implemented with the general multiplier, can calculate the error magnitude polynomial very rapidly. The version

implemented for NASA finds the location and magnitude polynomials in less than 237 clock cycles.

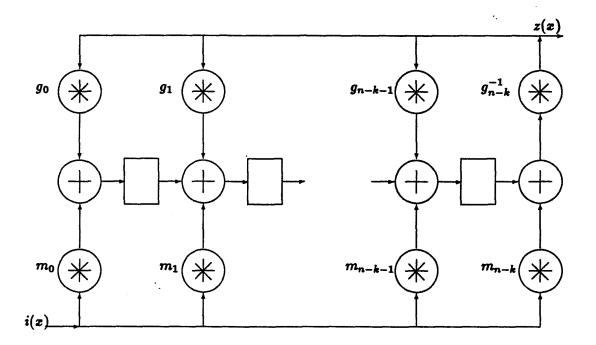

The Euclid chip is implemented on a single, 3 micron CMOS chip. Even though there are approximately 61,900 transistors in a  $7600 \times 6800$  area. The extraordinary density is achievable because : 1) The general multiplier can be drawn exceedingly dense, and 2) The given architecture is highly regular and requires virtually no interconnect. These two characteristics make it ideal for VLSI implementation.

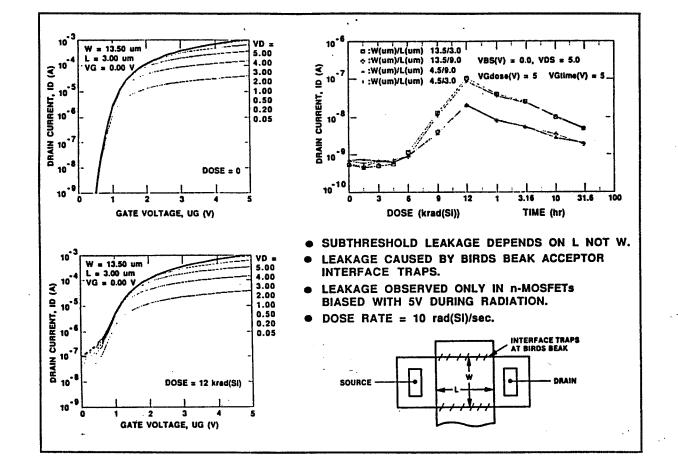

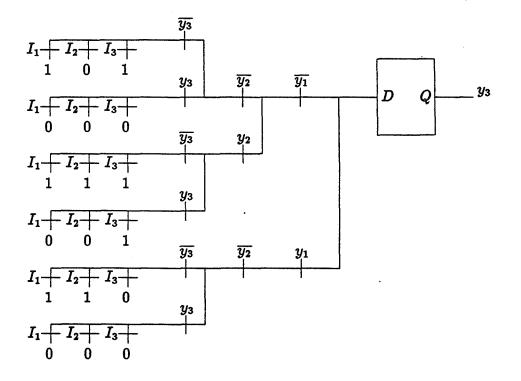

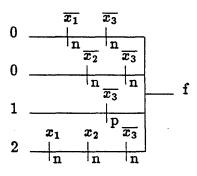

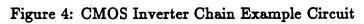

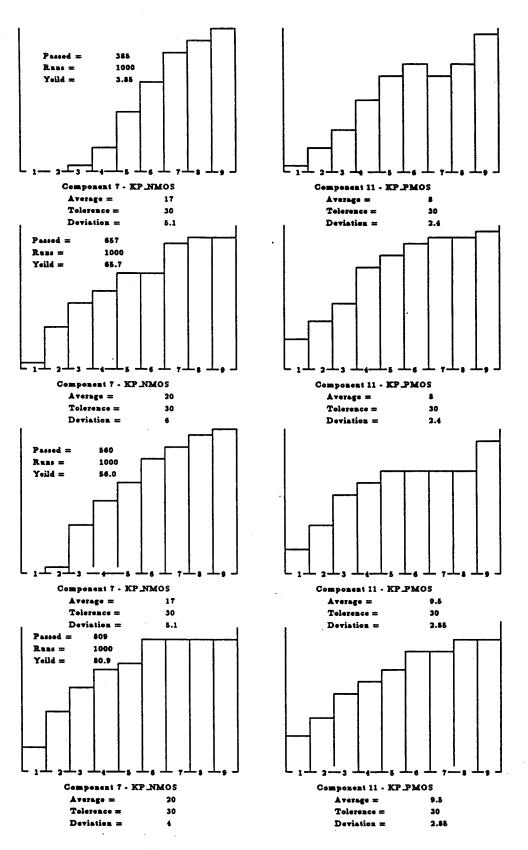

#### 4.3 Polynomial Solver