# Article Battery Charger Based on a Resonant Converter for High-Power LiFePO<sub>4</sub> Batteries

Christian Brañas <sup>1</sup>,\*<sup>1</sup>, Juan C. Viera <sup>2</sup>, Francisco J. Azcondo <sup>1</sup>, Rosario Casanueva <sup>1</sup>, Manuela Gonzalez <sup>2</sup>, and Francisco J. Díaz <sup>1</sup>

- <sup>1</sup> Electronics Technology, Systems and Automation Engineering Department, University of Cantabria,

- 39005 Santander, Spain; azcondof@unican.es (F.J.A.); casanuer@unican.es (R.C.); diazrf@unican.es (F.J.D.)

<sup>2</sup> Department of Electrical Engineering, University of Oviedo, Campus de Gijón, Módulo 3, 33204 Gijón, Spain; viera@uniovi.es (J.C.V.); mgonzalez@uniovi.es (M.G.)

- Correspondence: branasc@unican.es Tel.: +34-942-200-873

**Abstract:** A new battery charger, based on a multiphase resonant converter, for a high-capacity 48 V LiFePO<sub>4</sub> lithium-ion battery is presented. LiFePO<sub>4</sub> batteries are among the most widely used today and offer high energy efficiency, high safety performance, very good temperature behavior, and a long cycle life. An accurate control of the charging current is necessary to preserve the battery health. The design of the charger is presented in a tight correlation with a battery model based on experimental data obtained at the laboratory. With the aim of reducing conduction losses, the general analysis of the inverter stage obtained from the parallel connection of *N* class D  $LC_pC_s$  resonant inverters is carried out. The study provides criteria for proper selection of the transistors and diodes as well as the value of the DC-link voltage. The effect of the leakage inductance of the transformer on the resonant circuit is also evaluated, and a design solution to cancel it is proposed. The output stage is based on a multi-winding current-doubler rectifier. The converter is designed to operate in open-loop operation as an input voltage-dependent current source, but in closed-loop operation, it behaves as a voltage source with an inherent maximum output current limitation, which provides high reliability throughout the whole charging process. The curve of efficiency of the proposed charger exhibits a wide flat zone that includes light load conditions.

**Keywords:** lithium-ion battery; battery modeling; battery chargers; power supplies; resonant inverters; phase control

# 1. Introduction

Lithium iron phosphate (LiFePO<sub>4</sub>) batteries have a great electrochemical performance and a good thermal stability, which makes them safer and more robust. This lithium-based technology exhibits a very low internal resistance offering a high current rating. Their cycle life is significantly longer compared to other technologies [1,2]. The applications of LiFePO<sub>4</sub> batteries are, among others, for storage systems in renewable energy facilities, powering electric vehicles and uninterruptible power supplies (UPS) in data centers, telecommunications, and hospitals. A battery model is an important tool for designing the charger allowing the study of the dynamic response of the battery-charger system along the whole charging process, wherein the converter load, i.e., the equivalent resistance of the battery, varies from almost short-circuit to open-circuit values. Most of the battery models are aimed to improve the battery management system (BMS) performance, providing information about important parameters of the battery such as the state of charge (SOC) [3]. The estimation of the battery SOC and power capacity is usually solved by applying three methods, i.e., the look-up table method, the model-based method, and the artificial intelligence method [4–7]. In addition to that, the BMS is responsible for ensuring the battery operation within safety margins of temperature and sets the overvoltage and

Citation: Brañas, C.; Viera, J.C.; Azcondo, F.J.; Casanueva, R.; Gonzalez, M.; Díaz, F.J. Battery Charger Based on a Resonant Converter for High-Power LiFePO<sub>4</sub> Batteries. *Electronics* **2021**, *10*, 266. https://doi.org/10.3390/ electronics10030266

Received: 21 December 2020 Accepted: 21 January 2021 Published: 23 January 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). under voltage protection limits. In this work, the battery modeling is presented in a tight correlation with the battery charger design.

The technology of resonant converters is chosen to implement the proposed battery charger. The advantages of the resonant conversion of energy, such as high frequency of operation, sinusoidal waveforms, and low switching losses are well known [8]. Among all possible configurations of resonant converters, the series resonant converter and the LLC converter have been widely used [9-12]. Usually, the converter is designed to operate as a voltage source with some kind of control to limit the charging current. In this work, the converter is designed as a voltage-dependent current source. In this approach, the circuit presents an inherent maximum current limitation, which is a safer operation mode. The LiFePO<sub>4</sub> technology reaches current rates as high as hundreds of amps. In circuit design for high-current applications, conduction losses are a major design limitation [13,14]. In high-current resonant converters, increasing the dc-link voltage,  $V_{dc}$ , and using a stepdown transformer (n > 1) reduces the amplitude of the resonant currents in the inverter stage, minimizing the conduction loss in transistors and resonant inductors. New Wide Band Gap (WBG) devices enable the operation at an 800 V to 1700 V dc-link voltages range [15]. WBG devices achieve high performance at high current levels with important simplifications in the power circuit. However, the cost of WBG devices limits their use for certain applications.

In this work, a generalized design method aimed at minimizing the conduction loss is presented for multiphase resonant converters [16]. The number of parallel branches and therefore phases, N, in the inverter stage is calculated according to the maximum output power and the expected efficiency. This alternative offers another degree of freedom for achieving efficiencies higher than 90% even at relatively low values of  $V_{dc}$  and using low-cost transistors. Moreover, the multi-phase structure makes it possible to regulate the charging current at constant switching frequency by shifting the phase of the output voltages of each class D section of the inverter.

This paper is organized as follows: After the introduction, Section 2 describes the charging profile of the target LiFePO<sub>4</sub> battery, which is oriented to obtain a fast charge without reducing its lifetime. The battery model is presented in Section 3. The analysis of the proposed charger and main design equations are developed in Section 4. The efficiency of the charger is studied in Section 5. A detailed step-by-step design sequence of the proposed charger is explained in Section 6. In Sections 7 and 8, the results obtained for the modeling of the battery and experimental waveforms to verify the performance of the prototype are presented, ending with a discussion about Si vs. SiC solutions and concluding remarks.

## 2. Charging Method

The main characteristics of the commercial 48NPFC50 LiFePO<sub>4</sub> battery (Narada Power Source Co., Ltd., Hangzhou, China) [17] used in this work are 48 V nominal voltage and 50 Ah nominal capacity ( $C_n$ ) i.e., 2.4 kWh of power capacity. The battery consists of fifteen ( $N_s = 15$ ) stacked cells in series and incorporates a BMS that guarantees the right balance-of-charge of all cells. Thus, the voltage across each cell is assumed identical to any other. The battery charger is designed to meet all operational limits settled by the BMS.

The charging protocol recommended for LiFePO<sub>4</sub> batteries is the well-known [18] constant current (CC)–constant voltage (CV) method (i.e., CC–CV). During the CC stage, the battery is charged at the maximum current rate, which depends on the battery capacity and technology. Once the battery voltage reaches its maximum charging voltage specified in the battery data sheet, the CV stage begins. At this point, the power drawn from the charger is the maximum, which happens at 90% of the *SOC* approximately. During the CV stage, the charging current diminishes. Three experimental charging profiles are carried on at the battery laboratory facility shown in Figure 1. They are evaluated at room temperature (25 °C) using the battery test equipment PEC SBT-10050 (PEC, Leuven, Belgium) and taking into account that the battery is fully discharged as the initial condition.

Figure 1. (Left) Laboratory facility for battery testing. (Right) Battery connected to SBT-10050 test equipment.

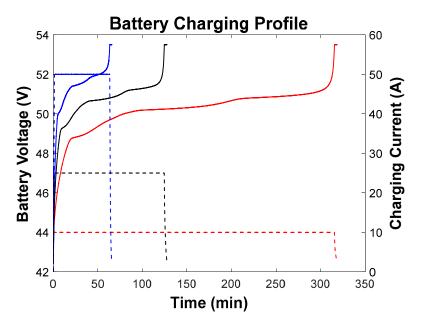

Those profiles correspond to the battery charge at current rates equal to  $C_n/5$ ,  $C_n/2$ , and  $C_n$  during the CC stage. The results are shown in Figure 2.

Figure 2. Experimental charging profiles at 10, 25, and 50 A for a 48NPFC50 LiFePO<sub>4</sub> battery.

The temperature is observed by the BMS during the whole charging process, and it implements the corresponding protection (maximum value 55 °C for charging) to prevent the battery aging. Electro-thermal models for studying the temperature of a lithium-ion cell as a function of the charging/discharging current have been reported in [19,20]. The user manual recommends a conservative value,  $C_n/5$ , for the charging current rate; however, LiFePO<sub>4</sub> technology tolerates fast-charging protocols [21–24]. In this work, in order to shorten the charging time, a maximum charging current rate of 20 A (approximately  $C_n/2$ ) is chosen the charger design. According to the experimental characterization of the battery, charging at  $C_n/2$  keeps the temperature of the battery well below 55 °C.

### 3. Battery Model

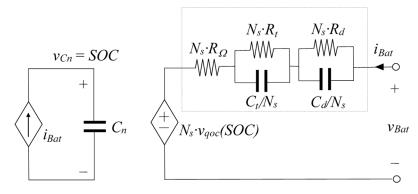

Although the LiFePO<sub>4</sub> cell is a complex physical system with several variables involved, a good trade-off among simplicity, accuracy, and insight information is obtained with the electrical parameters-based models [25], as shown in Figure 3. The single cell

model is generalized by affecting all parameters by the total number of cells,  $N_s$ , under the assumption that all cells are identical, as shown in Figure 3.

**Figure 3.** Battery model considering *N*<sub>s</sub> stacked cells in series.

The state of charge (SOC) [26] of the battery is defined as the ratio of the battery charge, Q, to the nominal capacity,  $C_n$ .

$$SOC = \frac{Q}{C_n} \cdot 100\% \tag{1}$$

The model calculates the *SOC* [26], integrating the battery current-dependent current source,  $i_{bat}$ , which charges/discharges the capacitor  $C_n$ . The *SOC* is equal to the voltage across the capacitor  $C_n$ ,  $v_{Cn}$  varying from zero to one corresponding to exhausted to fully charged battery, respectively.

$$SOC(t) = SOC(t_o) + \frac{1}{C_n} \int_{t_o}^t i_{bat}(t) dt$$

<sup>(2)</sup>

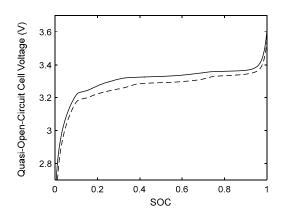

The voltage-controlled voltage source,  $N_s v_{qoc}(SOC)$ , dependent on the voltage  $v_{Cn}$ , represents the quasi-open-circuit battery voltage, where  $v_{qoc}$ , is the quasi-open-circuit voltage across one single cell. The experimental measurement of  $v_{qoc}$  as a function of the *SOC* is a time-consuming task because it should be obtained while keeping the cell in electrochemical equilibrium [27], charging and discharging the cell at a very low current rate. From the experimental study of one single cell, the  $v_{qoc}$  as a function of the *SOC* was obtained by charging and discharging the cell at  $C_n/50$ . This test required 100 h. The result is shown in Figure 4.

**Figure 4.** Quasi-open-circuit voltage of the cell as a function of the state of charge (*SOC*) obtained at  $C_n/50$  for a complete charge/discharge cycle. Solid line: Charge trajectory. Dashed line: Discharge trajectory.

As it is observed in Figure 4, the quasi-open-circuit cell voltage,  $v_{qoc}$ , incorporates the effect of the voltage hysteresis caused by the battery structure [27]. The maximum hysteresis is about  $\approx 40$  mV within the 30% *SOC* region, and the average is  $\approx 20$  mV within the 40% to 80% SOC region. The experimental test results show a cell capacity  $C_n = 50$  Ah, which is represented in the model by a capacitance  $C_n = 180,000$  F.

The electrolyte and electrode resistance are modeled by  $R_{\Omega}$ . In addition to that, the model also includes two time constants, which are modeled by networks  $R_tC_t$  and  $R_dC_d$ . The time constant  $R_tC_t$  is associated to chemical reactions and charge transportation phenomenon in the electrodes. This time constant is within the range from milliseconds to a few seconds. In contrast, the time constant  $R_dC_d$  governs the mass diffusion in the electrolyte and electrodes and is within the tens of seconds range [27]. From the point of view of the battery charger design, the electrical parameters of the battery at the end of the CC stage are of interest. At this point, the power supplied by the charger is the maximum. For a given *SOC*, the battery model can be simplified to a resistance,  $r_{Bat}$ , in series with a voltage source equal to the quasi-open-circuit voltage  $N_s V_{qoc}$ . Assuming the battery is in steady state,  $r_{bat}$  is obtained from the model shown in Figure 3 as

$$r_{Bat} = N_s \cdot (R_\Omega + R_t + R_d). \tag{3}$$

The specific values  $R_t$  and  $R_d$  for a given *SOC* should be obtained from the dynamic study of the battery, once the time constants associated with transport and diffusion phenomena were obtained. Finally, the battery voltage is obtained as:

$$V_{Bat} = N_s V_{qoc} + I_{Bat} r_{Bat}.$$

(4)

## 4. Multiphase $LC_pC_s$ Resonant Converter

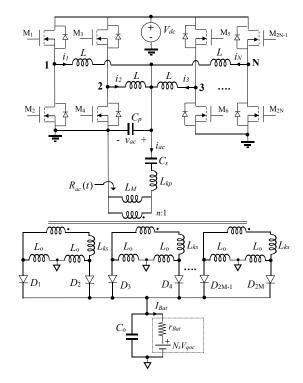

The proposed battery charger is a multiphase resonant converter. The general form of the circuit is shown in Figure 5, where the battery is modeled in steady state by its internal impedance,  $r_{Bat}$ , in series with the quasi-open-circuit battery voltage  $N_s V_{qoc}$ .

**Figure 5.** General architecture of the battery charger based on an *N*-phase  $LC_pC_s$  resonant inverter with an *M*-winding current-doubler rectifier as output stage. Multiple configurations are possible according to the *N* and *M* values.

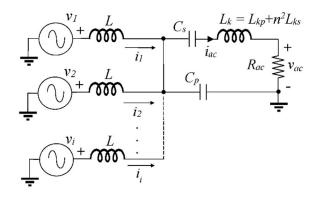

The AC side is a multiphase resonant inverter, which consists of *N* paralleled  $LC_pC_s$  class D sections [16,28]. Among the possible configurations of the resonant network, the configuration  $LC_pC_s$  of the *LCC* family is chosen to achieve a current source behavior while preserving the zero voltage switching (ZVS) mode of transistors [8,29]. Unlike the *LLC* converter, the proposed  $LC_pC_s$  does not require a gapped-core transformer [30], so the magnetizing inductance,  $L_M$ , is high enough to neglect its impact in the later analysis.

The DC side consists of an *M*-winding current multiplier, which is derived from the parallel connection of an *M* current-doubler rectifier [31,32]. The low output voltage of this application recommends the use of Schottky diodes without any control circuit in the secondary side, which is a simplification in comparison to solutions based on synchronous rectification (SR).

#### 4.1. Resonant Inverter Stage

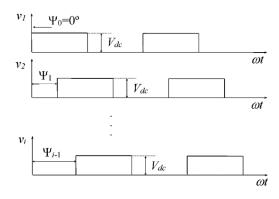

The converter is analyzed considering the general case, where each midpoint voltage  $v_i$  of all class D sections has associated a phase-angle  $\Psi_0, \Psi_1, \ldots, \Psi_{i-1}$ . To illustrate this assumption, the midpoint voltages,  $v_i$ , are shown in Figure 6.

Figure 6. Output voltages of each inverter section obtained in the midpoint of the transistors leg.

Using the fundamental approximation, the input voltages,  $v_i$ , are represented with the exponential form given in (5),

$$\mathbf{V_i} = \frac{2V_{dc}}{\pi} \cdot e^{-j\Psi_{i-1}},\tag{5}$$

where  $i \in [1, 2, ..., N]$  is the phase number. In steady state and using the low ripple approximation, the *M*-winding output rectifier is reduced to an equivalent impedance  $R_{ac}$  [8,29]. The resonant inverter stage is analyzed using the simplified circuit model shown in Figure 7.

**Figure 7.** Simplified model using the fundamental approximation for circuit analysis purposes of the inverter stage.

The parallel parameters of the resonant inverter are defined in Table 1.

| Parallel Resonant Frequency          | Parallel Characteristic Impedance           | Parallel Quality Factor     |

|--------------------------------------|---------------------------------------------|-----------------------------|

| $\omega_p = \frac{1}{\sqrt{LC_p/N}}$ | $Z_p = \omega_p L = \frac{N}{\omega_p C_p}$ | $Q_p = \frac{NR_{ac}}{Z_p}$ |

#### **Table 1.** Parameters of the $LC_pC_s$ resonant inverter.

# 4.1.1. AC Side Output Current

During the CC stage of the charging process, the converter provides an inherent current limitation, protecting the battery and extending its life. The current source behavior of the resonant converter is achieved by fixing the switching frequency at  $\omega = \omega_p$ , where  $\omega_p$  is the parallel resonant frequency, as given in Table 1. Once the switching frequency is fixed at  $\omega = \omega_p$ , the output current, seen from the primary side of the transformer, i.e., through  $C_s$ ,  $\mathbf{I_{ac}}$ , is calculated by (6).

$$\mathbf{I_{ac}} = -\frac{2V_{dc}}{\pi Z_p} \left\{ \sum_{m=1}^{N} \sin \Psi_{m-1} + j \sum_{m=1}^{N} \cos \Psi_{m-1} \right\}$$

(6)

From (6), the current source behavior is verified, given that  $I_{ac}$  has no dependence on the load.

# 4.1.2. Switching Mode

The switching losses are minimized by ensuring the zero voltage switch (ZVS) on the primary side of the converter [8,29]. The ZVS mode requires sufficient phase-delay of the resonant current with respect to the input voltage. A high value of  $Q_p$  reduces the reactive energy in the resonant converter, which is beneficial from the point of view of reducing the conduction loss. However, some reactive energy must be accepted for ensuring the ZVS mode of all transistors. The complex form,  $I_i$ , of each resonant current is given in (7) as a function of the angles  $\Psi_0$ ,  $\Psi_1$ , ...,  $\Psi_{N-1}$ .

$$\mathbf{I_{i}} = \frac{2V_{dc}}{\pi Z_{p}} \times \begin{cases} \frac{Q_{p}}{N} \sum_{m=1}^{N} \cos \Psi_{m-1} - \left(\frac{C_{p}}{NC_{s}} - \frac{L_{k}}{L}\right) \sum_{m=1}^{N} \sin \Psi_{m-1} - \sin \Psi_{i-1} \\ -j \left[\frac{Q_{p}}{N} \sum_{m=1}^{N} \sin \Psi_{m-1} + \left(\frac{C_{p}}{NC_{s}} - \frac{L_{k}}{L}\right) \sum_{m=1}^{N} \cos \Psi_{m-1} + \cos \Psi_{i-1} \right] \end{cases}$$

(7)

In order to determine the power factor angle,  $\phi_i$ , of each transistor's leg, the input impedance  $\mathbf{Z}_i = \mathbf{V}_i / \mathbf{I}_i$ , of each phase is calculated. The power factor angle,  $\phi_i$  is obtained using  $\phi_i$  = angle( $\mathbf{Z}_i$ ) as a function of the control angles,  $\Psi_0$ ,  $\Psi_1$ , ...,  $\Psi_{N-1}$ , the number of phases, N, and the quality factor,  $Q_p$ . Upon substitution of  $\Psi_0 = \Psi_1 = \ldots \Psi_{N-1} = 0^\circ$  in (5) and (7),  $\phi_i$  at the maximum output current is obtained:

$$\phi_i = \arctan\left(\frac{1 + \frac{C_p}{C_s} - N\frac{L_k}{L}}{Q_p}\right).$$

(8)

From (8), it can be observed that the effect of leakage inductance referred to the primary side of the transformer,  $L_k$ , is more significant for high-power as well as for high-frequency designs, where the value of inductance of the resonant circuit, L, is usually low, and a high value of leakage inductance could produce the loss of the ZVS mode. However, the series disposition of  $L_k$  and  $C_s$  enables the cancelation of the  $L_k$  effect on the AC side by calculating  $C_s$  to achieve, at the switching frequency, the series resonance with  $L_k$ . According to this proposal,  $C_s$  is obtained from (9).

$$C_s = \frac{L}{NL_k} C_p \tag{9}$$

With the cancellation of the  $L_k$  effect, the value of the power factor angle,  $\phi_i$ , depends essentially on the value of the quality factor  $Q_p$ , which is set during the design process of the converter. The minimum value of power factor angle for achieving ZVS,  $\phi_{zvs}$ , depends on the dead time,  $t_d$ , of the transistors' driver and the switching frequency  $\omega_p$  [33].

$$p_{zvs} = \frac{t_d \omega_p}{2\pi} \cdot 360^{\circ} \tag{10}$$

As design criteria, a value of power factor angle  $\phi_i = 2\phi_{zvs}$  is assumed at nominal conditions for achieving a reliable operation of the converter. This is the most restrictive design condition for operating in ZVS mode for the whole range of variation of the control angle  $\Psi$ . From (8) to (10), the value of the quality factor at nominal conditions,  $Q_{vN}$ , is obtained:

$$Q_{pN} = \frac{1}{\tan 2\varphi_{zvs}} \tag{11}$$

4.1.3. Variation of the Quality Factor and Transformer Turns Ratio

During the charging process, the equivalent impedance of the battery,  $R_{Bat}$ , changes depending on  $V_{Bat}$  and  $I_{Bat}$ , whose relationship is given by the charging profile of the battery, as shown in Figure 1. At the end of the CC stage,  $V_{Bat} = V_{Bat(Max)}$  and the power supplied to the battery reaches the maximum,  $P_{Bat} = V_{Bat(Max)}I_{Bat(Max)}$ . The specifications of the point of maximum output power are used for defining the nominal value of the quality factor,  $Q_{pN}$ . Thus, during the CC stage of the charging profile, the converter works with a quality factor lower than the nominal one, which strengthens the inductive behavior of the resonant tank, assuring the ZVS mode.

During the CV stage, the reduction of the charging current leads to a significant increment in the equivalent resistance  $R_{Bat}$  and consequently, the reflected impedance on the AC side,  $R_{ac}$ , and the quality factor  $Q_p$  also increase. Assuming that  $V_{Bat(Max)}$  is constant and working with (6), the quality factor as a function of  $\Psi$  is obtained in (12),

$$Q_{p} = \frac{n\pi^{2}V_{Bat(Max)}}{2V_{dc}} \frac{N}{\sqrt{\left(\sum_{m=1}^{N}\sin\Psi_{m-1}\right)^{2} + \left(\sum_{m=1}^{N}\cos\Psi_{m-1}\right)^{2}}}$$

(12)

The increment of  $Q_p$ , as a consequence of the reduction of the charging current during the CV stage could put at risk the ZVS mode of the transistors of the converter. However, it is beneficial from the point of view of achieving waveforms with low distortion and increases the converter efficiency. The nominal value of quality factor is obtained by evaluating (12) for  $\Psi_0 = \Psi_1 = \Psi_{N-1} = 0^\circ$ .

$$Q_{pN} = \frac{n\pi^2 V_{Bat(Max)}}{2V_{dc}} \tag{13}$$

From (13) and (11), the transformer's turns ratio (n:1) can be obtained:

$$n = \frac{2V_{dc}}{\pi^2 V_{Bat(Max)} \tan 2\varphi_{zvs}}.$$

(14)

#### 4.2. Output Current Multiplier

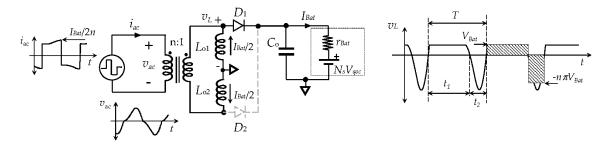

In order to analyze the output current multiplier stage, first, a single-winding currentdoubler rectifier with an ideal transformer, as seen in Figure 8, is considered. The quasisinusoidal voltage  $v_{ac}$  at parallel capacitor  $C_p$  drives the current multiplier stage. The diodes  $D_1$  and  $D_2$  turn on alternatively according the positive or negative cycle of  $v_{ac}$ , respectively.

**Figure 8.** (Left) Current-doubler rectifier considering the positive semi-cycle of the drive voltage  $v_{ac}$ . (**Right**) Theoretical voltage waveform at the filter inductors.

The diodes conduction time,  $t_1$ , is obtained from the volts–seconds balance across the inductors. The areas are calculated according to the approximation shown in Figure 8 right.

$$t_1 = \frac{n\pi}{1 + n\pi}T\tag{15}$$

The average current through each inductor,  $L_{o1,2}$ , is equal to one-half of the charging current  $I_{Bat}$ . The amplitude of the current ripple in each inductor is determined by

$$\Delta i_L = \frac{n\pi^2 V_{Bat(Max)}}{(1+n\pi)\omega_v L_o}.$$

(16)

The total ripple current through the filter capacitor  $C_o$  is calculated considering M parallel rectifiers and taking into account the ripple cancellation effect due to the 180° phase displacement between the current through each inductor [31,32] in the current-doubler structure; thus,

$$\Delta i_{C} = \frac{n\pi^{2}MV_{Bat(Max)}}{2(1+n\pi)\omega_{p}L_{o}}$$

(17)

The output voltage ripple is

$$\Delta v_{Bat} = \frac{n\pi^3 M V_{Bat(Max)}}{16(1+n\pi)\omega_p^2 L_o C_o} \tag{18}$$

From (18), the ripple of the charging current is a function of the switching frequency, output filter components, and battery parameters.

$$\Delta i_{Bat} = \frac{n\pi^3 M V_{Bat(Max)}}{16(1+n\pi)r_{Bat}\omega_p^2 L_o C_o} \tag{19}$$

The limitation of the output current ripple,  $\Delta i_{Bat}$ , is mandatory in order to avoid the battery degradation [12].

Reflected Impedance on the Primary Side of the Transformer

Since the output filter removes the high-frequency ripple, the low ripple approximation [29] is used to study the proposed rectifier in steady state. Considering the total current in the primary side and using the first harmonic of the square waveform, the relationship between the AC and DC currents is given in (20).

$$\hat{t}_{ac} = \frac{2I_{Bat}}{n\pi} \tag{20}$$

where  $\hat{I}_{ac}$  is the amplitude of the transformer's primary current. From (20) and (6), the charging current is obtained as a function of the angles  $\Psi_0, \Psi_1, \ldots, \Psi_{N-1}$ ,

$$I_{Bat} = \frac{nV_{dc}}{Z_p} \sqrt{\left(\sum_{m=1}^N \sin\Psi_{m-1}\right)^2 + \left(\sum_{m=1}^N \cos\Psi_{m-1}\right)^2}$$

(21)

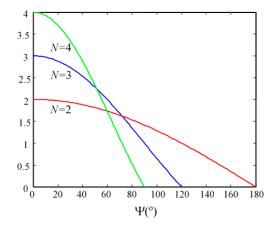

The normalized amplitude of the charging current,  $I_{Bat}$ , is depicted in Figure 9 as a function of the control angle,  $\Psi$ , and considering the modulation pattern where all phases are evenly shifted.

**Figure 9.** Amplitude of the normalized charging current,  $I_{Bat}$ , as a function of the control angle,  $\Psi$ , for N = 2, 3, and 4. All phases are evenly shifted,  $\Psi_0 = 0^\circ$ ,  $\Psi_1 = \Psi$ ,  $\Psi_2 = 2\Psi$ , ...,  $\Psi_{N-1} = (N-1)\Psi$ .

Working with (21), the maximum charging current is achieved at  $\Psi_0 = \Psi_1 = \Psi_{N-1} = 0^\circ$  and is given by

$$I_{Bat(Max)} = \frac{nV_{dc}}{Z_p} \cdot N \tag{22}$$

From (22), it can be observed that the output current capability of the multiphase converter is enhanced by increasing the number, *N*, of paralleled phases. An accurate acquisition of the modulation angle, covering the whole range over the entire battery charging process, facilitates the computation of ampere-hours in order to calculate the supplied capacity.

The amplitude of the voltage in the primary side of the transformer is obtained from the power balance in the windings. Assuming a lossless transformer,

$$P_{ac} = P_{Bat} = \frac{\hat{I}_{ac}\hat{V}_{ac}}{2} = I_{Bat}V_{Bat}$$

(23)

and substituting (20) into (23),

$$\hat{V}_{ac} = n\pi V_{Bat} = n\pi r_{Bat} \cdot I_{Bat} + n\pi \cdot V_{Bat}.$$

(24)

From (20) and (24), the battery is modeled from the AC side by

$$\hat{V}_{ac} = \frac{n^2 \pi^2}{2} r_{Bat} \cdot \hat{I}_{ac} + n \pi \cdot V_{Bat}.$$

(25)

The reflected impedance of the current multiplier and load,  $R_{ac}$ , into the AC side of the converter defines important characteristics of the resonant inverter, such as the switching

mode of the transistors, the distortion of the waveforms, and the efficiency [11]. From (25), the rectifier stage is reflected into the AC side as the equivalent resistance  $R_{ac}$  in (26),

$$R_{ac} = \frac{\pi^2}{2} n^2 R_{Bat} = \frac{\pi^2}{2} n^2 \left( r_{Bat} + \frac{V_{Bat}}{I_{Bat}} \right)$$

(26)

Assuming an ideal transformer, where the leakage inductance reflected in the secondary side is  $L_{ks} = 0$ , the maximum voltage across the diodes is  $V_B = -n\pi V_{Bat}$ . However, in practice,  $L_{ks}$  is in series with the junction capacitance of the reverse-biased diode,  $C_j$ , causing a high-frequency oscillation or ringing. The selection of the Schottky devices takes into account the minimization of this effect.

# 5. Efficiency of the Multiphase $LC_pC_s$ Resonant Converter

The overall efficiency of the converter is calculated by

$$\eta = \eta_I \cdot \eta_R, \tag{27}$$

where  $\eta_I$  is the efficiency of the resonant inverter stage and  $\eta_R$  is the efficiency of the output current multiplier stage.

#### 5.1. Efficiency of the Inverter Stage

Taking into account the ZVS mode operation of the converter, the switching loss is considered negligible in comparison to the conduction loss. The efficiency of the resonant inverter stage,  $\eta_I$ , considering the conduction loss only [16] is

$$\eta_{I} = \frac{1}{1 + \frac{r}{R_{ac}} \cdot \frac{\sum_{k=1}^{N} \hat{I}_{i}^{2}}{1 + \frac{r}{R_{ac}} \cdot \frac{k=1}{\hat{I}_{ac}^{2}}}}$$

(28)

where  $I_i$  is the amplitude of each resonant current given in (7). The resistance *r* represents the  $rds_{on}$  of the transistors as well as the ESR of the inductors. The highest efficiency,  $\eta_{I(Max)}$ , is achieved with  $\Psi_0 = \Psi_1 = \ldots = \Psi_{N-1} = 0^\circ$ . Upon substitution of  $\Psi_0 = \Psi_1 = \ldots = \Psi_{N-1} = 0^\circ$  in (28) and under the assumption that  $C_s$  is calculated according to (9), the maximum efficiency as a function of the ratio  $r/R_{ac}$ , the nominal value of the quality factor,  $Q_{pN}$ , and the number of phases, N, is obtained.

$$\eta_{I(Max)} = \frac{1}{1 + \frac{r}{NR_{ac}} \cdot \left[1 + Q_{pN}^2\right]}$$

(29)

From (28), it is observed that  $\eta_{I(Max)}$  is improved by increasing  $R_{ac}$ . The straightforward way to increase  $R_{ac}$  is through the larger transformer turns ratio, n. However, it should be considered that  $Q_{pN}$  increases with n, according to (12), which could jeopardize the ZVS mode of the converter transistors. Taking into account the tight correlation among, N,  $Q_{pN}$ , n, and  $r/R_{ac}$ , the design process oriented to find a suitable value of these parameters involves iterative cycles. Upon the substitution of (12) and (20) into (29),  $\eta_{I(Max)}$  is obtained as a function of the converter parameters,

$$\eta_{I(Max)} = \frac{1}{1 + \frac{\pi^2 r I_{Bat(Max)} V_{Bat(Max)}}{2NV_{dc}^2} + \frac{2r I_{Bat(Max)}}{n^2 \pi^2 N V_{Bat(Max)}}} \approx \frac{1}{1 + \frac{2r I_{Bat(Max)}}{n^2 \pi^2 N V_{Bat(Max)}}}$$

(30)

The maximum efficiency of the resonant inverter stage,  $\eta_{I(Max)}$ , improves, approaching one asymptotically as the number of phases, *N*, increases.

# 5.2. Efficiency of the Output Current Multiplier

Limiting the current level through the output rectifier stage is a major design challenge oriented to reduce the conduction loss. The proposed *M*-windings output current multiplier

lowers the amplitude of the current through diodes by a factor M and the average current through filters inductors by a factor 2M. An expression for the rectifier efficiency,  $\eta_R$ , only including the conduction loss, is obtained from the analysis of the current paths shown in Figure 7. Considering a lossless transformer, the total power,  $P_T$ , in the secondary side of the current multiplier is

$$P_T = P_{Bat} + M\left(\frac{V_D I_{Bat}}{M} + \frac{I_{Bat}^2 r_D}{M^2} + \frac{I_{Bat}^2 r_{LF}}{4M^2}\right),$$

(31)

where  $P_{Bat}$  is the output power,  $P_{Bat} = V_{Bat} \cdot I_{Bat}$ ,  $V_D$  and  $r_D$  are the voltage and dynamic resistance of the linear model of the diode, and  $r_{LF}$  is the ESR of the filter inductor  $L_o$ . The efficiency,  $\eta_R$ , is calculated with  $\eta_R = P_{Bat}/P_T$ ,

$$g_R = \frac{1}{1 + \frac{V_D}{V_{Bat}} + \frac{\binom{r_D + \frac{r_{IF}}{2M}}{M} I_{Bat}}{V_{Bat}}}.$$

(32)

The efficiency of the output current multiplier,  $\eta_R$ , is improved by increasing the number of secondary windings, *M*. The theoretical limit  $\eta_{R(Max)}$  of  $\eta_R$  is obtained letting  $M \rightarrow \infty$ ,

$$\eta_{R(Max)} = \frac{1}{1 + \frac{V_D}{V_{Bat(Max)}}}.$$

(33)

From (32) and (33), it can be observed that the ratio  $V_D/V_{Bat(Max)}$  should be minimized, which confirms the benefit of using Schottky diodes or sync rectifiers to improve the efficiency of the rectifier stage.

# 5.3. Optimum N and M of Parallelized Stages

1

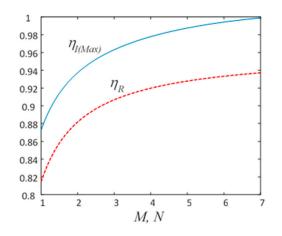

The expressions (30) to (33) are used as a criterion to define the appropriate number of phases, N, of the resonant inverter stage as well as the number of secondary windings, M, of the output current multiplier. The maximum efficiency of the inverter section,  $\eta_{I(Max)}$ , and the efficiency of the current multiplier,  $\eta_R$ , are depicted in Figure 10 as a function of N and M.

**Figure 10.** Maximum efficiency of the resonant inverter stage,  $\eta_{I(Max)}$ , and efficiency of the output current multiplier,  $\eta_R$ , as a function of the number of phases, N, and secondary windings M. The following typical values are assumed: n = 2,  $r = 1.7 \Omega$ ,  $I_{Bat(Max)} = 20 \text{ A}$ ,  $2rI_{Bat(Max)}/\pi^2 V_{Bat(Max)} = 0.5$ ,  $V_D/V_{Bat(Max)} = 0.05$  and  $r_D = r_{LF} = 0.1$ .

From a practical point of view, the asymptotic variation of  $\eta_R$  and  $\eta_{I(Max)}$ , shown in Figure 10, limits the maximum values of *M* and *N*. The criterion for choosing the suitable values of *M* and *N* is a tradeoff between the increment of the efficiency and the circuit complexity. It is assumed that if the increment of efficiency achieved is barely 1%, a higher number of secondary windings *M* or phases, *N*, is not justified.

# 6. Design of the Multiphase $LC_pC_s$ Resonant Converter

- (1) The maximum battery voltage is set at  $V_{Bat(Max)} = 53.5$  V, which is below the overvoltage protection limit (54.7 V) defined by the BMS. The output current capability of the circuit is set to  $I_{Bat} = 20$  A in order to shortening the charging time. The equivalent impedance of the battery is  $R_{Bat} = 2.67 \Omega$ . The peak power that must be supplied by the charger is  $P_{Bat} = 1.07$  kW. The converter supply voltage is  $V_{dc} = 400$  V, which is the output voltage of a previous front-end PFC stage. The switching frequency is set at  $\omega_p = 2\pi(125 \text{ kHz})$ .

- (2) The drive signals of the transistors are obtained from an integrated circuit IR2111 with a dead time,  $t_d = 650$  ns. From (10), the minimum value of the power factor angle for each class D section is  $\phi_{zvs} = 29.25^{\circ}$ . Using the design constrain  $\varphi_i = 2\phi_{zvs} = 58^{\circ}$  from (11), the nominal value of the quality factor is obtained,  $Q_{pN} = 0.624$ . The transformer turns ratio, *n*, is calculated from (14), approximating to the nearest entire value, n = 1.

- (3) The number of phases, *N*, is calculated taking into account that transistors are low-cost CoolMOS<sup>TM</sup> SPA11N60C3 (Infineon, Neubiberg, Germany) with  $rds_{(on)} = 0.38 \Omega$ . Considering the equivalent series resistant (ESR) of the resonant inductors and tracks of the printed circuit board (PCB), a worst case of  $r = 1 \Omega$  is assumed. Upon substitution in (30), the pair n = 1 and N = 4 yields  $\eta_{I(Max)} = 0.98$ . This value of efficiency means 21 W power loss in the resonant inverter stage at full load conditions.

- (4) The expected efficiency of the rectifier stage is calculated using the conduction loss model of the Schottky diode STPS30M60S (STMicroelectronics, Geneva, Switzerland) from ST with  $V_D = 0.395$  V and  $r_D = 0.0047 \Omega$ . The filter inductors are Vishay IHLP–8787MZ (Vishay Intertechnology, Malvern, USA) with  $L_o = 75 \mu$ H and  $r_{LF} = 30 m\Omega$  at 25° C. Taking into account the temperature effect, the value  $r_{LF} = 90 m\Omega$  is assumed. Upon substitution of  $V_D$ ,  $r_D$ ,  $V_{Bat(Max)}$ ,  $r_{LF}$ , and  $I_{Bat} = 20$  A in (32), the value M = 1 yields an efficiency of the rectifier stage at maximum load,  $\eta_R = 0.97$ . This value of efficiency means 32 W power loss in the current-doubler rectifier at full load. In this way, the configuration of a four-phases (N = 4) resonant inverter with a single (M = 1) current-doubler rectifier as output stage achieves an overall efficiency at full load equal to  $\eta = \eta_I \cdot \eta_R = 0.95$ .

- (5) From (16), the amplitude of the current ripple in each inductor is  $\Delta i_L = 2.16$  A. The  $r_{Bat}$  is estimated at 40 m $\Omega$ . The output capacitor,  $C_o$ , is calculated to achieve a maximum current ripple equal to 0.1% of the charging current,  $\Delta i_{Bat} = 20$  mA. From (19),  $C_o = 680 \mu$ F.

- (6) The characteristic impedance is obtained from (22),  $Z_p = 80 \Omega$ . In Table 1, the reactive components are  $L = Z_p / \omega_p = 100 \mu$ H and  $C_p = 4 / \omega_p Z_p = 64 n$ F.

- (7) The transformer has been built with an ETD49 core of material N87. The primary and secondary are 16 single-layer turns of 40 strands of litz wire. The resulting magnetizing inductance is  $L_M = 800 \ \mu\text{H}$  and the leakage inductance from the primary and secondary sides are  $L_{kp} = L_{ks} = 1.4 \ \mu\text{H}$ . The total leakage inductance is  $L_k = L_{kp} + n^2 \cdot L_{ks} = 2.8 \ \mu\text{H}$ .

- (8) Once  $L_k$  is known, the series capacitor  $C_s$  is calculated with (9) to cancel out the effect of  $L_k$ ,  $C_s = 571$  nF.

# 7. Control Circuit and Battery Modeling

During the CV stage, the charging current must be regulated to avoid the voltage of the battery exceeding  $V_{Bat(Max)}$ . The current is modulated through the phase-angles  $\Psi_0$ ,  $\Psi_1$ , and  $\Psi_{N-1}$ , while keeping the switching frequency constant. Different patterns are possible for adjusting  $\Psi_1$ ,  $\Psi_2$ , and  $\Psi_{N-1}$ . For any value of *N*, the full control of the charging current is achieved if the phase shift is evenly distributed among all *N* phases, e.g.,  $\Psi_0 = 0^\circ$ ,  $\Psi_1 = \Psi$ ,  $\Psi_2 = 2\Psi \dots \Psi_{N-1} = (N-1)\Psi$ . In this case, the minimum current  $I_{Bat} = 0$  A is achieved at  $\Psi = 360^\circ/N$ . This pattern requires *N* control signals. For this design, where N = 4, the control angles are adjusted as follows:  $\Psi_0 = \Psi_1 = 0^\circ$  and  $\Psi_2 = \Psi_3 = \Psi$ . For this approach, the minimum  $I_{Bat} = 0$  A is achieved at  $\Psi = 180^\circ$ , and only two control signals are required, which implies a simplification of the control circuit.

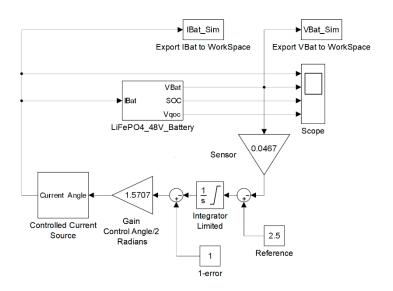

Once the converter is designed, the battery-charger system is completed with a control loop to limit the output voltage of the charger to the maximum value recommended for the battery. The action of the control loop transforms the circuit's open-loop current source behavior into a voltage source. A type I error amplifier is enough for this action. The scheme of the charger-battery system, modeled in Simulink, is shown in Figure 11. In the voltage mode, the battery imposes the dynamic response of the converter-battery system [27].

Figure 11. Control loop for limiting the maximum battery voltage, V<sub>Bat(Max)</sub>.

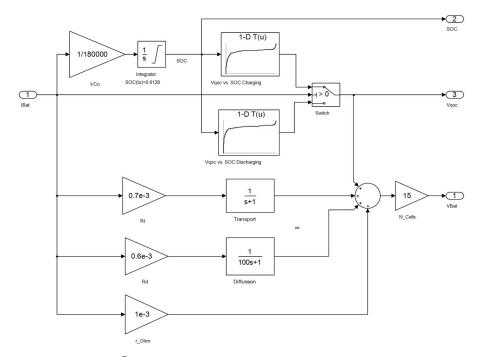

The Simulink<sup>®</sup> model of the battery [34,35] is shown in Figure 12. The look-up tables include the quasi-open circuit voltage of a basic cell for the charge and discharge trajectories as a function of the *SOC*.

Figure 12. Simulink<sup>®</sup> model of the battery.

The different parameters of the model can be tuned using curve fitting. The data used as reference for adjusting the model were obtained from the experimental characterization of the battery charging at 25 A, which has been shown in Figure 1. The time constant for charge transportation and diffusion phenomena are 1 s and 100 s, respectively. The

impedance for the charge transport is  $R_t = 0.7 \text{ m}\Omega$  and the capacitance is  $C_t = 1428 \text{ F}$ . The impedance of the diffusion is  $R_d = 0.6 \text{ m}\Omega$  and the corresponding capacitance is  $C_d = 166,000 \text{ F}$ . The impedance due to electrodes and electric connections is  $R_\Omega = 1 \text{ m}\Omega$ . The impedance of the battery pack is obtained from (4),  $r_{bat} = 34.5 \text{ m}\Omega$ . This value of  $r_{Bat}$  includes the impedance of connectors and cables, which is used to conform to the battery by the series connection of the 15 cells.

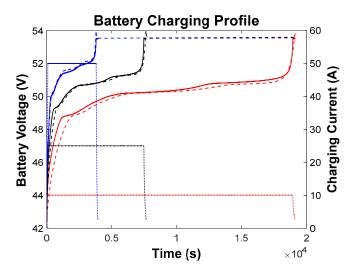

The variation of the battery voltage, obtained from the simulation of the system in Figure 11, is shown in Figure 13. It can be observed that simulation and experimental results are in good agreement for the three charging profiles in Figure 2 that were evaluated experimentally.

**Figure 13.** Charging profiles at 10, 25, and 50 A. Solid lines: Experimental battery voltage. Dashed lines: Simulation result. Dot lines: Charging current.

# 8. Results of the Experimental Prototype

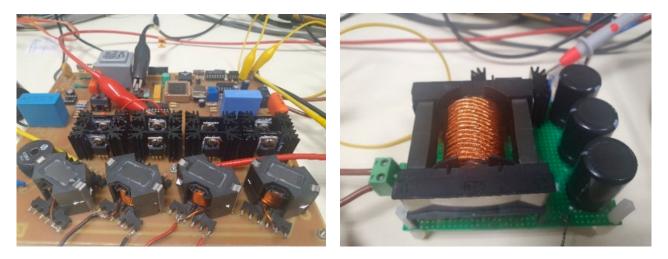

An experimental prototype, shown in Figure 14, has been built to validate the theoretical proposal.

Figure 14. Details of the experimental prototype of the charger. (Left) Four-phase resonant inverter stage. (Right) Currentdoubler rectifier.

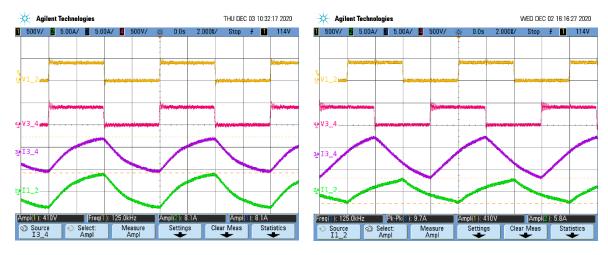

When connecting the battery to the charger, an initial frequency sweep is programmed to ensuring the gradual growth of the charging current to prevent the occurrence of an overvoltage across the discharged battery. The experimental waveforms in different circuit sections are shown in Figures 15–17. In order to demonstrate the charger performance at different operation points, the waveforms for full load and 70% of full load operation are

shown. In Figure 15, it is observed that the resonant current has a phase lag with respect to the input voltage. At full load condition,  $\varphi_{i1,2} = \varphi_{i3,4} = 54^\circ$ , which is in good agreement with the theoretical value, and at 70% of the full load condition,  $\varphi_{i1,2} = 54^\circ$ ,  $\varphi_{i3,4} = 72^\circ$ . The ZVS mode operation was verified for all phases of the resonant inverter section.

**Figure 15.** From top to bottom: Midpoint voltages of phases 1 and 2,  $v_{1,2}$ . Midpoint voltages of phases 3 and 4,  $v_{3,4}$ . Resonant current of phases 1 and 2,  $i_{1,2}$ . Resonant current of phases 3 and 4,  $i_{3,4}$ . (Left) Full load condition ( $\Psi_0 = \Psi_1 = \Psi_2 = \Psi_3 = 0^\circ$ ). (**Right**) 70% of full load condition ( $\Psi_0 = \Psi_1 = 0^\circ, \Psi_2 = \Psi_3 = 90^\circ$ ).

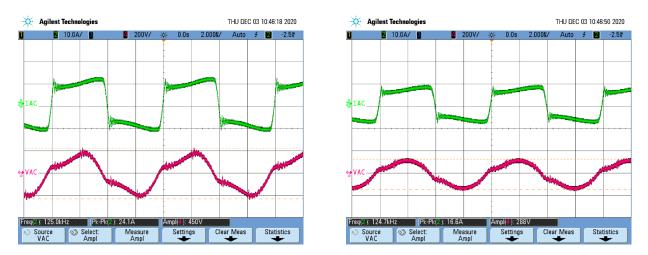

**Figure 16.** From top to bottom: Output current through the primary side of the transformer,  $i_{ac}$ . Output voltage applied to the primary side of the transformer,  $v_{ac}$ . (**Left**) Full load condition ( $\Psi_0 = \Psi_1 = \Psi_2 = \Psi_3 = 0^\circ$ ). (**Right**) 70% of full load condition ( $\Psi_0 = \Psi_1 = 0^\circ, \Psi_2 = \Psi_3 = 90^\circ$ ).

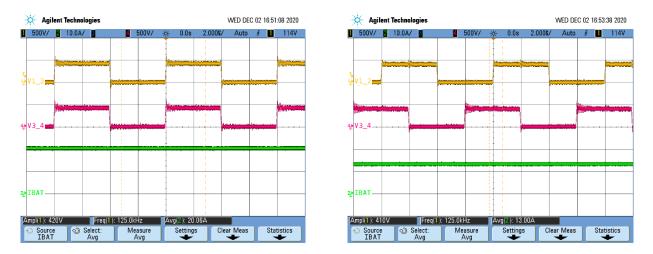

In Figure 16, the current and voltage at the primary side of the transformer are shown. The amplitude of the current square waveform is half (10 A) of the battery charging current. In Figure 17, the charging current at full load (20 A) and at 70% of full load are shown. The results are in good agreement with the theoretical value according to the control angle  $\Psi$ . It can be observed that the charging current ripple is negligible as it is required for this application. The experimental efficiency of the prototype measured at the point of maximum load ( $I_{Bat} = 20 \text{ A}$ ,  $P_{Bat} = 1.07 \text{ kW}$ ) was  $\eta = 91.3\%$ . The efficiency at 70% and 50% of the full load was  $\eta = 90.2\%$  and  $\eta = 88\%$ , respectively. The experimental efficiency is slightly lower than the theoretical due to the switching losses, the power dissipation at the transistors drive circuit, and the auxiliary power supply loss.

**Figure 17.** From top to bottom: Midpoint voltages of phases 1 and 2,  $v_{1,2}$ . Midpoint voltages of phases 3 and 4,  $v_{3,4}$ . Charging current  $i_{Bat}$ . (**Left**) Full load condition ( $\Psi_0 = \Psi_1 = \Psi_2 = \Psi_3 = 0^\circ$ ). (**Right**) 70% of full load condition ( $\Psi_0 = \Psi_1 = 0^\circ$ ,  $\Psi_2 = \Psi_3 = 90^\circ$ ).

# 9. Discussion

In this work, the general design method of the proposed charger has been explained, but the particular configuration of the final solution depends on the chosen technology. One key decision is the most suitable value of the dc-link voltage. The solution for an dc-link voltage  $V_{dc}$  = 400 V, which was obtained from a single-phase power factor corrector (PFC) based on a Boost Converter, and using the CoolMOS<sup>TM</sup> SPA11N60C3 MOSFET transistor and the STPS30M60S Schottky diode has been fully developed. As alternative, a solution with  $V_{dc}$  = 800 V, obtained from a three-phase PFC and using silicon carbide (SiC) components is also assessed. For this case, the third-generation C3M0065100K MOSFET transistor (Wolfspeed, Research Triangle Park, USA) with the CGD15SG00D2 driver (Wolfspeed, Research Triangle Park, USA) is used in the inverter section. As the voltage, current, and power at the circuit output are the same, the silicon (Si) Schottky diode STPS30M60S is used in both cases. For a better comparison, both designs are summarized in Table 2.

| Table 2. | Designs companson. |  |

|----------|--------------------|--|

|          |                    |  |

Table ? Designs comparison

| V <sub>dc</sub> | n | N | M | $Z_p$ | $Q_{pN}$ | η     | I <sub>Bat(Max)</sub> | P <sub>Bat(Max)</sub> |

|-----------------|---|---|---|-------|----------|-------|-----------------------|-----------------------|

| 400 V           | 1 | 4 | 1 | 80 Ω  | 0.624    | 0.95  | 20 A                  | 1.07 kW               |

| 800 V           | 2 | 2 | 1 | 160 Ω | 0.624    | 0.966 | 20 A                  | 1.07 kW               |

As it can be seen in Table 2, both designs achieve a similar theoretical efficiency, but the SiC technology uses only two phases for the resonant inverter stage.

## Considerations about the Solution Cost

SiC technology for power devices is becoming more competitive in technical performance and cost. Important advances have been reported in terms of increasing the wafer diameter and minimization of the defect density [36], which contribute to lowering the cost of the devices, so it is worth comparing the cost of the proposed alternatives. Focusing on the inverter section of the described designs, i.e.,  $V_{dc} = 400$  V for the four-phase Si inverter and  $V_{dc} = 800$  V for the two-phase SiC inverter, the cost assessment reveals that at present, the solution based on SiC components is more expensive despite requiring fewer transistors. The cost of the third-generation SiC MOSFET C3M0065100K is five times (5 ×) that of the SPA11N60C3 Si MOSFET. On the other hand, in contrast to the simplicity of the half-bridge driver, based on the integrated circuit IR2111, the complexity and cost of the selected driver CGD15SG00D2 for SiC MOSFETS are also significantly higher [37]. In addition, the PFC section adds a cost difference in favor of the  $V_{dc} = 400$  V four-phase Si design. For illustrating the analysis, in Tables 3 and 4, the cost of the SiC components and its Si counterparts are summarized [38]. Differences in the magnetic elements, capacitors, and control circuit have less impact on cost.

Table 3. SiC resonant inverter.

| Component             | Quantity | Cost<br>(Retail Sale) |

|-----------------------|----------|-----------------------|

| MOSFET<br>C3M0065100K | 4        | 40€                   |

| Driver<br>CGD15SG00D2 | 4        | 200€                  |

Table 4. Si resonant inverter.

| Component            | Quantity | Cost<br>(Retail Sale) |

|----------------------|----------|-----------------------|

| MOSFET<br>SPA11N60C3 | 8        | 16€                   |

| Driver<br>IR2111     | 4        | 8€                    |

Nowadays, for a given architecture, the use of SiC MOSFETs could be recommended if the maximum current, voltage, and temperature limits of the Si MOSFETs are compromised, e.g., for charging currents and powers higher than 50 A and 2.5 kW, respectively.

# 10. Conclusions

The general design procedure of a multiphase resonant converter for battery charger applications has been presented. Since the output current on the AC side is shared among N equal inverter sections, the circuit presents high output current capability using low-cost power MOSFETs, and the design of the resonant inductors is simplified. The proposed output rectifier is based on an M-winding current-doubler rectifier that also diminishes the conduction loss by using passive components. The efficiency curve of the proposed charger exhibits a wide flat zone, assuring a constant value of efficiency even at light load conditions. This feature is very interesting for the battery charger applications, taking into account that high efficiency is desirable along the whole charging process, despite the heavy load variation. The effect on the AC side of the leakage inductance of the transformer  $L_k$  is canceled out by the series capacitor  $C_s$ . The maximum charging current is limited by the circuit in an inherent manner, without the necessity of any control. However, the output voltage is limited to the maximum value recommended for the battery by a voltage control loop with a type I error amplifier. The control action is performed keeping constant the switching frequency by adjusting the control angle,  $\Psi$ , while maintaining the ZVS mode at any operation point. The general proposal has been validated by implementing an experimental prototype for charging a commercial 48 V LiFePO<sub>4</sub> battery with 50 Ah of capacity. The achieved efficiency of the N = 4 inverter with  $V_{dc} = 400$  V using Si MOSFETs is similar to the predicted with an N = 2 inverter with  $V_{dc} = 800$  V using SiC MOSFETs.

**Author Contributions:** The battery characterization and the experimental evaluation of the different charging profiles were carried out at the Batteries Laboratory of University of the Oviedo by J.C.V. and M.G. The proposed charger was developed at the Power Electronics Laboratory of the University of Cantabria by C.B., F.J.A., R.C. and F.J.D. Conceptualization, C.B. and J.C.V.; methodology, C.B. and J.C.V.; validation, C.B., J.C.V., R.C. and F.J.D.; formal analysis, C.B. and J.C.V.; investigation, C.B., J.C.V. and F.J.A.; writing—original draft preparation, C.B. and J.C.V.; writing—review and editing, F.J.A., M.G., R.C. and F.J.D.; project administration, F.J.A. and M.G.; funding acquisition, F.J.A. and M.G. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was funded by the Spanish Ministry of Science and the EU through the projects RTI2018-095138-B-C31: "Power Electronics for the Grid and Industry Applications", TEC2016-80700-R (AEI/FEDER/UE), PID2019-110955RB-I00, and by the Principality of Asturias via Project FC-IDI/2018/000226.

Conflicts of Interest: The authors declare no conflict of interest.

# References

- 1. Khaligh, A.; Li, Z. Battery ultracapacitor, fuel cell, and hybrid energy storage systems for electric, hybrid electric, fuel cell, and plug-in hybrid electric vehicles: State of the art. *IEEE Trans. Veh. Technol.* **2010**, *59*, 2806–2814. [CrossRef]

- Braun, P.; Cho, J.; Pikul, J.; King, W.; Zhang, H. High power rechargeable batteries. *Curr. Opin. Solid State Mater. Sci.* 2012, 16, 186–198. [CrossRef]

- 3. Waag, W.; Fleischer, C.; Sauer, D.U. Critical review of the methods for monitoring of lithium-ion batteries in electric and hybrid vehicles. *J. Power Sources* **2014**, *258*, 321–339. [CrossRef]

- 4. Wei, Z.; Zhao, J.; Xiong, R.; Dong, G.; Pou, J.; Tseng, K.J. Online Estimation of Power Capacity With Noise Effect Attenuation for Lithium-Ion Battery. *IEEE Trans. Ind. Electron.* 2019, *66*, 5724–5735. [CrossRef]

- 5. Wei, Z.; Zhao, D.; He, H.; Cao, W.; Dong, G. noise-tolerant model parameterization method for lithium-ion battery management system. *Appl. Energy* **2020**, *268*, 114932. [CrossRef]

- 6. Ke, M.Y.; Chiu, Y.H.; Wu, C.Y. Battery Modelling and SOC Estimation of a LiFePO<sub>4</sub> Battery. In Proceedings of the 2016 International Symposium on Computer, Consumer and Control (IS3C), Xi'an, China, 4–6 July 2016.

- Wang, A.; Jin, X.; Li, Y.; Li, N. LiFePO<sub>4</sub> battery modeling and SOC estimation algorithm. In Proceedings of the 2017 29th Chinese Control and Decision Conference (CCDC), Chongqing, China, 28–30 May 2017.

- 8. Kazimierczuk, M.K.; Czarkowski, D. Resonant Power Converters, 2nd ed.; John Wiley & Sons: Hoboken, NJ, USA, 2012.

- Lin, C.H.; Wang, C.M.; Hung, M.H.; Li, M.H. Series-resonant battery charger with synchronous rectifiers for LiFePO<sub>4</sub> battery pack. In Proceedings of the 2011 6th IEEE Conference on Industrial Electronics and Applications, Beijing, China, 21–23 June 2011.

- Karimi, S.; Tahami, F. A Comprehensive Time-domain-based Optimization of a High-Frequency LLC-based Li-ion Battery Charger. In Proceedings of the 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), Shiraz, Iran, 12–14 February 2019.

- 11. Shafiei, N.; Ordonez, M.; Craciun, M.; Botting, C.; Edington, M. Burst Mode Elimination in High-Power LLC Resonant Battery Charger for Electric Vehicles. *IEEE Trans. Power Electron.* **2016**, *31*, 1173–1188. [CrossRef]

- Park, S.M.; Kim, D.H.; Joo, D.M.; Kim, M.J.; Lee, B.K. Design of Output Filter in LLC Resonant Converters for Ripple Current Reduction in Battery Charging Applications. In Proceedings of the 9th International Conference on Power Electronics-ECCE Asia, Seoul, Korea, 1–5 June 2015.

- Liu, X.; Baguley, C.A.; Madawala, U.K.; Thrimawithana, D.J. A Compact Power Converter for High Current and Low Voltage Applications. In Proceedings of the 39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 140–144.

- 14. Yilmaz, M.; Krein, P.T. Review of battery charger topologies, charging power levels, and infrastructure for plug-in electric and hybrid vehicles. *IEEE Trans. Power Electron.* 2013, *28*, 2151–2169. [CrossRef]

- 15. Ashok, B. Wide-Bandgap-Based Power Devices. IEEE Power Electron. Mag. 2015, 2, 42-47.

- 16. Branas, C.; Azcondo, F.J.; Casanueva, R. A Generalize Study of Multiphase Parallel Resonant Inverters for High-Power Applications. *IEEE Trans. Circuits Syst.* 2008, 55, 2128–2138. [CrossRef]

- 17. Narada NPFC Series. Operation Manual. Available online: https://mpinarada.com/wp-content/uploads/2019/01/OM-Narada-NPFC-Series-Li-Ion-0423-V8.pdf (accessed on 22 January 2021).

- 18. Keil, P.; Jossen, A. Charging protocols for lithium-ion batteries and their impact on cycle life—An experimental study with different 18650 high-power cells. *J. Energy Storage* **2016**, *6*, 125–141. [CrossRef]

- 19. Wu, J.; Wei, Z.; Liu, K.; Quan, Z.; Li, Y. Battery-Involved Energy Management for Hybrid Electric Bus Based on Expert-Assistance Deep Deterministic Policy Gradient Algorithm. *IEEE Trans. Veh. Technol.* **2020**, *69*, 12786–12796. [CrossRef]

- 20. Wu, J.; Wei, Z.; Li, W.; Wang, Y.; Li, Y.; Sauer, D. Battery Thermal- and Health-Constrained Energy Management for Hybrid Electric Bus based on Soft Actor-Critic DRL Algorithm. *IEEE Trans. Ind. Inform.* **2020**. [CrossRef]

- 21. Notten, P.H.; het Veld, J.O.; Van Beek, J.R.G. Boostcharging Li-ion batteries: A challenging new charging concept. *J. Power Sources* **2005**, 145, 89–94. [CrossRef]

- 22. Perez, H.E.; Dey, S.; Hu, X.; Moura, S.J. Optimal Charging of Li-Ion Batteries via a Single Particle Model with Electrolyte and Thermal Dynamics. *J. Electrochem. Soc.* **2017**, *164*, 1–10. [CrossRef]

- 23. Anseán, D.; González, M.; Viera, J.C.; García, V.M.; Blanco, C.; Valledor, M. Fast charging technique for high power lithium iron phosphate batteries: A cycle life analysis. *J. Power Sources* **2013**, *239*, 9–15. [CrossRef]

- 24. Anseán, D.; Dubarry, M.; Devie, A.; Liaw, B.Y.; García, V.M.; Viera, J.C.; González, M. Fast charging technique for high power LiFePO<sub>4</sub> batteries: A mechanistic analysis of aging. *J. Power Sources* **2016**, *321*, 201–209. [CrossRef]

- 25. Chen, M.; Rincon-Mora, G.A. Accurate Electrical Battery Model Capable of Predicting Runtime and I-V Performance. *IEEE Trans. Energy Convers.* **2006**, *21*, 504–511. [CrossRef]

- 26. Truchot, C.; Dubarry, M.; Liaw, B.Y. State-of-charge estimation and uncertainty for lithium-ion battery strings. *Appl. Energy* **2014**, 119, 218–227. [CrossRef]

- 27. Jossen, A. Fundamentals of battery dynamics. J. Power Sources 2006, 154, 530–538. [CrossRef]

- Bojarski, M.; Asa, E.; Colak, K.; Czarkowski, D. A 25 kW Industrial Prototype Wireless Electric Vehicle Charger. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 1756–1761.

- 29. Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics, 2nd ed.; Springer: New York, NY, USA, 2001.

- 30. Zhang, J.; Hurley, W.G.; Wölfle, W.H. Gapped Transformer Design Methodology and Implementation for LLC Resonant Converters. *IEEE Trans. Ind. Appl.* **2016**, *52*, 342–350. [CrossRef]

- 31. Huber, L.; Jovanovic, M.H. Forward-flyback Converter with Current-Doubler Rectifier: Analysis, Design and Evaluation Results. *IEEE Trans. Power Electron.* **1999**, *14*, 184–192. [CrossRef]

- Alou, P.; Oliver, J.A.; García, O.; Prieto, R.; Cobos, J.A. Comparison of Current Doubler Rectifier and Center Tapped Rectifier for Low Voltage Applications. In Proceedings of the Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition, (APEC'06), Dallas, TX, USA, 19–23 March 2006; pp. 744–750.

- Lopez, V.M.; Navarro-Crespin, A.; Schnell, R.W.; Branas, C.; Azcondo, F.J.; Zane, R. Current Phase Surveillance in Resonant Converters for Electric Discharge Applications to Assure Operation in Zero-Voltage-Switching Mode. *IEEE Trans. Power Electron.* 2012, 27, 2925–2935. [CrossRef]

- 34. Plett, G. Extended Kalman Filtering for Battery Management System of LiPB-Based HEV Battery Packs—Part 1: Background. *J. Power Sources* 2004, 134, 252–261. [CrossRef]

- 35. Plett, G. Extended Kalman Filtering for Battery Management Systems of LiPb-Based HEV Battery Packs—Part 2: Modeling and Identification. *J. Power Sources* 2004, 134, 262–276. [CrossRef]

- Loboda, M.J.; Chung, G.; Carlson, E.; Drachev, R.; Hansen, D.; Sanchez, E.; Wan, J.; Zhang, J. Advances in SiC Substrates for Power and Energy Applications. In Proceedings of the GOMACTECH Conference, Palm Springs, CA, USA, 16–19 May 2011.

- Hazra, S.; Vechalapu, K.; Madhusoodhanan, S.; Bhattacharya, S.; Hatua, K. Gate Driver Design Considerations for SiliconCarbide MOSFETs Including For Series Connected Devices. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017.

- Nielsen, R.Ø.; Török, L.; Munk-Nielsen, S.; Blaabjerg, F. Efficiency and Cost Comparison of Si IGBT and SiC JFET Isolated DC/DC Converters. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013.