Abstract

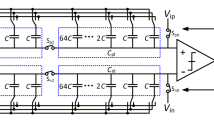

A simple energy-efficient switching procedure is proposed to reduce the total number of switches and facilitate the capacitors matching requirements in SAR ADCs. The main idea is that the coupling capacitor (CC) is utilized as the same as the unit one, which is applied for LSB charge production. After the reset phase, only the MSB capacitor is connected to the input potential, while the other experience either low and high reference potential; hence, a simplified switching strategy with 55% reduction in number of switches is retrieved. Post-layout simulation results confirm SNDR and ENOB of around 80 dB and 13 bit, respectively, at Nyquist input frequency when the conversion rate is 17 MS/s. In these conditions, FOMW and FOMS reach to 139.9 fJ/Conv-Step and 166.15 dB, respectively. Also, INL and DNL would experience the maximum level of + 0.95/− 0.58 LSB and + 0.63/− 0.74 LSB, respectively. The proposed ADC occupies active area of 1.7 mm2 and consumes around 20.6 mW power at 5 V supply and 17 MS/s conversion rate. Post-layout simulation results are performed using the HSPICE BSIM3 model of a 0.50 µm CMOS process.

Similar content being viewed by others

References

Hadidi, K. H. (2005). Data converter course notes. Urmia: Urmia University.

Kramer, M., Janssen, E., Doris, K., & Murmann, B. (2015). A 14 b 35 MS/s SAR ADC achieving 75 dB SNDR and 99 dB SFDR with loop-embedded input buffer in 40 nm CMOS. IEEE Journal of Solid-State Circuits,50(12), 2891–2900.

Luo, J., Li, J., Ning, N., Liu, Y., & Yu, Q. (2018). A 09-V 12-bit 100-MS/s 146-fJ/conversion-step SAR ADC in 40-nm CMOS. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,26(10), 1980–1988.

Sooraj, V. S., & Joseph, G. M. (2018). Speed & resolution enhancement of 12-Bit SAR ADC. In 2018 second (ICICCS) (pp. 1655–1658).

Ning, Q., Silin, L., Fang, Y., & Zhongli, L. (2010). A low power 14-bit 1 MS/s differential SAR ADC with on chip multi-segment bandgap reference. In 2010 10th IEEE international conference on solid-state and integrated circuit technology (pp. 205–207).

Krämer, M., Janssen, E., Doris, K., & Murmann, B. (2017). A 14-Bit 30-MS/s 38-mW SAR ADC Using Noise Filter Gear Shifting. IEEE Transactions on Circuits and Systems II: Express Briefs,64(2), 116–120.

Kung, C., Huang, C., Li, C., & Chang, S. (2018). A low energy consumption 10-Bit 100 kS/s SAR ADC with timing control adaptive window. IEEE (ISCAS),2018, 1–4.

Chen, B., Yaul, F., Tan, Z., & Fernando, L. (2018). An adaptive SAR ADC for DC to Nyquist rate signals. IEEE (ISCAS),2018, 1–5.

Liu, C., Huang, M., & Hsuan Tu, Y. (2016). A 12 bit 100 MS/s SAR-assisted digital-slope ADC. IEEE Journal of Solid-State Circuits,51(12), 2941–2950.

Savitha, M., & Reddy, R. V. S. (2018). 14-bit low power successive approximation ADC using two step split capacitive array DAC with multiplexer switching. In 2018 Second international conference on advances in electronics, computers and communications (ICAECC) (pp. 1–4).

Kazeminia, S., & Mahdavi, S. (2019). Highly-matched sub-ADC cells for pipeline analogue-to-digital converters. International Journal of Electronics,106(12), 1785–1813.

Mahdavi, S. (2017). A 12 bit 76MS/s SAR ADC with a capacitor merged technique in 0.18 µm CMOS technology. Journal of Electrical and Computer Engineering Innovations (JECEI),5(2), 121–130.

Özkaya, İ., Gürleyük, Ç., Ergül, A., Akkaya, A., & Aksın, D. Y. (2014). A 50 V input range 14 bit 250 kS/s ADC with 97.8 dB SFDR and 80.2 dB SNR. In ESSCIRC 2014—40th European solid state circuits conference (ESSCIRC) (pp. 71–74).

Liu, S., Shen, Y., & Zhu, Z. (2012). A 12-Bit 10 MS/s SAR ADC with high linearity and energy-efficient switching. IEEE Transactions on Circuits and Systems I: Regular Papers,63(10), 1616–1627.

Hadidi, K. H., Tso, V. S., & Temes, G. C. (1990). An 8-b 13-MHz successive approximation A/D converter. IEEE Journal of Solid-State Circuits,25(3), 880–885.

Baek, S., Lee, J., & Ryu, S. (2013). An 88-dB Max-SFDR 12-bit SAR ADC with speed-enhanced ADEC and dual registers. IEEE Transactions on Circuits and Systems II: Express Briefs,60(9), 562–566.

Yoshioka, M., Ishikawa, K., Takayama, T., & Tsukamoto, S. (2010). A 10-b 50-MS/s 820-µW SAR ADC with on-chip digital calibration. IEEE Transactions on Biomedical Circuits and Systems,4(6), 410–416.

Chung, Y., Wu, M., & Li, H. (2013). A 14b 80 MS/s SAR ADC with 73.6 dB SNDR in 65 nm CMOS. IEEE Journal of Solid-State Circuits,48(12), 3059–3066.

Thirunakkarasu, S., & Bakkaloglu, B. (2015). Built-in self-calibration and digital-trim technique for 14-Bit SAR ADCs achieving ± 1 LSB INL. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,23(5), 916–925.

Tseng, W. H., Lee, W. L., Huang, C. Y., & Chiu, P. C. (2016). A 12-bit 104 MS/s SAR ADC in 28 nm CMOS for digitally-assisted wireless transmitters. IEEE Journal of Solid-State Circuits,51(10), 2222–2231.

Song, Y., Xue, Z., Shiquan Fan, Y., & Geng, L. (2016). A 0.6-V 10-bit 200-kS/s fully differential SAR ADC with incremental converting algorithm for energy efficient applications. IEEE Transactions on Circuits and Systems I: Regular Papers,63(4), 449–458.

Taherzadeh-Sani, M., Lotfi, R., & Nabki, F. (2014). A 10-bit 110 kS/s 1.16 µW SA-ADC with a hybrid differential/single-ended DAC in 180-nm CMOS for multichannel biomedical applications. IEEE Transactions on Circuits and Systems II: Express Briefs,61(8), 584–588.

Zhang, Q., Li, J., Zhang, Z., Wu, K., Ning, N., & Yu, Q. (2019). A low-power and area-efficient 14-bit SAR ADC with hybrid CDAC for array sensors. IEEE International Symposium on Circuits and Systems (ISCAS),2019, 1–4.

Chung, Y., Wu, M., & Li, H. (2015). A 12-bit 8.47-fJ/conversion-step capacitor-swapping SAR ADC in 110-nm CMOS. IEEE Transactions on Circuits and Systems I: Regular Papers,62(1), 10–18.

Wong, S. S., Chio, U. F., Zhu, Y., Sin, S. W., Seng-Pan, U., & Martins, R. P. (2013). A 2.3 mW 10-bit 170 MS/s two-step binary-search assisted time-interleaved SAR ADC. IEEE Journal of Solid-State Circuits,48(8), 1783–1794.

Zhang, D., Bhide, A., & Alvandpour, A. (2012). A 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13 μm CMOS for medical implant devices. IEEE JSSC,47(7), 1585–1593.

Mahdavi, S., & Gaznag, T. T. (2018). A 2.52 fJ/conversion-step 12-bit 154MS/s with 68.78 dB SNDR full differential SAR ADC with a novel capacitor switching scheme. In 26th Iranian conference on electrical engineering (ICEE2018) (pp. 81–86).

Chen, D. G., Tang, F., & Bermak, A. (2013). A low-power pilot-DAC based column parallel 8b SAR ADC with forward error correction for CMOS image sensors. IEEE Transactions on Circuits and Systems I: Regular Papers,60(10), 2572–2583.

Tsai, W., Kuo, C., Chang, S., Lo, L., Wu, Y., & Chen, C. (2015). A 10-bit 50-MS/s SAR ADC for dual-voltage domain portable systems. IEEE International Symposium on Circuits and Systems (ISCAS),2015, 2425–2428.

Chen, X., Ye, F., & Ren, J. (2017). A 13-bit non-binary weighted SAR ADC with bridge structure using digital calibration for capacitor weight error. In 2017 IEEE 12th international conference on ASIC (ASICON) (pp. 32–35).

Kardonik, O. (2013). A study of SAR ADC and implementation of 10-Bit asynchronous design. A thesis submitted to the University of Texas at Austin for the degree of Master of Science in Engineering.

Ha, H., Lee, S., Kim, B., Park, H., & Sim, J. (2014). A 0.5-V, 1.47-µW 40-kS/s 13-bit SAR ADC with capacitor error compensation. IEEE Transactions on Circuits and Systems II: Express Briefs,61(11), 840–844.

Fateh, S., Schönle, P., Bettini, L., Rovere, G., Benini, L., & Huang, I. (2015). A reconfigurable 5-to-14 bit SAR ADC for battery-powered medical instrumentation. IEEE TCAS I: Regular Papers,62(11), 2685–2694.

Lee, P., Lin, J., & Hsieh, C. (2016). A 0.4 V 1.94 fJ/conversion-step 10 bit 750 kS/s SAR ADC with input-range-adaptive switching. IEEE Transactions on Circuits and Systems I: Regular Papers,63(12), 2149–2157.

Wen, J. Y., Chang, P. H., Huang, J. F., & Lai, W. C. (2015). Chip design of a 12-bit 5MS/s fully differential SAR ADC with resistor-capacitor array DAC technique for wireless application. In 2015 IEEE international conference on signal processing, communications and computing (ICSPCC) (pp. 1–4).

Navidi, S. M., & Ehsanian, M. (2018). A 9-bit low-power fully differential SAR ADC using adaptive supply and reference voltages. In ICEE (pp. 205–210) IEEE.

Mahdavi, S., & Ghadimi, E. (2017). A new 13-bit 100 MS/s full differential successive approximation register analog to digital converter (SAR ADC) using a novel compound R-2R/C structure. In 2017 IEEE 4th international conference on knowledge-based engineering and innovation (KBEI) (pp. 0237–0242).

Haenzsche, S., Höppner, S., Ellguth, G., & Schüffny, R. (2014). A 12-b 4-MS/s SAR ADC with configurable redundancy in 28-nm CMOS technology. IEEE Transactions on Circuits and Systems II: Express Briefs,61(11), 835–839.

Huang, G. Y., Chang, S. J., Liu, C. C., & Lin, Y. Z. (2012). 10-bit 30-MS/s SAR ADC using a switchback switching method. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,21(3), 584–588.

Yang, S., Liu, M., Mu, Y., & Chang, Y. (2017). A 14-bit 5 MS/s split non-binary SAR ADC. In 2017 IEEE 12th international conference on ASIC (ASICON) (pp. 765–768).

Deng, H., & Li, P. (2014). A 8-bit 10 MS/s asynchronous SAR ADC with resistor-capacitor array DAC. In 2014 international conference on anti-counterfeiting, security and identification (ASID) (pp. 1–5).

Liu, C., Chang, S., Huang, G., & Lin, Y. (2010). A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE JSSC,45(4), 731–740.

Chung, Y., Yen, C., & Wu, M. (2016). A 24-μW 12-bit 1-MS/s SAR ADC with two-step decision DAC switching in 110-nm CMOS. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,24(11), 3334–3344.

Kazeminia, S., & Mahdavi, S. (2016). A 800 MS/s, 150 µV input-referred offset single-stage latched comparator. In 2016 MIXDES-23rd international conference mixed design of integrated circuits and systems (pp. 119–123).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Mahdavi, S., Kazeminia, S. & Hadidi, K. A 17 MS/s SAR ADC with energy-efficient switching strategy. Analog Integr Circ Sig Process 103, 223–236 (2020). https://doi.org/10.1007/s10470-020-01634-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01634-9