### 8253-Timer

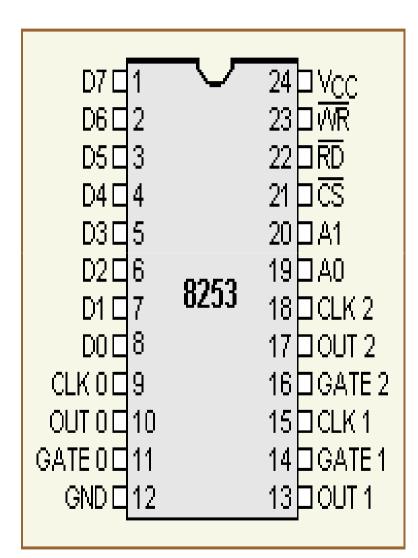

### 8253 Pin Diagram

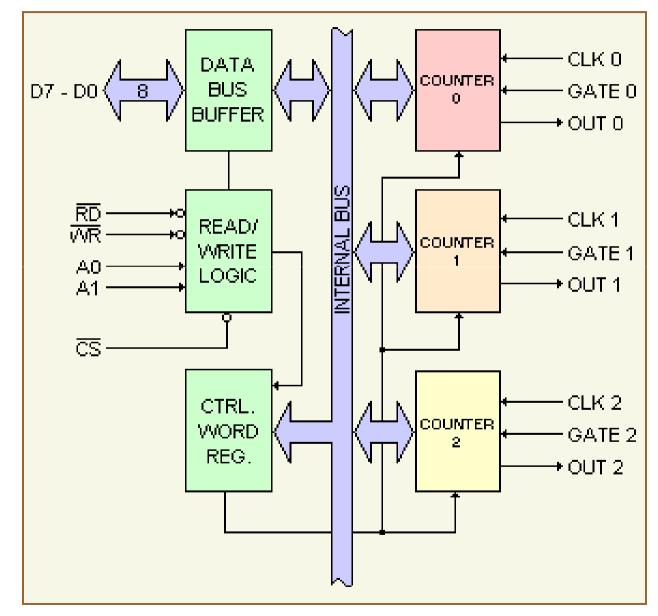

### 8253 Block Diagram

## **Pin Description**

- Clock: This is the clock input for the counter. The counter is 16 bits.

- The maximum clock frequency is 1 / 380 nanoseconds or

2.6 megahertz. The minimum clock frequency is DC or static operation.

- Out: This single output line is the signal that is the final programmed output of the device.

- Actual operation of the out line depends on how the device has been programmed.

- Gate: This input can act as a gate for the clock input line, or it can act as a start pulse, depending on the programmed mode of the counter.

### **Counter Features**

- Each counter is **identical**, and each consists of a **16-bit**, pre-settable, **down** counter.

- Each is **fully independent** and can be easily read by the CPU.

- When the counter is read, the data within the counter will not be disturbed.

- This allows the system or your own program to **monitor** the counter's value at any time, without disrupting the overall function of the 8253.

### **Counter Selection**

|                              | RD | WR | AO | A1 | function        |

|------------------------------|----|----|----|----|-----------------|

|                              | 1  | 0  | 0  | 0  | Load counter O  |

| COUNTER 0                    | 0  | 1  | 0  | 0  | Read counter 0  |

| COUNTER 1                    | 1  | 0  | 0  | 1  | Load counter 1  |

| COUNTERT                     | 0  | 1  | 0  | 1  | Read counter 1  |

| COUNTER 2                    | 1  | 0  | 1  | 0  | Load counter 2  |

|                              | 0  | 1  | 1  | 0  | Read counter 2  |

| MODE WORD or<br>CONTROL WORD | 1  | 0  | 1  | 1  | Write mode word |

|                              | 0  | 1  | 1  | 1  | No-operation    |

# **Control Word Register**

- This internal register is used to write information to, prior to using the device.

- This register is addressed when **A0** and **A1** inputs are logical 1's.

- The data in the register **controls the operation mode** and the selection of either binary or BCD counting format.

- The register can **only** be written to.

- You can't read information from the register.

## **Control Word Format**

| CONTROL BYTE D7 - D0 |     |     |     |    |    |    |     |

|----------------------|-----|-----|-----|----|----|----|-----|

| D7                   | D6  | D5  | D4  | DЗ | D2 | D1 | DO  |

| SC1                  | SCO | RL1 | RLO | M2 | M1 | MO | BCP |

| D7  | D6  |    | D5  | D4  | R         | D3 | D2 | D1 |                               | DO    | counts down in        |          |  |  |

|-----|-----|----|-----|-----|-----------|----|----|----|-------------------------------|-------|-----------------------|----------|--|--|

| SC1 | SCO |    | RL1 | RLO | к         | M2 | M1 | MO | Μ                             | 0     | binary                |          |  |  |

| 0   | 0   |    | 0   | 0   | C(<br>th  | 0  | 0  | 0  | rr                            | 1     | BCD                   | al count |  |  |

| 0   | 1   |    |     |     | сс<br>lat | 0  | 0  | 1  | mode 1: programmable one-shot |       |                       |          |  |  |

| 1   | 0   |    | 0   | 1   | Rŧ        | х  | 1  | 0  | mode 2: rate generator        |       |                       |          |  |  |

| 1   | 1   | il | 1   | 0   | Rŧ        | х  | 1  | 1  | mode 3: square wave generator |       |                       |          |  |  |

|     |     |    | 1   | 1   | Rŧ        | 1  | 0  | 0  | m                             | ode 4 | 4: software triggered | strobe   |  |  |

|     |     |    |     |     | th        | 1  | 0  | 1  | m                             | ode 5 | 5: hardware triggere  | d strobe |  |  |

Once a counter is set up, it will remain that way until it is changed by another control word.

#### **Different uses of the 8253 gate input pin**

| Signal Status | Low or going low                                           | Rising                                                        | High             |

|---------------|------------------------------------------------------------|---------------------------------------------------------------|------------------|

| Mode          |                                                            |                                                               |                  |

| 0             | Disables counting                                          |                                                               | Enables counting |

| 1             |                                                            | 1) Initiates counting<br>2) Resets output<br>after next clock |                  |

| 2             | 1) Disables counting<br>2) Sets output<br>immediately high | 1) Reloads counter<br>2) Initiates counting                   | Enables counting |

| 3             | 1) Disables counting<br>2) Sets output<br>immediately high | Initiates counting                                            | Enables counting |

| 4             | Disables counting                                          |                                                               | Enables counting |

| 5             |                                                            | Initiates counting                                            |                  |

This table shows the different uses of the 8253 gate input pin.

Each mode of operation for the counter has a different use for the GATE input pin.

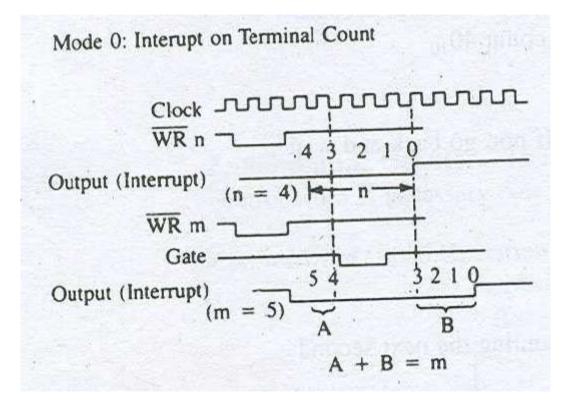

- Interrupt on Terminal Count

- The counter will be programmed to an initial value and afterwards **counts down** at a rate equal to the input clock frequency(8 MHz).

- When the count is equal to 0, the **OUT pin** will be a logical 1.

- The output will stay a logical 1 **until the counter is reloaded** with a new value or the same value or **until a mode word is written** to the device.

- Once the counter starts counting down, the **GATE input can disable the internal counting** by setting the GATE to a logical 0.

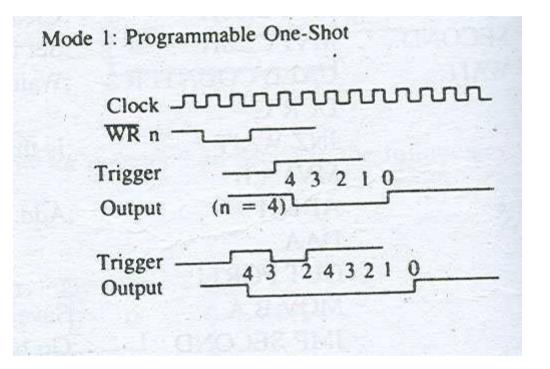

- Programmable One-Shot

- In mode 1, the device can be setup to give an **output pulse** that is an integer number of clock pulses.

- The one-shot is **triggered** on the rising edge of the GATE input.

- If the trigger occurs during the pulse output, the 8253 will be **retriggered** again.

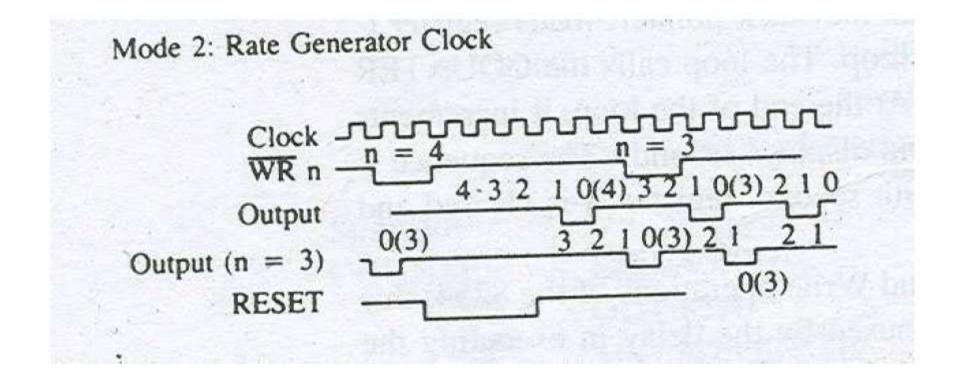

- Rate Generator

- The counter that is programmed for mode 2 becomes a "divide by n" counter.

- The **OUT pin** of the counter goes to low for one input clock period.

- The time between the pulses of going low is dependent on the **present count in the counter's register**.

- For example, suppose to get an output frequency of 1,000 Hz, the period would be 1 / 1,000 s = 1 ms or 1,000 μs.

- If an input clock of 1 MHz were applied to the clock input of the counter #0, then the counter #0 would need to be programmed to 1000 μs.

- This could be done in **decimal or in BCD**. (The period of an input clock of 1 MHz is  $1 / 1,000,000 = 1 \mu s$ .)

- The formula is: **n=fi/fout**, where fi = input clock frequency, fout = output frequency, n = value to be loaded.

- Square Wave Generator

- Mode 3 is similar to the mode 2 except that the output will be high for half the period and low for half.

- If the count is odd, the output will be high for (n+1)/2 and low for (n-1)/2 counts.

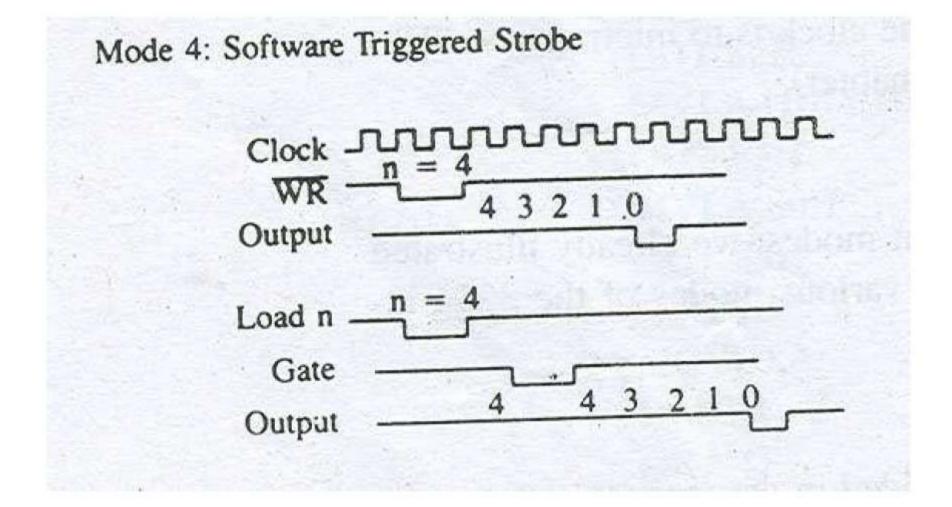

- Software Triggered Strobe

- In this mode the programmer can set up the counter to give an **output timeout** starting when the register is loaded.

- On the terminal count, when the counter equals to 0, the output will go to a logical 0 for one clock period and then returns to a logical 1.

- Firstly, when the mode is set, the **output will be a** logical 1.

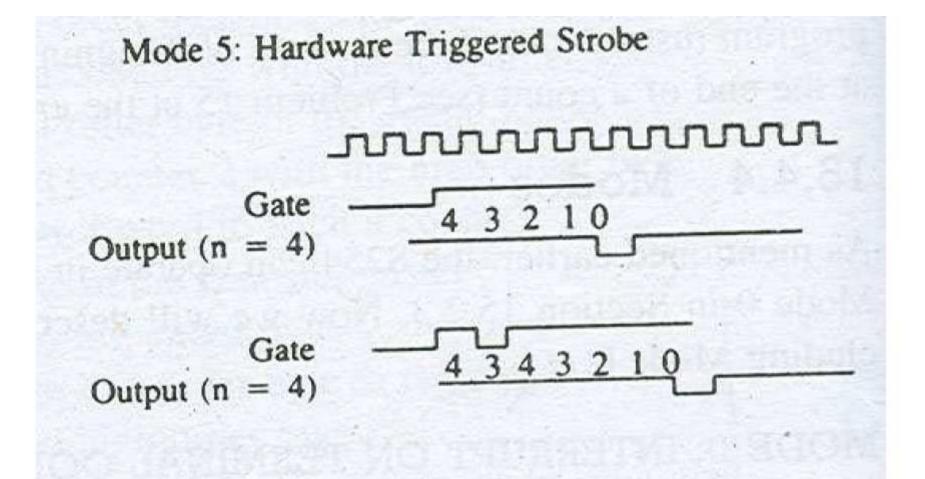

- Hardware Triggered Strobe

- In this mode **the rising edge of the trigger input** will start the counting of the counter.

- The **output goes low for one clock** at the terminal count.

- The counter is **re triggerable**, thus meaning that if the trigger input is taken low and then high during a count sequence, the sequence will start over.

- When the external trigger input goes to a logical 1, the timer will start to time out.

- If the **external trigger occurs again**, prior to the time completing a full timeout, the timer will retrigger.