# HARDWARE OPEN SYSTEMS TECHNOLOGIES

Hardware Open Systems Technologies OpenVPX Core Technology Tier 2 Standard

Document Number: HOST00002-11

Version: 4.1

Date: June 29, 2021

i

# Table of Contents

| 1 HOS  | T Overview                                 | L  |

|--------|--------------------------------------------|----|

| 1.1    | HOST Tier 2 Objective                      | L  |

| 1.2    | HOST– OpenVPX Core Technology              | L  |

| 1.3    | Referenced Documents                       | 2  |

| 2 Guid | lelines                                    | 1  |

| 2.1    | Typography                                 | t  |

| 2.2    | Identifier                                 | t  |

| 2.2.1  | Rule                                       | ţ  |

| 2.2.2  | Recommendation                             | ł  |

| 2.2.3  | Permission                                 | 1  |

| 2.2.4  | Observation                                | 5  |

| 3 HOS  | T Conformance                              | 5  |

| 3.1    | HOST Conformance Program                   | 5  |

| 3.1.1  | HOST Conformance Program Terminology       | 5  |

| 3.1.2  | Verification Methods                       | 7  |

| 3.1.3  | HOST OpenVPX Verification Methods Document | 1  |

| 3.1.4  | HOST Tier 3 Specification Conformance      | 7  |

| 3.1.5  | HOST Component Conformance                 | 7  |

| 3.1.6  | •                                          |    |

| 4 Impl | ementation                                 | )  |

| 4.1    | Hardware System Management                 | )  |

| 4.2    | Hardware Implementation                    | )  |

| 4.2.1  | HOST Components                            | )  |

| 4.     | .2.1.1 HOST Modules                        | )  |

| 4.     | .2.1.2 HOST External Interface             | LO |

| 4.     | .2.1.3 HOST Transmission Components        | LO |

| 4.     | .2.1.4 HOST Enclosure                      | 1  |

| 4.3    | Resource Implementation                    | 11 |

| 5 Tier | 2 Standard Requirements                    | 13 |

| 5.1    | HOST Module Requirements                   | 13 |

| 5.1.1  | HOST Plug-In Module Requirements           | 14 |

ii

# HOST OpenVPX Core Technology Tier 2 Standard v4.1

|      | 5.1. | 1.1    | VPX Modules                                               | 14  |

|------|------|--------|-----------------------------------------------------------|-----|

|      | 5.1. | 1.2    | Power Supply Modules                                      | 50  |

| 5.1  | L.2  | Mezza  | nine Requirements                                         | 52  |

|      | 5.1. | 2.1    | Common Mezzanine Requirements                             | 52  |

|      | 5.1. | 2.2    | XMC Mezzanine Requirements                                | 53  |

|      | 5.1. | 2.3    | PMC Mezzanine Requirements                                | 54  |

| 5.2  | Н    | ardwar | e System Management Option                                | 54  |

| 5.3  | Н    | ardwar | e System Management                                       | 54  |

| 5.3  | 3.1  | Hardw  | vare System Management Overview                           | 54  |

| 5.3  | 3.2  | Hardw  | vare System Management Architecture                       | 55  |

| 5.3  | 3.3  | Hardw  | vare System Management Requirements                       | 56  |

|      | 5.3. | 3.1    | Chassis Manager                                           | 56  |

|      | 5.3. | 3.2    | IPMCs                                                     | 57  |

|      | 5.3. | 3.3    | Additional Hardware Management Requirements               | 58  |

|      | 5.3. | 3.4    | Additional Mandatory Messages                             | 58  |

| 5.4  | Н    | ardwar | e                                                         | 61  |

| 5.4  | 1.1  | HOST   | Transmission Interfaces                                   | 62  |

|      | 5.4. | 1.1    | Common Transmission Interface Requirements                | 63  |

|      | 5.4. | 1.2    | System Communications Transmission Interface Requirements | 63  |

|      | 5.4. | 1.3    | System I/O Transmission Interface Requirements            | 65  |

|      | 5.4. | 1.4    | External I/O Transmission Interface Requirements          | 65  |

|      | 5.4. | 1.5    | Chassis Management Transmission Interface Requirements    | 67  |

|      | 5.4. | 1.6    | System Power Distribution Interface Requirements          | 71  |

| 5.4  | 1.2  | HOST   | Components                                                | 73  |

|      | 5.4. | 2.1    | HOST Components Common Environmental Requirements         | 74  |

|      | 5.4. | 2.2    | HOST Enclosure                                            | 75  |

|      | 5.4. | 2.3    | HOST Module                                               | 76  |

|      | 5.4. | 2.4    | HOST Transmission Components                              | 79  |

| 6 Gl | ossa | ry     |                                                           | .84 |

| 7 Ac | rony | /ms    |                                                           | .90 |

iii

# List of Figures

| Figure 4-1 – HOST Component Categories                                     | . 11 |

|----------------------------------------------------------------------------|------|

| Figure 4-2 – Resource Implementation Example                               | . 12 |

| Figure 5-1 – HOST Module Rules Hierarchy                                   |      |

| Figure 5-2 – Slot Profile SLT6-PAY-4F1Q2U2T-10.2.1                         | . 18 |

| Figure 5-3 – Slot Profile SLT6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-10.6.3-n        | . 20 |

| Figure 5-4 – Slot Profile SLT6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-10.6.4-n        |      |

| Figure 5-5 – Slot Profile SLT3-PAY-2F2U-14.2.3                             | . 24 |

| Figure 5-6 – Slot Profile SLT3-PAY-1F1F2U-14.2.4                           |      |

| Figure 5-7 – Slot Profile SLT3-PAY-1F1U1S1S1U1U4F1J-14.6.13-n              | . 26 |

| Figure 5-8 – Slot Profile SLT3-PAY-1F1U1S1S1U1U2F1H-14.6.11-n              | . 27 |

| Figure 5-9 – Slot Profile SLT3-PAY-1F1F2U1TU1T1U1T-14.2.16                 |      |

| Figure 5-10 – Slot Profile PAY-1F1F2U5S-HOST                               |      |

| Figure 5-11 – Slot Profile SLT3x-TIM-2S1U22S1U2U1H-14.9.2-n                | . 33 |

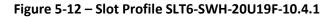

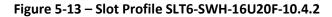

| Figure 5-12 – Slot Profile SLT6-SWH-20U19F-10.4.1                          | . 35 |

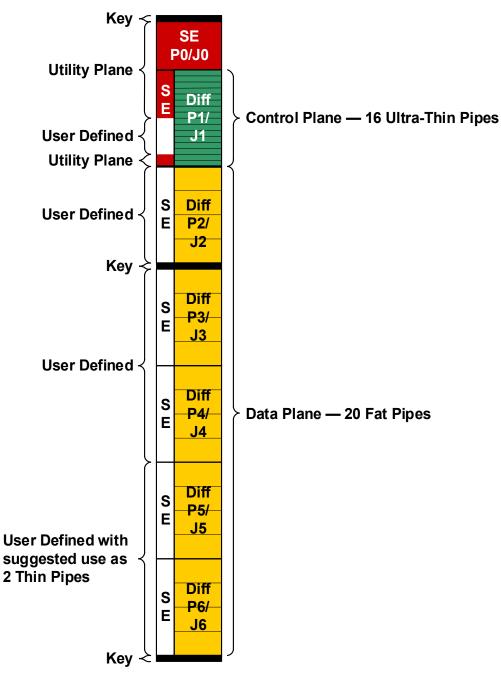

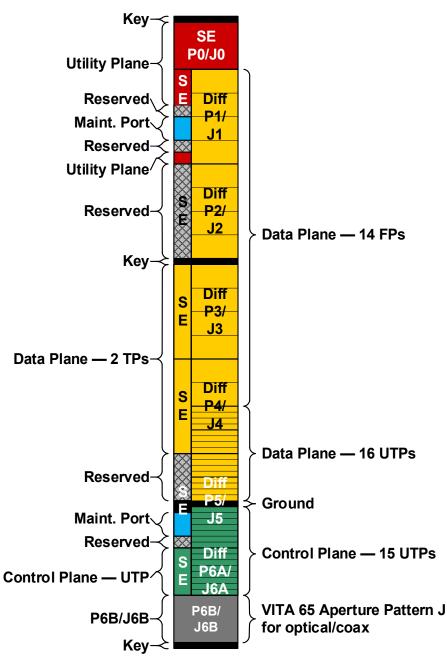

| Figure 5-13 – Slot Profile SLT6-SWH-16U20F-10.4.2                          | . 37 |

| Figure 5-14 – Slot Profile SLT6-SWH-14F16U1U15U1J-10.8.1                   | . 39 |

| Figure 5-15 – Slot Profile SLT3-SWH-6F8U-14.4.15                           | . 40 |

| Figure 5-16 – Slot Profile SLT3-SWH-2F24U-14.4.3                           |      |

| Figure 5-17 – Slot Profile SLT3-SWH-6F1U7U-14.4.14                         |      |

| Figure 5-18 – Slot Profile SLT3-SWH-4F1U7U1J-14.8.7-n                      |      |

| Figure 5-19 – Slot Profile SLT3-SWH-1F1S1S1U1U1K-14.8.8-n                  | . 44 |

| Figure 5-20 – Slot Profile SLT6-PAY-4U2U-10.2.8                            |      |

| Figure 5-21 – Slot Profile SLT6-PER-2F-10.3.2                              | . 47 |

| Figure 5-22 – Slot Profile SLT3-PAY-2U2U-14.2.17                           | . 48 |

| Figure 5-23 – Slot Profile SLT3-PER-1U-14.3.3                              | . 49 |

| Figure 5-24 – Slot Profile SLT3-PER-1F-14.3.2                              |      |

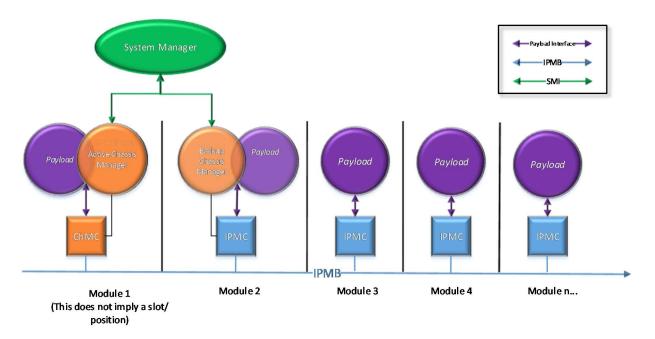

| Figure 5-25 – Hardware System Management                                   | . 56 |

| Figure 5-26 – HOST Tier 2 Transmission Interface Configuration             | . 63 |

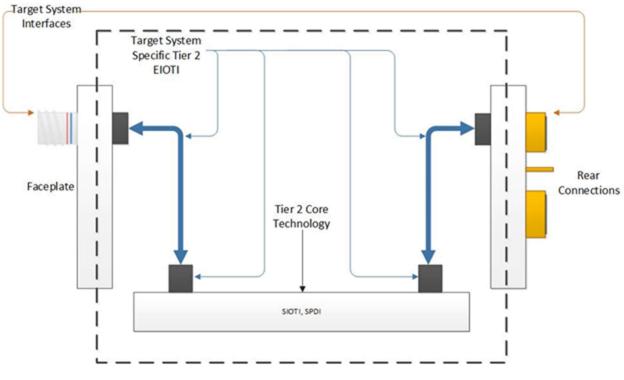

| Figure 5-27 – HOST EIOTI Interconnect Diagram                              | . 66 |

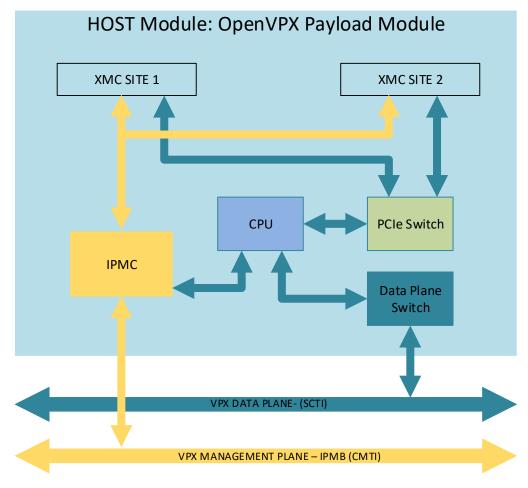

| Figure 5-28 – Example HOST Payload Module XMC Mezzanine CMTI Configuration | . 69 |

| Figure 5-29 – Example HOST Payload Module PMC Mezzanine CMTI Configuration | . 70 |

| Figure 5-30 – Notional Side View of a Generic ATR Mission Computer         | . 74 |

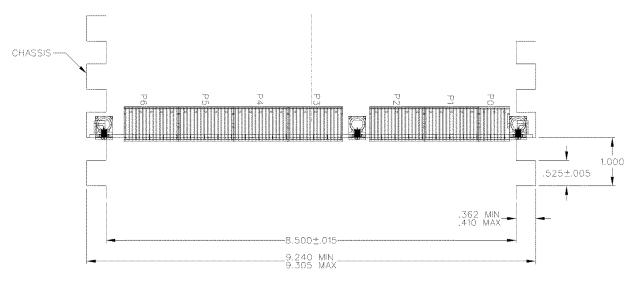

| Figure 5-31 – 6U Rail Geometry                                             | . 75 |

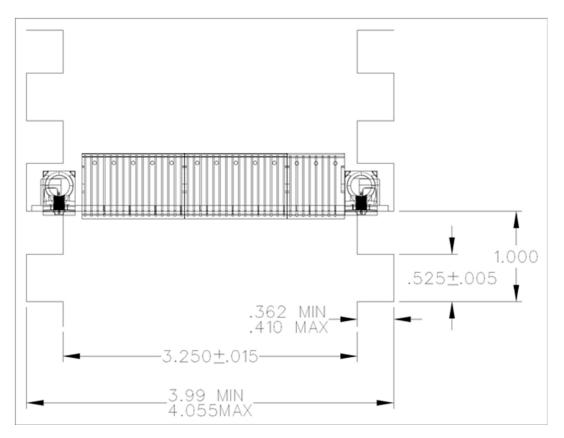

| Figure 5-32 – 3U Rail Geometry                                             | . 76 |

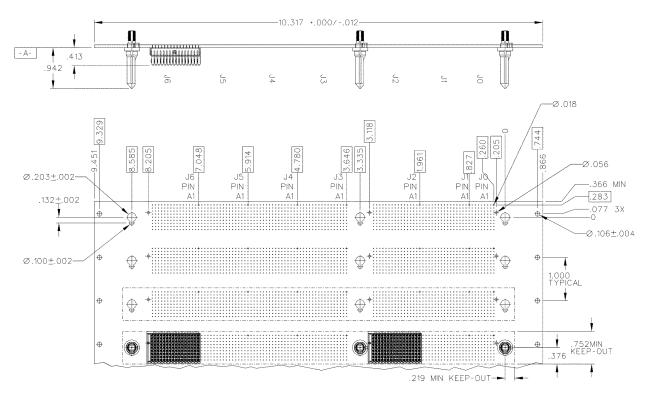

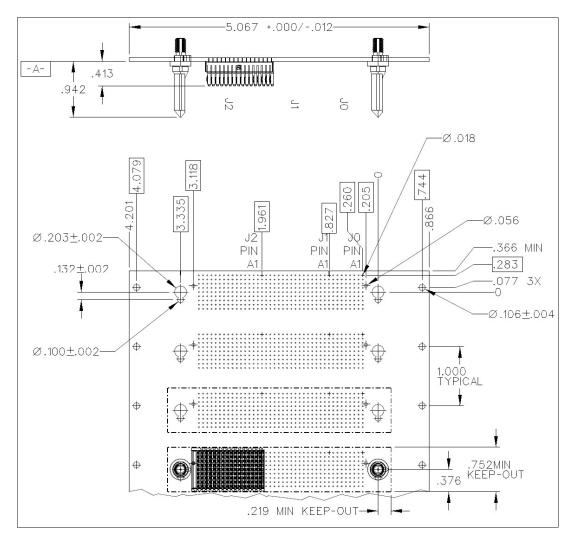

| Figure 5-33 – 6U OpenVPX Backplane Form Factor                             | . 80 |

| Figure 5-34 – 3U OpenVPX Backplane Form Factor                             | . 81 |

iv

# List of Tables

| Table 5-1 P1/J1 Pin Mapping for PAY-1F1F2U5S-HOST | 30 |

|---------------------------------------------------|----|

| Table 5-2 P2/J2 Pin Mapping for PAY-1F1F2U5S-HOST |    |

| Table 5-3 Module Profiles for PAY-1F1F2U5S-HOST   |    |

| Table 5-4 Additional Mandatory Messages           | 61 |

| Table 5-5 Module Environmental Requirements       |    |

# 1 HOST Overview

Hardware Open Systems Technologies (HOST) is a standards framework that applies open architectures to high-performance embedded computing. The HOST Standard contains well-defined interfaces based on established industry standards that support a Modular Open Systems Approach (MOSA) and defines the implementation of *Commercial-Off-the-Shelf* (COTS) components for embedded computing on Open systems, so scalability and compatibility across the breadth of U.S. Defense *platforms*, systems, and applications can be achieved to improve defense acquisition. The HOST Standard is intended to promote Open System Architectures (OSA), reduce production cost, shorten development time, and improve Life Cycle Sustainment through the increased use of COTS components, system modularity, and improved upgradeability.

# 1.1 HOST Tier 2 Objective

The HOST OpenVPX Core Technology Tier 2 Standard applies OpenVPX embedded computing technologies to the HOST Tier 1 Standard architecture, supports the framework outlined in the HOST Tier 1, and is platform agnostic so to not incorporate specific *Target System* requirements. This document provides a description of *HOST components*, as it relates to OpenVPX, and the interfaces (physical, logical, mechanical, electrical, etc.) required to create a *HOST conformant* system based on unique customer needs. The objective of the HOST Tier 2 is to introduce the application of OpenVPX as a Core Technology to the HOST architecture, adopt the conventions and conformance standards applicable to OpenVPX, and define platform requirements for this Core Technology Standard.

# 1.2 HOST- OpenVPX Core Technology

The HOST ecosystem is a framework based on a hierarchical tiered architecture and through the adoption of core technologies and leveraging industry standards, HOST is able to establish a derivation of *Tier 3 Specifications* for modular component *interoperability*. This HOST OpenVPX Core Technology Standard leverages existing OpenVPX standards such as ANSI/VITA 65.0 for system interface standardizations, ANSI/VITA 48.2 for conduction-cooled interfaces, and ANSI/VITA 46.11 for hardware system management to define platform requirements. HOST Tier 2 standards are *Platform* agnostic; therefore, this standard does not incorporate specific requirements of Target Systems. The goals of this HOST Core Technology Standard are to:

- Enable the derivation of HOST Tier 3 Specifications from the combination of the HOST Tier 1 Standard, HOST Tier 2 Standard, and Target System requirements

- Facilitate OpenVPX module interoperability and reuse through defined requirements

- Facilitate the use of OpenVPX Commercial-Off-the-Shelf (COTS) components while adhering to the requirements defined within the HOST Tier 2 Standard.

- Apply OpenVPX embedded computing technologies while leveraging industry standards to fit the needs of HOST

The scope of coverage for this HOST Tier 2 Standard includes governing the implementation of HOST conformant systems, explaining HOST Conformance in relation to the tiered hierarchy, introducing *HOST Module* types inclusive of a requirement hierarchy, Hardware System Management Architecture, and HOST Architecture which establishes the five HOST Transmission Interfaces and the four HOST components relative to OpenVPX as the core technology.

## 1.3 **Referenced Documents**

ANSI/VITA 42.0-2016, Switched Mezzanine Card (XMC)

ANSI/VITA 42.3-2020, XMC PCI Express Protocol Layer Standard

ANSI/VITA 46.0-2019, VPX Base Standard

ANSI/VITA 46.6-2013(R2018), Gigabit Ethernet Control Plane on VPX

ANSI/VITA 46.9-2018, PMC/XMC Rear I/O Fabric Signal Mapping on 3U and 6U VPX Modules Standard

ANSI/VITA 46.11-2015, System Management on VPX

ANSI/VITA 47.0-2019, Construction, Safety, and Quality for Plug-In Modules Standard

ANSI/VITA 47.2-2019, Class 2 Requirements for Environments, Design and Construction, Safety, and Quality f or V ITA 47 Plug-In Modules

ANSI/VITA 47.3-2019, Class 3 Requirements for Environments, Design and Construction, Safety, and Quality for VITA 47 Plug-In Modules

ANSI/VITA 48.2-2020, Mechanical Specifications for Microcomputers Using REDI Conduction Cooling Applied to VITA 46

ANSI/VITA 62.0-2016, Modular Power Supply Standard

ANSI/VITA 65.0-2019, OpenVPX System Standard

ANSI/VITA 65.1-2019, OpenVPX System Standard – Profile Tables

ANSI/VITA 66.0-2016, Optical Interconnect on VPX – Base Standard

ANSI/VITA 67.0-2019, Coaxial Interconnect on VPX – Base Standard

ANSI/VITA 67.3-2017, Coaxial Interconnect on VPX, Spring-Loaded Contact on Backplane

ARINC Specification 404A (March 15, 1974) – Air Transport Equipment Cases and Racking

ASTM G85 - 11 (August 2011), Standard Practice for Modified Salt Spray (Fog) Testing

DO-160 (December 16, 2014), Environmental Conditions and Test Procedures for Airborne Equipment

IEC 61000-4-2 (December 09, 2019), Electromagnetic compatibility (EMC) - Part 4-2: Testing and measurement techniques - Electrostatic discharge immunity test

IEEE 1101.1-1998 (December 18, 1998), IEEE Standard for Mechanical Core Specifications for Microcomputers Using IEC 60603-2 Connectors

IEEE 1101.2-1992 (January 31, 2008), IEEE Standard for Mechanical Core Specifications for Conduction-Cooled Eurocards

IEEE 1386.1-2001 (June 14, 2001), IEEE Standard Physical and Environmental Layers for PCI Mezzanine

#### HOST OpenVPX Core Technology Tier 2 Standard v4.1

Intelligent Platform Management Interface (IPMI) Specification Version 2.0, Revision 1.1, dated 01 October 2013

IPC J-STD-001F (July 2014), Requirements for Soldered Electrical and Electronic Assemblies

IPC-CC-830B with Amendment 1 (October 2008), Qualification and Performance of Electrical Insulating Compound for Printed Wiring Assemblies

IPMI Platform Management FRU Information Storage Definition Version 1.0, Revision 1.2, dated 28 February 2013

MIL-STD-202H (April 18, 2015), Electronic and Electrical Component Parts

MIL-STD-810H (January 31, 2019), Environmental Engineering Considerations and Laboratory Tests

PICMG 3.0 AdvancedTCA Base Specification (March 24, 2008)

QPDSIS-46058 Insulating Compound, Electrical, dated 22 June 2017

# 2 Guidelines

# 2.1 Typography

The following typographical conventions are used throughout this document:

- Italics Indicates a term defined in the glossary or for emphasis (occurs on first instance).

- Bold Indicates identifiers and their terms (ex: "shall", "should", "may") as defined in SECTION Error! Reference source not found.

- SMALL CAPS Cross-reference to another section, figure, or table in this document.

# 2.2 Identifier

To avoid confusion, many of the paragraphs in this standard are provided with an identifier that indicates the type of information that the paragraph contains and is uniquely identifiable.

These identifiers are of the format **Tk-nnn-xxxx** where:

- k is equal to the HOST Tier that the identifier is from

- nnn is an indicator of the type of content, where:

- RUL is a rule

- REC is a recommendation

- PER is a permission

- OBS is an observation

- xxxx is a sequence number

The types of content are reserved for specific use as defined in subsequent sections.

References to a section or paragraph from an external source that are included in a statement with an identifier will also contain all lower level sections and paragraphs.

Any text not provided with an identifier is to be interpreted as descriptive in nature. This text will be written in either a descriptive or a narrative style.

## 2.2.1 Rule

Compliance with rules is mandatory. Rules always include the term "shall." Rules are expressed in some combination of text, figures, tables, or drawings. All rules will be followed to ensure compatibility across interfaces.

## 2.2.2 Recommendation

Compliance with Recommendations is optional. Recommendations always include the term "should." Recommendations are used to convey implementation advice based on the community's collective knowledge base. Recommendations found in this standard are provided to designers to reduce their learning curve.

## 2.2.3 Permission

Compliance with Permissions is optional. Permissions always include the term "may." In some cases, a rule does not specifically prohibit a certain design approach, but the reader might be left wondering whether that approach might violate the spirit of the rule or whether it might lead to some subtle problem. Permissions reassure the reader that a certain approach is acceptable.

## 2.2.4 Observation

Observations do not offer any specific advice. They are provided to enhance comprehension and usually follow naturally from what has just been discussed. They spell out the implications of certain rules and bring attention to things that might otherwise be overlooked. They also give the rationale behind certain rules so that the reader understands the spirit of the rule.

# 3 HOST Conformance

Defining conformance and creating a method for verifying and certifying HOST products is vital to establishing an effective standard. Certification provides formal recognition of conformance to a HOST standard or specification. Without the associated conformance criteria and processes, there is no assurance that a supplier has developed or implemented products or solutions according to the approved HOST Technical Standards and Specifications. Verification provides evidence of conformance to a HOST Technical Standard or Specification, which allows:

- Buyers to specify and successfully procure hardware from vendors who provide solutions that conform to the HOST Specifications and Standards.

- System Integrators to make and substantiate clear claims of conformance to HOST Specifications and/or Standards.

- Hardware component suppliers to make and substantiate clear claims of conformance to HOST Specifications.

The government will establish conformance criteria and define an associated Conformance Program for the HOST Tier 3 Specifications and HOST Components.

The conformance assessment is intended to certify compliance with HOST requirements and is not intended to ensure a component or system will function as intended in its final application. Conformance assessment is not meant to assist with or replace developmental or operational test.

## 3.1 HOST Conformance Program

The HOST Conformance Program will have two primary functions:

- 1) Verification that a newly developed or revised Tier 3 Specification complies with the requirements of the applicable HOST Tier 2 Standard.

- 2) Verification that a hardware component complies with the requirements of the applicable HOST Tier 3 Specification.

## 3.1.1 HOST Conformance Program Terminology

**HOST Conformant** is used for an article an article if and only if the Tier 3 Specification and/or Module has completed the HOST Conformance Verification Process and been *HOST Gatekeeper* Approved. For a module, this entails demonstration of strict adherence to a *HOST Conformant Tier 3 Specification's* requirements. For a Tier 3 Specification, this requires proper documentation of the requirements levied on a module in accordance with the tenets of the Tier 3 Specification Guide.

**HOST Verification** is the act of determining the conformance of a HOST product to the applicable HOST technical standard or specification requirements. The applicable Tier 2 Standards and Tier 3 Specification will have associated matrices that recommend or specify a verification method for each rule. Verification will be carried out by the agency responsible for developing the HOST product being verified. Results and artifacts of the verification will be submitted to a *Verification Authority* (VA). The VA will review the verification results and artifacts to make a determination on whether the verification process was sufficiently correct and complete to show conformance to the next higher level specification or standard.

*HOST Registration* is the process of listing Certified HOST Tier 3 Specifications and Components in a public listing known as the *HOST Registry*.

## 3.1.2 Verification Methods

HOST Component requirements will be based on one of the following conformance methods: *Inspection*, *Analysis*, *Demonstration*, or *Test*.

## 3.1.3 HOST OpenVPX Verification Methods Document

The *HOST OpenVPX Verification Methods* (HOVM) document provides two different types of information in support of this Tier 2 standard. First, the HOVM identifies which Tier 2 rules pertain to HOST Modules and which rules pertain to other portions of the HOST system such as the Backplane or Enclosure. Second, the HOVM provides detailed verification method information required for Tier 3 module specifications that conform to the requirements of this document.

The HOVM contains a *Conformance Verification and Applicability Matrix (CVAM)*. The CVAM will include entries for all HOST Tier 2 requirements and identify, at a minimum, the following details for each Tier 2 rule: requirement ID, an indication of whether the rule pertains to a HOST Module or the HOST system, applicability to the specific types of components identified in the Tier 2 Standard, recommended verification method for the requirement, and additional information as necessary. The HOVM also defines the types of documentation that are required for verification of a Tier 3 Specification.

## 3.1.4 HOST Tier 3 Specification Conformance

Tier 3 Specifications will be verified to show conformance to this Tier 2 Standard. The agency authoring the Tier 3 Specification will perform and document a requirements trace to show that all applicable rules of this document have been flowed down to the Tier 3 Specification. In addition, a check will be made to verify that the Tier 3 Specification's *Requirements Verification Matrix* (RVM) covers all of the requirements identified in the Tier 3 Specification. The Tier 3 RVM will be checked to verify that it lists the appropriate verification methodology for each requirement per the CVAM contained in the HOVM. The submitting agency will provide the results of their verification efforts and supporting documentation to be reviewed by the VA. Upon successful completion of the HOST Tier 3 conformance process, the Tier 3 Specification will be published.

## 3.1.5 HOST Component Conformance

Components will be verified to show conformance to the applicable HOST Tier 3 Specification. Verification methods for component requirements will be identified in an RVM included in the Tier 3 Specification. The submitting agency will perform verification of the developed product to show conformance to the Tier 3 Specification. The submitting agency will provide the results of their verification efforts and supporting documentation to be reviewed by the VA. Upon successful completion of the HOST conformance process and review by the VA, the component data will be entered into the HOST Registry.

**T2-RUL-0005:** HOST Modules **shall** conform to one or more HOST Tier 3 Specifications.

**T2-RUL-0008:** Documentation for all Tests conducted, including environmental, to show conformance to HOST rules/requirements **shall** include, at a minimum, Test procedures, Test equipment information, collected Test data, and Test results.

**T2-OBS-0044:** Requiring documentation for tests conducted for conformance is in line with industry practices for compliance, for example ANSI/VITA 65.0, Rule 2.2.4-1.

**T2-PER-0001:** Non-Module HOST Components **may** conform to one or more HOST Tier 3 Specifications.

T2-RUL-0016: Level A Conformant Modules shall implement all applicable rules within this standard.

**T2-RUL-0017:** Level B Conformant Modules **shall** implement all rules except SECTION 5.3 Hardware System Management Rules.

**T2-OBS-0041:** The difference between a Level A and Level B Conformant Modules essentially comes down to whether the Module supports ANSI/VITA 46.11 based Hardware System Management, per SECTION 5.3 of this Standard. Level A Conformant Modules support all of the HOST System Management requirements, while Level B Conformant Modules do not. Note that *HOST Mezzanine Modules* are Level A by default due to not having any applicable rules in SECTION 5.3.

#### 3.1.6 Requirements Verification Matrix

The Tier 3 Specification will include an RVM. The purpose of the RVM is to identify the required verification method for each Tier 3 Specification requirement. The RVM will identify whether or not each Tier 3 requirement traces to a HOST Tier 2 Standard requirement. In addition, the RVM will include the required verification method, and an indication on whether each Tier 3 requirement was derived from this HOST Tier 2 Standard, the product specification, or both. For clarity, the RVM shall include entries for Tier 2 rules that are not applicable to the HOST component. These rules will be identified as not applicable.

**T2-RUL-0001:** A HOST Tier 3 Specification conforming to this standard **shall** include an RVM that includes one or more entries for each rule of this standard.

**T2-RUL-0002:** For each Tier 3 requirement, the Tier 3 RVM **shall** indicate whether the requirement was derived from a HOST Tier 2 rule, the product specification or both.

**T2-RUL-0018:** For each Tier 3 requirement that traces to one or more HOST Tier 2 rules, the Tier 3 RVM **shall** identify which Tier 2 rules trace to that Tier 3 requirement.

**T2-RUL-0019:** For each Tier 3 requirement, the Tier 3 RVM **shall** specify the required verification method.

**T2-RUL-0004:** For each Tier 2 rule applicable to the type of component specified in Tier 3, the Tier 3 Specification **shall** identify the required artifacts and any additional information required for verification.

**T2-RUL-0021:** For each Tier 2 rule that does not apply to the HOST component type specified by the Tier 3 as specified by the CVAM, the RVM **shall** contain an entry which identifies that Tier 2 rule as not applicable.

# 4 Implementation

The HOST OpenVPX Tier 2 Standard defines the technical requirements levied on an OpenVPX system so to govern a procedural conformance process for which this section further defines the HOST hardware components necessary in the implementation process with OpenVPX as a core technology. Throughout, the HOST Tier 2 standard will leverage ANSI/VITA 65.0 OpenVPX System Specifications and other embedded computing standards to structure the implementation process for which OpenVPX components align with HOST. This section also defines the HOST Architecture elements embodied within an OpenVPX System and relates those HOST elements to OpenVPX elements in a HOST framework. To conclude this section, there is a description of the resource implementation for standardizing the interfaces of the physical components of a system and their associated functions.

## 4.1 Hardware System Management

Hardware System Management within HOST establishes an autonomous subsystem that provides hardware management applications with supervisory capabilities to monitor, diagnose, and debug the hardware assemblies during system operations for abnormalities in the transporting or processing of data. The HOST Tier 2 Standard leverages ANSI/VITA 46.11 and IPMI standards to define the required data exchanges and Hardware System Management messages. Hardware System Management interfaces are well defined within this HOST Tier 2 standard and provide the following capabilities to HOST Modules:

- Sensor Management temperature, voltage, current, vibration

- System/Module Inventory vendor & revision identification, model number, serial number

- System/Module Configuration parameter and policy settings

- Software/Firmware Management load, clean, recover

- Field Replaceable Unit (FRU) Recovery power cycle or reset a hardware element

- Diagnostic Management initiate and collect diagnostic results

## 4.2 Hardware Implementation

This Tier 2 HOST Standard standardizes hardware components and their interfaces to facilitate interoperability between the components residing in an Enclosure.

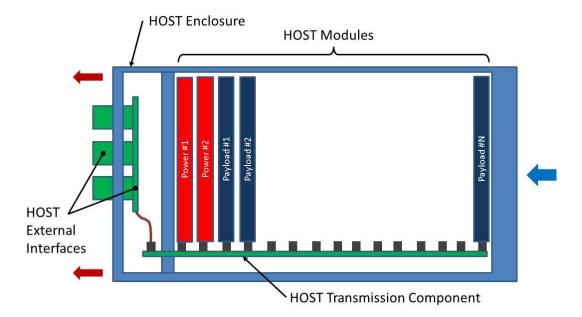

## 4.2.1 HOST Components

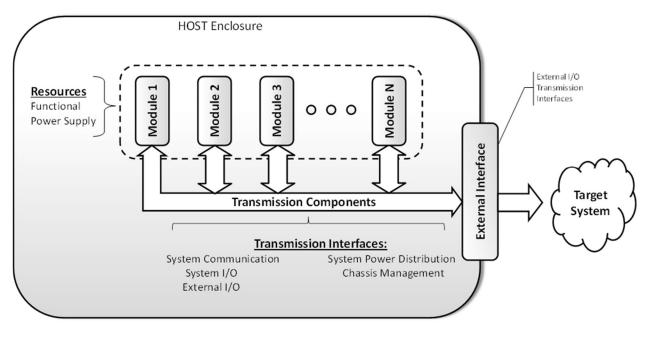

HOST Components are divided into four main categories: HOST Modules, HOST External Interfaces, HOST Transmission Components, and the HOST Enclosure.

## 4.2.1.1 HOST Modules

Within this HOST Tier 2 standard, HOST Modules are realized as *HOST Plug-In Modules* or as HOST Mezzanine Modules.

HOST Plug-In Modules are realized to ANSI/VITA 65.0 OpenVPX System Standard, ANSI/VITA 48.2 Conduction-cooled VPX Modules, or ANSI/VITA 62.0 Power Supplies throughout the HOST Tier 2 Standard. VPX Modules, as described in ANSI/VITA 65.0, include Payloads, External I/O Modules, Switches, and other miscellaneous Module types.

HOST Mezzanine Modules are realized to ANSI/VITA 42.0 Switched Mezzanine Cards (XMC), ANSI/VITA 42.3 XMC PCI Express Protocol Layer Standard or IEEE 1386.1 PCI Mezzanine Cards (PMC) here throughout for Mezzanine Cards.

## 4.2.1.2 HOST External Interface

HOST External Interfaces provide the physical connections between the HOST Transmission Components and external systems, which facilitates the signal and power transfer of the HOST OpenVPX system.

## 4.2.1.3 HOST Transmission Components

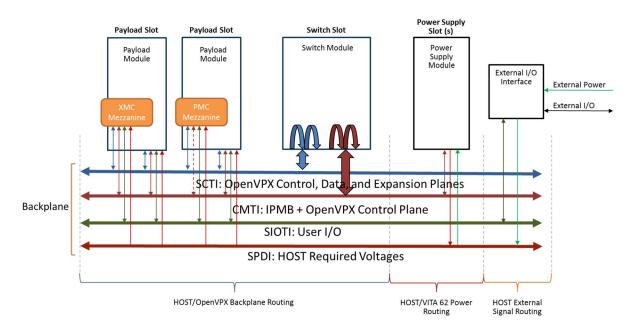

HOST Transmission Components facilitate the logical and physical connectivity between modules and external systems. The HOST Architecture establishes five Transmission Interfaces and each Transmission Interface, except for the *System I/O Transmission Interface* (SIOTI) and *External I/O Transmission Interface* (EIOTI), contain attributes of one or more planes defined in the ANSI/VITA 65.0 multi-plane architecture for OpenVPX as the core technology. This HOST OpenVPX Core Technology Tier 2 Standard has adopted those five transmission interfaces from the HOST Architecture, as defined in the HOST Tier 1 Standard. The transmission interfaces are as follow:

- System Communications Transmission Interface (SCTI)

- Chassis Management Transmission Interface (CMTI)

- System I/O Transmission Interface (SIOTI)

- External I/O Transmission Interface (EIOTI)

- System Power Distribution Interface (SPDI)

These Transmission Interfaces are introduced from a high-level architecture perspective within the HOST Tier 1 Standard and are further defined within the scope of OpenVPX as the core technology later in this Tier 2 Standard. It is important to understand that HOST Transmission Interfaces include a physical architecture construct of HOST Transmission Components which provide the interconnecting physical relationships between HOST Modules and the External Interfaces of the HOST Enclosure as shown in FIGURE 4-1 below.

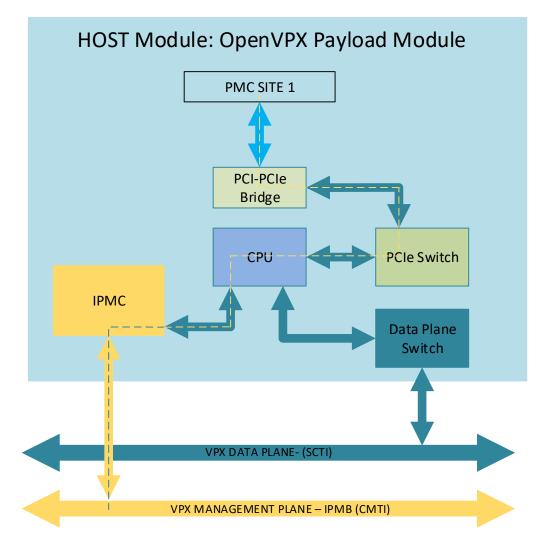

Figure 4-1 – HOST Component Categories

HOST Transmission Interfaces also facilitate the logical functions of Chassis Management, Power Supply, and *Functional Resources* (FR) between HOST Components as explained in Section 4.3, Resource Implementation.

## 4.2.1.4 HOST Enclosure

The HOST Enclosure is implemented utilizing ANSI/VITA 48.2 and ARINC Specification 404A 1-ATR Enclosure design elements.

## 4.3 **Resource Implementation**

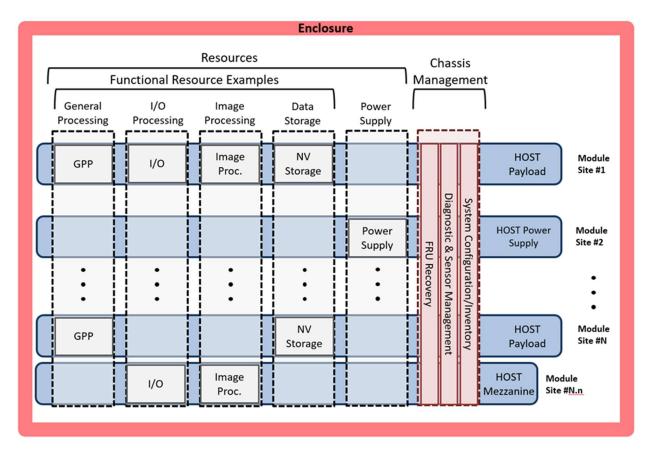

Resources primarily serve as the embedded computing building blocks in a system's logical architecture and provide the functional and power capabilities to a Target System. Resources with logical domain qualities such as processing and storage are characterized as Functional Resources, and the *Power Supply Resource* (PSR) provides a space for power subsystem standardization. Chassis Management is another attribute of the logical domain but is associated separately from Resources since Chassis Management is not a "system resource" but a framework for high-reliability hardware management. For clarity, HOST has defined *Functional Resource*, Power Supply Resource and *Chassis Management* as follows:

• Functional Resource – FRs perform the main functions of the system. Functions may include, but are not limited to, processing of the I/O, image processing, data processing, general purpose processing, data storage, etc. These resources differ from PSRs and Chassis Management in that those architectural elements exist to support the FRs.

• **Power Supply Resource** – PSRs transform a Platform's power into chassis power that is supplied to HOST Modules via the system power distribution segment. Modules that implement PSRs must support the Power Distribution Interface since that is the exclusive power distribution interface for HOST Modules.

• **Chassis Management** – Module-level hardware management with aggregate status and control provided at the chassis-level; extensible to systems-of-chassis management.

Although this Tier 2 HOST Standard is primarily based upon the use of ANSI/VITA 65.0 and OpenVPX as the core technology, this standard will further define requirements for OpenVPX modules and resources so they are HOST Tier 2 conformant. Therefore, a component that is OpenVPX conformant is not necessarily HOST conformant. Figure 4-2 shows an example of how different Functional Resources, Power Supply Resources and Chassis Management could be implemented on different HOST Modules.

Figure 4-2 – Resource Implementation Example

In Figure 4-2 the HOST Payload Module is based on an ANSI/VITA 65.0 Plug-In Module; the HOST Mezzanine, which is seated with the HOST Payload and thus indented in the figure, could be either a PMC or XMC module; and the HOST Power Supply is based on an ANSI/VITA 62.0 Power Supply Plug-In Module.

# 5 Tier 2 Standard Requirements

# 5.1 HOST Module Requirements

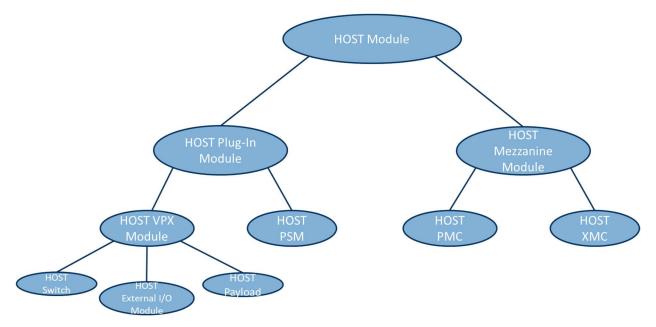

This HOST Tier 2 Core Technology Standard implements HOST Modules as 6U and 3U OpenVPX Plug-In Modules, ANSI/VITA 62.0 Power Supply Plug-In Modules, and PMC/XMC Mezzanine Modules. HOST Plug-In Modules consist of HOST VPX Modules and HOST *Power Supply Modules* (PSM) that connect (plug-in) directly to the *HOST Backplane* component. HOST Payload Modules are used to implement the *Functional Resources* (FR) and/or act as carriers of HOST Mezzanine Modules. HOST Switch Modules provide System Communications Transmission Interface (SCTI) interconnection between HOST Payload Modules. HOST External I/O Modules are used to interface with platform I/O and convert the I/O into standard protocols communicating with other VPX Modules throughout a system. HOST Power Supply Modules transform Platform power into system power for use by HOST VPX modules.

The hierarchy of rules for the various HOST Module types is shown in FIGURE 5-1.

Figure 5-1 – HOST Module Rules Hierarchy

The module hierarchy clarifies which rules each module type must follow. For example, a HOST Switch must follow any rules levied on HOST Switches, HOST VPX Modules, HOST Plug-In Modules, and HOST Modules, but a HOST Switch does not have to follow rules levied on HOST Payloads, HOST PSMs, or HOST Mezzanines Modules.

**T2-RUL-0010:** For this Tier 2 Core Technology Standard a HOST Module **shall** be defined as a VPX Module, Power Supply Module, PMC Mezzanine Module, or an XMC Mezzanine Module.

**T2-RUL-0011:** VPX Modules and Power Supply Modules **shall** conform to the requirements of HOST Plug-In Modules.

**T2-RUL-0012:** PMC and XMC Modules **shall** conform to the requirements of HOST Mezzanine Modules.

**T2-RUL-0020:** A HOST Module **shall** conform to interface requirements of the Chassis Management Transmission Interface (CMTI) per SECTION 5.4.1.5.

**T2-PER-0010:** A HOST Module **may** utilize the *System I/O Transmission Interface* (SIOTI) per SECTION 5.4.1.3.

**T2-RUL-0030:** A HOST Module **shall** conform to the interface requirements of the System Power Distribution Interface (SPDI) per SECTION 5.4.1.6.

**T2-RUL-0052:** HOST Modules **shall** leave signals HOST defines as reserved unconnected.

**T2-PER-0012:** A HOST Module **may** have only a subset of the SPDI voltages defined within the OpenVPX Utility Plane as an input.

**T2-RUL-0031:** If a HOST Module uses only a subset of the SPDI voltages defined within the OpenVPX Utility Plane as an input, the HOST Module **shall** leave the pins meant for the unused voltages as Reserved.

#### 5.1.1 HOST Plug-In Module Requirements

**T2-RUL-0121:** HOST Plug-In Module requirements **shall** be applied using the following order of precedence:

- 1. Requirements of SECTION 5.1.1.1 VPX Modules and SECTION 5.1.1.2 Power Supply Modules

- 2. Requirements of SECTION 5.1.1 HOST Plug-In Module Requirements

**T2-RUL-0053:** HOST Plug-In Modules **shall** follow ANSI/VITA 46.0ANSI/VITA 46.0ANSI/VITA 46.0, Rule 3-1 regarding safety ground.

**T2-RUL-0057:** HOST Plug-In Modules **shall** follow the rules of ANSI/VITA 46.0ANSI/VITA 46.0, Section 4.8.9 3.3V\_AUX.

**T2-RUL-0058:** HOST Plug-In Modules **shall** follow the rules of ANSI/VITA 46.0, Section 4.8.11 SYSRESET\*.

**T2-RUL-0059:** HOST Plug-In Modules **shall** draw no more than 1 mA from VBAT per Rule 4-56.1 of ANSI/VITA 46.0.

**T2-RUL-0061:** If implementing the 12V\_AUX +/-, HOST Plug-In Modules **shall** follow the rules of ANSI/VITA 46.0, Section 4.8.10 12V\_AUX.

## 5.1.1.1 VPX Modules

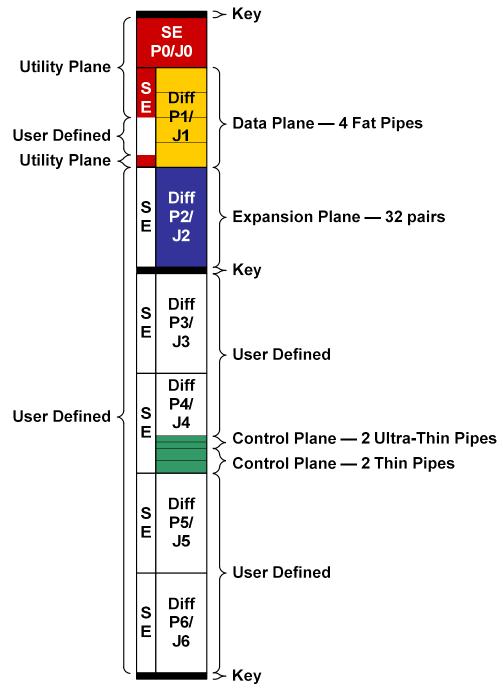

This Tier 2 Standard utilizes and refines the ANSI/VITA 46.0 and ANSI/VITA 65.0 standards to define the primary type of HOST Module for this Tier 2 technology. This Tier 2 HOST Standard leverages a set of the ANSI/VITA 65.0 (OpenVPX) *Slot Profiles* and *Module Profiles* for all HOST VPX Modules in addition to a few Slot Profiles that are defined for HOST-specific drivers. The Slot Profile maps OpenVPX ports to the HOST Backplane's connector interface. The Module Profile specifies which protocols are mapped to the ports defined in the Slot Profile.

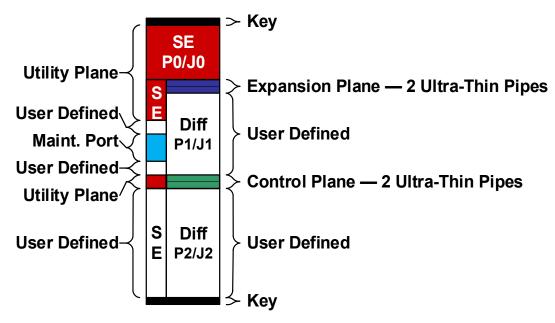

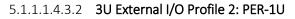

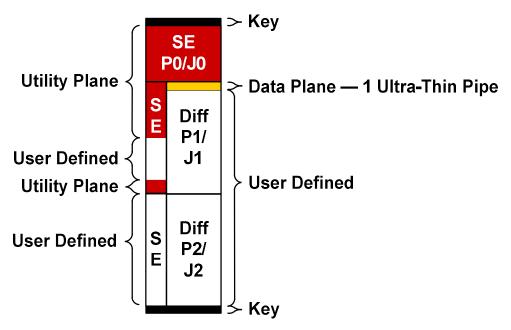

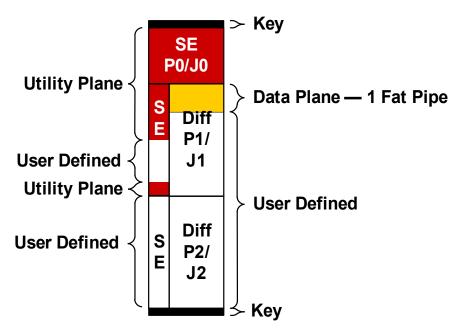

These Slot Profiles are also depicted graphically in ANSI/VITA 65.0 for ease of recognition, with the requirements referencing separate tables for the exact pinouts. The Slot Profile pictures from ANSI/VITA 65.0 are recreated here.

## 5.1.1.1.1 Common 6U and 3U VPX Module Requirements

**T2-RUL-0122:** VPX Module requirements **shall** be applied using the following order of precedence:

- 1. Requirements for a specific Module Form Factor and Profile Number, e.g. SECTION 5.1.1.1.2.3.1 3U Payload Profile 1: PAY-2F2U

- 2. Requirements for a specific Form Factor and Profile Type, e.g. SECTION 5.1.1.1.2.3 3U Payload Module Requirements

- 3. Requirements common to a Profile Type, e.g. SECTION 5.1.1.1.3.1 Common 6U and 3U HOST Switch Requirements

- 4. Requirements for a VPX Module in SECTION 5.1.1.1.1 Common 6U and 3U VPX Module Requirements

**T2-RUL-0531:** VPX Modules **shall** implement the requirements of ANSI/VITA 65.0, Section 3.7 (OpenVPX ANSI/VITA 46.0 Connector P0/J0 and P1/J1 Connector Pin Assignments).

**T2-RUL-0055:** VPX Modules **shall** be designed to accommodate any combination of power supply power up and power down sequences without causing board failure.

T2-RUL-0535: VPX Modules shall follow the rules of ANSI/VITA 46.0, Section 4.8.3 System Controller

**T2-RUL-0536**: VPX Modules **shall** follow the rules of ANSI/VITA 65.0, Section 3.4.1 System Controller.

**T2-RUL-0140:** VPX Modules **shall** conform to the applicable interface requirements of the SCTI per SECTION 5.4.1.2.

**T2-OBS-0100:** The OpenVPX Data Plane is part of the SCTI as defined in SECTION 5.4.1.2.

**T2-OBS-0101:** The OpenVPX Expansion Plane is part of the SCTI as defined in SECTION 5.4.1.2.

**T2-RUL-0240:** VPX Modules **shall** implement the requirements of ANSI/VITA 65.0, Section 6.3.3, (User Defined).

**T2-OBS-0150:** The OpenVPX User Defined connections are part of the SIOTI as defined in SECTION 5.4.1.3.

**T2-OBS-0120:** Reserved signals cannot be utilized for any other purpose (such as user I/O).

**T2-REC-0010:** When single-ended user defined signals that require tight tolerances, precise values, and/or very short rise times, are routed over pins intended for differential pairs, just the positive pin of a pair **should** be used for the signal, with the negative pin of the pair grounded. This is to prevent potential crosstalk of the single-ended user defined signals.

**T2-OBS-0080:** The SPDI supports the battery backup power rail per ANSI/VITA 65.0, Section 3.2.2 and ANSI/VITA 46.0, Section 4.9.2.

**T2-OBS-0081:** Refer to recommendations of ANSI/VITA 65.0, Section 3.2.4 on inrush (surge) current.

T2-PER-0061: VPX Modules may implement 10GBASE-KR on the UTPs.

**T2-RUL-0511:** VPX Modules using 10GBASE-KR **shall** comply with ANSI/VITA 65.0, Section 5.1.7.

**T2-PER-0072:** VPX Modules **may** implement 25GBASE-KR on the UTPs.

T2-RUL-0512: VPX Modules using 25GBASE-KR shall comply with ANSI/VITA 65.0, Section 5.1.15.

**T2-OBS-0019:** The OpenVPX Control Plane is part of both the SCTI and CMTI as defined in SECTION 5.4.1.2 and SECTION 5.4.1.5.

**T2-PER-0039:** VPX Modules **may** utilize a newer generation of *Peripheral Component Interconnect Express* (PCIe) than what is called out in the Module Profile.

## 5.1.1.1.2 Payload Modules

Payload Modules are primarily intended to provide hardware processing resources as well as I/O resources as necessary. Payload Modules provide a mixture of ports intended for the SCTI and SIOTI, with more defined high-speed ports than the External I/O Modules.

## 5.1.1.1.2.1 Common Payload Module with Mezzanine Site Requirements

**T2-RUL-0080:** Payload Modules with PMC mezzanine sites **shall** conform to the carrier board, referred to as a host board in IEEE 1386.1, requirements of IEEE 1386.1.

**T2-RUL-0090:** Payload Modules with XMC mezzanine sites **shall** conform to the carrier board requirements of ANSI/VITA 42.0, XMC.

**T2-OBS-0010:** Compatibility with the PMC/XMC communications protocols is defined by the SCTI in SECTION 5.4.1.2.

**T2-OBS-0020:** Compatibility with the PMC/XMC power interfaces is defined by the SPDI in SECTION 5.4.1.6.

**T2-OBS-0030:** It is possible for a single mezzanine site to be compatible with both XMC and PMC mezzanine formats.

**T2-OBS-0040:** Mezzanine connector pinout requirements for Payload Modules with PMC Mezzanine sites are specified by IEEE 1386.1 Section 5.2.

**T2-OBS-0050:** Voltage keying requirements for Payload Modules with PMC Mezzanine sites are specified by IEEE 1386.1 Section 4.2.

**T2-OBS-0060:** Mezzanine connector pinout requirements for Payload Modules with XMC Mezzanine sites are specified by ANSI/VITA 42.0 Section 5-1.

**T2-OBS-0070:** It is possible for Payload Modules to be mezzanine carriers that do not natively contain any resources. In those cases, the Payload Module might only contain the bridges required to attach the PMC/XMC modules to the SCTI and CMTI.

**T2-RUL-0100:** Payload Module mezzanine sites configured to support a XMC Mezzanine **shall** implement the secondary XMC connector ground pins in accordance with ANSI/VITA 42.0 Table 5-4, Secondary XMC Connector Pin Definition, even if the signals of the Secondary connector are not used.

## 5.1.1.1.2.2 6U Payload Module Requirements

**T2-RUL-0070:** 6U Payload Modules **shall** conform to the 6U conduction-cooled requirements of ANSI/VITA 48.2.

**T2-RUL-0051:** 6U Payload Modules **shall** follow ANSI/VITA 65.0, Section 12.1.2 with regards to Power Voltages and System Management.

**T2-OBS-0079:** Refer to ANSI/VITA 65.0, Recommendation 12.1.1.2-1 regarding maximum module power draw.

**T2-RUL-0251:** 6U Payload Modules **shall** conform to one of the 6U Payload Profiles as listed in SECTION 5.1.1.1.2.2.

5.1.1.1.2.2.1 6U Payload Profile 1: PAY-4F1Q2U2T

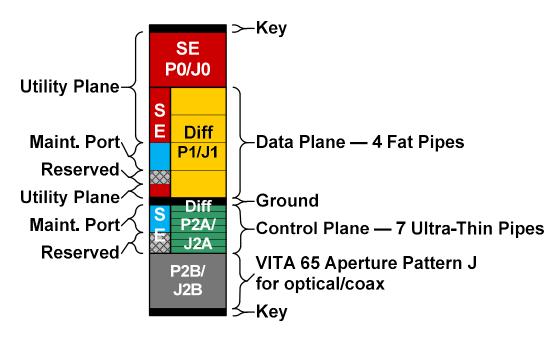

Figure 5-2 – Slot Profile SLT6-PAY-4F1Q2U2T-10.2.1

**T2-RUL-0249:** 6U Payload Profile 1 Modules **shall** conform to the Slot Profile SLT6-PAY-4F1Q2U2T-10.2.1 per ANSI/VITA 65.0, Section 10.2.1.

**T2-RUL-0200:** If a 6U Payload Profile 1 Module implements the Control Plane thin pipes, a Payload Module **shall** use the Control Plane thin pipes exclusively as part of the SIOTI.

T2-REC-0001: 6U Payload Profile 1 Modules should use the Control Plane thin pipes for debug.

**T2-RUL-0250:** 6U Payload Profile 1 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD6-PAY-4F1Q2U2T-12.2.1-8

- MOD6-PAY-4F1Q2U2T-12.2.1-14

- MOD6-PAY-4F1Q2U2T-12.2.1-15

- MOD6-PAY-4F1Q2U2T-12.2.1-19

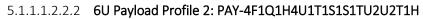

#### Figure 5-3 – Slot Profile SLT6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-10.6.3-n

**T2-RUL-0032:** 6U Payload Profile 2 Modules **shall** conform to the Slot Profiles SLT6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-10.6.3-n per ANSI/VITA 65.0, Section 10.6.3.

**T2-RUL-0101:** 6U Payload Profile 2 Modules **shall** conform to one of the following Slot Profiles per ANSI/VITA 65.1:

- SLT6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-10.6.3-0

- SLT6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-10.6.3-1

- SLT6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-10.6.3-2

**T2-RUL-0033:** If a 6U Payload Profile 2 Module implements the Control Plane thin pipes, a Payload Module **shall** use the Control Plane thin pipes exclusively as part of the SIOTI.

**T2-REC-0004:** 6U Payload Profile 2 Modules **should** use the Control Plane thin pipes for debug.

**T2-RUL-0034:** 6U Payload Profile 2 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-12.6.3-1

- MOD6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-12.6.3-2

- MOD6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-12.6.3-3

- MOD6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-12.6.3-4

- MOD6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-12.6.3-5

- MOD6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-12.6.3-6

- MOD6-PAY-4F1Q1H4U1T1S1S1TU2U2T1H-12.6.3-7

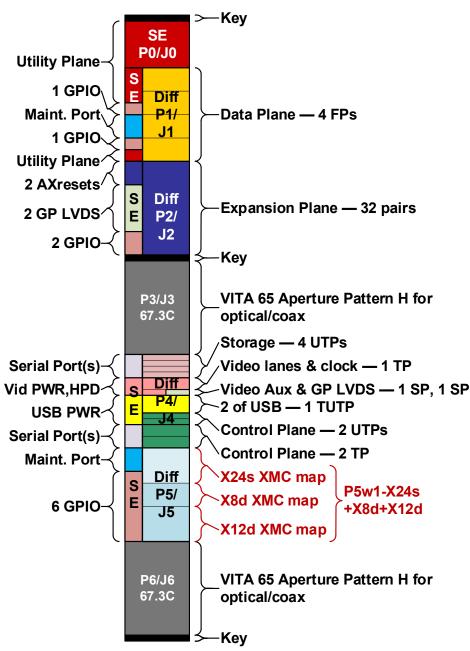

Figure 5-4 – Slot Profile SLT6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-10.6.4-n

**T2-RUL-0035:** 6U Payload Profile 3 Modules **shall** conform to the Slot Profiles SLT6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-10.6.4-n per ANSI/VITA 65.0, Section 10.6.4.

**T2-RUL-0102:** 6U Payload Profile 3 Modules **shall** conform to one of the following Slot Profiles per ANSI/VITA 65.1:

- SLT6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-10.6.4-0

- SLT6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-10.6.4-1

- SLT6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-10.6.4-2

**T2-RUL-0036:** If a 6U Payload Profile 3 Module implements the Control Plane thin pipes, a Payload Module **shall** use the Control Plane thin pipes exclusively as part of the SIOTI.

**T2-REC-0005:** 6U Payload Profile 3 Modules **should** use the Control Plane thin pipes for debug.

**T2-RUL-0037:** 6U Payload Profile 3 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-12.6.4-1

- MOD6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-12.6.4-2

- MOD6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-12.6.4-3

- MOD6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-12.6.4-4

- MOD6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-12.6.4-5

- MOD6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-12.6.4-6

- MOD6-PAY-4F2Q1H4U1T1S1S1TU2U2T1H-12.6.4-7

#### 5.1.1.1.2.2.4 **6U Payload Module with Mezzanine Site Requirements**

**T2-RUL-0110:** 6U Payload Module mezzanine sites configured to exclusively support a PMC Mezzanine **shall** conform to ANSI/VITA 46.9, Section 5.1 (P64S) regarding user defined pin mapping from the mezzanine site to the Payload Module Backplane connector.

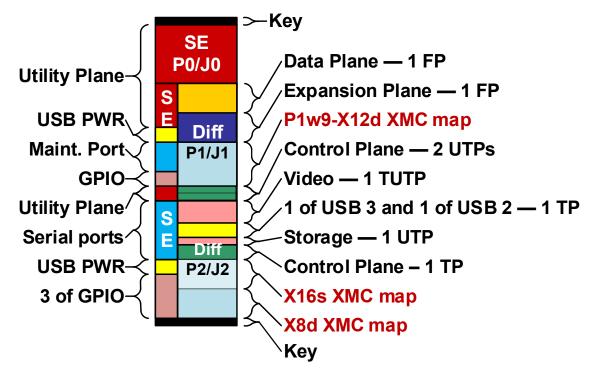

**T2-RUL-0120:** 6U Payload Module mezzanine sites configured to exclusively support a XMC Mezzanine **shall** conform to ANSI/VITA 46.9, Section 5.4 (X38S+X8D+X12D) regarding user defined pin mapping from the mezzanine site to the Payload Module Backplane connector.

**T2-RUL-0130:** 6U Payload Module mezzanine sites configured to support both PMC and XMC Mezzanines **shall** conform to ANSI/VITA 46.9, Section 5.2 (P64S+X12D) regarding user defined pin mapping from the mezzanine site to the Payload Module Backplane connector.

#### 5.1.1.1.2.3 **3U Payload Module Requirements**

**T2-RUL-0142:** 3U Payload Modules **shall** conform to the 3U conduction-cooled requirements of ANSI/VITA 48.2.

**T2-RUL-0141:** 3U Payload Modules **shall** follow ANSI/VITA 65.0, Section 16.1.2 with regards to Power Voltages and System Management.

**T2-OBS-0154:** Refer to ANSI/VITA 65.0, Recommendation 16.1.1.2-1 regarding maximum module power draw.

**T2-RUL-0159:** 3U Payload Modules **shall** conform to one of the 3U Payload Profiles as listed in SECTION 5.1.1.1.2.3.

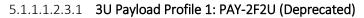

Figure 5-5 – Slot Profile SLT3-PAY-2F2U-14.2.3

This profile is marked as deprecated and will be removed in a future version of this standard. System designers are recommended to transition to one of the slot profiles without user-defined pins where possible. 3U Payload Profiles 3 and 4 are recommended for general-purpose computing resources or resources where RF or optical connections are required. 3U Payload Profiles 5 and 6 are recommended for general-purpose computing resources or where external I/O can be covered by commonly provided interfaces like USB, DisplayPort, etc. or can be addressed via a system-specific mezzanine site. As an alternative option, the 3U External I/O Modules can be used to gather the system-specific I/O to a single slot.

**T2-RUL-0160:** 3U Payload Profile 1 Modules **shall** conform to the Slot Profile SLT3-PAY-2F2U-14.2.3 per ANSI/VITA 65.0, Section 14.2.3.

**T2-RUL-0161:** 3U Payload Profile 1 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD3-PAY-2F2U-16.2.3-3

- MOD3-PAY-2F2U-16.2.3-5

- MOD3-PAY-2F2U-16.2.3-10

- MOD3-PAY-2F2U-16.2.3-11

**T2-PER-0050:** 3U Payload Profile 1 Modules utilizing Ethernet on the Data Plane **may** use 40GBase-KR4 Ethernet per ANSI/VITA 65.0, Section 5.1.8.

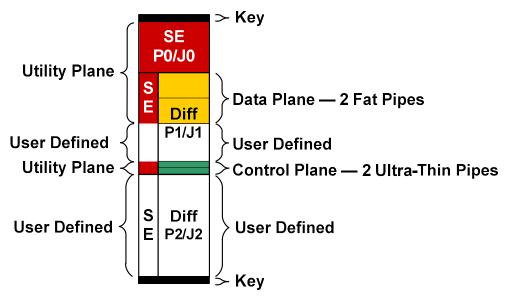

5.1.1.1.2.3.2 **3U Payload Profile 2: PAY-1F1F2U (Deprecated)**

Figure 5-6 – Slot Profile SLT3-PAY-1F1F2U-14.2.4

This profile is marked as deprecated and will be removed in a future version of this standard. Reference Section 5.1.1.1.2.3.1 for recommended replacement profiles for new designs.

**T2-RUL-0162:** 3U Payload Profile 2 Modules **shall** conform to the Slot Profile SLT3-PAY-1F1F2U-14.2.4 per ANSI/VITA 65.0, Section 14.2.4.

**T2-RUL-0163:** 3U Payload Profile 2 Modules **shall** conform to the following Module Profile per ANSI/VITA 65.1:

- MOD3-PAY-1F1F2U-16.2.4-8

**T2-PER-0055:** 3U Payload Profile 2 Modules utilizing Ethernet on the Data Plane **may** use 40GBase-KR4 Ethernet per ANSI/VITA 65.0, Section 5.1.8.

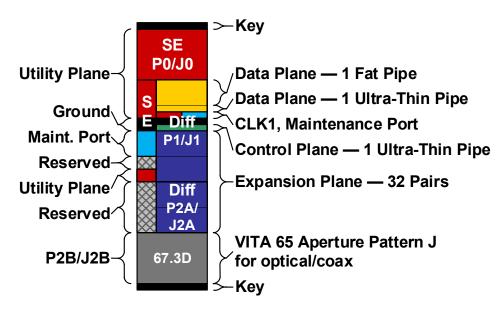

Figure 5-7 – Slot Profile SLT3-PAY-1F1U1S1S1U1U4F1J-14.6.13-n

**T2-RUL-0023:** 3U Payload Profile 3 Modules **shall** conform to the Slot Profiles SLT3-PAY-1F1U1S1S1U1U4F1J-14.6.13-n per ANSI/VITA 65.0, Section 14.6.13.

**T2-RUL-0103:** 3U Payload Profile 3 Modules **shall** conform to the following Slot Profile per ANSI/VITA 65.1:

- SLT3-PAY-1F1U1S1S1U1U4F1J-14.6.13-0

**T2-RUL-0024:** 3U Payload Profile 3 Modules **shall** conform to the following Module Profile per ANSI/VITA 65.1:

- MOD3-PAY-1F1U1S1S1U1U4F1J-16.6.13-1

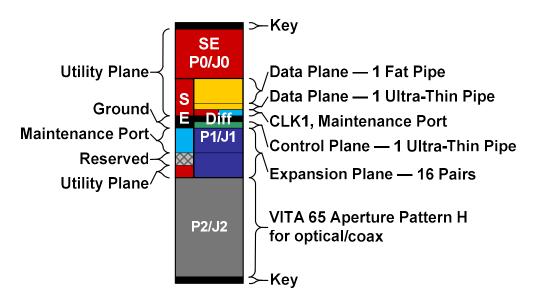

Figure 5-8 – Slot Profile SLT3-PAY-1F1U1S1S1U1U2F1H-14.6.11-n

**T2-RUL-0104:** 3U Payload Profile 4 Modules **shall** conform to the Slot Profiles SLT3-PAY-1F1U1S1S1U1U2F1H-14.6.11-n per ANSI/VITA 65.0, Section 14.6.11.

**T2-RUL-0042:** 3U Payload Profile 4 Modules **shall** conform to one of the following Slot Profiles per ANSI/VITA 65.1:

- SLT3-PAY-1F1U1S1S1U1U2F1H-14.6.11-0

- SLT3-PAY-1F1U1S1S1U1U2F1H-14.6.11-1

- SLT3-PAY-1F1U1S1S1U1U2F1H-14.6.11-2

- SLT3-PAY-1F1U1S1S1U1U2F1H-14.6.11-4

**T2-RUL-0043:** 3U Payload Profile 4 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-1

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-2

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-3

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-4

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-5

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-6

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-9

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-10

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-11

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-12

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-13

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-14

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-15

- MOD3-PAY-1F1U1S1S1U1U2F1H-16.6.11-16

Figure 5-9 – Slot Profile SLT3-PAY-1F1F2U1TU1T1U1T-14.2.16

**T2-RUL-0068:** 3U Payload Profile 5 Modules **shall** conform to the Slot Profile SLT3-PAY-1F1F2U1TU1T1U1T-14.2.16 per ANSI/VITA 65.0, Section 14.2.16.

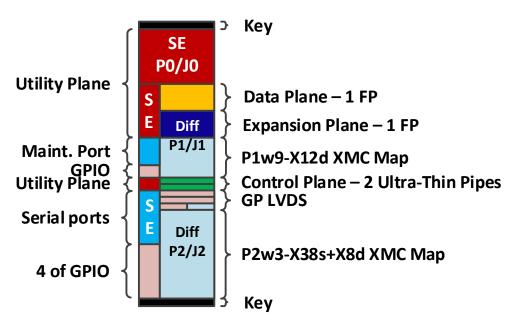

**T2-RUL-0075:** 3U Payload Profile 5 Modules **shall** conform to ANSI/VITA 46.9 XMC mapping P1w9-X12d+P2w9-X16s+X8d.

**T2-RUL-0069:** 3U Payload Profile 5 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD3-PAY-1F1F2U1TU1T1U1T-16.2.15-1

- MOD3-PAY-1F1F2U1TU1T1U1T-16.2.15-2

- MOD3-PAY-1F1F2U1TU1T1U1T-16.2.15-3

- MOD3-PAY-1F1F2U1TU1T1U1T-16.2.15-4

## 5.1.1.1.2.3.6 **3U Payload Profile 6: PAY-1F1F2U5S-HOST**

Figure 5-10 – Slot Profile PAY-1F1F2U5S-HOST

**T2-RUL-4000:** The Utility Plane pins on PO/JO **shall** be implemented as described in Table 3.7-1 and Table 3.7-2 of ANSI/VITA 65.0.

**T2-RUL-4001:** The single-ended Utility Plane pins on P1/J1 **shall** be implemented as described in Table 3.7-3 and Table 3.7-4 of ANSI/VITA 65.0.

**T2-RUL-4002:** There **shall** be pins allocated for one Maintenance Port on P1/J1, MP01, as given in TABLE 5-1 of this document, with usage complying with ANSI/VITA 65.0, Section 5.13.

**T2-RUL-4003:** There **shall** be a pin allocated for GPIO on P1/J1, GPIO1, as given in TABLE 5-1 of this document, with usage complying with ANSI/VITA 65.0, Section 5.15.1.

**T2-RUL-4004:** The Data Plane pins on P1/J1 **shall** be implemented as described in TABLE 5-1 of this document, with usage complying with ANSI/VITA 65.0, Section 6.2.2.

**T2-RUL-4005:** The Expansion Plane pins on P1/J1 **shall** be implemented as described in TABLE 5-1 of this document, with usage complying with ANSI/VITA 65.0, Section 6.2.2.

**T2-RUL-4006:** The Control Plane pins on P1/J1 **shall** be implemented as described in TABLE 5-1 of this document, with usage complying with ANSI/VITA 65.0, Section 6.2.2.

**T2-RUL-4007:** There **shall** be pins allocated for Serial Port on P2/J2, SER01, as given in TABLE 5-2 of this document, with usage complying with ANSI/VITA 65.0, Section 5.13.

**T2-RUL-4008:** There **shall** be pins allocated for an XMC mapping P1w9-X12d+P2w3-X38s+X8d as given in TABLE 5-1 and TABLE 5-2 of this document, with usage complying with ANSI/VITA 46.9, Section 4.6.

**T2-RUL-4009:** There **shall** be pins allocated for GPIO on P2/J2, GPIO2-GPIO5, as given in TABLE 5-2 of this document, with usage complying with ANSI/VITA 65.0, Section 5.15.1.

**T2-RUL-4010:** There **shall** be pins allocated for GPLVDS on P2/J2, as given in TABLE 5-2 of this document, with usage complying with ANSI/VITA 65.0, Section 5.15.2.

**T2-RUL-4011:** 3U Payload Profile 6 Modules **shall** conform to one of the following Module Profiles listed in TABLE 5-3.

| Plug-in<br>module P1 |                  | Row G        | Row F      | Row E<br>Even Odd  |                 | Row D           | Row C           | Row B<br>Even Odd |                 | Row A           |                 |                 |           |           |        |

|----------------------|------------------|--------------|------------|--------------------|-----------------|-----------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-----------|-----------|--------|

| Bplane J1            |                  | Row i        | Row h      | Row g              | Row f           | Row e           | Row d           | Row c             | Row b           | Row a           |                 |                 |           |           |        |

| 1                    |                  | 7            | GDiscrete1 | GND                | GND-J1          | DP01-TD0-       | DP01-TD0+       | GND               | GND-J1          | DP01-RD0-       | DP01-RD0+       |                 |           |           |        |

| 2                    | Port 1           |              | 2 / 4x1    | GND                | DP01-TD1-       | DP01-TD1+       | GND-J1          | GND               | DP01-RD1-       | DP01-RD1+       | GND-J1          | GND             |           |           |        |

| 3                    | DP Po            |              | x4/        | x4/2x2             | / 2x2           | P1-VBAT         | GND             | GND-J1            | DP01-TD2-       | DP01-TD2+       | GND             | GND-J1          | DP01-RD2- | DP01-RD2+ |        |

| 4                    |                  | _            |            |                    | GND             | DP01-TD3-       | DP01-TD3+       | GND-J1            | GND             | DP01-RD3-       | DP01-RD3+       | GND-J1          | GND       |           |        |

| 5                    |                  | X            | T.         | SYS_CON*           | GND             | GND-J1          | EP01-TD0-       | EP01-TD0+         | GND             | GND-J1          | EP01-RD0-       | EP01-RD0+       |           |           |        |

| 6                    | Port 1           |              | 2 / 4x     | GND                | EP01-TD1-       | EP01-TD1+       | GND-J1          | GND               | EP01-RD1-       | EP01-RD1+       | GND-J1          | GND             |           |           |        |

| 7                    | EP P             |              | / 2X       | Reserved           | GND             | GND-J1          | EP01-TD2-       | EP01-TD2+         | GND             | GND-J1          | EP01-RD2-       | EP01-RD2+       |           |           |        |

| 8                    |                  |              | х4         | GND                | EP01-TD3-       | EP01-TD3+       | GND-J1          | GND               | EP01-RD3-       | EP01-RD3+       | GND-J1          | GND             |           |           |        |

| 9                    |                  |              | lap        |                    |                 |                 | MP01-TD         | GND               | GND-J1          | Jn6-A5          | Jn6-B5          | GND             | GND-J1    | Jn6-D5    | Jn6-E5 |

| 10                   |                  | X12d XMC Map |            |                    | GND             | Jn6-A7          | Jn6-B7          | GND-J1            | GND             | Jn6-D7          | Jn6-E7          | GND-J1          | GND       |           |        |

| 11                   |                  |              |            | MP01-RD            | GND             | GND-J1          | Jn6-A9          | Jn6-B9            | GND             | GND-J1          | Jn6-D9          | Jn6-E9          |           |           |        |

| 12                   |                  |              |            | GND                | Jn6-A15         | Jn6-B15         | GND-J1          | GND               | Jn6-D15         | Jn6-E15         | GND-J1          | GND             |           |           |        |

| 13                   |                  | X12          |            | GPIO1              | GND             | GND-J1          | Jn6-A17         | Jn6-B17           | GND             | GND-J1          | Jn6-D17         | Jn6-E17         |           |           |        |

| 14                   |                  |              |            | GND                | Jn6-A19         | Jn6-B19         | GND-J1          | GND               | Jn6-D19         | Jn6-E19         | GND-J1          | GND             |           |           |        |

| 15                   |                  | trol<br>ne   |            | Maskable<br>Reset* | GND             | GND-J1          | CPutp02-<br>TD- | CPutp02-<br>TD+   | GND             | GND-J1          | CPutp02-<br>RD- | CPutp02-<br>RD+ |           |           |        |

| 16                   | Control<br>Plane |              |            | GND                | CPutp01-<br>TD- | CPutp01-<br>TD+ | GND-J1          | GND               | CPutp01-<br>RD- | CPutp01-<br>RD+ | GND-J1          | GND             |           |           |        |

Table 5-1 P1/J1 Pin Mapping for PAY-1F1F2U5S-HOST

| Plug-In   |             | Row G         | Row F     | Row E     |           | Row D Row C |           | Row B     |           | Row A     |

|-----------|-------------|---------------|-----------|-----------|-----------|-------------|-----------|-----------|-----------|-----------|

| Mod P2    |             |               |           | Even      | Odd       |             |           | Even      | Odd       |           |

| Bplane J2 |             | Row i         | Row h     | Row g     | Row f     | Row e       | Row d     | Row c     | Row b     | Row a     |

| 1         | SC          | SER01-<br>TX- | GND       | GND-J2    | GPIvds01- | GPlvds01+   | GND       | GND-J2    | GPIvds02- | GPIvds02+ |

| 2         | o LVDS      | GND           | GPIvds03- | GPIvds03+ | GND-J2    | GND         | GPIvds04- | GPlvds04+ | GND-J2    | GND       |

| 3         | GP          | SER01-<br>TX+ | GND       | GND-J2    | GPIvds05- | GPlvds05+   | GND       | GND-J2    | Jn6-C1    | Jn6-F1    |

| 4         |             | GND           | Jn6-C2    | Jn6-C3    | GND-J2    | GND         | Jn6-F2    | Jn6-F3    | GND-J2    | GND       |

| 5         |             | SER01-<br>RX- | GND       | GND-J2    | Jn6-C4    | Jn6-C5      | GND       | GND-J2    | Jn6-F4    | Jn6-F5    |

| 6         | _           | GND           | Jn6-C6    | Jn6-C7    | GND-J2    | GND         | Jn6-F6    | Jn6-F7    | GND-J2    | GND       |

| 7         | IC map      | SER01-<br>RX+ | GND       | GND-J2    | Jn6-C8    | Jn6-C9      | GND       | GND-J2    | Jn6-F8    | Jn6-F9    |

| 8         | X38s XMC    | GND           | Jn6-C10   | Jn6-C11   | GND-J2    | GND         | Jn6-F10   | Jn6-F11   | GND-J2    | GND       |

| 9         | X38         | GPIO2         | GND       | GND-J2    | Jn6-C12   | Jn6-C13     | GND       | GND-J2    | Jn6-F12   | Jn6-F13   |

| 10        |             | GND           | Jn6-C14   | Jn6-C15   | GND-J2    | GND         | Jn6-F14   | Jn6-F15   | GND-J2    | GND       |

| 11        |             | GPIO3         | GND       | GND-J2    | Jn6-C16   | Jn6-C17     | GND       | GND-J2    | Jn6-F16   | Jn6-F17   |

| 12        |             | GND           | Jn6-C18   | Jn6-C19   | GND-J2    | GND         | Jn6-F18   | Jn6-F19   | GND-J2    | GND       |

| 13        | ap          | GPIO4         | GND       | GND-J2    | Jn6-A1    | Jn6-B1      | GND       | GND-J2    | Jn6-D1    | Jn6-E1    |

| 14        | ŭ<br>C      | GND           | Jn6-A3    | Jn6-B3    | GND-J2    | GND         | Jn6-D3    | Jn6-E3    | GND-J2    | GND       |

| 15        | X8d XMC map | GPIO5         | GND       | GND-J2    | Jn6-A11   | Jn6-B11     | GND       | GND-J2    | Jn6-D11   | Jn6-E11   |

| 16        | X8          | GND           | Jn6-A13   | Jn6-B13   | GND-J2    | GND         | Jn6-D13   | Jn6-E13   | GND-J2    | GND       |

Table 5-2 P2/J2 Pin Mapping for PAY-1F1F2U5S-HOST

| Module Profile           | Protocols for Copper Planes |                  |                   | Miscellaneous         |

|--------------------------|-----------------------------|------------------|-------------------|-----------------------|

|                          | Data Plane                  | Expansion Plane  | Control Plane     | Protocols over copper |

| MOD3-PAY-1F1F2U5S-HOST   | DP01                        | EP01             | CPutp01,CPutp02   |                       |

|                          |                             |                  |                   |                       |

|                          | PCIe Gen 2 - per            | PCle Gen 2 - per | 1000BASE-KX - per |                       |

|                          | ANSI/VITA 65.0,             | ANSI/VITA 65.0,  | ANSI/VITA 65.0,   |                       |

|                          | Section 5.3.3.2             | Section 5.3.3.2  | Section 5.1.2     |                       |

| MOD3-PAY-1F1F2U5S-HOST-1 |                             |                  |                   |                       |

|                          |                             |                  |                   |                       |

|                          | 10GBASE-KX4 - per           | PCle Gen 2 - per | 1000BASE-KX - per |                       |

|                          | ANSI/VITA 65.0,             | ANSI/VITA 65.0,  | ANSI/VITA 65.0,   |                       |

|                          | Section 5.1.5               | Section 5.3.3.2  | Section 5.1.2     |                       |

| MOD3-PAY-1F1F2U5S-HOST-2 |                             |                  |                   |                       |

|                          |                             |                  |                   |                       |

|                          | PCIe Gen 3 - per            | PCle Gen 3 - per | 10GBase-KR - per  |                       |

|                          | ANSI/VITA 65.0,             | ANSI/VITA 65.0,  | ANSI/VITA 65.0,   |                       |

|                          | Section 5.3.3.3             | Section 5.3.3.3  | Section 5.1.7     |                       |

| MOD3-PAY-1F1F2U5S-HOST-3 |                             |                  |                   |                       |

|                          |                             |                  |                   |                       |

|                          | 40GBase-KR4 - per           | PCle Gen 3 - per | 10GBase-KR - per  |                       |

|                          | ANSI/VITA Section           | ANSI/VITA 65.0,  | ANSI/VITA 65.0,   |                       |

|                          | 5.1.8                       | Section 5.3.3.3  | Section 5.1.7     |                       |

| MOD3-PAY-1F1F2U5S-HOST-4 |                             |                  |                   |                       |

| Table 5-3 Module Profiles for | PAY-1F1F2U5S-HOST |

|-------------------------------|-------------------|

|-------------------------------|-------------------|

# 5.1.1.1.2.3.7 **3U Payload Module with Mezzanine Site Requirements**

**T2-RUL-0148:** 3U Payload Module mezzanine sites configured to exclusively support a PMC Mezzanine shall conform to ANSI/VITA 46.9, Section 4.1 (P64S) regarding user defined pin mapping from the mezzanine site to the Payload Module Backplane connector.

**T2-RUL-0149:** 3U Payload Module mezzanine sites configured to exclusively support a XMC Mezzanine **shall** conform to one of the following options regarding user defined pin mapping from the mezzanine site to the Payload Module Backplane connector if not defined by the payload profile:

- 1. ANSI/VITA 46.9, Section 4.3, X8D+X12D.

- 2. ANSI/VITA 46.9, Section 4.4, X24S+X8D+X12D.

- 3. ANSI/VITA 46.9, Section 4.6, X12D+X38S+X8D.

- 4. ANSI/VITA 46.9, Section 4.8, X12D.

**T2-RUL-0151:** 3U Payload Module mezzanine sites configured to support both PMC and XMC Mezzanines **shall** conform to ANSI/VITA 46.9, Section 4.2 (X12D+P64S) regarding user defined pin mapping from the mezzanine site to the Payload Module Backplane connector.

5.1.1.1.2.3.8 **3U HOST Payload Profile 1 using ANSI/VITA 66.0 or ANSI/VITA 66.0 Connectors Requirements** (Deprecated)

**T2-PER-0054:** 3U Payload Profile 1 Modules **may** replace the P2 connector with a blind mate connector compliant to ANSI/VITA 66.0 or ANSI/VITA 67.0 and their related dot standard.

**T2-RUL-0152:** If following T2-PER-0054, 3U Payload Modules **shall** conform to the Slot Profiles SLT3-PAY-2F2U1J-14.6.9-n per ANSI/VITA 65.1, Section 14.6.9.

**T2-OBS-0147:** For 3U Payload Profile 1 Modules with apertures HOST only defines the aperture type and location and not the specific connector. The J aperture takes ANSI/VITA 67.3 type D connector modules.

5.1.1.1.2.4 3U Radial Clock Payload Module Requirements

5.1.1.1.2.4.1 **3U Radial Clock Payload Profile 1: TIM-2S1U22S1U2U1H**

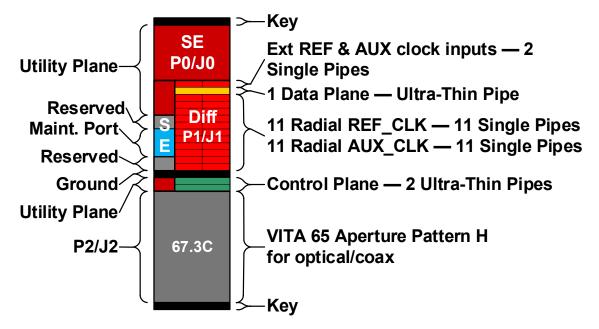

Figure 5-11 – Slot Profile SLT3x-TIM-2S1U22S1U2U1H-14.9.2-n

**T2-RUL-0038:** 3U Radial Clock Payload Profile 1 Modules **shall** conform to the Slot Profiles SLT3x-TIM-2S1U22S1U2U1H-14.9.2-n per ANSI/VITA 65.0, Section 14.9.2.

**T2-RUL-0105:** 3U Radial Clock Payload Profile 1 Modules **shall** conform to one of the following Slot Profiles per ANSI/VITA 65.1:

- SLT3x-TIM-2S1U22S1U2U1H-14.9.2-0

- SLT3x-TIM-2S1U22S1U2U1H-14.9.2-1

**T2-RUL-0039:** 3U Radial Clock Payload Profile 1 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD3p-TIM-2S1U22S1U2U1H-16.9.2-1

- MOD3p-TIM-2S1U22S1U2U1H-16.9.2-2

**T2-RUL-0123:** 3U Radial Clock Payload Profile 1 Modules **shall** draw no more than 2.2 A from VBAT, per ANSI/VITA 65.0, Section 14.9.1.1.2.

**T2-REC-0006:** For requirements common to all Slot Profiles using VITA 66 and/or VITA 67 connectors, Designers **should** see ANSI/VITA 65.0, Section 6.4.4.

**T2-RUL-0041:** The P2/J2 location of this Slot Profile **shall** either be loaded with a VITA 67.3 type C Connector Module, any other Connector Module which fits in an Aperture Pattern H location, or left empty.

## 5.1.1.1.3 Switch Modules

When using multiple VPX Modules, it is often necessary to utilize a Switch Module to accomplish the necessary communication.

## 5.1.1.1.3.1 Common 6U and 3U HOST Switch Requirements

**T2-PER-0062:** Switch Modules **may** combine Control Plane ultra-thin pipes to create Control Plane fat pipes.

**T2-OBS-0237:** It might be necessary to combine 4 10GBASE-KR ultra-thin pipes to create a single 40GBASE-KR4 fat pipe.

**T2-RUL-0513:** When combining ultra-thin pipes to create a 40GBASE-KR4 fat pipe, a Switch Module **shall** comply with ANSI/VITA 65.0, Section 5.1.8.

**T2-RUL-0514:** When combining ultra-thin pipes to create a 100GBASE-KR4 fat pipe, a Switch Module **shall** comply with ANSI/VITA 65.0, Section 5.1.18.

#### 5.1.1.1.3.2 **6U Switch Module Requirements**

**T2-RUL-0520:** 6U Switch Modules **shall** be implemented as 6U OpenVPX Switch Plug-In Modules per SECTION 5.4.2.3.

**T2-REC-0018**: In order to allow their use in a Standard Development Chassis, 6U conduction-cooled Switch Modules **should** be designed to require ≤150W per slot.

**T2-PER-0034**: 6U conduction-cooled Switch Modules **may** be designed to require >150W per slot, but these modules might not be properly powered in a Standard Development Chassis.

**T2-RUL-0533:** 6U Switch Modules **shall** follow ANSI/VITA 65.0, Section 12.1.2 with regard to Power Voltages and System Management.

**T2-RUL-0532:** 6U Switch Modules **shall** conform to one of the 6U Switch Profiles as listed in SECTION 5.1.1.1.3.2.

**T2-RUL-0537:** 6U Switch Modules **shall** conform to the 6U conduction-cooled requirements of ANSI/VITA 48.2.

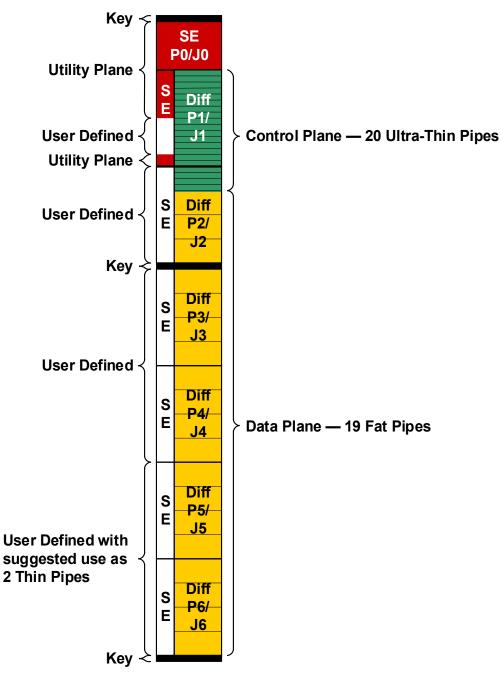

5.1.1.1.3.2.1 **6U Switch Profile 1: SWH-20U19F**

**T2-RUL-0540:** 6U Switch Profile 1 Modules **shall** conform to the Slot Profile SLT6-SWH-20U19F-10.4.1 per ANSI/VITA 65.0, Section 10.4.1.

**T2-RUL-0550:** 6U Switch Profile 1 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD6-SWH-20U19F-12.4.1-3

- MOD6-SWH-20U19F-12.4.1-5

- MOD6-SWH-20U19F-12.4.1-10

- MOD6-SWH-20U19F-12.4.1-15

**T2-OBS-0238:** Note that the MOD6-SWH-20U19F-12.4.1-3 switch has PCIe in the Data Plane, but this is the profile that would be used in a system that wants to utilize HOST Payload's PCIe Expansion Plane as a switched network. Due to the Expansion Plane being primarily used for adjunct modules, the OpenVPX ecosystem does not contain Expansion Plane Switch Modules.

5.1.1.1.3.2.2 **6U Switch Profile 2: SWH-16U20F**

**T2-RUL-0560:** 6U Switch Profile 2 Modules **shall** conform to the Slot Profile SLT6-SWH-16U20F-10.4.2 per ANSI/VITA 65.0, Section 10.4.2.

**T2-RUL-0570:** 6U Switch Profile 2 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD6-SWH-16U20F-12.4.2-3

- MOD6-SWH-16U20F-12.4.2-5

- MOD6-SWH-16U20F-12.4.2-11

- MOD6-SWH-16U20F-12.4.2-15

**T2-OBS-0239:** Note that the MOD6-SWH-16U20F-12.4.2-3 switch has PCIe in the Data Plane. This is the profile that would be used in a system that wants to utilize HOST Payload's PCIe Expansion Plane as a switched network. Due to the Expansion Plane being primarily used for adjunct Modules, the OpenVPX ecosystem does not contain Expansion Plane Switch Modules.

#### 5.1.1.1.3.2.3 6U Switch Profile 3: SWH-14F16U1U15U1J

Figure 5-14 – Slot Profile SLT6-SWH-14F16U1U15U1J-10.8.1

**T2-RUL-0106:** 6U Switch Profiles 3 Modules **shall** conform to the Slot Profiles SLT6-SWH-14F16U1U15U1J-10.8.1-n per ANSI/VITA 65.0, Section 10.8.1.

T2-RUL-0025: 6U Switch Profile 3 Modules shall conform to the following Slot Profiles per ANSI/VITA 65.1:

- SLT6-SWH-14F16U1U15U1J-10.8.1-0

**T2-RUL-0026:** 6U Switch Profile 3 Modules **shall** conform to the following Module Profiles per ANSI/VITA 65.1:

- MOD6-SWH-14F16U1U15U1J-12.8.1-1

- MOD6-SWH-14F16U1U15U1J-12.8.1-2

5.1.1.1.3.3 3U Switch Module Requirements

**T2-RUL-0568:** 3U Switch Modules **shall** be implemented as 3U OpenVPX Switch Plug-In Modules per SECTION 5.4.2.3.

**T2-REC-0019**: In order to allow their use in a Standard Development Chassis, 3U conduction-cooled Switch Modules **should** be designed to require ≤75W per slot.

**T2-PER-0035**: 3U conduction-cooled Switch Modules **may** be designed to require >75W per slot, but these modules might not be properly powered in a Standard Development Chassis.

**T2-RUL-0571:** 3U Switch Modules **shall** follow ANSI/VITA 65.0, Section 16.1.2 with regard to Power Voltages and System Management.

**T2-RUL-0572:** 3U Switch Modules **shall** conform to one of the 3U Switch Profiles as listed in SECTION 5.1.1.1.3.3.

**T2-RUL-0587:** 3U Switch Modules **shall** conform to the 3U conduction-cooled requirements of ANSI/VITA 48.2.

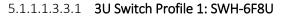

Figure 5-15 – Slot Profile SLT3-SWH-6F8U-14.4.15

**T2-RUL-0573:** 3U Switch Profile 1 Modules **shall** conform to the Slot Profile SLT3-SWH-6F8U-14.4.15 per ANSI/VITA 65.0, Section 14.4.15.

**T2-RUL-0045:** If a 3U Switch Profile 1 Module implements the Control Plane thin pipe, a Switch Module **shall** use the Control Plane thin pipe exclusively as part of the SIOTI.

**T2-RUL-0575:** 3U Switch Profile 1 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD3-SWH-6F8U-16.4.16-1

- MOD3-SWH-6F8U-16.4.16-2

5.1.1.1.3.3.2 3U Switch Profile 2: SWH-2F24U

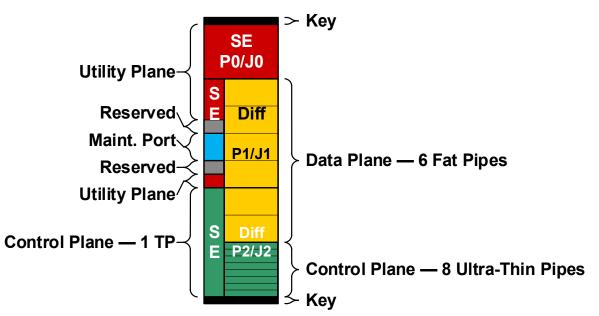

Figure 5-16 – Slot Profile SLT3-SWH-2F24U-14.4.3

**T2-RUL-0576:** 3U Switch Profile 2 Modules **shall** conform to the Slot Profile SLT3-SWH-2F24U-14.4.3 per ANSI/VITA 65.0, Section 14.4.3.

**T2-PER-0101:** If an application requires more than 24 Ultra-Thin Pipes the P1 Fat Pipes of 3U Switch Profile 2 **may** be repartitioned into Ultra-Thin Pipes.

**T2-RUL-0591:** If only one of the two available Fat Pipes on P1 of the 3U Switch Profile 2 is repartitioned it **shall** be the Fat Pipe closer to P2.

**T2-PER-0021:** If more than 2 Fat-Pipes are needed, the UTPs, CPutp01 thru CPutp24, **may** be repartitioned into Fat Pipes.

**T2-RUL-0581:** 3U Switch Profile 2 Modules **shall** conform to MOD3-SWH-2F24U-16.4.3-4 per ANSI/VITA 65.1.

5.1.1.1.3.3.3 **3U Switch Profile 3: SWH-6F1U7U**

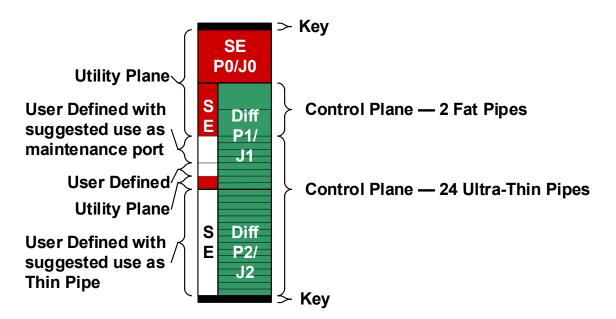

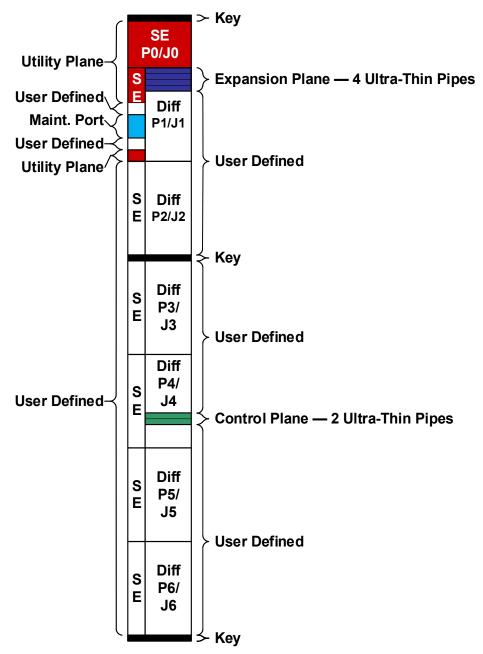

Figure 5-17 – Slot Profile SLT3-SWH-6F1U7U-14.4.14

**T2-RUL-0081:** 3U Switch Profile 3 Modules **shall** conform to the Slot Profile SLT3-SWH-6F1U7U-14.4.14 per ANSI/VITA 65.0, Section 14.4.14.

**T2-RUL-0082:** 3U Switch Profile 3 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.1:

- MOD3-SWH-6F1U7U-16.4.15-1

- MOD3-SWH-6F1U7U-16.4.15-2

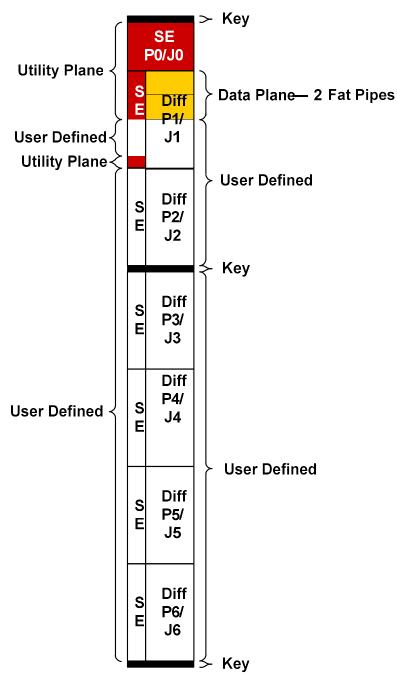

5.1.1.1.3.3.4 **3U Switch Profile 4: SWH-4F1U7U1J**

Figure 5-18 – Slot Profile SLT3-SWH-4F1U7U1J-14.8.7-n

**T2-RUL-0107:** 3U Switch Profile 4 Modules **shall** conform to the Slot Profiles SLT3-SWH-4F1U7U1J-14.8.7n per ANSI/VITA 65.0, Section 14.8.7.

**T2-RUL-0013:** 3U Switch Profile 4 Modules **shall** conform one of the following Slot Profiles per ANSI/VITA 65.1:

- SLT3-SWH-4F1U7U1J-14.8.7-0

- SLT3-SWH-4F1U7U1J-14.8.7-1

**T2-RUL-0014:** 3U Switch Profile 4 Modules **shall** conform to one of the following Module Profiles per ANSI/VITA 65.0 and ANSI/VITA 65.1:

- MOD3-SWH-4F1U7U1J-16.8.7-1

- MOD3-SWH-4F1U7U1J-16.8.7-2

5.1.1.1.3.3.5 **3U Switch Profile 5: SWH-1F1S1S1U1U1K**

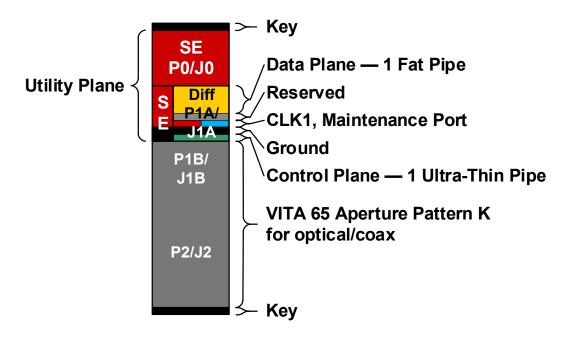

Figure 5-19 – Slot Profile SLT3-SWH-1F1S1S1U1U1K-14.8.8-n

**T2-RUL-0111:** 3U Switch Profile 5 Modules **shall** conform to the Slot Profiles SLT3-SWH-1F1S1S1U1U1K-14.8.8-n per ANSI/VITA 65.0, Section 14.8.8.