Académique Documents

Professionnel Documents

Culture Documents

2018chapitre1 6800

Transféré par

lyza DZTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

2018chapitre1 6800

Transféré par

lyza DZDroits d'auteur :

Formats disponibles

Université : Kasdi Merbah Ouargla Année Universitaire : 2017 / 2018

Faculté : F.N.T.I.C Spécialité : 1ere Master Instrumentation

Département : Electronique et télécommunications Module : Systèmes à Microprocesseurs

Cours Motorola 6800 …

Chapitre 1 : Généralités / Evolution des microprocesseurs

3. Microprocesseur :

1. Logique câblée : Elément indispensable en électronique. Il s’agit d’un élément

C’est une discipline qui permet de réaliser un système logique, en réalisé à base de semi-conducteurs dont la fabrication nécessite une

choisissant les composants appropriés et en adaptant le câblage. extrême précision.

La réalisation d’un système oblige trouver d’abord une solution théorique Il intègre des millions de transistors, et permet de manipuler es données

(en utilisant l’algèbre de Boole, table de Karnaugh, graphe des états, réseau numériques et d’exécuter des instructions stockées en mémoire

de Petri … etc) au problème posé. (Opérations arithmétiques et logiques) dans un ordre prédéfinis.

Problème !

- La réalisation de systèmes câblés pour les problèmes complexes

n’est pas évidente.

- En plus, ce genre de systèmes sont réalisés pour des applications

particulières. Toute modification sur le système impose une

modification du câblage et un changement de composants.

- Néanmoins, la logique câblée garde l’avantage en terme de

rapidité. De nos jours, le microprocesseur est partout :

A la maison (Ordinateurs, machine à laver, alarme, jouets, …)

2. Logique programmée : Dans la voiture.

Contrairement aux systèmes câblés, les systèmes programmés En industrie.

fonctionnent indépendamment du câblage, qui reste toujours le même. En

effet, leurs fonctionnement est déterminé par un programme, qui peut être Le microprocesseur est aussi appelé : MPU ou CPU.

modifié en fonction de l’application. MPU = Microprocessor Unit

Le fameux exemple de la logique câblée est bien le microprocesseur. CPU = Central Processing Unit

Site : www.sites.google.com/site/universite2ouargla Groupe Facebook : Nasri Instrumentation Ouargla

Elearn : Systèmes à Microprocesseur – N.NASRI Youtube : nadjib nasri matlablog

Chargé du cours/TD/TP : N.Nasri …

Université : Kasdi Merbah Ouargla Année Universitaire : 2017 / 2018

Faculté : F.N.T.I.C Spécialité : 1ere Master Instrumentation

Département : Electronique et télécommunications Module : Systèmes à Microprocesseurs

Cours Motorola 6800 …

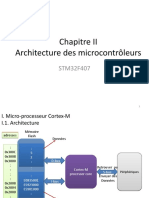

4. Architecture d’un système à microprocesseur : - De la mémoire CPU

Un système à microprocesseur se présente comme suit : - Du CPU Mémoire

- Du CPU Entrées / Sorties

Bus de données (8 bits)

- Des Entrées / Sorties CPU

Quartz

Bus E/S

Périphériques

Remarquez que le bus de données est bidirectionnel (Il transporte

CPU ROM RAM PIO dans les deux sens).

Horloge

Bus d’adresses (16 bits) : transporte une adresse générée par le

CPU. Il est unidirectionnel.

Bus adresses (16 bits)

Bus de commande : transporte les signaux de synchronisation

Bus de commande requis par le système. Il est bidirectionnel.

Il comporte :

Microprocesseur (CPU). Horloge / Quartz : Le microprocesseur est cadencé au rythme

d’une horloge interne grâce à un oscillateur (Cristal en quartz), qui

RAM (Read Only Memory, en français : mémoire à lecture seule) soumis à un courant électrique envoi des impulsions.

ou mémoire morte : Contient le programme du système. La fréquence d’horloge correspond au nombre d’impulsions par

seconde. Elle est exprimée en Hertz.

RAM (Random Access Memory, en français : mémoire à lecture et

écriture) : Stocke les données liées au système. Exemple : Un microprocesseur à 2 GHz possède une horloge qui

envoi 2 000 000 000 impulsions / seconde.

PIO (Parallel Input Output en français : Boitier d’entrées sorties A chaque impulsion, le microprocesseur exécute une action

parallèles) : Permet de communiquer avec le monde extérieur. (instruction).

Bus de données (8 bits) : Transporte les données échangées par les Bus d’entrée / sortie : Assure la communication Avec les

différents éléments du système. périphériques.

Site : www.sites.google.com/site/universite2ouargla Groupe Facebook : Nasri Instrumentation Ouargla

Elearn : Systèmes à Microprocesseur – N.NASRI Youtube : nadjib nasri matlablog

Chargé du cours/TD/TP : N.Nasri …

Université : Kasdi Merbah Ouargla Année Universitaire : 2017 / 2018

Faculté : F.N.T.I.C Spécialité : 1ere Master Instrumentation

Département : Electronique et télécommunications Module : Systèmes à Microprocesseurs

Cours Motorola 6800 …

5. Evolution des microprocesseurs :

Dans ce qui suit, les dates importantes dans l’histoire des

microprocesseurs.

1958 par Texas Instruments (1er circuit

intégré)

1947 par John Bardeen, William Shockey et

1643 par Blaise Pascal. (Machine mécanique Walter Brattain (1er transistor)

capable de faire l’addition et la soustraction)

Il ya 2000 ans : Boulier chinois

(A l’intérieur de la Pascaline)

1971 par INTEL (1er microprocesseur)

Ce sont des évènements importants dans l’histoire des

microprocesseurs, Bien sur, ce n’est pas les seuls. Dans ce qui suit on

donnera les dates importantes dans l’évolution des microprocesseurs.

En effets, deux grandes familles ont muni une course vers la perfection …

1946 ENIAC : Electronic Numerical Integrator ce fut deux entreprises américaines : INTEL Corporation (1968) premier

and Computer (Premier calculateur fabriquant mondial de semi-conducteurs et Motorola Inc (1928)

électronique)

- Pèse 30 tonne (6000 relais, 1800 tubes spécialisée en électronique et télécommunications.

1834 par Charles Babbage (Machine à électroniques, 70000 résistances).

calculer mécanique) - Réalise 5000 additions / s

- Réalise 3000 multiplications / s

Site : www.sites.google.com/site/universite2ouargla Groupe Facebook : Nasri Instrumentation Ouargla

Elearn : Systèmes à Microprocesseur – N.NASRI Youtube : nadjib nasri matlablog

Chargé du cours/TD/TP : N.Nasri …

Université : Kasdi Merbah Ouargla Année Universitaire : 2017 / 2018

Faculté : F.N.T.I.C Spécialité : 1ere Master Instrumentation

Département : Electronique et télécommunications Module : Systèmes à Microprocesseurs

Cours Motorola 6800 …

INTEL (IBM)

1971 : 4004 (4 bits) 1974: 8080 (8 bits) 1978 : 8086 (16 bits) – 8 MHz 1990: IBM Power 1 2004 : Itanium (64 bits) 2008 - 2016 : INTEL Core i3

1982 : 80186 (16 bits) – 16 MHz (Pour l’Unix) Mémoire cache intégrée ( Core i5, Core i7)

2300 transistors. 1er PC IBM 1982 : 80286 (16 bits) – 20 MHz 1993: IBM Power 2

60 000 opérations /s. 4 MHz 1985 : 80386 (32 bits) – 30 MHz 1998: IBM Power 3 2006 : Yonah

108 KHz. 250 Mo de RAM 1989 : 80486(i486) – 33 à 100 MHz … Faible consommation

1993 : Pentium1 – 90 MHz … d’énergie.

1997 : Pentium2 – 400 MHz 2010: IBM Power 7 Intégré dans ordinateurs

1999 : Pentium3 – 1 GHz 2013 : IBM Power8 portables.

2000 : Pentium4 – 3 GHz 2017 : IBM Power 9

3,1 millions de transistors

32 / 64 bits

Mémoire cache 8 Ko

Motorola (APPLE)

1975 : 6800 (8 bits) 1977 : 6809 (8 bits) 1979 : 68000 (16 bits) 1991 : Le power PC

7000 transistors. 59 instructions. Pc Macintosh. (En Collaboration avec IBM)

2 MHz. Architecture CISC. Architecture RISC.

78 instructions. 68000 transistors. Téléphonie et Smartphones … etc

Invention de la souris. 1994 et 2006 : Utilisé dans les

Pc Apple Macintosh, les

1980 : 68010 (16 bits) consoles de jeux vidéo et

1984 : 68020 (32 bits) dans les dispositifs

automobiles.

Site : www.sites.google.com/site/universite2ouargla Groupe Facebook : Nasri Instrumentation Ouargla

Elearn : Systèmes à Microprocesseur – N.NASRI Youtube : nadjib nasri matlablog

Chargé du cours/TD/TP : N.Nasri …

Université : Kasdi Merbah Ouargla Année Universitaire : 2017 / 2018

Faculté : F.N.T.I.C Spécialité : 1ere Master Instrumentation

Département : Electronique et télécommunications Module : Systèmes à Microprocesseurs

Cours Motorola 6800 …

Il existe d’autres familles de microprocesseurs qui ont rejoint la course : Remarque :

- Zilog : Z80 (8 bits) [1976] CISC = Complex Instruction Set Computer. En français : Jeu

Z8000 (16 bits) [1979] d’instruction étendu ou complexe.

- Compaq : Alpha 21064 [1993] (nommé EV4) RISC = Reduced Instruction Set Computer. En français : Jeu

Alpha 21164 [1995] (nommé EV5) d’instruction réduit.

Alpha 21264 [1998] (nommé EV6)

Alpha 21364 [2003] (nommé EV7) Core = noyau ( Core Solo = 1 noyau, Core Duo = 2 noyaux)

Alpha 21464 [2004] (nommé EV8)

Core 2 = le 2 est le nombre de couche L2 (la couche L2 est une

- SUN : SPARC [1987] mémoire cache).

Ultra SPARC II [1998] La mémoire cache est la mémoire tampon qui permet le

Ultra SPARC III [2001] (21 million de transistors) stockage d'informations (instructions et données)

Ultra SPARC IV (66 million de transistors) redondantes (qui se répètent). Elle offre ainsi un accès

Ultra SPARC T1 [2001] (Contient plus de 8 processeurs) plus rapide à ces dernières.

- HP : PA-RISC (Precision Architecture RISC) [1986] Core i3 = le i fait référence à integrated GPU (GPU = Graphical

PA- 8000 Processing Unit appelé aussi : VPU = Visual processing

PA- 8200 Unit). Le 3 = 1 integrated GPU + 2 Cores.

PA- 8500

PA- 8600

Références :

… - Daniel J.David, Rodnay Zaks, « Programmation du 6800 », Sybex Europe,1980.

EFCIS Circuits intégrés MOS, Edition Véliz, France, 1982.

PA- 890 -

- Mokrani.K, Cours Tec480, Université de A.Mira de Bejaia.

Sites :

- https://www.intel.fr/content/www/fr/fr/products/processors.html

Site : www.sites.google.com/site/universite2ouargla Groupe Facebook : Nasri Instrumentation Ouargla

Elearn : Systèmes à Microprocesseur – N.NASRI Youtube : nadjib nasri matlablog

Chargé du cours/TD/TP : N.Nasri …

Vous aimerez peut-être aussi

- Théorie et conception des filtres analogiques, 2e édition: Avec MatlabD'EverandThéorie et conception des filtres analogiques, 2e édition: Avec MatlabPas encore d'évaluation

- Jeu D - Instructions Du PIC16F84ADocument9 pagesJeu D - Instructions Du PIC16F84AOMAR ENNAJIPas encore d'évaluation

- Chapitre 4 Alimentation - Moteur - Pas - À - PasDocument37 pagesChapitre 4 Alimentation - Moteur - Pas - À - Paskhaled100% (1)

- DéfinitionDocument5 pagesDéfinitionAicha B'mh100% (1)

- Cours - Architecture ch4Document41 pagesCours - Architecture ch4Hoody 05100% (1)

- Modéle de RedactionDocument31 pagesModéle de RedactionBöuäbdälläh AïmenPas encore d'évaluation

- Cours CIs - 2012Document174 pagesCours CIs - 2012Ayman OubghachiPas encore d'évaluation

- Microcontroleur PIC16F84Document33 pagesMicrocontroleur PIC16F84redaPas encore d'évaluation

- Introduction Au SystemCDocument42 pagesIntroduction Au SystemCsupremPas encore d'évaluation

- Travaux Dirigés Architecture Des Ordinateurs Smi4 2019/2020Document2 pagesTravaux Dirigés Architecture Des Ordinateurs Smi4 2019/2020kpossou hermannPas encore d'évaluation

- Cours I2CDocument22 pagesCours I2CMarwen SellamiPas encore d'évaluation

- Cours DSP STRDocument52 pagesCours DSP STRMazen RakroukiPas encore d'évaluation

- Fascicule CAO Electronique TP3Document8 pagesFascicule CAO Electronique TP3Kyle LylyPas encore d'évaluation

- Compte Rendu TP Archetecture Des Systèmes EmbarquésDocument19 pagesCompte Rendu TP Archetecture Des Systèmes EmbarquésKhawla KholitaPas encore d'évaluation

- MMO Corrigé Sujet 1synthèse M21Document3 pagesMMO Corrigé Sujet 1synthèse M21Abdou KarimPas encore d'évaluation

- Chap2 3 Pla Pal GalDocument17 pagesChap2 3 Pla Pal GalMENANI ZineddinePas encore d'évaluation

- TP CmosDocument17 pagesTP CmosHiba TANTAOUIPas encore d'évaluation

- TD Stm32 Ex1:: RCC - Apb2Periphclockcmd Et Gpio - Deinit EtDocument7 pagesTD Stm32 Ex1:: RCC - Apb2Periphclockcmd Et Gpio - Deinit EtNesrine Zouari100% (1)

- Cours Systèmes À MicroprocesseursDocument33 pagesCours Systèmes À MicroprocesseursMomoBj50% (2)

- 2018chapitre2 6800Document5 pages2018chapitre2 6800lyza DZPas encore d'évaluation

- STR - TP-1 - Travaux PratiquesDocument12 pagesSTR - TP-1 - Travaux Pratiquesfellah baha eddinePas encore d'évaluation

- CHAP1Document6 pagesCHAP1riadh hassnaouiPas encore d'évaluation

- TD N - 1architecture PDFDocument2 pagesTD N - 1architecture PDFABDELKARIM AINPas encore d'évaluation

- CHAPITRE II Circuits Séquentiels PDFDocument35 pagesCHAPITRE II Circuits Séquentiels PDFTimble PuteurPas encore d'évaluation

- Correction TD 4 1Document17 pagesCorrection TD 4 1Kouraichi Zeineb100% (1)

- Rapport Tap Univ BBA Partie 1Document25 pagesRapport Tap Univ BBA Partie 1Emy ImenePas encore d'évaluation

- Arch Circuit Stm32-1Document97 pagesArch Circuit Stm32-1ilPas encore d'évaluation

- Les Microcontrôleurs PIC de MicrochipDocument28 pagesLes Microcontrôleurs PIC de MicrochipMohamed CoulibalyPas encore d'évaluation

- Chapitre 4 - 2008 1 PDFDocument38 pagesChapitre 4 - 2008 1 PDFoussema zmerliPas encore d'évaluation

- Presentation Du Pic 16f877 PDFDocument22 pagesPresentation Du Pic 16f877 PDFyoussefPas encore d'évaluation

- API Sturcture PDFDocument8 pagesAPI Sturcture PDFDivin MakitaPas encore d'évaluation

- 3 Cours Microprocesseur 16 BitsDocument15 pages3 Cours Microprocesseur 16 BitsSeghiour AbdellatifPas encore d'évaluation

- Chap II Architecture Des MicrocontrôleursDocument8 pagesChap II Architecture Des MicrocontrôleursMohamed Aziz Ben RomdhanePas encore d'évaluation

- TP12 Electronique 2 - 2019 - 2020 PDFDocument19 pagesTP12 Electronique 2 - 2019 - 2020 PDFKhaoula Amahouch100% (1)

- Eléments-De-Correction Eval Type CodesignDocument4 pagesEléments-De-Correction Eval Type CodesignhurnelPas encore d'évaluation

- Notice Prog C MPLAB & Cc5xDocument10 pagesNotice Prog C MPLAB & Cc5xkaimissPas encore d'évaluation

- Cours Architectures Avancées Sur PucesDocument84 pagesCours Architectures Avancées Sur PucesArafet BelhajPas encore d'évaluation

- Chapitre 5 LE TMS320C6701 DSP PDFDocument9 pagesChapitre 5 LE TMS320C6701 DSP PDFSmart ClassePas encore d'évaluation

- Chapitre 4 Introduction Au Langage MikrocDocument13 pagesChapitre 4 Introduction Au Langage MikrocMedPas encore d'évaluation

- Compte RENDU InformatiqueindutrielDocument21 pagesCompte RENDU InformatiqueindutrielOUTMANE FERNOUCHPas encore d'évaluation

- Cour Travaux Avant ProjetDocument5 pagesCour Travaux Avant ProjetHIMA SAFIPas encore d'évaluation

- TP 2Document2 pagesTP 2Usb MasPas encore d'évaluation

- Abdou. Initiation API Millenium 3Document21 pagesAbdou. Initiation API Millenium 3sethabdellahPas encore d'évaluation

- Chap2 4 FpgaDocument20 pagesChap2 4 FpgaMENANI ZineddinePas encore d'évaluation

- Projet VHDLDocument6 pagesProjet VHDLFadwa JabriPas encore d'évaluation

- Le Microprocesseur 8086Document22 pagesLe Microprocesseur 8086Merbai YassinePas encore d'évaluation

- Microprocesseur 6809 - ExpoDocument44 pagesMicroprocesseur 6809 - ExpoZAAIRA HAMZAPas encore d'évaluation

- Variateur de Vitesse Pour Moteur MonophaséDocument9 pagesVariateur de Vitesse Pour Moteur MonophaséJIHENE GHAOUIPas encore d'évaluation

- TP Initiation A La Programmation Du C PIC 16F84A en Mikro CDocument6 pagesTP Initiation A La Programmation Du C PIC 16F84A en Mikro CPaty MuyengwaPas encore d'évaluation

- Chapitre 3 Mise en Œuvre Des Microcontrôleurs AVR - CopieDocument18 pagesChapitre 3 Mise en Œuvre Des Microcontrôleurs AVR - Copiejulio KetchaPas encore d'évaluation

- TP1 Initiation À La carteSTM32F407Document12 pagesTP1 Initiation À La carteSTM32F407Hichem Guedri100% (1)

- TP1Document5 pagesTP1Oumayma AmiriPas encore d'évaluation

- LabviewDocument19 pagesLabviewtortorouPas encore d'évaluation

- Exercices 1Document2 pagesExercices 1koloPas encore d'évaluation

- Port Parallèle Pia 8255Document11 pagesPort Parallèle Pia 8255alex bbapPas encore d'évaluation

- TD1: Synthèse VHDL: Exercice 1Document2 pagesTD1: Synthèse VHDL: Exercice 1Mohamed Aziz Ben RomdhanePas encore d'évaluation

- Le système d'approvisionnement en terres dans les villes d'Afrique de l'Ouest: L’exemple de BamakoD'EverandLe système d'approvisionnement en terres dans les villes d'Afrique de l'Ouest: L’exemple de BamakoPas encore d'évaluation

- Twistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesD'EverandTwistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesPas encore d'évaluation

- Cours Microprocesseur ENSADocument138 pagesCours Microprocesseur ENSASheeya FilaliPas encore d'évaluation

- Polycop - TP MESUREDocument81 pagesPolycop - TP MESUREAmoul DhahriPas encore d'évaluation

- 2018TP1 6800Document4 pages2018TP1 6800lyza DZPas encore d'évaluation

- Instrumentation Et MesuresDocument5 pagesInstrumentation Et Mesureslyza DZPas encore d'évaluation

- Solutions Des Exercices TDDocument7 pagesSolutions Des Exercices TDlyza DZPas encore d'évaluation

- 2018chapitre4 6800Document6 pages2018chapitre4 6800lyza DZPas encore d'évaluation

- 2018TD4 6800Document1 page2018TD4 6800lyza DZPas encore d'évaluation

- 2018TD4 6800Document1 page2018TD4 6800lyza DZPas encore d'évaluation

- 2018TD3 6800Document2 pages2018TD3 6800lyza DZPas encore d'évaluation

- 2018TP1 6800Document4 pages2018TP1 6800lyza DZPas encore d'évaluation

- 2018TD1 6800Document1 page2018TD1 6800lyza DZPas encore d'évaluation

- 2018TD2 6800Document2 pages2018TD2 6800lyza DZPas encore d'évaluation

- 2018chapitre3 6800Document6 pages2018chapitre3 6800lyza DZPas encore d'évaluation

- 2018chapitre2 6800Document5 pages2018chapitre2 6800lyza DZPas encore d'évaluation

- 2018TP2 6800Document5 pages2018TP2 6800lyza DZPas encore d'évaluation

- Schema Montage Electronique Blogspot Com 2012 02 Architecture Des Ordinateurs 2eme Partie HTML TCMBCKDocument20 pagesSchema Montage Electronique Blogspot Com 2012 02 Architecture Des Ordinateurs 2eme Partie HTML TCMBCKhoodPas encore d'évaluation

- PIC LeçonN°0Document7 pagesPIC LeçonN°0Smart ClassePas encore d'évaluation

- TD1 19corrDocument5 pagesTD1 19corrSaid ReganiPas encore d'évaluation

- Cours RealizerDocument35 pagesCours Realizermaoukil ayoubPas encore d'évaluation

- Cours FinalDocument58 pagesCours FinalBASMA MIRHISSPas encore d'évaluation

- Présenté Par:: Mr. Mazoughou GOEPOGUIDocument161 pagesPrésenté Par:: Mr. Mazoughou GOEPOGUITojonirina Jacky RAKOTOMANANAPas encore d'évaluation

- Chapitr 001Document5 pagesChapitr 001oussama bouguerraPas encore d'évaluation

- Table Des Matières: Chapitre 1: La Smart House PrésentationDocument79 pagesTable Des Matières: Chapitre 1: La Smart House PrésentationM'hamed El AzzaouiPas encore d'évaluation

- Support Cours MicrocontroleursDocument80 pagesSupport Cours MicrocontroleursJrk MukalayPas encore d'évaluation

- Chapitre 2 - Microprocesseur - Ok - CopieDocument36 pagesChapitre 2 - Microprocesseur - Ok - CopieHama Mossi Abdoul RazakPas encore d'évaluation

- Programme 2017-2018 MAT Et INF 2ème AnnéeDocument12 pagesProgramme 2017-2018 MAT Et INF 2ème AnnéeUniversité des AntillesPas encore d'évaluation

- Cour 12Document30 pagesCour 12Colmain NassiriPas encore d'évaluation

- Cours Microcontrôleur Microprocesseur 76Document144 pagesCours Microcontrôleur Microprocesseur 76FadwaPas encore d'évaluation

- Fiche de TD SIE GE3Document6 pagesFiche de TD SIE GE3sigha josuePas encore d'évaluation

- Memoire Corrige Da SILVEIRADocument78 pagesMemoire Corrige Da SILVEIRADavid da SILVEIRAPas encore d'évaluation

- Les Puces RISCDocument3 pagesLes Puces RISCOumar Farouk Achirou ElhadjiPas encore d'évaluation

- Microproc Enstb2001Document124 pagesMicroproc Enstb2001Mohamed EnnajiPas encore d'évaluation

- A - Introduction ElectroniqueDesSysEmbarqués PDFDocument59 pagesA - Introduction ElectroniqueDesSysEmbarqués PDFAnas AsranPas encore d'évaluation

- Les Microcontrôleurs de La Famille PICDocument75 pagesLes Microcontrôleurs de La Famille PICNabil DakhliPas encore d'évaluation

- VHDL ProcesseurDocument21 pagesVHDL ProcesseurchaoukiPas encore d'évaluation

- Rapport Sujet1 Iut 9900Document65 pagesRapport Sujet1 Iut 9900Mounir MahjoubiPas encore d'évaluation

- Informatique Industrielle - 1st PartDocument53 pagesInformatique Industrielle - 1st PartMoussa SEYEPas encore d'évaluation

- La Carte Arduino Uno (PDFDrive)Document258 pagesLa Carte Arduino Uno (PDFDrive)Korota Arsène COULIBALYPas encore d'évaluation

- C2 - Archi - Processeurs - Définitions Et Concept Clefs - 2023Document36 pagesC2 - Archi - Processeurs - Définitions Et Concept Clefs - 2023Saamson StephenPas encore d'évaluation

- Cours Archi 2eme Ing Partie 01Document87 pagesCours Archi 2eme Ing Partie 01Anis MezniPas encore d'évaluation

- QCM - Calculateurs - Embarques Corr PDFDocument5 pagesQCM - Calculateurs - Embarques Corr PDFBilelAmerPas encore d'évaluation

- Examen IE5 Janvier 2020 FinalDocument14 pagesExamen IE5 Janvier 2020 FinalDhafer MezghaniPas encore d'évaluation

- Systèmes Embarquée - Lpi PDFDocument158 pagesSystèmes Embarquée - Lpi PDFAbdelkarim MeskaouiPas encore d'évaluation

- Conception IoT Part1Document60 pagesConception IoT Part1dhamer inesPas encore d'évaluation

- Architecture Matérielle Des OrdinateursDocument7 pagesArchitecture Matérielle Des OrdinateursZouhour GawaPas encore d'évaluation