# PCIe SSC Test using MP1900A

Signal Quality Analyzer-R MP1900A Series

# **Contents**

| 1   | Introduction                                 | 2 |

|-----|----------------------------------------------|---|

| 2   | SSC Outline                                  | 2 |

| 3   | PCI-SIG Activities                           | 3 |

| 4   | Anritsu Solution                             | 4 |

| 4.1 | Product Setup and Jitter Tolerance Standards | 4 |

| 4.2 | Rx LEQ Test Support                          | 5 |

| 4.3 | Rx LEQ Compliance Test Setup                 | 6 |

| 5   | Conclusion                                   | 7 |

## 1 Introduction

Spread Spectrum Clocking (SSC) is a signal modulation technology used by interfaces for connecting various electronic parts within a product and by external equipment connections.

To reduce electromagnetic interference (EMI), the U.S. FCC and EU guidelines establish the following rigorous rules concerning clock signal modulation, or in other words jitter addition, frequency distribution scatter, and the concentration of energy at specific EMI frequencies.

Since PCIe also uses SSC technology, the above guidelines also explain the required standards.

On the other hand, SSC is a factor causing jitter components degrading overall system communications quality. For example, confirming interconnectivity while applying SSC is a key subject because problems such as data loss occur when equipment peers cannot link-up due to interconnectivity issues.

#### 2 SSC Outline

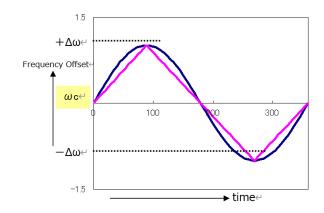

SSC standardized by PCIe is triangular-shaped modulation waveform. Generally, frequency modulation is applied as phase-modulation components, which are large stress components for electronic parts. When converting frequency modulation to phase modulation, the phase displacement  $\Delta$ TTpp at the triangular-shaped frequency modulation is defined as follows:

$$\Delta TT_{pp} = \frac{\pi}{4} \cdot \frac{1}{2 \cdot \pi \cdot fc} \cdot \frac{\Delta f_{pp}}{fm}$$

fc : Center Frequencyfm : Modulation Frequency

$\Delta \! f_{PP}$  : Frequency Deviation ( Peak to Peak ) $\!\!\!\leftarrow$

As defined by PCle, 5000 ppm frequency modulation at 30 to 33 kHz is equivalent to phase modulation of about 20 ns and is clearly a major high-stress source.

### 3 PCI-SIG Activities

The PCI-SIG Base Specification regulates the following SSC modulation requirements.

Table 1. Base Specification Rev 5.0 Ver 1.0

| Symbol                          | Description                                                                                         | Limits                      | Units      | Notes |

|---------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------|------------|-------|

| FREFCLK                         | Refclk Frequency                                                                                    | 99.97 (min)<br>100.03 (max) | MHz        |       |

| FREFCLK_32G                     | Refclk Frequency for devices that support 32.0 GT/s                                                 | 99.99 (min)<br>100.01 (max) | MHz        |       |

| Fssc                            | SSC frequency range                                                                                 | 30 (min)<br>33 (max)        | kHz        | 3     |

| T <sub>SSC-FREQ-DEVIATION</sub> | SSC deviation                                                                                       | -0.5 (min)<br>0.0 (max)     | %          | 3     |

| TSSC-FREQ-DEVIATION_32G_SRIS    | SSC deviation for devices that support 32.0 GT/s and SRIS when operating in SRIS mode at all speeds | -0.3 (min)<br>0.0 (max)     | %          | 3     |

| T <sub>TRANSPORT-DELAY</sub>    | Tx-Rx transport delay                                                                               | 12 (max)                    | ns         | 1, 4  |

| T <sub>SSC-MAX-FREQ-SLEW</sub>  | Max SSC df/dt                                                                                       | 1250                        | ppm/<br>μs | 2, 3  |

#### Notes

- 1. Parameter is relevant only for Common Refclk architecture.

- 2. Measurement is made over  $0.5~\mu s$  time interval with a  $1^{st}$  order LPF with an  $f_c$  of 60x the modulation frequency.

- When testing the a device configured for the <u>IR</u> reference clock architecture the SSC related parameters must be tested with the Tx output data instead of the reference clock.

- 4. There are form factors (for example topologies including long cables) that may exceed the transport delay limit. Extra jitter from the large transport delay must be accounted by these form factor specifications.

Although the Base Specification regulates electrical requirements at the chip level, SSC was not a required item in the Compliance Test prior to Gen4. As a result, although the Receiver Test in the Compliance Test defines the worst-case conditions for other types of stress tests (SJ, RJ, DM-I, CM-I, Insertion Loss), there were no requirements concerning application of SSC.

On the other hand, the many PCIe systems on the market support SSC application from the perspective of reducing EMI. As a result, although many systems validated by the Compliance Test claim to support application of SSC, since SSC application tests have not actually been executed, sometimes, there are SSC-related problems in the commercial market.

In these circumstances, PCI-SIG revised the PHY Test Specification regulating the Compliance Test electrical test methods to specify worst-case conditions for SSC application and added clear SSC Application requirements to Draft 0.7 of the PCIe 5.0 PHY Test Specification.

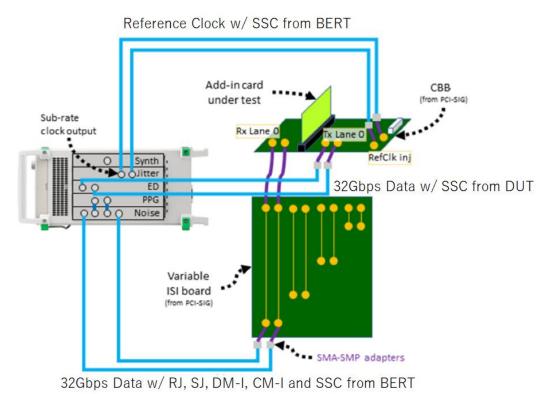

## 2.15.6 Add-in Card Receiver Link Equalization Test for 32.0 GT/s

The test is performed by following these steps:

- 1. Insert the Add-in Card under test into the CEM 5.0 CBB without power. The signal source should be connected to the Rx lane under test on the CBB, the receiver of the protocol aware test equipment should be connected to the Tx lane under test on the CBB. Other TX lanes can be terminated with 50-ohm terminations or unterminated as requested by the device under test operator.

- 2. Connect 100MHz SSC enabled (-0.5% down-spread) REF CLK from BERT into the CLK IN connectors on CBB.

AIC (Add-In Card) Receiver Test Procedure

# 2.16.6 System Board Receiver Link Equalization Test for 32.0 GT/s

1. Insert the CEM 5.0 CLB into the system under test without power. The signal source should be connected to the Rx lane under test on the CLB, the receiver of the protocol aware test equipment should be connected to the Tx lane under test on the CLB. The CLB 100 MHz clock output from the system under test shall be connected to the test equipment and drive the test equipment transmissions after being filtered by a *PCI Express Base Specification* compliant PLL or equivalent. The system will use SSC enabled or SSC disabled reference clock to be consistent with settings for the system during normal operation. Other TX lanes must be unterminated on the CLB.

System Receiver Test Procedure

#### 4 Anritsu Solution

## 4.1 Product Setup and Jitter Tolerance Standards

For the Receiver test, the Anritsu solution uses a Pulse Pattern Generator (PPG) to apply SSC and measures the BER of the signal with applied SSC using an Error Detector (ED).

## SI PPG MU195020A Specifications

| Jitter Tolerance Mask* | Bit rate: 16, 28.1*, 32.1 Gbit/s*                                                                       |

|------------------------|---------------------------------------------------------------------------------------------------------|

|                        | Pattern: PRBS 2 <sup>31</sup> – 1                                                                       |

|                        | SSC with a 7000 ppm amplitude and RJ of 0.3 UI can be simultaneously applied by using MU181500B.        |

|                        | These specifications are defined assuming the following conditions:                                     |

|                        | Loopback connection to the MU195040A, defined by one specific temperature in the range of 20°C to 30°C. |

|                        | When RJ + BUJ is bigger than 0.5 Ulp-p or SJ + RJ + BUJ is bigger than the standard value + 0.3 Ulp-p,  |

|                        | "Overload" is displayed on the MU181500B screen                                                         |

PPG Jitter Tolerance Specification

## **SI ED MU195040A Specifications**

#### **Jitter Tolerance**

| Jitter Tolerance | Bit rate: 16 Gbit/s, 28.1 Gbit/s*, 32.1 Gbit/s*                                                         |

|------------------|---------------------------------------------------------------------------------------------------------|

|                  | Pattern: PRBS 2 <sup>31</sup> – 1                                                                       |

|                  | SSC with a 7000 ppm amplitude and RJ of 0.3 UI can be simultaneously applied by using MU181500B.        |

|                  | These specifications are defined assuming the following conditions:                                     |

|                  | Loopback connection to the MU195020A, defined by one specific temperature in the range of 20°C to 30°C. |

|                  | When RJ + BUJ is bigger than 0.5 Ulp-p or SJ + RJ + BUJ is bigger than the standard value + 0.3 Ulp-p,  |

|                  | "Overload" is displayed on the MU181500B screen.                                                        |

**ED Jitter Tolerance Specification**

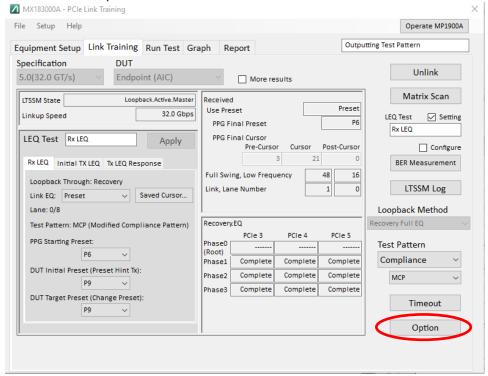

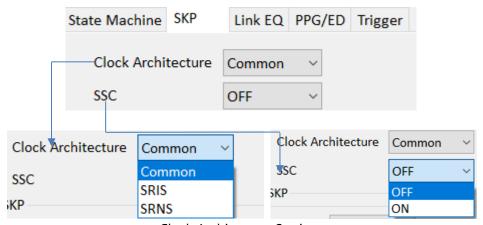

## 4.2 Rx LEQ Test Support

The Signal Quality Analyzer-R MP1900A supports tests with the following clock architectures

- · Common Clock with SSC

- Common Clock without SSC

- SRIS (Separate Reference Independent SSC)

- SRNS (Separate Reference Clock Non SSC)

Settings are made at the Option menu shown below.

**Rx LEQ Test Application**

**Clock Architecture Settings**

## 4.3 Rx LEQ Compliance Test Setup

The Compliance Test specifies testing with a Common Clock.

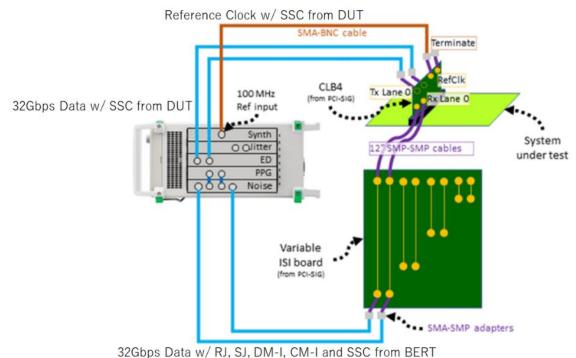

Although the measurement target can be either the Add in Card (AIC) or System, as shown in the following setup diagrams, the MP1900A supports SSC stress tests of both as the target DUT.

AIC Receiver Test Setup

System Receiver Test Setup

### 5 Conclusion

This application note has introduced the use of SSC in the PCIe market and the importance of testing under these environments.

Sometimes, latent errors that are not a problem may occur at conventional Compliance Tests with applied SSC. At testing under these environments, pretesting to discover latent error factors is important to improve and assure product quality.

These requirements dictate the specifications for a Bit Error Rate Tester (BERT) used for these particular tests. The measuring instrument itself must also be able to withstand higher stress signals than specified by the test. Anritsu's MP1900A is currently the only measuring instrument supporting these conditions.

Anritsu supports worst-case testing with timely solutions helping to improve customers' product quality and contributing to the industry's development

#### References

PCI-Express Base Specification 5.0 Ver 1.0

PCI-Express PHY Test Specification 5.0 Ver 0.7 (Draft)

## United States

#### **Anritsu Americas Sales Company**

450 Century Parkway, Suite 190, Allen, TX 75013 U.S.A. Phone: +1-800-Anritsu (1-800-267-4878)

## Anritsu Electronics Ltd.

700 Silver Seven Road, Suite 120, Kanata, Ontario K2V 1C3, Canada Phone: +1-613-591-2003

Fax: +1-613-591-1006

#### • Brazil

#### Anritsu Eletronica Ltda.

Praça Amadeu Amaral, 27 - 1 Andar 01327-010 - Bela Vista - Sao Paulo - SP, Brazil Phone: +55-11-3283-2511 Fax: +55-11-3288-6940

#### Mexico

#### Anritsu Company, S.A. de C.V.

Blvd Miguel de Cervantes Saavedra #169 Piso 1, Col. Granada Mexico, Ciudad de Mexico, 11520, MEXICO Phone: +52-55-4169-7104

## United Kingdom

### Anritsu EMEA Ltd.

200 Capability Green, Luton, Bedfordshire, LU1 3LU, U.K. Phone: +44-1582-433200 Fax: +44-1582-731303

#### • France

#### Anritsu S.A.

12 avenue du Québec, Immeuble Goyave, 91140 VILLEBON SUR YVETTE, France Phone: +33-1-60-92-15-50

#### Germany

#### Anritsu GmbH

Nemetschek Haus, Konrad-Zuse-Platz 1, 81829 München, Germany Phone: +49-89-442308-0 Fax: +49-89-442308-55

## Italy

#### Anritsu S.r.l.

Spaces Eur Arte, Viale dell'Arte 25, 00144 Roma, Italy Phone: +39-6-509-9711

#### Sweden

#### Anritsu AB

Kistagången 20 B, 2 tr, 164 40 Kista, Sweden Phone: +46-8-534-707-00

#### Finland

#### Anritsu AB

Technopolis Aviapolis, Teknobulevardi 3-5 (D208.5.), FI-01530 Vantaa, Finland Phone: +358-20-741-8100

#### Anritsu A/S

c/o Regus Winghouse, Ørestads Boulevard 73, 4th floor, 2300 Copenhagen S, Denmark Phone: +45-7211-2200

#### Anritsu EMEA Ltd.

#### Representation Office in Russia

Tverskaya str. 16/2, bld. 1, 7th floor., Moscow, 125009, Russia Phone: +7-495-363-1694 Fax: +7-495-935-8962

#### • Spain

#### Anritsu EMEA Ltd.

#### Representation Office in Spain

Paseo de la Castellana, 141. Planta 5, Edificio Cuzco IV 28046, Madrid, Spain Phone: +34-91-572-6761

#### Austria

#### Anritsu EMEA GmbH

Am Belvedere 10, A-1100 Vienna, Austria Phone: +43-(0)1-717-28-710

#### • United Arab Emirates Anritsu EMEA Ltd.

#### Anritsu A/S

Office No. 164, Building 17, Dubai Internet City P. O. Box – 501901, Dubai, United Arab Emirates Phone: +971-4-3758479

#### • India

#### **Anritsu India Private Limited**

6th Floor, Indiqube ETA, No.38/4, Adjacent to EMC2, Doddanekundi, Outer Ring Road, Bengaluru – 560048, India Phone: +91-80-6728-1300 Fax: +91-80-6728-1301

## Singapore

#### Anritsu Pte. Ltd.

11 Chang Charn Road, #04-01, Shriro House, Singapore 159640 Phone: +65-6282-2400 Fax: +65-6282-2533

Specifications are subject to change without notice.

#### Vietnam

#### **Anritsu Company Limited**

Room No. 1635, 16th Floor, ICON 4 Tower, 243A De La Thanh Street, Lang Thuong Ward, Dong Da District, Hanoi, Vietnam Phone: +84-24-3760-6216 Fax: +84-24-6266-2608

## • P.R. China (Shanghai)

Anritsu (China) Co., Ltd.

Room 2701-2705, Tower A, New Caohejing International

Business Center No. 391 Gui Ping Road Shanghai, 200233, P.R. China Phone: +86-21-6237-0898 Fax: +86-21-6237-0899

#### • P.R. China (Hong Kong) Anritsu Company Ltd.

Unit 1006-7, 10/F., Greenfield Tower, Concordia Plaza, No. 1 Science Museum Road, Tsim Sha Tsui East, Kowloon, Hong Kong, P.R. China Phone: +852-2301-4980 Fax: +852-2301-3545

#### Japan

#### Anritsu Corporation

8-5, Tamura-cho, Atsugi-shi, Kanagawa, 243-0016 Japan Phone: +81-46-296-6509 Fax: +81-46-225-8352

#### Korea

### Anritsu Corporation, Ltd.

5FL, 235 Pangyoyeok-ro, Bundang-gu, Seongnam-si, Gyeonggi-do, 13494 Korea Phone: +82-31-696-7750 Fax: +82-31-696-7751

#### Australia

**Anritsu Pty. Ltd.**Unit 20, 21-35 Ricketts Road, Mount Waverley, Victoria 3149, Australia Phone: +61-3-9558-8177 Fax: +61-3-9558-8255

#### Taiwan

#### **Anritsu Company Inc.**

7F, No. 316, Sec. 1, NeiHu Rd., Taipei 114, Taiwan Phone: +886-2-8751-1816 Fax: +886-2-8751-1817

210422