# NHD-C0216CZ-FSW-FBW-3V3

# COG (Chip-on-Glass) Liquid Crystal Display Module

**Newhaven Display** NHD-

C0216-COG, 2 lines x 16 characters

CZ-Model

F-Transflective

SW-Side White LED Backlight

F-FSTN (+)

6:00 View Angle

W-Wide Temp (-20 c  $\sim$  +70 c)

3V3-3Vdd, 3V Backlight

**RoHS Compliant**

## Newhaven Display International, Inc.

2511 Technology Drive, Suite 101

Elgin IL, 60124

Ph: 847-844-8795 Fax: 847-844-8796

www.newhavendisplay.com

nhtech@newhavendisplay.com nhsales@newhavendisplay.com

# **Document Revision History**

| Revision | Date       | Description                        | Changed by |

|----------|------------|------------------------------------|------------|

| 0        | 11/11/2008 | Initial Release                    |            |

| 1        | 8/26/2009  | User guide reformat                | BE         |

| 2        | 10/9/2009  | Updated Electrical Characteristics | MC         |

| 3        | 10/22/2009 | Font Table Revision                | BE         |

| 4        | 10/27/2009 | Updated the Block Diagram          | MC         |

| 5        | 11/19/2009 | Updated backlight supply current   | MC         |

| 6        | 12/18/2009 | Pin description updated            | BE         |

## **Functions and Features**

- 2 lines x 16 characters

- Built-in controller (ST7032 or equivalent)

- 5x8 dots with cursor

- 4-line SPI MPU interface

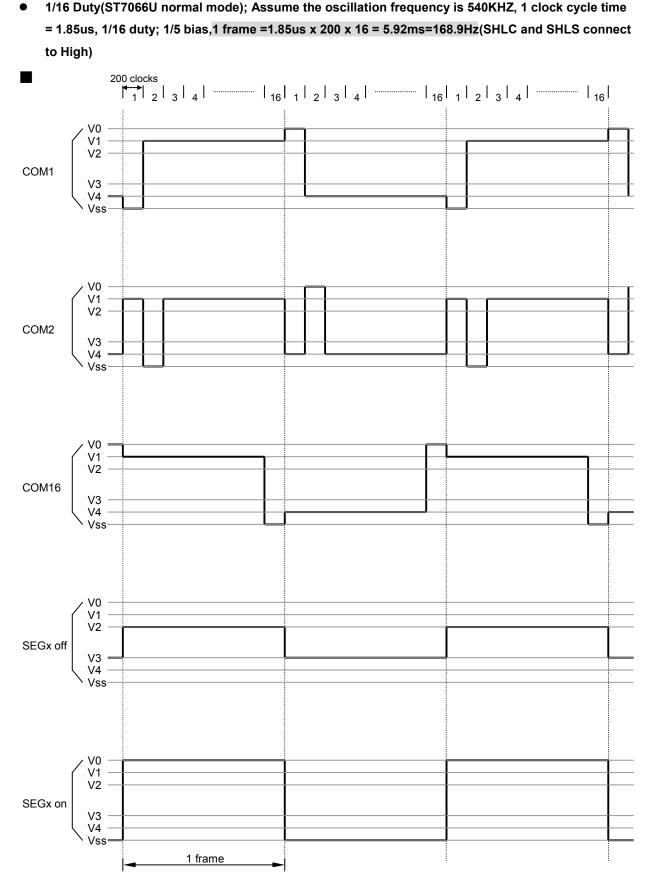

- 1/16 duty, 1/5 bias

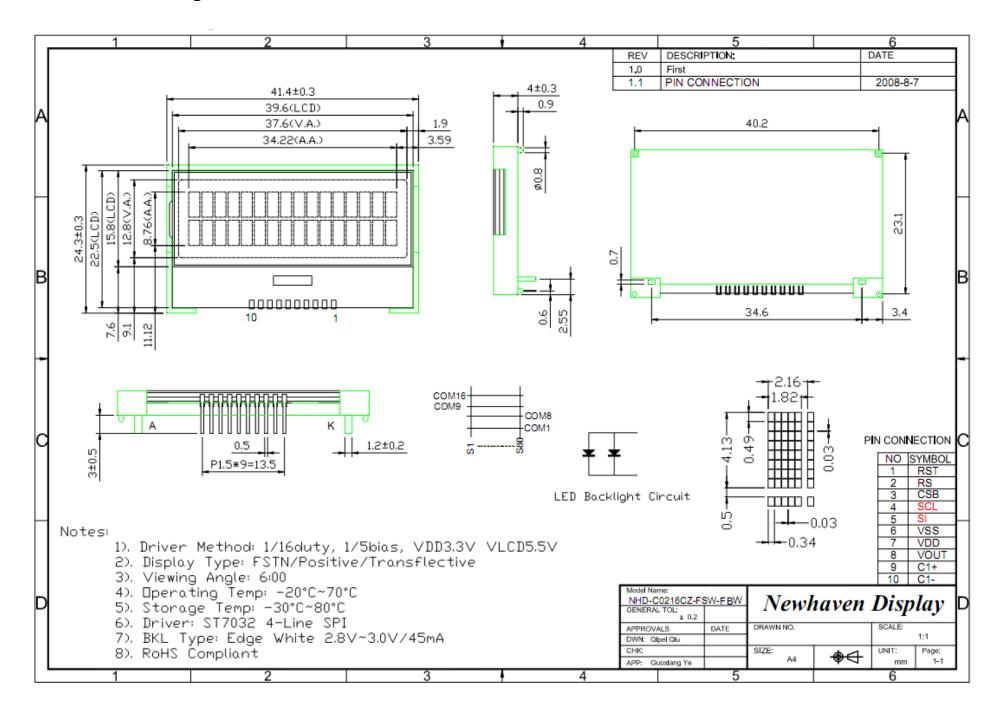

## **Mechanical Drawing**

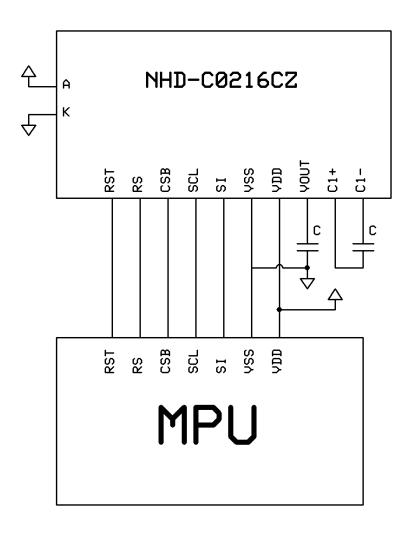

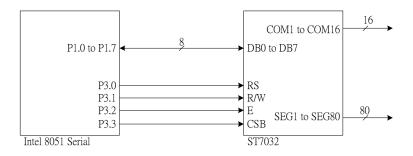

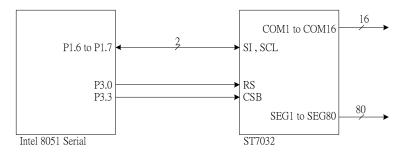

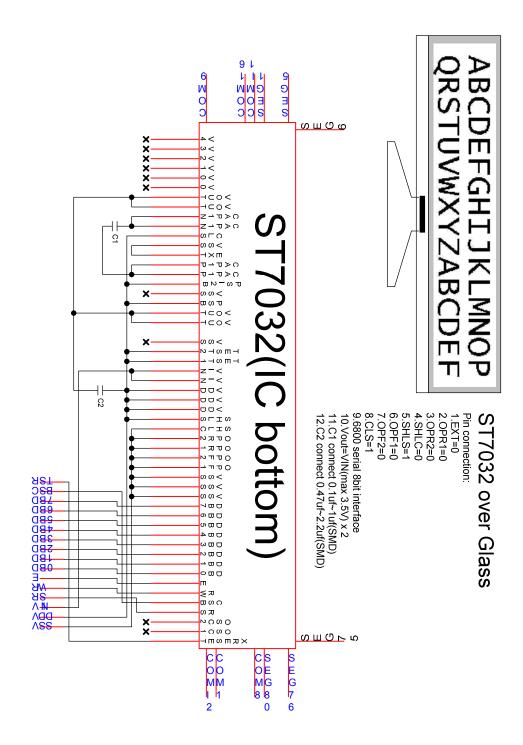

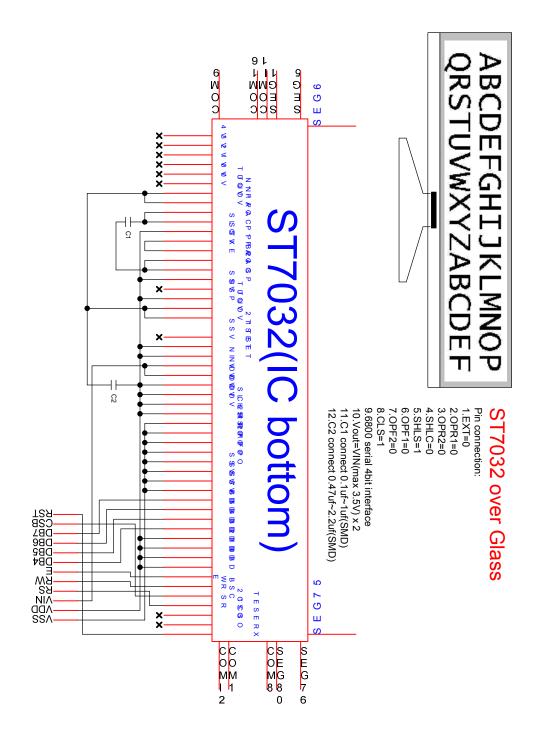

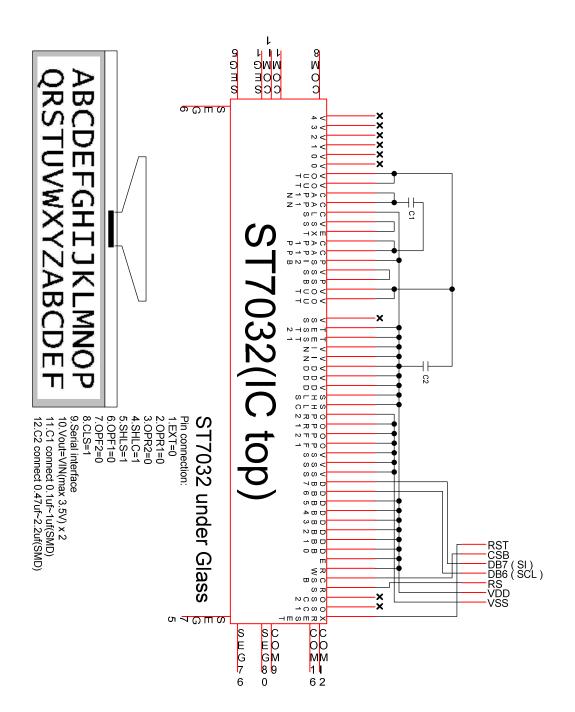

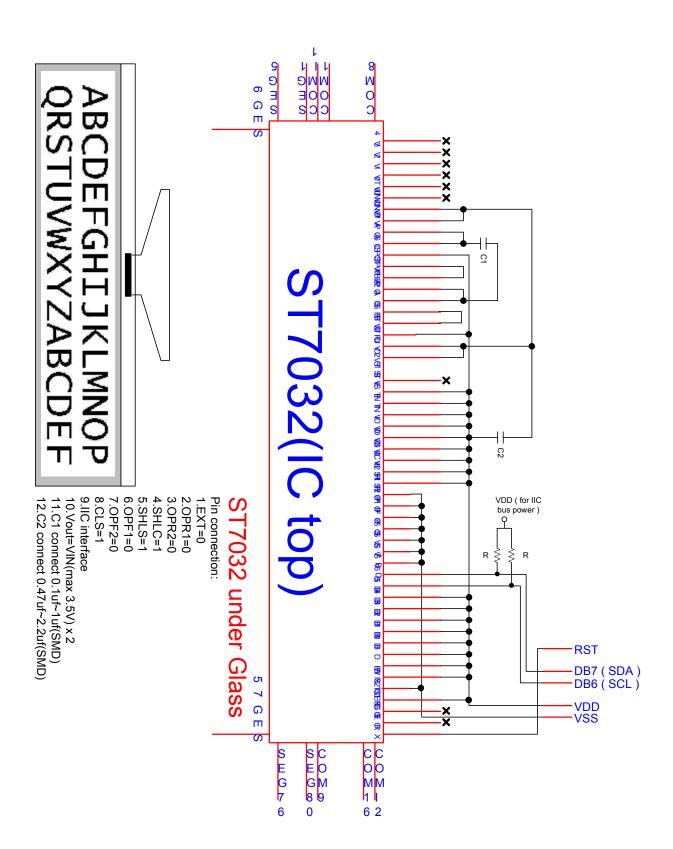

## **Pin Description and Wiring Diagram**

| Pin No. | Symbol | External     | Function Description                                            |

|---------|--------|--------------|-----------------------------------------------------------------|

|         |        | Connection   |                                                                 |

| 1       | RST    | MPU          | Active LOW Reset Signal                                         |

| 2       | RS     | MPU          | Register Select Signal. RS=0: instruction; RS=1: data           |

| 3       | CSB    | MPU          | Active LOW Chip Select signal                                   |

| 4       | SCL    | MPU          | Serial clock                                                    |

| 5       | SI     | MPU          | Input data                                                      |

| 6       | Vss    |              | Ground                                                          |

| 7       | VDD    | Power Supply | Power supply for logic for LCD (3.3V).                          |

| 8       | VOUT   |              | DC/DC voltage converter. Connect to 1uF capacitor to VDD or Vss |

| 9       | C1+    |              | Voltage booster circuit. Connect to 0.47uF-2.2uF cap to PIN10.  |

| 10      | C1-    |              | Voltage booster circuit. Connect to 0.47uF-2.2uF cap to PIN9.   |

| Α       | LED+   | Power Supply | Power supply for Backlight (3.0V)                               |

| K       | LED-   | Power Supply | Backlight Ground                                                |

**Recommended LCD connector:** 1.5mm pitch, 10 pins Soldered to PCB **Backlight connector:** A and K pins **Mates with:** - Solder to wires or PCB

## **Electrical Characteristics**

| Item                        | Symbol | Condition    | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|--------------|------|------|------|------|

| Operating Temperature Range | Тор    | Absolute Max | -20  | -    | +70  | °C   |

| Storage Temperature Range   | Tst    | Absolute Max | -30  | -    | +80  | °C   |

| Supply Voltage              | VDD    |              | 2.7  | 3.3  | 4.5  | V    |

| Supply Current              | IDD    | VDD= 3.3V    | -    | 0.3  | 0.5  | mA   |

| Supply for LCD (contrast)   | VDD-Vo | Ta=25°C      | -    | 5.5  | -    | V    |

| "H" Level input             | VIH    |              | 2.2  | -    | VDD  | V    |

| "L" Level input             | VIL    |              | 0    | -    | 0.6  | V    |

| "H" Level output            | VoH    |              | 2.4  | -    | -    | V    |

| "L" Level output            | VoL    |              | -    | -    | 0.4  | V    |

|                             |        |              |      |      |      |      |

| Backlight Supply Voltage    | VLED   |              | -    | 3.0  | -    | V    |

| Backlight Supply Current    | ILED   | VLED=3.0V    | -    | 30   | 45   | mA   |

# **Optical Characteristics**

| Item                       | Symbol | Condition | Min. | Тур. | Max. | Unit |

|----------------------------|--------|-----------|------|------|------|------|

| Viewing Angle - Vertical   | AV     | Cr ≥ 2    | -60  | -    | +35  | 0    |

| Viewing Angle - Horizontal | AH     | Cr ≥ 2    | -40  | -    | +40  | 0    |

| Contrast Ratio             | Cr     |           | -    | 6    | ı    | -    |

| Response Time (rise)       | Tr     | -         | -    | 150  | 250  | ms   |

| Response Time (fall)       | Tf     | -         | -    | 150  | 250  | ms   |

## **Controller Information**

Built-in ST7032. Download specification at <a href="http://www.newhavendisplay.com/app">http://www.newhavendisplay.com/app</a> notes/ST7032.pdf

# **Table of Commands**

| Instruction                      |    | •   | Ir  | nstr | ucti | on  | Coc | le  |     |     | Deceriation                                                                                                                      |                | nstructio<br>cution T |                |

|----------------------------------|----|-----|-----|------|------|-----|-----|-----|-----|-----|----------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|----------------|

|                                  | RS | R/W | DB7 | DB6  | DB5  | DB4 | DB3 | DB2 | DB1 | DB0 | Description                                                                                                                      | OSC=<br>380KHz |                       | OSC=<br>700KHz |

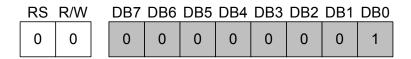

| Clear<br>Display                 | 0  | 0   | 0   | 0    | 0    | 0   | 0   | 0   | 0   | 1   | Write "20H" to DDRAM. and set DDRAM address to "00H" from AC                                                                     | 1.08<br>ms     | 0.76<br>ms            | 0.59 ms        |

| Return<br>Home                   | 0  | 0   | 0   | 0    | 0    | 0   | 0   | 0   | 1   | x   | Set DDRAM address to "00H" from AC and return cursor to its original position if shifted. The contents of DDRAM are not changed. | 1.08<br>ms     | 0.76<br>ms            | 0.59 ms        |

| Entry Mode<br>Set                | 0  | 0   | 0   | 0    | 0    | 0   | 0   | 1   | I/D | s   | Sets cursor move direction and specifies display shift. These operations are performed during data write and read.               | 26.3 us        | 18.5 us               | 14.3 us        |

| Display<br>ON/OFF                | 0  | 0   | 0   | 0    | 0    | 0   | 1   | D   | С   | В   | D=1:entire display on<br>C=1:cursor on<br>B=1:cursor position on                                                                 | 26.3 us        | 18.5 us               | 14.3 us        |

| Function Set                     | 0  | 0   | 0   | 0    | 1    | DL  | N   | DH  | *0  | IS  | DL: interface data is 8/4 bits N: number of line is 2/1 DH: double height font IS: instruction table select                      | 26.3 us        | 18.5 us               | 14.3 us        |

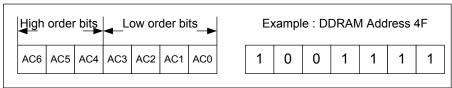

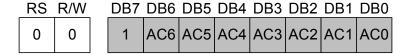

| Set DDRAM address                | 0  | 0   | 1   | AC6  | AC5  | AC4 | AC3 | AC2 | AC1 | AC0 | Set DDRAM address in address counter                                                                                             | 26.3 us        | 18.5 us               | 14.3 us        |

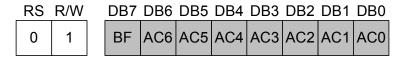

| Read Busy<br>flag and<br>address | 0  | 1   | BF  | AC6  | AC5  | AC4 | AC3 | AC2 | AC1 | AC0 | Whether during internal operation or not can be known by reading BF. The contents of address counter can also be read.           | 0              | 0                     | 0              |

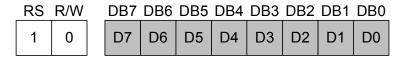

| Write data to RAM                | 1  | 0   | D7  | D6   | D5   | D4  | D3  | D2  | D1  | D0  | Write data into internal RAM (DDRAM/CGRAM/ICONRAM)                                                                               | 26.3 us        | 18.5 us               | 14.3 us        |

| Read data<br>from RAM            | 1  | 1   | D7  | D6   | D5   | D4  | D3  | D2  | D1  | D0  | Read data from internal RAM (DDRAM/CGRAM/ICONRAM)                                                                                | 26.3 us        | 18.5 us               | 14.3 us        |

Note \*: this bit is for test command , and must always set to "0"

|                            | Instruction table 0(IS=0) |   |   |   |     |     |     |     |     |     |                                                                                                                        |         |         |         |

|----------------------------|---------------------------|---|---|---|-----|-----|-----|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|

| Cursor or<br>Display Shift | 0                         | 0 | 0 | 0 | 0   | 1   |     | R/L |     | x   | S/C and R/L:<br>Set cursor moving and display shift<br>control bit, and the direction, without<br>changing DDRAM data. | 26.3 us | 18.5 us | 14.3 us |

| Set CGRAM                  | 0                         | 0 | 0 | 1 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 | Set CGRAM address in address<br>counter                                                                                | 26.3 us | 18.5 us | 14.3 us |

|                                        |   |   |   |   |   |   | Ins | tru      | ctio     | n ta | ble 1(IS=1)                                                                                                       |         |         |         |

|----------------------------------------|---|---|---|---|---|---|-----|----------|----------|------|-------------------------------------------------------------------------------------------------------------------|---------|---------|---------|

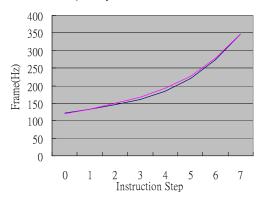

| Internal OSC frequency                 | 0 | 0 | 0 | 0 | 0 | 1 | BS  | F2       | F1       | F0   | BS=1:1/4 bias<br>BS=0:1/5 bias<br>F2~0: adjust internal OSC<br>frequency for FR frequency.                        | 26.3 us | 18.5 us | 14.3 us |

| Set ICON address                       | 0 | 0 | 0 | 1 | 0 | 0 | AC3 | AC2      | AC1      | IAC0 | Set ICON address in address counter.                                                                              | 26.3 us | 18.5 us | 14.3 us |

| Power/ICON<br>control/Contr<br>ast set |   | 0 | 0 | 1 | 0 | 1 | lon | Bon      | C5       | C4   | lon: ICON display on/off<br>Bon: set booster circuit on/off<br>C5,C4: Contrast set for internal<br>follower mode. | 26.3 us | 18.5 us | 14.3 us |

| Follower<br>control                    | 0 | 0 | 0 | - | 1 | 0 | Fon | Rab<br>2 | Rab<br>1 | Rab  | Fon: set follower circuit on/off<br>Rab2~0:<br>select follower amplified ratio.                                   | 26.3 us | 18.5 us | 14.3 us |

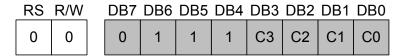

| Contrast set                           | 0 | 0 | 0 | 1 | 1 | 1 | СЗ  | C2       | C1       | CO   | Contrast set for internal follower mode.                                                                          | 26.3 us | 18.5 us | 14.3 us |

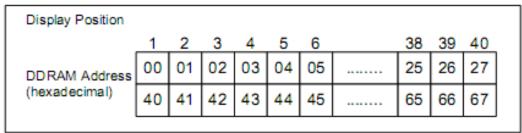

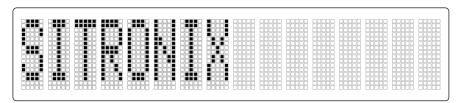

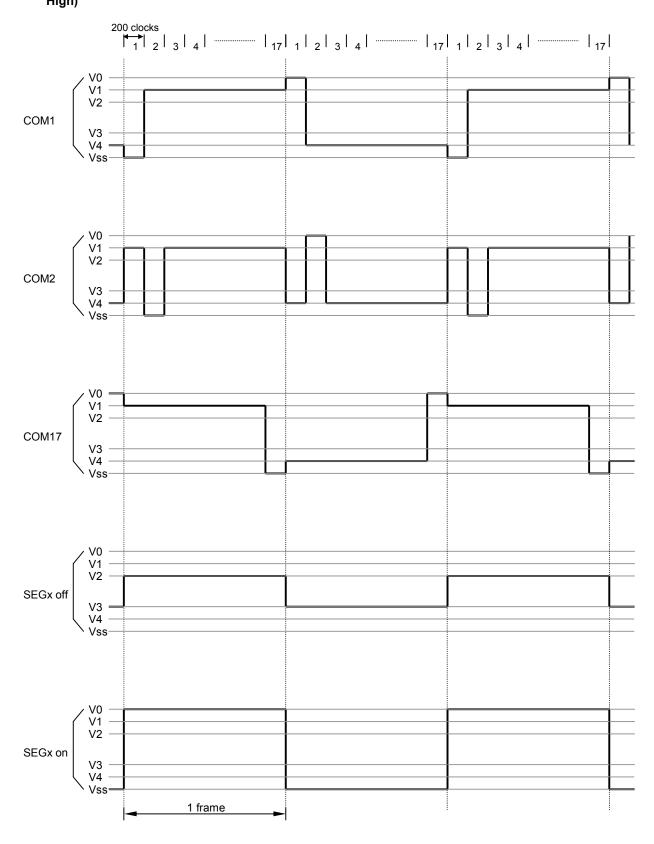

Figure 10. 2-Line Display

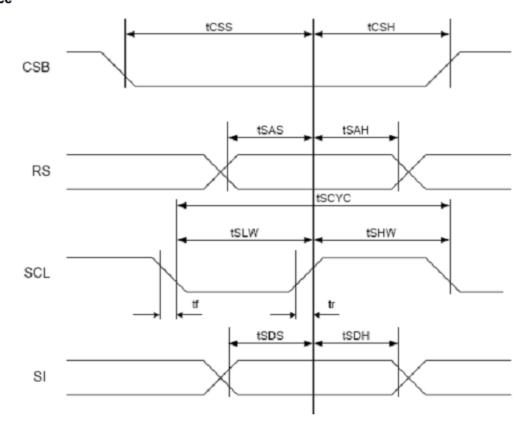

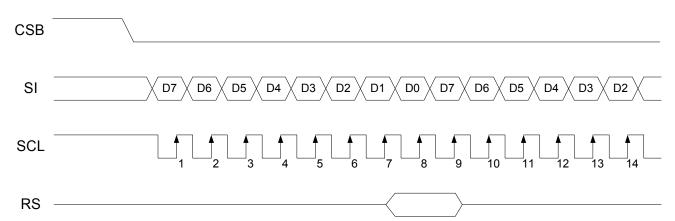

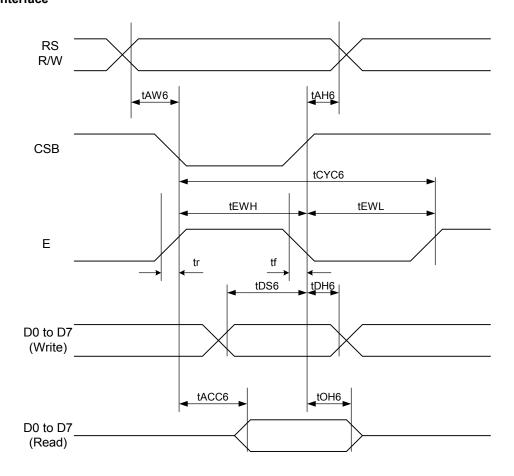

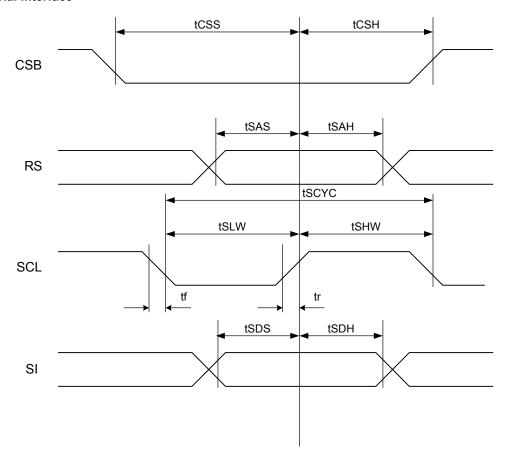

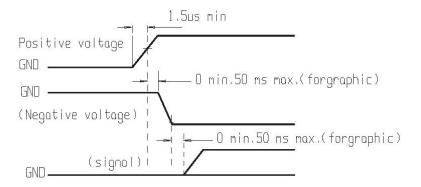

# **Timing Characteristics**

(Ta=25°C, VDD=3.0V)

| Item                | Symbol | Symbol | Min. | Тур. | Max. | Unit |

|---------------------|--------|--------|------|------|------|------|

| Serial clock period |        | tSCYC  | 200  | -    | -    |      |

| SCL 'H' pulse width | SCL    | tSHW   | 20   | -    | -    |      |

| SCL 'L' pulse width |        | tSLW   | 160  | -    | -    |      |

| SCL rise/fall time  | SCL    | Tr,tf  | -    | -    | 20   |      |

| Address setup time  | RS     | tSAS   | 10   | -    | -    | 20   |

| Address hold time   | KS     | tSAH   | 250  | -    | -    | ns   |

| Data setup time     | SI     | tSDS   | 10   | -    | -    |      |

| Data hold time      | Si     | tSDH   | 10   | -    | -    |      |

| CS-SCL time         | 00     | tCSS   | 20   | -    | -    |      |

|                     | CS     | tCSH   | 350  | -    | -    |      |

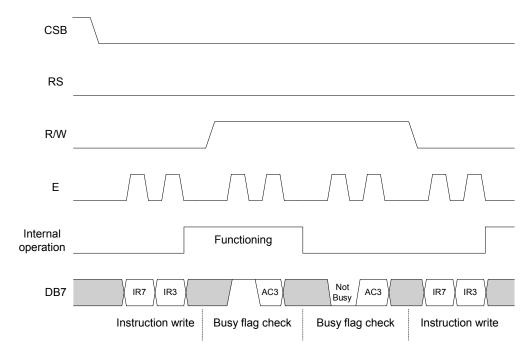

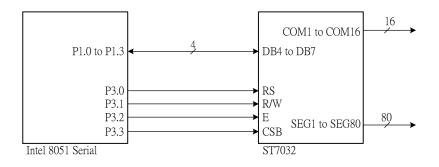

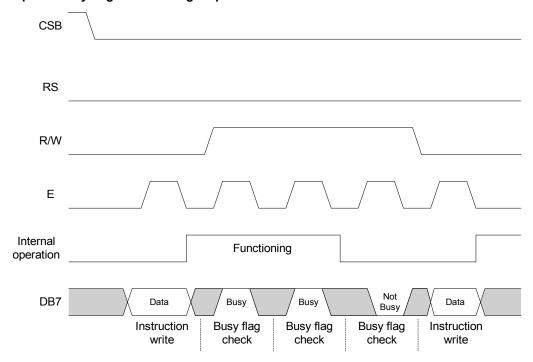

#### Serial interface

**Built-in Font Table**

# ST7032-0D (ITO option OPR1=0, OPR2=0)

|                | 002  |      |      |      |      |      |      | V    | -    | ٠,   | · ·  |              | -,   |      |      |      |

|----------------|------|------|------|------|------|------|------|------|------|------|------|--------------|------|------|------|------|

| b7-b4<br>b3-b0 | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 101 <b>1</b> | 1100 | 1101 | 1110 | 1111 |

| 0000           |      |      |      |      |      |      |      |      |      |      |      |              |      | ***  |      |      |

| 0001           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 0010           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 0011           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 0100           |      |      |      |      |      |      |      |      |      |      | •    |              |      |      |      |      |

| 0 <b>1</b> 01  |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 0110           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 0111           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 1000           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 1001           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 1010           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 1011           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      | ***  |

| 1100           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 1101           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 1110           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

| 1111           |      |      |      |      |      |      |      |      |      |      |      |              |      |      |      |      |

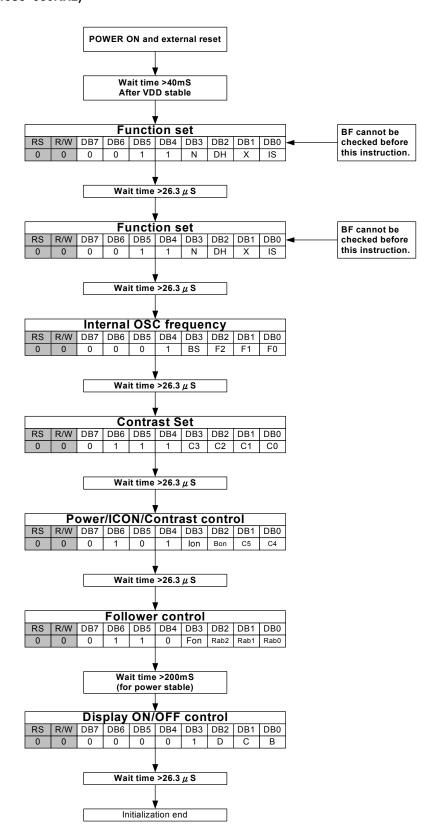

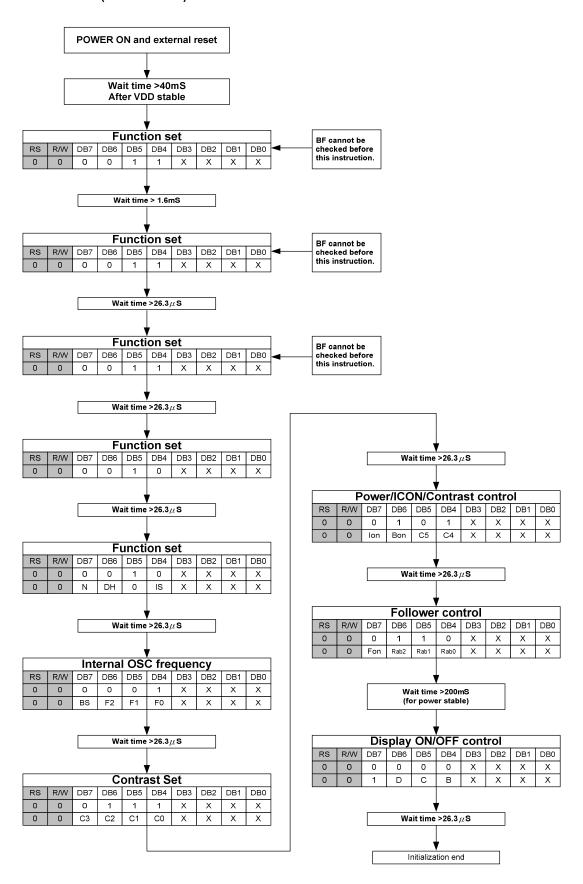

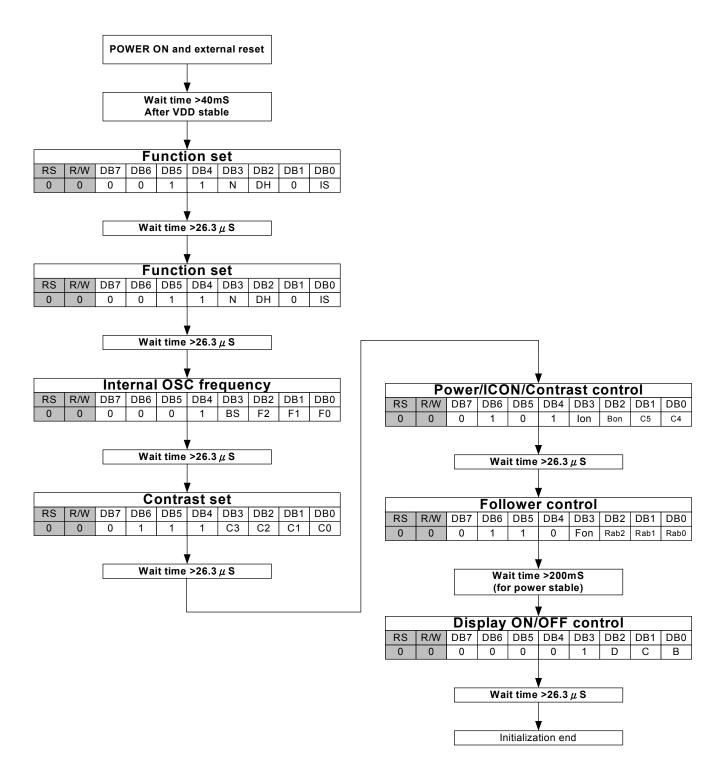

## **Example Initialization Program**

```

void init()

//initialize the LCD

P3 = 1;

P1 = 1;

RST = 0;

//RESET

delay(2);

RST = 1;

//end reset

delay(20);

Writecom(0x30);

//wake up

delay(2);

Call writecom(0x30);

//wake up

Call writecom(0x30);

//wake up

Call writecom(0x39);

//function set

Call writecom(0x14);

//internal osc frequency

Call writecom(0x56):

//power control

Call writecom(0x6D);

//follower control

Call writecom(0x70);

//contrast

Call writecom(0x0C);

//display on

Call writecom(0x06);

//entry mode

Call writecom(0x01);

//clear

delay(10);

void writecom(int d)

CS = 0;

//CS

RS = 0:

//A0 = Command

for(serialcounter = 1; serialcounter <= 8; serialcounter++) //send 8 bits

if((d\&0x80)==0x80)

//get only the MSB

//if 1, then SI=1

SI=1;

else

SI=0;

//if 0, then SI=0

d=(d<<1):

//shift data byte left

SCL = 0:

SCL = 1;

//SCL

SCL = 0;

CS = 1;

}

void writedata(int d)

CS = 0;

//CS

RS = 1;

//A0 = Data

for(serialcounter = 1; serialcounter <= 8; serialcounter++) //send 8 bits

if((d&0x80)==0x80)

//get only the MSB

//if 1, then SI=1

SI=1;

else

SI=0;

//if 0, then SI=0

d=(d<<1);

//shift data byte left

SCL = 0;

SCL = 1;

SCL = 0;

//SCL

CS = 1;

```

## **Quality Information**

| Test Item                                | Content of Test                                                                                                                 | Test Condition                                                                         | Note |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|

| High Temperature storage                 | Endurance test applying the high storage temperature for a long time.                                                           | +80°C , 48hrs                                                                          | 2    |

| Low Temperature storage                  | Endurance test applying the low storage temperature for a long time.                                                            | -30°C , 48hrs                                                                          | 1,2  |

| High Temperature<br>Operation            | Endurance test applying the electric stress (voltage & current) and the high thermal stress for a long time.                    | +70°C , 48hrs                                                                          | 2    |

| Low Temperature<br>Operation             | Endurance test applying the electric stress (voltage & current) and the low thermal stress for a long time.                     | -20°C , 48hrs                                                                          | 1,2  |

| High Temperature /<br>Humidity Operation | Endurance test applying the electric stress (voltage & current) and the high thermal with high humidity stress for a long time. | +40°C, 90% RH, 96hrs                                                                   | 1,2  |

| Thermal Shock resistance                 | Endurance test applying the electric stress (voltage & current) during a cycle of low and high thermal stress.                  | 0°C,30min -> 25°C,5min -> 50°C,30min = 1 cycle 10 cycles                               |      |

| Vibration test                           | Endurance test applying vibration to simulate transportation and use.                                                           | 10-55Hz , 15mm amplitude.<br>60 sec in each of 3 directions<br>X,Y,Z<br>For 15 minutes | 3    |

| Static electricity test                  | Endurance test applying electric static discharge.                                                                              | VS=800V, RS=1.5k $\Omega$ , CS=100pF<br>One time                                       |      |

**Note 1:** No condensation to be observed.

**Note 2:** Conducted after 4 hours of storage at 25°C, 0%RH.

**Note 3:** Test performed on product itself, not inside a container.

## **Precautions for using LCDs/LCMs**

See Precautions at <a href="https://www.newhavendisplay.com/specs/precautions.pdf">www.newhavendisplay.com/specs/precautions.pdf</a>

## **Warranty Information and Terms & Conditions**

http://www.newhavendisplay.com/index.php?main\_page=terms

# **Sitronix**

#### ST7032

#### Dot Matrix LCD Controller/Driver

#### **■** Features

- 5 x 8 dot matrix possible

- Low power operation support:

- -- 2.7 to 5.5V

- Range of LCD driver power

- -- 3.0 to 7.0V

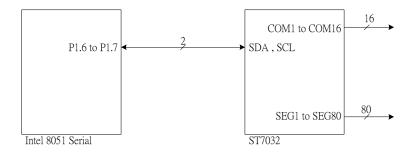

- 4-bit, 8-bit, serial MPU or 400kbits/s fast I<sup>2</sup>C-bus interface are available

- 80 x 8-bit display RAM (80 characters max.)

- 10,240-bit character generator ROM for a total of 256 character fonts(max)

- 64 x 8-bit character generator RAM(max)

- 16-common x 80-segment and 1-common x 80-segment ICON liquid crystal display driver

- 16 x 5 -bit ICON RAM(max)

- Wide range of instruction functions:

Display clear, cursor home, display on/off, cursor on/off, display character blink, cursor shift, display shift, double height font

- Automatic reset circuit that initializes the controller/driver after power on and external reset pin

- Internal oscillator(Frequency=540KHz) and external clock

- Built-in voltage booster and follower circuit (low power consumption)

- Com/Seg direction selectable

- Multi-selectable for CGRAM/CGROM size

- Instruction compatible to ST7066U

- Available in COG type

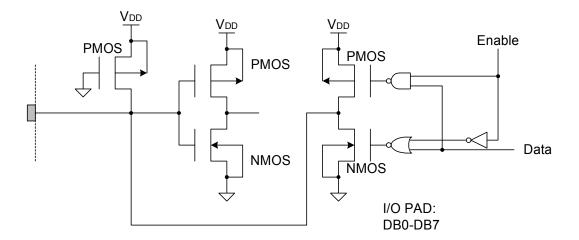

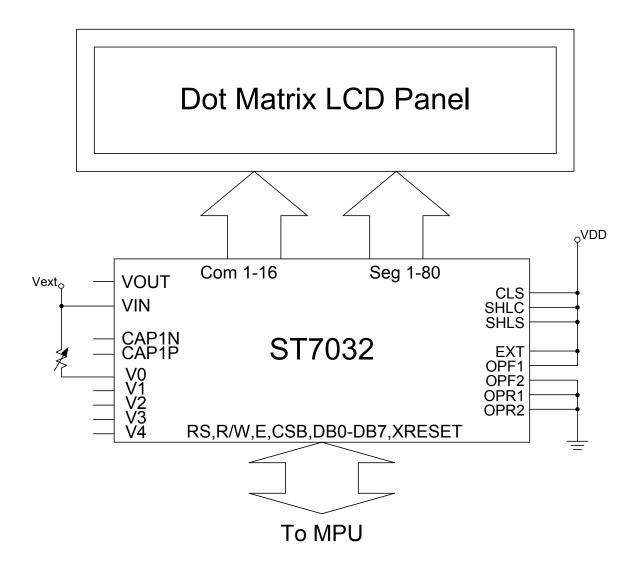

## **■** Description

The ST7032 dot-matrix liquid crystal display controller can display alphanumeric, Japanese kana characters, and symbols. It can be configured to drive a dot-matrix liquid crystal display under the control of a 4 / 8-bit with 6800-series or 8080-series, 3/4-line serial interface microprocessor. Since all the functions such as display RAM, character generator ROM/RAM and liquid crystal driver, required for driving a dot-matrix liquid crystal display are internally provided on one chip, a minimal system can be used with this controller/driver.

The ST7038 character generator ROM size is 256 5x8dot bits which can be used to generate 256 different character fonts (5x8dot).

The ST7032 is suitable for low voltage supply 2.7V to 5.5V) and is perfectly suitable for any portable product which is driven by the battery and requires low power consumption.

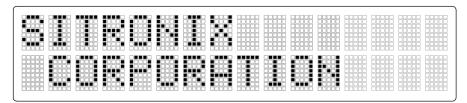

The ST7032 LCD driver consists of 17 common signal drivers and 80 segment signal drivers. The maximum display RAM size can be either 80 characters in 1-line display or 40 characters in 2-line display. A single ST7032 can display up to one 16-character line or two 16-character lines.

The ST7032 dot-matrix LCD driver does not need extra cascaded drivers.

| <b>Product Name</b> | Character generator<br>ROM Size | OPR1 | OPR2 | Support Character      |

|---------------------|---------------------------------|------|------|------------------------|

| ST7032-0D           | 256                             | 1    | 1    | English/Japan/European |

| ST7032  | 6800-4bit / 8bit interface<br>(without IIC interface) | G3<br> |

|---------|-------------------------------------------------------|--------|

| ST7032i | IIC interface                                         | BUS    |

|         | ST70:      | 32 Serial Specification Revision History                                                                                                                                                                                                                                                |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Version | Date       | Description                                                                                                                                                                                                                                                                             |

| 1.0     | 2003/3/24  | 1. Change "Version 0.1y-Preliminary" to "Version 1.0"  2. Modify Bias resistor value  3. Modify OSC frequency table  4. Adding Serial interface flow chart & example code  5. Adding "E" connection state for serial interface                                                          |

| 1.1     | 2003/8/27  | 1. Include ST7032i                                                                                                                                                                                                                                                                      |

| 1.2     | 2005/10/17 | <ol> <li>To modify Operating Temperature Range Ta=-30°C to 85°C</li> <li>To modify Storage Temperature Range Ta=-65°C to 150°C</li> <li>To modify the vlcd voltage Range 3.0v~7.0v</li> <li>To modify the limiting values -0.3v~+6.0v</li> <li>To add Chip Thickness: 480 um</li> </ol> |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

|         |            |                                                                                                                                                                                                                                                                                         |

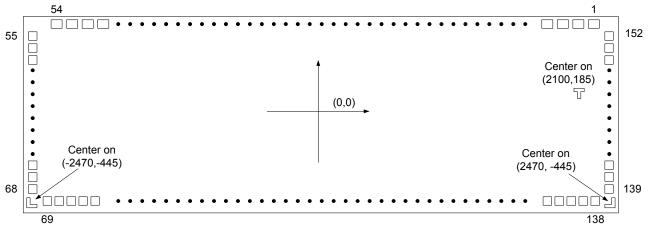

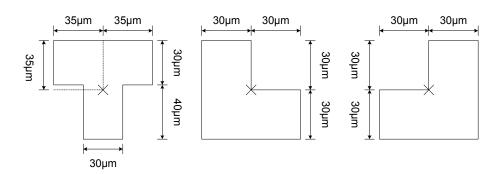

## **■** Pad Dimensions

> Chip Size: 5130.0 x 1080.0 μm

➤ Chip Thickness: 480µm

Bump Pitch : 62μm(min)

Bump Height : 17μm

Bump Size :

Pad No.1~54 : 54 x 97μm

Pad No.55~152 : 40 x 97μm

# ■ Pad Location Coordinates

|         |          | 1 000141 | 3.7   |  |  |

|---------|----------|----------|-------|--|--|

| Pad No. | Function | Х        | Y     |  |  |

| 1       | XRESET   | 2165.5   | 420.5 |  |  |

| 2       | OSC1     | 2089.5   | 420.5 |  |  |

| 3       | OSC2     | 2013.5   | 420.5 |  |  |

| 4       | RS       | 1937.5   | 420.5 |  |  |

| 5       | CSB      | 1861.5   | 420.5 |  |  |

| 6       | RW       | 1785.5   | 420.5 |  |  |

| 7       | Е        | 1709.5   | 420.5 |  |  |

| 8       | DB0      | 1633.5   | 420.5 |  |  |

| 9       | DB1      | 1557.5   | 420.5 |  |  |

| 10      | DB2      | 1481.5   | 420.5 |  |  |

| 11      | DB3      | 1405.5   | 420.5 |  |  |

| 12      | DB4      | 1329.5   | 420.5 |  |  |

| 13      | DB5      | 1253.5   | 420.5 |  |  |

| 14      | DB6      | 1177.5   | 420.5 |  |  |

| 15      | DB7      | 1101.5   | 420.5 |  |  |

| 16      | VSS      | 1025.5   | 420.5 |  |  |

| 17      | VSS      | 949.5    | 420.5 |  |  |

| 18      | VSS      | 873.5    | 420.5 |  |  |

| 19      | OPF1     | 797.5    | 420.5 |  |  |

| 20      | OPF2     | 721.5    | 420.5 |  |  |

| 21      | OPR1     | 645.5    | 420.5 |  |  |

| 22      | OPR2     | 569.5    | 420.5 |  |  |

| 23      | SHLC     | 493.5    | 420.5 |  |  |

| 24      | SHLS     | 417.5    | 420.5 |  |  |

| 25      | VDD      | 341.5    | 420.5 |  |  |

| 26      | VDD      | 265.5    | 420.5 |  |  |

| 27      | VDD      | 189.5    | 420.5 |  |  |

| 28      | VIN      | 113.5    | 420.5 |  |  |

| 29      | VIN      | 37.5     | 420.5 |  |  |

| 30      | TEST1    | -38.5    | 420.5 |  |  |

| 31      | TEST2    | -114.5   | 420.5 |  |  |

| 32      | VSS      | -190.5   | 420.5 |  |  |

| 33      | NC       | -266.5   | 420.5 |  |  |

| 34      | VOUT     | -342.5   | 420.5 |  |  |

| 35      | VOUT     | -418.5   | 420.5 |  |  |

| 36      | PSB      | -494.5   | 420.5 |  |  |

| 37      | VSS      | -570.5   | 420.5 |  |  |

| 38      | PSI2B    | -646.5   | 420.5 |  |  |

| 39      | CAP1P    | -722.5   | 420.5 |  |  |

| 40      | CAP1P    | -798.5   | 420.5 |  |  |

| Pad No. | Function | X       | Υ      |

|---------|----------|---------|--------|

| 41      | EXT      | -874.5  | 420.5  |

| 42      | VSS      | -950.5  | 420.5  |

| 43      | CLS      | -1026.5 | 420.5  |

| 44      | CAP1N    | -1102.5 | 420.5  |

| 45      | CAP1N    | -1178.5 | 420.5  |

| 46      | VOUT     | -1254.5 | 420.5  |

| 47      | VOUT     | -1330.5 | 420.5  |

| 48      | V0       | -1406.5 | 420.5  |

| 49      | V0       | -1482.5 | 420.5  |

| 50      | V1       | -1558.5 | 420.5  |

| 51      | V2       | -1634.5 | 420.5  |

| 52      | V3       | -1710.5 | 420.5  |

| 53      | V4       | -1786.5 | 420.5  |

| 54      | NC       | -1862.5 | 420.5  |

| 55      | COM[8]   | -2445.5 | 423    |

| 56      | COM[7]   | -2445.5 | 361    |

| 57      | COM[6]   | -2445.5 | 299    |

| 58      | COM[5]   | -2445.5 | 237    |

| 59      | COM[4]   | -2445.5 | 175    |

| 60      | COM[3]   | -2445.5 | 113    |

| 61      | COM[2]   | -2445.5 | 51     |

| 62      | COM[1]   | -2445.5 | -11    |

| 63      | COMI1    | -2445.5 | -73    |

| 64      | SEG[1]   | -2445.5 | -135   |

| 65      | SEG[2]   | -2445.5 | -197   |

| 66      | SEG[3]   | -2445.5 | -259   |

| 67      | SEG[4]   | -2445.5 | -321   |

| 68      | SEG[5]   | -2445.5 | -383   |

| 69      | SEG[6]   | -2130.5 | -420.5 |

| 70      | SEG[7]   | -2068.5 | -420.5 |

| 71      | SEG[8]   | -2006.5 | -420.5 |

| 72      | SEG[9]   | -1944.5 | -420.5 |

| 73      | SEG[10]  | -1882.5 | -420.5 |

| 74      | SEG[11]  | -1820.5 | -420.5 |

| 75      | SEG[12]  | -1758.5 | -420.5 |

| 76      | SEG[13]  | -1696.5 | -420.5 |

| 77      | SEG[14]  | -1634.5 | -420.5 |

| 78      | SEG[15]  | -1572.5 | -420.5 |

| 79      | SEG[16]  | -1510.5 | -420.5 |

| 80      | SEG[17]  | -1448.5 | -420.5 |

| Pad No. | Function | Х       | Υ      |

|---------|----------|---------|--------|

| 81      | SEG[18]  | -1386.5 | -420.5 |

| 82      | SEG[19]  | -1324.5 | -420.5 |

| 83      | SEG[20]  | -1262.5 | -420.5 |

| 84      | SEG[21]  | -1200.5 | -420.5 |

| 85      | SEG[22]  | -1138.5 | -420.5 |

| 86      | SEG[23]  | -1076.5 | -420.5 |

| 87      | SEG[24]  | -1014.5 | -420.5 |

| 88      | SEG[25]  | -952.5  | -420.5 |

| 89      | SEG[26]  | -890.5  | -420.5 |

| 90      | SEG[27]  | -828.5  | -420.5 |

| 91      | SEG[28]  | -766.5  | -420.5 |

| 92      | SEG[29]  | -704.5  | -420.5 |

| 93      | SEG[30]  | -642.5  | -420.5 |

| 94      | SEG[31]  | -580.5  | -420.5 |

| 95      | SEG[32]  | -518.5  | -420.5 |

| 96      | SEG[33]  | -456.5  | -420.5 |

| 97      | SEG[34]  | -394.5  | -420.5 |

| 98      | SEG[35]  | -332.5  | -420.5 |

| 99      | SEG[36]  | -270.5  | -420.5 |

| 100     | SEG[37]  | -208.5  | -420.5 |

| 101     | SEG[38]  | -146.5  | -420.5 |

| 102     | SEG[39]  | -84.5   | -420.5 |

| 103     | SEG[40]  | -22.5   | -420.5 |

| 104     | SEG[41]  | 39.5    | -420.5 |

| 105     | SEG[42]  | 101.5   | -420.5 |

| 106     | SEG[43]  | 163.5   | -420.5 |

| 107     | SEG[44]  | 225.5   | -420.5 |

| 108     | SEG[45]  | 287.5   | -420.5 |

| 109     | SEG[46]  | 349.5   | -420.5 |

| 110     | SEG[47]  | 411.5   | -420.5 |

| 111     | SEG[48]  | 473.5   | -420.5 |

| 112     | SEG[49]  | 535.5   | -420.5 |

| 113     | SEG[50]  | 597.5   | -420.5 |

| 114     | SEG[51]  | 659.5   | -420.5 |

| 115     | SEG[52]  | 721.5   | -420.5 |

| 116     | SEG[53]  | 783.5   | -420.5 |

| 117     | SEG[54]  | 845.5   | -420.5 |

| 118     | SEG[55]  | 907.5   | -420.5 |

| 119     | SEG[56]  | 969.5   | -420.5 |

| 120     | SEG[57]  | 1031.5  | -420.5 |

| Pad No. | Function | X      | Υ      |  |  |

|---------|----------|--------|--------|--|--|

| 121     | SEG[58]  | 1093.5 | -420.5 |  |  |

| 122     | SEG[59]  | 1155.5 | -420.5 |  |  |

| 123     | SEG[60]  | 1217.5 | -420.5 |  |  |

| 124     | SEG[61]  | 1279.5 | -420.5 |  |  |

| 125     | SEG[62]  | 1341.5 | -420.5 |  |  |

| 126     | SEG[63]  | 1403.5 | -420.5 |  |  |

| 127     | SEG[64]  | 1465.5 | -420.5 |  |  |

| 128     | SEG[65]  | 1527.5 | -420.5 |  |  |

| 129     | SEG[66]  | 1589.5 | -420.5 |  |  |

| 130     | SEG[67]  | 1651.5 | -420.5 |  |  |

| 131     | SEG[68]  | 1713.5 | -420.5 |  |  |

| 132     | SEG[69]  | 1775.5 | -420.5 |  |  |

| 133     | SEG[70]  | 1837.5 | -420.5 |  |  |

| 134     | SEG[71]  | 1899.5 | -420.5 |  |  |

| 135     | SEG[72]  | 1961.5 | -420.5 |  |  |

| 136     | SEG[73]  | 2023.5 | -420.5 |  |  |

| 137     | SEG[74]  | 2085.5 | -420.5 |  |  |

| 138     | SEG[75]  | 2147.5 | -420.5 |  |  |

| 139     | SEG[76]  | 2445.5 | -383   |  |  |

| 140     | SEG[77]  | 2445.5 | -321   |  |  |

| 141     | SEG[78]  | 2445.5 | -259   |  |  |

| 142     | SEG[79]  | 2445.5 | -197   |  |  |

| 143     | SEG[80]  | 2445.5 | -135   |  |  |

| 144     | COM[9]   | 2445.5 | -73    |  |  |

| 145     | COM[10]  | 2445.5 | -11    |  |  |

| 146     | COM[11]  | 2445.5 | 51     |  |  |

| 147     | COM[12]  | 2445.5 | 113    |  |  |

| 148     | COM[13]  | 2445.5 | 175    |  |  |

| 149     | COM[14]  | 2445.5 | 237    |  |  |

| 150     | COM[15]  | 2445.5 | 299    |  |  |

| 151     | COM[16]  | 2445.5 | 361    |  |  |

| 152     | COMI2    | 2445.5 | 423    |  |  |

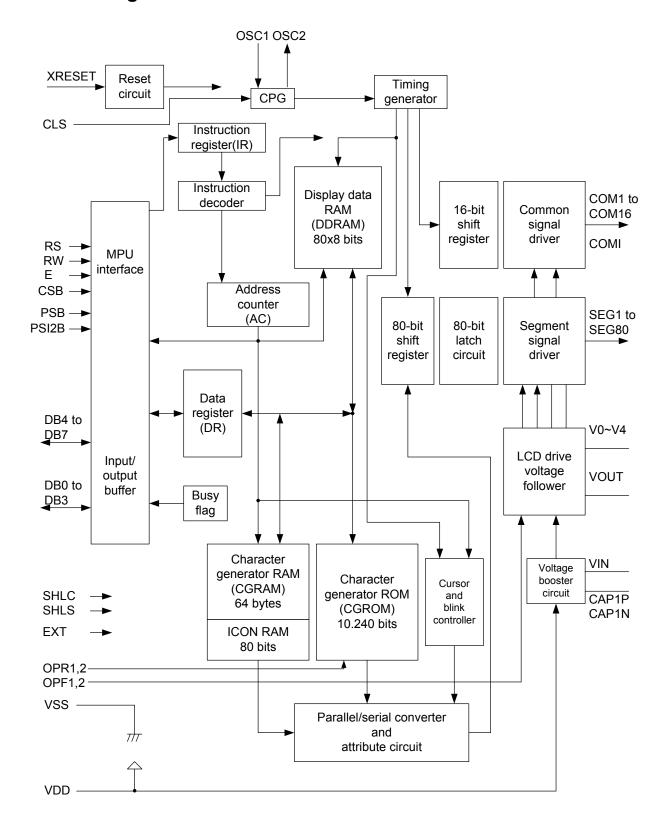

## **■** Block Diagram

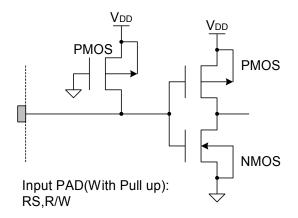

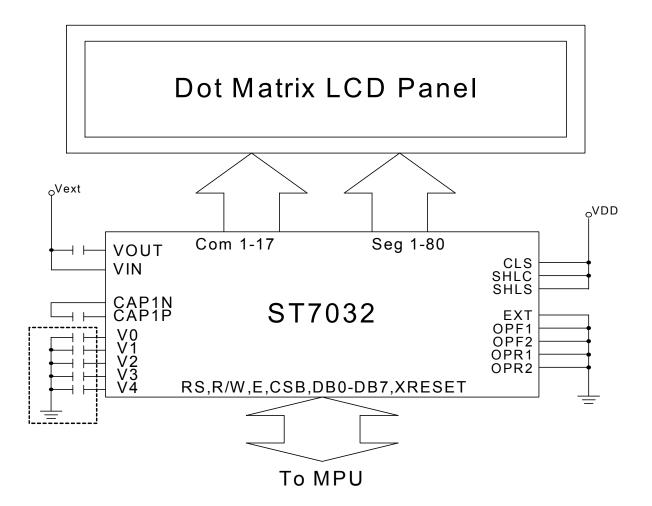

## **■** Pin Function

| Name       | Number | I/O | Interfaced with | th Function                                                                                                                                                                    |              |                                            |                                           |  |  |  |  |

|------------|--------|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------|-------------------------------------------|--|--|--|--|

| Name       | Number | 1/0 | interraceu with | External reset pin. Only if the power on reset used, the                                                                                                                       |              |                                            |                                           |  |  |  |  |

|            | _      |     |                 |                                                                                                                                                                                | •            |                                            | reset usea, the                           |  |  |  |  |

| XRESET     | 1      | I   | MPU             | Low activ                                                                                                                                                                      | -            | e fixed to VDD.                            |                                           |  |  |  |  |

|            |        | 1   |                 |                                                                                                                                                                                |              |                                            |                                           |  |  |  |  |

|            |        |     |                 | Select registers. 0: Instruction register (for write)                                                                                                                          |              |                                            |                                           |  |  |  |  |

| RS         | 1      | I   | MPU             |                                                                                                                                                                                | _            | ess counter (for read                      | 1)                                        |  |  |  |  |

|            |        |     |                 | -                                                                                                                                                                              | -            | write and read)                            | -,                                        |  |  |  |  |

|            |        |     |                 |                                                                                                                                                                                |              | (In parallel mode).                        |                                           |  |  |  |  |

| R/W        | 1      | l i | MPU             | 0: Write                                                                                                                                                                       |              | ( p                                        |                                           |  |  |  |  |

| 10.44      | '      | '   |                 | 1: Read                                                                                                                                                                        |              |                                            |                                           |  |  |  |  |

| _          | _      | T.  |                 | Starts dat                                                                                                                                                                     | a read/wri   | te. ( <u>"E" must connec</u>               | t to "VDD" when                           |  |  |  |  |

| E          | 1      | I   | MPU             |                                                                                                                                                                                | rface is se  |                                            |                                           |  |  |  |  |

|            |        |     |                 | Chip sele                                                                                                                                                                      | ct in parall | el mode and serial ir                      | nterface (Low                             |  |  |  |  |

| CSB        | 1      | 1   | MPU             | active).W                                                                                                                                                                      | hen the C    | SB in falling edge sta                     | ate (in serial                            |  |  |  |  |

|            |        |     |                 |                                                                                                                                                                                |              |                                            |                                           |  |  |  |  |

|            |        |     |                 | interface), the shift register and the clock counter are rese Four high order bi-directional data bus pins. Used for data transfer and receive between the MPU and the ST7032. |              |                                            |                                           |  |  |  |  |

|            |        |     |                 |                                                                                                                                                                                |              |                                            |                                           |  |  |  |  |

|            |        |     | MPU             |                                                                                                                                                                                |              | s a busy flag. In seria                    |                                           |  |  |  |  |

| DB4 to DB7 | 4      | 1/0 |                 |                                                                                                                                                                                |              | a), DB6 is SCL (seria                      |                                           |  |  |  |  |

| 55110551   |        |     |                 | In I <sup>2</sup> C interface DB7 (SDA) is input data and DB6 (SCL) is                                                                                                         |              |                                            |                                           |  |  |  |  |

|            |        |     |                 | clock input.  SDA and SCL must connect to I <sup>2</sup> C bus (I <sup>2</sup> C bus is to connect                                                                             |              |                                            |                                           |  |  |  |  |

|            |        |     |                 | a resister between SDA/SCL and the power of I <sup>2</sup> C bus ).                                                                                                            |              |                                            |                                           |  |  |  |  |

|            |        | -   |                 |                                                                                                                                                                                |              | rectional data bus pi                      |                                           |  |  |  |  |

| DD0 4: DD0 | _      | 1/0 | MELL            |                                                                                                                                                                                |              | rectional data bus pi<br>between the MPU a |                                           |  |  |  |  |

| DB0 to DB3 | 4      | I/O | MPU             |                                                                                                                                                                                |              | used during 4-bit ope                      |                                           |  |  |  |  |

|            |        | -   |                 |                                                                                                                                                                                | instructio   |                                            | J. G. |  |  |  |  |

|            |        |     |                 |                                                                                                                                                                                |              | instruction(add contr                      | rast/ICON/double                          |  |  |  |  |

| Ext        | 1      | 1   | ITO option      |                                                                                                                                                                                |              | on instruction)                            |                                           |  |  |  |  |

|            |        | '   | 110 00000       | 1:disable extension instruction(compatible to ST7066U, but                                                                                                                     |              |                                            |                                           |  |  |  |  |

|            |        | 1   |                 |                                                                                                                                                                                | k11dot fon   |                                            |                                           |  |  |  |  |

|            |        |     |                 | Interface                                                                                                                                                                      | selection    |                                            |                                           |  |  |  |  |

|            |        |     |                 | 0:serial m                                                                                                                                                                     |              |                                            |                                           |  |  |  |  |

| PSB        | 1      | 1   | MPU             | -                                                                                                                                                                              |              | o "VDD" when serial                        | mode is selected.)                        |  |  |  |  |

|            |        |     |                 |                                                                                                                                                                                | mode(4/8     |                                            |                                           |  |  |  |  |

|            |        |     |                 | In I'C inte                                                                                                                                                                    | rface PSE    | must connect to VE                         | DD                                        |  |  |  |  |

|            |        |     |                 | PSB                                                                                                                                                                            | PSI2B        | Interface                                  | ]                                         |  |  |  |  |

|            |        |     |                 | 0                                                                                                                                                                              | 0            | No use                                     |                                           |  |  |  |  |

| PSI2B      | 1      | 1   | ITO option      | 0                                                                                                                                                                              | 1            | SI4                                        |                                           |  |  |  |  |

|            |        |     | ·               | 1                                                                                                                                                                              | 0            | SI2 (I <sup>2</sup> C )                    |                                           |  |  |  |  |

|            |        |     |                 | 1                                                                                                                                                                              | 1            | Parallel 68                                |                                           |  |  |  |  |

|            |        |     |                 |                                                                                                                                                                                | generato     |                                            |                                           |  |  |  |  |

|            |        |     |                 | OPR1                                                                                                                                                                           | OPR2         | CGROM                                      | CGRAM                                     |  |  |  |  |

| OPR1,      |        |     |                 | 0                                                                                                                                                                              | 0            | 240                                        | 8                                         |  |  |  |  |

| OPR2       | 2      | I   | ITO option      | 0                                                                                                                                                                              | 1            | 250                                        | 6                                         |  |  |  |  |

| 0.112      |        |     |                 | 1                                                                                                                                                                              | 0            | 248                                        | 8                                         |  |  |  |  |

|            |        |     |                 | 1                                                                                                                                                                              | 1            | 256                                        | 0                                         |  |  |  |  |

| 1          | l .    |     | 1               | <u> </u>                                                                                                                                                                       |              |                                            |                                           |  |  |  |  |

| Name             | Number | I/O | Interfaced with | Function                                                                                                                                    |  |  |  |  |  |  |

|------------------|--------|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SHLC             | 1      | I   | ITO option      | Common signals direction select: 0:Com1~16←Row address 15~0(Invert) 1:Com1~16←Row address 0~15(Normal)                                      |  |  |  |  |  |  |

| SHLS             | 1      | I   | ITO option      | Segment signals direction select:  0:Seg1~80 ←Column address 79~0(Invert)  1:Seg1~80 ←Column address 0~79(Normal)                           |  |  |  |  |  |  |

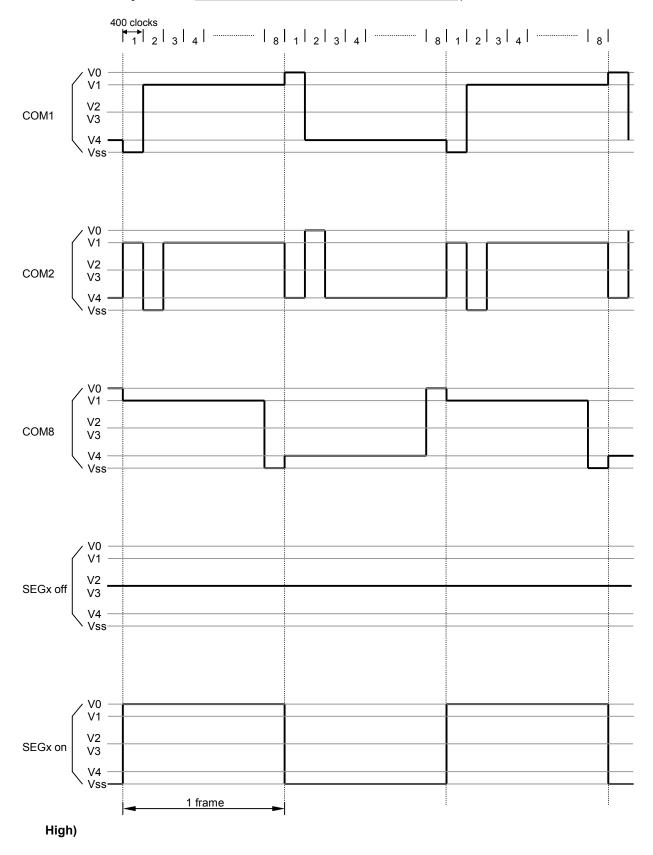

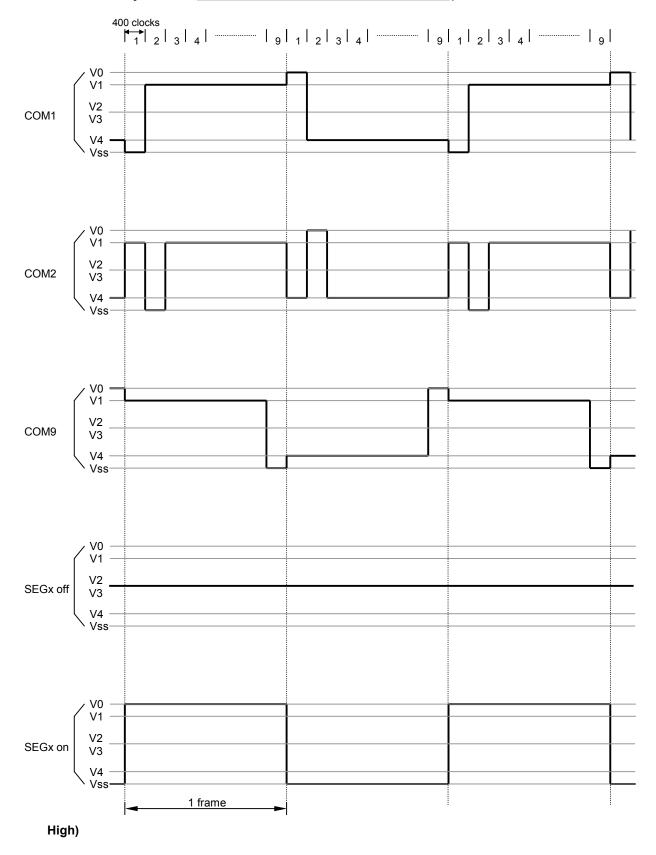

| COM1 to          | 16     | 0   | LCD             | Common signals that are not used are changed to non-selection waveform. COM9 to COM16 are non-selection waveforms at 1/8 or 1/9 duty factor |  |  |  |  |  |  |

| COMI             | 2      | 0   | LCD             | ICON common signals                                                                                                                         |  |  |  |  |  |  |

| SEG1 to<br>SEG80 | 80     | 0   | LCD             | Segment signals                                                                                                                             |  |  |  |  |  |  |

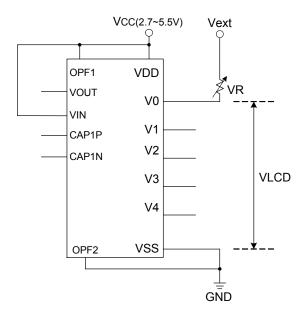

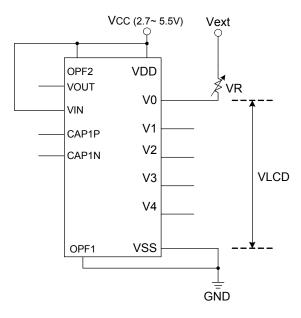

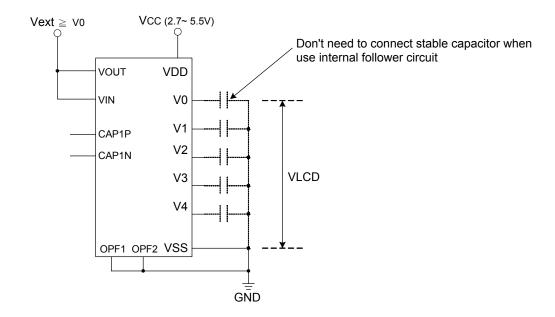

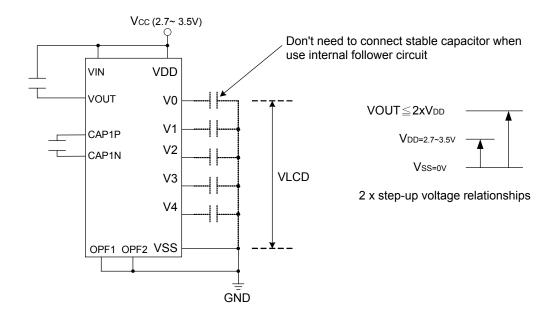

| OPF1<br>OPF2     | 2      | 1   | ITO option      |                                                                                                                                             |  |  |  |  |  |  |

| CAP1P            | 1      | -   | Power supply    | For voltage booster circuit(VDD-VSS)                                                                                                        |  |  |  |  |  |  |

| CAP1N            | 1      | -   | Power supply    | External capacitor about 0.1u~4.7uf                                                                                                         |  |  |  |  |  |  |

| VIN              | 1      | -   | Power supply    | Input the voltage to booster                                                                                                                |  |  |  |  |  |  |

| VOUT             | 1      | -   | Power supply    | DC/DC voltage converter. Connect a capacitor between this terminal and VIN when the built-in booster is used.                               |  |  |  |  |  |  |

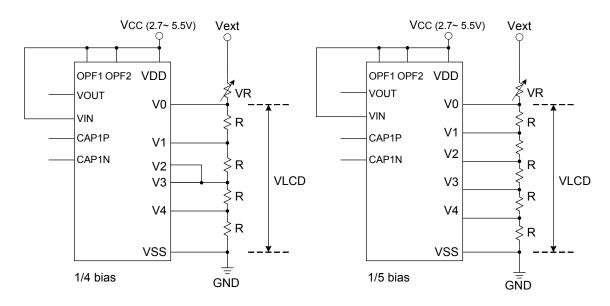

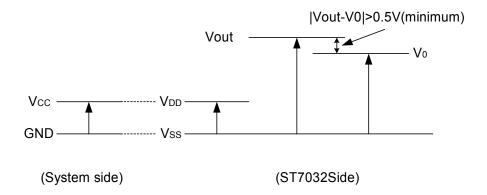

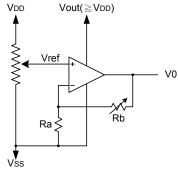

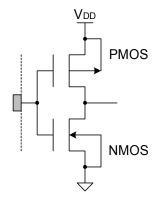

| V0 to V4         | 5      | -   | Power supply    | Power supply for LCD drive<br>V0-Vss = 7V (Max)<br>Built-in/external Voltage follower circuit                                               |  |  |  |  |  |  |

| VDD<br>VSS       | 2      | -   | Power supply    | VDD: 2.7V to 5.5V, VSS: 0V                                                                                                                  |  |  |  |  |  |  |

| CLS              |        | 1   | ITO option      | Internal/External oscillation select 0:external clock 1:internal oscillation                                                                |  |  |  |  |  |  |

| OSC1<br>OSC2     | 2      | I/O | Oscillation     | When the pin input is an external clock, it must be input to OSC1.                                                                          |  |  |  |  |  |  |

| TEST1,2          | 2      | I/O | Test pin        | TEST1,2 must connect to VDD.                                                                                                                |  |  |  |  |  |  |

**■ EXT** option pin difference table

|                      | ST7066U normal mode (EXT=1)                                                              | Extension mode (EXT=0)                                                                          |

|----------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Booster              | Always OFF                                                                               | ON/OFF control by instruction                                                                   |

| Bias (V0~V4)         | Can't use the follower circuit Only use external resistor or internal resistor(1/5 bias) | Follower or internal/external resistor selectable                                               |

| Contrast adjust      | Control by external VR                                                                   | Control by instruction with follower     Control by external VR with internal/external resistor |

| ICON RAM             | Can't be use                                                                             | RAM size has 80 bit width (S1~S80).                                                             |

| Instruction          | Control normal instruction similar to ST7066U.                                           | Control extension instruction for low power consumption.                                        |

| Double height font   | Only 5x8 font                                                                            | Can set 5x8 or 5x16 font                                                                        |

| OSC frequency adjust | Only adjust by external clock.                                                           | Can set OSC frequency by instruction set.                                                       |

## **■** Function Description

#### System Interface

This chip has all four kinds of interface type with MPU: 4-bit bus, 8-bit bus, serial and fast  $^{\circ}$ C interface. 4-bit bus or 8-bit bus is selected by DL bit in the instruction register.

During read or write operation, two 8-bit registers are used. One is data register (DR); the other is instruction register (IR).

The data register (DR) is used as temporary data storage place for being written into or read from DDRAM/CGRAM/ICON RAM, target RAM is selected by RAM address setting instruction. Each internal operation, reading from or writing into RAM, is done automatically. So to speak, after MPU reads DR data, the data in the next DDRAM/CGRAM/ICON RAM address is transferred into DR automatically. Also after MPU writes data to DR, the data in DR is transferred into DDRAM/CGRAM/ICON RAM automatically.

The Instruction register (IR) is used only to store instruction code transferred from MPU. MPU cannot use it to read instruction data.

Using RS input pin to select command or data in 4-bit/8-bit bus mode.

| RS | R/W | Operation                                                |  |  |  |  |  |  |  |  |  |  |  |  |

|----|-----|----------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|

| т  | т   | Instruction Write operation (MPU writes Instruction code |  |  |  |  |  |  |  |  |  |  |  |  |

| П  | П   | into IR)                                                 |  |  |  |  |  |  |  |  |  |  |  |  |

| L  | Н   | Read Busy Flag(DB7) and address counter (DB0 ~ DB6)      |  |  |  |  |  |  |  |  |  |  |  |  |

| Н  | L   | Data Write operation (MPU writes data into DR)           |  |  |  |  |  |  |  |  |  |  |  |  |

| Н  | Н   | Data Read operation (MPU reads data from DR)             |  |  |  |  |  |  |  |  |  |  |  |  |

Table 1. Various kinds of operations according to RS and R/W bits.

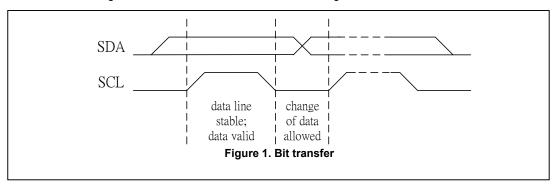

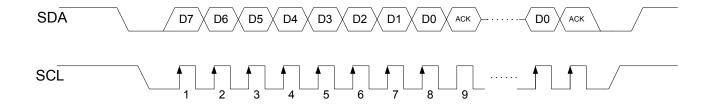

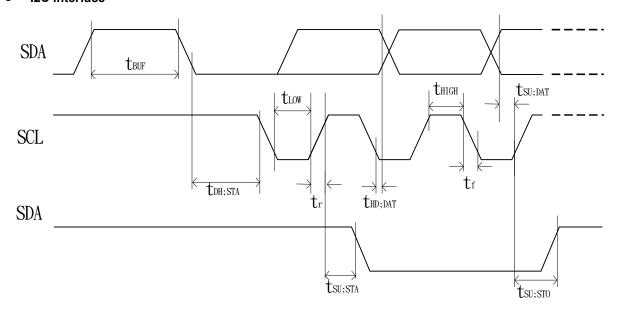

#### I<sup>2</sup>C interface

It just only could write Data or Instruction to ST7032 by the IIC Interface. It could not read Data or Instruction from ST7032 (except Acknowledge signal).

SCL: serial clock input SDA: serial data input

Slaver address could only set to 0111110, no other slaver address could be set

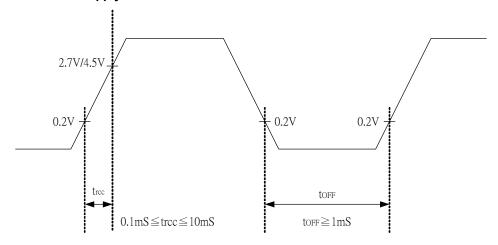

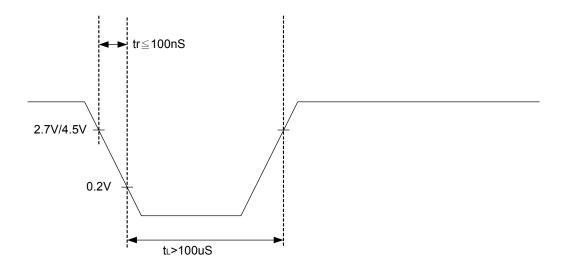

The I<sup>2</sup>C interface send RAM data and executes the commands sent via the I<sup>2</sup>C Interface. It could send data bit to the RAM. The I<sup>2</sup>C Interface is two-line communication between different ICs or modules. The two lines are a Serial Data line (SDA) and a Serial Clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor. Data transfer may be initiated only when the bus is not busy.

#### **BIT TRANSFER**

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse because changes in the data line at this time will be interpreted as a control signal. Bit transfer is illustrated in Fig.1.

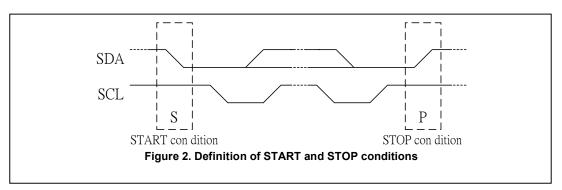

#### START AND STOP CONDITIONS

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P). The START and STOP conditions are illustrated in Fig.2.

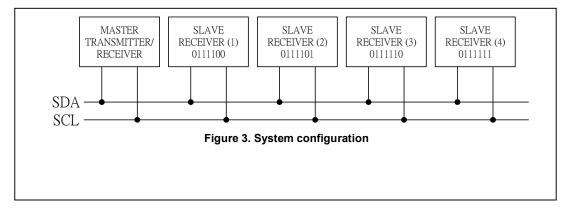

#### **SYSTEM CONFIGURATION**

The system configuration is illustrated in Fig.3.

- · Transmitter: the device, which sends the data to the bus

- · Master: the device, which initiates a transfer, generates clock signals and terminates a transfer

- · Slave: the device addressed by a master

- · Multi-Master: more than one master can attempt to control the bus at the same time without corrupting the message

- · Arbitration: procedure to ensure that, if more than one master simultaneously tries to control the bus, only one is allowed to do so and the message is not corrupted

- · Synchronization: procedure to synchronize the clock signals of two or more devices.

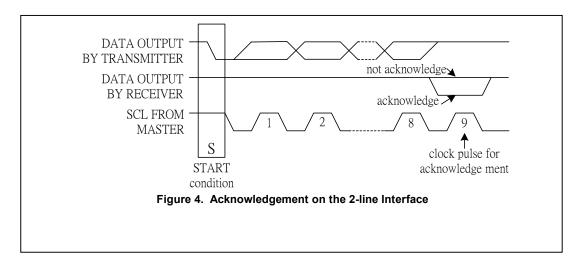

#### **ACKNOWLEDGE**

#### Acknowledge is not Busy Flag in I2C interface.

Each byte of eight bits is followed by an acknowledge bit. The acknowledge bit is a HIGH signal put on the bus by the transmitter during which time the master generates an extra acknowledge related clock pulse. A slave receiver which is addressed must generate an acknowledge after the reception of each byte. A master receiver must also generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges must pull-down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse (set-up and hold times must be taken into consideration). A master receiver must signal an end-of-data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a STOP condition. Acknowledgement on the I<sup>2</sup>C Interface is illustrated in Fig.4.

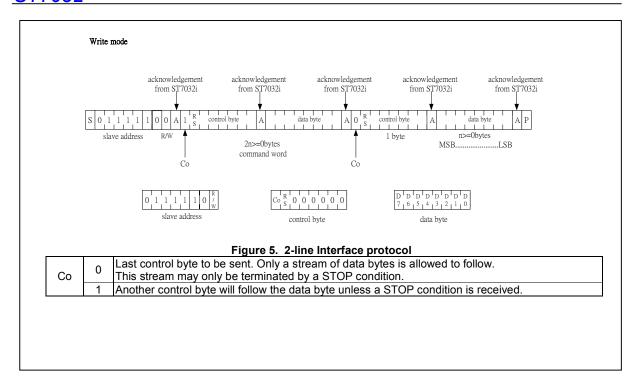

#### I<sup>2</sup>C Interface protocol

The ST7032 supports command, data write addressed slaves on the bus.

Before any data is transmitted on the I<sup>2</sup>C Interface, the device, which should respond, is addressed first. Only one 7-bit slave addresses (0111110) is reserved for the ST7032. The R/W is assigned to 0 for Write only. The I<sup>2</sup>C Interface protocol is illustrated in Fig.5.

The sequence is initiated with a START condition (S) from the I<sup>2</sup>C Interface master, which is followed by the slave address. All slaves with the corresponding address acknowledge in parallel, all the others will ignore the I<sup>2</sup>C Interface transfer. After acknowledgement, one or more command words follow which define the status of the addressed slaves.

A command word consists of a control byte, which defines Co and RS, plus a data byte.

The last control byte is tagged with a cleared most significant bit (i.e. the continuation bit Co). After a control byte with a cleared Co bit, only data bytes will follow. The state of the RS bit defines whether the data byte is interpreted as a command or as RAM data. All addressed slaves on the bus also acknowledge the control and data bytes. After the last control byte, depending on the RS bit setting; either a series of display data bytes or command data bytes may follow. If the RS bit is set to logic 1, these display bytes are stored in the display RAM at the address specified by the data pointer. The data pointer is automatically updated and the data is directed to the intended ST7032i device. If the RS bit of the last control byte is set to logic 0, these command bytes will be decoded and the setting of the device will be changed according to the received commands. Only the addressed slave makes the acknowledgement after each byte. At the end of the transmission the I<sup>2</sup>C INTERFACE-bus master issues a STOP condition (P).

During write operation, two 8-bit registers are used. One is data register (DR), the other is instruction register (IR).

The data register (DR) is used as temporary data storage place for being written into DDRAM/CGRAM/ICON RAM, target RAM is selected by RAM address setting instruction. Each internal operation, writing into RAM, is done automatically. So to speak, after MPU writes data to DR, the data in DR is transferred into DDRAM/CGRAM/ICON RAM automatically.

The Instruction register (IR) is used only to store instruction code transferred from MPU. MPU cannot use it to read instruction data.

To select register, use RS input in I<sup>2</sup>C interface.

| RS | R/W  | Operation                                                            |  |  |  |  |  |  |  |  |  |  |  |  |  |

|----|------|----------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|

| L  | l li | Instruction Write operation (MPU writes Instruction code into IR) $$ |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Н  | L    | Data Write operation (MPU writes data into DR)                       |  |  |  |  |  |  |  |  |  |  |  |  |  |

Table 2. Various kinds of operations according to RS and R/W bits.

#### Busy Flag (BF)

When BF = "High", it indicates that the internal operation is being processed. So during this time the next instruction cannot be accepted. BF can be read, when RS = Low and R/W = High (Read Instruction Operation), through DB7 port. Before executing the next instruction, be sure that BF is not High.

#### Address Counter (AC)

Address Counter (AC) stores DDRAM/CGRAM/ICON RAM address, transferred from IR.

After writing into (reading from) DDRAM/CGRAM/ICON RAM, AC is automatically increased (decreased) by 1.

When RS = "Low" and R/W = "High", AC can be read through DB0 ~ DB6 ports.

#### Display Data RAM (DDRAM)

Display data RAM (DDRAM) stores display data represented in 8-bit character codes. Its extended capacity is 80 x 8 bits, or 80 characters. The area in display data RAM (DDRAM) that is not used for display can be used as general data RAM. See Figure 7 for the relationships between DDRAM addresses and positions on the liquid crystal display.

The DDRAM address (ADD) is set in the address counter (AC)as hexadecimal.

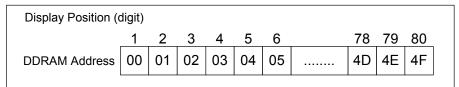

#### 1-line display (N = 0) (Figure 8)

When there are fewer than 80 display characters, the display begins at the head position. For example, if using only the ST7032, 16 characters are displayed. See Figure 8.

When the display shift operation is performed, the DDRAM address shifts. See Figure 9.

Figure 7. DDRAM Address

Figure 8. 1-Line Display

Figure 9. 1-Line by 16-Character Display Example

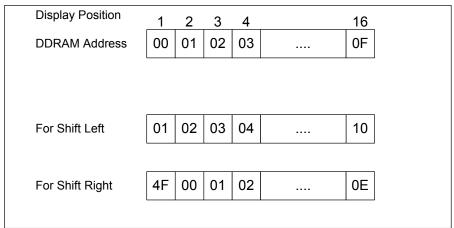

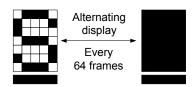

#### 2-line display (N = 1) (Figure 10)

Case 1: When the number of display characters is less than 40  $_{\cdot}$  2 lines, the two lines are displayed from the head. Note that the first line end address and the second line start address are not consecutive. See Figure 10.

Figure 10. 2-Line Display

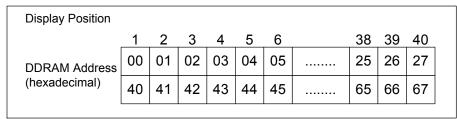

Case 2: For a 16-character \_ 2-line display See Figure 11. When display shift operation is performed, the DDRAM address shifts. See Figure 11.

| Display<br>Position | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| DDRAM               | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 80 | 09 | 0A | 0B | 0C | 0D | 0E | 0F |

| Address             | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F |

|                     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| For Shift           | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 80 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | 10 |

| Left                | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F | 50 |

|                     |    | 1  |    |    |    |    |    |    | 1  |    |    | 1  | 1  |    |    |    |

| For Shift           | 27 | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 80 | 09 | 0A | 0B | 0C | 0D | 0E |

| Right               | 67 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E |

|                     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

Figure 11. 2-Line by 16-Character Display Example

#### Character Generator ROM (CGROM)

The character generator ROM generates 5 x 8 dot character patterns from 8-bit character codes. It can generate 240/250/248/256 5 x 8 dot character patterns (select by OPR1/2 ITO pin). User-defined character patterns are also available by mask-programmed ROM.

#### Character Generator RAM (CGRAM)

In the character generator RAM, the user can rewrite character patterns by program. For 5 x 8 dots, eight character patterns can be written.

Write into DDRAM the character codes at the addresses shown as the left column of Table 3 to show the character patterns stored in CGRAM.

See Table 4 for the relationship between CGRAM addresses and data and display patterns. Areas that are not used for display can be used as general data RAM.

#### ICON RAM

In the ICON RAM, the user can rewrite icon pattern by program.

There are totally 80 dots for icon can be written.

See Table 5 for the relationship between ICON RAM address and data and the display patterns.

#### Timing Generation Circuit

The timing generation circuit generates timing signals for the operation of internal circuits such as DDRAM, CGROM and CGRAM. RAM read timing for display and internal operation timing by MPU access are generated separately to avoid interfering with each other. Therefore, when writing data to DDRAM, for example, there will be no undesirable interference, such as flickering, in areas other than the display area.(In I<sup>2</sup>C interface the reading function is invalid.)

#### LCD Driver Circuit

LCD Driver circuit has 17 common and 80 segment signals for LCD driving. Data from CGRAM/CGROM/ICON is transferred to 80 bit segment latch serially, and then it is stored to 80 bit shift latch. When each common is selected by 17 bit common register, segment data also output through segment driver from 80 bit segment latch.

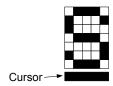

#### Cursor/Blink Control Circuit

It can generate the cursor or blink in the cursor/blink control circuit. The cursor or the blink appears in the digit at the display data RAM address set in the address counter.

Table 3. Correspondence between Character Codes and Character Patterns

## ST7032-0D (ITO option OPR1=1, OPR2=1)

| 67-64<br>63-60 | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

|----------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| 0000           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0001           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0010           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0011           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0100           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0101           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0110           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0111           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1000           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1001           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1010           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1011           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1100           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1101           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1110           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1111           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

|    |    |    |    | er (<br>M D |    |    |    |    |    |    | RAN<br>res |    |    |    |    | ara<br>CG |    |    |    |    | }  |

|----|----|----|----|-------------|----|----|----|----|----|----|------------|----|----|----|----|-----------|----|----|----|----|----|

| b7 | b6 | b5 | b4 | b3          | b2 | b1 | b0 | b5 | b4 | b3 | b2         | b1 | b0 | b7 | b6 | b5        | b4 | b3 | b2 | b1 | b0 |

|    |    |    |    |             | 0  | 0  | 0  |    |    |    | 0          | 0  | 0  |    |    |           | 1  | 1  | 1  | 1  | 1  |

|    |    |    |    |             | 0  | 0  | 0  |    |    |    | 0          | 0  | 1  |    |    |           | 0  | 0  | 1  | 0  | 0  |

|    |    |    |    |             | 0  | 0  | 0  |    |    |    | 0          | 1  | 0  |    |    |           | 0  | 0  | 1  | 0  | 0  |

| 0  | 0  | 0  | 0  | _           | 0  | 0  | 0  | 0  | 0  | 0  | 0          | 1  | 1  | _  | _  | _         | 0  | 0  | 1  | 0  | 0  |

| ľ  |    | U  |    | 0           | 0  | 0  |    | U  | U  | 1  | 0          | 0  |    |    |    | 0         | 0  | 1  | 0  | 0  |    |

|    |    |    |    |             | 0  | 0  | 0  |    |    |    | 1          | 0  | 1  |    |    |           | 0  | 0  | 1  | 0  | 0  |

|    |    |    |    |             | 0  | 0  | 0  |    |    |    | 1          | 1  | 0  |    |    |           | 0  | 0  | 1  | 0  | 0  |

|    |    |    |    |             | 0  | 0  | 0  |    |    |    | 1          | 1  | 1  |    |    |           | 0  | 0  | 0  | 0  | 0  |