AD-A260 752

# INFLIGHT EVALUATION OF AN ACOUSTIC ORIENTATION INSTRUMENT

Dan D. Fulgham John L. Orr Brian Mikiten S FEB 1 7 1993 C

MacAulay Brown, Incorporated 3915 Germany Lane Dayton, OH 45431

Southeastern Center for Electrical Engineering Education 1101 Massachusetts Avenue St. Cloud, FL 34769

CREW SYSTEMS DIRECTORATE 2504 D Drive, Suite 1 Brooks Air Force Base, TX 78235-5104

December 1992

Interim Technical Report for Period 16 November 1987 - 30 April 1991

Approved for public release; distribution is unlimited.

93 2 16 041

AIR FORCE MATERIEL COMMAND BROOKS AIR FORCE BASE, TEXAS

# DISCLAIMER NOTICE

THIS DOCUMENT IS BEST QUALITY AVAILABLE. THE COPY FURNISHED TO DTIC CONTAINED A SIGNIFICANT NUMBER OF PAGES WHICH DO NOT REPRODUCE LEGIBLY.

# NOTICES

This technical report is published as received and has not been edited by the technical editing staff of the Armstrong Laboratory.

When Government drawings, specifications, or other data are used for any purpose other than in connection with a definitely Government-related procurement, the United States Government incurs no responsibility or any obligation whatsoever. The fact that the Government may have formulated or in any way supplied the said drawings, specifications, or other data, is not to be regarded by implication, or otherwise in any manner construed, as licensing the holder, or any other person or corporation; or as conveying any rights or permission to manufacture, use, or sell any patented invention that may in any way be related thereto.

The Office of Public Affairs has reviewed this report, and it is releasable to the National Technical Information Service, where it will be available to the general public, including foreign nationals.

This report has been reviewed and is approved for publication.

Kent K. Millingham

KENT K. GILLINGHAM, M.D., Ph.D. Project Scientist

RONALD C. HILL, Lt Col, USAF, BSC Chief, Flight Motion Effects Branch

RICHARD L. MILLER, Ph.D. Chief, Crew Technology Division

| وروار المراجلة |                |         |        |

|----------------|----------------|---------|--------|

| Accest         | on For         | /       |        |

| NTIS           | CRA&           | 6       |        |

| DTIC           | TAB            | Ū       |        |

| Unannounced    |                |         |        |

| Justitie       | cation         |         |        |

| By<br>Distrib  | ution #        |         |        |

| A              | vailabilit     | y Codes |        |

| Dist           | Avail a<br>Spe |         | ****** |

| - 1            |                | (10)    |        |

| $\Gamma H$     |                |         |        |

|                |                |         |        |

|                | 1              |         |        |

DTIC QUALITY INSPECTED 3

# REPORT DOCUMENTATION PAGE

Form Approved

÷

| 1. AGENCY USE ONLY Leave b   |                                         | REPORT TYPE AND DATES COVERED<br>Interim - 16 November 1987 – 30 April 1991                     |

|------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------|

| 4. TITLE AND SUBTITUE        | ustic Orientation Instrument            | C FUNDING NUM2EPS<br>C - F33615-87-C-0534<br>(Task 0002)<br>C - F33615-87-D-0609<br>(Task 0014) |

| 6 AUTHOR(S,                  | ۵٬۰۰۰٬۰۰۰٬۰۰۰٬۰۰۰٬۰۰۰٬۰۰۰٬۰۰۰٬۰۰۰٬۰۰۰٬۰ | PE - 61101F, 62202F                                                                             |

| Dan D. Fulgham               |                                         | PR - 7930                                                                                       |

| John L. Orr<br>Brian Mikiten |                                         | TA - 14<br>WU - 8E                                                                              |

| 7. PERFORMING OSGANIZATION   | NAMEES AND LODRESSES                    | E PER OPAN SHUKA 24 O                                                                           |

| MacAulay Brown, Inc.         | Southeastern Center for Electrical      | GERGAT NUMBER                                                                                   |

| 3915 Germany Lane            | Engineering Education (SCEEE)           | SwRI Project No. 12-2301                                                                        |

| Dayton, OH 45431             | 1101 Massachusetts Avenue               | Subcontract No. 1107-02-                                                                        |

|                              | St. Cloud, FL 34769                     | 08SWA                                                                                           |

| C PRONSORIEL .               |                                         |                                                                                                 |

| Armstrong Laboratory         |                                         |                                                                                                 |

| Crew Systems Directorate     |                                         |                                                                                                 |

| 2504 D Drive, Suite 1        |                                         |                                                                                                 |

| Brooks Air Force Base, TX    | 78235-5104                              | AL-TR-1992-0160                                                                                 |

| 11. SUPPLEMENTAR NOTES       |                                         |                                                                                                 |

| Armstrong Laboratory Tech    | nnical Monitor: Dr. Kent K. Gillingham, | , (210) 536-3521                                                                                |

| 120 DISTRIBUTION AND COLOR   |                                         |                                                                                                 |

Approved for public release; distribution is unlimited.

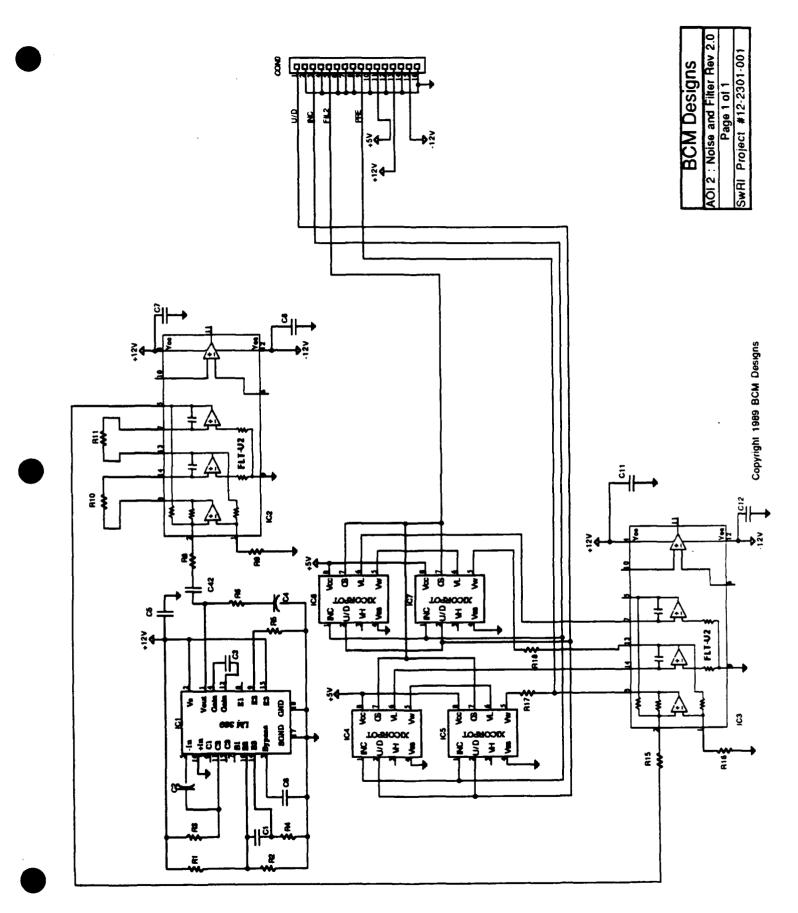

Subcontractor (Southwest Research Institute) provides engineering data and system software description for the Acoustic Orientation Instrument (AOI), which they developed for inflight testing. The overall scheme of operation of the system involves inputting a frame of scaled flight data (airspeed, bank angle, vertical velocity, etc.) from the Flight Instrument Package (FIP) over an RS232 serial link to the AOI, conversion of the flight data to corresponding output voltage waveforms by the AOI, and delivery of those outputs to stereo headphones to generate an auditory display of the flight parameters of interest. This report constitutes an operation and maintenance manual for the AOI, including system programming in the FORTH computer language.

| Acoustic orientation<br>Aural displays<br>Flight instrumentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |                                                                                                                 | 400                                                                        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| CORPORE DE LA CORRECTION DE LA CORRECTIO |              | and and a second sec | ngan berallar i Aggingan di ga daribahan di kapaninan na dari sebelah ga a |  |

| Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Unclassified | Unclassified                                                                                                    | UL                                                                         |  |

## TABLE OF CONTENTS

## Introduction

# Software

- A. Acoustic Orientation Aid Software

- B. Software Operations Overview

- C. Operating Sequence

- D. Values Displayed When AOI Operates

- E. Reading and Setting Variables

- G. Changing the Value of a Variable in DEMO

- H. Software Vector Hooks

- I. Acoustic Transformations

- J. Changing AOI Function Routines

- K. Substituting AOI Function Routines

- L. Development Environment

- M. Delivered Files

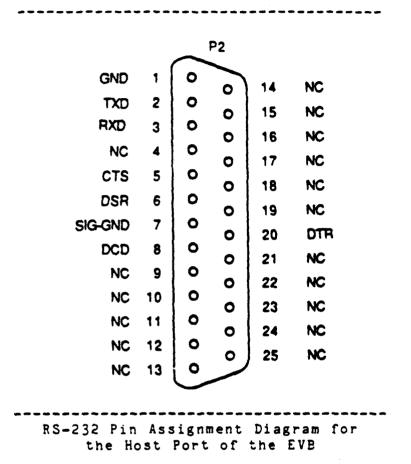

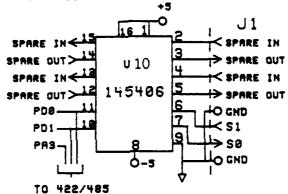

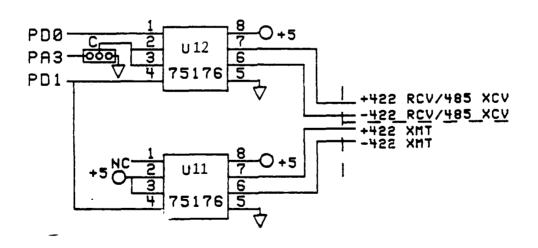

Serial Communications Information

A. Serial Communications

System Overview

- A. Purpose

- B. Component Overview

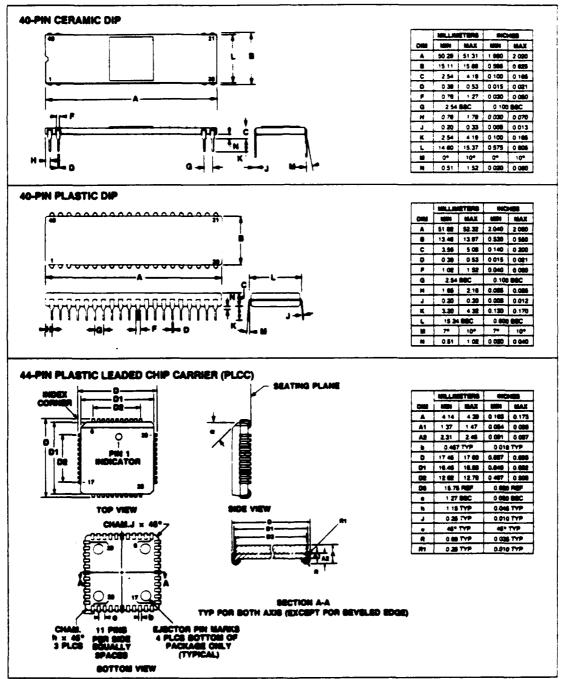

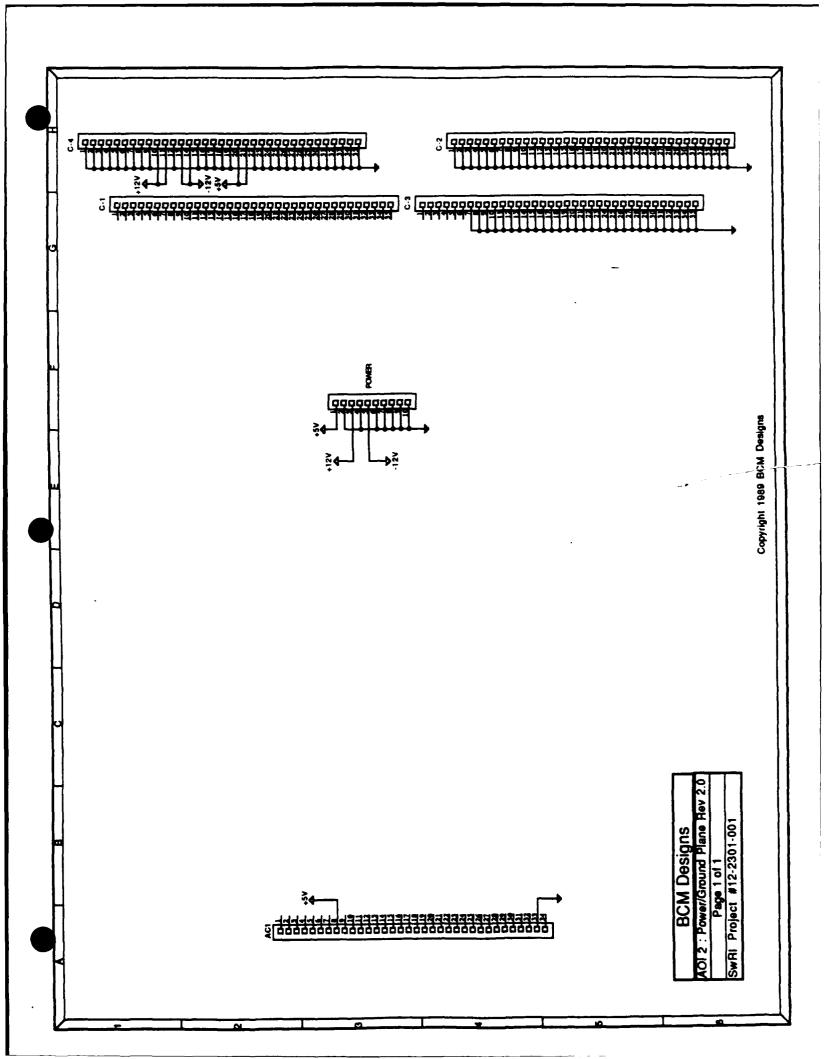

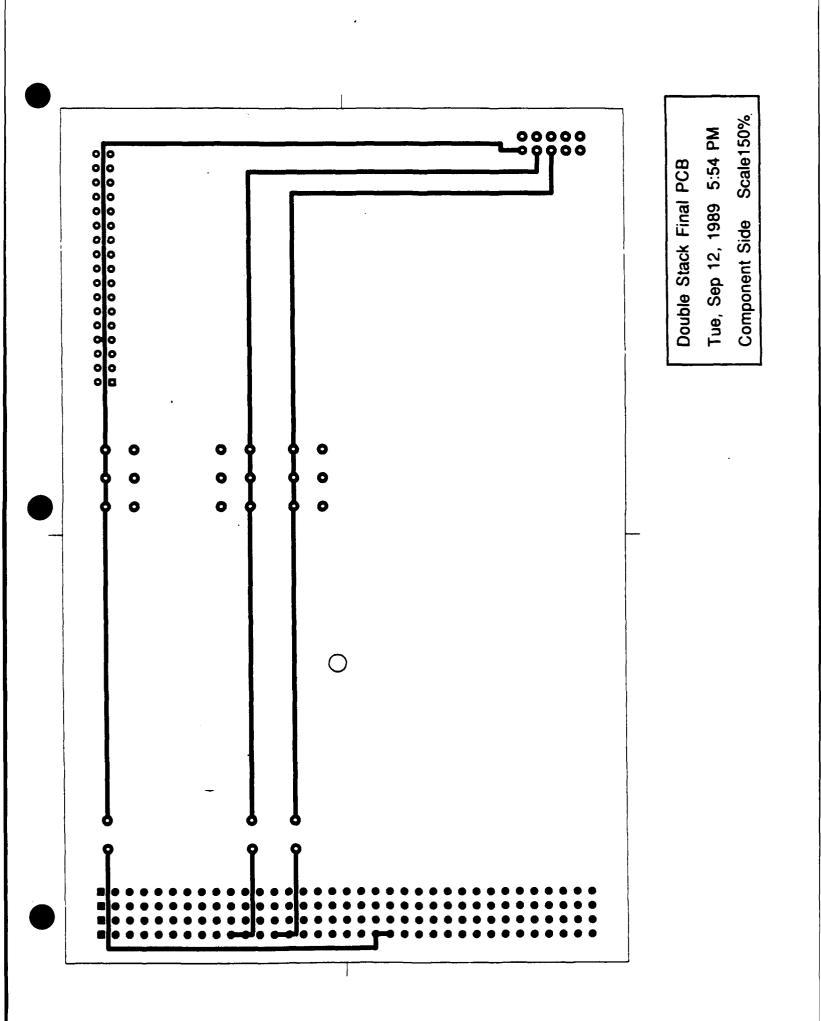

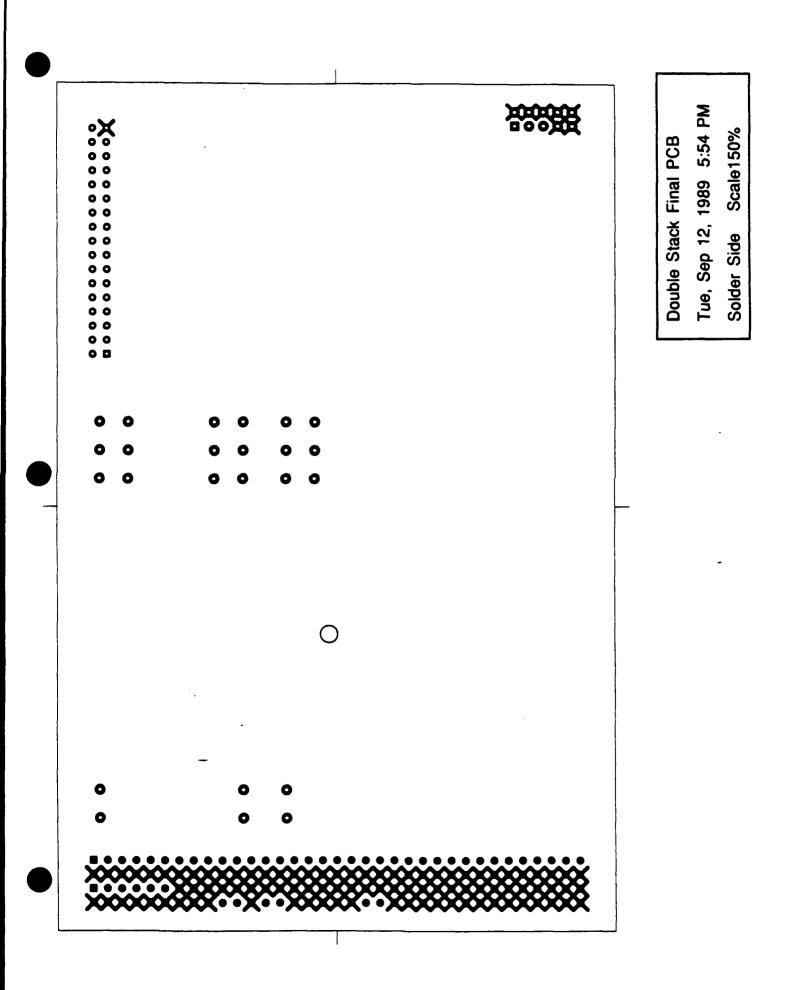

Appendices: Appendix A - 8930/6522 board PCB schematics PCB layouts data sheets 74LS688 AY-8930 R65C22 PCB silkscreens

Appendix B - 68HC11 Max-Forth manual NMI board manual

Appendix C - R65C52

Appendix D - Ground plane/Power board

schematic PCB layouts

Appendix E - Filter board schematic PCB layouts FLT-U2 data PCB silks

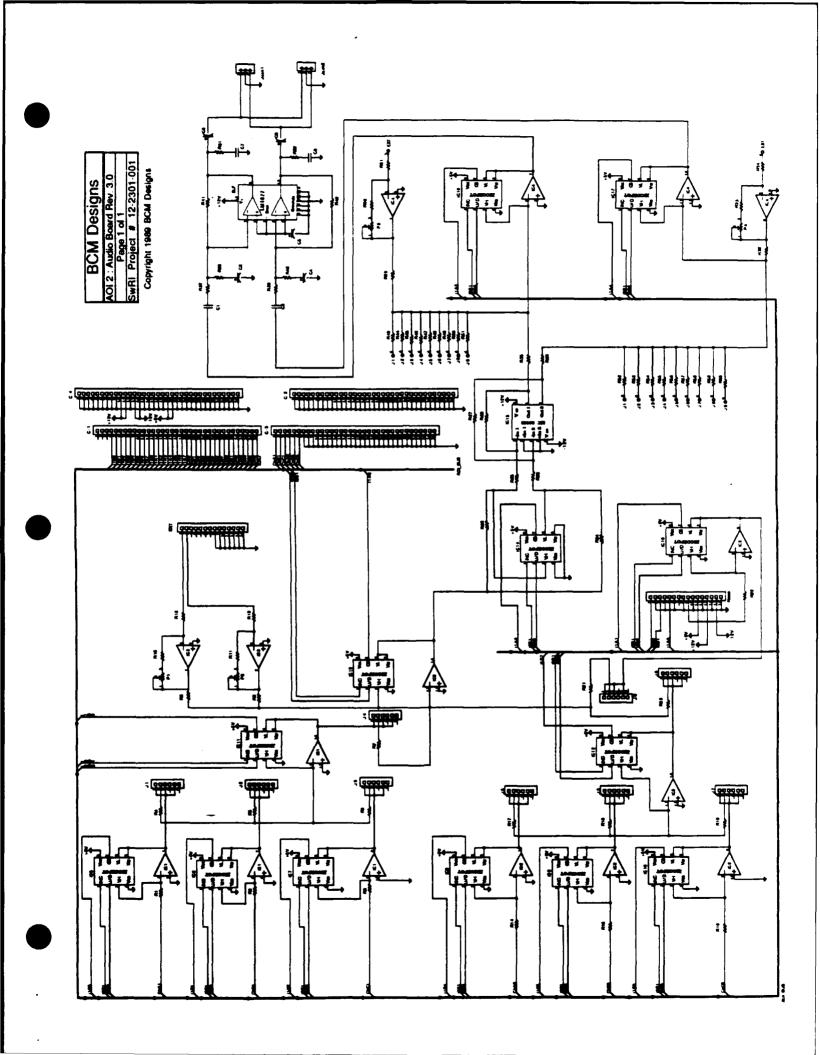

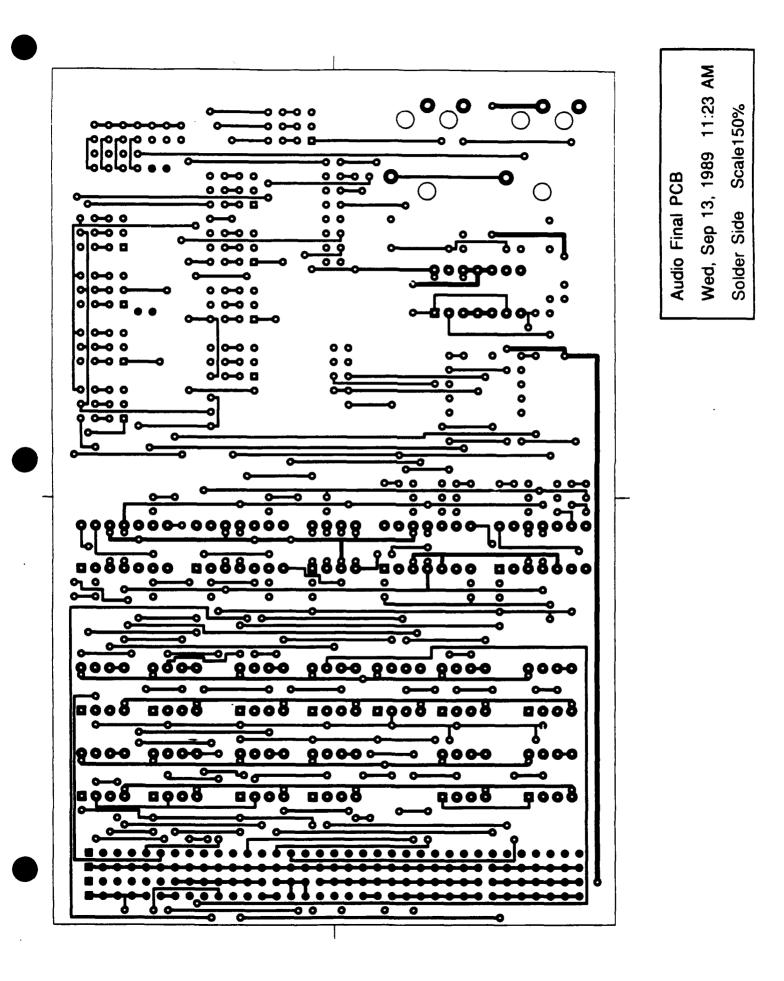

Appendix F - Audio mixer board schematic layout PCB silks data sheets op amps Xicor digital pots

Appendix G - Parts list

Appendix H - Source code listing

ii

## INTRODUCTION

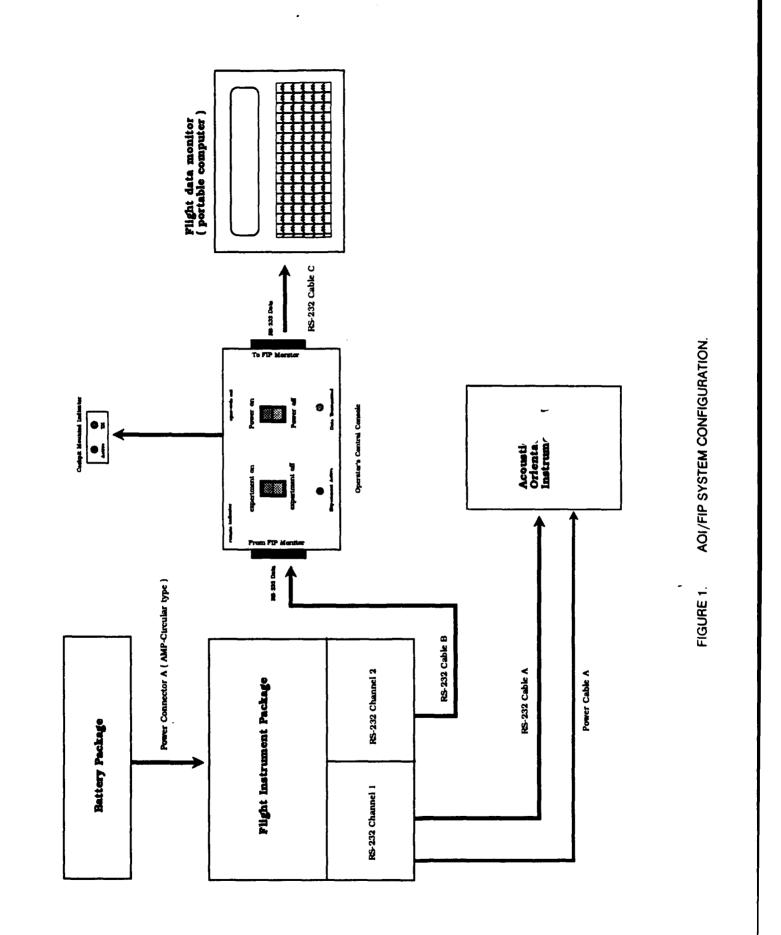

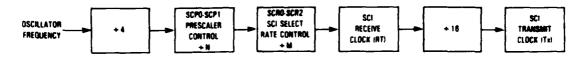

Selected flight parameters of the aircraft are monitored by the Flight Information Package (FIP). Upon a request from the Acoustic Orientation Instrument (AOI), the FIP sends a frame of scaled data corresponding to the current flight parameters over a RS232 serial link to the AOI. Figure 1 shows a diagram of the system.

The audio control circuitry of the AOI provides direct microprocessor control over six channels of waveform generation. Scaled parameters from the FIP are mapped to an output waveform heard by the pilot through stereo earphones. A simple example follows: Heading deviation (the deviation of actual heading relative to a set heading) is used to help the pilot stay on a pre-determined course. This heading deviation information is used to control the position of the acoustic signal across the pilot's head by adjusting the signal to the channels of the pilot's stereo headset. A course deviation of 10 degrees or greater results in a monophonic signal in the ear opposite the deviation. As the pilot corrects the error, the signals become more centrally located between the left and right ears, until finally there is an equal amplitude between the pilot's left and right ears and the auditory image is centered.

Other aircraft parameters which may be presented as transformations mapped to acoustic signals include airspeed, angle of attack, vertical velocity, altitude, and pitch and roll angle. Input parameters may be represented as changes in waveform frequency, amplitude, modulation, duration, attack, and decay times. The system software is written in the FORTH computer language and is designed for flexibility over parameter minimums, maximums, activation values, and types of signals used for stimulus. This system allows changes in control values to remap the acoustic signals with little knowledge of the theory of the system or programming.

#### SOFTWARE

#### Acoustic Orientation Aid Software

The software for the AOI has been provided in three formats: 1) source code listing in Appendix H 2) MS-DOS "non-document" text files on 1.2 Mbyte 5 1/4 inch floppy disk and 3) 720 Kbyte 3 1/2 Inch disks.

#### Software Operations Overview

A MS-DOS laptop computer with a communications program such as CrossTalk XVI or Mirror III should be used to load the software into the AOI and monitor its operation.

A batch file for Mirror is included which SENDS modules to the AOI. If another communications program is used, it should be set to require character echo and wait for a CR/LF before sending the next line.

Once the AOI software has been loaded, the laptop functions as a terminal to the AOI. The delivered DEMO module can stream the values read from the FIP to the screen.

Each of the AOI functional components - for example DO.AIRSPEED, which translates the data from the airspeed channel of the FIP into tone frequency - has several variables associated with it. Two of the airspeed related variables are AIRSPEED.MAX.FREQ. and AIRSPEED.MIN.FREQ. These variables correspond to the maximum and minimum frequencies generated by the airspeed channel. The characteristics of the AOI may be modified by simply placing a new value in the variable and starting the program. The functional components and their associated variables are described in detail in the section Acoustic Transformations.

Software integrity is only maintained by avoiding modifications of the source code. Changes in the variable settings should be made in the file DEMO.DO using a text editor.

#### **Operating Sequence**

The FIP and AOI computer programs must be loaded into the respective systems before a flight occurs. First, secure the battery package to the aircraft seat channels. Next, mount the FIP to the top of the battery package and engage the holding straps. This places the FIP in the correct configuration for flight. Following the steps outlined below will run the system.

- Turn the FIP control switches located on the to panel of the FIP to the off position.

- Connect the battery pack power connector labeled Power Cable A to the FIP and lock in place

- Connect RS-232 Cable A to the AOI but not the FIP

- Connect RS-232 Cable B to the Inflight contoller

- Connect RS-232 Cable C from the Inflight controller to the Flight data monitor

- Connect the cockpit mounted remote indicator

- Connect the AOI Power Cable from the FIP to the AOI

- Turn on the Inflight controller power and verify battery power

- Turn on the FIP main power switch

- Turn on the Gyro power

- Turn on the FIP computer power

- Connect the downloading computer to port A of the FIP

- Turn on the downloading computer and start MIRROR

- Confirm the <OK> from the FIP computer \*

- Download the FIP computer program

- Hook up the AOI RS-232 Cable A to the FIP Port A

- Hook up the downloading computer RS-232 cable to the

AOI terminal port.

- Confirm the OK from the AOI \*\*

- Download the code from the computer to the AOI ( see

below)

- Start the AOI program

- Turn the experiment-on switch to the on position

- Confirm data streaming and the TX light at a rate

of approximately 1Hz. \*\*\*

- Start the recording system and the flight

\* If an <ok> is not present, the connections are faulty or the FIP computer is not working. If the green light on the FIP computer is on, the connections are faulty.

\*\* If an <ok> is not present, check the power connection and press the red reset button on the front panel of the AOI. If this does not correct the problem, the AOI or FIP power system may require service.

\*\*\* If data is not streaming or Tx light is not at 1 Hz, the FIP may not be executing its program. Check the download program and the status of the FIP computer system. AOI Code loading instructions:

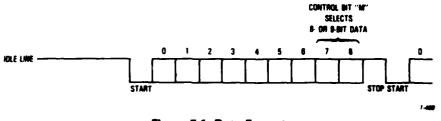

- 1. Start the communications program. The settings are 9600 baud, 8 bits 1 stop hit, no parity, character echo.

- 2. Line Wait = CTRL J.

- 3. From the MIRROR command line type: DO STARTUP and press the ENTER key.

- 4. The program modules will then load into the AOI.

- 5. Normal operation of the AOI is indicated by an OK prompt.

NOTE: BE CERTAIN THAT THE CAPS KEY ON THE LAPTOP IS DEPRESSED. ALL COMMANDS TO THE AOI MUST BE IN UPPER CASE!

- 6. Type AOI and press ENTER. In a few seconds, data values from the FIP will start streaming to the laptop display.

- 7. Pressing any key will stop the AOI program. Typing AOI and pressing ENTER will partially re-initialize the system and start the program. Variables which have been changed at the OK prompt will now be in effect until changed or until the program is reloaded.

## Values Displayed When AOI Operates

The values displayed are scaled data values from the FIP. The figures in the section Acoustic Transformations show the relationships between the readings on the cockpit instruments and the scaled data.

#### **Reading and Setting Variables**

To see the value of a variable you must do three things: 1) obtain the location of the variable by typing its name, 2) fetch the value of the variable by typing @, and 3) display the variable by typing a period. The OK prompt means the AOI is ready to accept a command.

For example:

OK AIRSPEED.MIN.FREQ @ .

40

OK

shows that the current value of the variable AIRSPEED.MIN.FREQ. is 40.

To temporarily change the value of a variable, three steps are again required: 1) type the new value and a space, 2) type the name of the variable and a space, and 3) type ! and Enter. Each of these entries must be separated with a blank space.

For example to make the lowest frequency for airspeed 200 Hz:

## OK 200 HZ AIRSPEED.MIN.FREQ !

OK

and the value is changed. HZ is a word which translates frequency to period.

## Changing the Value of a Variable in DEMO

The same commands may be used in DEMO to change the values of a variable. Use a text editor in the laptop to edit the file DEMO to contain the command.

As in the airspeed example above, type:

## 200 HZ AIRSPEED.MIN.FREQ !

then save the modified DEMO file. There is no OK here because we are editing a text file, not interacting with the interpreter. When DEMO is reloaded, the new value will be in effect. The advantage of this approach is that the program itself is not changed, it is easy to keep track of where changes have been made, and a complete re-loading of the program is not required.

#### Software Vector Hooks

DEMO contains examples of the use of the Forth MAKE construct. As AOI was written, portions of the program were constructed as changeable hooks, also known as forward references or execution vectors. The MAKE command is used to plug a particular section of code into the hook. Initially, all hooks are connected to a routine called NOP (no operation), which does nothing. Inspection of the source code in Appendix H for the routine AOI in the module AOI will show that it is just an infinite loop with a series of named hooks. The declaration of one of these hooks is by the word DOER. The declaration of the execution vectors for the routine AOI in the module AOI in the module

If AOI was loaded, but not DEMO, and AOI typed to start it, the AOI microprocessor would be an infinite loop doing nothing. It would be necessary to either remove power from the system and reload the software or press the reset button on the AOI in order to stop the execution.

## In DEMO the phrase:

#### MAKE HOOK4 GET.OUT

changes the operation of HOOK3 from NOP to the routine GET.OUT which checks for depression of any key and exits the loop if any key has been pressed.

Similarly, the phrase:

## MAKE N.STARTUP SETUP

Causes the routine SETUP to be inserted into the hook N.STARTUP.

Hooks can be turned off by setting them to execute the routine NOP as follows:

#### MAKE HOOK2 NOP

This phrase will stop the display of the scaled data values on the laptop.

In general, the vectors can be hooked and unhooked as desired, with one exception. The routines for airspeed (DO.AIRSPEED) and for vertical velocity (DO.VERTICAL.VELOCITY) are related since the vertical velocity routine controls the amplitude of the airspeed tone.

## Acoustic Transformations

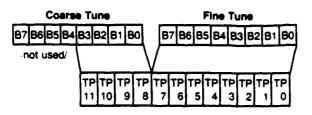

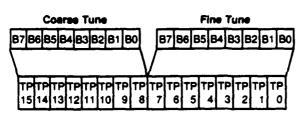

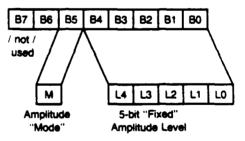

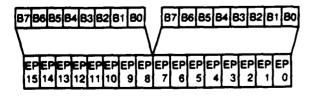

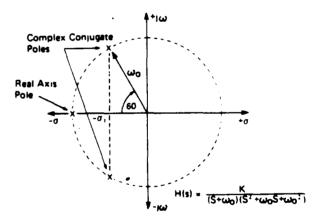

The software modules for the various functions work in a consistent manner. There is a range of scaled data values defined by endpoints and a range of AY-8930 control parameters for an acoustic dimension defined by endpoints.

The software linearly scales the data value to the AY-8930 parameter value and loads the appropriate AY-8930 register to set the corresponding acoustic dimension. The rest of the code in the function routines is primarily logic to prepare for the appropriate scaling.

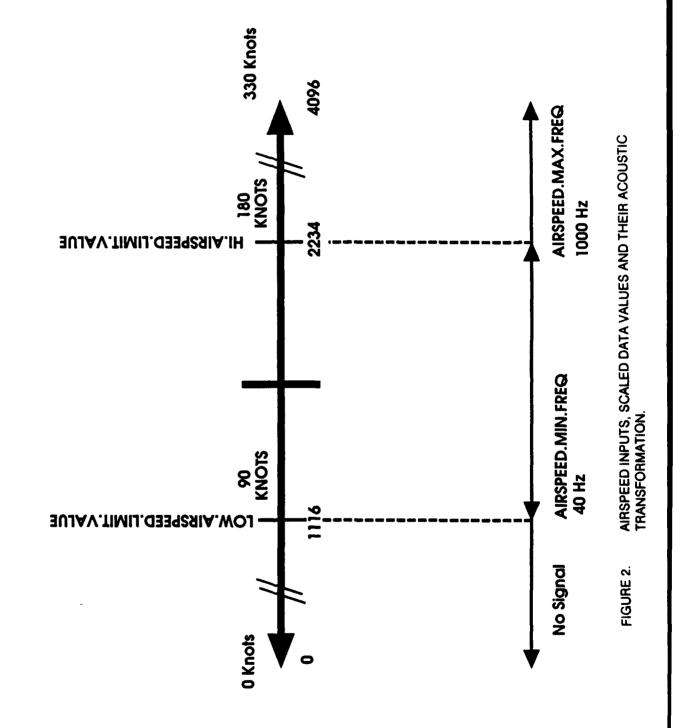

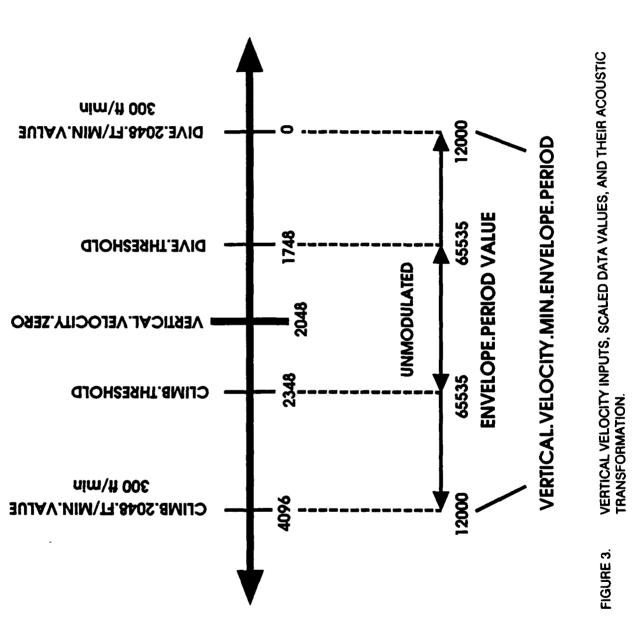

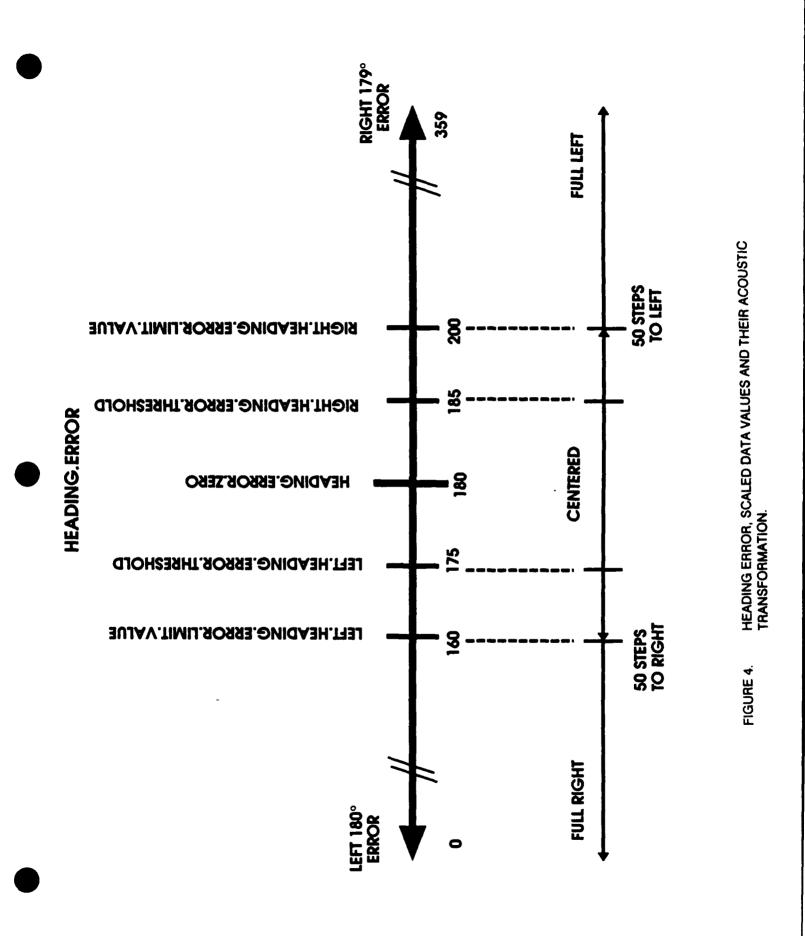

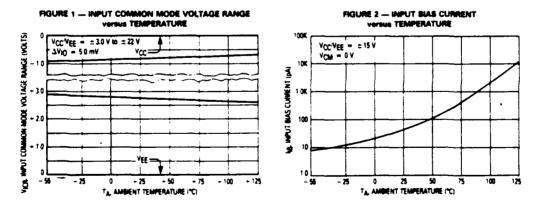

The following discusses the relationships between the scaled data from the FIP and parameters for the acoustic signals. The specific values described are those originally delivered with AOI-II. As described above, it is intended that these parameters be changed by modifying the file DEMO. It is important to understand that the encoding relationships described here are only and example of the set of possible encoding schemes. The source code containing FIP data to AOI scaled data is found in Appendix H. One must carefully read the source code to understand the details of the encoding examples. In figures 2-7, the upper line indicates the range of scaled data from the FIP and the corresponding physical parameter values, while the lower line displays the range of acoustic parameters.

AIRSPEED

VERTICAL.VELOCITY

## **Airspeed**

Airspeed is encoded into the frequency of a square wave output which increases in frequency as airspeed increases. The upper line in Figure 2 shows that the range of scaled airspeed values is from 0 to 330 knots, corresponding to scaled data values from 0 to 4096. The lower line shows that the AIRSPEED.MIN.FREQ is 40 Hz and the AIRSPEED.MAX.FREQ is 1000 Hz. This range of frequencies is mapped linearly between the scaled data values corresponding to LOW.AIRSPEED.LIMIT.VALUE (current scaled data value of 1116 corresponding to 90 knots) and HI.AIRSPEED.LIMIT.VALUE (current scaled data value of 2235 corresponding to 180 knots). Changes in these variables will change the scaling. If LOW.AIRSPEED.LIMIT.VALUE was set to 1861 (150 knots) and HI.AIRSPEED.LIMIT.VALUE was set to 2110 (170 knots) and the other variables unchanged, the new airspeed range of 20 knots would be scaled from 40 to 1000 Hz. Similarly, if the airspeed limit values were at their original values and AIRSPEED.MAX.FREQ was changed to 1500 Hz, airspeeds from 90 to 180 knots would be mapped onto a 50% larger frequency ange.

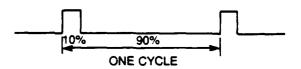

#### Vertical Velocity

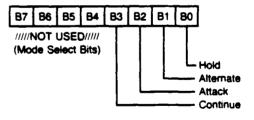

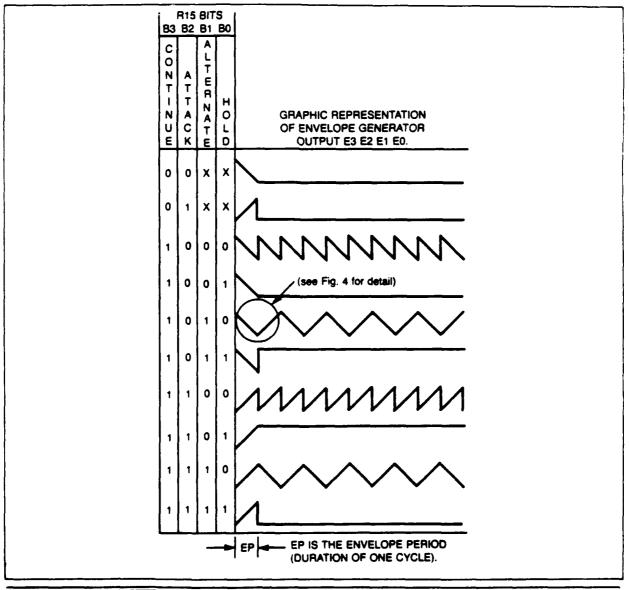

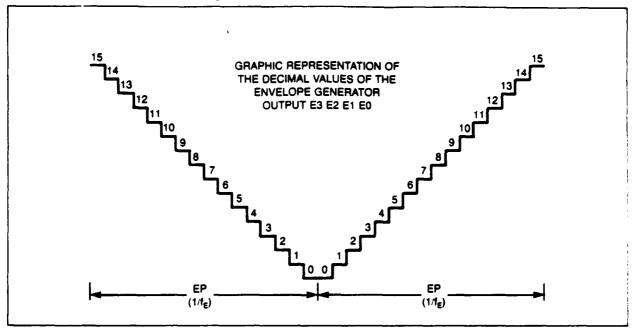

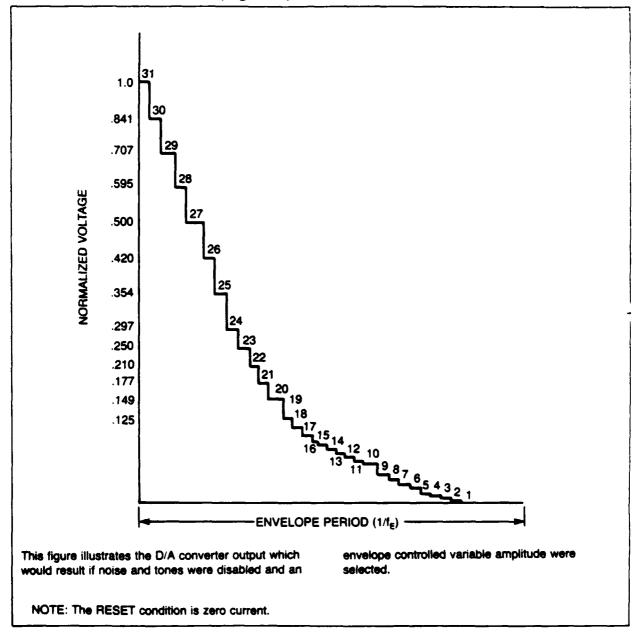

The direction of vertical velocity (climb or dive) is encoded as a change in amplitude modulation (attack or decay) of the airspeed tone. The magnitude of vertical velocity is encoded into the period of the amplitude modulation with long periods corresponding to low vertical velocities and short periods corresponding to high vertical velocities. There are selectable vertical velocities beyond which the modulation period does not change. As shown in Figure 3 the scaled values of vertical velocity from the FIP range from 0 (2048 feet/minute dive) through 2048 (level flight) to 4096 (2048 feet/minute climb). The range between the DIVE.THRESHOLD of 1748 (300 feet/minute climb) and the CLIMB.THRESHOLD of 2348 (300 feet/minute dive) define a null region where there is no amplitude modulation of the airspeed tone. Between the CLIMB.THRESHOLD and the CLIMB.2048.FT/MIN.VALUE, the period of amplitude modulation (decays starting with the maximum intensity and decreasing in 32 logarithmic steps) changes from slow (the maximum envelope period of 65535) to fast (the minimum envelope period of 12000). The signal changes between the DIVE.THRESHOLD and the DIVE.2048.FT/MIN.COUNTS are analogous except when the amplitude modulation consists of attacks starting with the lowest intensity and stepping to the maximum. The VERTICAL VELOCITY. MINIMUM.ENVELOPE.PERIOD is set to 12000 in order to permit discrimination of the decays and attacks. Although the demo program has symmetrical thresholds and limit values, this is not a requirement.

## Heading.error

Heading error is relative to the heading set on the FIP. Heading errors move the apparent location of the acoustic signal in a direction opposite the deviation. Figure 4 shows the encoding of heading error. Scaled heading error values from the FIP range from 0 (180 degrees left heading error) to 180 (on course) to 359 (179 degrees right heading error). Between LEFT.HEADING.ERROR.THRESHOLD (scaled value of 175 which corresponds to a 5 degree left

14

heading error) and RIGHT.HEADING.ERROR.THRESHOLD (185 which corresponds to a 5 degree riaht heading the acoustic signal is error) centered. Between LEFT. HEADING. ERROR. THRESHOLD LEFT.HEADING.ERROR.LIMIT.VALUE and (160 corresponding to a 20 degree left heading error) there are 50 position steps toward an apparent location of the acoustic signal on the right. Left heading errors larger than the LEFT.HEADING.LIMIT.VALUE are positioned at the maximum location to the right. Heading deviations to the right are similar in concept, except that the apparent acoustic signal location moves to the left with increasing deviations.

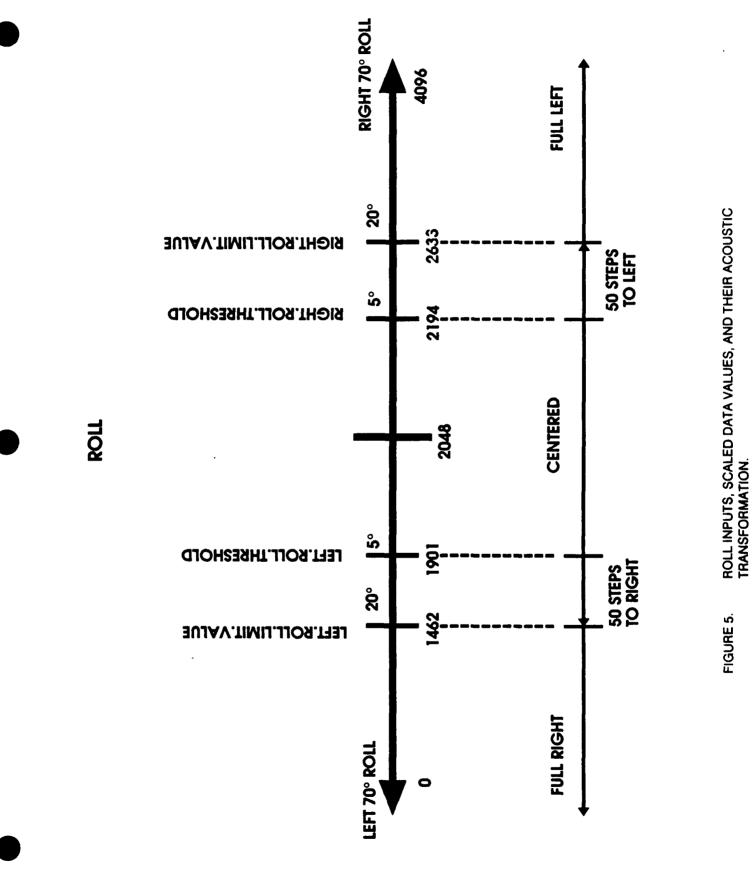

#### Roll

Encoding of roll is directly analogous to the encoding for heading error. Figure 5 shows the particular values of the values in the roll variables used in the supplied version of AOI. Because heading error and roll both encode to position within the head on the interaural axis, only one may be connected to its software vector hook at a time.

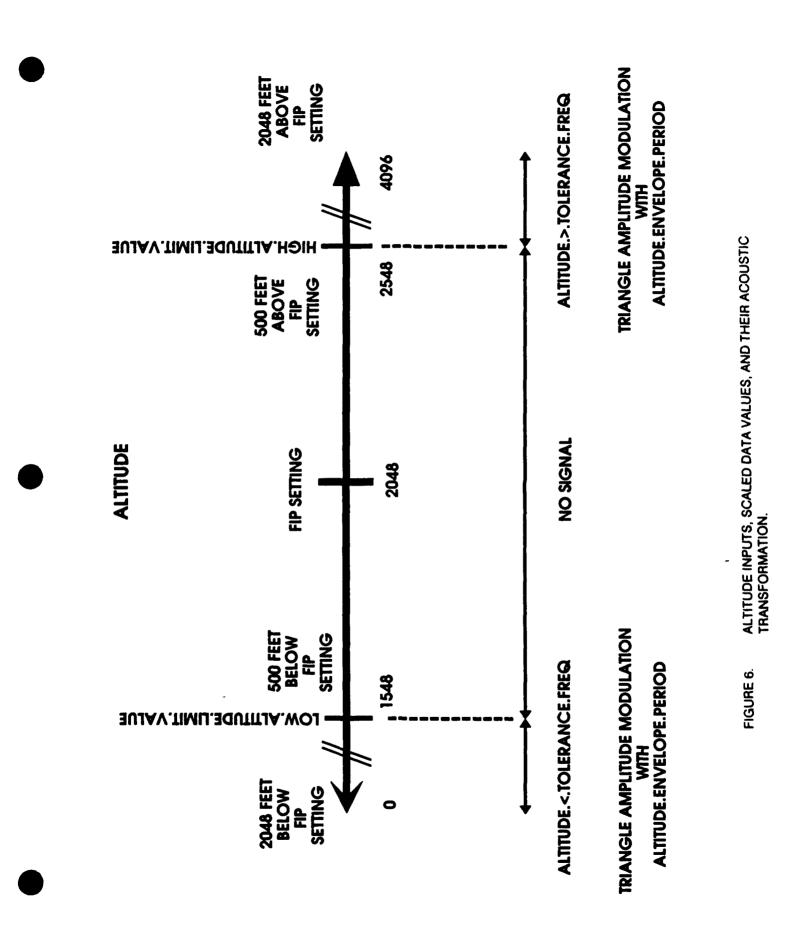

#### **Altitude Deviation**

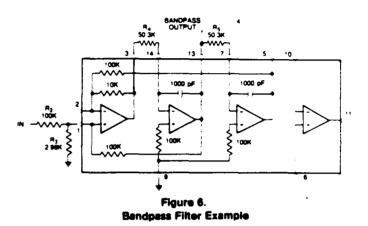

Altitude deviation is relative to the value set on the FIP. Figure 6 shows the altitude encoding scheme. Altitude deviation covers a range between 2048 feet below the FIP setting (scaled data value of 0) and 2048 above the FIP setting (scaled data value of 4096). Above the HIGH.ALTITUDE.LIMIT.VALUE of 2548 (500 feet above FIP setting), a high pitched triangle modulated annunciatior is added to the acoustic signal. ALTITUDE.>.TOLERANCE.FREQ is the variable which controls the frequency of the annunciator and ALTITUDE.ENVELOPE.PERIOD is the variable which controls the period of the annunciator. Below the LOW.ALTITUDE.LIMIT.VALUE of 1548 (500 feet below FIP setting) the annunciator is added to the acoustic signal with a frequency controlled by the variable ALTITUDE.<...

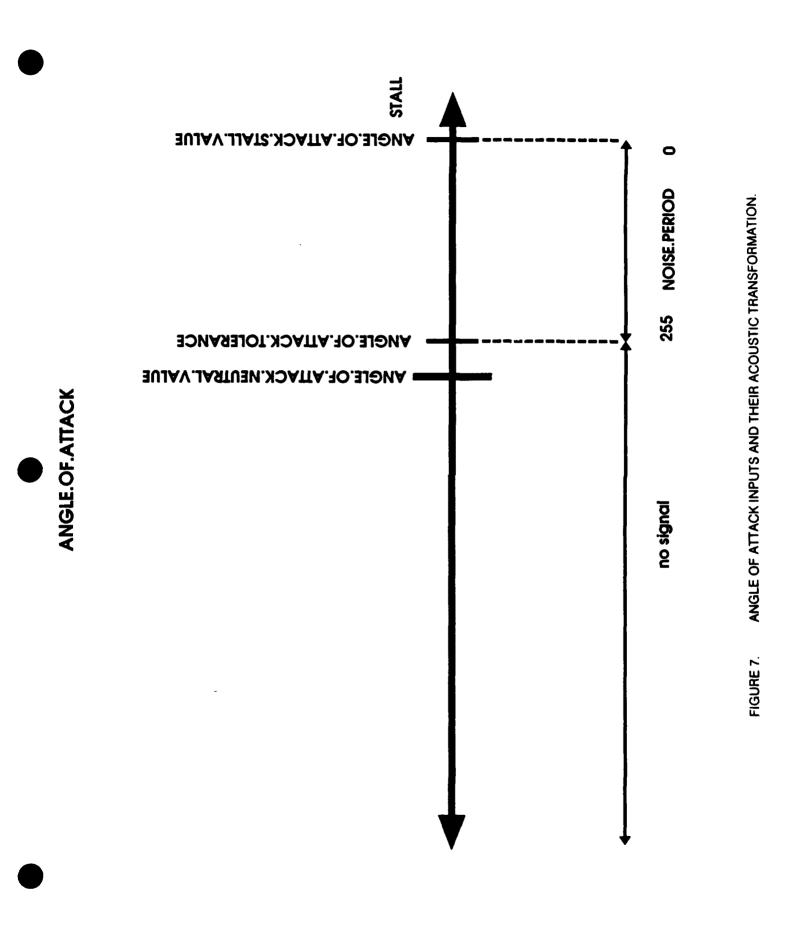

#### Angle.Of.attack

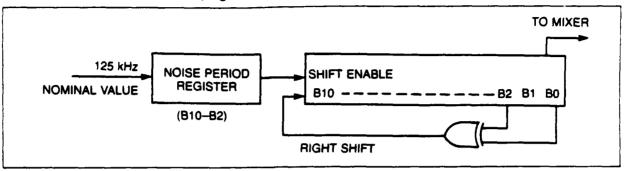

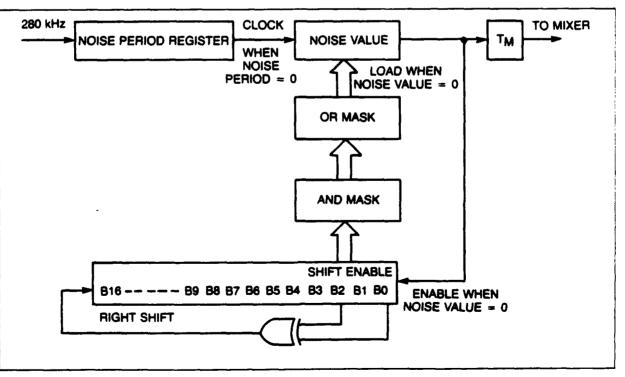

Encoding of angle of attack is shown in Figure 7. Because there is not a functioning angle of attack vane on our test aircraft, this function is not yet implemented. The acoustic signal for angle of attack is intended to provide a warning of an impending stall. ANGLE.OF.ATTACK.NEUTRAL.VALUE is an offset. If the scaled data value for angle of attack is less than ANGLE.OF.ATTACK.NEUTRAL.VALUE plus ANGLE.OF.ATTACK.THRESHOLD, there is no acoustic output for angle of attack. If the scaled data value is greater than ANGLE.OF.ATTACK.THRESHOLD but less than the stall value, angle of attack deviation from threshold is mapped onto the period of a digital noise generator in one of the AY-8930 programmable sound chips. Just above the threshold, the acoustic signal is randomly spaced clicks with a low average rate. As deviation above threshold increases, the average rate increases until just before a stall, the acoustic signal resembles wide band noise. When data value scaling is known, it is merely necessary to insert appropriate scaled values into the variables in the module DEMO as described above.

#### Changing AOI Function Routines

The diagrams in the section Acoustic Transformations show the important variables for the different functional routines. A great deal of flexibility in the operation of the AOI is available by careful changing of the values of the variables. Alternatively, by inappropriate changes in the variables, it is possible to render the AOI non-functional until the original code is reloaded.

#### Substituting AOI Function Routines

Using the delivered source code as a guide, new routines can be written in the MAX-FORTH language of the AOI microprocessor. For example, a new vertical velocity routine, for example, DO.NEW.VERTICAL.VELOCITY, could be written and loaded after the file AOI. By editing the line in file named DEMO from

# MAKE N.DO.VERTICAL VELOCITY DO.VERTICAL.VELOCITY

to

MAKE N.DO.VERTICAL VELOCITY DO.NEW.VERTICAL.VELOCITY

the new routine would be hooked into the AOI-II software.

## **Development Environment**

The AOI software was developed on IBM-PC compatibles. Either Crosstalk XVI from Digital Communications Associates or Mirror from Softklone Associates were used as communications programs. Mirror includes a screen editor which allows the editing of files while still in serial communications with the AOI.

## **Delivered Files**

The following files are on the MS-DOS format disk delivered with the AOI system. The first group of files are modules which make up the AOI software. These files are listed in Appendix H. These source code files have comments which clarify the actions being performed. Since the source code is written in MAX-FORTH, the language embedded in the ROM of the microprocessor of the AOI, one must be proficient in FORTH to understand the code in detail. However, because of the ability to use meaningful names for routines in Forth, one does not need to be an expert to read the Forth source code and understand the function of the components of the routines.

Forth has a variety of unique characteristics. The language is a postfix notation similar to that of most Hewlett Packard calculators. This means that first the operands are entered and then the operator. For example, to add four and six in Forth, you would type 4.6 + and then a period. (. is the print command) to print out the result of 10. The MAX-Forth reference manual delivered with the AOI includes an introduction to programming Forth. A second feature of Forth is the dictionary. Routines are called words, and as new words are defined they are entered into the dictionary. Because of its structure, Forth requires that any words used within another defining word must have been previously entered into the dictionary (unless it is a forward reference preceded by the word DOER). Another feature of Forth is that most parameter passing is done on a data stack instead of through static data structures. Forth is ideally suited for hardware oriented, real-time control problem applications such as the AOI, because routines (words) may be interactively tested and debugged.

The following source code files are listed in the order in which they are loaded into the AOI system.

| SETUP    | Configures the system memory and defines utilities |

|----------|----------------------------------------------------|

| ARRAYS   | Defines array and table words                      |

| CASE     | Defines a case selection execution structure       |

| CHIPCTRL | Hardware control primitives for the AY-8930s       |

| DOERMAKE | Implements the forward reference mechanism         |

| SELECTOR | Connects functional names to AY-8930 registers     |

| VIEW8930 | Controls AY-8930 shape/cycle registers             |

| ENVELOPE | Dumps all AY-8930 registers in AOI context         |

| CONVERT  | Converts frequency to period                       |

| TIME6522 | Uses 6522 as a timer                               |

| XICOR    | Controls digital potentiometers                    |

| CONFIGUR | Sets up hardware                                   |

| TRANSIT  | Provides AOI 1&2 compatibility                     |

| ACIACOM  | Provides communications to FIP                     |

| SHOFRAME | Displays scaled data                               |

## AOI Performs the AOI transformations

SYSINITS Initializes routines

The AOI module is the module relevant for understanding the operation of the AOI and seeing the meaning of the variables which are analogous to the trimmer potentiometers on traditional instruments. Skilled adjustment and change can enhance AOI performance.

The source code modules listed below contain comments and white space to enhance readability.

DEMO is the last module downloaded to the AOI and contains the following:

MAKE N.STARTUP SETUP (IN FILE SYSINITS)

MAKE HOOK1 SYNCH

(WAITS UNTIL 1 SECOND HAS ELAPSED SINCE TIMER STARTED)

(THE TIME FOR THE AOI PROCESSING IS WITHIN THE SECOND)

MAKE HOOK2 GET.DATA.FRAME

(PUTS A FRAME OF DATA INTO INPUT.DATA ARRAY)

(INPUT.DATA IS DEFINED IN FILE TRANSITS)

(GET.DATA.FRAME IS DEFINED IN ACIACOM)

MAKE HOOK3 SHOW.DATA.FRAME

(SHOWS THE DATA FRAME FROM INPUT.ARRAY)

MAKE HOOK4 GET.OUT

(GET.OUT BREAKS YOU OUT OF THE PROGRAM IF ANY KEY IS HIT )

(GET.OUT DEFINED IN FILE SETUP)

(MAKE N.DO.AOA DO.AOA)

(AOA VANE IS NOT YET ON AIRPLANE)

MAKE N.DO.AIRSPEED DO.AIRSPEED

(BOTH DO.ROLL AND DO.HEADING.ERROR USE THE HEADPHONE

## **BALANCE**)

(THEREFORE ONLY ONE CAN BE USED AT A TIME)

MAKE N.DO.ROLL DO.ROLL

(MAKE N.DO.HEADING.ERROR DO.HEADING.ERROR)

MAKE N.DO.ALTITUDE DO.ALTITUDE

## MAKE N.DO.VERTICAL.VELOCITY DO.VERTICAL.VELOCITY

The modules above connect the routines to the hooks in the AOI program (resolves the forward references from NOP to the desired action. DEMO. is the appropriate place to add changes to set variables to new values.

LP.DOC explains how the listings were printed and contains the following:

This is the command line used with Norton's LP program to produce the HP Laserjet listings:

ip filespec /h60/w132/set:\aoi\lasercod/l25/r25

The file LASERCOD contains the setup for the HP Laserjet and consists of:

\027E\027(s16.66H)

(This information is only relevant if you have Norton Utilities and an HP-Laserjet printer).

#### SERIAL COMMUNICATIONS INFORMATION

#### Serial Communications

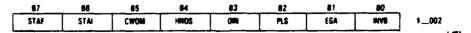

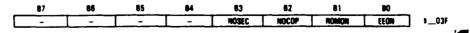

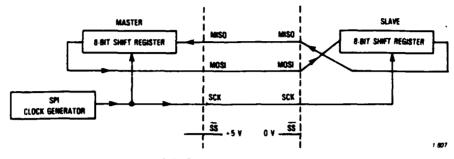

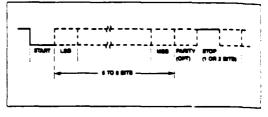

The following data frame is used when data is sent from the FIP to the AOI-II.

Frame Start Character (STX ascii 02) Airspeed Angle of Attach (not used) Vertical Velocity Heading Deviation (+ -) Roll Angle Pitch Angle Altitude Deviation (+ -) End of Frame Character (ETX - ascii 03)

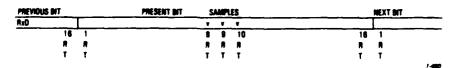

Data is sent at 9600 baud, 8 data bits, 1 stop bit, no parity. The data are sent as 16 bit binary integers with a check sum.

19

#### SYSTEM OVERVIEW

#### Purpose

The Acoustic Orientation Instrument (AOI) has been designed as an acoustic signal synthesis and output device driven by the Flight Instrumentation Package (FIP). As a system, the AOI is directly connected through a serial communications line to the FIP and generates acoustic parameters based on the scaled values of flight parameters measured by the FIP while in flight.

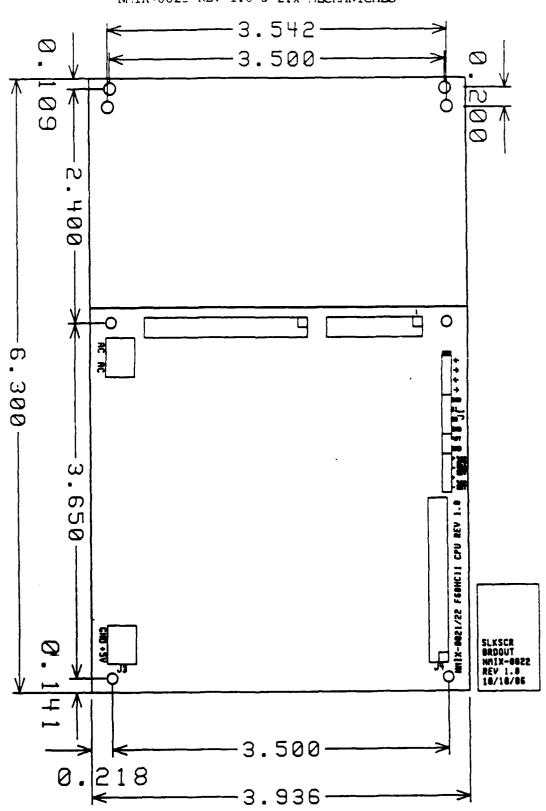

The FIP-AOI system is designed to operate for up to 4 hours from a battery package that supplies both the AOI and the FIP. Audio output is provided to two stereo headphone jacks located on the front panel of the AOI. The AOI is housed in a 6x6x4 inch metal case and consists of six individual printed circuit boards.

#### Component Overview

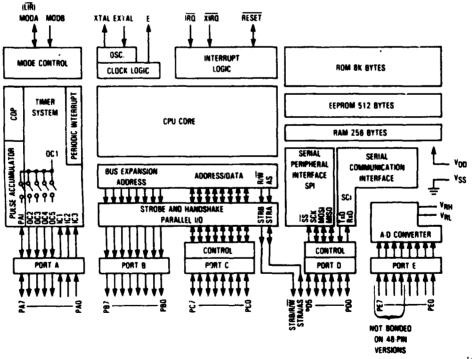

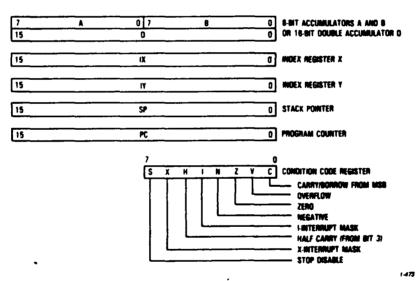

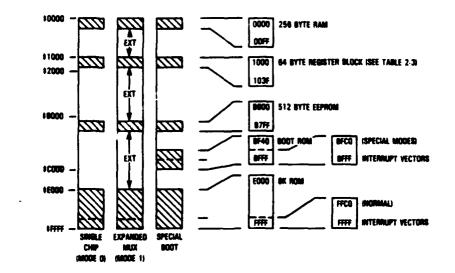

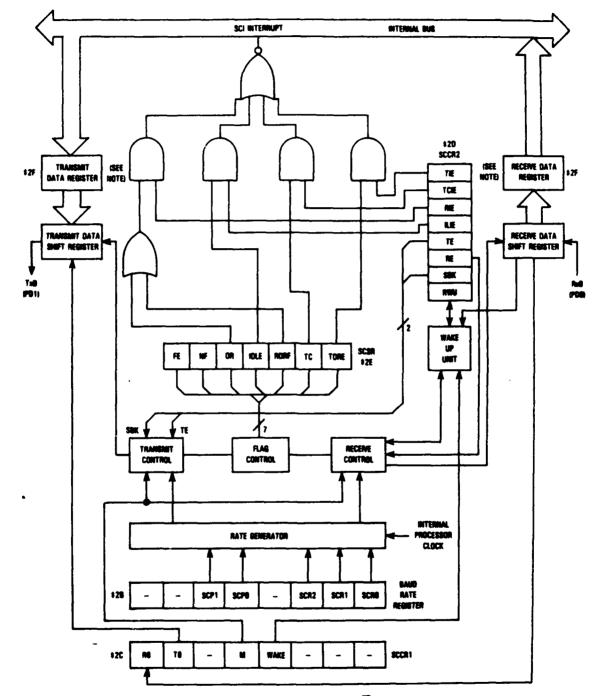

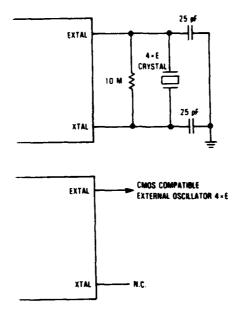

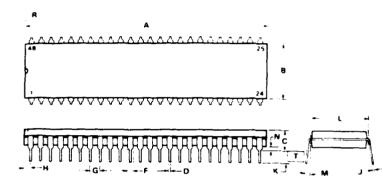

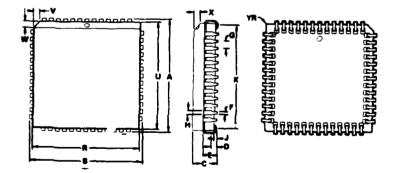

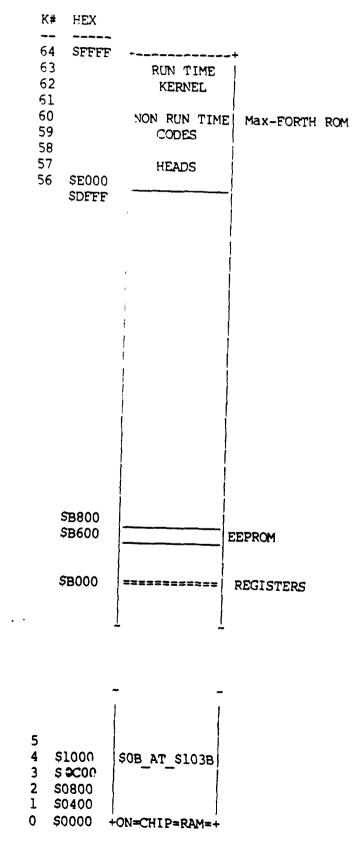

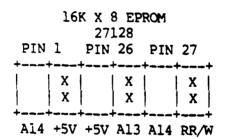

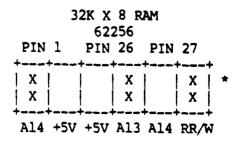

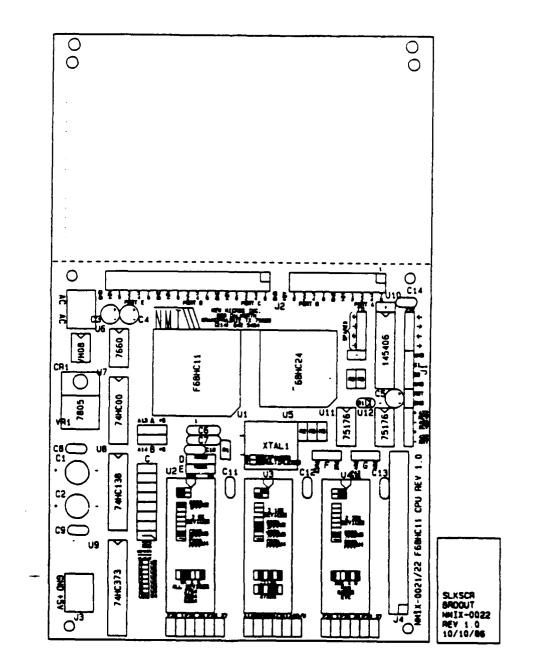

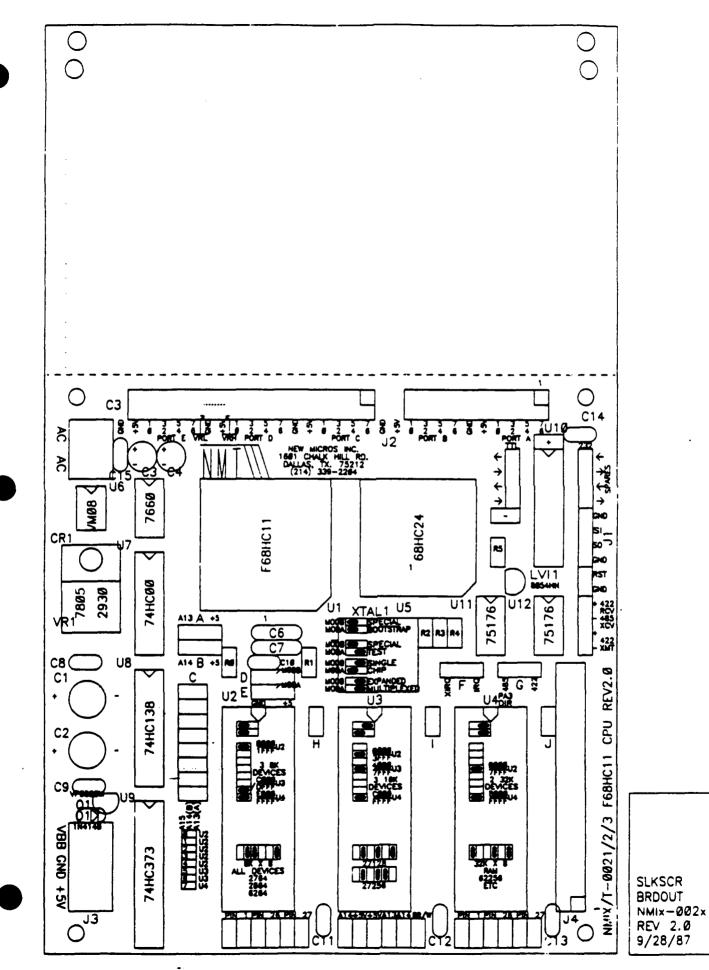

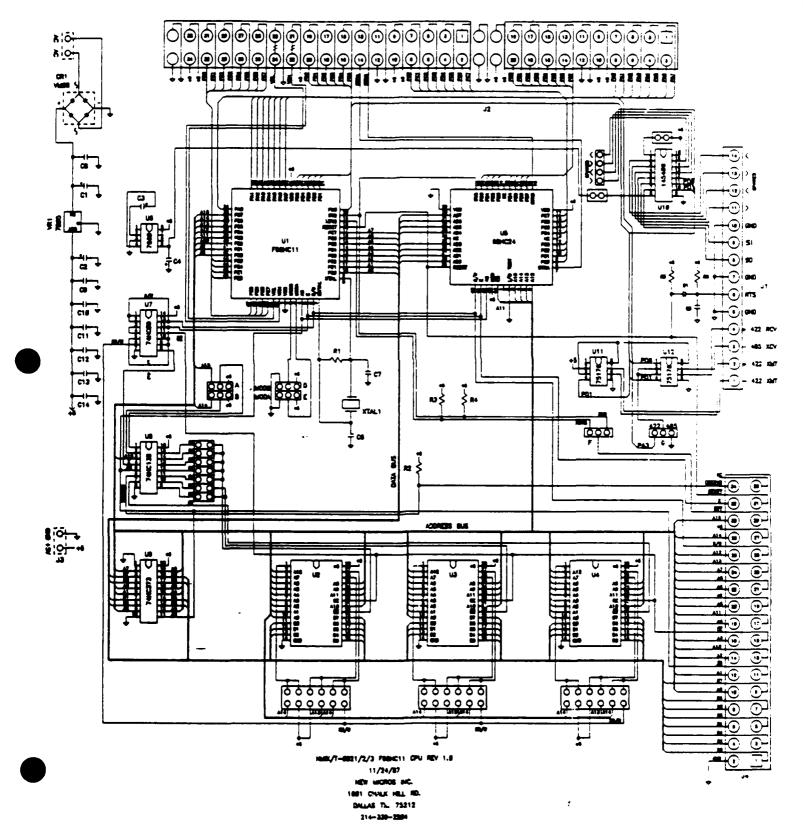

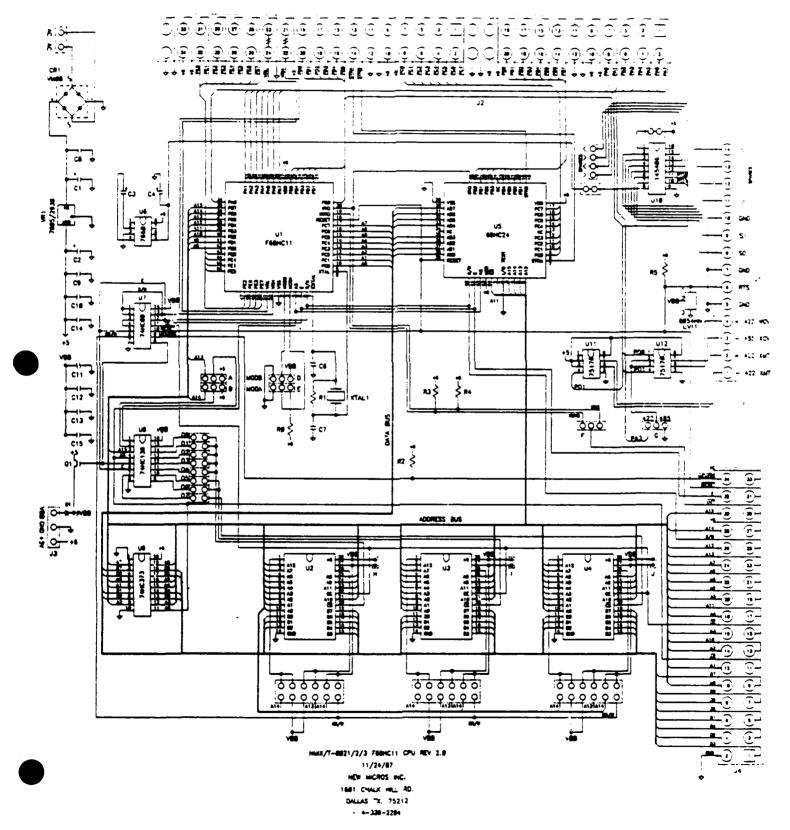

#### 68HC11/F Single Board Computer

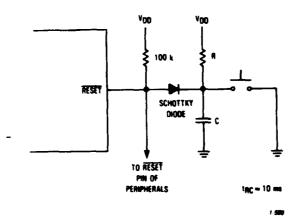

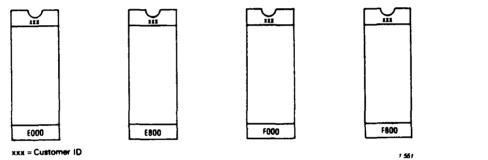

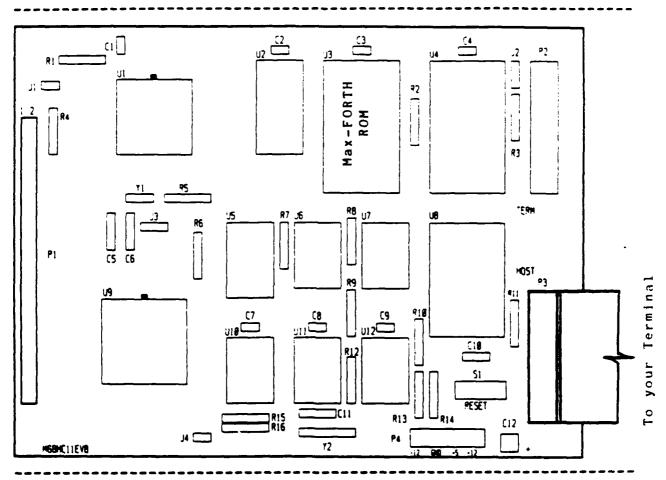

The first component in the system is a 68HC11/F, single-board computer operating at 4 MHz from New Micros Inc., Dallas, Texas. The board runs the FORTH programming language as well as assembly code and contains a port replacement unit (PRU), three sockets for RAM, and a total addressable range of 64K, minus the space used by the FORTH language in ROM within the microprocessor. Also included on the board is a RS232 communications port for the console operating at 9600 baud, 8 bits no parity, one stop bit. In this implementation the board utilizes 32K of RAM and the Forth language in ROM. All components in the AOI-II are memory mapped on the bus using the JEDSTACK connector on the board. The bus contains 16 address lines, 8 data lines multiplexed, read/write signals, interrupt signals and other miscellaneous microprocessor generated signals. The clock used on the microprocessor board is used as the AOI system clock and drives all other boards. Bus addressing has been used to guarantee high speed operations and data transfer to all other boards in the system. The bus also provides one leg of the mechanical support for the entire AOI board set. Other information on the 68HC11/F board can be found in the Appendix B. Also included in Appendix B are the Max-Forth and 68HC11 manuals.

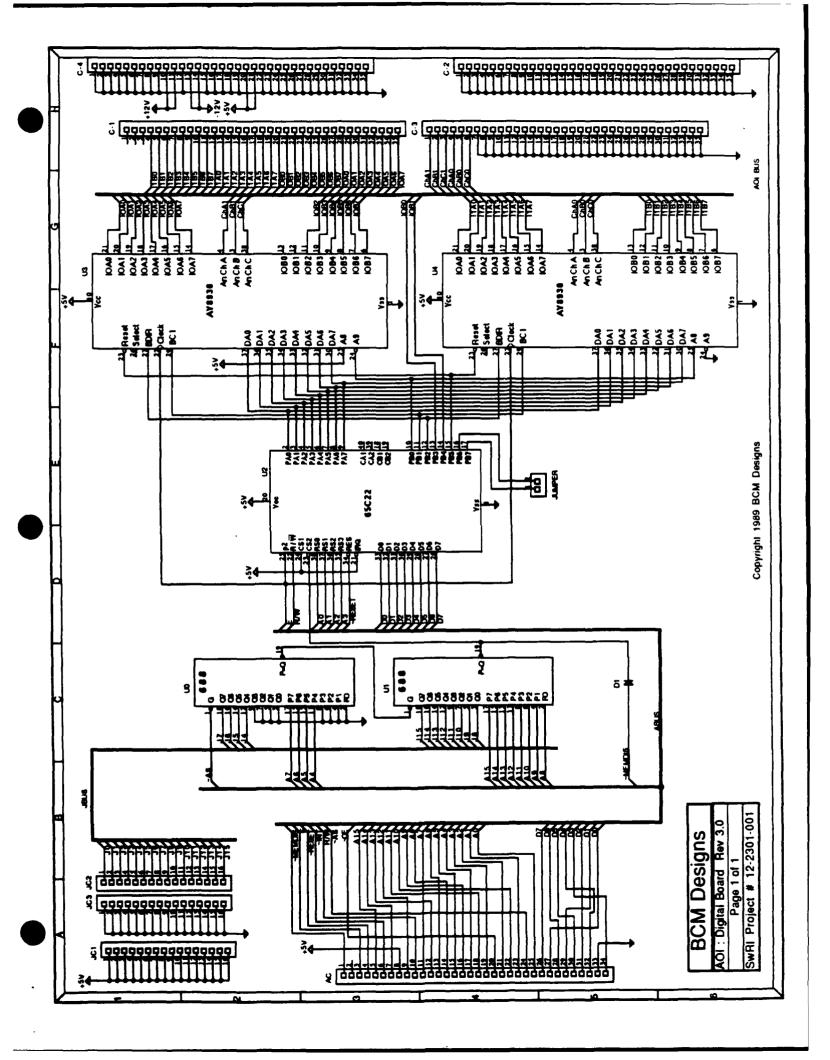

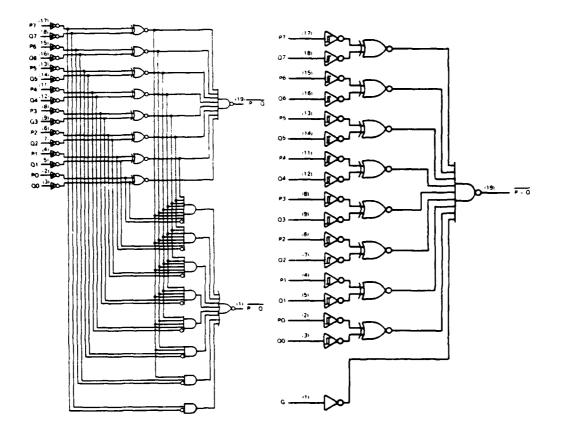

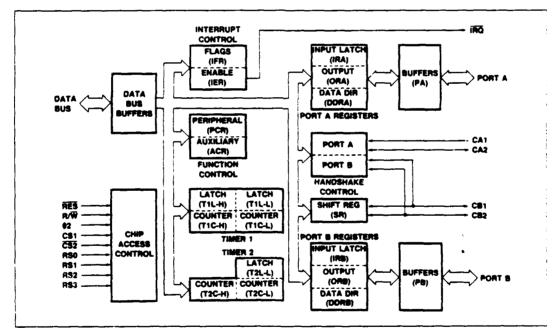

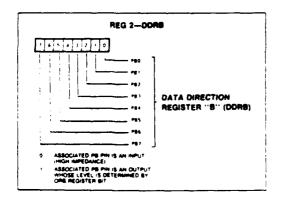

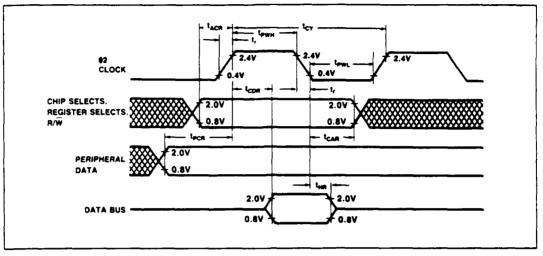

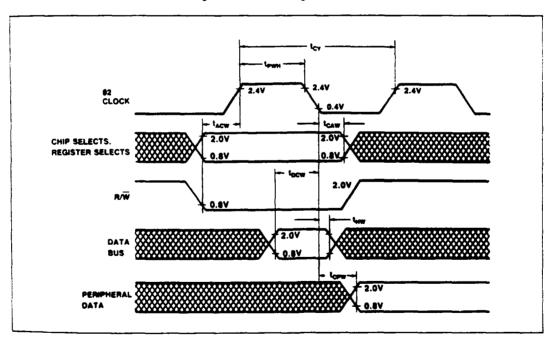

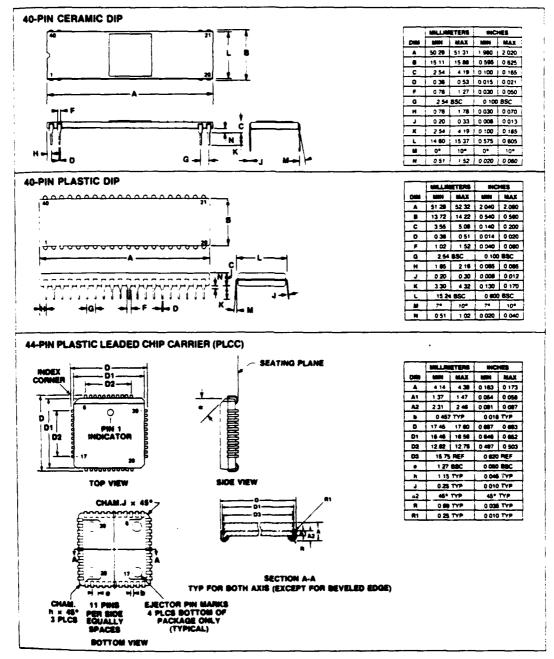

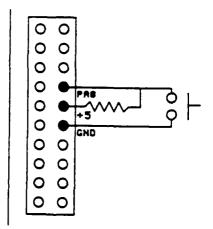

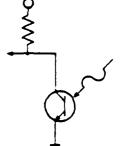

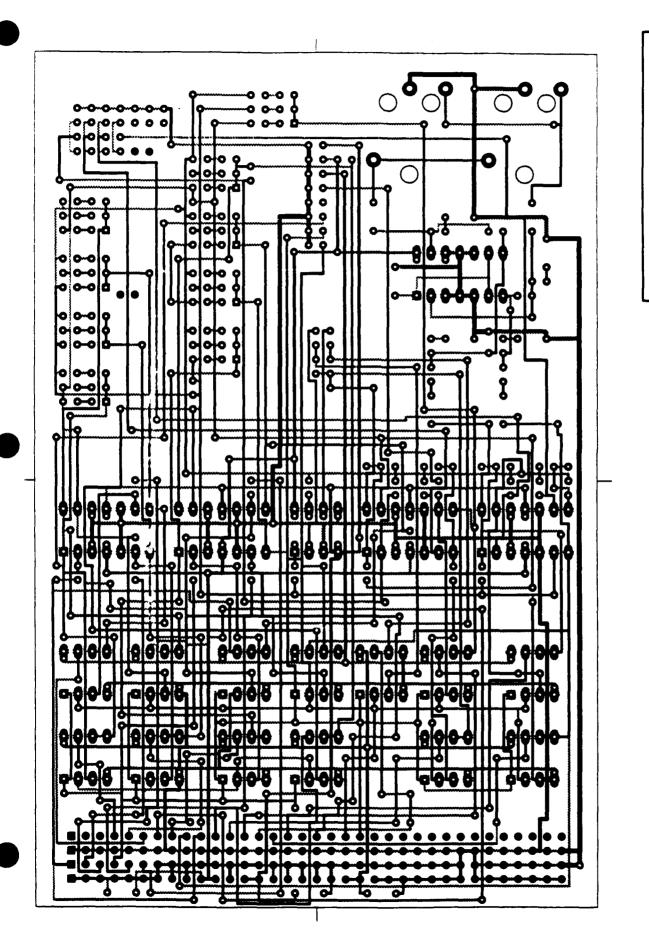

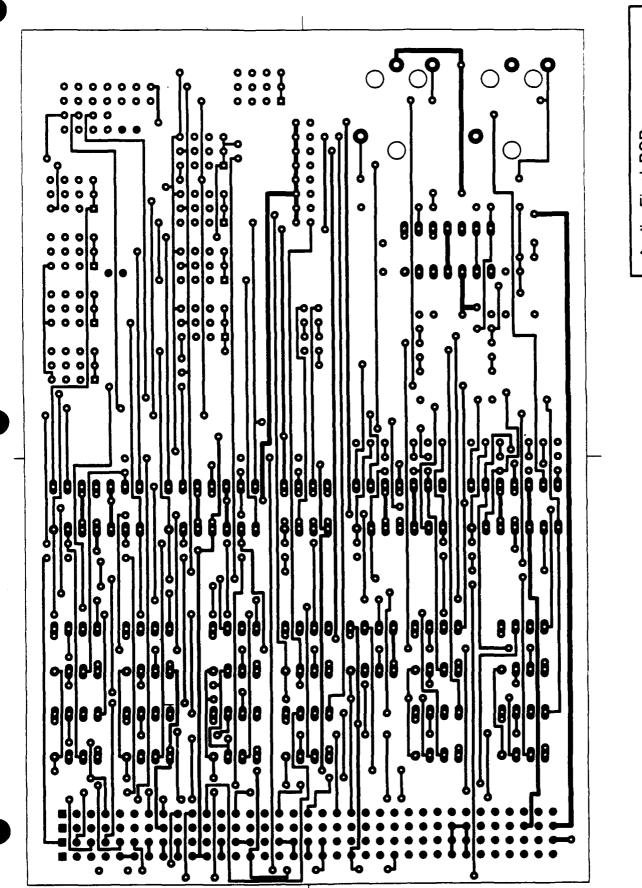

#### 6522/8930 Board

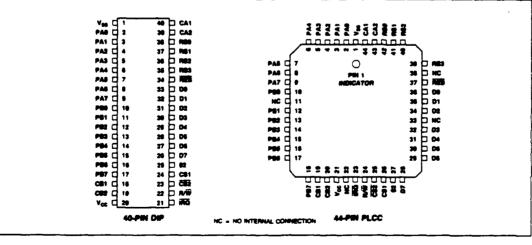

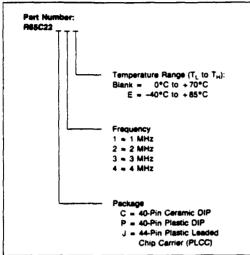

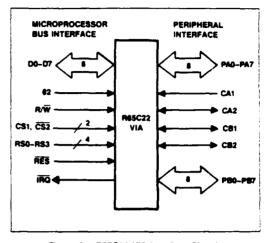

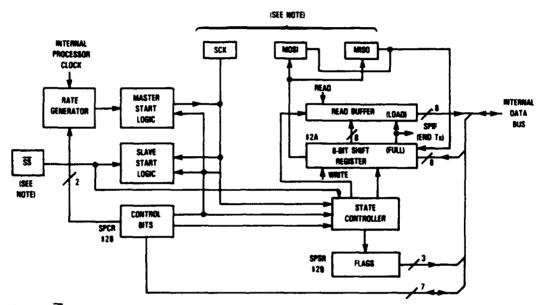

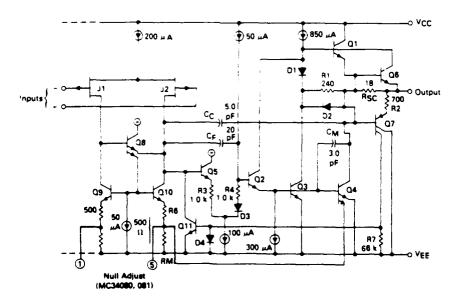

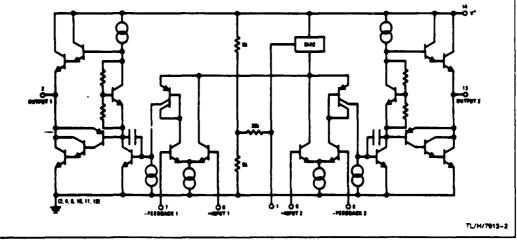

The 6522/8930 board is used in the system to generate acoustic signals. Two General Instruments AY-8930s are located on the board and provide up to six independent channels of digital audio. Each 8930 is separately memory mapped and operates independently. During the development of the system it was found that the 8930s are not directly compatible with the bus structure of the JEDSTACK. To correct the interface signal problems, a Rockwell Semiconductor 65C22 was used. This single 65C22 provides two extra parallel ports and thereby the ability to synthesize a secondary bus used to interface the AY-8930s to the 68HC11/F.

#### **Board Function**

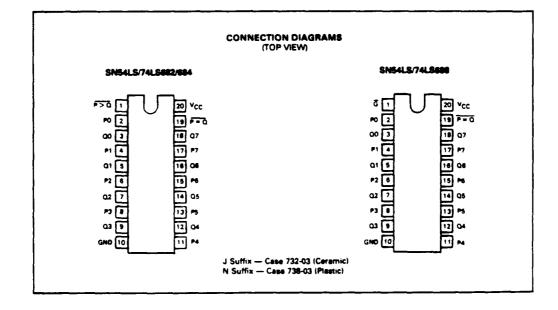

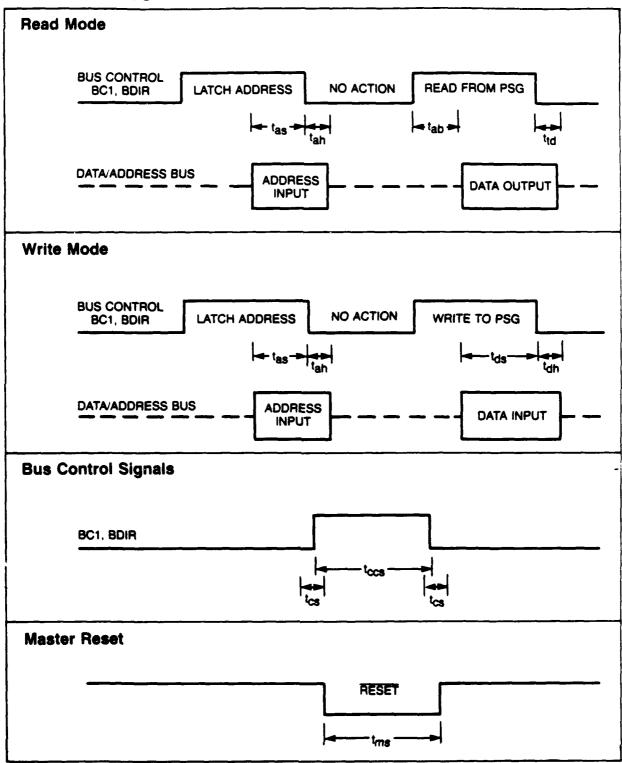

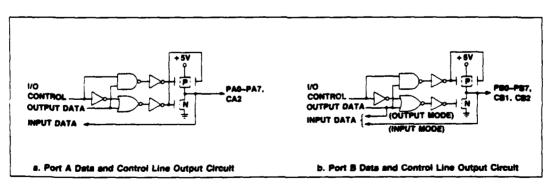

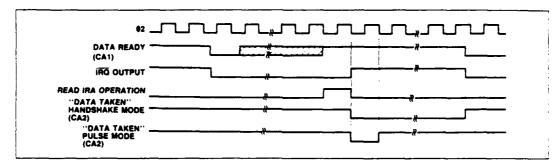

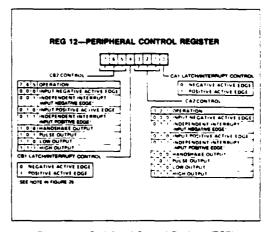

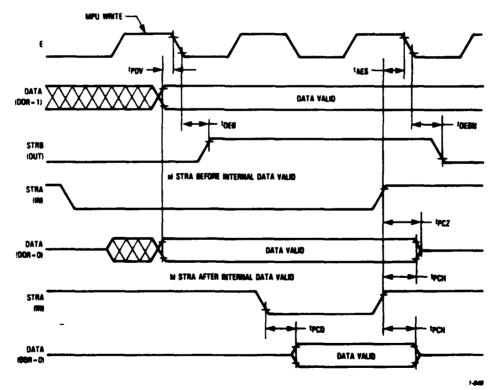

Signals from the bus are decoded by two 74HC688 8 bit bus comparators. The board is decoded in 16 bytes of RAM and can be located anywhere within the free memory space of the microprocessor. The dual 688s decode address lines A15-A4 based on a low address strobe on the bus. The subsequent P = Q line pulls down memory disable and provides the chip select line to the 6522. All subsequent reads and writes to the 6522 are done using standard bus nomenclature. The 6522 is used in this application to synthesize the 8 bit data bus going to both AY-8930s and the required control lines BDIR, BC1, Reset, A8 and A9. Because of this synthetic bus, transfer rates to the AY-8930s are substantially lower than that which could be achieved using direct bus access. Fortunately, in this application, higher speed access was not a requirement.

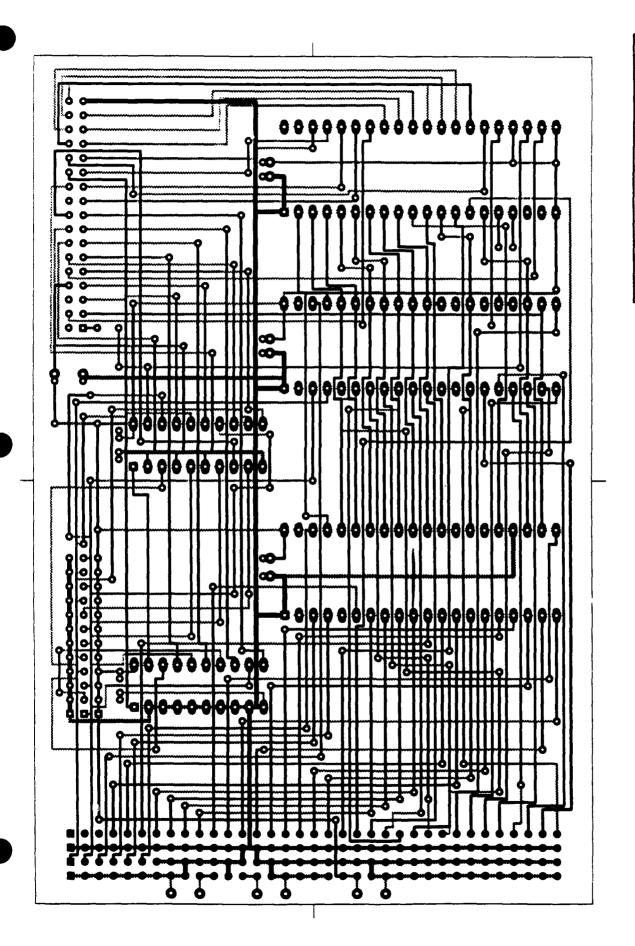

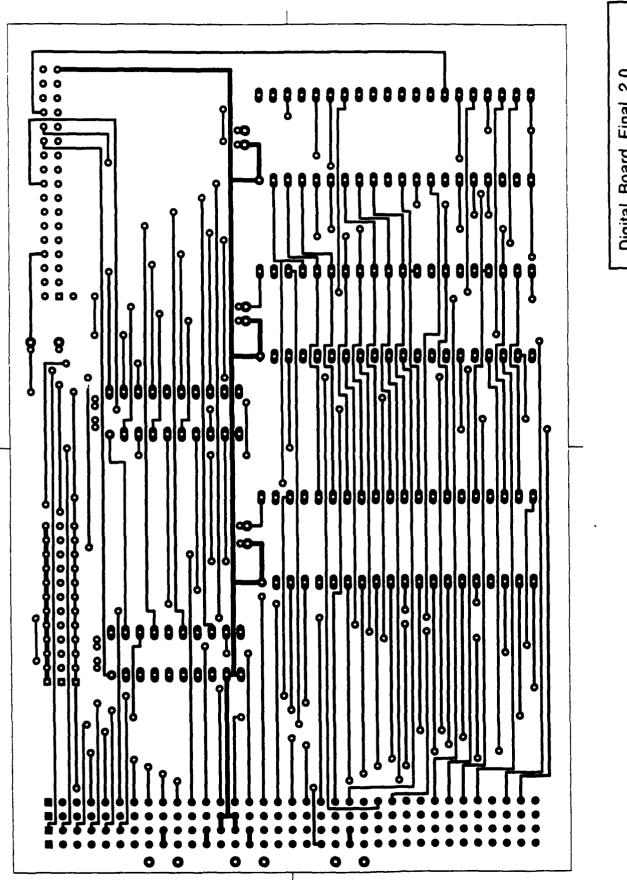

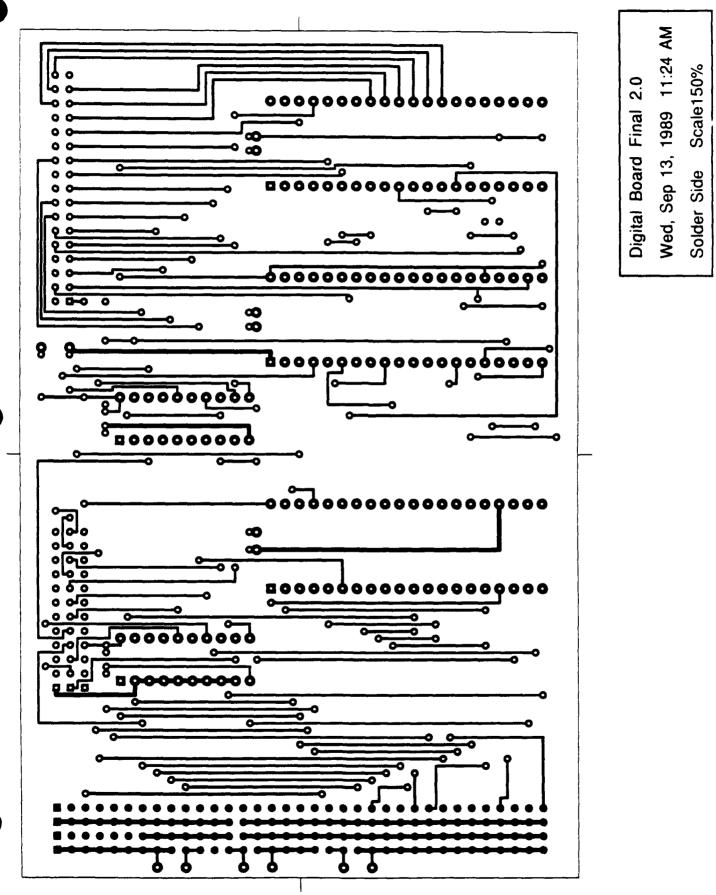

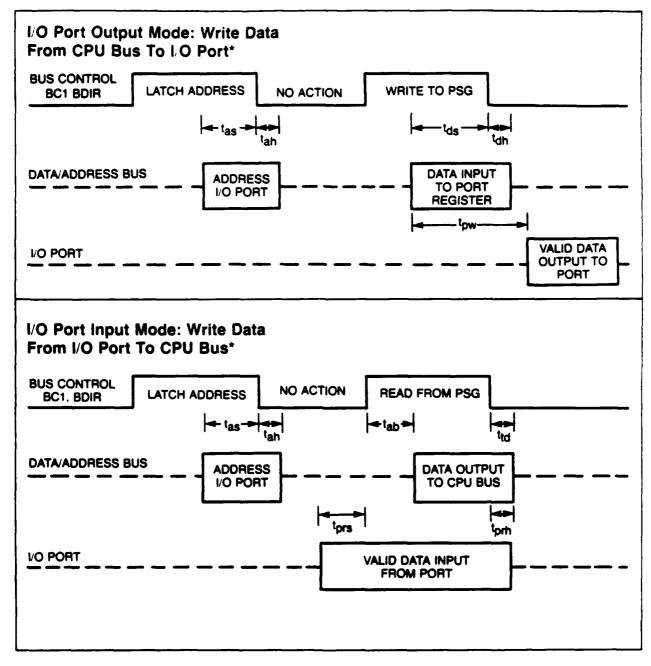

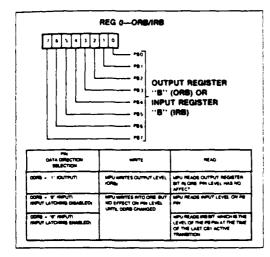

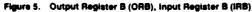

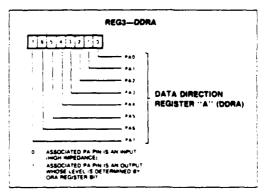

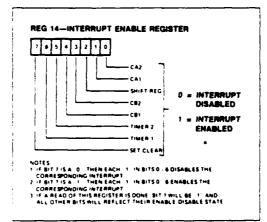

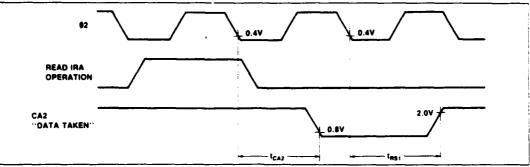

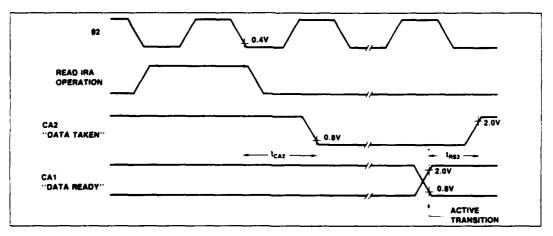

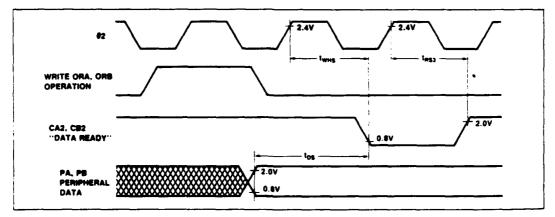

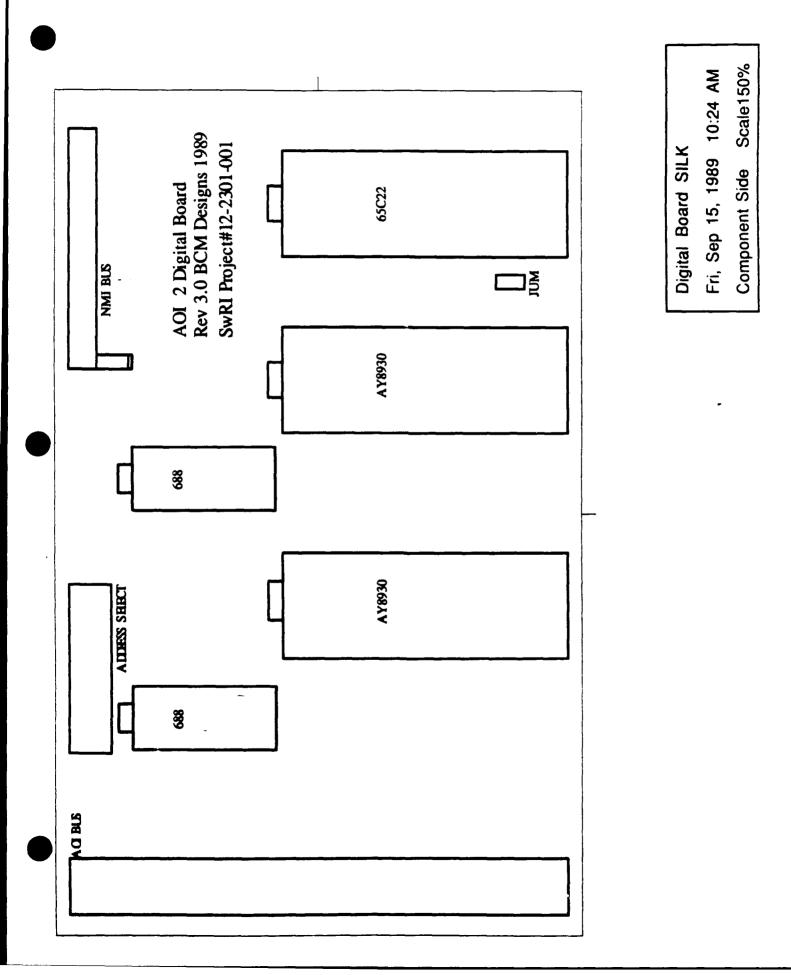

Port A on the 65C22 is used to provide data and address lines to both AY-8930s as shown in the schematic labeled AOI Digital Board Rev 3.0 in Appendix A. The 6522 pins CA1, CA2, CB1, CB2 are not used at this time. Port B synthesizes all of the control lines used for both of the AY-8930s. PB1 and PB2 are used to synthesize BDIR and BC1 on the 8930 chips. PB0 is used to select AY-8930-0 or AY-8930-1. AY-8930-0 has its control line A8 tied high thereby using a low signal on PB 5 to select it. AY-8930-1 has bit A9 tied low, and uses a high signal on A8 to select it. This single line provides simple, quick chip select logic between the two devices and guarantees that bus contention between the two chips never occurs.

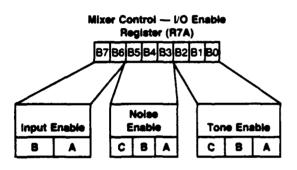

All of the parts on this board are clocked using the microprocessor's 2MHz clock. A secondary bus system is also provided on the AY-8930/6522 board. It consists of four rows of 35 pins located on the rear portion of the board and is designed for board-to-board interconnection. All signals from the 8930 as well as 12V, -12V, +5v, and ground are present on this bus. 1/0 control ports from both AY-8930s are used to control mixer board functions on the audio mixer board (see that section).

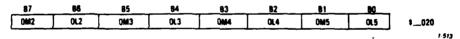

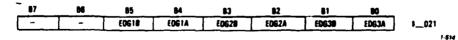

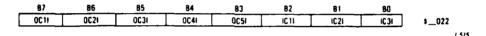

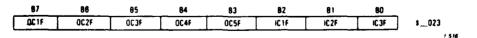

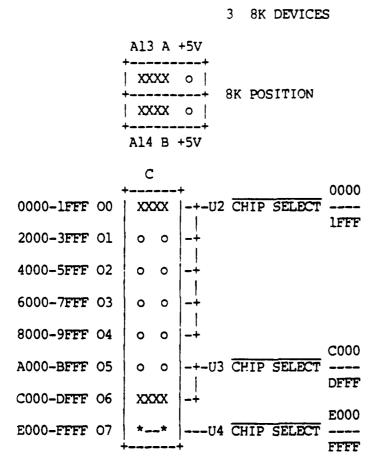

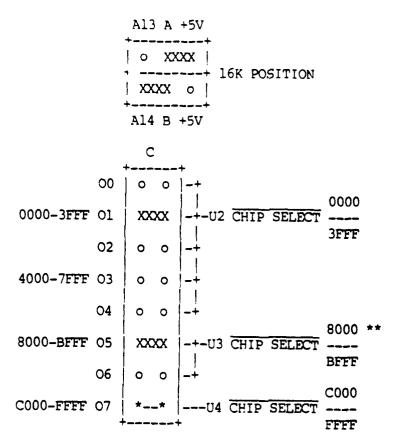

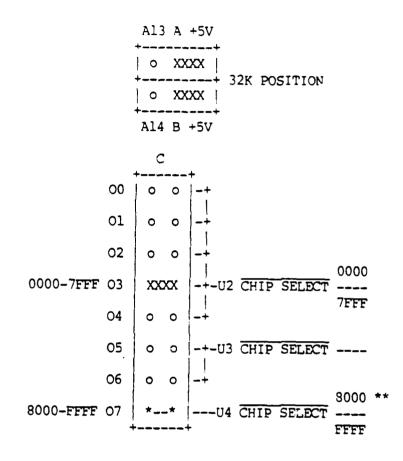

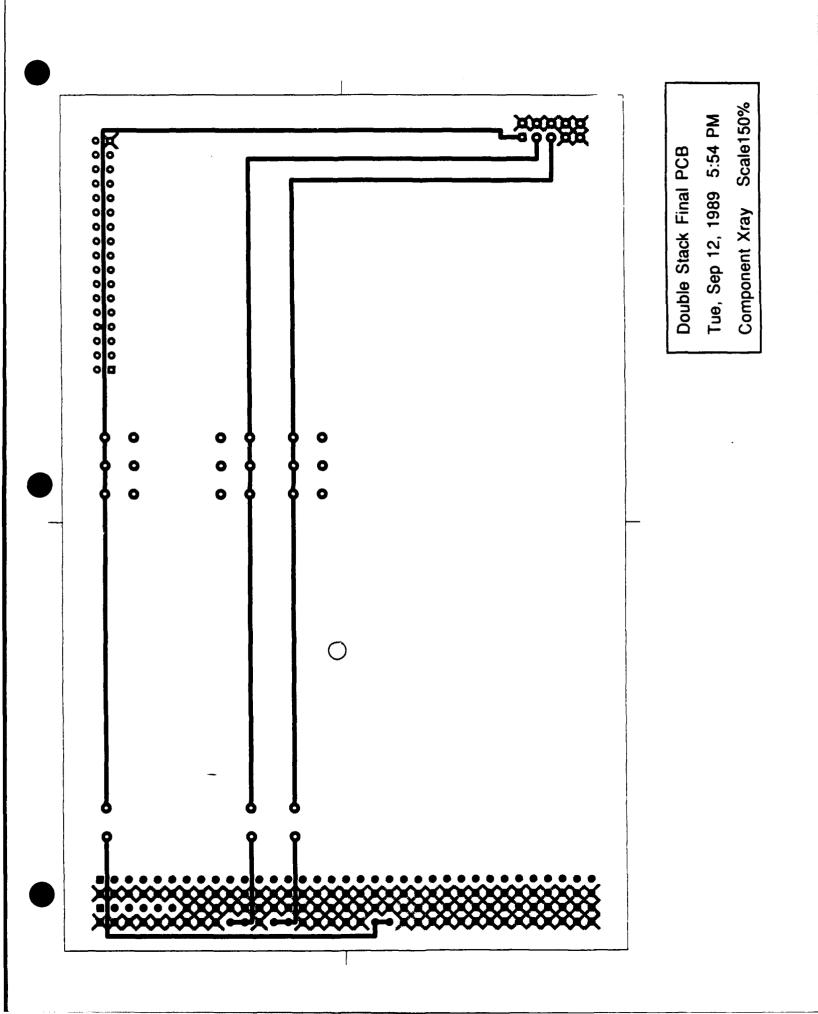

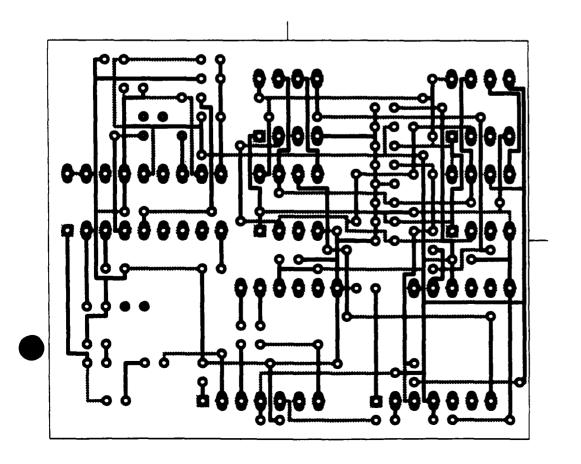

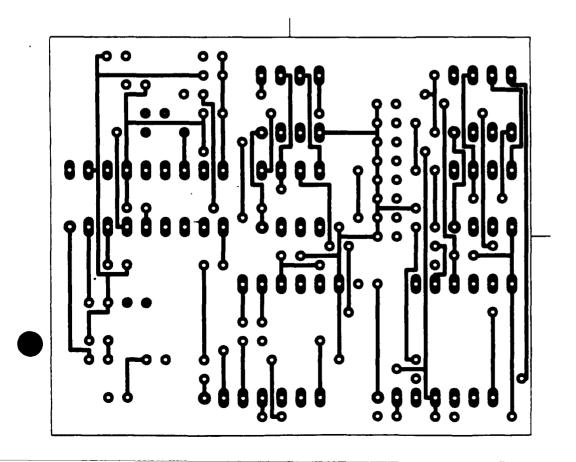

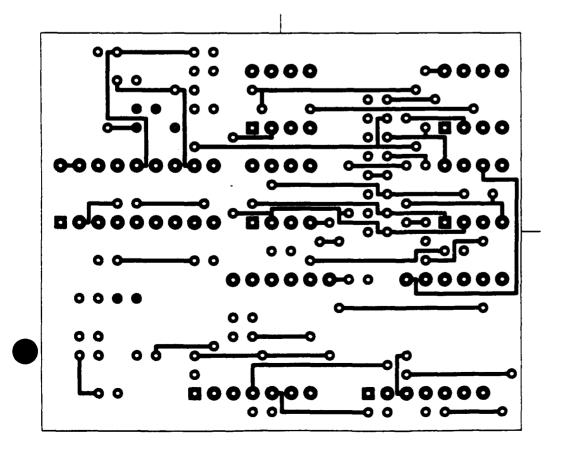

The board-to-board interconnection bus is configured as four rows of 35 pins. Row 1, labeled C1, contains all four of the 8 bit ports found on the AY-8930s. Row 2, C2, is completely grounded to provided isolation and noise immunity to the system. Row 3, C3, carries on pins 1-6, all stx channels of audio generated by the AY-8930s chips 0 and 1. Row 4, C4, contains ground, +12V, -12V and 5V. See the schematic for pin labeling on this bus. Silk screens for this board are provided in Appendix A. One 150% board layout is provided in Appendix A. A component list for this board is provided in Appendix G. A bit list for this board is shown on the following page.

# AOI II Digital Potentiometer Control Bit List

The following list shows the AY-8930 output bits used to control the digital potentiometers. All bits are shown with the AY-8930 pin number and the function.

10 = Chip 0

I1 = Chip 1

Negative logic is shown with a ~

| <u>Bit</u>                                | Function                                       | <b>Description</b>                                                                          |

|-------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------|

| IO- <b>B</b> 0                            | U/~D                                           | All U/D for the Xicors                                                                      |

| IO-B1                                     | INC Xicor Pot                                  | Increment all Xicors                                                                        |

| I1-AO                                     | Pre-Mixer Pot                                  | Level control                                                                               |

| 11- <b>A1</b>                             | Noise Level                                    | Noise level control                                                                         |

| 11- <b>A2</b>                             | Balance                                        | Balance Xicor control                                                                       |

| l1-A3                                     | Left Volume                                    | Post balance gain                                                                           |

| j1-A4                                     | Right Volume                                   | Post balance gain                                                                           |

| l1-A5                                     |                                                | Not Used                                                                                    |

|                                           |                                                |                                                                                             |

| i1-A6                                     | HP Filter                                      | Sets the pass band* tied to A7                                                              |

| 11-A6<br>11-B0                            | HP Filter<br>Ch 0A                             | Sets the pass band* tied to A7<br>Audio output gain                                         |

|                                           |                                                |                                                                                             |

| l1-B0                                     | Ch 0A                                          | Audio output gain                                                                           |

| 1-80<br> 1-81                             | Ch 0A<br>Ch 0B                                 | Audio output gain<br>Audio output gain                                                      |

| 1-80<br> 1-81<br> 1-82                    | Ch 0A<br>Ch 0B<br>Ch 0C                        | Audio output gain<br>Audio output gain<br>Audio output gain                                 |

| 11-B0<br>11-B1<br>11-B2<br>11-B3          | Ch 0A<br>Ch 0B<br>Ch 0C<br>all Chip 0          | Audio output gain<br>Audio output gain<br>Audio output gain<br>Mixer 0                      |

| 11-80<br>11-81<br>11-82<br>11-83<br>11-84 | Ch 0A<br>Ch 0B<br>Ch 0C<br>all Chip 0<br>Ch 1A | Audio output gain<br>Audio output gain<br>Audio output gain<br>Mixer 0<br>Audio output gain |

Note: I0-A0 through I0-B7 and Ch 0A, 0B, 0C, are from chip zero (0) and I1-A0 through I1-B7 and Ch 1A, 1B, 1C are from chip one (1).

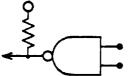

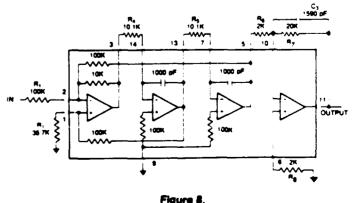

#### Audio Mixer Board

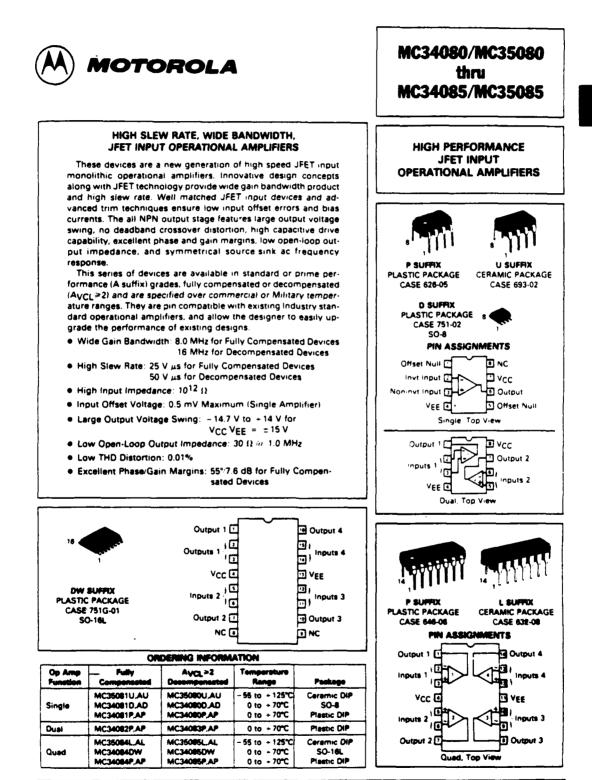

The Audio mixer board provides six channels of mix-down capability and final amplification of the audio signals generated by the 6522/8930 board. The board contains six channels of independent mixers with independent digitally controlled volume, two 3 to 1 mixers, mixers for four external signal sources with manually controlled potentiometers, computer-controlled balance circuitry, and final amplification. Also included on this board is a variable bandwidth filtered white noise source. Information about this board is in Appendix F.

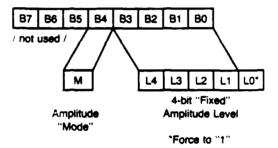

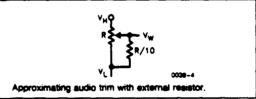

Each of the audio channels from the AY-8930 board (A,B,C AY-8930-0, A',B',C' AY-8930-1) are provided to this board using the board to board bus interconnections described under the AY-8930 board section. The board provides several stages of modification to the audio signal generated on the AY-8930 board. The first stage, buffering, attenuation and amplification, is realized using a digital XICOR potentiometer. The potentiometer is located on the feedback loop of the Op-amp used to buffer the digital signal to this board. Gains up to 2X and attenuation to .5X can be achieved with the 100 step potentiometer. Individual control of each of the six channels and each of the gain/amplification/attenuation network is provided using AY-8930 control bits (see the AY-8930 board bit list). Once amplified or attenuated, the raw signals are provided to jumper blocks J1-J3 for AY-8930-1 or J5-J7 for AY-8930-0. Each jumper block provides the user the capability of mixing the signal within the output group of that chip, or separating the signal to be used in the post-balance portion of this board's circuitry. If used in the default configuration all signals from the single attenuation /amplification stages, will be routed to the 3:1 mixer on IC1. At this point, all three of the signals from AY-8930-0 will be routed to IC2 and all signals from AY-8930-1 will be routed to IC1. In this configuration, complete 3:1 mixing is achieved on one guad opamp. The output of this 3:1 mixer is then sent to a 2:1, or final mixing stage, on IC3. IC3 also contains the amplifiers used in the external mixing sources referred to as pre-balance external mixers. Note that the output of both 3:1 mixers and the subsequent 4:1 include only monaural signals from the two AY-8930s and the two external signal sources. The external signal source opamps, located on IC3, provide up to .2X attenuation or +2X amplification of the external signal source. R12 and R13 (components list appendix G) are used to match the impedance and set the gain of the circuit for the external signals to the internal circuitry used on this PC board.

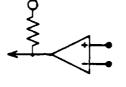

The final portion of circuitry in the prebalance mixing chain, op-amp 4, located on IC3, allows the user to digitally control all AY-8930 and two external prebalance signal sources before they are processed by the balance circuit. Complete digital control of attenuation and gain of this combined signal is provided using another XICOR digital potentiometer and the control lines found on the external bus. Once the signals are mixed, a balance circuit, utilizing one XICOR digital potentiometer and one MC34082 dual op-amp allows the users to modulate the signal source across the head of the pilot. Near full attenuation on either channel is attained using this system. Note that unity gain is provided through this circuit.

#### Balance Circuit - A note

Note, at this point in the circuitry the user is allowed to route signals either prebalance or postbalance. If prebalance is selected, all signals are mixed through IC3 op-amp 4. If post balance is selected, signals are routed to jumpers 1-9 pins 6 or 4 and are processed post balance. As was the case with the prebalance signals, two external inputs are provided for the user. In contrast to the prebalance signals, the postbalance external mixers are either external left or external right. Crossover between the two channels is nonexistent. The final stage before power amplification mixes any signals routed from the prebalance mixers or external prebalance signal sources and the external post balance sources. Again, digital gain using the XICOR digital potentiometers is provided with attenuation characteristics similar to those mentioned above.

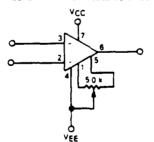

Final mixers, located on IC2, op-amps 2 and 4, are routed to the LM 1877 power amplifier. This power amplifier is capable of driving loads up to 8 ohms at one watt. Two jacks have been provided on the AOI front panel both wired in parallel. Because of this, impedance calculations should be considered before attaching any low impedance systems.

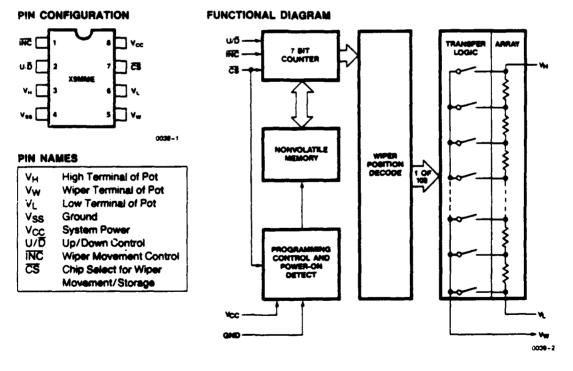

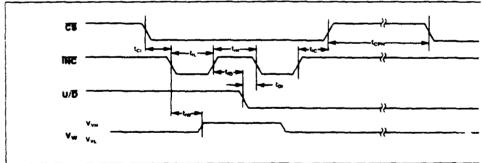

#### **XICOR Digital Potentiometers**

The XICOR digital potentiometers (data sheet shown in Appendix F) provide full digital control of an IC-based 100 step potentiometer. In the AOI system, 10K, 50K, and 100K ICs are used. Implementation of the potentiometers on this board is simple. All up, down, and increment lines are tied to a single pin and are operated using the AY-8930 control pins. Chip select, Pin 7, is individually controlled across the entire board using individual pins on the AY-8930s (see the chip control data sheet under the AY-8930 section). This implementation provides two features. The first, the lessening of control lines by ganging all up/down and increment lines together, provides a simpler and less noisy board layout. The second, individual control of chip select but not up/down and increment, provides high speed chip select and the ability to gang together the operation of several devices at once, i.e., the entire AY-8930-0 audio can be attenuated while not affecting the channels on AY-8930-1.

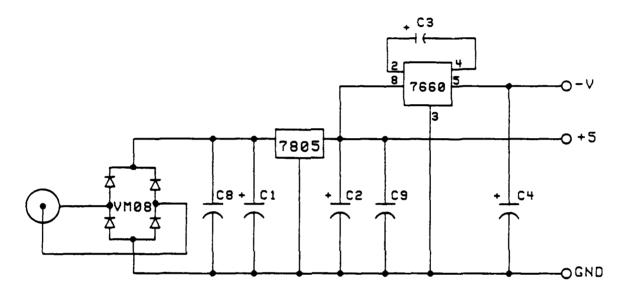

## The Ground Plane / Power Board

The ground plane power board provides two basic functions. The first, distribution of power and signals for the entire AOI system. The second, isolation of high frequency noise from the microprocessor unit to the sensitive analog audio portions of the AOI. Power from the external DB-9 power connector is routed directly across the board through several bypass capacitors and ferrite beads. This implementation of power filtering provides not only low frequency filtering and decoupling but also high frequency noise attenuation. Once the power is brought to the board, it is distributed to both the AY-8930 board to board bus, busses C1-C4, and connector AC1. Complete schematics, board layouts, and pin numbering for this board can be found in Appendix D.

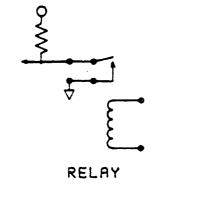

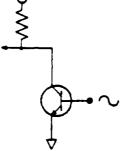

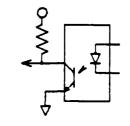

## Noise Filter Board

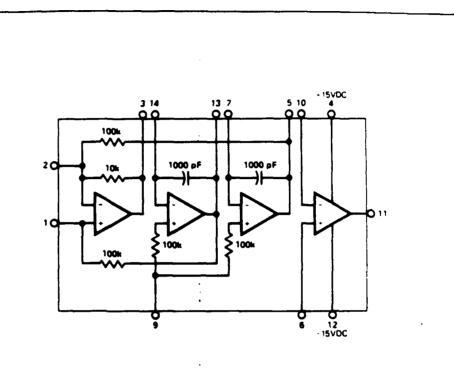

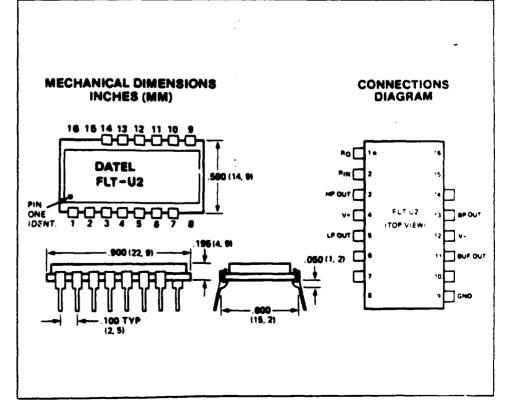

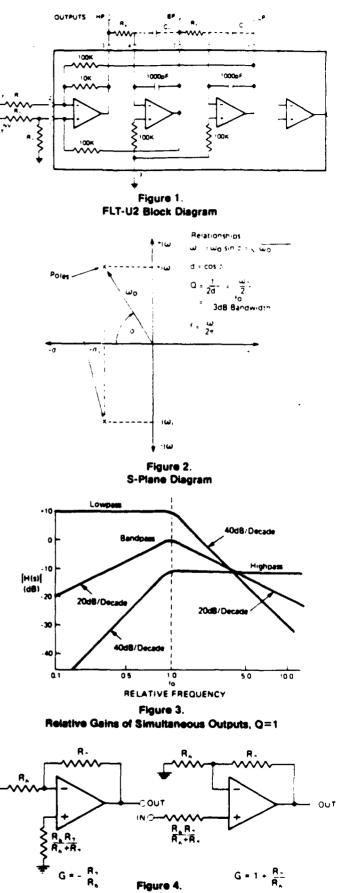

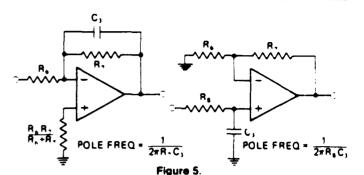

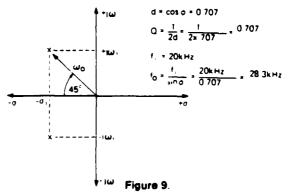

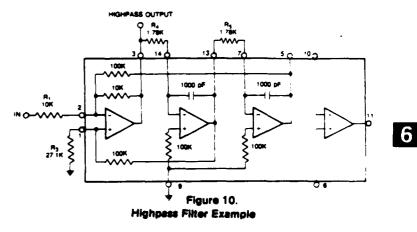

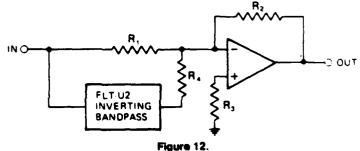

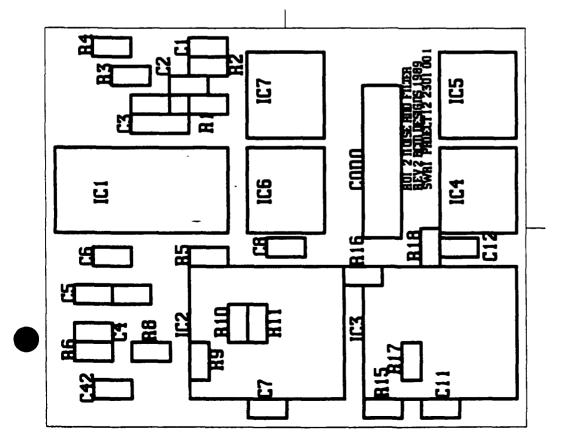

The noise filter board, a final addition to the AOI-II system, consists of a white noise source, a fixed low pass and variable high pass digitally controlled filter system. Wide band white noise is achieved using the LM389 audio op-amp. The op-amp and its associated free transistor are used in conjunction to generate white noise. The transistor shown in the data sheet, located in Appendix E, is used in an open collector mode to generate transistor noise. The resulting noise is amplified and used within this circuit. The resulting signal is processed using a variable high pass. fixed low pass, band passed filter configuration. This filter utilized a fixed low pass edge, located on IC2, and a variable high pass, Located on IC3. The filter building blocks, consisting of four free op-amps on the FLT-U2s, provide not only stable, easy to configure filter configurations, but also in the case of the high pass variability, provide a simple resistor based frequency cut-off variations. In this configuration four XICOR pots are used to set the cut-off filter frequency. The four pots on the board share the up/down and increment lines found on the main board. A single chip select line is used for all of the XICOR pots on this board. The board has been developed as a daughter board, and because of this, all signals provided through connector C0 on the mixer audio board. Note that 5V, -12V, +12V and ground are also provided through this connector. Because of the mechanical features of this board, and because of its mounting position on the audio mixer board, care must be taken when mounting or unmounting these components. See Appendix E for schematics, board layouts and other information on the FLT-U2 Universal Filter Building Block.

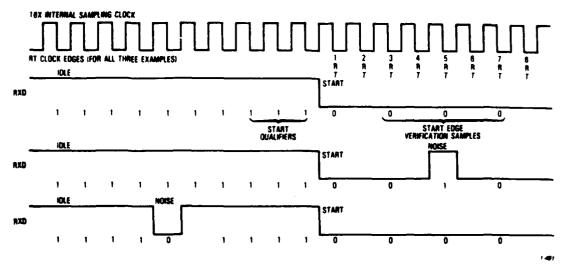

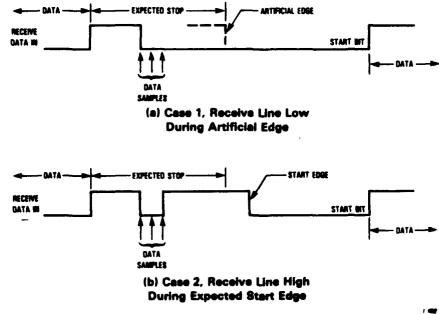

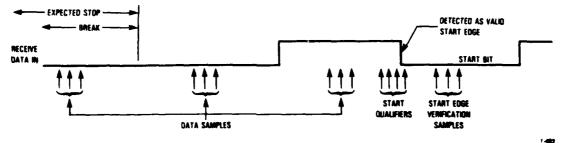

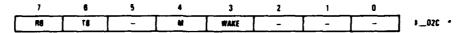

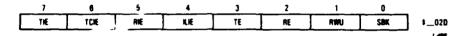

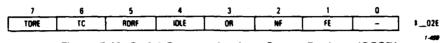

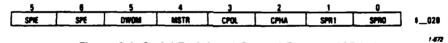

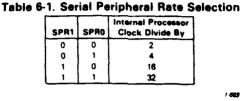

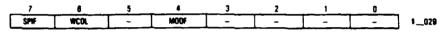

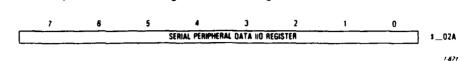

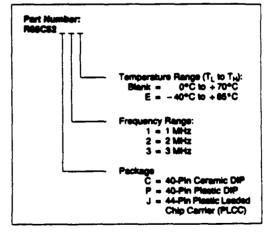

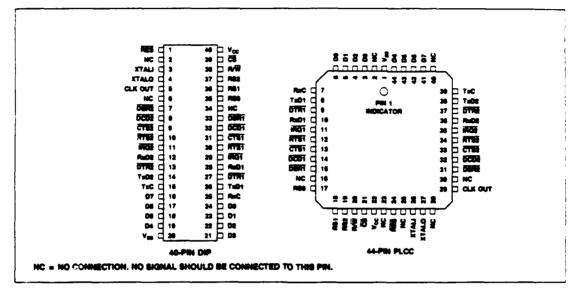

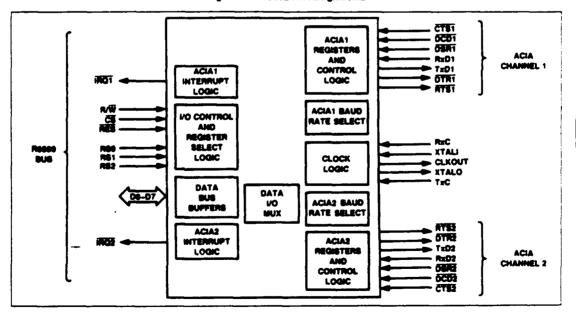

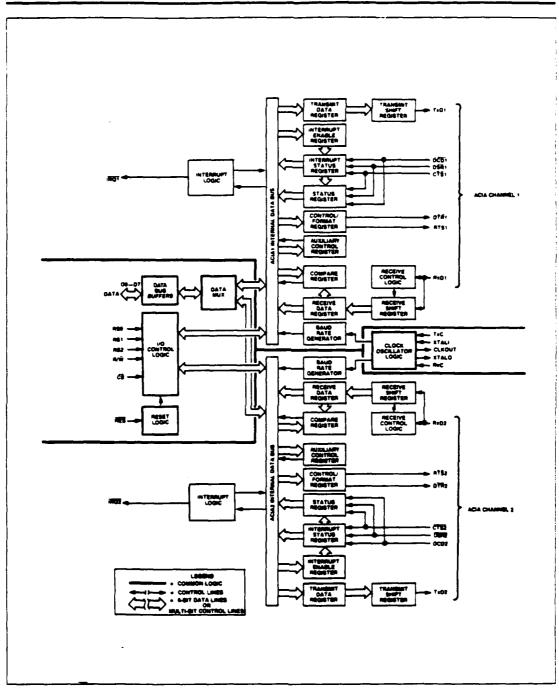

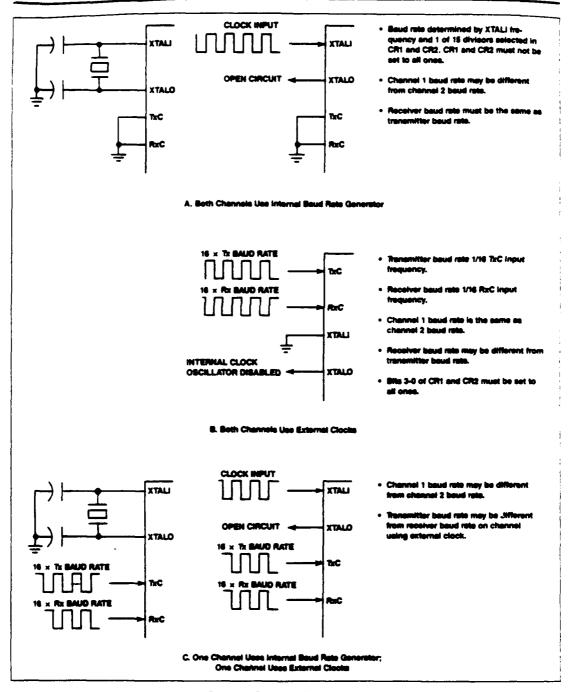

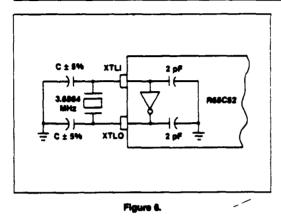

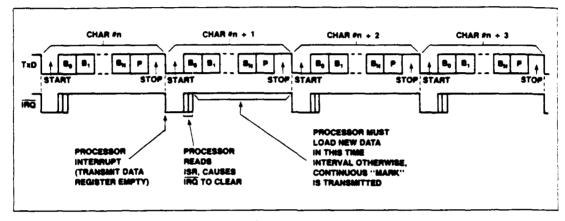

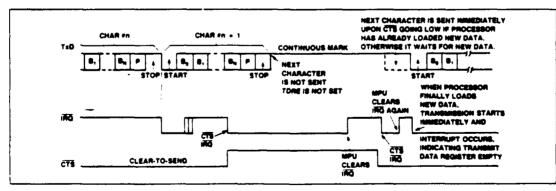

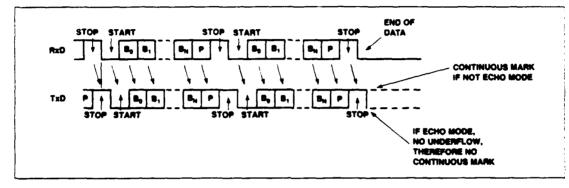

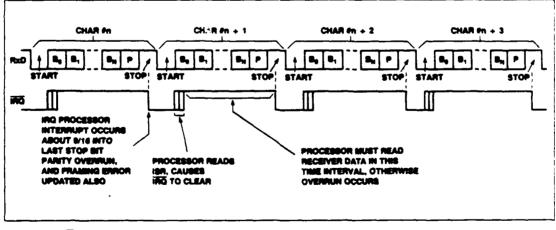

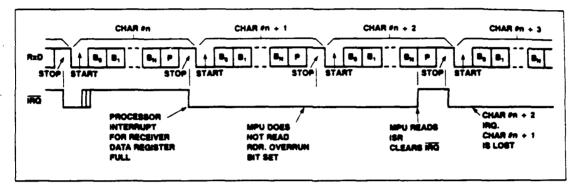

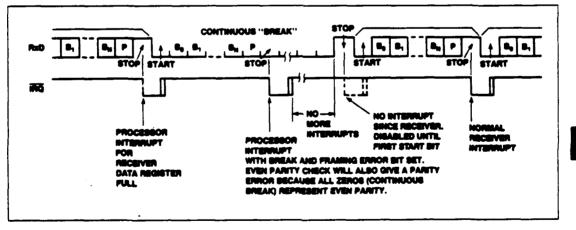

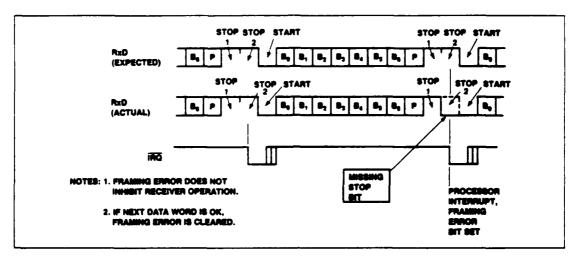

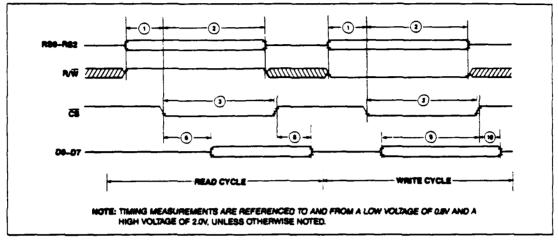

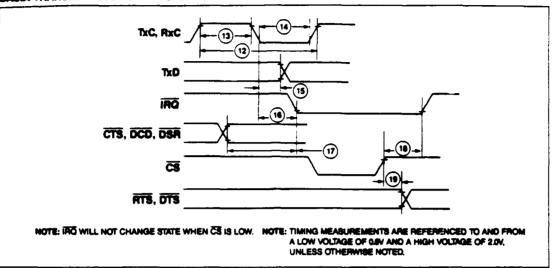

## 6255 Board

The final board in the system is the 6255 New Micros dual ACIA board. This board consisting of a Rockwell 6552 dual ACIA that provides two 8 bit serial ports memory mapped under full control of the microprocessor to the AOI-II. Only a single port on this board is used to communicate between the AOI and the FIP. For a description of the protocols used, see the module ACIACOM in the source code in Appendix H on the software. Detailed information on the 65C52 dual ACIA is provided in Appendix C.

Appendix A - 8930/6522 board

1

Appendix A - PCB schematics

Appendix A - PCB layouts

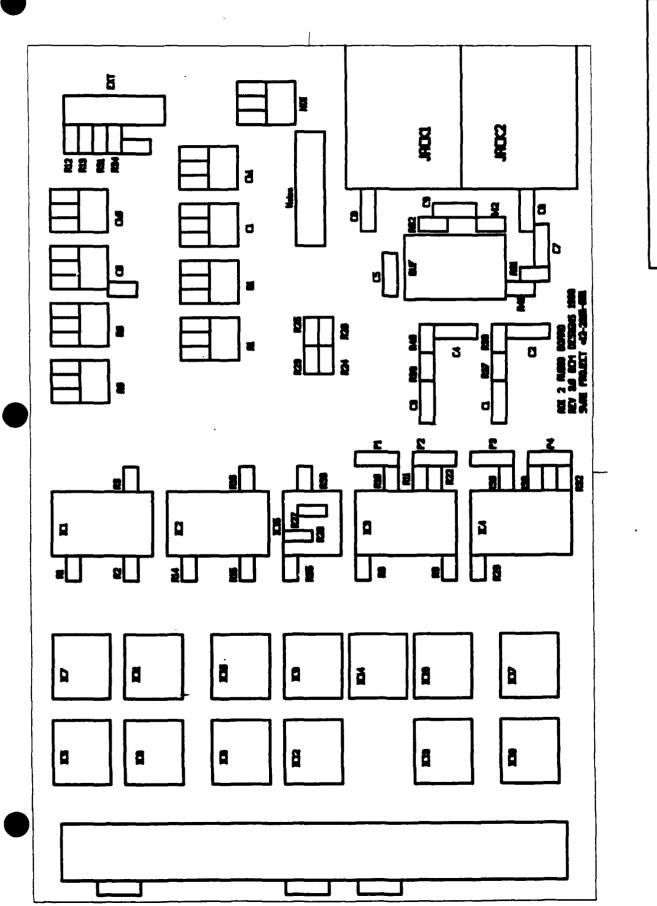

Digital Board Final 2.0 Wed, Sep 13, 1989 11:24 AM Component Xray Scale150%

Digital Board Final 2.0 Wed, Sep 13, 1989 11:24 AM Component Side Scale150%

Appendix A - data sheets 74LS688

data.

**DESCRIPTION** — The SN54LS/74LS682, 684, 688 are 8-bit magnitude comparators. These device types are designed to perform comparisons between two eight-bit binary or BCD words. All device types provide  $\overline{P=Q}$  outputs and the LS682 and LS684 have  $\overline{P>Q}$  outputs also.

The LS682, LS684 and LS688 are totem pole devices. The LS682

has a 20 kΩ pullup resistor on the Q inputs for analog or switch

SN54/74LS682 SN54/74LS684 SN54/74LS688

#### 8-BIT MAGNITUDE COMPARATORS

LOW POWER SCHOTTKY

| TYPE  | ₽=Q | P>Q | OUTPUT | OUTPUT<br>CONFIGURATION | PULLUP |

|-------|-----|-----|--------|-------------------------|--------|

| LS682 | yes | yes | no     | totem-pole              | yes    |

| LS683 | yes | yes | no     | open-collector          | yes    |

| LS684 | yes | Yes | no     | totem-pole              | no     |

| LS685 | yes | yes | no     | open-collector          | no     |

| LS686 | Yes | Yes | yes    | totem-pole              | no     |

| LS687 | yes | Yes | yes    | open-collector          | no     |

| LS688 | yes | no  | yes    | totem-pole              | no     |

| LS689 | yes | no  | ves    | open-collector          | no     |

| FUNCTION   | TABLE |

|------------|-------|

| 1011011011 |       |

|                                                               | INPUTS  |     | OUTPUTS                   |     |  |  |

|---------------------------------------------------------------|---------|-----|---------------------------|-----|--|--|

| DATA                                                          | ENABLES |     |                           |     |  |  |

| P. Q                                                          | G, GT   | G2  | $\mathbf{P} = \mathbf{Q}$ | P>Q |  |  |

| P = Q                                                         | L       | L   | L                         | н   |  |  |

| P > Q                                                         | L       | ίL. | н                         | L   |  |  |

| P <q< td=""><td>( L</td><td>L</td><td>Í Н</td><td>н</td></q<> | ( L     | L   | Í Н                       | н   |  |  |

| x                                                             | н       | ÌН. | н                         | H-  |  |  |

.

H = high level, L = low level, X = intelevant

FAST AND LS TTL DATA

## SN54/74LS682 + SN54/74LS684 + SN54/74LS688

#### GUARANTEED OPERATING RANGES

. .

| SYMBOL | PARAMETER                           |          | MIN         | TYP        | MAX         | UNIT |

|--------|-------------------------------------|----------|-------------|------------|-------------|------|

| Vcc    | Supply Voltage                      | 54<br>74 | 4.5<br>4.75 | 5.0<br>5.0 | 5 5<br>5.25 | v    |

| TA     | Operating Ambient Temperature Range | 54<br>74 | 55<br>0     | 25<br>25   | 125<br>70   | °C   |

| Юн     | Output Current High                 | 54.74    |             |            | -04         | 4    |

| IOL    | Output Current — Low                | 54<br>74 |             |            | 12<br>24    | п.А  |

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL    | PARAMETEI               |                   |     | LIMITS |      | UNITS | TEST CONDITIONS                                                                    |                     |  |

|-----------|-------------------------|-------------------|-----|--------|------|-------|------------------------------------------------------------------------------------|---------------------|--|

| STMBUL    | PARAMETER               | n                 | MIN | TYP    | MAX  |       | IEST                                                                               | CONDITIONS          |  |

| ∨ін       | Input HIGH Voltage      |                   | 2.0 |        |      | v     | Guaranteed Input HIGH Voltage for<br>All Inputs                                    |                     |  |

|           |                         | 54                |     |        | 0.7  |       | Guaranteed In                                                                      | put LOW Voltage for |  |

| VIL       | Input LOW Voltage       | 74                |     |        | 0.8  | 1 *   | All Inputs                                                                         |                     |  |

| VIK       | Input Clamp Diode Volta | ge                |     | -0.65  | ~1.5 | V     | VCC = MIN. IIN = -18 mA                                                            |                     |  |

|           |                         | 54                | 2.5 | 3.5    |      | V     | $V_{CC} = MIN$ , $I_{OH} = MAX$ , $V_{IN} = V_{IH}$<br>or $V_{IL}$ per Truth Table |                     |  |

| ЧОН       | Output HIGH Voltage     | 74                | 27  | 3.5    |      | V     |                                                                                    |                     |  |

| ·····     |                         | 54,74             |     | 0.25   | 0.4  | V     | IOL = 12 mA                                                                        | VCC = VCC MIN.      |  |

| VOL       | Output LOW Voitage      | 74                |     | 0.35   | 0.5  | v     | IOL = 24 mA VIN = VIL or VIN<br>per Truth Table                                    |                     |  |

|           |                         |                   |     |        | 20   | μA    | VCC = MAX.                                                                         | VIN = 2.7 V         |  |

| чн        | Input HIGH Current      | LS682-Q<br>Inputs |     |        | 0.1  | mA    | V <sub>CC</sub> = MAX. V <sub>IN</sub> = 5.5 V                                     |                     |  |

|           |                         | Others            |     |        | 01   | mA    | VCC = MAX.                                                                         | VIN = 7.0 V         |  |

| ۰.<br>۱۱L | Input LOW Current       | LS682-Q<br>Inputs |     |        | -0.4 | mA    | VCC = MAX                                                                          | /m = 0.4 V          |  |

|           |                         | Others            |     |        | -0.2 | mA    |                                                                                    |                     |  |

| los       | Short Circuit Current   |                   | -30 |        | -130 | mA    | V <sub>CC</sub> = MAX                                                              |                     |  |

|           |                         | LS682             |     |        | 70   | mA    |                                                                                    |                     |  |

| 'cc       | Power Supply Current    | LS684             |     |        | 65   | mA    | VCC = MAX                                                                          |                     |  |

|           |                         | LS668             |     |        | 65   | mA    |                                                                                    |                     |  |

FAST AND LS TTL DATA

#### SN54/74LS682 + SN54/74LS684 + SN54/74LS688

## LOGIC DIAGRAMS

SN54LS/74LS682 thru L8684

SN54L\$/74L3005

FAST AND LS TTL DATA

5-321

#### SN54/74LS682 + SN54/74LS684 + SN54/74LS688

## AC CHARACTERISTICS: TA = 25°C

#### SN54L5/74L5682

|              |                                                       |     | LIMITS   |          |       | TEST CONDITIONS                                                             |  |  |

|--------------|-------------------------------------------------------|-----|----------|----------|-------|-----------------------------------------------------------------------------|--|--|

| SYMBOL       | PARAMETER                                             | MIN | TYP      | MAX      | UNITS | TEST CONDITIONS                                                             |  |  |

| ԳՈԼ<br>ՄԲՈԼ  | Propagation Delay, P to $\overline{P} = Q$            |     | 13<br>15 | 25<br>25 | ns    |                                                                             |  |  |

| ФLH<br>ФHL   | Propagation Delay, Q to $\overline{P} = \overline{Q}$ |     | 14<br>15 | 25<br>25 | ns    | V <sub>CC</sub> = 5 0 V<br>C <sub>L</sub> = 45 pF<br>R <sub>L</sub> = 667 Ω |  |  |

| tPLH<br>tPHL | Propagation Delay, P to $\overline{P > Q}$            |     | 20<br>15 | 30<br>30 | ns    |                                                                             |  |  |

| ምLH<br>ምዘL   | Propagation Delay, Q to $\overline{P > Q}$            |     | 21<br>19 | 30<br>30 | ns    |                                                                             |  |  |

#### SN54LS/74LS684

|                                      |                                                             |     | LIMITS   |          |       | TECT CONDITIONS          |  |  |

|--------------------------------------|-------------------------------------------------------------|-----|----------|----------|-------|--------------------------|--|--|

| SYMBOL                               | PARAMETER                                                   | MIN | TYP      | MAX      | UNITS | TEST CONDITIONS          |  |  |

| <sup>ир</sup> LH<br><sup>I</sup> PHL | Propagation Delay, P to $\overline{P} = \overline{Q}$       |     | 15<br>17 | 25<br>25 | ns    | -                        |  |  |

| IPLH<br>IPHL                         | Propagation Delay, Q to $\overline{P} \approx \overline{Q}$ |     | 16<br>15 | 25<br>25 | ns    | $V_{CC} = 50V$           |  |  |

| чрін<br>чрні                         | Propagation Delay, P to $\overline{P > Q}$                  |     | 22<br>17 | 30<br>30 | ns    | CL ≠ 45 pF<br>RL = 667 Ω |  |  |

| 1PLH<br>1PHL                         | Propagation Delay, Q to $\overline{P > Q}$                  |     | 24<br>20 | 30<br>30 | ns    |                          |  |  |

#### SN54LS/74LS688

|                          |                                                                                      |     | LIMITS   |          | LINET C | TEST CONDITIONS                                                            |  |

|--------------------------|--------------------------------------------------------------------------------------|-----|----------|----------|---------|----------------------------------------------------------------------------|--|

| SYMBOL                   | PARAMETER                                                                            | MIN | TYP      | MAX      | UNITS   | TEST CONDITIONS                                                            |  |

| <sup>и</sup> РLH<br>ИРHL | Propagation Delay, P to $\overline{P \approx Q}$                                     |     | 12<br>17 | 18<br>23 | ns      |                                                                            |  |

| tPLH<br>tPHL             | Propagation Delay, Q to $\overline{P} = \overline{Q}$                                |     | 12<br>17 | 18<br>23 | ns      | V <sub>CC</sub> = 50 V<br>C <sub>L</sub> = 45 pF<br>R <sub>1</sub> = 667 Ω |  |

| PLH<br>PHL               | Propagation Delay, $\overline{G}$ , $\overline{G1}$ to $\overline{P} = \overline{Q}$ |     | 12<br>13 | 18<br>20 | ns      | nt - 00/11                                                                 |  |

Appendix A - AY-8930

# AY8930

## **Enhanced Programmable Sound Generator**

## **FEATURES**

- Two Modes Available On-Chip

- AY8930 Expanded Mode

- AY-3-8910A-Compatible Mode

- Improved Frequency Range

- Three Independently Programmable Analog Output Channels with Separate Frequency, Duty Cycle and Envelope Controls for Each Channel

- 5 Bits of Logarithmic Digital-to-Analog Conversion Per Channel

- Bus Interface Independent of Clock Frequency

- Input Clock Frequency: 2 or 4MHz

- Two 8-Bit General Purpose I/O Ports

## DESCRIPTION

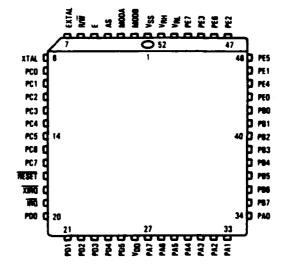

The AV9930 Enhanced Programmable Sound Generator (EPSG) is an LSI circuit that can produce a wide variety of complex sounds under software control. The AV8930 is manufactured in the Microchip Technology Inc. n-channel silicon gate process. The AV8930 is an enhanced version of the company's industry standard AY-3-8910A ~ \_-nd generator. Enhanced features include improved frequency range and noise synthesis and independent control of each channel's envelope and duty cycle.

The PSG is easily interfaced to any bus-oriented system. Its flexibility makes it useful in applications such as music synthesis, sound effects generation, audible alarms, tone signalling, and home computer usage. In order to generate sound effects while allowing the processor to perform other tasks, the PSG can continue to produce sound after the initial commands have been given by the control processor. The fact that realistic sound production often involves more than one effect is satisfied by the three independently controllable analog sound output channels available in the device. These analog sound output channels can each provide five bits of logarithmic digital-to-analog conversion, greatly enhancing the dynamic range of the sounds produced.

| PIN C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ONFIC                                                                                            | GUF                                                 | RATION                                                                                                                     |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|