| <br>ISSIFIE | ع ا |  |  | MICRO<br>DL SYS<br>PATTER |  |   |            |

|-------------|-----|--|--|---------------------------|--|---|------------|

|             |     |  |  |                           |  |   |            |

|             |     |  |  |                           |  | ÷ |            |

|             |     |  |  |                           |  |   |            |

| <u> </u>    |     |  |  |                           |  |   |            |

|             |     |  |  |                           |  |   |            |

|             |     |  |  |                           |  |   |            |

|             |     |  |  |                           |  |   | 714<br>117 |

|             |     |  |  |                           |  |   |            |

MICROCOP

CHART

ŝ

# AD-A167 914

AFWAL-TR-85-2074

PERFORMANCE ANALYSIS OF A MICROCOMPUTER-BASED SINGLE-LOOP DIGITAL CONTROL SYSTEM

M. Gauder

Data Acquisition Group Technology Branch

April 1986

FINAL REPORT FOR PERIOD AUGUST 1982 - AUGUST 1984

NTIL FILE COPY

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED

AERO PROPULSION LABORATORY AIR FORCE WRIGHT AERONAUTICAL LABORATORIES AIR FORCE SYSTEMS COMMAND WRIGHT-PATTERSON AIR FORCE BASE, OHIO 45433

LECTE

MAY 3 0 1986

B

- 5

86

ŝ

# NOTICE

When Government drawings, specifications, or other data are used for any purpose other than in connection with a definitely related Government procurement operation, the United States Government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data, is not to be regarded by implication or otherwise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use, or sell any patented invention that may in any way be related thereto.

This report has been reviewed by the Office of Public Affairs (ASD/PA) and is releasable to the National Technical Information Service (NTIS). At NTIS, it will be available to the general public, including foreign nations.

This technical report has been reviewed and is approved for publication.

Michael J. Llauder

MICHAEL J. GAUDER Project Engineer

Chief, Technology Branch

FOR THE COMMANDER

Bus

H. I. BUSH Director \* Turbine Engine Division Acro Propulsion Laboratory

"If your address has changed, if you wish to be removed from our mailing list, or if the addressee is no longer employed by your organization, please notify <u>AFWAL/POTX</u>, W-PAFB, OH 45433-6563 to help us maintain a current mailing list."

Copies of this report should not be returned unless return is required by security considerations, contractual obligations, or notice on a specific document.

| Unclassified            |    |      |      |

|-------------------------|----|------|------|

| SECURITY CLASSIFICATION | OF | THIS | PAGE |

| A | ٨.         | Δ | 16 | n | 91       | V |  |

|---|------------|---|----|---|----------|---|--|

|   | <u>y</u> - |   | 0  | 1 | <u> </u> | 7 |  |

|                     |                                     |               |             | REPORT DOCUME                                 | NTATION PAGE                                                                        |                      |                              |                                       |  |  |  |  |

|---------------------|-------------------------------------|---------------|-------------|-----------------------------------------------|-------------------------------------------------------------------------------------|----------------------|------------------------------|---------------------------------------|--|--|--|--|

| Unclass             |                                     |               |             |                                               | 15. RESTRICTIVE MARKINGS                                                            |                      |                              |                                       |  |  |  |  |

| N/A                 | TY CLASSIFIC                        |               |             |                                               | 3. DISTRIBUTION/AVAILABILITY OF REPORT<br>Approved for public release; distribution |                      |                              |                                       |  |  |  |  |

| 26. DECLAS          | SIFICATION                          | DOWNGR        | ADING SCHED |                                               | unlimited.                                                                          | public rel           | ease; distri                 | bution                                |  |  |  |  |

| 4. PERFOR           | MING ORGAN                          | IZATION       | REPORT NUM  | BER(S)                                        | 5. MONITORING OR                                                                    | GANIZATION RE        | PORT NUMBER(S)               |                                       |  |  |  |  |

|                     | L-TR-85                             |               |             |                                               |                                                                                     |                      |                              |                                       |  |  |  |  |

|                     | F PERFORM                           |               |             | 6b. OFFICE SYMBOL<br>( <i>if applicable</i> ) | 7a. NAME OF MONIT<br>Aero Propuls                                                   |                      |                              | Pot)                                  |  |  |  |  |

|                     | opulsion                            |               |             | AFWAL/POTX                                    | Air Force Wi                                                                        |                      | أنث عتمال استعوار والمعادي   | ratories                              |  |  |  |  |

|                     | SS (City, State<br>Wright           |               |             | boratories (AFSC)                             | 75. ADDRESS (City, S                                                                | State and ZIP Code   | e )                          |                                       |  |  |  |  |

|                     |                                     |               | H 45433-6   |                                               | Wright Patte                                                                        | erson AFB O          | H 45433-6563                 |                                       |  |  |  |  |

|                     | F FUNDING                           | SPONSORI      | NG          | 86. OFFICE SYMBOL                             | 9. PROCUREMENT                                                                      | NSTRUMENT IDE        | INTIFICATION NU              | MBER                                  |  |  |  |  |

| Aero_Pr             | IZATION<br>Opulsion<br>ce Wright    | Labora        | tory        | (If applicable)<br>AFWAL/POTX                 | N/A                                                                                 |                      |                              |                                       |  |  |  |  |

|                     | <u>ce Wright</u><br>SS (City, State |               |             | L                                             | 10. SOURCE OF FUN                                                                   | DING NOS             |                              |                                       |  |  |  |  |

|                     |                                     | -             | н 45433-6   | 563                                           | PROGRAM                                                                             | PROJECT              | TASK                         | WORK UNIT                             |  |  |  |  |

|                     |                                     |               |             |                                               | ELEMENT NO.                                                                         | NO.                  | NO.                          | NO.                                   |  |  |  |  |

| 11 TITLE (          | Include Securi                      | ty Classifica | tion)Perfor | mance Analysis                                | 62203F                                                                              | 3066                 | 17                           | 20                                    |  |  |  |  |

|                     |                                     |               |             | -Loop Digital_                                |                                                                                     |                      |                              |                                       |  |  |  |  |

| 12. PERSON          | AL AUTHOR                           | (s) Cont      | rol Syste   |                                               | •                                                                                   |                      |                              | · · · · · · · · · · · · · · · · · · · |  |  |  |  |

|                     | J. Gaude                            | er            |             |                                               |                                                                                     |                      |                              |                                       |  |  |  |  |

|                     | OF REPORT                           |               | 136. TIME C |                                               | 14. DATE OF REPOR                                                                   |                      | 15. PAGE CC<br>79            | UNT                                   |  |  |  |  |

| Final<br>16. SUPPLE | MENTARY                             | OTATION       |             |                                               | <u> </u>                                                                            | <u>+</u>             |                              |                                       |  |  |  |  |

| Ret                 | ort cont                            | ains ha       | armless c   | omputer software                              | 2                                                                                   |                      |                              |                                       |  |  |  |  |

| 17.                 | COSATI                              |               |             | 18. SUBJECT TERMS (C                          |                                                                                     |                      |                              |                                       |  |  |  |  |

| FIELD               | GROUP                               |               | 8. GR.      | Microcompu                                    |                                                                                     | ceasery and identity | y by olock number            |                                       |  |  |  |  |

| 09                  | 02                                  |               |             | Analog com                                    |                                                                                     |                      |                              |                                       |  |  |  |  |

|                     |                                     |               |             | <u>Digital co</u>                             | ntrols                                                                              |                      |                              |                                       |  |  |  |  |

|                     |                                     |               |             | d identify by block number                    |                                                                                     |                      |                              |                                       |  |  |  |  |

| Digital             | control                             | system        | design h    | as been popular                               | in the aerosp                                                                       | ace and pro          | ocess contro                 | 1 :                                   |  |  |  |  |

|                     | ity The                             | ances :       | in microp   | rocessor technol<br>cocessor-based sy         | logies have ad                                                                      | ded new gro          | owth to this                 |                                       |  |  |  |  |

| demands             | on digit                            | al con        | trol theo   | ry. Since micro                               | valeus IVI com                                                                      | e relative           | ses praces n<br>ly elow digi | ew<br>tal                             |  |  |  |  |

| machine             | s and usu                           | ally h        | ave small   | work lengths, i                               | lt is necessar                                                                      | y to place           | importance                   | on the                                |  |  |  |  |

| effects             | of time                             | delays        | and ampl    | itude quantizati                              | lon with respe                                                                      | ct to the o          | control syst                 | em. The                               |  |  |  |  |

| word lei            | ngth and                            | speed         | of the si   | gnal processing                               | components; A                                                                       | nalog-to-Di          | lgital (A/D)                 | and                                   |  |  |  |  |

| Digital             | -to-Analo                           | <u>g (D/A</u> | ) convert   | ers placed addit                              | tional constra                                                                      | ints on the          | e digital co                 | ntrol                                 |  |  |  |  |

| involve             | d in micr                           |               | a order t   | o be able to ana<br>d control system          | alyze the effe                                                                      | cts of cons          | straints that                | t are                                 |  |  |  |  |

| a basic             | system a                            | ind a so      | et of pro   | cedures that are                              | e modifiable t                                                                      | o a variety          | essary to de                 | velop                                 |  |  |  |  |

| figurat             | ions.                               |               | - 4         |                                               |                                                                                     |                      | , or control                 | con                                   |  |  |  |  |

| (Contin             | ued on Re                           | verse)        |             |                                               |                                                                                     |                      |                              |                                       |  |  |  |  |

|                     |                                     |               | OF ABSTRA   | ст                                            | 21. ABSTRACT SECU                                                                   | RITY CLASSIFIC       | ATION                        |                                       |  |  |  |  |

| UNCLASSIF           | ED/UNLIMI                           | TED 'X S      | AME AS APT. |                                               | Unclassified                                                                        | l 、                  |                              |                                       |  |  |  |  |

|                     | OF RESPONS                          |               | VIDUAL      |                                               | 225 TELEPHONE NI<br>(Include Area Co                                                |                      | 22c. OFFICE SYM              | 30L                                   |  |  |  |  |

| Michael             | J. Gaude                            | er            |             |                                               | 513-255-390                                                                         |                      | AFWAL/POTX                   |                                       |  |  |  |  |

|                     | 1473, 83                            |               |             | EDITION OF 1 JAN 73 I                         | S OBSOLETE.                                                                         |                      |                              |                                       |  |  |  |  |

DD FORM 1473, 83 APR

SECURITY CLASSIFICATION OF THIS PAGE

SECURITY CLASSIFICATION OF THIS PAGE

Block 19. (Cont)

Accession For

281

nde 5

1.1.1.1

con 1

MR

۲ : ·

The subject of this thesis is the design, development, and analysis of a 16-bit microprocessor based digital control system. The purpose of the study is threefold:

1. To show that a hybrid computer system, consisting of 16-bit single board microcomputer and an analog computer, can be used effectively for digital control studies.

MAY 3 0 1986

B

SECURITY CLASSIFICATION OF THIS PAGE

2. To evaluate the frequency response of the hybrid system.

3. To identify and evaluate the error contributors which can effect the performance of digital control systems.

# TABLE OF CONTENTS

|     |                                                             | Page |

|-----|-------------------------------------------------------------|------|

| 1.Ø | INTRODUCTION                                                | 1    |

| 2.0 | DESIGN OF THE DIGITAL CONTROL SYSTEM                        | 3    |

|     | 2.1 Selection of the Microcomputer and Analog Computer      | 3    |

|     | 2.2 Digital Control System Configuration                    | . 3  |

|     | 2.3 Derivation of the Control Algorithms                    | . 7  |

|     | 2.4 Implementation of the Control Equation on the Micro-    |      |

|     | computer                                                    | 7    |

|     | 2.5 Simulation of Plant Parameters on the Analog Computer . | . 11 |

|     | 2.6 Interface Between the Microcomputer and Analog Computer | . 13 |

| 3.Ø | CONTROL LOOP PERFORMANCE ANALYSIS                           | . 16 |

|     | 3.1 Response to a Step Input                                | . 16 |

|     | 3.2 Response to Sinusoidal Inputs                           | . 19 |

|     | 3.3 Frequency Response and Phase Angle Measurements         | . 19 |

|     | 3.4 Improved A/D Conversion                                 | . 22 |

|     | 3.5 Step Responses of a Tustin Based Controller             | . 22 |

|     | 3.6 Comparison Between the Tustin-Based and Rattan-Based    |      |

|     | Controllers                                                 | . 25 |

| 4.9 | ERROR CONTRIBUTORS                                          | . 28 |

|     | 4.1 Analog Computer                                         | . 28 |

|     | 4.2 D/A Biasing                                             | . 28 |

| ł   | 4.3 A/D and D/A Quantization                                | · 29 |

|     | 4.4 Word Length                                             | . 29 |

# TABLE OF CONTENTS (CONTINUED)

Course accounters persons a coursel

W. T. C. L. L. L. L. L. L.

|      |            |                                                           | Page |

|------|------------|-----------------------------------------------------------|------|

|      | 4.5        | Computation Delay                                         | 3ø   |

|      | 4.6        | Truncation and Round Off                                  | 34   |

| 5.Ø  | PLAN       | NT SIMULATION ON TEXAS INSTRUMENTS (TI) TMS32Ø1Ø DIGITAL  |      |

|      | SIG        | NAL PROCESSING CHIP                                       | 36   |

|      | 5.1        | Rationale                                                 | 36   |

|      | 5.2        | Plant Digitization                                        | 37   |

|      | 5.3        | Control Loop Configuration                                | 37   |

|      | 5.4        | Implementation of the Plant on the Texas Instruments TMS  |      |

|      |            | 32010 EVM Microcomputer                                   | 39   |

|      | 5.5        | Step Response of the TMS32010 Plant                       | 39   |

|      | 5.6        | State Space Representation of the Plant                   | 43   |

| 6.0  | CONC       | CLUSIONS                                                  | 48   |

| APPE | NDICI      | ES                                                        |      |

|      | <b>A</b> 1 | Program Listing: 8-bit A/D; 8-bit D/A                     | 5ø   |

|      | A2         | Program Listing: 8-bit A/D; 12-bit D/A                    | 52   |

|      | <b>A</b> 3 | Program Listing: 12-bit A/D; 12-bit D/A                   | 54   |

|      | <b>A</b> 4 | Program Listing: Computational Delay                      | 56   |

|      | <b>A5</b>  | Program Listing: Round Off Routine                        | 58   |

|      | <b>A6</b>  | Program Listing: TMS32Ø1Ø Digitized Plant                 | . 6Ø |

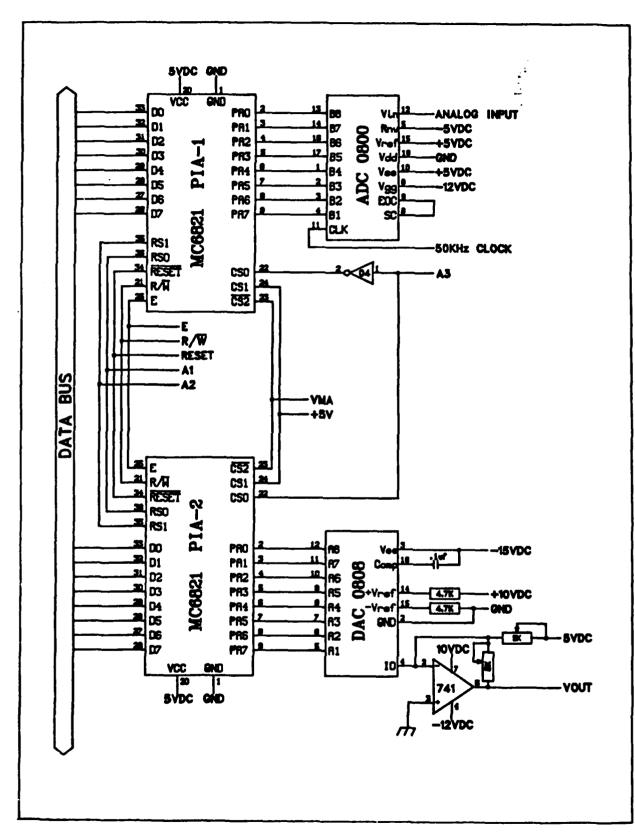

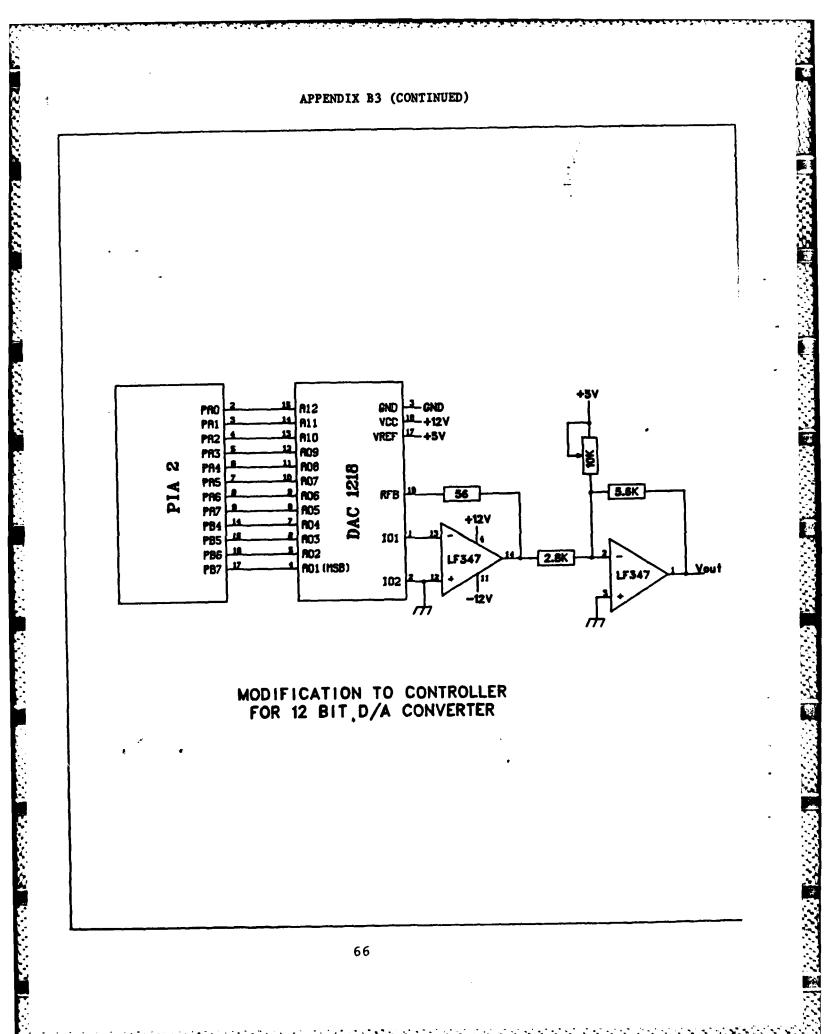

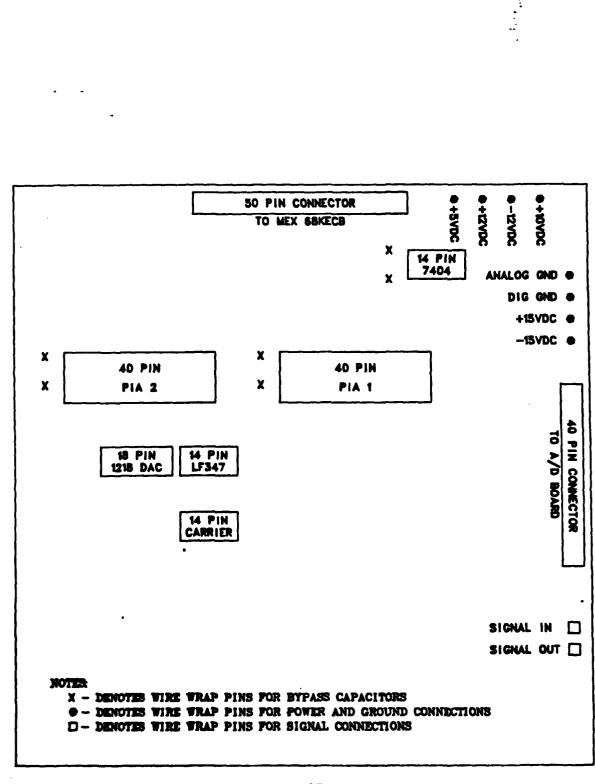

|      | <b>B1</b>  | Circuit Diagram: Interface Circuit 8-bit A/D; 8-bit D/A   | . 62 |

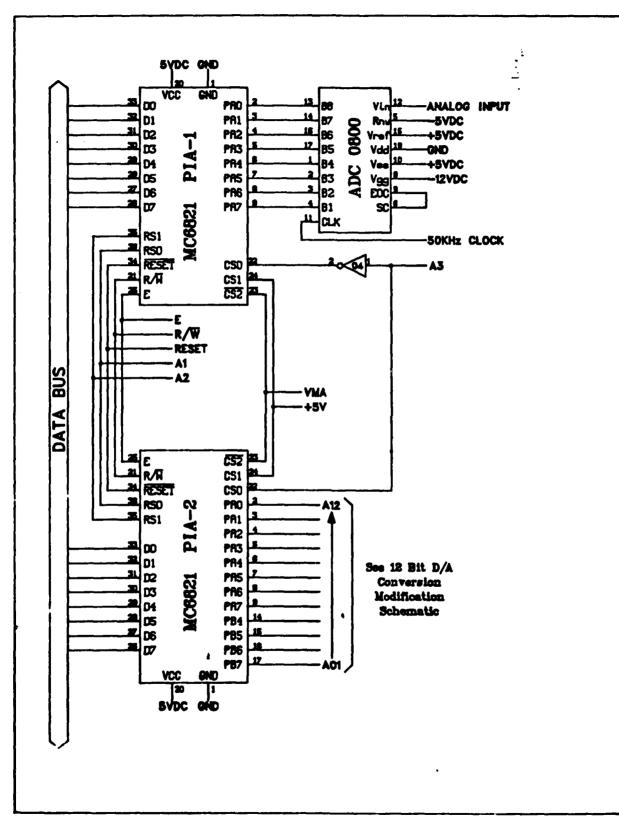

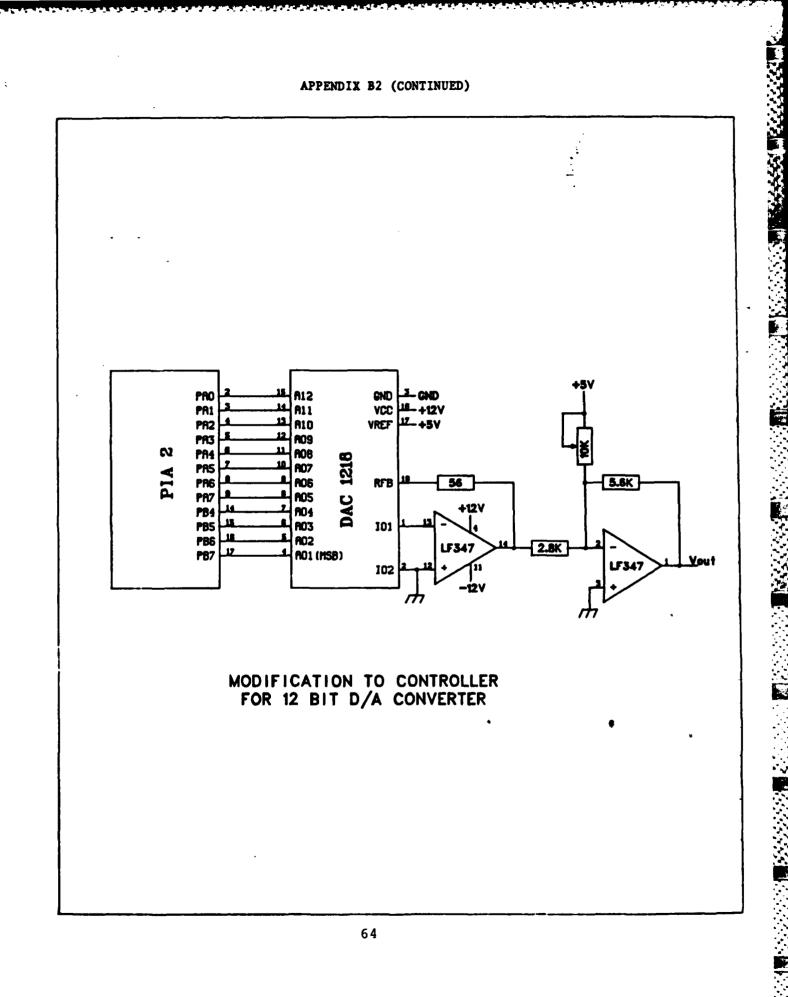

|      | B2         | Circuit Diagram: Interface Circuit 8-bit A/D; 12-bit D/A. | . 63 |

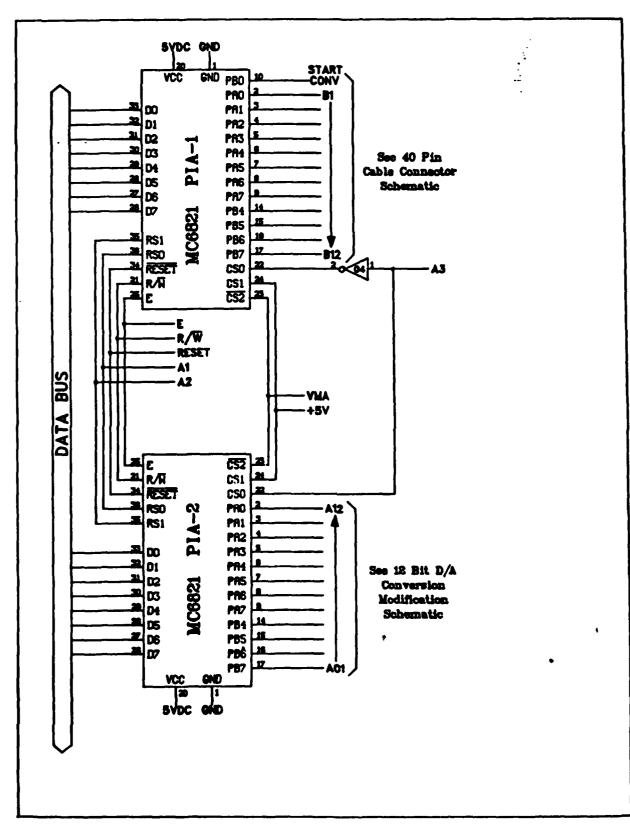

|      | B3         | Circuit Layout and Diagram: Interface Circuit 12-bit A/D; | ;    |

|      |            | 12-bit D/A                                                | . 65 |

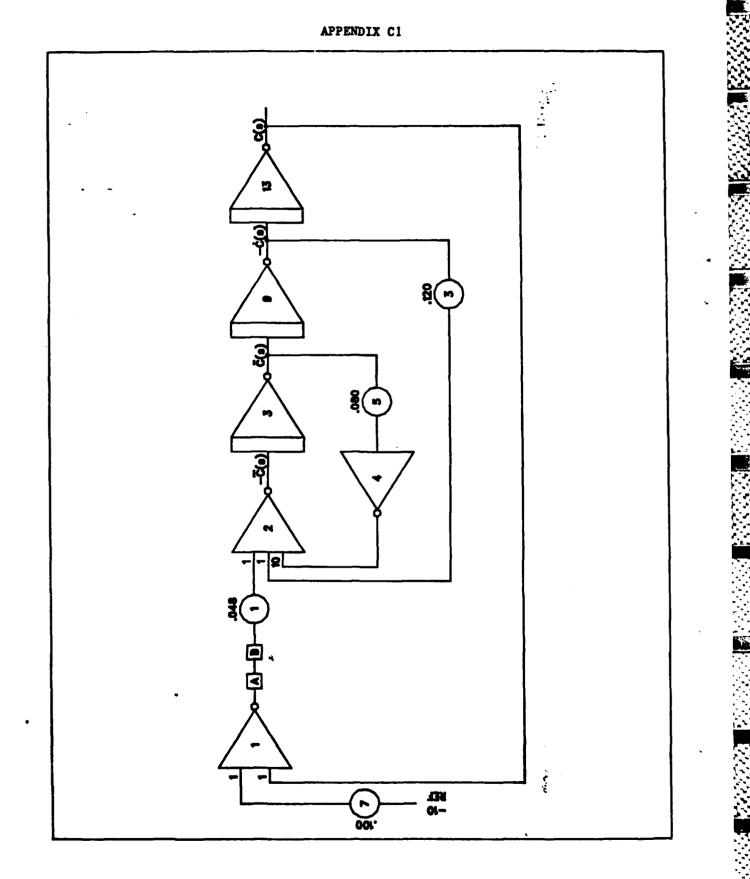

|      | C1         | Wiring Diagram: Analog Computer Patch for Uncompensated   |      |

|      |            | Plant                                                     | . 70 |

# TABLE OF CONTENTS (CONTINUED)

|             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | Page | ; |

|-------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|---|

| REFERENCES. | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 71   |   |

## LIST OF FIGURES

| Figure |                                                                                                             | Page |

|--------|-------------------------------------------------------------------------------------------------------------|------|

| • 1.   | Block diagram of a sampled-data control loop                                                                | . 4  |

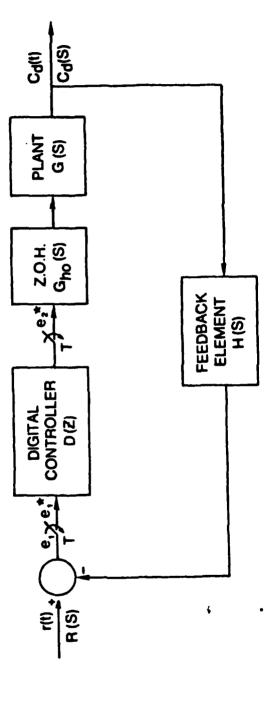

| 2.     | Block diagram of a digital control loop with H(s)=1                                                         | . 5  |

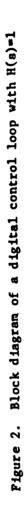

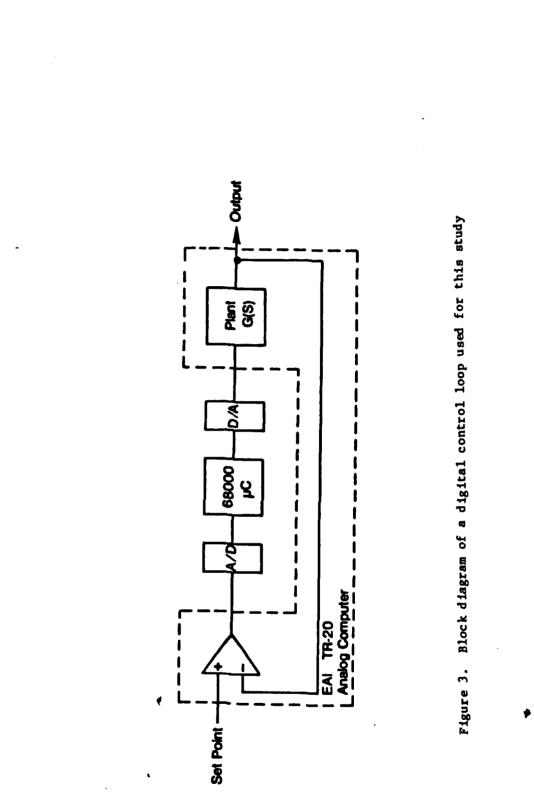

| 3.     | Block diagram of a digital control loop used for this study                                                 | . 6  |

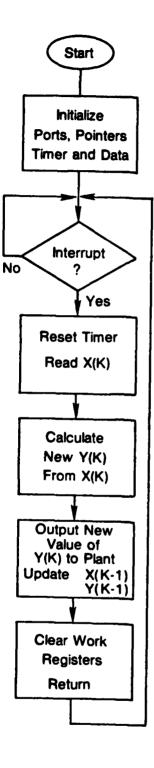

| 4.     | Flow chart of the software package for the digital controller                                               | . 1Ø |

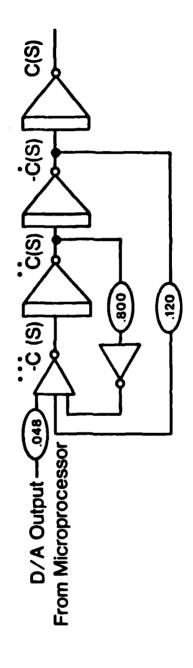

| 5.     | Analog computer patching configuration                                                                      | . 12 |

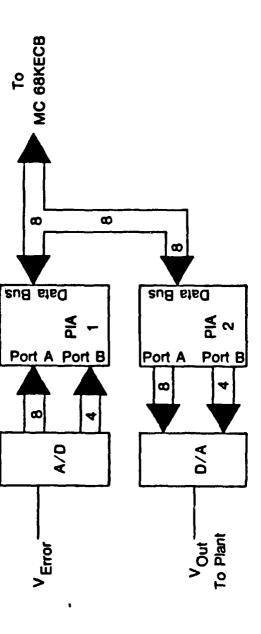

| 6.     | Interface circuitry for interconnecting the MEX68KECB and the analog computer                               |      |

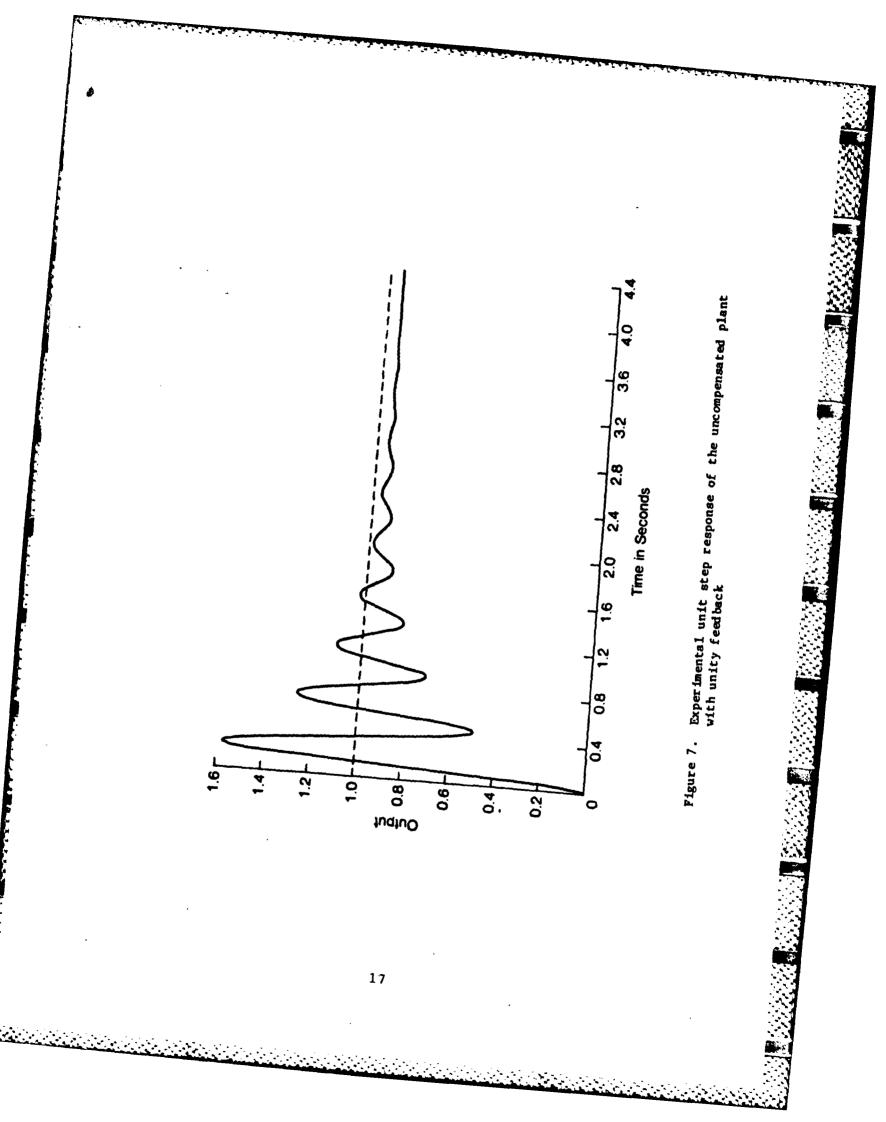

| 7.     | Experimental unit step response of the uncompensated plant with unity feedback.                             | . 17 |

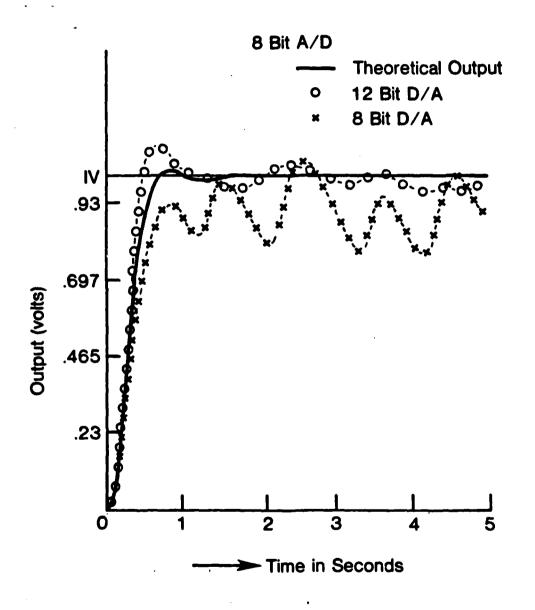

| 8.     | Unit step responses with an 8-bit A/D converter and two<br>different D/A converters                         | . 18 |

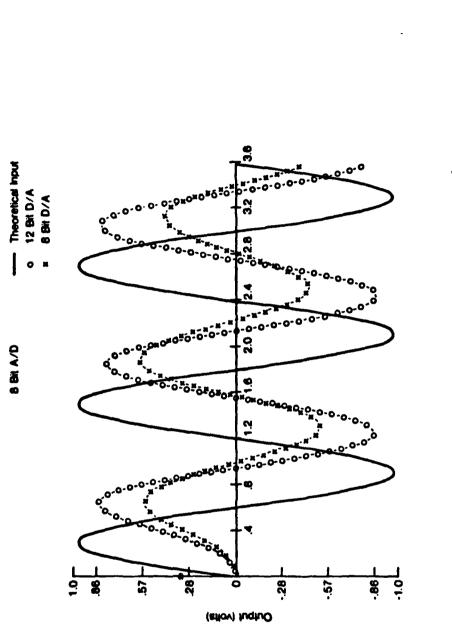

| 9.     | Experimental sinusoidal response of the digital control system                                              | . 2ø |

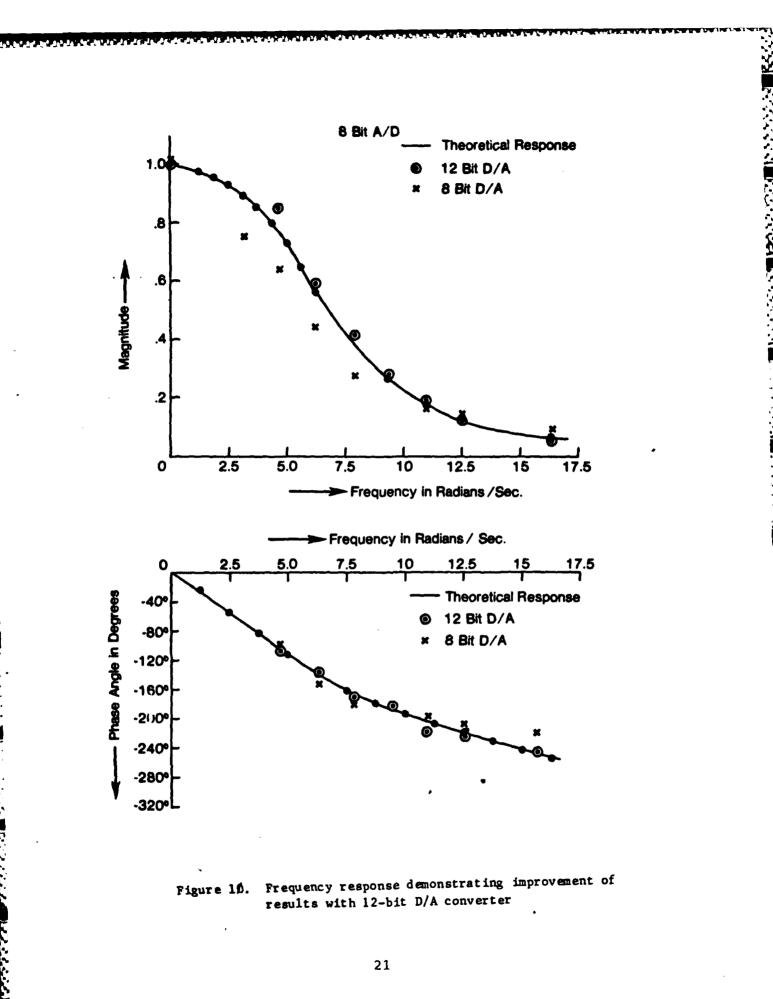

| 19.    | Frequency response demonstrating improvement of results with 12-bit D/A converter                           |      |

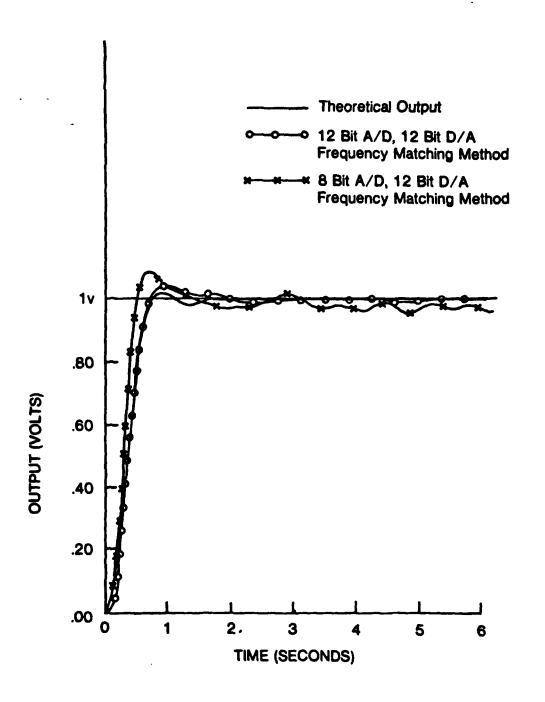

| 11.    | Unit step responses demonstrating improvement of results with<br>12-bit A/D converter                       |      |

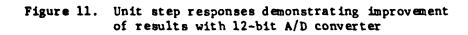

| 12.    | Comparison between unit step responses of Rattan- and Tustin<br>based controllers with 8-bit A/D converter  |      |

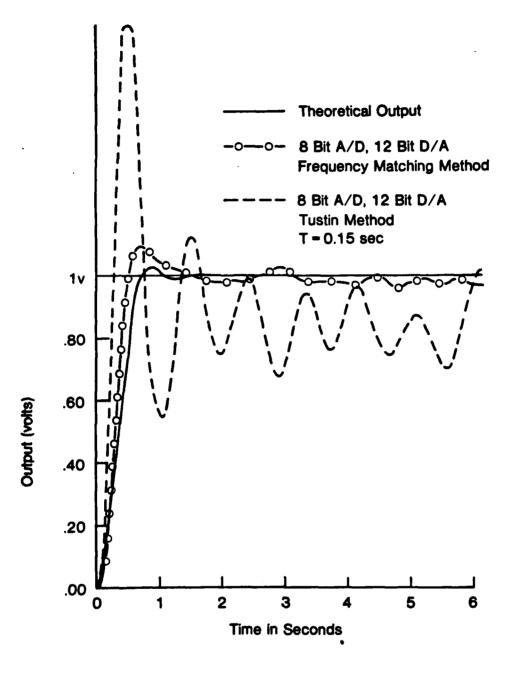

| 13.    | Comparison between unit step responses of Rattan- and Tustin<br>based controllers with 12-bit A/D converter |      |

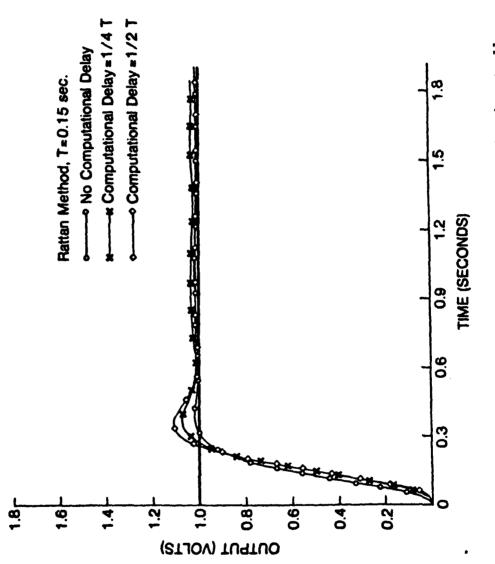

| 14.    | Computation delay results for Rattan-based controller                                                       | . 31 |

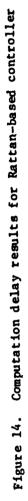

| 15.    | Computation delay results for Tustin-based (T=0.04 sec) controller                                          | . 32 |

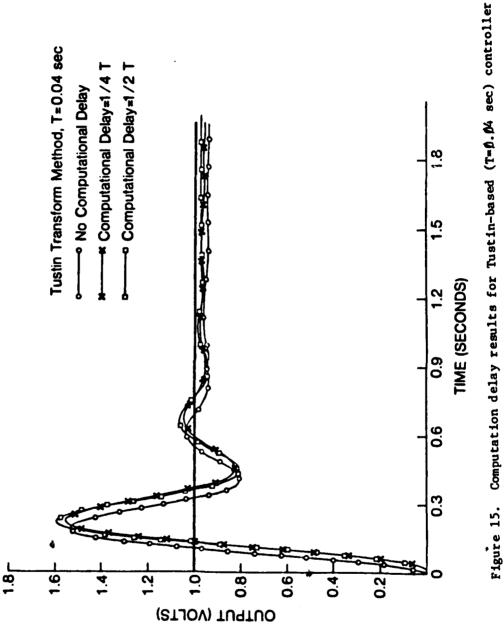

| 16.    | Computation delay results for Tustin-based (T=Ø.15 sec)<br>controller                                       | . 33 |

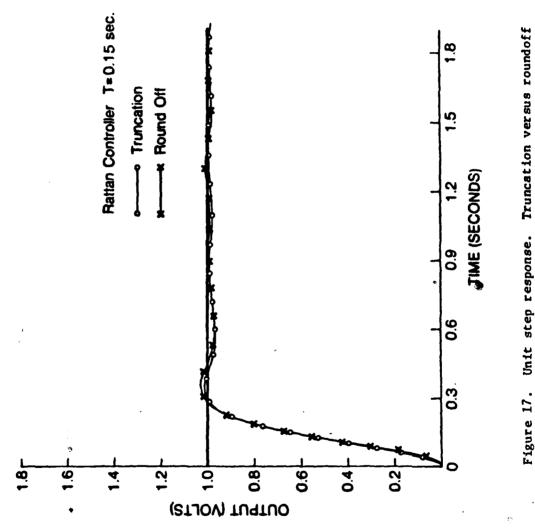

| 17.    | Unit step response. Truncation versus round off                                                             | . 35 |

# LIST OF FIGURES (CONTINUED)

| Figure |                                                                     | Page      |

|--------|---------------------------------------------------------------------|-----------|

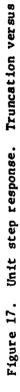

| . 18.  | Block diagram of a MC68000/TMS32010 digital control loop            | . 38      |

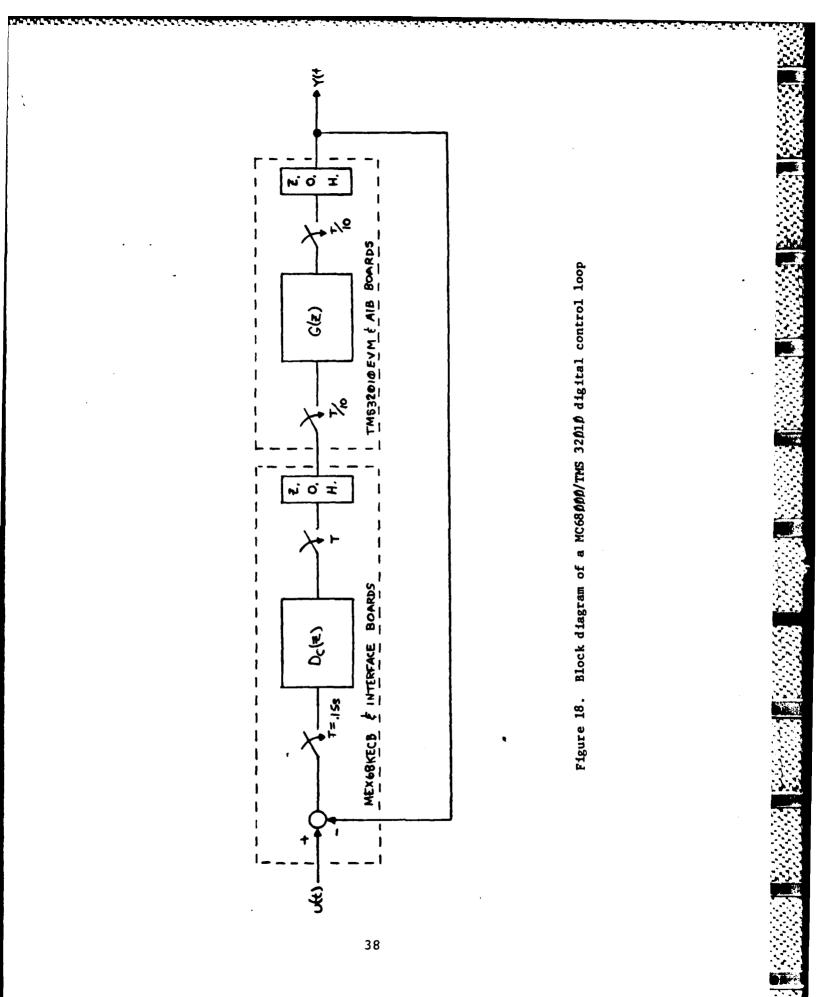

| 19.    | Flow chart of the TMS32010 software package for the digitized plant | d<br>. 4Ø |

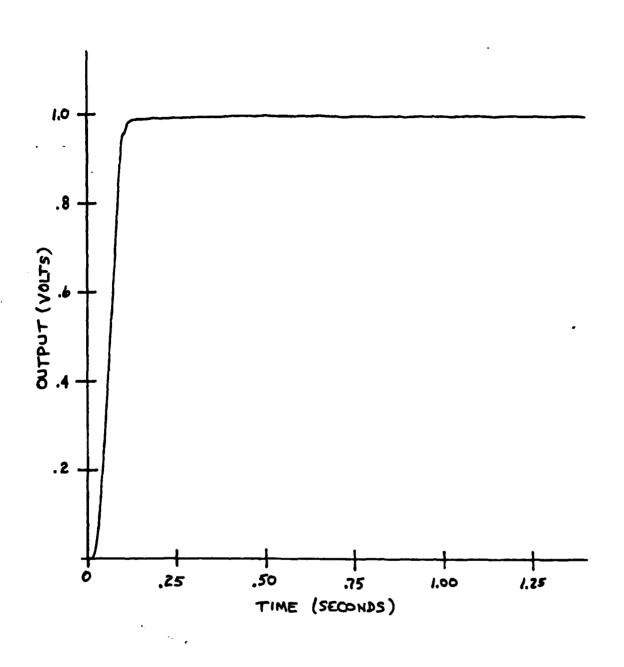

| 20.    | Unit step response of TMS32Ø1Ø Plant at T=Ø.15 sec                  | . 42      |

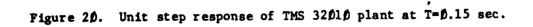

| 21.    | State space representation of the plant                             | . 44      |

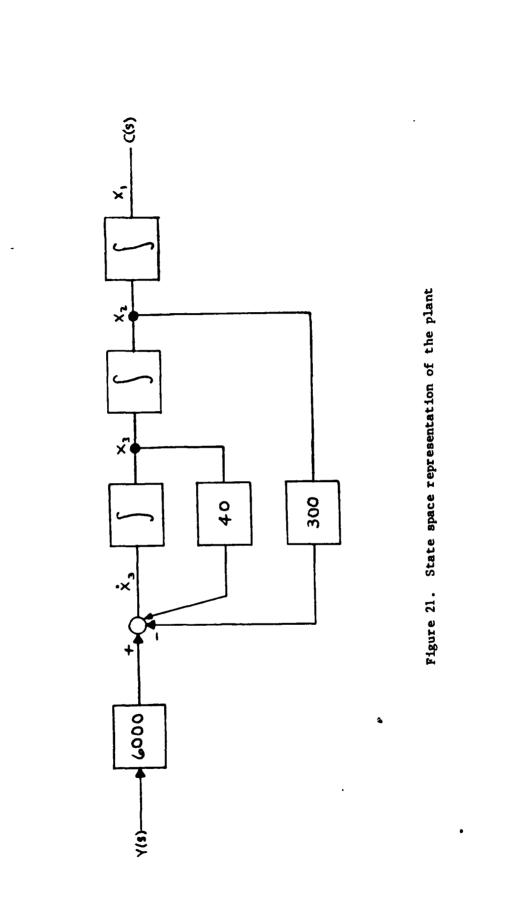

| 22.    | Alternative state space representation of the plant                 | . 45      |

#### ACKNOWLEDGEMENTS

I wish to express my sincere appreciation to Dr. Kulip S. Rattan, Department of Engineering, Wright State University, for his contribution to my academic growth and the guidance he provided throughout this project. I would also like to thank Alok Sarwal, a fellow graduate student, for his help at certain points in the project. Special thanks to Gloria J. Chrisman for typing the manuscript, Betty J. Baldwin for proofreading, and to Robert K. VanHook for producing the schematic diagrams. Thanks to the Graphics Department at Wright State University for producing the data traces.

#### **1.0** INTRODUCTION

Interest in digital control has expanded rapidly as a result of low cost 16-bit microprocessors and associated support devices being introduced. Digital control is an attractive alternative when consider ing a control strategy. Therefore, it is important that the capabilities and shortcomings of microprocessor based controllers be fully understood before they are put into service.

It is well known to designers of control systems that major difficulties are found in mechanization of the control algorithm. Mechanization means the selection of digital equipment, such as the Analogto-Digital (A/D) and Digital-to-Analog (D/A) converters and the word length of the computer; the actual programming of the algorithm; and analysis of various error sources and the effects each has on the dynamics of the controller.

The digital control configuration, used for this study, consists of: a digital controller, implemented on a Motorola MC68000 based microcomputer board; in series with an analog plant, simulated on an analog computer.

The steps needed to meet the stated objectives are:

1. Selection of the digital processing components.

2. Generation of the software package which implements the control algorithm on the microcomputer system.

3. Simulation of the analog plant on an analog computer, and interconnection of the microcomputer and analog computer.

4. Evaluation of the performance of the control loop for several configurations.

5. Identification of items which cause degradation in the performance of the control loop.

6. Demonstration of a totally digital control loop configuration where the plant is digitized and simulated on a high speed microcomputer.

The results of this study will demonstrate the effectiveness of using a microprocessor based system for digital control.

#### 2.4 DESIGN OF THE DIGITAL CONTROL SYSTEM

### 2.1 SELECTION OF THE MICROCOMPUTER AND ANALOG COMPUTER

The resources for performing digital control studies should be readily available and moderate in cost. The equipment used for this study was available for use at Wright State University. The Comdyna GP-6 and Electronics Associates, Inc., (EAI) TR-20 were the analog computers used throughout the digital control study effort. The processor chosen for the digital controller was the Motorola MC68000 16-bit microprocessor. This chip is representative of the many 16-bit microprocessors on the market, but it has several attributes which made it more suitable for the control study. The Motorola MEX68KECB Educational Circuit Board, a low cost MC68000 based microcomputer board, was used as the digital controller. This computer board was purchased for this project and several other digital control studies which will follow.

2.2 DIGITAL CONTROL SYSTEM CONFIGURATION

A single-loop sampled data control configuration is shown in Figure 1. The primary components of the loop are:  $D_c(z)$ , the digital controller which receives and transmits control data at sampling instant T;  $G_{ho}(s)$ , a zero order hold device; G(s), the plant or device which is to be controlled; and H(s), the feedback element which takes the output of the plant to a summing junction where the difference between the set point and plant output, or the amount of error remaining to be corrected, is fed back to the controller input.

ų,

٠.,

Received success success and

The digital control loop used for this control study is similar to the configuration of Figure 1, except that the feedback element, H(s), was set equal to one. Figure 2 shows this configuration. Figure 3 is a block diagram representation of the control system as implemented.

The plant G(s), the unity feedback element H(s), and the summing junction were implemented on an analog computer. The digital controller was implemented on the Motorola MEX68KECB computer board. The signal conversion devices, the A/D and D/A converters, were part of an interface board which was developed for this project.

The system characteristics are the following:

$$G(s) = \frac{6000}{s(s^2 + 40s + 300)}$$

(1)

$$H(s) = 1$$

(2)

## 2.3 DERIVATION OF THE CONTROL ALGORITHM

The pulse-transfer function of the first order digital controller, used with the control loop, was obtained using the computer aided frequency matching method of Rattan [1]. The equation for  $T=\emptyset.15$ seconds is given by:

$$D_{c}(z) = 0.154 \frac{z - 0.523}{z - 0.425}$$

(3)

This control equation will be the reference control algorithm to which other algorithms (under evaluation) will be compared.

2.4 IMPLEMENTATION OF THE CONTROL EQUATION ON THE MICROCOMPUTER

The digital control equation  $D_c(z)$  must be implemented on a microcomputer. One method that is readily adaptable to computer application and the method chosen for this study is the representation of  $D_{c}(z)$  as a difference equation. Equation (3) can be written as:

$$\frac{Y(z)}{X(z)} = \frac{\emptyset.154z - \emptyset.\emptyset81}{z - \emptyset.425}$$

(4)

Cross-multiplying equation (4), multiplying this result by  $z^{-1}$ , and solving for Y(z), we get:

$$Y(z) = \emptyset.425z^{-1}Y(z) + \emptyset.154X(z) - \emptyset.\emptyset81z^{-1}x(z)$$

(5)

Taking the inverse z-transform of equation (5) yields:

$$Y(K) = \emptyset.425*Y(K-1)+\emptyset.154*X(K)-\emptyset.\emptyset81*X(K-1)$$

(6)

To implement the first-order difference equation given in equation (6) on a microprocessor, the coefficients have to be scaled to a convenient base for ease of numerical calculation. Since the word length of the MC68000 is essentially 16 bits, and none of the coefficients in the difference equation are greater than one,  $32767(2^{15})$  was chosen as the base for all coefficients to maximize word length utilization (1 sign bit/15 magnitude bits). The resulting scaled integer coefficients were then converted to hexidecimal, and the resulting equation (7) is given by:

$$Y(K) = 3666*Y(K-1)+13B6*X(K)-\#A5E*X(K-1)$$

(7)

where the coefficients for equation (7) were obtained by:

$$3666_{16} = \emptyset.425 * 32767$$

(8)

$$13B6_{16} = \emptyset.154 * 32767$$

(9)

Now that a control equation is in a form that can be implemented on the microprocessor, a software package must be written to instruct the microprocessor to execute a sequence of steps in order to achieve the desired output. The software package developed for the digital controller consists of four sections:

- 1. Initialization section

- 2. Interrupt servicing and data input section

- 3. Algorithm section

4. Data output section

The initialization section establishes the appropriate configuration for the microprocessor and its support chips. Some of the operations performed are: programming the peripheral interface adapters (PIAs), initializing the programmable interrupt timer (PI/T), and setting initial conditions for the control equation. The last operation of the initialization section is to enable interrupts, enter the halt mode, and wait for an interrupt to occur.

The interrupt service and data input section, which begin at each sampling instant by acknowledging the interrupt, resets the interrupt device and reads the data value, X(K), to be processed.

The algorithm section calculates Y(K) based on the control equation programmed on the microprocessor, outputs the results to the D/A for use by the plant, and stores appropriate values of Y(K-1) and X(K-1)for the next enumeration. The last operation performed is again enabling interrupts, forcing the processor to enter the wait mode until the next sampling instant. The flow chart of the software package is shown in Figure 4.

Figure 4. Flow chart of the software package for the digital controller

## 2.5 SIMULATION OF PLANT PARAMETERS ON THE ANALOG COMPUTER

The analog computer provides a convenient method for implementing the summing junction, the unity feedback element, and the plant characteristics. It contains a variety of active and passive components which can be externally configured through a patchboard to simulate the desired transfer function. The transfer function of the plant can be converted into an analog computer program as follows:

$$G(s) = \frac{C(s)}{Y(s)} = \frac{6000}{s^{3} + 40s^{2} + 300s}$$

(11)

Cross multiplying equation (11), we get:

$$s^{3}C(s)+4\emptyset s^{2}C(s)+3\emptyset\emptyset sC(s) = 6\emptyset\emptyset\emptyset Y(s)$$

(12)

Inverse Laplace-transform of equation (12) yields:

$$\frac{d^{3}C(t)}{dt^{3}} + 4p \frac{d^{2}C(t)}{dt^{2}} + 300 \frac{dC(t)}{dt} = 6000Y(t)$$

(13)

In order to assure that the rate of change of C(t) is consistent with the dynamic properties of the analog computer and X-Y plotter, equation (13) needs to be "time scaled" before it can be implemented on the analog computer. A time scaling of 50 resulted in the following equation:

$$s^{3}C(s) = -\emptyset.8s^{2}C(s) - \emptyset.12sC(s) + \emptyset.\emptyset48Y(s)$$

(14)

This Laplace-transform representation of C(s) can now be patched on the analog computer using the configuration shown in Figure 5.

Figure 5. Analog computer patching configuration

## 2.6 INTERFACE BETWEEN THE MICROCOMPUTER AND ANALOG COMPUTER

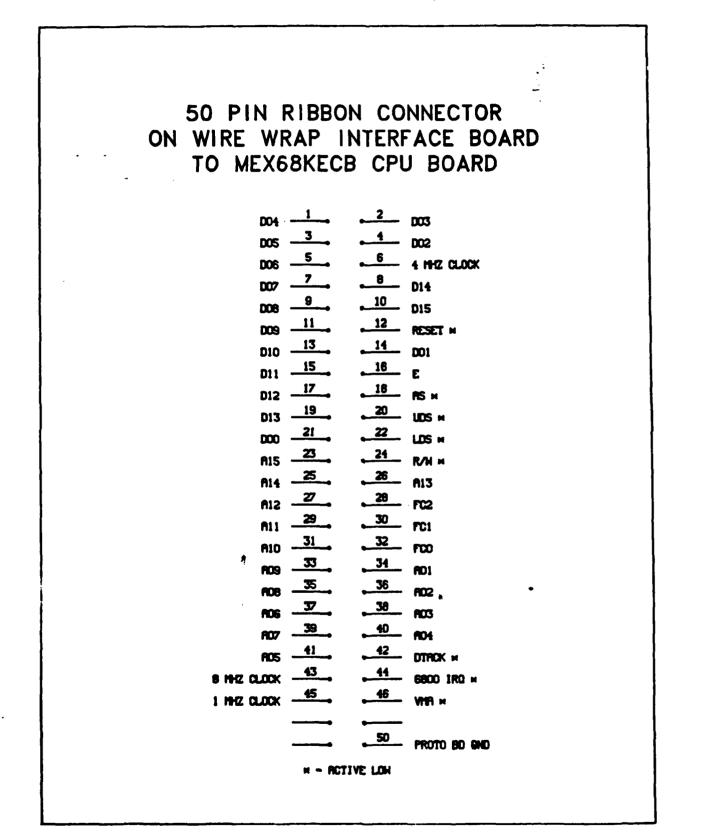

Interface circuitry, which would permit interconnection of the microcomputer board and the analog computer, was developed for this study. This circuitry consisted of: the A/D and D/A converters and associated circuitry; two Peripheral Interface Adapters (PIA), one programmed as an input port (PIA1) and one programmed as an output port (PIA2); and devices used for chip enable circuits. Figure 6 shows a block diagram representation of the interface circuit. Interconnection between the interface circuit and the microcomputer was accomplished with 50 pin ribbon connectors and two specially made patchcords for connection to the analog computer. The interface circuit was easily modifiable for different A/D and D/A configurations. Let us take a closer look at each of the blocks of Figure 6. A substantial amount of time went into the design of the interface circuitry so a little more detailed description is called for at this time.

Motorola MC6821 Peripheral Interface Adapters (PIA) were used as the bus interface devices since the MC68000 contained control lines which would permit easy interconnection and operation. When a memory location above 030000 Hex was accessed on the MEX68KECB, the MC68000 microprocessor would enter the synchronous mode of operation. The Valid Memory Address (VMA\*), an active-low signal was used as on chip enable signal for each PIA. Once a PIA was selected, a negative-going edge of the Enable (E) signal would cause the transfer of data. Three address lines (A1, A2 and A3) were used to select the proper PIA and the peripheral register. Each PIA needed to be initialized before it could be used to transfer data. Writing the proper data to the Control Registers and Data Direction Registers would set up each bit of the selected port

as an input or output. Bits PAØ through PA7 were programmed as input lines on PIA1. Bits PB4 through PB7 were also used when a 12-bit A/D converter was to be connected into the circuit. PBØ of PIA1 was used to provide a start convert signal to the 12-bit A/D converter. PIA2 was programmed in a similar manner as PIA1 except the peripheral ports were used as output lines. The Read/Write (R/W\*) would determine the direction of the data transfer. When the R/W\* line was a high logic level, data was transferred from the A/D converter, to a CPU register. When this line was a low logic level, data was transferred from a CPU register to the D/A converter.

The 8-bit devices used for the first hardware configuration were National Semiconductor ADCØ8ØØ 8-bit successive approximation A/D converter; the D/A converter was the 8-bit DACØ8Ø8. The 12-bit D/A converter selected for the second configuration was the National Semiconductor DAC1218. The 8-bit A/D converter of the two previous arrangements was replaced with an Analog Devices AD572 12-bit successive approximation A/D converter. These conversion devices were selected for use since they were representative of current technology and readily available for use in the laboratory.

#### 3.0 CONTROL LOOP PERFORMANCE ANALYSIS

## 3.1 RESPONSE TO A STEP INPUT

There were three signal conversion configurations used for this control study. The first configuration was an 8-bit A/D converter and an 8-bit D/A converter arrangement. The second configuration was similar to the first except that the 8-bit D/A converter was replaced with a 12-bit D/A converter. The final arrangement consisted of a 12-bit A/D converter and a 12-bit D/A converter. As will be shown later, the third arrangement provided the best performance, consequently, a permanent interface card was wire-wrapped.

The first step response to be measured was that of the uncompensated plant. Figure 7 shows the response obtained when the uncompensated plant was subject to a unit step input. Notice that the step response demonstrates the classical overshoot and oscillations associated with an underdamped system. Also notice that the steady-state value of the plant output is not 1 volt, but slightly less. This fact will be discussed further in Section 4.1.

The unit step responses of Figure 8 are for the compensated plant for the first- and second-signal conversion configurations. The overshoot is reduced significantly, as would be expected with a compensated plant. The steady-state oscillations observed will be discussed more thoroughly in Section 4.3.

Figure 8. Unit step responses with 8-bit A/D converter and two different D/A converters

#### 3.2 RESPONSE TO SINUSOIDAL INPUTS

One of the goals of the study effort was to experimentally evaluate the control loop response to sinusoidal inputs. This would provide a means of determining the frequency response of the digital control system. Sinusoidal inputs of frequency between  $\emptyset$  and  $\omega_{g/2}$  were applied to the set point input of the control loop. Due to the amount of time scaling involved for the plant simulation, the frequency range needed for the sine waves was lower than that obtainable with waveform generators available in the laboratory. It was then necessary to use a second analog computer which generated the desired sine wave. The Laplace transform of the sine function is given by:

$$F(s) = \frac{\omega}{s^2 + \omega^2}$$

(15)

The analog computer was configured for equation (15) and different values for  $\omega$  were programmed to yield the proper input frequency. Figure 9 shows the results obtained for one of the input frequencies. Results for both 8-bit D/A and 12-bit D/A converters are shown on the same plot, along with the input frequency. Notice the magnitude attenuation and phase shift associated with each response. The magnitude attenuation is greater with the 8-bit D/A converter than with the 12-bit D/A converter. Comparison of the phase shifts for each D/A configuration shows little difference between them.

#### 3.3 FREQUENCY RESPONSE AND PHASE ANGLE MEASUREMENTS

The results obtained for frequency response and phase angle measurements are shown in Figure 10. Data for both D/A converter configurations are plotted together with the theoretical responses. The theoretical responses for magnitude and phase angle were obtained using

AND THE DESCRIPTION ADDRESS ADDRESS

AND IN A REAL PROPERTY.

Experimental sinusoidal response of the digital control system Figure 9.

the interactive control analysis program TOTAL. The theoretical data curves provide a reference to which the experimental results can be compared. The magnitude plot shows that the frequency response with the 12-bit D/A converter follows the theoretical frequency response more closely than with the 8-bit D/A converter. Results from the phase angle plot demonstrate that little differences exist between the phase plots for the 8-bit D/A and 12-bit D/A converters, except at the highest frequencies where the 8-bit D/A converter exhibited more deviation from the theoretical phase angle curve.

3.4 IMPROVED A/D CONVERSION

All of the performance analysis of the control loop thus far has been with an 8-bit A/D converter. There was an improvement in control system accuracy when the 8-bit D/A converter was replaced with the 12-bit D/A device. The 8-bit A/D converter will be replaced with a 12-bit A/D converter, resulting in the third control system configuration, that is, 12-bit A/D and 12-bit D/A converters. The remaining performance tests were based on this configuration. Figure 11 contains step responses, one where the loop uses an 8-bit A/D converter and one where the loop uses a 12-bit A/D converter. The step response associated with the \*12-bit A/D device exhibits slightly less steady-state oscillation than with the 8-bit A/D converter. The improvement in control loop performance (obtained with improved A/D conversion) is not as pronounced as the improvement demonstrated with improved D/A conversion.

3.5 STEP RESPONSES OF A TUSTIN BASED CONTROLLER

Control loop performance was demonstrated with several different hardware configurations, but all of them with the Rattan-based control

algorithm. The Tustin transformation or bilinear transformation [4] as it is commonly known, provides another means of obtaining a discrete system from the continuous system. The continuous controller on which the Rattan algorithm was based is given by:

$$G(s) = \emptyset.322 \frac{(s+1.914)}{(s+\emptyset.616)}$$

(16)

Substituting:

$$s = \frac{2}{T} \frac{z - 1}{z + 1}$$

(17)

into equation (16) and using the appropriate value for the sampling period (T), the result obtained is a digitized controller of the same order. The Tustin-based controllers for T= $\emptyset$ .15 seconds and T= $\emptyset$ . $\emptyset$ 4 seconds are given by equations (18) and (19), respectively as:

$$D(z) = \emptyset.352 \frac{(z - \emptyset.749)}{(z - \emptyset.912)}$$

(18)

$$D(z) = \emptyset.33\emptyset \frac{(z - \emptyset.926)}{(z - \emptyset.976)}$$

(19)

The Tustin controller equations can be rearranged and the coefficients converted to hexidecimal, as previously demonstrated with the Rattan controller, to obtain the control algorithms:

$$Y(K) = 74B2Y(K-1) + 2D\emptyset 4X(K) - 21B7X(K-1)$$

(2\$)

$$Y(K) = 7CE3Y(K-1) + 2A4\emptyset X(K) - 2721X(K-1)$$

(21)

for T=0.15 seconds and T=0.04 seconds, respectively. The Tustin control algorithms were implemented on the digital controller by changing the memory locations, which contained the associated coefficients.

3.6 COMPARISON BETWEEN THE TUSTIN BASED AND RATTAN BASED CONTROLLERS

The step responses of Figures 12 and 13 demonstrate the significant response variations between the Rattan and Tustin control algorithms. The lessons learned from this indicate that for a given hardware configuration, variations in the control algorithm can have a significant effect on the overall performance of the control loop. The Tustin control algorithms seem to be more sensitive to the size of the signal conversion device than the Rattan algorithm. It is best to use the largest bit sized conversion device possible when implementing a Tustin based controller to insure proper control loop operation.

Figure 12. Comparison between unit step responses of Rattan- and Tustin-based controllers with 8-bit A/D converter

Figure 13. Comparison between unit step responses of Rattan- and Tustin-based controllers with 12-bit A/D converter

#### 4.Ø ERROR CONTRIBUTORS

#### 4.1 ANALOG COMPUTER

\* \* \* \*

ļ

ことになる とうない ないない 大手 たいかん たいたい きょうかん ひんかい 手手 アイアイチャ

ľ

The transfer function of equation (1) is of type 1, which means that the theoretical steady-state error is equal to zero. However, the plant, as implemented on the analog computer, was found to have an error of +50 millivolts (mV) when configured with unity feedback and a set point of 1 volt, (v), hence, it was necessary to establish a D/A bias at "digital zero," which resulted in a +50 mV output from the controller. This D/A bias would, in effect, compensate for the analog computer error.

#### 4.2 D/A BIASING

The use of a +50 mV D/A bias is in itself an induced error, since it is desirable to have "digital zero" to the D/A represent a true value of zero volt. Two problems closely related to the D/A biasing error are over/under D/A biasing and D/A bit size. If the bias was set to some value other than +50 mV, excessive steady-state oscillations would occur. Care was taken to insure the setting of the proper D/A bias prior to any data collection. Proper setting of the required D/A bias was difficult at best with the 8-bit D/A converter, but became less of a problem when the 12-bit D/A converter was used. Establishment of the proper D/A bias insured that the overall plant response would be correct.

#### 4.3 A/D AND D/A QUANTIZATION

An 8-bit converting device has 256 discrete values, whereas, a 12bit converting device has 4096 discrete values associated with it. For a reference voltage range of 10 V ( $\pm$ 5V), the resolution for an 8-bit and a 12-bit converters are 39 mV and 2.44 mV, respectively. Due to D/A quantization, the plant output oscillated between the D/A output levels, which drove it positive or negative. As the D/A size was increased, the number of quantization levels also increased, which resulted in smaller increments between the output levels, therefore, less steady-state oscillation. Similarly, an increase in A/D bit size increased the digital accuracy and reduced the input quantization approximation error.

A comparison of the D/A output quantization effects can be seen in the unit step plots of Figure 8. The reduction in oscillation of the 12-bit configuration is very evident. The step response plots of Figure 11 demonstrate that further improvement in plant response was observed with a 12-bit A/D converter, although this improvement is not as significant as seen with the D/A converter change.

#### 4.4 WORD LENGTH

Another source of system error is the finite word length of the computer. As seen previously, the size of the signal conversion components has a significant effect on the performance of the control loop. The coefficients of the control algorithm are scaled values based upon a binary fixed-point numerical representation. As the internal precision of the word length of the computer goes up, so does the resolution of the coefficients. This increased precision propagates throughout the calculations so that the upper word of the final computed value is a more accurate representation than what would have been

obtained using lower precision numerical representation. It is the upper word of the final value which is sent to the D/A converter. The 16-bit word length of the MC68000 found to be more than sufficient for producing acceptable accuracy.

#### 4.5 COMPUTATION DELAY

The control algorithm takes a finite amount of time to produce an output based upon a given input. This delay is the amount of time it takes to calculate the control output at a given sampling instant from an error input taken simultaneously. The effects of computation delay on control loop performance may or may not be significant. If the ratio of computation delay to sample rate is small, then computation delay should not be a problem. As this ratio becomes larger, the effects of computation delay on loop performance should become apparent. experimentally determine computation delay, it was necessary to place a delay routine in the control algorithm. The length of the delay was controlled by a specific value, placed in a register, which was decremented until it was zero. Computation delay values of 1/4T and 1/2Twere used. Figures 14 and 15 show results obtained for the Rattan based and Tustin-based (T=0.04 sec.) controllers. The plots for computation delays of 1/2T show that during transient periods, the plant will tend to overshoot more when compared to the plots with computation delay of 1/4T. A comparison of computation delays of 1/16T and 1/8T for the Tustin-based (T=Ø.15 sec.) is given in Figure 16. The effects of smaller computation delays are more noticable with this longer sampling period than with the T=0.04 sec. controller. This is an indication that the plant is sensitive to a fixed amount of computation delay since 1/16T of the T=Ø.15 sec. controller is approximately equal to 1/4T of

CONTRACTOR OF

BUULT SERVICE REPORTS DISTURDED INSTRUME SUBJECTS

ومحدديد

Figure 15.

アンシンショ

the  $T=\emptyset.04$  sec. controller. As the plant approaches steady-state, the effects of computation delay diminish. For the control configurations of this study, it appeared that computation delay did not effect the control loop significantly; however, this may not be true for other types of reference inputs.

4.6 TRUNCATION AND ROUND OFF

Truncation is the process of ignoring all bits less than the least significant bit, whereas, round off is the process of selecting a number which is closest to the unrounded quantity. For example, the decimal number 1.96 will be truncated to a value of 1.9 and rounded to 2.0 for two significant digits of accuracy. The procedures of truncation and round off for binary numbers are the same. All of the control algorithms so far have used truncation of the final output result. The final result obtained was either a 24-bit or a 28-bit result, depending on the size of the A/D converter used. The most significant 8- or 12bits for the final value were passed to the D/A converter, depending on the size of the D/A device. The remainder of the lower significant bits did not contribute to the magnitude of the final output value. A rounding routine was written for the 12-bit A/D, 12-bit D/A control configuration to include the effects on these lowest bits in the final value. Figure 17 shows unit step responses of the plant; one with rounding, one without. For the configuration used in this control study, rounding did not provide significant improvement in loop performance as anticipated. However, the step response of the control algorithm with rounding did seem to have a steady-state value slightly closer to the value of 1 volt.

÷.,

#### 5.0 PLANT SIMULATION ON THE TEXAS INSTRUMENTS (TI) TMS32010 DIGITAL SIGNAL PROCESSING (DSP) CHIP

#### 5.1 RATIONALE

- The plant for the control study thus far has been simulated on an analog computer, which has a time scale factor of 50. This time scaling equates to a sampling period of 7.5 seconds. There could be several advantages in replacing the analog computer with a digital computer such as; more flexibility, elimination of offset error and elimination of time scaling. The sampling period of the control loop whould then be  $\emptyset$ .15 seconds instead of 7.5 seconds. The requirement is that the plant must be able to be simulated on a computer, which would permit proper operation of the control loop at the desired sampling rate. One approach is to digitize the plant using the Tustin transform with a sampling period of  $\emptyset.\emptyset15$  seconds and implement the resulting digital transfer function on a high speed digital signal processing computer. The computer considered for plant implementation was the Texas Instruments (TI) TMS32Ø1Ø Evaluation Module (EVM) and the TI TMS32Ø1Ø Analog Interface Board (AIB). The EVM board is an evaluation microcomputer board based upon the TI TMS32010 digital signal processor chip. The AIB is a support board which provides the necessary 12-bit signal conversion so that the EVM board can be used for signal processing applications. The combination of these boards would provide everything needed for " "real-time" digital simulation of the plant.

TOTAL TANAL SAMARANA SAMARANAN

•

#### 5.2 PLANT DIGITIZATION

The transfer function of the plant must be digitized before it can be implemented on the TMS32Ø1Ø EVM. The Tustin transformation, equation (17) must be substituted into equation (1). Keeping T unspecified so that a general equation can be derived and simplifying the resulting expression will give a digitized transfer function of:

$$G(z) = \frac{6\emptyset\emptyset\emptysetT^{3}[z^{3}+3z^{2}+3z+1]}{8[z^{3}-3z^{2}+3z-1]+160T[z^{3}-z^{2}-z+1]+6\emptyset\emptyset T^{2}[z^{3}+z^{2}-z-1]}$$

(22)

If T is set equal to  $\emptyset.\emptyset15$  seconds, equation (22), when simplified becomes

$$G(z) = \frac{Y(z)}{X(z)} = \frac{\emptyset \cdot \emptyset 2 \emptyset 2 5 z^{3} + \emptyset \cdot \emptyset 6 \emptyset 7 5 z^{2} + \emptyset \cdot \emptyset 6 \emptyset 7 5 z + \emptyset \cdot \emptyset 2 \emptyset 2 5 2}{19 \cdot 535 z^{3} - 26 \cdot 265 z^{2} + 21 \cdot 465 z - 5 \cdot 735}$$

(23)

Equation (23) will be implemented in software on the TMS32Ø1Ø EVM board.

#### 5.3 CONTROL LOOP CONFIGURATION

The control loop configuration (using the TMS32010 EVM) is essentially the same as that of Figure 1, except that now there is a digital plant instead of analog plant. Figure 18 is a block diagram of the control loop configuration needed for this portion of the control study. There are two major differences between the control loop of Figure 1 and the control loop of Figure 18; the summing junction is a difference amplifier located on the digital controller interface card and the plant transfer function, which is implemented on the TMS32010 EVM/AlB combination, is a sampled data system operating one-tenth of the controller sample rate.

#### 5.4 IMPLEMENTATION OF THE PLANT ON THE TEXAS INSTRUMENTS TMS32Ø1Ø EVM MICROCOMPUTER

Equation (23) must be converted to a difference equation so that the plant transfer function can be implemented directly on the EVM. Solving equation (23) for Y(z) yields the following:

$$Y(z) = 2.493z^{-1}Y(z) - 2.037z^{-2}Y(z) + 0.544z^{-3}Y(z) + 0.00192X(z) + 0.00577z^{-1}X(z) + 0.00577z^{-2}X(z) + 0.00192z^{-3}X(z)$$

(24)

Notice that the first two coefficients are larger than one, which means that scaling must be employed to obtain functional values for the coefficients. The smallest number that is equal to  $2^n$  and larger than all of the coefficients is 4. Dividing all coefficients of equation (24) is effectively a normalization process. Taking the inverse Z-transform and converting the coefficients to their representative hexidecimal values which results in the following:

$$\frac{Y(K)}{4} = 4FCE*Y(K-1)+BED1*Y(K-2)+1168*Y(K-3)+0010*X(K)002F*X(K-1)$$

$$+002F*X(K-2)+0010*X(K-3)$$

(25)

Equation (25) can now be programmed directly into TMS32010 assembly language, employing the same techniques as used when the digital control equation was implemented in software. Figure 19 is a flow chart for implementation of the digitized plant transfer function on the TMS32010 EVM/A1B system.

#### 5.5 STEP RESPONSE OF THE TMS32010 PLANT

The unit step response of the uncompensated digital plant at T=Ø.Ø15 sec. was not obtainable for some unknown reason, so a search into the possible problems was conducted. The software was checked for

7

Figure 19. Flow chart of the TMS 32010 package for the digitized plant

any logic or programming errors. corrections were made, but the control loop still did not function properly. Once the program had been thoroughly checked, the next step was to try a slower sampling rate, in this case T=Ø.15 sec. The unit step response of Figure 20 is that of the uncompensated digital plant in closed loop form with the slower sampling rate. The unit step response had proven that the program was indeed working, since there is little difference between this program and the program for the digitized plant operating at T=9.915 sec. Furthermore, the plant is undersampled at  $T=\emptyset.\emptyset15$  sec., an indication that a higher sampling rate is definitely needed for proper plant representation. The major difference between the two plant programs is in the coefficients of the difference equation. Closer inspection of equation (24) shows that the ratio between the largest coefficient and the smallest coefficient is approximately 1300 to 1. This large of a coefficient span was not represented accurately with the fixed point binary numbering scheme. The use of coefficient normalization apparently added to the problem. By comparison, the closed loop representation of the T=0.15 sec. plant required no coefficient normalization and the span of the coefficients was smaller.

The problem just discussed becomes worse as the sampling rate of a system is increased. Direct implementation of a difference equation is not feasible particularly when higher sampling rates are used. An alternative method of implementation that produces more manageable fixed point coefficients is needed. One method which may work is to represent the plant as a set of discrete state equations.

â

#### 5.6 STATE SPACE REPRESENTATION OF THE PLANT

The characteristics of the plant can be represented in standard state space form as:

$$\mathbf{x} = \mathbf{A}\mathbf{x} + \mathbf{B}\mathbf{u} \tag{26}$$

$$\mathbf{y} = \mathbf{C}^{\mathrm{T}} \mathbf{x} \tag{27}$$

where

$$A = \begin{bmatrix} \emptyset & 1 & \emptyset \\ \emptyset & \emptyset & 1 \\ \emptyset & -3\emptyset\emptyset & -4\emptyset \end{bmatrix}$$

(28)

$$B = \begin{bmatrix} \emptyset \\ \emptyset \\ 6\emptyset\emptyset\emptyset\emptyset \end{bmatrix}$$

(29)

The block diagram of this system is shown in Figure 21. An equivalent system can be derived by changing the B and  $C^{T}$  matrices slightly. The resulting matrices are:

$$B = \begin{bmatrix} \emptyset \\ \emptyset \\ 1 \\ 1 \\ \emptyset \\ \emptyset \end{bmatrix}$$

(31)

$$\mathbf{C}^{\mathbf{T}} = \{ \mathbf{6} \boldsymbol{\emptyset} \ \boldsymbol{\emptyset} \ \mathbf{0} \} \tag{32}$$

The block diagram of the alternative state space form is shown in Figure 22. The discrete state transition equations are given by:

$$X(K + 1) = \Phi X(K) + \theta u(K)$$

(33)

trice to the trice

West Constant

F

$$C(K) = DX(K)$$

(34)

where

المتحذ متحد لما

$$\bullet = \mathcal{A}^{-1}(SI - A)^{-1}$$

(35)

$$\theta = \int_{\beta}^{T} \Phi(T - \tau) B d\tau$$

(36)

The alternative state space representation can be implemented in the following manner. Portions of Figure 22 can be converted directly into discrete state space form. Forming a system including only the first two integraters will give:

$$\mathbf{A} = \begin{bmatrix} \emptyset & 1 \\ -3\emptyset\emptyset & -4\emptyset \end{bmatrix}$$

(37)

$$B = \begin{bmatrix} \emptyset \\ 1 \emptyset \emptyset \end{bmatrix} .$$

(38)

Solving equation (35) and equation (36) yields:

The discrete state equations of this system become:

$$\begin{bmatrix} \mathbf{X}_{1}(\mathbf{K}+1) \\ \mathbf{X}_{2}(\mathbf{K}+1) \end{bmatrix} = \begin{bmatrix} \emptyset.972 & \emptyset.\emptyset11 \\ -3.346 & \emptyset.526 \end{bmatrix} \begin{bmatrix} \mathbf{X}_{1}(\mathbf{K}) \\ \mathbf{X}_{2}(\mathbf{K}) \end{bmatrix} + \begin{bmatrix} \emptyset.\emptyset09 \\ 1.115 \end{bmatrix} U(\mathbf{K})$$

(41)

The remaining portion of the system to be implemented is:

$$y = \frac{6\emptyset}{8} X_1$$

(42)

Substituting equation (17) into equation (42) and using value of  $T=\emptyset.\emptyset15$  sec. will give:

$$y = \emptyset.45 X_1(K) + \emptyset.45 X_1(K-1) + y(K-1)$$

(43)

Equation (41) and equation (43) totally discribe the system characteristics and can be implemented in software without the coefficient problems which were previously discussed. Verification of the discrete state space technique is left as an exercise for future control studies.

P

#### 6.Ø CONCLUSIONS

The major objective of this control study was to demonstrate the effectiveness of using 16-bit microprocessors for digital control applications. Emphasis was placed on control implementation techniques and error identification rather than control algorithm analysis. Control loop performance was measured for several hardware configurations and several control algorithm variations.

Sources of error which effect the performance of the control loop were identified. Methods were suggested which would reduce the error effects. Quantization error was the most troublesome error encountered. The use of larger bit-sized converters reduced quantization error significantly. Computation delay was shown to introduce a slight amount of error in the control loop during transients as the amount of delay increased. Computation delay did not seem to effect the steady-state behavior of the control loop. To insure proper performance, the microprocessor must be able to execute the control algorithm well within the sampling period so that the effects of the computation delay will be minimized.

The stated objectives of the control study were met. Digital control using microprocessors is practical when considering a control strategy. The increased execution speed of the DSP chips will undoubtedly make these devices even more suitable for more complex

digital control applications. It is recommended that additional control studies be performed which would exploit the full capabilities of the newer DSP chips. APPENDIX A1

|                         |                                  | <br>             |                                               |

|-------------------------|----------------------------------|------------------|-----------------------------------------------|

| TUTOR<br>001000         | 1.1 > MD 1000 DA;D1<br>46FC2000  | <br>HOVE .W      | : 8 BIT D/A ) 5/1/83<br>88192.5R              |

| 001004                  | 4280                             | CLR.L            | DO                                            |

| 881886                  | 7284                             | MOVEQ.L          | #4,D1                                         |

| 00100B                  | 20700030000                      | HOVE .L          | #19668B,A0                                    |

| 00100E                  | 3000                             | MOVE .N          | D8,(A8)+                                      |

| 881818                  | 3801                             | MOVE .N          | D1,(A8)+<br>D8,(A8)+                          |

| 001012<br>001014        | 38C8<br>38C1                     | MOVE .W          | D1.(A8)+                                      |

| 881816                  | 4648                             | NOT .W           | <b>D0</b>                                     |

| \$01\$1B                | 3000                             | MOVE .W          | D8,(A8)+                                      |

| 88181A                  | 36C1                             | MOVE .W          | D1, (A0) +                                    |

| 66161C                  | 3000                             | MOVE .W          | D0, (A0) +                                    |

| 00101E                  | 3001                             | MOVE .W          | D1,(A0)+                                      |

| 001020                  | 13FC008000030009<br>203C008E4E1C | MOVE.B<br>MOVE.L | #128, <b>\$80838889</b><br>#937 <b>588,00</b> |

| 001028<br>00102E        | 207000010025                     | MOVELL           | #65573. <b>AB</b>                             |

| 001034                  | 0100000                          |                  | D8,58988(A8)                                  |

| 001030                  | 13FC000000010035                 | MOVE .B          | #8,\$88818835                                 |

| 881848                  | 4260                             | CLR.L            | De                                            |

| 001042                  | 4281                             | CLR.L            | .D1                                           |

| 881844                  | 4282                             | CLR.L<br>CLR.L   | D2<br>D3                                      |

| <b>881846</b><br>881848 | 4283<br>327 <b>C2008</b>         | MOVE W           | #8192,A1                                      |

| \$8184C                 | 347C2002                         | MOVE .W          | #8194,A2                                      |

| 661638                  | 36702004                         | MOVE .W          | #8194,A3                                      |

| 881854                  | 38702918                         | MOVE .W          | #820B,A4                                      |

| 88185B                  | 3A7C2020                         | MOVE .W          | #8224,A5                                      |

| 68165C                  | 328C3666                         | MOVE .W          | #13926,(A1)                                   |

| 001060                  | 34BC 1386<br>368C6A5E            | MOVE.W           | #5846,(A2)<br>#2654,(A3)                      |

| 001064<br>001068        | 4254                             | CLR.W            | (44)                                          |

| 80186A                  | 4255                             | CLR.W            | (A5)                                          |

| 60106C                  | 13FC884888818823                 | MOVE.B           | <b>64,400010023</b>                           |

| 021874                  | 21FC000010880100                 | MOVE .L          | 44232,\$888688188                             |

| 00107C                  | 13FC00A100010021                 | MOVE.B           | #161, <b>\$888</b> 18821                      |

| <b>001004</b>           | 4E71<br>40FC                     | NOP<br>Bra.s     | \$0818B4                                      |

| 001086<br>001088        |                                  | MOVE .B          | W1,988818835                                  |

| 881878                  | 143788838681                     | MOVE .B          | \$00030001,D2                                 |

| 881896                  | 143700030001                     | MOVE.B           | \$08036001,D2                                 |

| 88189C                  | 6A828888                         | EOR.8            | #128,D2                                       |

| 6616A8                  | 4482                             | NEG.B            | D2                                            |

| 8818A2                  | 4882<br>4286                     | EXT.W<br>Clr.L   | D2<br>D6                                      |

| 0819A4<br>8819A6        |                                  | MOVE .W          | · · · · · · · · · · · · · · · · · · ·         |

| 6818AB                  |                                  | MOVE .W          | (A4) ,D3                                      |

| 8818AA                  |                                  | MOVE .W          | D2, (Å4)                                      |

| 0010AC                  | ·                                | HULS.W           | (A1),D1                                       |

| 0010AE                  | i na n                           | MOVE .L          |                                               |

| \$81\$B8                |                                  | HULS.W           | (A2),D2<br>D2,D6                              |

| 0010B2<br>0010B4        |                                  | MULS.W           |                                               |

| \$816B6                 |                                  | SUB.L            | D3, D6                                        |

| 0010B8                  |                                  | ASL .L           | #1,D6 *                                       |

| 8019BA                  | 2486                             | MOVE.L           | D6, (A5)                                      |

| 6018BC                  |                                  | BMI.S            | 50010D4                                       |

| 0010BE                  |                                  | BSET             | . 023,06                                      |

| 0010C2                  |                                  | SHAP.N<br>MOVE.B |                                               |

| 0010C4<br>0010CA        | ·                                | CLR.L            | D9                                            |

| 001000                  |                                  | CLR.L            | D1                                            |

| 0010CE                  |                                  | CLR.L            | D2                                            |

| 08 18 DE                | 4283                             | CLR.L            | D3                                            |

|                         |                                  |                  |                                               |

# APPENDIX A2 (CONTINUED)

| 0818D2<br>0616D4<br>0810D8 | 4E73<br>08868817<br>68E8 | RTE<br>BCLR<br>BRA.S | #23,D6<br>68818C2 |

|----------------------------|--------------------------|----------------------|-------------------|

|                            |                          |                      |                   |

TUTOR 1.1 >

# APPENDIX A2

S.

0

| TUTOR<br>601000  | 1.1 > MD 1000 11E;DI<br>44FC2000      | ( B BIT A/D 1 12 BIT D/A ) 5/1/83<br>MOVE W 08192,58 |

|------------------|---------------------------------------|------------------------------------------------------|

|                  | 4288                                  | CLR.L DB                                             |

| 891884<br>891886 | 7284                                  | MOVEQ.L #4,D1                                        |

|                  | 13000030003                           | MOVE.B D0, \$00030003                                |

| 00100E           | 13000030007                           | MOVE. B D0, \$00030007                               |

| 001014           | 13C00003000B                          | MOVE.B DO, SOOB 3000B                                |

| 88191A           | 13C00003000F                          | MOVE.B D0,48883088F                                  |

| 881828           | 13000030001                           | MOVE.B D0, \$00030001                                |

| 681826           | 130100030003                          | MOVE.B D1, \$00030003                                |

| 00102C           | 13000030005                           | MOVE.B D0,400030005                                  |

| 001032           | 130100030007                          | MOVE.B D1,600030007<br>Not.b D0                      |

| 001038<br>00103A | 4688<br>130888838889                  | MOVE.B D8,688838889                                  |

| 881848           | 13C 10003000B                         | MOVE.B D1, \$98838888                                |

| 001046           | 13C68883888D                          | MOVE.B D8, \$8883888D                                |

| 60104C           | 13C10003008F                          | MOVE.B D1, \$8883888F                                |

| 001052           | 13FC0080003000D                       | MOVE.B #128,68083080D                                |

| 88185A           | 13FC800008630009                      | MOVE.B 48,588838889                                  |

| 001062           | 203C000E4E1C                          | MOVE.L #937500,D0                                    |

| 001068           | 20700010025                           | MOVE.L 465573,A0<br>Movep.L D0,\$0000(A0)            |

| 00106E<br>001072 | <b>e</b> 1C80000<br>13FC0000000010035 | MOVE.B #8,\$88818835                                 |

| 80187A           | 4288                                  | CLR.L DO                                             |

| 08107C           | 4281                                  | CLR.L D1                                             |

| 00107E           | 4282                                  | CLR.L D2                                             |

| <b>8</b> 01888   | 4283                                  | CLR.L D3                                             |

| <b>001082</b>    | 327C2000                              | MOVE.W #8192,A1                                      |

| 001086           | 347C2002                              | MOVE.W #8194,A2                                      |

| 8818BA           | 36702004                              | MOVE.W #8196,A3<br>Move.W #8268,A4                   |

| 00108E<br>001092 | 387C2010<br>3A7C2020                  | MOVE .W #8224,A5                                     |

| 001096           | 32BC3666                              | MOVE.W #13926, (A1)                                  |

| 88189A           | 34BC 13B6                             | MOVE .W #5046, (A2)                                  |

| 88189E           | 36BCOA5E                              | MOVE .W #2654, (A3)                                  |

| 0010A2           | 4254                                  | CLR.W (A4)                                           |

| 8818A4           | 4255                                  | CLR.W (A5)                                           |

| 881846           | 13FC004000010023                      | MOVE.B #64,688618823                                 |

| 0010AE<br>0010B6 | 21FC000010C20100<br>13FC00A100010021  | MDVE.L #4298,\$888888188<br>MOVE.B #161,\$88818821   |

| 0010BE           | 4671                                  | NOP                                                  |

| 8818C8           | 60FC                                  | BRA.S \$60108E                                       |

| 0010C2           | 13FC000100010035                      | MOVE.B #1,688818835                                  |

| 8818CA           | 143988838881                          | MOVE.B \$00030001,D2                                 |

| 0010D8           | 143988838881                          | MOVE.B \$88838881,D2                                 |

| 6818D6           |                                       | EOR.B #128,D2<br>NEG.B D2                            |

| 8818DA           |                                       | EXT.W D2                                             |

| 0010DC<br>0010DE |                                       | CLR.L D6                                             |

| 6619E8           |                                       | MOVE .W (A5) ,D1                                     |