| UNCI     | LASSIFIE                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | - | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -           | RADC | -TR-80-            | 274         | Conception in the | NL                                                                                                             |         |   |

|----------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|--------------------|-------------|-------------------|----------------------------------------------------------------------------------------------------------------|---------|---|

|          | 1 of <b>2</b>                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      |                    | a. Alimeter | No.               |                                                                                                                | il data |   |

|          |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | And an and the second s |             |      |                    |             |                   |                                                                                                                |         |   |

|          | plantania<br>Bilipinani<br>etinganani<br>Bilipinani<br>etinganani<br>etinganan |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1_1=1=1<br> |      |                    |             |                   | BUYCHINAN<br>ALTRACIAN<br>COMPANY<br>COMPANY<br>COMPANY<br>COMPANY<br>COMPANY<br>COMPANY<br>COMPANY<br>COMPANY |         |   |

|          |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      |                    |             |                   |                                                                                                                |         |   |

|          |                                                                                | 120 million<br>120 m |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12.20 B     | 11   | 1.                 |             |                   | Ľ                                                                                                              | Ŧ       |   |

| <b>7</b> | ***                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |      |                    |             |                   |                                                                                                                |         |   |

|          | The state                                                                      | III.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | Terr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | F           |      | Terrore<br>Terrore |             | 黀                 |                                                                                                                |         | T |

This report has been reviewed by the MADC Public Affairs Office (PA) and is releasable to the Marional Tachnical Information Service (NTIS). At NTIS it will be releasable to the general public, including Foreign nations.

RADC-TR-80-274 has been reviewed and is approved for publication.

APPROVED: Thisten 91

WARDER H. DEBANT, JR Project Engineer

APPROVED!

DAVID C. LUKE, Colonel, USAR Chief, Reliability & Compatibility Division

FOR THE COMMANDER: John S. Hurs

JOHN P. HUSS Acting Chief, Plans Office

If your address has changed or if you wish to be removed from the RADC mailing list, or if the addressee is no longer employed by your organisation, please notify RADC (REFA) Griffing AFB W 13461. This will apply us in maintaining a current mailing list.

Do not return this copy. Retain or destroy.

UNCLASSIFIED SECURITY ASSIFICATION OF THIS PAGE (When Data Entered) READ INSTRUCTIONS BEFORE COMPLETING FORM REPORT DOCUMENTATION PAGE 2. GOVT ACCESSION NO. 3. RECIPIENT'S CATALOG NUMBER RADCHTR-80-274 AD-A096360 Final Technical Report-TEST GENERATION AND FAULT ISOLATION FOR Julo 78- Julo 80 MICROPROCESSORS AND THEIR SUPPORT DEVICES. N/A . CONTRACT OR GRANT HUMBER(=) Warren H. Debany, Jr. F30602-78-C-0235 - STATE 10 Patricia A. Watson David A. O'Connor Basil K. Teague Mark S. Zemgulis (RADC 10. PROGRAM ELEMENT, PROJECT, TASK AREA & WORK UNIT NUMBERS EREORMIN General Electric Ordnance Systems 62702F Circuit Test Engineering 23380152 100 Plastics Ave, Pittsfield MA 01201 12. REPORT DATE 1. CONTROLLING OFFICE NAME AND ADORESS Rome Air Development Center (RBRA) November 1080 NUMBER OF PAGES Griffiss AFB NY 13441 191 15. SECURITY CLASS. (of thi 14. MONITORING AGENCY NAME & AOORESS(II dillerent from Controlling Office) UNCLASSIFIED Same 15. OECLASSIFICATION OOWNGRACING 16. OISTRIBUTION STATEMENT (of this Report) Approved for public release; distribution unlimited. 17. OISTRIBUTION STATEMENT (of the ebstrect entered in Block 20, if different from Report) Same 18. SUPPLEMENTARY NOTES RADC Project Engineer: Warren H. Debany, Jr. (RBRA) This report was written jointly by GEOS and RADC. 9. KEY WORDS (Continue on reverse side if necessary and identify by block number) Scanning Electron Automatic Test Equipment IC Microscope Computer-Aided Test LASAR Logic Integrity Test Device Under Test MIL-M-38510 FACTOR TEKTEST LSI, VLSI (See Reverse) High Level Language Qualified Parts Lis VHSIC Qualified Parts List This report covers the generation of tests for complex digital devices, implementation of those tests on currently available ATE, and fault isolation. Techniques are described for the modeling of devices in order to facilitate the testing process. A new algorithm for fault dictionary searching is given. Voltage Contrast (on the Scanning Electron ) (Cont'd DD 1 JAN 73 1473 UNCLASSIFIED EDITION OF I NOV 65 IS OBSOLETE 6 neut pa SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered) 149175

#### UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE(When Dete Entered)

## Item 20 (Cont'd)

Microscope) was used as an aid for fault insertion, which in turn provided test cases for fault isolation. Computer-Aided Test techniques are described. As the demonstration vehicle for this work was the development of MIL-M-38510 Detail Specifications (Slash Sheets) a tutorial description of a recommended slash sheet format is given. Many areas were only touched on during this contract; these have been described, with suggestions for further research topics.

Item 19 (Cont'd)

Computer Programs Software

> UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (When Dete Entered)

## ACKNOWLEDGEMENTS

The authors wish to offer their special thanks to the following persons, without whose help this report could not have been completed:

Tom Dellecave, William Bader, and Jack Haberer, who reviewed sections for

Patti Schram, Lorraine Armstrong, and Marie St. Thomas, for assistance in the data entry and manuscript preparation.

us.

1

6

2

Evelyn Mesagna, whose foresight and planning made the manuscript preparation possible.

Allen Converse, most sincere thanks for the many unpaid weekend and evening hours he spent formatting the final text for the word processor.

| Accession Fo               | r /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NTIS GRA&I                 | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DTIC TAB                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Urannounced                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Justificatio               | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Distributio:<br>Availabili | and the second sec |

| Dist Spec                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1 1                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### SUMMARY

This report is the result of a joint effort by General Electric Ordnance Systems and RADC, to improve RADC's in-house testing capability for complex digital microcircuits.

All of the topics covered relate to either the generation of tests, or the reduction of the data to provide fault isolation.

Section 1 of this report concerns the philosophy held by the investigators at the end of the effort. In many cases, this philosophy differs greatly from that with which the effort started.

Section 2 deals with the development of MIL-M-38510 "Slash Sheets," and the problems encountered when implementing the Slash Sheet tests on current Automatic Test Equipment.

Section 3 discusses the various software tools developed for use during this effort. Two types are shown: those running on the RADC Multics facility, and those which run on the S-3260/3270 IC Tester.

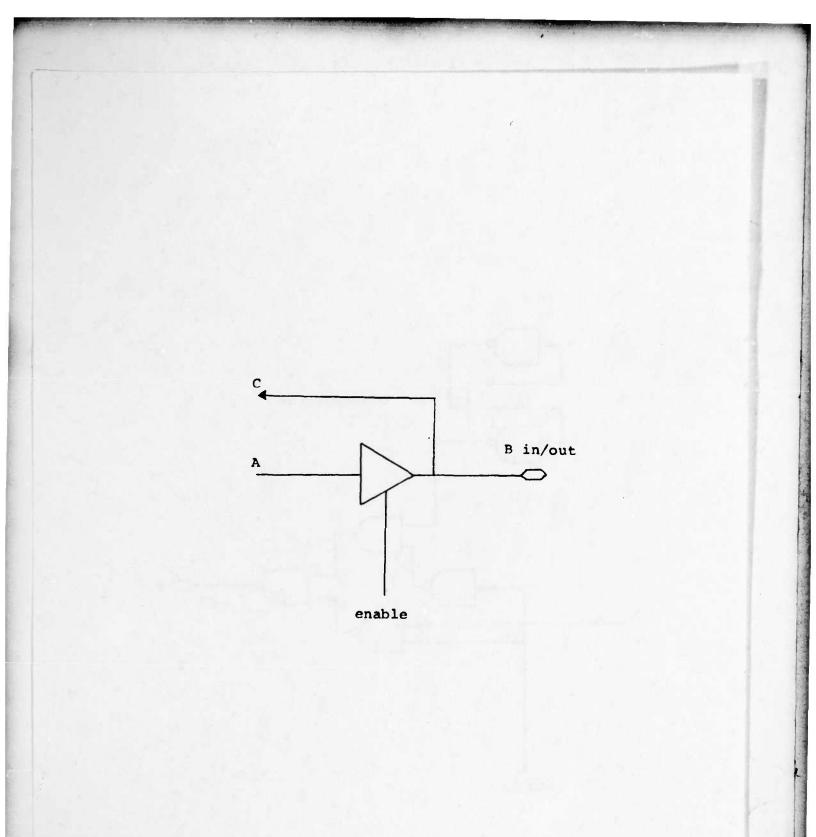

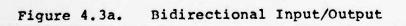

Section 4 describes the development of a test, including the items which should be considered during test generation, and the implementation of the test with the help of ALICE and LASAR.

Section 5 covers the reduction of failure data, producing a concise listing of possible bad nodes in a device (fault isolation). A new matching algorithm for the fault dictionary search was developed for this, and is described in this section.

Section 6 documents the techniques for <u>fault insertion</u> that were used in this effort. This was done to provide test cases for fault isolation.

Section 7 outlines the progress made with each of the devices studied under this effort. The "learning" process, test generation and implementation, fault insertion and isolation are covered.

Section 8 summarizes and provides some recommendations.

Appendix A is a tutorial on the use of Automaton Diagrams, which were one of the most fundamental tools used in this effort.

No "user's manuals" are provided here, as the techniques require further debugging before they should be declared to be complete. Once the rough spots have been fixed, more documentation will most likely follow, in the form of monographs or technical reports.

iv

# TABLE OF CONTENTS

| Section | Title                                              | Page No. |

|---------|----------------------------------------------------|----------|

| 1.      | Introduction                                       | 1        |

|         |                                                    |          |

| 2.      | Specification Writing                              | 4        |

| 2.1     | Outline of a Slash Sheet                           | 4        |

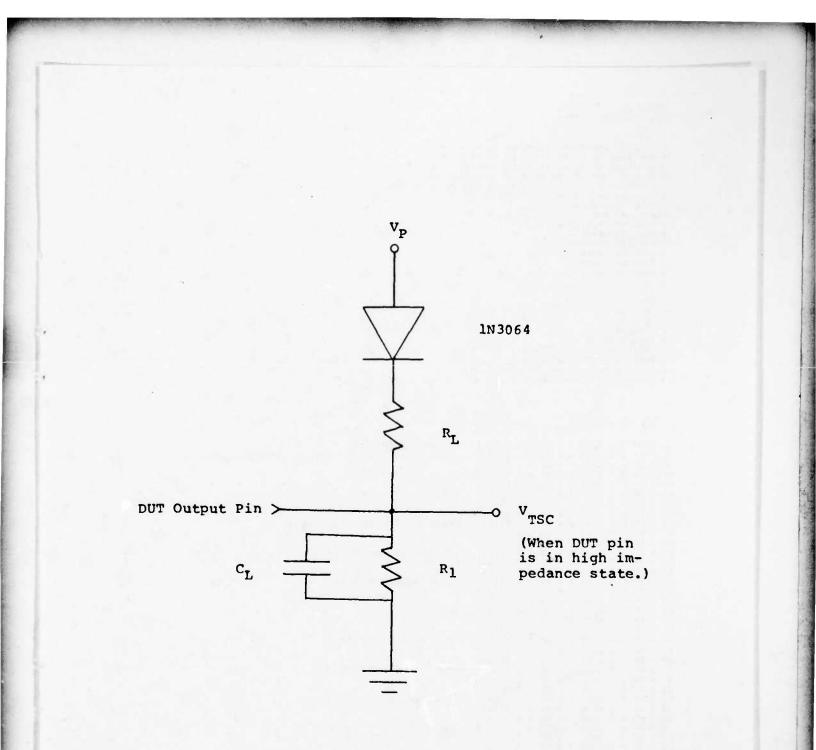

| 2.2     | Detailed Test Requirements                         | 8        |

| 2.2.1   | DC Parametric Tests                                | 8        |

| 2.2.2   | Logic Integrity Test                               | 10       |

| 2.2.3   | AC Parametric Tests                                | 10       |

| 2.2.4   | Limitations and Comments                           | 10       |

| 2.3     | Test Techniques                                    | 13       |

| 2.4     | Tester Limitations                                 | 13       |

| 2.4.1   | Comparison of Architectures                        | 14       |

| 2.4.2   | Modes of Operation                                 | 15       |

| 2.4.3   | Features Common to the S-3260/3270 and Sentry      | 15       |

| 2.4.3.1 | Cycle time                                         | 15       |

| 2.4.3.2 | Number of Timing Generators                        | 15       |

| 2.4.3.3 | Timing Generator Capabilities                      | 16       |

| 2.4.3.4 | Number of pins                                     | 16       |

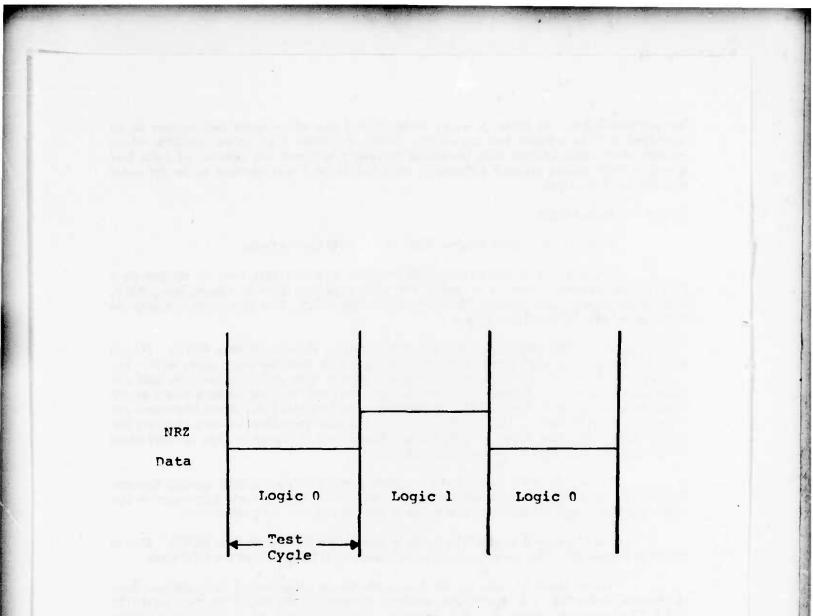

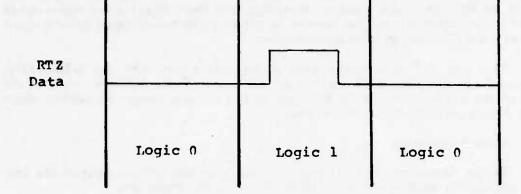

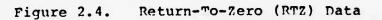

| 2.4.3.5 | Data Modes                                         | 17       |

| 2.4.4   | Test Implementation Limitations of the S-3260/3270 | 17       |

| 2.4.4.1 | Mode 3 Operation                                   | 20       |

| 2.4.4.2 | Double Pulsing                                     | 21       |

| 2.4.4.3 | Loss of Error Information                          | 21       |

| 2.4.4.4 | Timing Tolerance                                   | 22       |

| 2.4.4.5 | Time Measurement System                            | 22       |

| 2.4.4.6 | Programming Language Limitations                   | 23       |

|         |                                                    | 2        |

| 3.      | Computer-Aided Test Implementation Tools           | 25       |

| 3.1     | Programs Running on RADC Multics                   | 25       |

v

10 10 Ma

| Section  | Title                               | Page No. |

|----------|-------------------------------------|----------|

| 3.1.1    | ALICE                               | 26       |

| 3.1.2    | TECO                                | 26       |

| 3.1.3    | DUP                                 | 28       |

| 3.1.4    | ALICENUM                            | 28       |

| 3.1.5    | ADD OUTPUTS                         | 28       |

| 3.1.6    | REDUND                              | 28       |

| 3.1.7    | LOADMODULE                          | 32       |

| 3.1.8    | TEKTRONIX                           | 32       |

| 3.1.9    | SENTRY                              | 32       |

| 3.1.10   | CPAC                                | 32       |

| 3.1.11   | AANDB                               | 34       |

| 3.1.12   | SENPASS, SENPASS2                   | 34       |

| 3.1.13   | NQUINE, SWAPCOL, PLAGEN             | 35       |

| 3.1.14   | ATE_TAPE_UTIL                       | 35       |

| 3.2      | Programs Running on the S-3260/3270 | 35       |

| 3.2.1    | SIMPL Language                      | 36       |

| 3.2.2    | MATSIM Program                      | 36       |

| 3.2.3    | SIMTEK Program                      | 37       |

| 3.2.4    | CODE Routine                        | 37       |

| 3.2.5    | BATLOG Routine                      | 37       |

| 3.2.6    | BATRED Routine                      | 37       |

| 3.2.7    | DATRDB Program                      | 38       |

| 3.2.8    | PATPLO.ASC Routine                  | 38       |

| 3.2.9    | PATPLO.EDT Program                  | 38       |

| 3.2.10   | WAVE Program                        | 38       |

| 3.2.11   | FISO.ASC Routine                    | 38       |

| 3.2.12   | FISOVI Routine                      | 39       |

| 3.2.13   | FISO.EDT Program                    | 39       |

| 3.2.14   | TABPRT                              | 40       |

| 3.2.15   | XYZPRT                              | 40       |

| 3.2.16 * | RESIS                               | 40       |

| 4.       | Test Development and Implementation | 41       |

$d_{\rm s}$

ł

vi

| Section   | Title                                                            | Page No. |  |

|-----------|------------------------------------------------------------------|----------|--|

| 4.1       | Procedure For LSI Functional Test Development                    | 41       |  |

| 4.2       | Writing a LIT using ALICE and LASAR                              | 44       |  |

| 4.2.1     | Developing the ALICE Program                                     | 45       |  |

| 4.2.2     | Running LASAR                                                    | 50       |  |

| 4.2.3     | Using the Output of LASAR                                        | 50       |  |

| 4.3       | SIMPL Test Language                                              | 56       |  |

| 4.3.1     | Test Development and Transfer Problems                           | 56       |  |

| 4.3.2     | Possible Solutions                                               | 57       |  |

| 4.3.2.1   | Standardization of Test Systems.                                 | 57       |  |

| 4.3.2.2   | Conversion Programs                                              | 57       |  |

| 4.3.2.3   | Table Driven Test Generators                                     | 57       |  |

| 4.3.2.4   | Text Processing of Tester Source Language                        | 58       |  |

| 4.3.2.5   | Test Program Written in a High Level Tester Independent Language | 58       |  |

| 4.3.3     | SIMPL Test Language                                              | 58       |  |

| 4.3.3.1   | Philosophy of SIMPL                                              | 58       |  |

| 4.3.3.2   | SIMPL Opcodes                                                    | 59       |  |

| 4.3.3.3   | Program Restrictions                                             | 65       |  |

| 4.3.4     | SIMPL Interpreter Programs                                       | 66       |  |

| 4.3.4.1   | Philosophy                                                       | 66       |  |

| 4.3.4.2   | SIMFAIR Interpreter                                              | 66       |  |

| 4.3.4.3   | SIMTEK Interpreter                                               | 66       |  |

| 4.3.5     | Developing a SIMTEK Test                                         | 66       |  |

| 4.3.5.1   | Philosophy                                                       | 66       |  |

| 4.3.5.1.1 | The ".PIN" file                                                  | 67       |  |

| 4.3.5.1.2 | The ".PAT" file                                                  | 67       |  |

| 4.3.5.1.3 | The PINLIST                                                      | 67       |  |

| 4.3.5.1.4 | The Main Program                                                 | 67       |  |

| 4.3.5.2   | Development of Load Modules and Socket Card                      | 67       |  |

| 4.3.5.3   | Development of Pin Assignment File                               | 67       |  |

| 4.3.5.4   | Development of PINLIST (SC005.EDT) File                          | 67       |  |

| 4.3.5.4.1 | PIN Array                                                        | 72       |  |

| 4.3.5.4.2 | Pinlists                                                         | 72       |  |

| 4.3.5.5   | Development of a Pattern File                                    | 72       |  |

| Section   | Title                                         | Page No. |

|-----------|-----------------------------------------------|----------|

|           |                                               |          |

| 4.3.5.6   | Development of a Dummy Pattern File           | 72       |

| 4.3.5.7   | Development of the Header (SC001.EDT) File    | 72       |

| 4.3.5.8   | Development of a Device SIMTEK Program        | 77       |

| 4.3.6     | Development of SIMPL Language Device Test     | 80       |

| 4.3.7     | Setup to Log LIT Errors                       | 82       |

| 4.3.7.1   | CODE Routine                                  | 82       |

| 4.3.7.2   | BATLOG Routine                                | 82       |

| 4.3.8     | Testing a Device                              | 82       |

| 4.3.9     | Summary                                       | 85       |

| 5.        | LIT Failure Data Reduction                    | 87       |

| 5.1       | Displaying Logged Data                        | 87       |

| 5.2       | Plotting the Pseudo Timing Waveforms          | 87       |

| 5.3       | Isolating the Failed Element                  | 91       |

| 5.4       | Reformatting the YTABLE                       | 91       |

| 5.5       | Fault Signature Matching Algorithm            | 91       |

| 5.5.1     | XTABLE                                        | 93       |

| 5.5.2     | YTABLE                                        | 93       |

| 5.5.3     | ZTABLE                                        | 93       |

| 5.5.3.1   | The Matching Algorithm                        | 94       |

| 5.5.3.1.1 | The Ideal Case                                | 94       |

| 5.5.3.1.2 | The Non-Ideal Case                            | 97       |

| 5.5.3.2   | The Significance of G                         | 97       |

| 5.5.4     | Other Techniques                              | 97       |

| 6.        | Fault Insertion                               | 99       |

| 6.1       | Fault Site Selection/Circuit Descriptions     | 99       |

| 6.1.1     | Fault Site Selection Considerations           | 99       |

| 6.1.1.1   | Faults that Affect Mutually Exclusive Outputs | 99       |

| 6.1.1.2   | Faults that Affect Diverse Logic Areas        | 100      |

| 6.1.1.3   | Faults That Affect Limited Circuitry          | 100      |

| 6.1.1.4   | Ease of Physical Site Location                | 100      |

| 6.1.2     | Circuit Descriptions                          | 100      |

-

| Section | Title                                           | Page No. |

|---------|-------------------------------------------------|----------|

| 6.1.2.1 | Published Data Sheets                           | 100      |

| 6.1.2.2 | Automaton Diagrams                              | 100      |

| 6.1.2.3 | RADC Product Evaluation Reports                 | 100      |

| 6.1.2.4 | Manufacturer's Logic Schematics                 | 101      |

| 6.2     | Fault Tracing                                   | 101      |

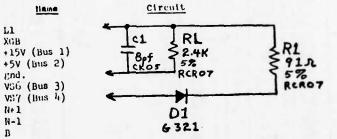

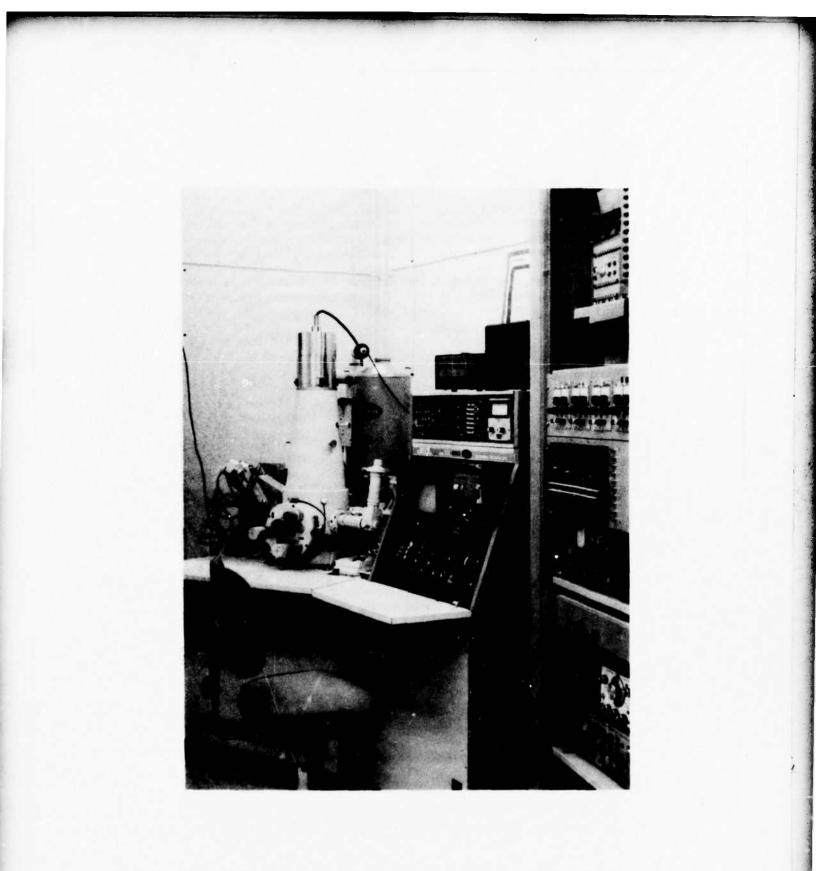

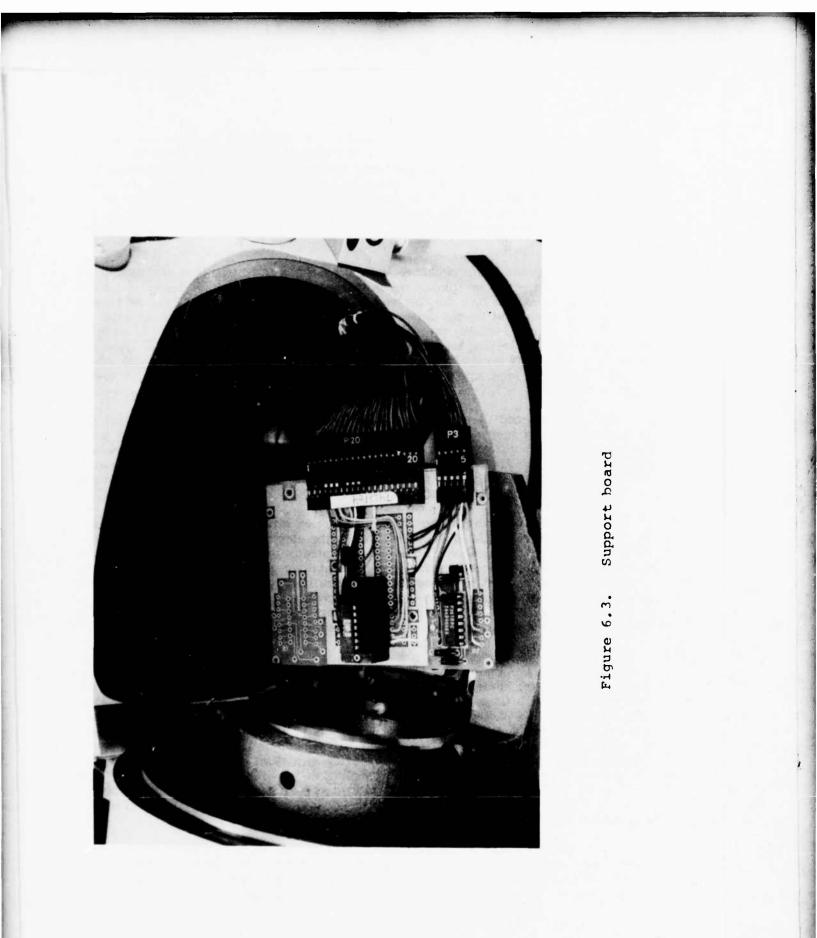

| 6.2.1   | Equipment, Support Circuitry, Adapters          | 103      |

| 6.2.2   | Device Preparation                              | 103      |

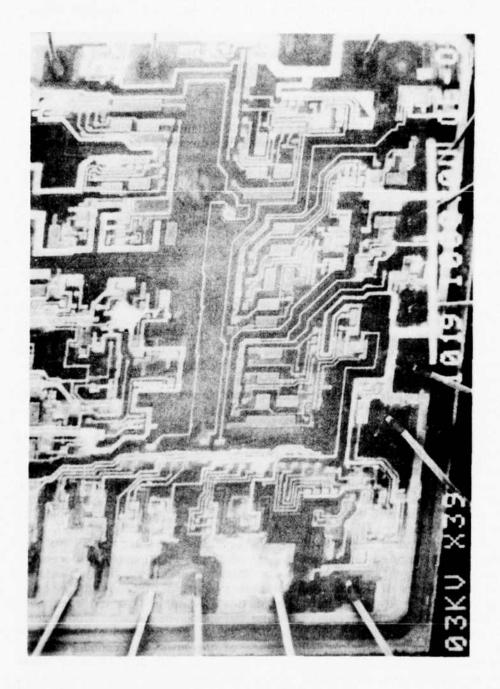

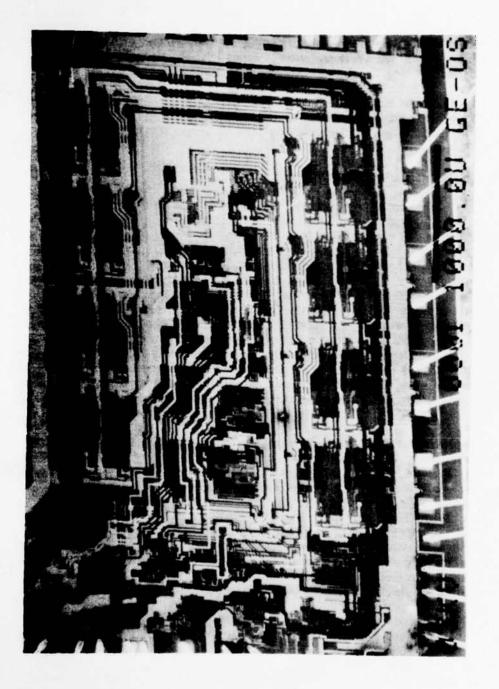

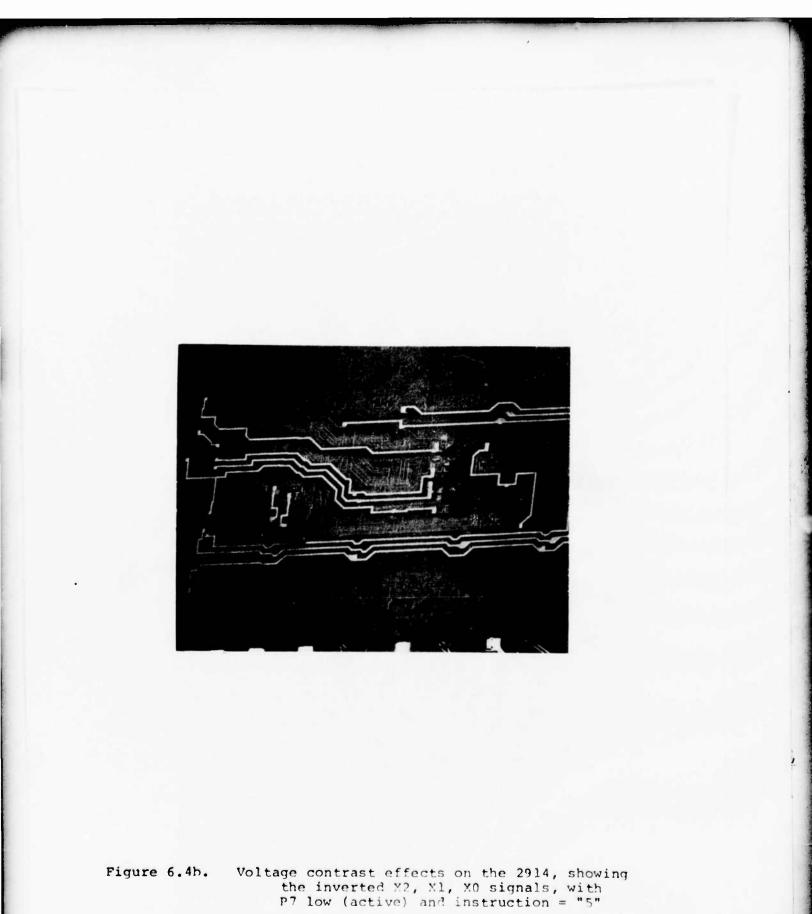

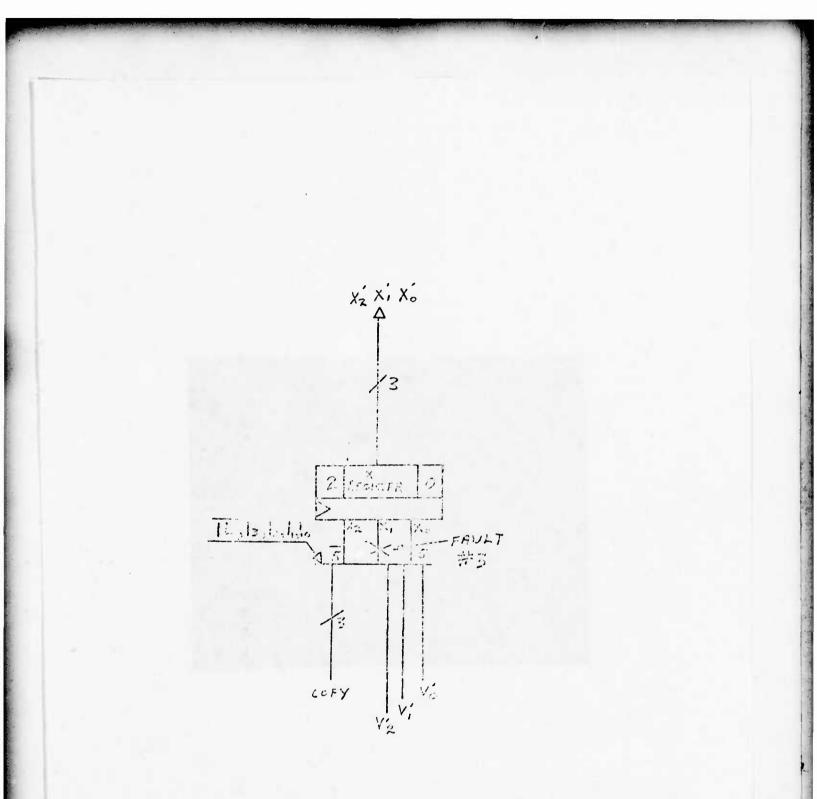

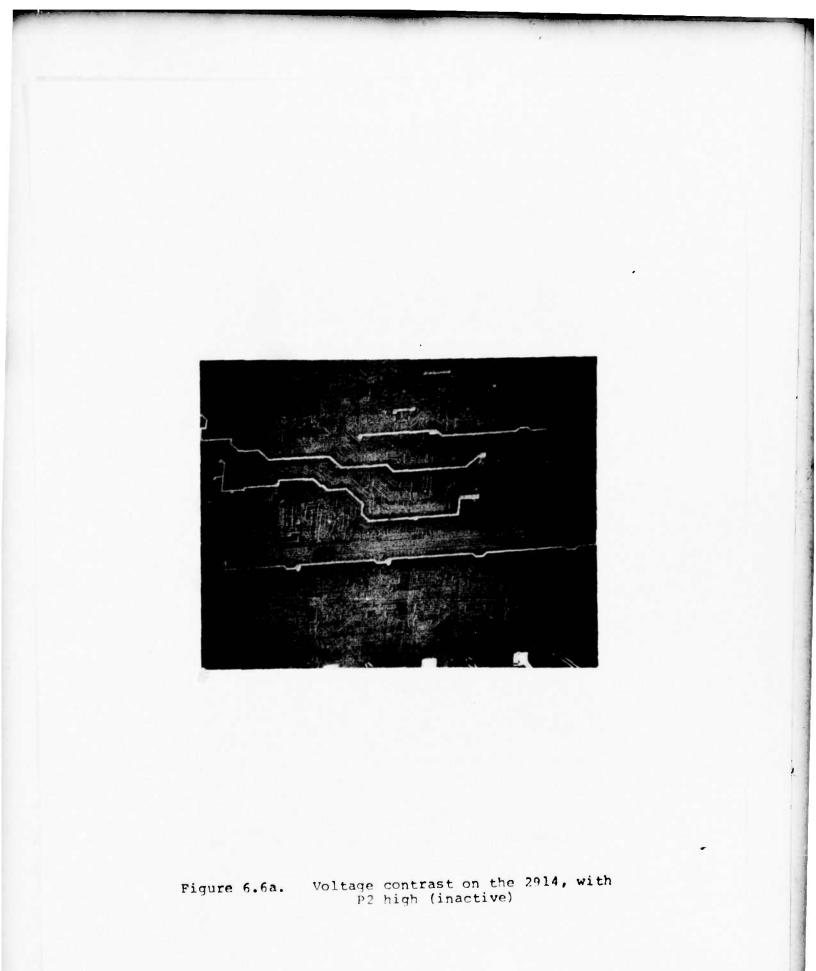

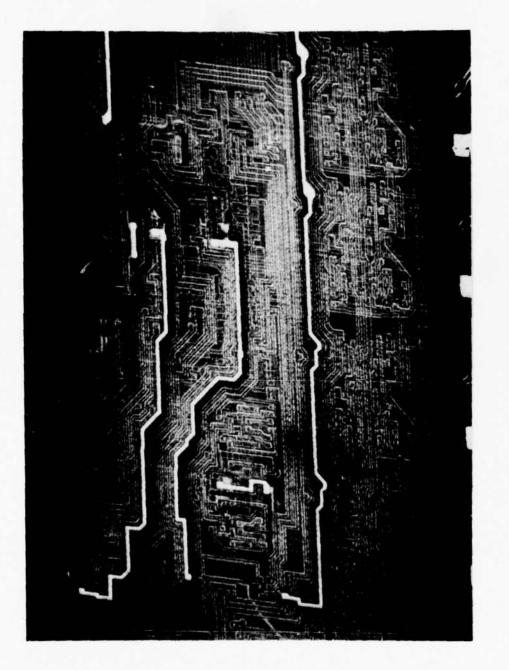

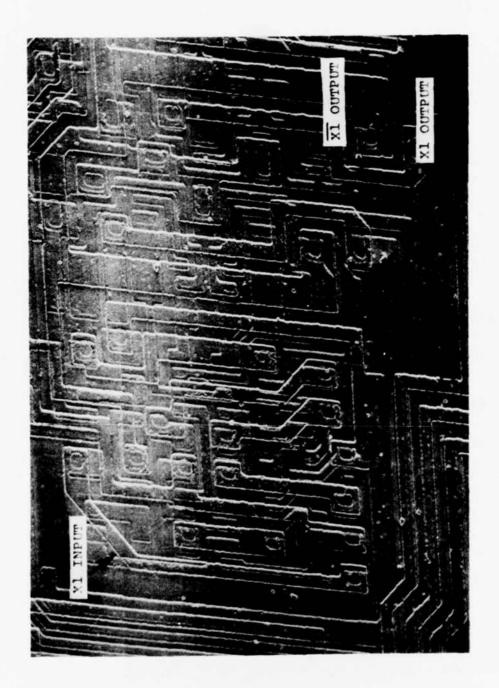

| 6.2.3   | Fault Site Identification with Voltage Contrast | 107      |

| 6.3     | Physical Fault Insertion                        | . 110    |

| 6.4     | False Modeling                                  | 115      |

|         |                                                 |          |

| 7.      | Applications                                    | 117      |

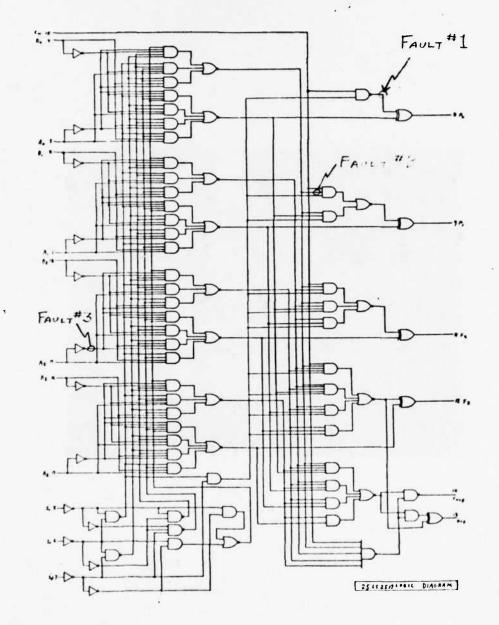

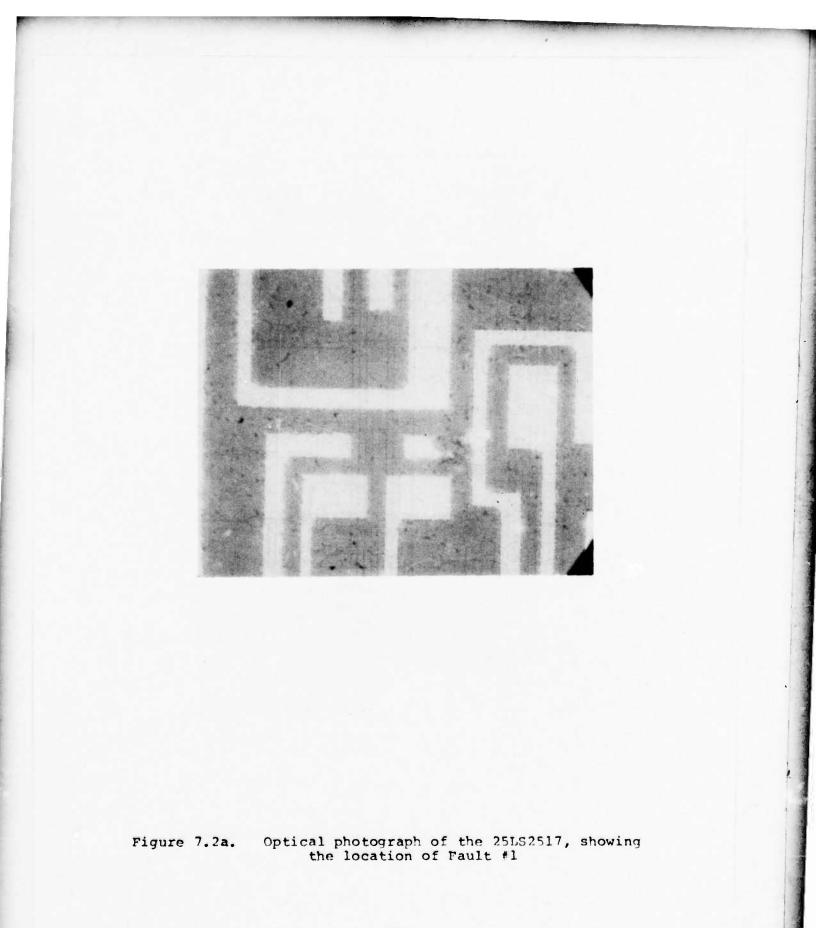

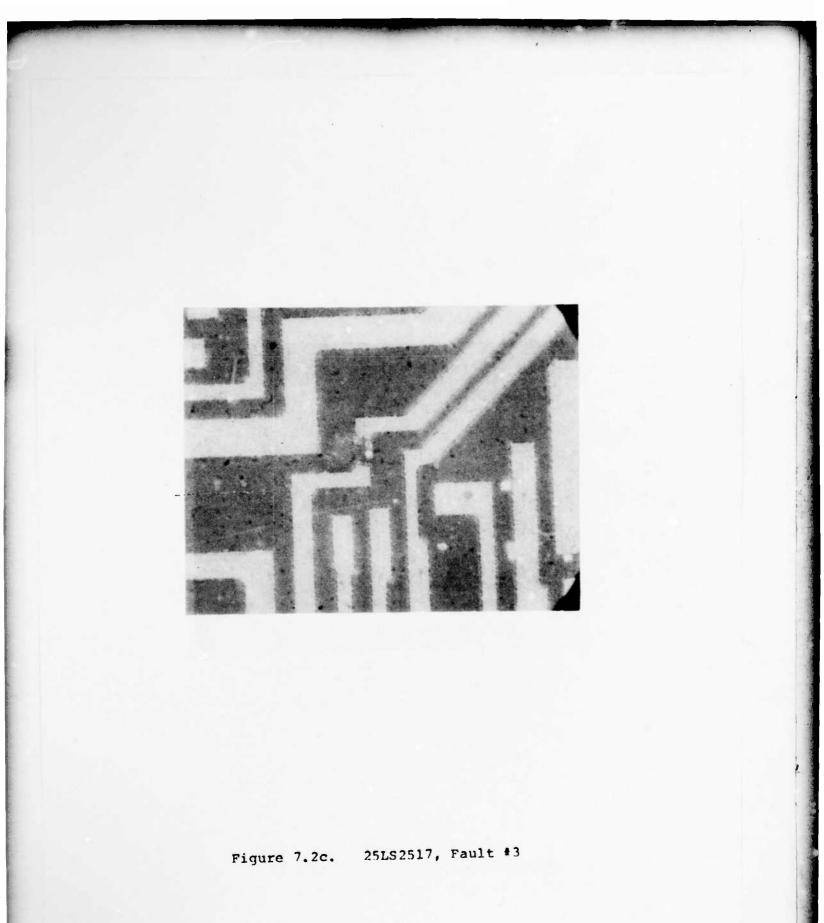

| 7.1     | 25LS2517                                        | 117      |

| 7.1.1   | Learning the 25LS2517                           | 117      |

| 7.1.2   | Test Generation for the 25LS2517                | 117      |

| 7.1.3   | Test Implementation for the 25LS2517            | 117      |

| 7.1.4   | Tracing and Inserting Faults in the 25LS2517    | 118      |

| 7.1.5   | Isolating Faults in the 25LS2517                | 118      |

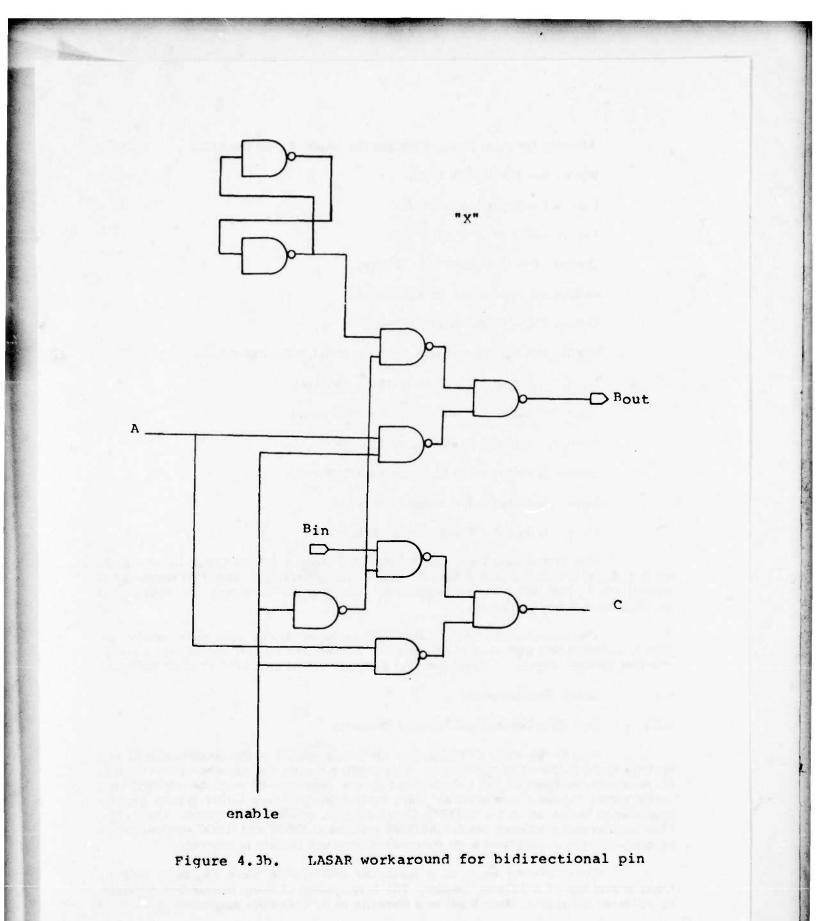

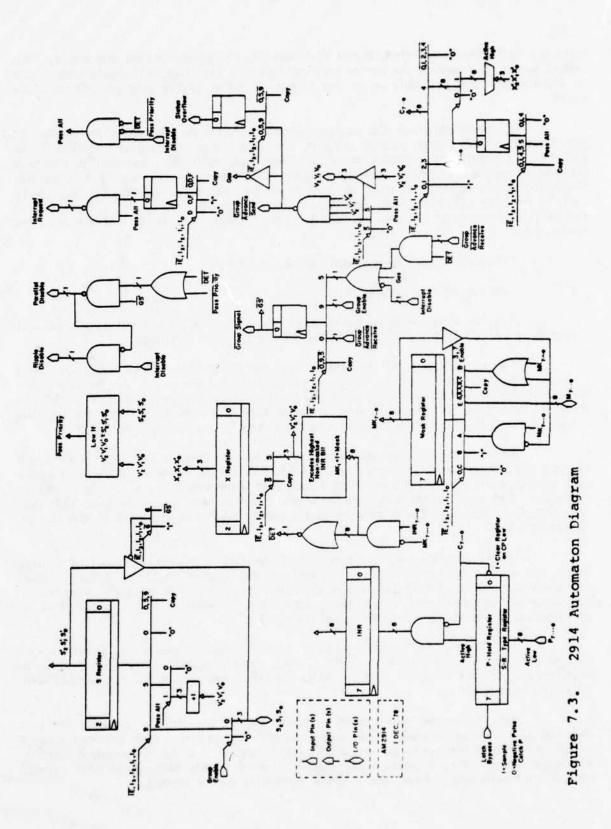

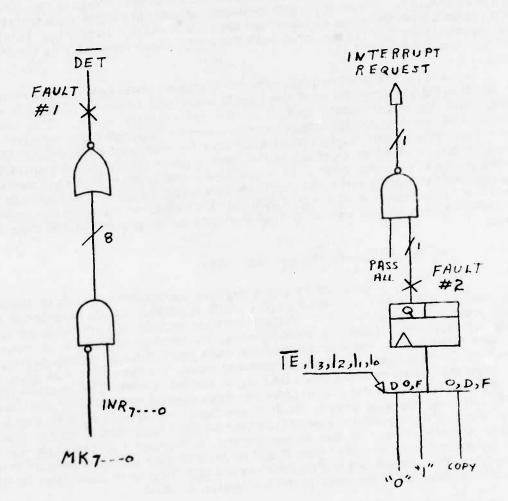

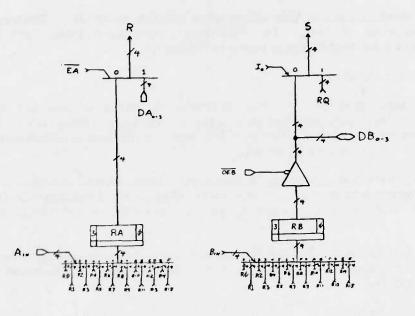

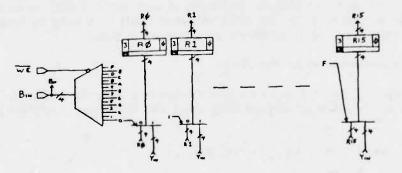

| 7.2     | 2914                                            | 118      |

| 7.2.1   | Learning the 2914                               | 118      |

| 7.2.2   | Test Generation for the 2914                    | 123      |

| 7.2.3   | Test Implementation for the 2914                | 125      |

| 7.2.4   | Tracing and Inserting Faults in the 2914        | 125      |

| 7.2.5   | Isolating Faults in the 2914                    | 125      |

| 7.3     | 15530 :                                         | 131      |

| 7.3.1   | Learning the 15530                              | 131      |

| 7.3.2   | Test Generation for the 15530                   | 131      |

| 7.3.3   | Test Implementation for the 15530               | 132      |

| 7.3.4   | Tracing and Inserting Faults in the 15530       | 132      |

| 7.3.5   | Isolating Faults in the 15530                   | 133      |

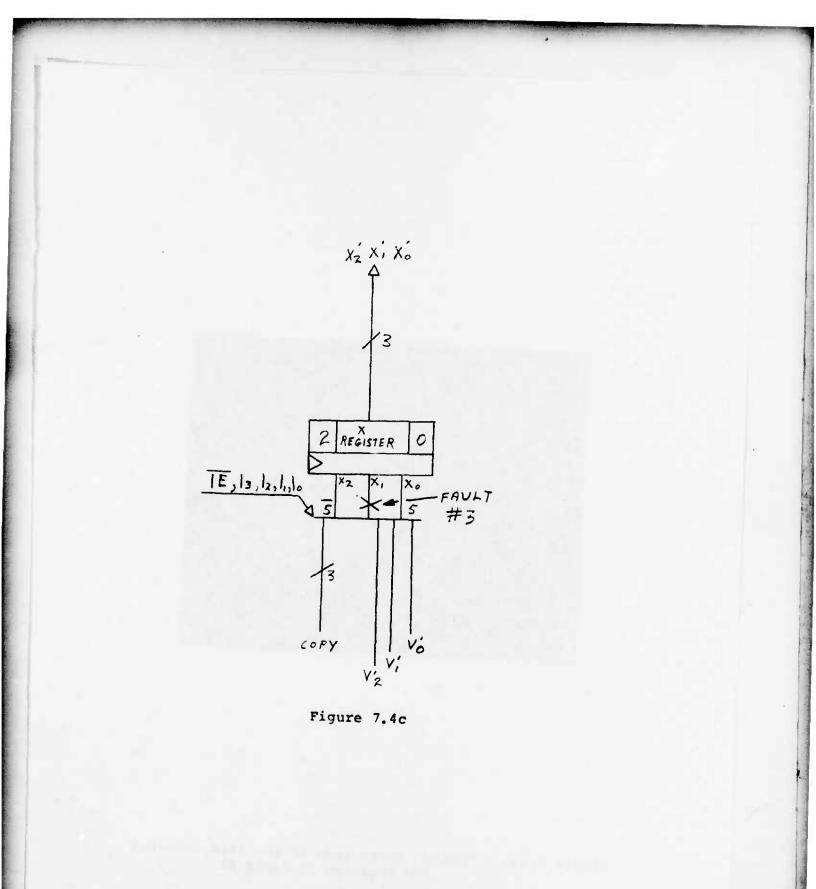

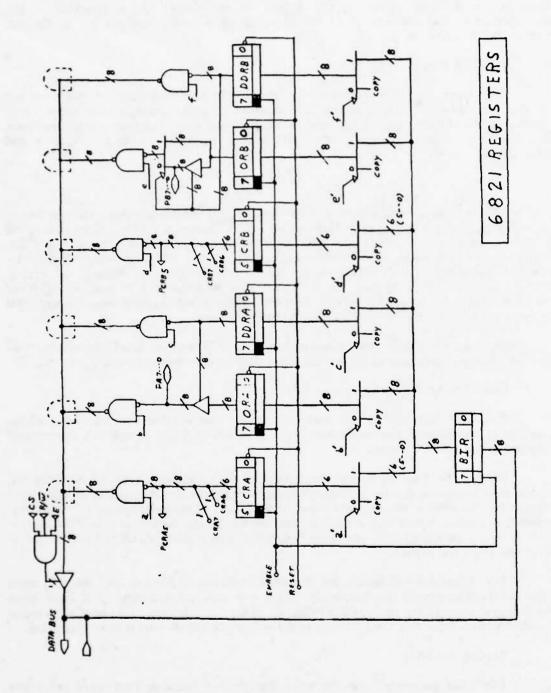

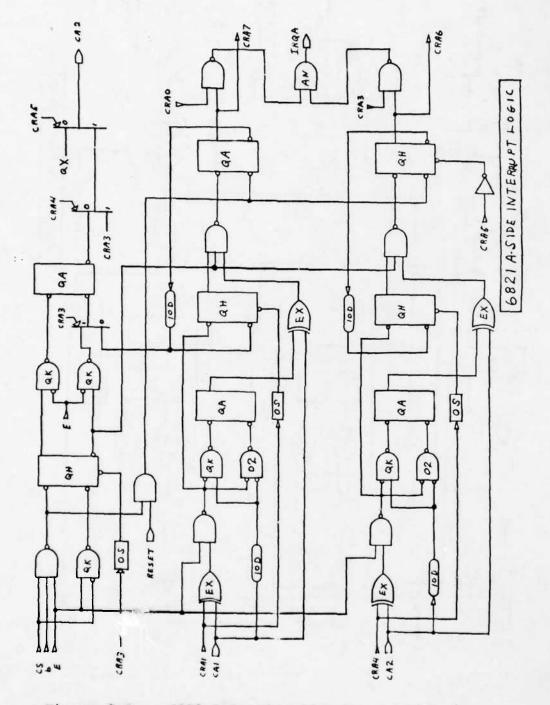

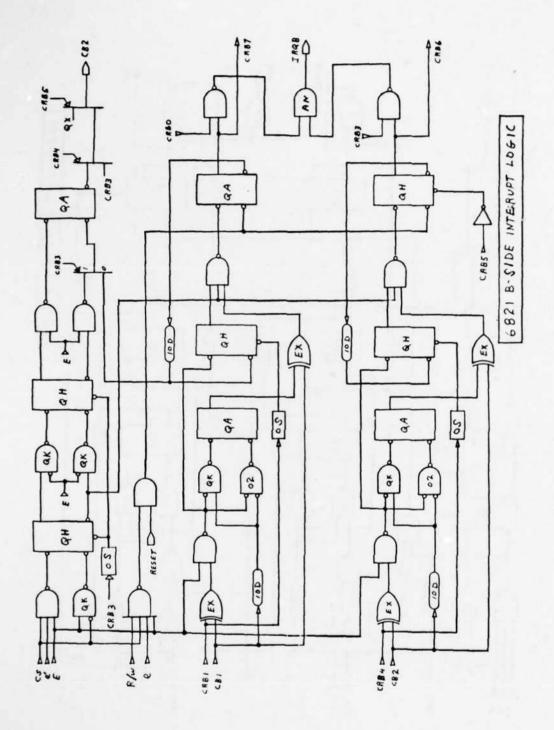

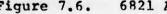

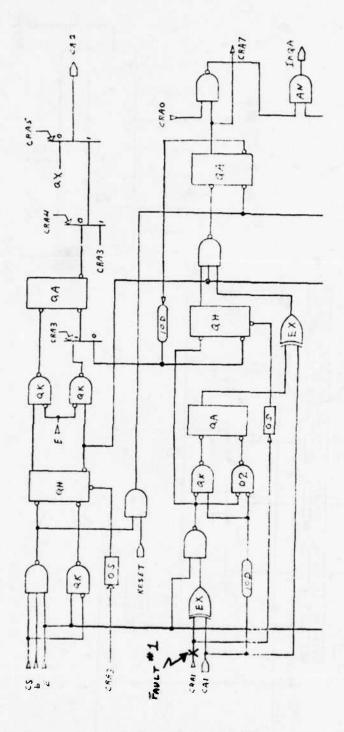

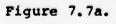

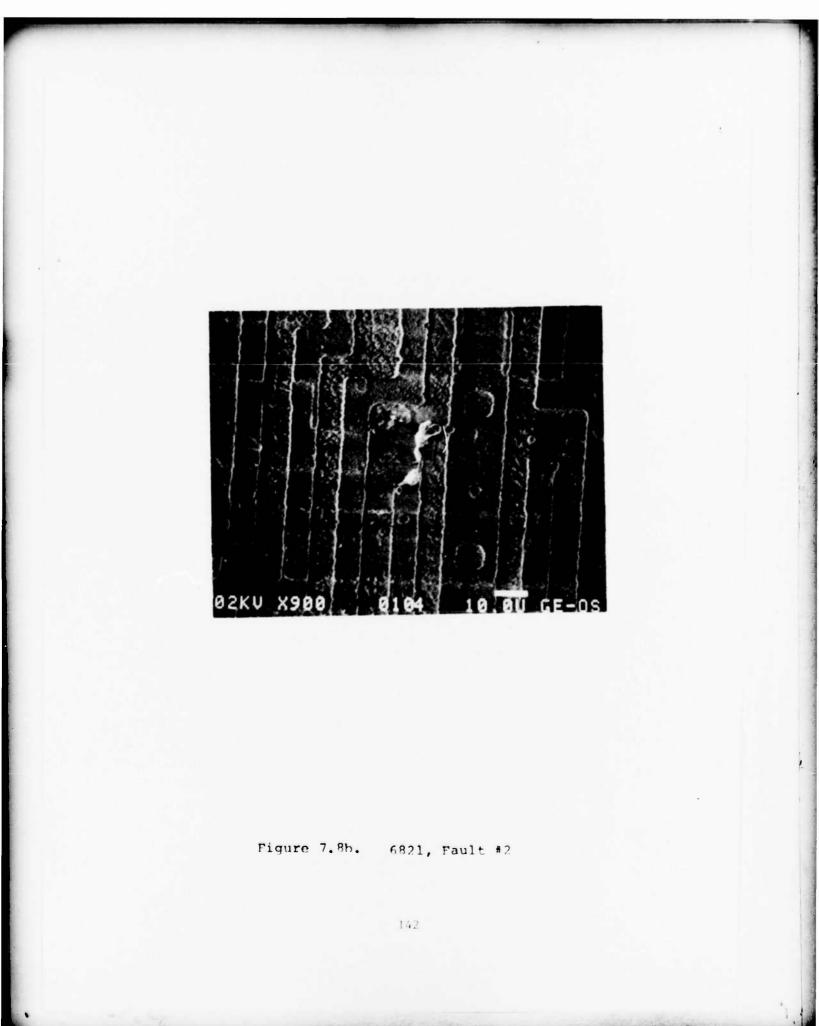

| 7.4     | 6821                                            | 133      |

| 7.4.1   | Learning the 6821                               | 133      |

| 7.4.2   | Testing the 6821                                | 133      |

ix

| Section | Title                                    | Page No. |

|---------|------------------------------------------|----------|

|         |                                          |          |

| 7.4.3   | Test Implementation for the 6821         | 138      |

| 7.4.4   | Tracing and Inserting Faults in the 6821 | - 138    |

| 7.4.5   | Isolating Faults in the 6821             | 138      |

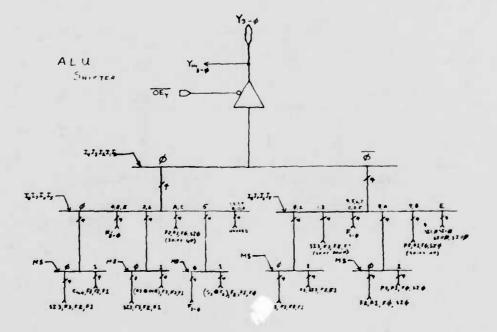

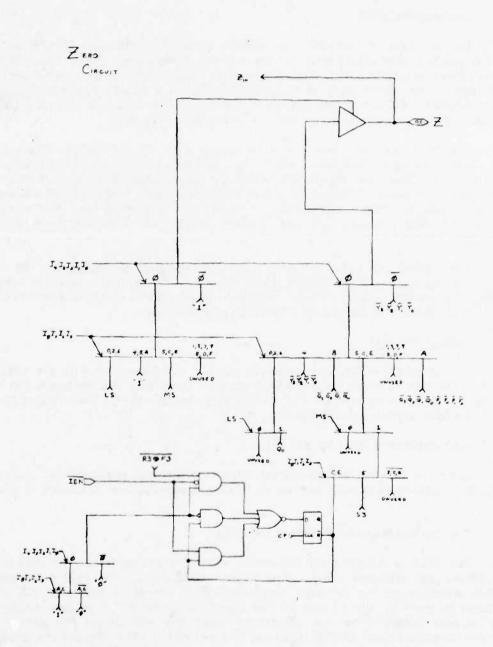

| 7.5     | 2903                                     | 138      |

| 7.5.1   | Learning the 2903                        | 143      |

| 7.5.2   | Testing the 2903                         | 143      |

| 7.5.3   | Test Implementation for the 2903         | 143      |

| 7.5.4   | Tracing and Inserting Faults in the 2903 | 143      |

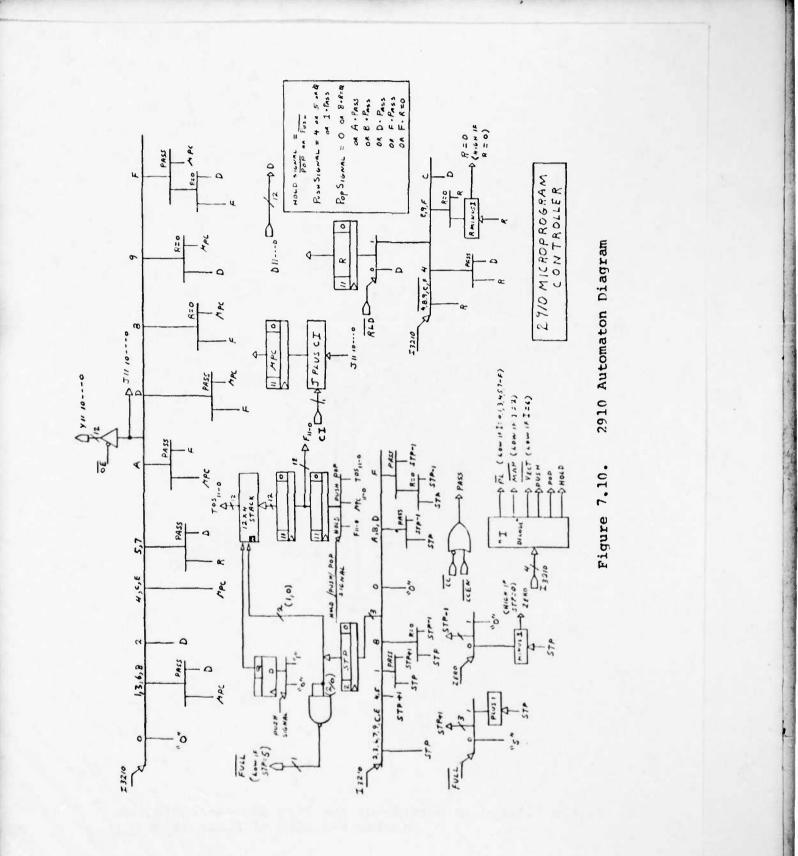

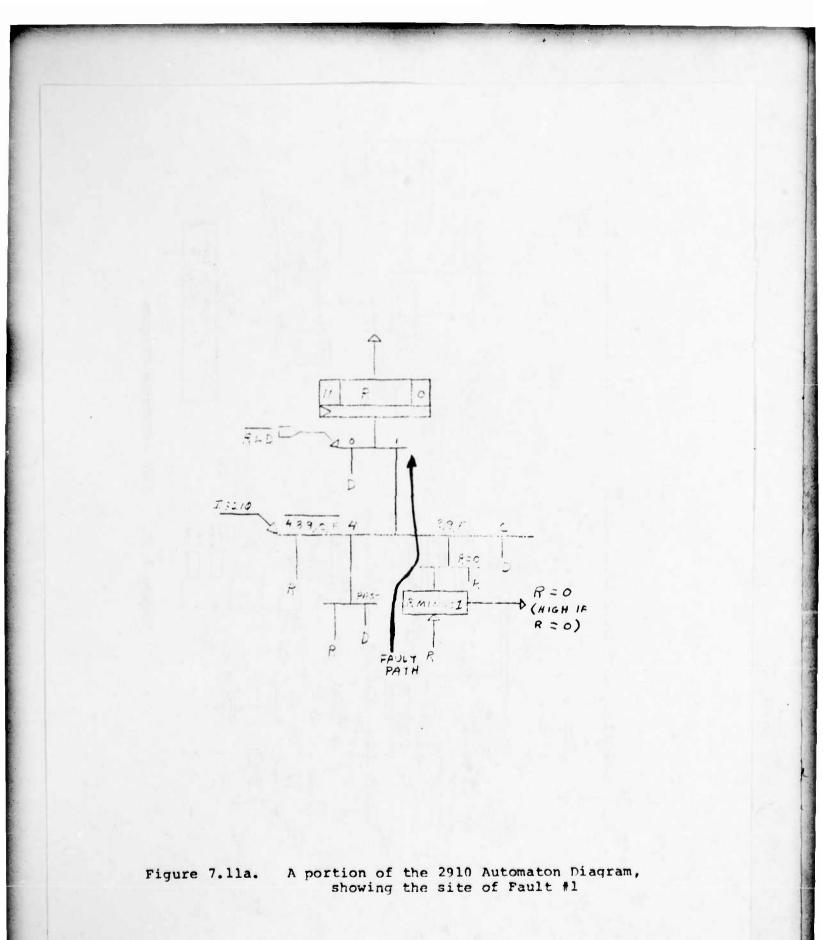

| 7.6     | 2910                                     | 143      |

| 7.6.1   | Learning the 2910                        | 148      |

| 7.6.2   | Testing the 2910                         | 148      |

| 7.6.3   | Test Implementation for the 2910         | 148      |

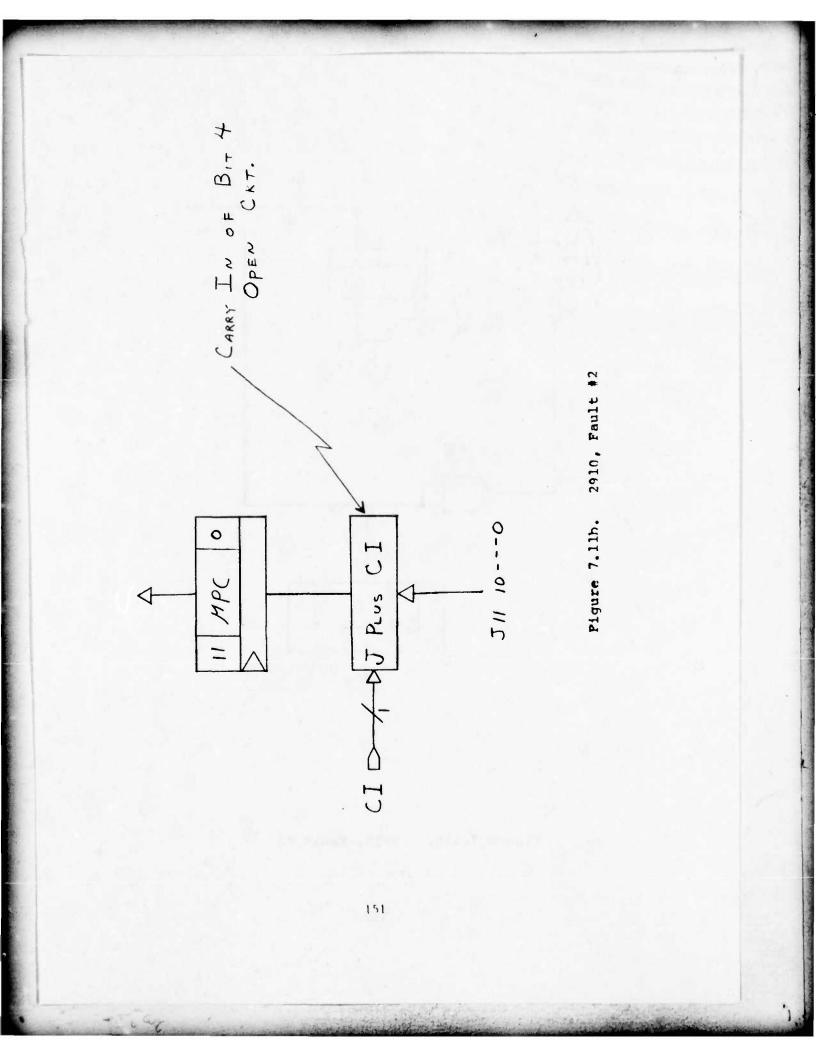

| 7.6.4   | Tracing and Inserting Faults in the 2910 | 148      |

|         |                                          |          |

| 8.      | Status                                   | 157      |

| 8.1     | Status of Slash Sheets                   | 157      |

| 8.2     | Status of Fault Isolation                | 157      |

| 8.3     | Status of Software                       | 157      |

| 8.3.1   | Multics Utilities                        | 158      |

| 8.3.2   | S-3260/3270 Utilities                    | 159      |

| 8.4     | Recommendations                          | 159      |

| 8.4.1   | Slash Sheet Format                       | 160      |

| 8.4.2   | Device Modeling                          | 160      |

| 8.4.3   | Specialized ATE Capabilities             | 160      |

| 8.4.4   | Desired CAT Tools/Techniques             | 160      |

|         |                                          |          |

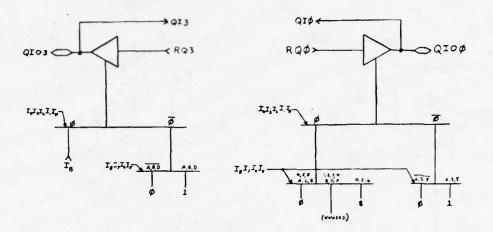

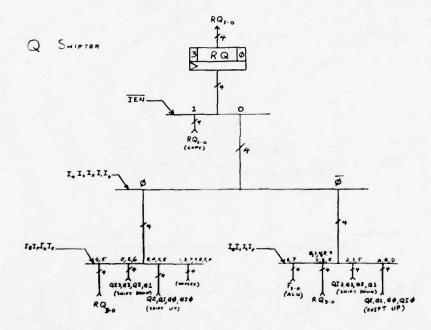

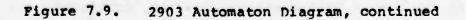

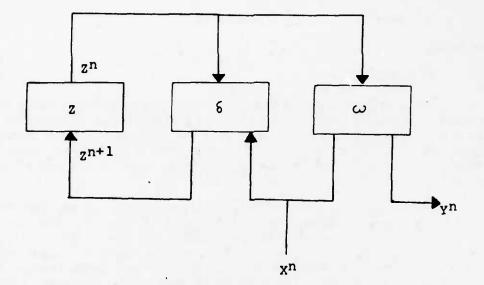

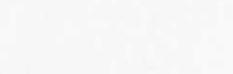

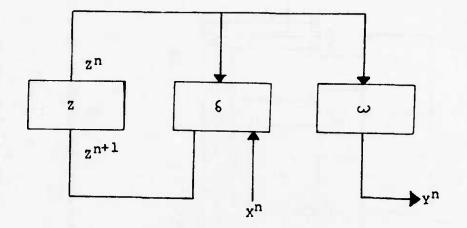

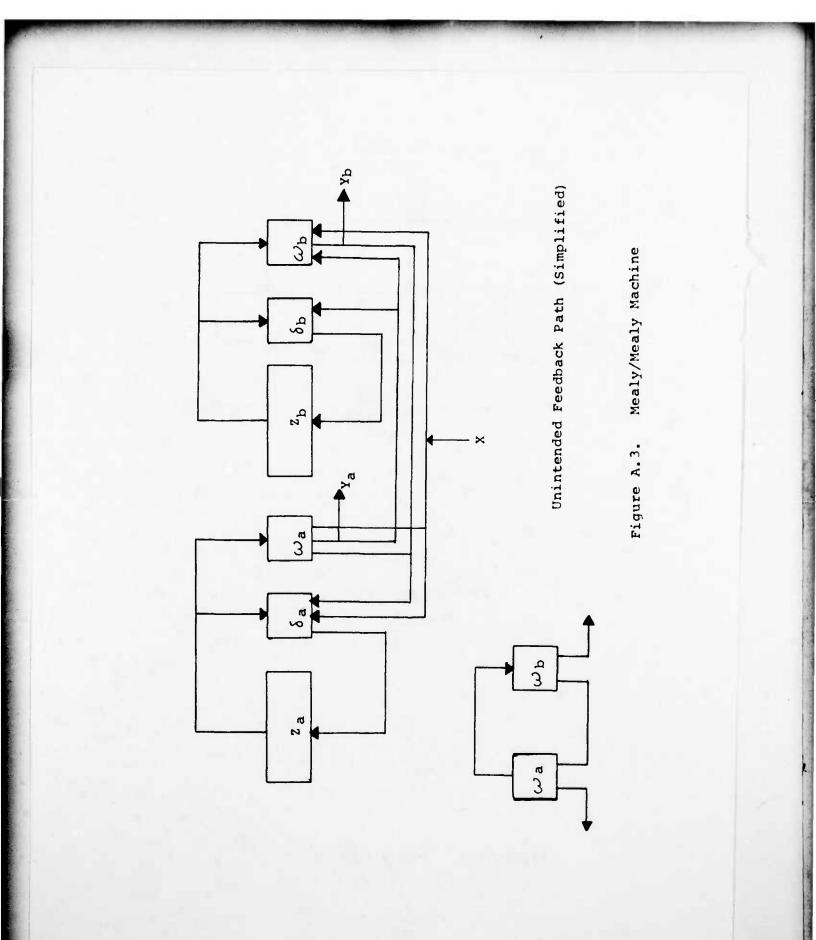

Appendix A. Automaton Diagrams

162

\*

# TERMS AND ABBREVIATIONS

| .ASC              | -     | ASCII-type file, used on the S-3260/3270                                                                                                                                                                             |

|-------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .EDT              |       | S-3260/3270 source program                                                                                                                                                                                           |

| .PAT              | -     | S-3260/3270 pattern file                                                                                                                                                                                             |

| .PIN              | -     | S-3260/3270 file for defining the configuration of the test fixture                                                                                                                                                  |

| .TST              | -     | S-3260/3270 compiled program                                                                                                                                                                                         |

| ALICE             | ī     | Automatic LASAR Input Coding Editor, the generic name for several Computer-Aided Testing utilities                                                                                                                   |

| ATE               | -     | Automatic Test Equipment                                                                                                                                                                                             |

| CAT               | -     | Computer-Aided Test                                                                                                                                                                                                  |

| CRT               | -     | Cathode Ray Tube (television screen)                                                                                                                                                                                 |