Ø

AFIT/GCE/ENG/87D-5

DESIGN AND IMPLEMENTATION OF A VLSI PRIME FACTOR ALGORITHM PROCESSOR *THESIS* Robert S. Hauser Second Lieutenant, USAF AFIT/GCE/ENG/87D-5

Approved for public release; distribution unlimited

ì٠)

# DESIGN AND IMPLEMENTATION OF A VLSI PRIME FACTOR ALGORITHM PROCESSOR

### THESIS

Presented to the Faculty of the School of Engineering

of the Air Force Institute of Technology

Air University

In Partial Fulfillment of the

Requirements for the Degree of

Master of Science in Computer Engineering

Robert S. Hauser, B.S.

Second Lieutenant, USAF

December 1987

Approved for public release; distribution unlimited.

### Acknowledgements

I would like to thank my thesis advisor, Captain Richard W. Linderman, for his continued support and dedication. Without his help, this thesis would not have been possible. I would also like to thank Major Joe DeGroat and Captain Nathaniel Davis for reading this thesis and providing their input.

Special thanks to Juanita M. Blackford for her endless work in keeping the computer systems up and functioning and preventing me from becoming a hermit. And a late night thank you to everybody that worked in the VLSI trailer.

Finally, thanks to Mom and Dad for continually providing constant support and encouragement, always.

## TABLE OF CONTENTS

| Acknowledgements | ii   |

|------------------|------|

| List of Figures  | viii |

| List of Tables   | x    |

| Abstract         | xi   |

### **Chapter 1: Introduction**

| 1.1 Background                              | 1  |

|---------------------------------------------|----|

| 1.2 Problem Statement                       | 3  |

| 1.3 Scope                                   | 3  |

| 1.4 Approach                                | 4  |

| 1.5 Summary of Current Knowledge            | 5  |

| 1.5.1 Digital Signal Processing.            | 5  |

| 1.5.2 Memory Techniques.                    | 6  |

| 1.5.3 Error Control Coding.                 | 8  |

| 1.6 Materials and Equipment                 | 8  |

| 1.7 Sequence of Presentation                | 9  |

| Chapter 2: Detailed Analysis of the Problem |    |

| 2.1 Overview                                | 11 |

| 2.2 Memory                                  | 11 |

2 Memory

11

2.2.1 Interfaces.

12

2.2.2 Data Flow.

12

2.2.3 Memory Cell.

13

2.2.4 Reading and Writing.

13

2.2.5 Address Selection.

13

iii

| 2.2.6 Error Control Coding.          | 14 |

|--------------------------------------|----|

| 2.3 PFA Controller                   | 14 |

| 2.3.1 Control State Sequencing.      | 14 |

| 2.3.2 Storing and Manipulating Data. | 15 |

| 2.3.3 Communication.                 | 16 |

### **Chapter 3: Architecture and Algorithms**

| 3.1 Overview                               | 18       |

|--------------------------------------------|----------|

| 3.2 Memory                                 | 18       |

| 3.2.1 Data Flow                            | 18       |

| 3.2.2 Storage.                             | 19       |

| 3.2.3 Error Control Coding.                | 19       |

| 3.2.3.1 Encoding                           | 20       |

| 3.2.3.2 Decoding                           | 22       |

| 3.3 PFA Controller<br>3.3.1 Host Algorithm | 24<br>25 |

| 3.3.2 PFA Controller Algorithm.            | 27       |

| 3.3.3 Microprogrammed Control Unit.        | 28       |

| 3.3.4 Processor Unit.                      | 31       |

| 3.3.5 Registers.                           | 31       |

| 3.3.6 Microcode Word Format.               | 34       |

| 3.3.7 Pipeline Fault Tolerance.            | 34       |

# Chapter 4: Computer Aided Design Environment Tools

| 4.1 Overview                                   | 38 |

|------------------------------------------------|----|

| 4.2 Design Methodology                         | 38 |

| 4.2.1 AFIT CAD Tools.                          | 39 |

| 4.2.2 Generic Microcode Assembler Tool (GMAT). | 41 |

2000

KUKUKU PREZER BEEREN PEREKU SUBBER PREFER PREFER KUKU USECOG PEREFER USECOG

| 4.2.3 GMAT Assembler.    | 42 |

|--------------------------|----|

| 4.2.3.1 Translation File | 44 |

| 4.2.4 PREG Operation.    | 46 |

### Chapter 5: VLSI Design

( •

· .

| 5.1 Design Techniques         | 48 |

|-------------------------------|----|

| 5.2 Memory Chip               | 50 |

| 5.2.1 Memory Cell.            | 50 |

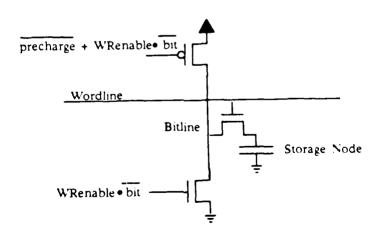

| 5.2.2 Bitline Control.        | 53 |

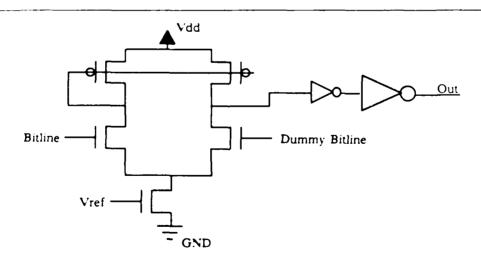

| 5.2.3 Sense Amplifiers.       | 54 |

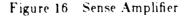

| 5.2.4 Word Selection          | 55 |

| 5.2.5 One-Shot.               | 56 |

| 5.2.6 ECC.                    | 56 |

| 5.2.6.1 Encoding.             | 56 |

| 5.2.6.2 Decoding.             | 57 |

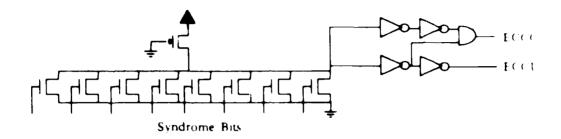

| 5.2.6.3 ECCC and ECCU.        | 59 |

| 5.2.7 Switching Circuitry.    | 60 |

| 5.3 PFA Chip                  | 62 |

| 5.3.1 Control Side            | 62 |

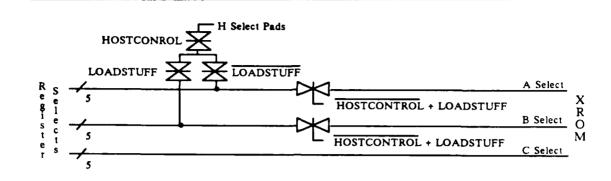

| 5.3.2 XROM                    | 63 |

| 5.3.2.1 XROM Memory Cell.     | 63 |

| 5.3.3 XROM Sense Amplifier    | 64 |

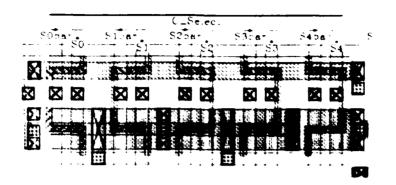

| 5.3.4 XROM Pipeline Register. | 65 |

| 5.3.5 Control Sequencer.      | 66 |

| 5.3.5.1 Address Selection     | 66 |

| 5.3.5.2 Condition Select.     | 66 |

| 5.3.5.3 Incrementer           | 67 |

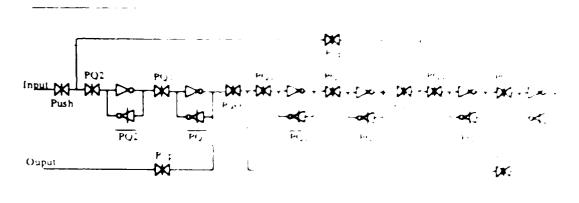

| 5.3.6 Subroutine Stack        | 68 |

| 5.3.6.1 Branch Selection      | 69 |

| 5.3.7 Data Side.              | 70 |

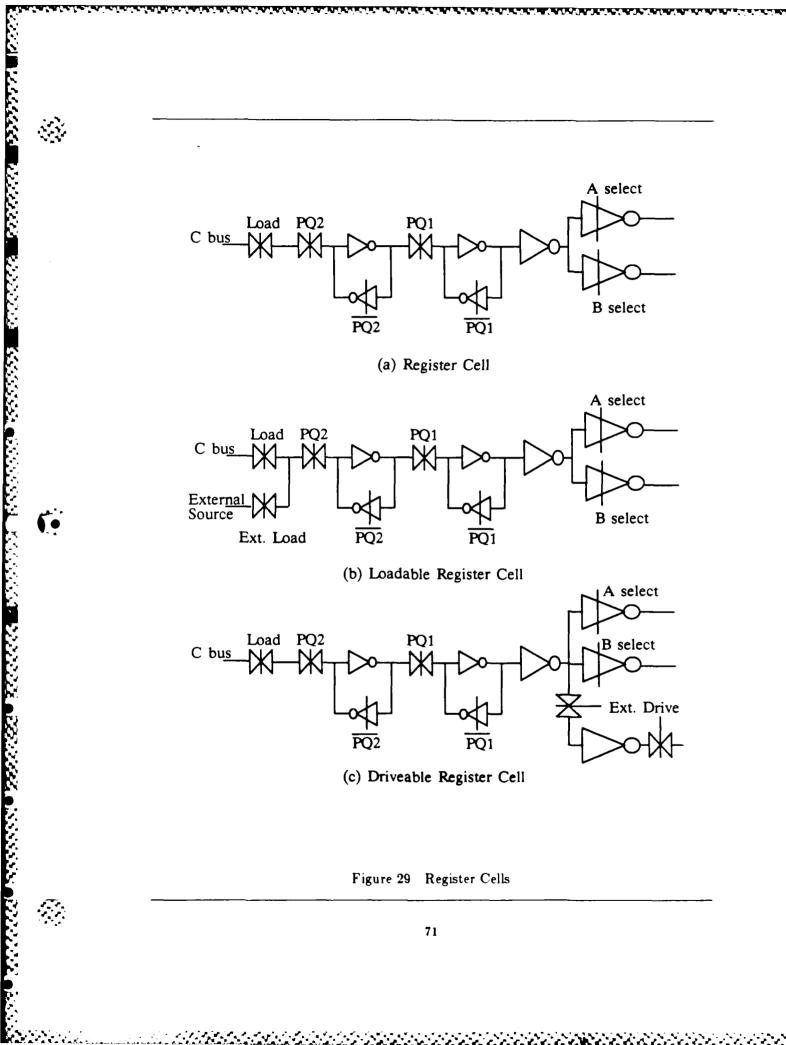

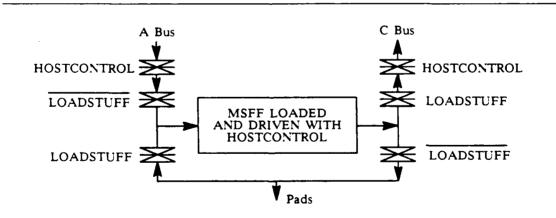

| 5.3.7.1 Register Cells        | 70 |

| 5.3.7.2 Registers.            | 72 |

. . . . . . . . . .

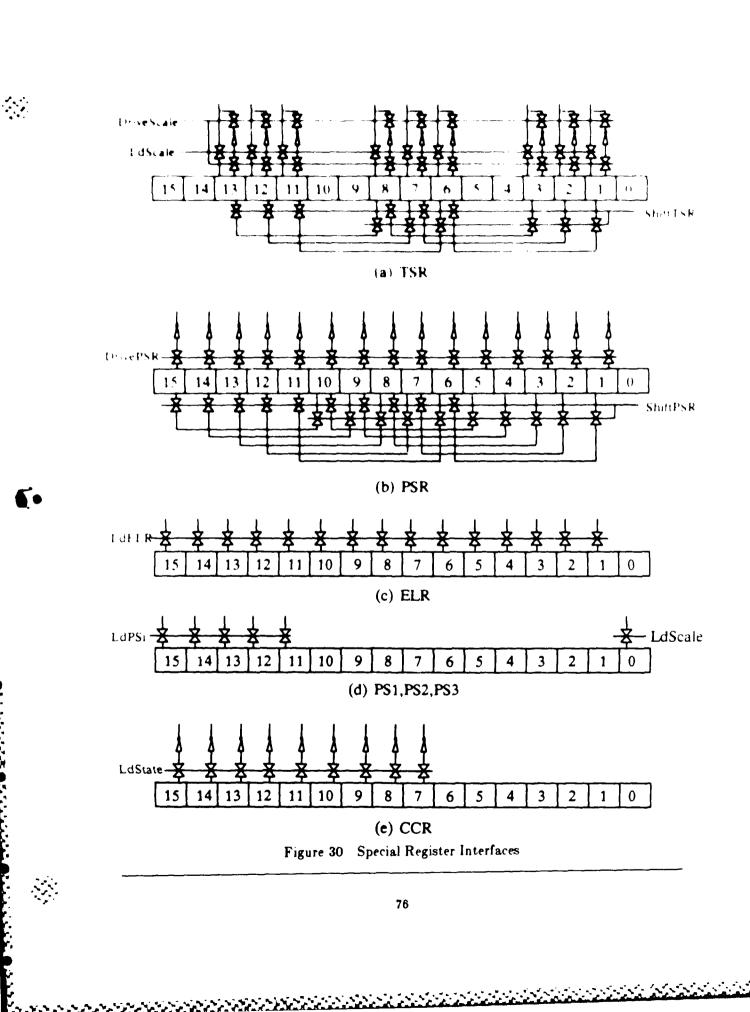

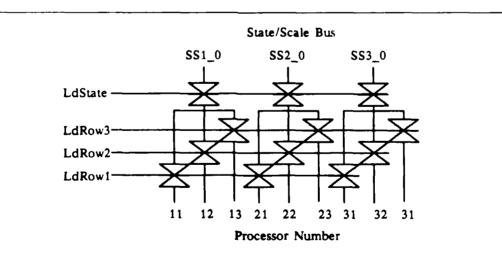

| 5.3.7.3 Special Register Interfaces. | 75  |

|--------------------------------------|-----|

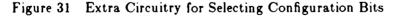

| 5.3.7.4 Register Selection.          | 77  |

| 5.3.8 Data Path Insertion.           | 79  |

| 5.3.9 Arithmetic/Logic Unit          | 80  |

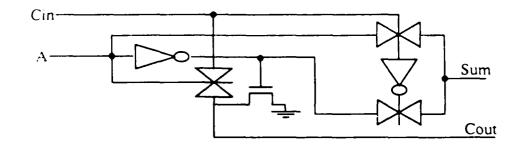

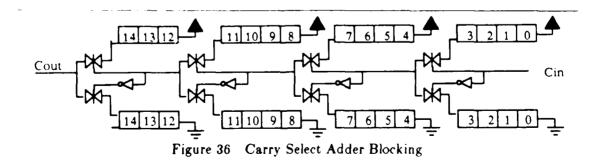

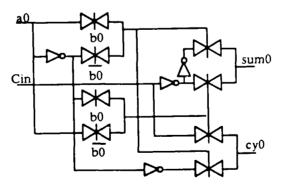

| 5.3.9.1 Integer Adder                | 80  |

| 5.3.9.2 Functions                    | 82  |

| 5.3.10 Host Control Interface.       | 83  |

| 5.3.11 Periphery                     | 85  |

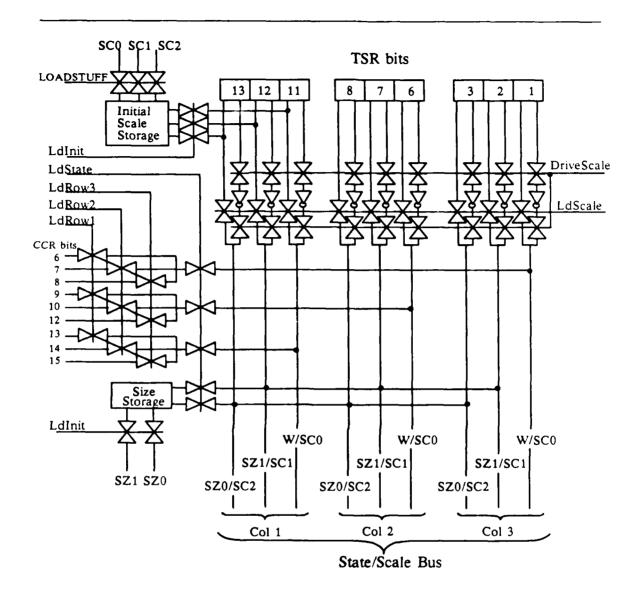

| 5.3.11.1 State/Scale Bus             | 85  |

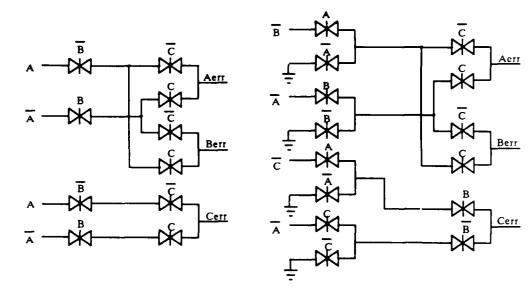

| 5.3.11.2 Voting Circuitry.           | 87  |

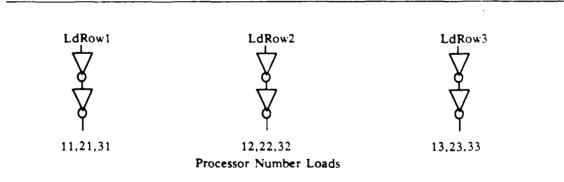

| 5.3.11.3 WFT Processor Loads.        | 88  |

| 5.3.11.4 Scale Factors               | 89  |

| 5.3.11.5 Size                        | 90  |

| 5.3.11.6 Done?                       | 91  |

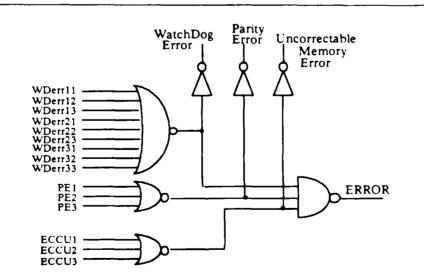

| 5.3.11.7 Error?.                     | 91  |

| 5.3.11.8 Toggle F/F.                 | 93  |

| 5.3.11.9 Column Done Storing         | 93  |

| 5.3.12 Microcode Development.        | 94  |

| 5.3.13 PFA Controller Summary.       | 100 |

# Chapter 6: Results

| 6.1 Results                             | 102 |

|-----------------------------------------|-----|

| 6.1.1 Memory Chips.                     | 102 |

| 6.1.2 PFA Chip.                         |     |

| 6.1.3 Generic Microcode Assembler Tool. | 105 |

## **Chapter 7: Conclusions and Recommendations**

| 7.1 Conclusions     | <br>107 |

|---------------------|---------|

| 7.2 Recommendations | <br>108 |

# Bibliography

### Vita

Appendix A: Error Correcting Code Matricies

Appendix B: GMAT Shell Script

Appendix C: PREG C Code

Appendix D: Code Created by PREG

Appendix E: Assembler Skeleton

Appendix F: Microcode Translation File

Appendix G: Microcode Word Format

# List of Figures

$\langle N \rangle$

| Figure 1: 4080-Point Processor                              | 4  |

|-------------------------------------------------------------|----|

| Figure 2: Memory Chip Partioning                            | 19 |

| Figure 3: Host Microcode Flow Chart                         | 26 |

| Figure 4: Controller Microcode Flow Chart                   | 27 |

| Figure 5: WFT Interface Microcode Flow Chart                | 29 |

| Figure 6: Microprogrammed Control Unit                      | 30 |

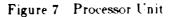

| Figure 7: Processor Unit                                    | 32 |

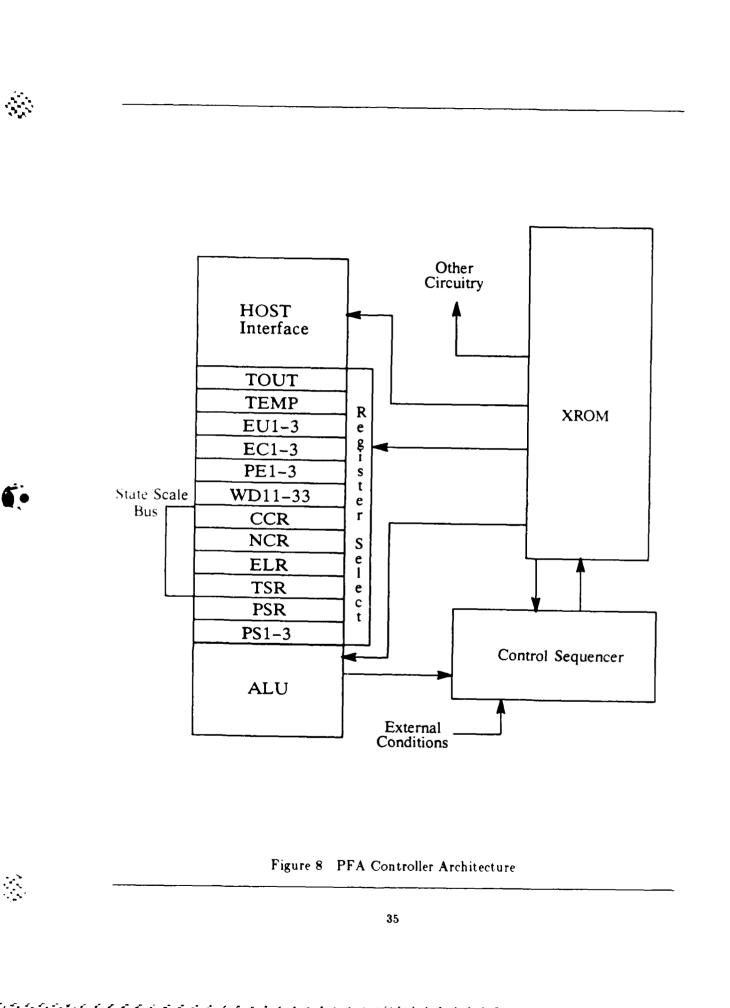

| Figure 8: PFA Controller Architecture                       | 35 |

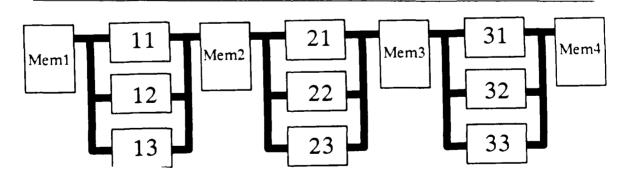

| Figure 9: Processor Names                                   | 37 |

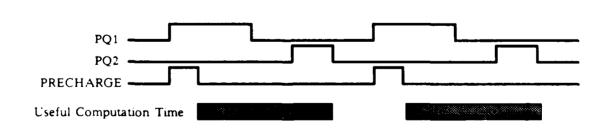

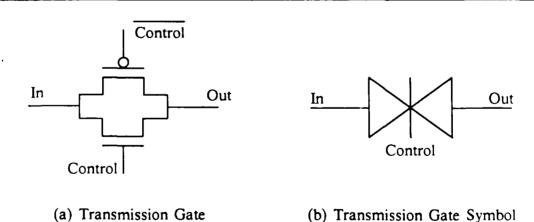

| Figure 10: 2-Phase Clocking Timing Diagram                  | 48 |

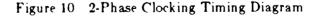

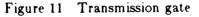

| Figure 11: Transmission gate                                | 49 |

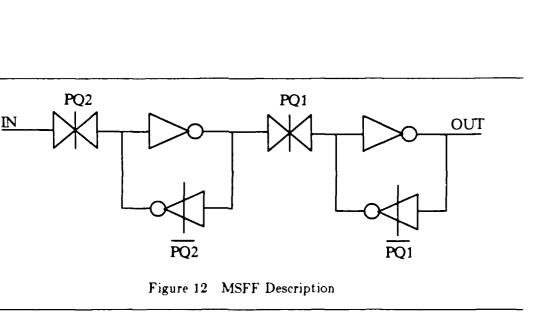

| Figure 12: MSFF Description                                 | 50 |

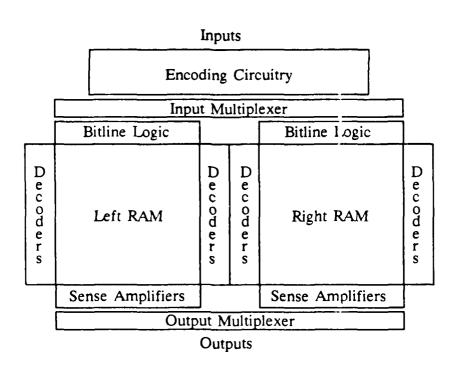

| Figure 13: Memory Chip Architecture                         | 51 |

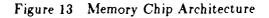

| Figure 14: One-Transistor Memory Cell Logic and Cifplot     | 52 |

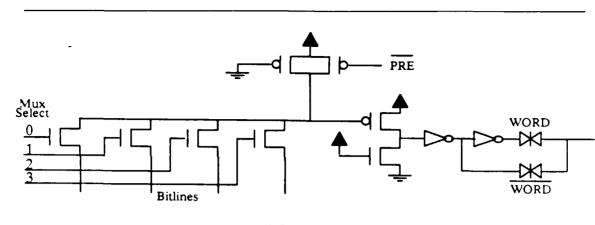

| Figure 15: Bitline Control Circuitry                        | 53 |

| Figure 16: Sense Amplifier                                  | 54 |

| Figure 17: Wordline Selection Decoder                       | 55 |

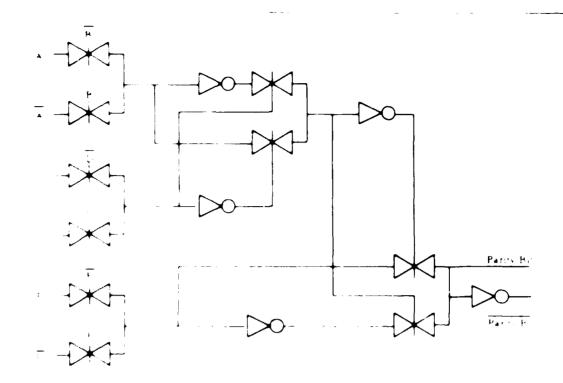

| Figure 18: Parity Bit Generator                             | 57 |

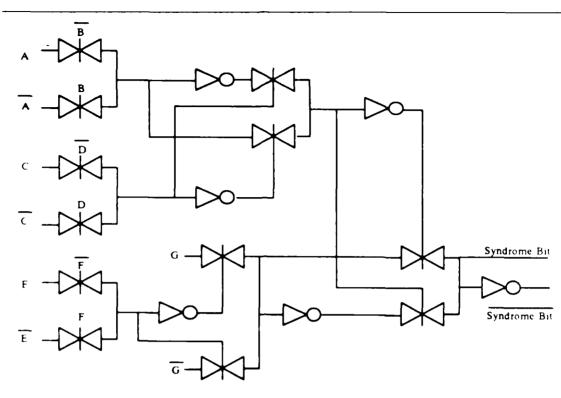

| Figure 19: Syndrome Bit Generator                           | 58 |

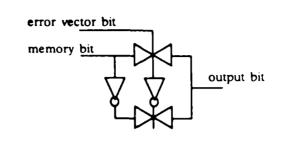

| Figure 20: Out Bit Generator                                | 59 |

| Figure 21: ECCC/ECCU Circuitry                              | 60 |

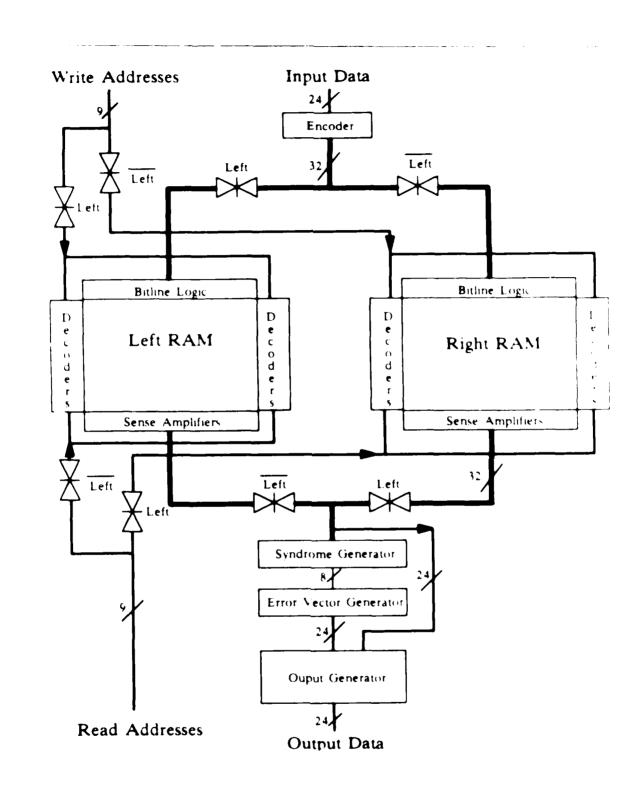

| Figure 22: Memory Chip Data Flow                            | 61 |

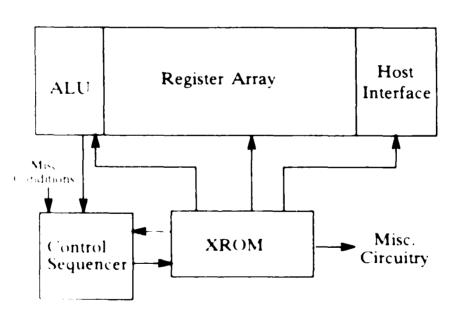

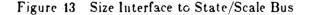

| Figure 23: PFA Major Components                             | 62 |

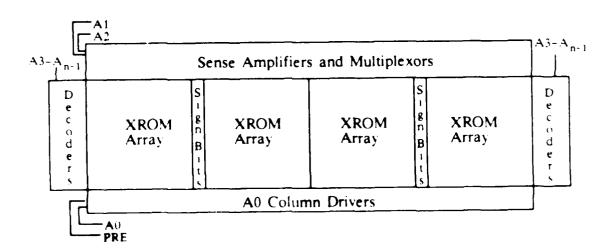

| Figure 24: AFIT XROM Structure                              | 63 |

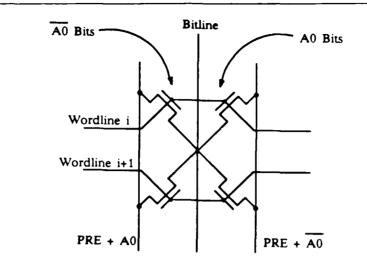

| Figure 25: XROM Memory Cell                                 | 64 |

| Figure 26: XROM Sense Amplifier                             | 65 |

| Figure 27: Incrementer Half-Adder                           | 68 |

| Figure 28: Subroutine Stack                                 | 69 |

| Figure 29: Register Cells                                   | 71 |

| Figure 30: Special Register Interfaces                      | 76 |

| Figure 31: Extra Circuitry for Selecting Configuration Bits | 77 |

| Figure 32: Gate-Level Description of a Register Select      | 78 |

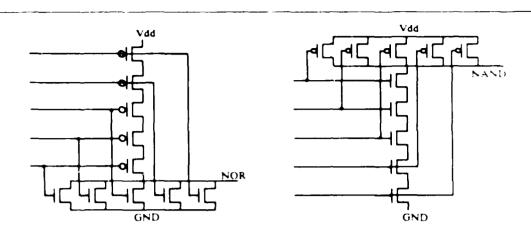

| Figure 33: NAND and NOR VLSI Gates                          | 79 |

| Figure 34: Register Select Cell with 00111 Personalization  | 80 |

| Figure 35: ALU Logic Implementation                         | 81 |

|                                                             |    |

# List of Figures (continued)

(م ا

| Figure 36: Carry Select Adder Blocking                          | 81         |

|-----------------------------------------------------------------|------------|

| Figure 37: ALU Adder Cell                                       | 82         |

| Figure 38: Source Determination for Register Selection          | 84         |

| Figure 39: Source and Destination Determination for Data Busses | 84         |

| Figure 40: Data Flow for State/Scale Bus                        | 86         |

| Figure 41: Voting Implementation                                | 88         |

| Figure 42: WFT Processor Load Determination                     | 89         |

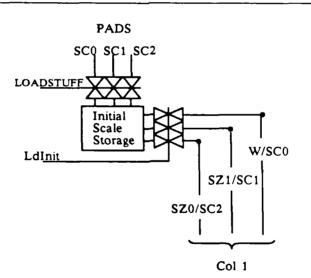

| Figure 43: Size Interface to State/Scale Bus                    | <b>9</b> 0 |

| Figure 44: Gate-Level Description of ERROR? Cell                | 91         |

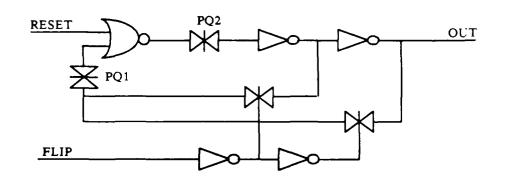

| Figure 45: Toggle Flip-Flop Gate-Level Representation           | 93         |

| Figure 46: PFA Controller Floorplan                             | 101        |

| Figure 47: Prototype Memory Photomicrograph                     | 103        |

| Figure 48: Memory Cifplot                                       | 104        |

| Figure 49: PFA Controller Cifplot                               | 106        |

1.1.1.1.1

# List of Tables

<u>.</u>

<u>\_\_\_\_</u>

| Table 1: Voting Strategy                           | 36 |

|----------------------------------------------------|----|

| Table 2: Bitline Control Logic                     | 54 |

| Table 3: One-Shot Truth Table                      | 56 |

| Table 4: ECCC and ECCU Determination               | 59 |

| Table 5: Condition Selects                         | 67 |

| Table 6: Next Address Field (NAF) Selection        | 69 |

| Table 7: Bit to Processor Translation              | 73 |

| Table 8: ELR Translation                           | 73 |

| Table 9: TSR and PSR Translation                   | 74 |

| Table 10: PSi Translation                          | 74 |

| Table 11: Special Register Requirements            | 75 |

| Table 12: ALU Control and Functions                | 82 |

| Table 13: Register Selection and Bus Determination | 85 |

| Table 14: PFA-WFT Interface Translation            | 87 |

| Table 15:         WFT DFT Size Determination       | 90 |

| Table 16: Microword Format                         | 94 |

| Table 17: BR_SEL Field                             | 95 |

| Table 18: ALU Field                                | 95 |

| Table 19: Bus Fields                               | 95 |

| Table 20 Register Select Translation               | 96 |

| Table 21: SPEC_FUNCT Field                         | 96 |

x

#### AFIT/GCE/ENG/87D-5

#### Abstract

High-speed digital signal processing has a wide range of applications including. radar, sonar, image processing, and target acquisition. The calculation of the Discrete Fourier Transform (DFT) used in these applications has long been a significant bottleneck for high-speed processing. Previous AFIT students have adopted a Prime Factor Algorithm (PFA) method using Winograd Fourier Transform (WFT) processors. Three WFT processors are pipelined into a system capable of computing a 4080-point DFT on complex data approximately every 120 microseconds when operating with a 70 MHz clock.

This thesis effort addressed the design and implementation of PFA controller chip and interconnecting memory modules between the WFT processors. The PFA controller is an application specific processor to control the flow of information in the pipeline, interface to the WFT processors, monitor pipeline status, and take corrective action in the presence of faults. The interconnecting memory modules buffer the data coming out of a WFT processor and going into another allowing concurrent reading and writing.

The PFA controller chip was designed, simulated, and submitted for fabrication through MOSIS. Twenty-eight 16-bit registers store the pipeline information. An arithmetic/logic unit (ALU) computes data transformations. A read only memory stores the microcode. A control sequencer sequences through the proper code segments. Finally, special circuitry interprets the fault information and reconfigures the pipeline. This thesis effort included writing a microcode assembler to to raise the user interface to the AFIT-XROM silicon compiler. Raising the user's level of abstraction to mnemonic microcode, while still providing an error free path to silicon layout, reduces chances for error in the microcode specification. A generic microcode assembler tool was created as an extension for use with other application specific processors. This tools generates a microcode assembler from a word for:..at and a translation file. The assembler will output a file compatible with the XROM compiler, a VHDL description of the XROM, a listing file, a reference file, and a reverse assembly. This tool was tested on two other AFIT theses and a computer architecture class

A prototype memory chip was designed and fabricated in 3 micron CMOS through MOSIS to test the 1-transistor memory cell, the wordline selectors, and the sense amplifiers. Simulations predict an access time of 10ns. A larger memory was designed, simulated, and submitted for fabrication through MOSIS. It contains storage for 272 words of 32 bits each. It is dual ported and permits concurrent reading and writing of 24 bit data. The memory also includes error control circuitry for single error correction and double error detection.

#### CHAPTER 1

### Introduction

#### 1.1. Background

The military has a demonstrated interest in high-speed digital signal processing (DSP). Digital signal processing is used in a wide range of applications including radar, sonar, image processing, voice processing, artificial intelligence, and target acquisition. Applications such as these require data from sample points to be processed as near to real-time as possible with a reasonable amount of resolution. A reasonable amount of resolution is determined by the importance of the application and how accurate the results must be. Since resolution increases with the number of points sampled, it is logical to increase the number of sample points. Unfortunately, as the number of sample points increases, the number of operations increases as the square of the number of sample points (i.e.,  $O(N^2)$ ).

Many current DSP applications involve computation of the Discrete Fourier Transform (DFT) which uses only a finite set of sampled signal values instead of the original analog signal. Using a finite set of points allows the signal to be processed and stored on a digital computer. The DFT, in summation form, is as follows:

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{kn} \qquad k = 0, 1, ..., N-1$$

(1.1)

where W sub N = e sup {-j(2 pi /N)}. Since the number of computations grows as  $O(N^2)$  when computed as a sequence of inner products, the DFT is not usually computed directly. Instead, a class of algorithms developed in 1965 by Cooley and Tukey [Coo65] is often used which capitalize on the symmetry in the DFT to reduce to complexity of computation. This class of algorithms, known as Fast Fourier Transforms (FFTs), reduces the number of operations from being proportional to the square of the number of sample points, as in the DFT, to the number of sample point times the log of the number of sample points (i.e.,  $O(\frac{N}{2}\log_2 N)$ ). The introduction of the FFT made many DSP applications possible on digital computers.

1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 199 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 199 Prior to the introduction of very large scale integration (VLSI), most DSP computations were performed on-line by general purpose computers, requiring large amounts of time, or off-line by special purpose banks of circuit boards using medium scale, or small scale integration (MSI or LSI respectively). Because the constraints of throughput and blocklengths were so high, real-time computation was not possible. The increased speed and density now available in VLSI, will allow certain DSP functions to be implemented on a single chip.

One way to further increase the speed of the DFT is to reduce the number of multiplications since these are the most consuming. In 1978, Winograd showed a way to reduce the number of multiplications of a DFT while keeping the number of additions approximately equal. He also proved that his class of algorithms, known as Winograd Fourier Transform Algorithms (WFTs), contain the minimum number of multiplication required for computation of a DFT [Win78]. Winograd's large algorithms, however, do not easily map into VLSI because of their size. But, when the small algorithms are combined with the Good-Thomas Prime Factor Algorithm (PFA), they easily map into VLSI due to their small size and regularity [Lin84].

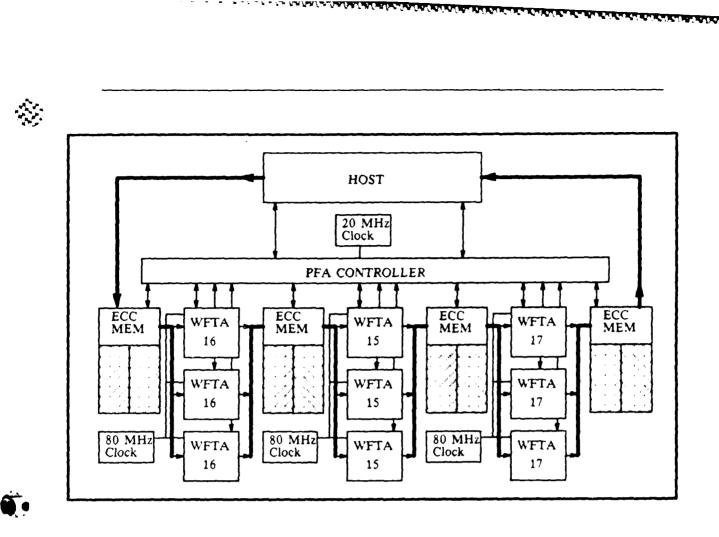

In 1985, a 4080-point transform was chosen as a representative system by the AFIT VLSI Design Group. The system consists of three WFTs of lengths 16, 15, and 17 pipelined together with interconnecting memory modules and a PFA controller. The block diagram of the system is shown in Figure 1. The goal of the WFT-PFA project is to produce a real-time signal processing system. With the PFA operating at 20MHz and each of the WFTs operating at 80MHz, one 4080-point transform will be computed every 120 seconds.

#### 1.2. Problem Statement

The first problem of this thesis effort will be to design the memory modules and implement one in 3-micron CMOS. The second problem will be to design the Prime Factor Algorithm controller chip and implement it in 3-micron CMOS.

#### 1.3. Scope

This thesis will include the design and implementation of the interconnecting memory modules and the PFA controller. First, the memory module will be architecturally specified, layed out in VLSI, and sent for fabrication; second, the PFA controller will be architecturally specified, laid out in VLSI, and sent for fabrication; third, both chips will be tested to ensure proper operation and validation.

Figure 1 4080-Point Processor

#### 1.4. Approach

This thesis will include the design and implementation of the interconnecting memory modules and the PFA controller. First, the problem requirements and their impact on the design will be analyzed. Second, the architectural descriptions for both chip will be developed. Third, the architectural description will be translated into gatelevel descriptions and from gate-level descriptions into VLSI. Fourth, the completed designs will be simulated to verify the design Fifth, the simulated designs will be sent for fabrication through MOSIS. 1.5. Summary of Current Knowledge

1.5.1. Digital Signal Processing. The current state of fast signal processing algorithms was forged in 1965 by Cooley and Tukey [Coo65]. They demonstrated a method for computing n-point discrete Fourier transforms that required on the order of O(NlogN) computations instead of  $O(N^2)$ . Their algorithm took advantage of the symmetry and periodicity inherent within DFTs to reduce the number of operations. This method, known as the Fast Fourier Transform or FFT, brought signal processing to digital computer computation.

Another important contribution to the field was Winograd's work published in 1978 [Win78]. Winograd presented algorithms that significantly reduced the number of multiplications required while keeping the number of additions approximately equal. Winograd also showed that his method required a minimal number of multiplications. Because multiplications were much more computationally intensive than additions, his method significantly reduced the computation time.

For a VLSI implementation, however, Winograd's algorithm lacked the modularity needed for effective VLSI design and the number of additions grew quickly as the transform size increased [Lin84]. One solution to this problem was given by Burrus who combined the Good-Thomas Algorithm (PFA) [Goo71] with small Winograd transforms [Bur83]. This combination took one-dimensional transforms and broke them into smaller multi-dimensional transforms. Finally, Linderman [Lin84] presented a way to embed the PFA into VLSI using Winograd Fourier Transform Algorithm (WFT) processors. His solution consisted of decomposing a 4080-point transform into three Winograd processors of lengths 15, 16, and 17. In 1985, four theses were dedicated to the implementation of Linderman's solution. Taylor presented the PFA and WFT theory, the overall signal processing architecture, and the numerical precision results [Tay85]. He showed that architecture would indeed compute a DFT and remain within acceptable numerical accuracy. Coutee described the arithmetic circuitry for the WFT 16-point transform processor [Cou85]. Rossbach presented the control circuitry for the WFT 16-point [Ros85]. He was able to demonstrate that the control sequencer operated correctly at speeds in excess of 60 MHz in 3-CMOS. Finally, Collins presented a description and validation of the WFT 16-point in the VHSIC (Very High Speed Integrated Circuit) Hardware Description Language, VHDL [Col85].

In 1986, two theses were involved in the PFA-WFT project [She86]. Shephard completed the VLSI design and implementation of the WFT16 chip and Hedrick discussed the memory modules and the PFA controller. Hedrick established the foundations of the PFA-ASP by describing the major functional blocks and their interfaces.

1.5.2. Memory Techniques. Weste and Eshragian classified memories into three types, random access, serial access, and content addressable [Wes85]. Random access memory, at the chip level, was described as having an access time independent of location. This contrasts with serial access and content addressable access where the time needed to read or write a value was variable depending on location. Random access memories (RAMs) may be further classified into read only (ROM) or read and write (usually referred to as RAM). ROMs are generally denser than RAMs but they are not as flexible due to the permanency of the data.

RAMs and ROMs can be further be divided according to whether they are static or dynamic. In a static memory, the value of the data is stored with some type of latch, whereas in a dynamic memory, the value is stored with some type of charge on a capacitor. Because the dynamic memory is stored on a capacitor, its charge will degrade and must be refreshed within a certain time interval. The advantage of dynamic memories is that they are much smaller than their static counterparts and use less power [Muk86]. Dynamic memories are smaller because there is no feedback circuitry within the memory cell to keep the location refreshed. The disadvantages are that they are hard to design, somewhat slower than static memories, and more suspectable to soft errors (errors caused by transient radiation).

Several authors described a dynamic memory consisting of a single transistor [Gla85, Muk86, Wes85]. In this type of memory cell, the charge was stored on a capacitor and a single transistor acted as a gate between the bit line and the capacitor. The value was written and read via the bit line. Various techniques for making the capacitor have been implemented including a double polysilicon method and a trench method [Rid79]. These methods tried to increase the amount of capacitance in the memory cell by exploiting non-standard techniques.

The most difficult part of a one-transistor memory cell is the sense amplifier. When a cell is read, the resultant value on the bit line is determined by charge sharing between the bit line and the storage capacitor. Because the storage capacitor is so small compared to the bit line, when the cell is read, there is little voltage change in the bit line. To detect this small change, a very sensitive amplifier is needed. A sense amplifier will amplify the change to levels that correspond to digital logic values.

In 1985, Shinn designed a double stage differential amplifier with current mirror active loading [Shi85]. He detected a differential of 0.01 volts when reading the value and its complement. Grebene fully described the transfer characteristics and gain of such an amplifier in 1984 [Gre84]. He found that the gain was directly proportional to the current loading and the width to length ratio of the gate on the nMOS devices to which the voltages to be sensed were connected.

1.5.3. Error Control Coding. In the transmission or storage of data, noise or other factors may cause erroneous results. In 1949, Shannon demonstrated that a proper encoding of the information could reduce the number of errors induced by a channel [Sha49]. Peterson and Weldon pointed out that as early as 1956, systems were being built that demonstrated error correction and detection [Pet72].

A typical storage system with error correction and detection consists of encoding the data before storage or transmission, the storing or transmission media, and decoding to output the data [Hed86]. With this kind of system, two different types of codes are popular, convolution codes and block codes. In a convolution code, the encoded data is based on the current data as well as previous data, thus requiring a storage media associated the encoder. In a block code, the encoded data only depends on the current information [Hed86].

Since digital computers deal with information coded in binary digits, the discussion of block codes can be limited to those with two symbols [Lin83]. Lin and Costello developed algorithms for block codes of this type using syndromes and standard arrays. Their algorithms will accomplish single error correction and double error detection.

#### 1.6. Materials and Equipment

The materials and equipment needed for this thesis are available at AFIT. All the computer aided design (CAD) tools require a UNIX environment. The tools from the AFIT/VLSI CAD system will include CSTAT, a tool that determines whether nodes can be set to logic 1, set to logic 0, affect the outputs, or can be affected by the inputs, STOVE, a circuit extraction tool, NOFEED, a tool which removes feedback paths for simulation, and FIXROM, a tool that alters the XROM for simulation. The other CAD tools are from the University of California at Berkeley. These tools are distributed each year to various academic institutions. The tools necessary for this thesis include MAGIC, a VLSI layout tool, MEXTRA, a circuit extraction tool, ESIM, a switch level simulator, CRYSTAL, a performance analyzer for VLSI circuits, SPICE, a timing analysis tool, and CIFPLOT, a tool to plot VLSI circuits. MAGIC requires either a SUN Workstation or an AED 767 graphics terminal, both of which are currently available.

This thesis will also require the use of the VHDL language. This language is supported on AFIT's Classroom Support Computer (CSC) operating under the VAX/VMS operating system.

A high-speed VLSI chip tester will also be needed. The tester is located in building 125 Area B.

#### 1.7. Sequence of Presentation

Chapter 2 gives a detailed analysis of the requirements needed for the two problems of this thesis. First the memory is discussed and then the PFA controller.

Chapter 3 presents the architectural descriptions for the memory chip and the PFA controller chip. It also discusses the algorithms involved in the error control coding for the memory and the algorithms involved in the operation of the PFA controller.

Chapter 4 discusses the AFIT CAD environment and the VLSI design methodology. This Chapter also discusses development and operation of the Generic Microcode Assembler Tool. Chapter 5 presents the VLSI description of the circuits used to implement the memory and the PFA controller. The development of the microcode is also presented.

Chapter 6 discusses the results of the thesis effort The features of the memory chip as well as the PFA controller will be discussed. This chapter will also discuss the results of the microcode assembler on this thesis effort and two other applications.

Chapter 7 discusses the conclusions from this work and presents recommendations for future work. The future work will focus on testing the parts of the pipeline and implementing the prototype.

### **CHAPTER 2**

#### Detailed Analysis of the Problem

#### 2.1. Overview

The scope of this thesis effort is to design the memory modules and the PFA controller chip. The memory modules are used as a buffer between the different stages of the WFT-PFA pipeline. They allow concurrent reading and writing so that the WFT processors may operate asynchronously with respect to each other and keep data flowing through the pipeline as it is needed and generated. The memory also encorporates single error correction and double error detection based on an (n, k) linear systematic block code to correct some simple errors and provide some error monitoring for the PFA controller.

The PFA controller operates and monitors the pipeline. It is responsible for the pipeline data flow, fault monitoring and reconfiguration, if necessary, and communication with the output host. The PFA controller is considered to be an application specific processor containing elements to store and manipulate data, sequence through a set of predetermined states, and communicate with outside activities.

#### 2.2. Memory

There are six major areas in the memory design. These are the interfaces, the data flow, the storage cell, reading and writing, address selection, and error control coding. The memory act as buffers for the data as it travels through the pipeline. Thus, there are predetermined interfaces which the memories must conform to as set by the previously designed WFT processors.

The first constraints imposed on the memory chip are 2.2.1. Interfaces. those of the external interfaces. The PFA controller interfaces with the memory via a LEFT(RIGHT) signal. This signal determines which side of the memory is written to and which side is read from. Additionally, the memory is required to send two signals to the PFA controller for error monitoring. The first signal is the Error Control Code Correctable (ECCC) and the second is the Error Control Code Uncorrectable (ECCU). The ECCC signal flags the PFA controller that a single error occurred and was corrected. The ECCU signal flags the PFA controller that a double error was detected and therefore the data could be flawed. These signals will be discussed more in Chapter 5. The WFT processors interface with several groups of signals, the address select lines, the input data lines, the output data lines, and *PRECHARGE*. There are 12 address select lines capable of addressing up to 4096 words. Each word is 24 bits long, giving 24 input data lines and 24 output data lines. The WFT processor on the left, or host in the case of the first memory, feeds the 12 write select addresses and the input data to the chip and the WFT processor on the right, or host in the case of the last memory, feeds the 12 read select addresses and receives the output data

2.2.2. Data Flow. The basic data flow through the chip is as follows; for the input data, the inputs come into the chip, pass through the ECC encoding and are written into the memory; for the output data, the values from the memory are passed through the ECC decoding and then sent off-chip to the WFT processor. To include concurrent reading and writing by two processors, two banks of the memory must exist so that while one bank is written the other bank is read. To accomplish this, the memory chip must be able to route data from the encoding circuitry to either side of the memory and from either side of the memory to the decoding circuitry. Additionally, the

PRECHARGE signal from the processors must also be routed to the side of the memory the respective processor is using.

2.2.3. Memory Cell. The memory cell holds the value of the input data for later retrieval. Ideally, the node should be able to store data for more than a millisecond. Two types of memory cells can be used, static or dynamic. In a static memory cell, loss of data due to leakage is not a problem. Static memories, however, are large compared to dynamic memories. Additionally, dynamic memories with no refresh are much more dense and less complicated that static memories. Data must be read within a certain time interval or it is lost without refreshing. One of the main results of this thesis will be to determine whether the memory cell will indeed hold the value within the time requirements.

2.2.4. Reading and Writing. The WFT processors operate at a clock frequency of 80MHz outputting a new word every other clock cycle. This means that a complete read or write must be accomplished at 40 MHz, or one operation every 25ns, for an input/output bandwidth of  $9.6 \times 10^8$  bits per second or total bandwidth of  $1.92 \times 10^9$  bits per second.

A complete write includes inputting, encoding, address selection, and value storage. A complete read includes address selection, value sensing, decoding, and outputting.

2.2.5. Address Selection. Each read or write must be able to access any one of the 4096 words in a non-linear fashion. The order of accesses is determined by the Prime Factor algorithms used to compute the Winograd Fourier Transform. Address selection is also included in the 25ns access time. Several different approaches to address selection will be discussed in Chapter 5. 2.2.8. Error Control Coding. As described in Chapter 1, the Error Control Coding is used to provide error correction and detection. The ECC included on the memory chip must be able to provide single error correction double error detection for the 24 bits of data. The ECC to implement this consists of four functional blocks. The first block is used to encode the data before it is written into the storage array. The input data and the parity bits are then written in to the memory. The second block is used to decode the output data into the syndrome bits. The third block takes the syndrome bits, computes the error vectors and generates the ECCC and ECCU signal discussed earlier. The fourth block takes the error vectors and the output data and generates the data output to the WFT processors.

#### 2.3. PFA Controller

As stated earlier, the PFA controller must be able to process instructions and take appropriate action on conditional data to accomplish its three major tasks. The first of these tasks is the ability to sequence through a set of predetermined control states, the second is the ability to store and manipulate data, and the third is the ability to communicate with off-chip activities. The requirements for each of these major tasks will be described below.

2.3.1. Control State Sequencing. To control the total state of the system. the controller must be able to sequence through a set of predetermined states. These states control the functioning of the pipeline, the storing and manipulation of the data. and the pipeline configuration. These states are expressed through the use of microinstructions. The microinstructions are stored in a read-only memory for execution The control sequencer determines which of the microinstructions will be executed next based on the current microinstruction. The source of the next microinstruction can either be an external address, the next sequential address, a field from the current instruction, or from the top of the stack. The sequencer determines the source from a set of input conditions and certain fields from the current microinstruction.

2.3.2. Storing and Manipulating Data. Subject to the control states, the PFA controller must be able to store and manipulate data. The controller must be able to store data which is passed from one stage of the pipeline to another after each DFT computation. It must also store information regarding pipeline configuration, catastrophic pipeline failure, memory faults, WFT processor faults, error location, and individual problem status.

The information that must pass from one stage of the pipeline to the other is the scale factor. The scale factor is a 3-bit number indicating the number of scale bit on the data words. A 3-bit scale factor is input along with the data to each WFT processor. After the WFT has completed the DFT it passes a new 3-bit scale factor. This scale factor is passed along to the next WFT processor in the pipeline. The total number of scale bits is accumulated in the PFA controller for each problem as it travels through the pipeline. Thus, the PFA controller must be able to store a 5 bit number for each problem at worst case (111 + 111 + 111 = 10101).

In addition to storing the data, the controller must also have the ability to manipulate it as well. Information from one source may need to be transferred to other sources or used in determining future controller states. This includes loading values from the pads, driving values to the pads, shifting a storage location, comparing two storage locations, and adding storage locations. For example, it will be necessary to increment the number of faults stored for a particular processor each time it fails. 2.3.3. Communication. The controller must be able to interface with the pipeline it operates and the host which submits DFTs for computation and receives the results. The following is a list of those signals which the PFA controller must be able to input or output:

Memory Chips:

1. *FLIP* (*from controller*) - Used to determine which side of the memory is read from or written to. One signal for all memory chips.

2. ECCC (to controller), Error Control Code Corrected - Used to indicate that a single error occurred in a read operation from the memory and it was corrected. Each memory has its own ECCC.

3. ECCU (to controller), Error Control Code Uncorrected - Used to indicate that an error occurred on a read that could not be corrected. Each memory has its own ECCU.

WFT processors:

1. WFTop (from controller), WFT Operate - Used to put the WFTs processors into computation mode. All WFT processors share one WFTop signal.

2. WD (from controller) - Used to put the WFTs in the operational or watchdog mode. Each pipeline stage has its own WD signal. (The signals described here in 2, 3, and 4 share the state/scale bus. This will be explained in Chapter 5)

3. SZ0 and SZ1 (from controller), SizeO and Size1 - Used to send the DFT size to the WFTs. Each pipeline stage has its own SZ0 and SZ1.

4. SC0, SC1, SC2 (bi-directional), Scale Factor 0,1,2 - Used to send the input data scaling factors and receive the output data scaling factors. Each pipeline stage has its own SC0, SC1, SC2.

5. *PE* (to controller), Parity Error - Used by the WFTs to signal that a parity error exists in the input data. Each pipeline stage has one *PE* signal.

6. WDerr (to controller), Watchdog Error - Used by the WFTs to signal that a Watchdog Error has occurred. Each WFT processor has a WDerr signal.

7. WFTdone (to controller), WFT Done - Used to signal that the WFT has finished a DFT. Each pipeline stage has one WFTdone signal.

16

8. LOAD (from controller), WFT Load - Used to signal a WFT processor to receive information on operation, scaling, and DFT size. Each WFT processor has its own LOAD signal.

HOST (these signals will be explained in Chapter 5):

- 1. PFAop (to controller), PFA Operate

- 2. PFA done (from controller), PFA Done

- 3. LOADSTUFF (to controller), Load/Read PFA

- 4. Hs4, Hs3, Hs2, Hs1, Hs0 (to controller), Storage Select

- 5. H15-H0 (from controller), Internal Data Output Lines

#### CHAPTER 3

#### Architecture and Algorithms

#### 3.1. Overview

This chapter discuss the architectures and algorithms used in the memory and the PFA controller. First, the memory architectures will be presented and then algorithms for the error control coding will be presented. Second, the general architecture for the PFA controller will be discussed then the algorithms used to operate the controller and the WFT processors will be developed, and finally, the resulting architecture will be shown.

#### 3.2. Memory

The memory can be broken into three main sections, data flow, storage, and error control coding. The data flow section deals with controlling the flow of data through the chip. The storage section discusses the actual storage cells; how they are selected, written to, or read from. Finally, the error control coding explains how the single error correction/double error detection is accomplished.

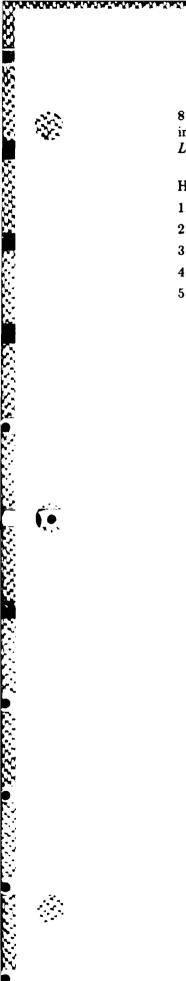

**3.2.1. Data Flow.** As previously mentioned, the memory must be partitioned into two halves to allow concurrent reading and writing. This partitioning is shown in Fig. 2. The data initially enters into the memory chip from the input pads, from there the data is passed through the input ECC circuitry and then to either memory side. A control signal determines to which side of the memory the data is written. After a side of the memory is read, also determined by the control signal, the values output by the

Figure 2 Memory Chip Partioning

memory arrays pass through the output ECC circuitry and then off-chip through the output pads.

<u>معاما ما محجود محدد م</u>

**3.2.2. Storage.** The storage area consists of several units, the word select, the memory cell, and the sense amplifier. The word select unit inputs the address lines and determines which of the 4096 words will be selected for the read or write operation. A memory word consists of 32 storage cells activated for reading or writing by a single word select line. When the value is read, the sense unit will detect the stored memory value and amplify it for further use in the chip.

**3.2.3. Error Control Coding.** Error Control Coding is accomplished in two steps. The first step to encode the input data and the second step is to decode the data from the memory before sending off-chip. The next two sections outline the devel priment of a systemetic block code described by Lin and Costello. Lin83. The matrices for the code were developed by Major Prescot in 1985. **3.2.3.1. Encoding** For this memory, a *message* is defined as an input word of 24 bits and denoted by u where  $u = (u_0, u_2, ..., u_{23})$ . With 24 bits, the maximum number of distinct messages is  $2^{24}$  or  $1.68 \times 10^7$ . The encoder transforms u into an *n*-tuple, v, where n > 24. The mapping of u to v is one to one and the set of all vectors v is the block code. Additionally, the  $2^k$  code words (k = 24) form a k-dimensional subspace of the vector space of all the *n*-tuples over the Galois field GF(2). Twenty-four linearly independent code words,  $g_0, g_1, \ldots, g_{23}$ , can be found from the block code such that every code word in the block code is a linear combination of the 24 code words. The resulting relationship between u and v is,

$$\mathbf{v} = u_0 \mathbf{g}_0 + u_1 \mathbf{g}_1 + \cdots + u_{23} \mathbf{g}_{23}. \tag{3.1}$$

The 24 linearly independent code words can be arranged into a  $(24 \times n)$  matrix, **G**, so that.

$$\mathbf{G} = \begin{bmatrix} \mathbf{g}_{0} \\ \mathbf{g}_{1} \\ \vdots \\ \vdots \\ \vdots \\ \mathbf{g}_{23} \end{bmatrix} = \begin{bmatrix} g_{0,0} & g_{0,1} & \cdots & g_{0,n-1} \\ g_{1,0} & g_{1,1} & \cdots & g_{1,n-1} \\ \vdots & \vdots & \ddots & \vdots \\ \vdots & \vdots & \vdots & \vdots \\ g_{23,0} & g_{23,1} & \cdots & g_{23,n-1} \end{bmatrix}.$$

(3.2)

**G** is considered to be the generator matrix for the linear block code. If  $\mathbf{u} = (u_0, u_1, \dots, u_{23})$  is the word to be encoded, then the code word,  $\mathbf{v}$ , is given as:

$\mathbf{v} = \mathbf{u} \mathbf{G}$

$$= (u_0, u_1, \dots, u_{23}) \cdot \begin{bmatrix} \mathbf{g}_0 \\ \mathbf{g}_1 \\ \vdots \\ \vdots \\ \mathbf{g}_{23} \end{bmatrix}$$

(3.3)

$$= u_0 \mathbf{g}_0 + u_1 \mathbf{g}_1 + \cdots + u_{23} \mathbf{g}_{23}$$

A variation on the linear block code is the linear systematic block code. A linear systematic block code divides the code word into two parts, the message part and the redundant part. The message part consists of the original input bits and the redundant part consists of parity-check digits which are linear sums of the input bits. For a linear systematic (n, 24) code, the 24xn G matrix has the following form:

where  $p_{ij}$  is a binary digit. Let **P** denote the first part of the generator matrix and  $I_{24}$  denote the 24x24 identity matrix. Then  $\mathbf{G} = \begin{bmatrix} \mathbf{P}I_{24} \end{bmatrix}$ . The code word now becomes

$$\mathbf{v} = (v_0, v_1, \dots, v_{n-1})$$

(3.5)

=  $(u_0, u_1, \dots, u_{23}) \cdot \mathbf{G}$ .

The last 24 bits of the code word correspond exactly to the original 24 in bits the input word and the first n-24 bits are the redundant parity-check bits. The equations used to compute the first n-24 bits are called parity-check equations and are of the form:

$$v_j = u_0 p_{0,j} + u_1 p_{1,j} + \dots + u_{23} p_{23,j}, \qquad (3.6)$$

for j = 0 to n-23. For our case we use 8 parity check bits making n=32. Appendix A shows the resulting P matrix. Using Eq. 3.6, the corresponding parity-check equations from matrix P are:

$$v_0 = u_0 + u_7 + u_8 + u_{14} + u_{16} + u_{21} \tag{3.7a}$$

$$v_1 = u_0 + u_1 + u_9 + u_{15} + u_{17} + u_{22} \tag{3.7b}$$

$$v_2 = u_1 + u_2 + u_8 + u_{10} + u_{18} + u_{23} \tag{3.7c}$$

$$v_3 = u_2 + u_3 + u_9 + u_{11} + u_{16} + u_{19} \tag{3.7d}$$

$$v_4 = u_3 + u_4 + u_{10} + u_{12} + u_{17} + u_{20} \tag{3.7e}$$

$$v_5 = u_4 + u_5 + u_{11} + u_{13} + u_{18} + u_{21} \tag{3.7f}$$

$$v_6 = u_5 + u_6 + u_{12} + u_{14} + u_{19} + u_{22} \tag{3.7g}$$

$$v_7 = u_6 + u_7 + u_{13} + u_{15} + u_{20} + u_{23} \tag{3.7h}$$

The code word  $\mathbf{v}$  can now be expressed as:

$$\mathbf{v} = (v_0, \ldots, v_7, u_0, \ldots u_{23}),$$

where  $v_0, \ldots, v_7$  are from Eqs 3.7a-h and  $u_0, \ldots, u_{23}$  are the original input word u.

**3.2.3.2. Decoding** Once  $\mathbf{v}$  has been stored in the memory it may be exposed to conditions which cause errors to appear. Because of the extra parity bits, the decoding scheme will correct single errors and detect double errors.

Let  $\mathbf{r} = (r_0, r_1, \ldots, r_{31})$  be the word read out of the memory. This word may or may not be different from the word initially stored. Now let  $\mathbf{e}$  be the vector sum of the code word,  $\mathbf{v}$ , and  $\mathbf{r}$  such that,

$$\mathbf{e} = \mathbf{v} + \mathbf{r} = (e_0, e_1, \dots, e_{31}),$$

(3.8)

where  $e_i$  is the boolean exclusive-or of  $v_i$  and  $r_i$ . Alternately, **r** may be represented as the vector sum of **e** and **v**.

It is necessary to introduce another matrix associated with the block code. This (n-k)xn matrix **H**, commonly referred to as the parity-check matrix, is defined so that any vector in the row space of **G** is orthogonal to the rows of **H** and any vector that is orthogonal to the rows of **H** is in the row space of **G**. Thus, a codeword generated by **G** solves the equation  $\mathbf{v} \cdot \mathbf{H}^T = 0$ . The parity-check equation may be written as follows:

| H = | • |   |   |       |   |                         |                         |                         |       |                            |   | (3. |

|-----|---|---|---|-------|---|-------------------------|-------------------------|-------------------------|-------|----------------------------|---|-----|

|     | 1 | 0 | 0 | •••   | 0 | <i>p</i> <sub>0.0</sub> | <b>p</b> <sub>0,0</sub> | <b>p</b> <sub>1,0</sub> |       | <b>P</b> 23.0              |   |     |

|     | 0 | 1 | 0 | · · · | 0 | <b>P</b> 0, 1           | <b>p</b> <sub>0,1</sub> | <b>p</b> <sub>1,1</sub> | • • • | <b>p</b> 23, 1             |   |     |

|     | 0 | 0 | 1 | · · . | 0 | <b>p</b> <sub>0,2</sub> | <b>p</b> <sub>0,2</sub> | <b>p</b> <sub>1,2</sub> |       | <b>P</b> 23,2              |   |     |

| =   | ŀ | • | • | •     | • | •                       |                         |                         |       |                            | , |     |

|     | ŀ | • | · | •     | • | •                       | •                       |                         | •     | •                          |   |     |

|     | ŀ | • | • | ·     | • | ·                       | •                       | •                       | •     |                            |   |     |

|     | 0 | 0 | 0 | •••   | 1 | <b>p</b> <sub>0,7</sub> | <b>p</b> <sub>0,7</sub> | <b>p</b> <sub>1,7</sub> | · · · | P 23.0<br>P 23.1<br>P 23.2 |   |     |

where  $\mathbf{P}^{T}$  represents the transpose of the matrix  $\mathbf{P}$ .

When  $\mathbf{r}$  is read, the decoder computes the following:

$$\mathbf{s} = \mathbf{r} \cdot \mathbf{H}^T = (s_0, s_1, \dots, s_7). \tag{3.10}$$

This equation defines the syndrome, **s**, of **r**. Because  $\mathbf{v} \cdot \mathbf{H}^T = 0$ , **r** is a valid codeword if and only if  $\mathbf{s} = 0$ . If  $\mathbf{s} \neq 0$  then the word read has been corrupted by errors. If the error vector **e** is identical to a codeword then  $\mathbf{e}+\mathbf{v}$  represents a valid code word and  $\mathbf{r} \cdot \mathbf{H}^T = 0$ . This condition is considered an undetectable error. Since there exist  $2^{24}$ -1 nonzero codewords, there exist the same number of undetectable error patterns. The  $\mathbf{H}^T$  matrix for our (32,24) block code is shown in appendix A.

The corresponding syndrome digit equations are:

$$s_0 = r_0 + r_8 + r_{15} + r_{16} + r_{22} + r_{24} + r_{29}$$

(3.11a)

$s_1 = r_1 + r_8 + r_9 + r_{17} + r_{23} + r_{25} + r_{30}$ (3.11b)

| $s_2 = r_2 + r_9 + r_{10} + r_{16} + r_{18} + r_{26} + r_{31}$ | (3.11c) | ) |

|----------------------------------------------------------------|---------|---|

|----------------------------------------------------------------|---------|---|

$$s_3 = r_3 + r_{10} + r_{11} + r_{17} + r_{19} + r_{24} + r_{27}$$

(3.11d)

$$s_4 = r_4 + r_{11} + r_{12} + r_{18} + r_{20} + r_{25} + r_{28}$$

(3.11e)

$$s_5 = r_5 + r_{12} + r_{13} + r_{19} + r_{21} + r_{26} + r_{29}$$

(3.11f)

$$s_6 = r_6 + r_{13} + r_{14} + r_{20} + r_{22} + r_{27} + r_{30}$$

(3.11g)

$$s_7 = r_7 + r_{14} + r_{15} + r_{21} + r_{23} + r_{28} + r_{31}$$

(3.11h)

Thus, we have computed the syndrome of **r** which is equal to  $\mathbf{r} \cdot \mathbf{H}^T$ . But,  $\mathbf{r} = (\mathbf{v} + \mathbf{e})$ so that  $\mathbf{s} = (\mathbf{v} + \mathbf{e})\mathbf{H}^T = \mathbf{v} \cdot \mathbf{H}^T + \mathbf{e} \cdot \mathbf{H}^T$ . However,  $\mathbf{v} \cdot \mathbf{H}^T = 0$  so that the following relationship is established:  $\mathbf{s} = \mathbf{e} \cdot \mathbf{H}^T$ . Because of the above relation it is possible to compute **e** from **s**. The reader is referred to Chapter 3 of Lin and Costello [Lin83] for the proof. The error vector, **e**, is computed from the matrix in Appendix A. Appendix A also shows the 32  $e_i$  equations. Each  $e_i$  is a combination of the 8 syndrome digits so that

# $e_j = s_0 \cdot s_1 \cdot s_2 \cdot s_3 \cdot s_4 \cdot s_5 \cdot s_6 \cdot s_7$ ,

where  $s_m \cdot s_n$  represents the boolean AND function and  $s_i$  may be boolean 1 or 0. For example, the syndrome decoding of  $e_8 = s_0 \cdot s_1 \cdot \overline{s}_2 \cdot \overline{s}_3 \cdot \overline{s}_4 \cdot \overline{s}_5 \cdot \overline{s}_6 \cdot \overline{s}_7$ , where  $s_i$  represents boolean 1 and  $\overline{s}_i$  represents boolean 0. From Eq. 3.8 it follows that  $\mathbf{v} = \mathbf{e} + \mathbf{r}$ . Therefore, the approximation of the original codeword is obtained by EXCLUSIVE-ORing the word read out of memory,  $\mathbf{r}$ , and the computed error vector,  $\mathbf{e}$ .

# 3.3. PFA Controller

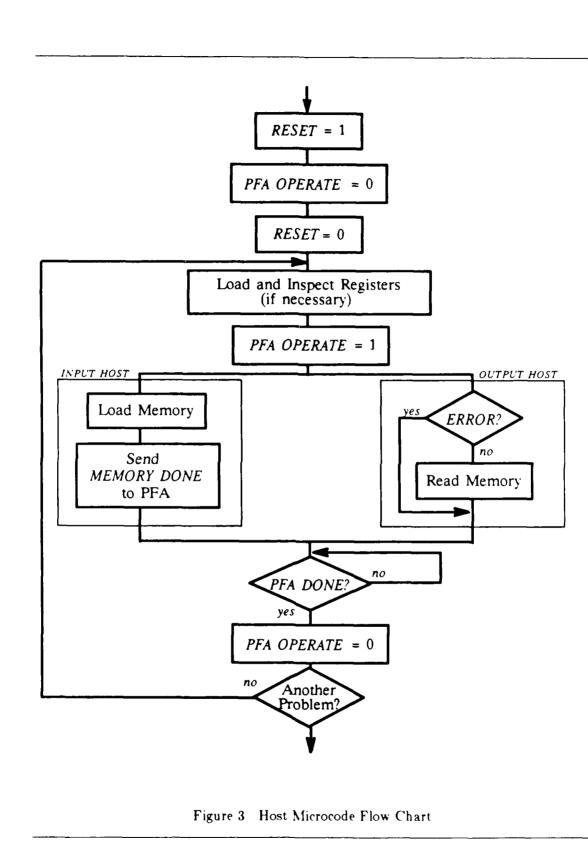

The PFA controller chip consists two main architectural parts, the microprogrammed control unit and the processor unit. The microprogrammed control unit is responsible for sequencing through predetermined states for the controller and initiating processor actions as well as data flow through the chip. The processor unit performs all the data manipulations as well as storing the data and sending signals to the microprogrammed control unit. In order to make the architectural description more meaningful, it is necessary to discuss the algorithms associated with the PFA controller. In an application specific processor, the algorithm drives the architecture. **3.3.1. Host Algorithm.** The host must operate and communicate with the PFA controller. Handshaking is kept to a minimum, optimally only an operate signal to the DFA controller. The does signal from the controller. The best algorithm is shown in

PFA controller. Handshaking is kept to a minimum, optimally only an operate signal to the PFA controller and a done signal from the controller. The host algorithm is shown in Fig. 3. Initially, the host must reset the controller. This initializes the storage areas and resets all counters and addresses lines. Now, the host lowers the operate signal and then lowers the reset signal. The host can proceed to inspect any storage locations and update if needed. Specifically, the host must specify the initial configuration, scale factors, size, and timeout information. Once the proper data has been set, the operate signal to the PFA controller is raised. Since the pipeline is set with data entering from one side and exiting from the other, there may be two different hosts, an input host and an output host. The input host must load the new data into the first memory and send a done signal to the PFA controller when all the data is loaded. The output host, at this time. must unload the DFT results from the last memory in the pipeline. From the register inspection, the output host knows whether the pipeline output data is valid or not. If the data is not valid, the host ignores the current output data. The next event is for the current DFT to be computed, this is signaled by the done signal from the PFA controller. The host may then continue to operate the PFA as long as needed.

At any time during the pipeline operation while the PFA is not computing, the host may change the configuration, change the size of the DFT to be computed, implying a hardware reconfiguration, or change the scale factors of the input data.

PERSONAL STREAM STREAMS (STREAMS)

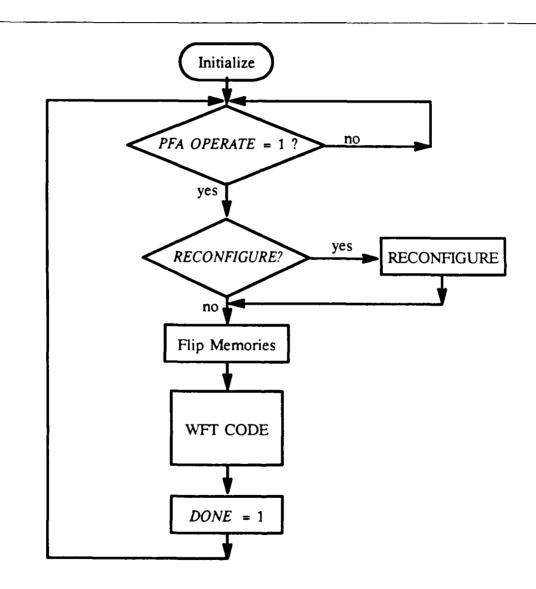

**3.3.2. PFA Controller Algorithm.** The high level algorithm for the PFA controller is shown in Fig. 4. The first section deals with initializing values and data on the chip during power up. The controller then waits for an operate signal from the host. While the PFA controller is waiting for the operate signal, the host has access to the internal data stored on the chip. Once the controller has received the operate signal, it

Figure 4 Controller Microcode Flow Chart

Ĩ

checks to see if the pipeline must be reconfigured. Reconfiguration is discussed later in this chapter. The PFA controller then toggles the flip signal sent to the memories. The controller then communicates with the WFT processors. Once the WFT computations are done, the PFA sends a done signal to the host.

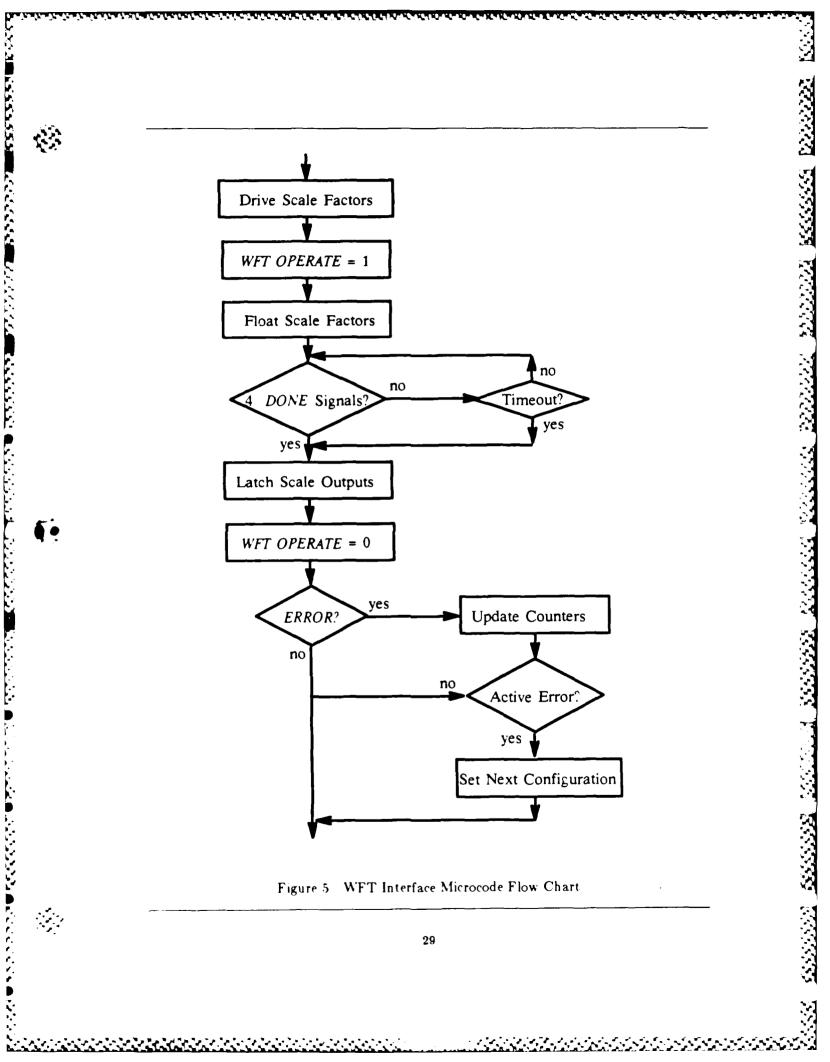

The WFT interface algorithm is shown in Fig. 5. The PFA controller must first send the scale factors to the WFT, then send the operate signal, and then float the scale factor lines so that the output scale factors may be returned by the WFT processors. The controller then waits for four done signals: one from the input host and one from each stage of WFT processors. Once all have finished, the PFA controller latches the new scale factors from each stage and stores them internally. The controller then lowers the WFT operate signal. The controller looks at information received from the pipeline to determine if any errors have occurred and updates certain storage locations if need be. If an error has occurred in the active WFT processor, the controller sets up a new configuration.

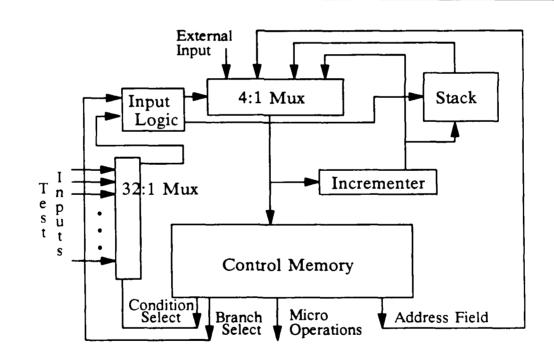

**3.3.3.** Microprogrammed Control Unit. The microprogrammed control unit (MCU) controls the operation of the chip. It generates the control signals that operate the pipeline, communicate with the host, or manipulate the internal data. This unit can be thought of as two separate sections: the control memory and the microprogrammed sequencer (Man82). The control memory is a read only memory (ROM) Where words read one at a time, represent a microinstruction. Each microinstruction contains information needed for the chip to operate. The instruction format is broken down into logical fields. Each of these fields defines a certain set of operations in the chip. These fields can be horizontally or vertically coded (Man82). To achieve a compromise of the benefits and tradeoffs of the two approaches, the PFA microinstruction contains both

.

The microprogrammed sequencer determines the next address to be read out of the ROM. The next address can come from several sources including the microinstruction itself, an external bus, a stack used for subroutines, or simply be the next address in sequence. The microprogrammed sequencer determines the address from a number of conditions selected by the microcode instruction.

Figure 6 shows a typical MCU. The control memory contains several main fields. Two of these fields determine how the next address is selected, the condition and the branch fields. The condition field selects one of the conditions used for branching and control that exist in the chip. The branch field selects either T or F for an unconditional branch or call, or positive or negative sense of the selected condition. The branch

Figure 6 Microprogrammed Control Unit

address may come from three different places, the instruction itself, the stack, or an external source. The stack is used as a temporary storage location in the event of subroutine call for the return address. When a call is executed, the address of the next instruction is pushed onto the top of the stack. On a return, the branch address is popped off the stack and selected as the next address. The MCU also contains an incrementer for sequential addressing.

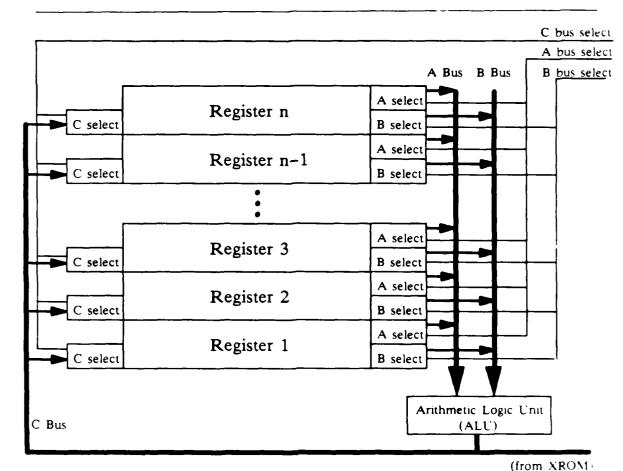

**3.3.4.** Processor Unit. The processor unit contains the internal storage for the chip and the circuitry necessary to manipulate the data. The PFA controller architecture is organized around a bus structure and is shown in Fig. 7. The data is stored in a set of registers that can be loaded or read. The registers are loaded through the C bus or from an XROM field. The particular register is selected via a decoder. The data may be read out on either the A bus or the B bus. The A bus and the B bus are fed into the arithmetic logic unit (ALU). The ALU can perform 15 functions on the data and set condition bits accordingly. For a detailed description of the ALU, the reader is referred to the thesis of Capt. David Gallagher [Gal87].

**3.3.5. Registers.** The registers store the data for the controller. There are 28 registers in the controller. Seven of the registers have special purposes requiring such options as being loaded from sources other than the load bus, driving the contents to destinations other than the data busses, and shifting. The following defines the registers used in the PFA controller and any special requirements:

ECC1-ECC3, Error Control Corrected registers.

These three registers are used as counters for the number of Error Control Code

No. Name and a subset

corrected from the first three memories. These registers can be used for fault monitoring.

ECU1-ECU3, Error Control Uncorrected registers.

These three registers are used as counters for the Error Control Code uncorrected from the first three memories. These registers can also be used for fault monitoring.

PE1-PE3, Parity Error registers.

يحدددن

These three registers are used as counters for the number of Parity Errors signaled by each stage of the pipeline.

# WD11-WD13,WD21-WD23,WD31-WD33, Watch Dog registers.

These nine registers are used as counters for the number of times the WFT processor was assigned as having a fault.

# TSR, Temporary Scale Register.

This register is used to store the scale factors to be given to each stage of the pipeline. Nine of the bits (3 sets of 3) must be able to be sent to the WFT processors. The register must also be able to receive the scale factors from the WFT processors and then shift those by 5 bit for the next stage of the pipeline.

# PSR. Permanent Scale Register.

This register is used to store the accumulating scale factors for each of the three problems in the pipeline. This register must be able to transfer the problem's scale factors to the respective problem's Problem Status register. This register must also be able to shift the scale factor bit by 5 positions

# PS1-PS3. Problem Status register.

These three registers store information about each of the three problems in the pipeline. They store the current accumulated scale factor, and whether there was a fault due to an active error, a memory uncorrectable error, or a parity error and which stage of the pipeline the error occurred. The register also contains a bit signifying whether the data was validated by the processor finishing.

## CCR, Current Configuration Register and NCR, Next Configuration Register.

These two registers store the current and next configurations respectively.

# TOUT, Timeout Register.

This register contains a time out value to determine whether a pipeline catastrophic pipeline failure has occurred, such as a processor not finishing.

TEMP, Temporary register.

This register is used as a scratch pad for many of the data manipulations.

**3.3.6.** Microcode Word Format. Now that all of the major architectural components have been identified, the fields in the word format can be identified. Figure 8 shows the architecture of the PFA controller. Each field in the microcode will control the operation of an architectural block, peripheral circuit, or direct output. The first field controls the addresses sequencer for the XROM. It determines where the next address originates. The second field specifies the operation of the ALU. The third field is used to indicate an insertion of the literal field onto the destination register bus. This is used to load a constant from the microword into a register. The fourth, fifth, and sixth fields select the two source registers and the destination register, respectively, for the ALU. The eighth field signals the WFT processors to operate. The ninth field signals the host that the DFT is done. Finally, the tenth field contains the address of the branch or a constant to be inserted onto the destination bus. The bit fields will be described in Chapter 4.

**3.3.7.** Pipeline Fault Tolerance. The pipeline is set up for fault tolerance using triple redundancy and voting for the WFT processors [Hed86]. In each stage, one of the three processors is considered to be active, the other two are considered to be in watchdog mode. When a processor operates in watchdog mode, it receives the same data as the active processor, computes the same transform and compares its results with the results of the active at the output pads without driving the pipeline data bus. If there is a discrepancy, a WatchDog error bit is signaled to the PFA controller. The PFA controller looks at the three WatchDog error bits from each of the processors in each stage.

and uses a voting strategy to assign the error, if any one of the WatchDog error bit is raised. The voting strategy is as follows:

| Active | Watchdog1 | Watchdog2 | Result                      |  |

|--------|-----------|-----------|-----------------------------|--|

| 0      | 0         | 0         | No Error Assigned           |  |

| 0      | 0         | 1         | Error Assigned to Watchdog2 |  |

| 0      | 1         | 0         | Error Assigned to Watchdog1 |  |

| 0      | 1         | 1         | Error Assigned to Active    |  |

| 1      | 0         | 0         | Error Assigned to Active    |  |

| 1      | 0         | 1         | Error Assigned to Watchdog1 |  |

| 1      | 1         | 0         | Error Assigned to Watchdog2 |  |

| 1      | 1         | 1         | No Error Assigned           |  |

Table 1: Voting Strategy

The (1, X, X) cases are conditions that are treated as normal because the possibility of the active signaling a watchdog error is too small to warrant the amount of microcode and hardware necessary for handling this condition. The conditions to cause a (1, X, X) case would be for the active processor to signal that it had a watchdog error. This can only happen when the WFT has suffered a major error, the pipeline has some kind of bus error in which the line is set high, or a transient fault. If the active processor signals a watchdog error and the others do not, this error will be assigned to the active as it should be. The problem arises when the the active signals as watchdog error and one watchdog also signals an error. In this case, the error will be assigned to the watchdog processor that did not signal the error. It is difficult to determine what was the true cause of the error was. The error could be in the active or either watchdog processor and this voting strategy will not find the fault. In the event that all three signal a watchdog error, no error is assigned. The probability of this occurring is extremely small except in a high radiation zone. And, should it occur, the data would probably be corrupted enough so that the next WFT in the pipeline would most likely detect a parity error. If it

is the last stage in the pipeline the data will be bad with no error reported.

•

When the PFA controller executes the code for error recording, it looks at the watchdog errors and determines if one of the three active processors has errored, if so it sets up the Next Configuration Register to make the next active processor to be the current watchdog with the smallest error count. If the two watchdogs have the same number of errors, it selects the processor with the lowest number name (ie. WDil < WDi2 < WDi3; where *i* represents the column). The names assigned to the processors are shown in Fig. 9.

~~~~

PERSON PROPERTY RECEIPTING

LANGER PRATICE STREET

A STATE AND A S

# CHAPTER 4

# **Computer Aided Design Environment Tools**

### 4.1. Overview

The computer aided design (CAD) environment has a great impact on the quality and timeliness of what can be produced. A well-integrated set of tools from the design stage through the implementation stage to the simulation stage allows easier transitions between stages and quicker execution. AFIT currently supports a limited number of tools for the design and implementation phases. In the following sections, the methodology for designing a VLSI chip within the AFIT CAD environment is discussed, descriptions of the tools needed are given, and a description and the development of a CAD tool created as a result of this thesis effort.

#### 4.2. Design Methodology

The first step in producing a VLSI chip to decide what problem to solve. A detailed problem specification limits the scope of what is to be done and thus limits the amount of extra design that might not be needed. The next step is to develop an architectural description from the problem specification. For the design parts of this thesis effort, the architectural descriptions are extremely different. The memory chip architecture supports a data flow architecture and the PFA controller chip supports a finite state machine architecture. Once the architecture has been described, the logic and circuit design follow. At this stage, the interfaces between the macrocells are defined as well as the incorporation of testiblility. The next step is the VLSI layout. Once the layout is complete, the simulation phase begins. Simulation and verification start at the lowest level of design and proceed up the hierarchy. When discrepancies are noted between the simulation and the descriptions, the chip design loops back to various levels depending on where the discrepancy occurred. Once the chip has met the simulation requirements, it is ready for fabrication. 122255

A COLOR DE PRESENTE

**4.2.1. AFIT CAD Tools.** AFIT currently supports the CAD environment near the lower design levels. These tools currently support VLSI layout and switch-level simulation. In addition to the software tools, AFIT has considerable computing power and other hardware support for CAD. The hardware used in this thesis effort included:

- 1. Two ELXSI 6400s,2-CPU(12MIP,6MIP) running UNIX 4.2BSD

- 3. SUN2 and SUN3 Workstations running UNIX 4.3BSD

- 4. Two VAX 11/785s running UNIX 4.3BSD

- 5. A VAX 11/785 running VMS 4.5

6. A Versatec Plotter, and an assortment of printers.

The current mainstay of the AFIT VLSI CAD toolset is Magic [Ost86]. Magic is an interactive VLSI layout tool that allows creation and modification of VLSI circuits using Manhattan circuit design geometries. For this thesis effort, Magic was run primarily on a SUN 3 because of the window environment and interactive speed for cell editing. Magic was run on the ELXSI 6400 when executing several features of Magic that are computationally intensive. This included the design rule checking of a silicon compiled XROM (described later) and hierarchal cell "flattening" of the same XROM. The XROM contains thousands of cells and was found to be easier, and faster, to work with the XROM "flattened."

Mextra [Fit83] was used to translate from the Cal-Tech Intermediate Form (CIF) to a switch-level format suitable for other simulations. Mextra takes the "cif" file, which

is a mask level description of the circuit produced by Magic, and makes a "sim" file which is a listing of all the transistors in the circuit and associated capacitances. In addition to the translation, Mextra outputs several other files. These include the alias file, the log file, and the nodes file. The alias file is very useful in finding nodes that are "shorted" together that should not be. The log file gives information about the number of occurrences of labels that are not connected together by stating that a certain label has X number of occurrences. The file provides information that usually lead to finding unwanted "open circuits" between nodes. Finally, the nodes file is a list of the node numbers assigned by Mextra and their location on the chip. This is useful reference when running other tools which refer to node numbers.

Cstat, a CMOS version of stat [Ter86], was run on the output of Mextra. Cstat provides information about nodes that cannot be affected by the inputs, cannot affect the outputs, and nodes that cannot be set to either logic-1 or logic-0. This tool is useful for finding nodes that are not connected or shorted to either Vdd(logic-1) or GND(logic-0). By the time the circuit is ready for fabrication, every node, if any, signaled by Cstat should be accounted for.

Nofeed and Fixrom are two tools needed to allow Esim, described below, to work properly. Nofeed scans the Mextra output to identify and remove the feedback loops from Master-Slave Flip-Flops (MSFFs) making them dynamic. A more complete discussion of the operation of the MSFF will be given in Chapter 5. Fixrom modifies two portions of the XROM for Esim compatibility. The first modification is to replace the shared drain in the XROM storage array and the second is to replace an inverter in the XROM sense amplifier. A thorough discussion of the operation of the XROM will be given in Chapter 5.

Esim [Ter86], is an event-driven switch simulator for nMOS or CMOS transistor circuits. Esim is used to exercise the switch level description from FIXROM. This tool was used to verify the logic created from the Magic layout for correct operation. Simulation can be preformed as if the chip is under test by stimulating only the inputs and observing only the outputs, or as a diagnostic tool by stimulating any node in the circuit and observing any node in the circuit. Once a circuit performs as expected under Esim, it is considered ready for fabrication.

Two tools developed at AFIT were used to create the XROM used in the control section. The first tool was the Generic Microcode Assembler Tool (GMAT). GMAT was developed as part of this thesis effort and is described in the following section. The second tool was an optimizing XROM silicon compiler. This tool, given a list of integer values describing the binary contents of the ROM, will minimize the transistor count and the number of drains. The compiler will also generate the Magic layout for the optimized ROM including the word selectors, column drivers, sense amplifiers, precharge circuitry, and cell arrays

4.2.2. Generic Microcode Assembler Tool (GMAT). When designing microcode, it is desirable to describe the code in a structured language representation using mnemonics. Describing microcode in these terms is helpful for two reasons; first, the code is more readable and second, the code is less prone to errors. These factors motivate the need for a microcode assembler. The CAD environment needs tools that can be applied to different projects so the assembler must be generic.

To achieve the above needs, a generic microcode assembler tool was developed. This tool takes a microcode word format description and mnemonic translation file and builds a microcode assembler for that particular microcode format. The resulting assembler reads in the translation file and the microcode to produce outputs that are compatible with other CAD tools and are useful in debugging the integration of the microcode into chip designs. Specifically, it generates an address stream used by the optimizing XROM compiler, a VHDL description of the ROM, a reference file, and a reverse assembly file