## WIND RIVER

# **VxWorks**<sup>®</sup>

# DEVICE DRIVER DEVELOPER'S GUIDE Volume 2: Writing Class-Specific Device Drivers

6.6

Copyright © 2007 Wind River Systems, Inc.

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means without the prior written permission of Wind River Systems, Inc.

Wind River, Tornado, and VxWorks are registered trademarks of Wind River Systems, Inc. The Wind River logo is a trademark of Wind River Systems, Inc. Any third-party trademarks referenced are the property of their respective owners. For further information regarding Wind River trademarks, please see:

http://www.windriver.com/company/terms/trademark.html

This product may include software licensed to Wind River by third parties. Relevant notices (if any) are provided in your product installation at the following location: *installDirlproduct\_name*/3rd\_party\_licensor\_notice.pdf.

Wind River may refer to third-party documentation by listing publications or providing links to third-party Web sites for informational purposes. Wind River accepts no responsibility for the information provided in such third-party documentation.

#### **Corporate Headquarters**

Wind River Systems, Inc. 500 Wind River Way Alameda, CA 94501-1153 U.S.A.

toll free (U.S.): (800) 545-WIND telephone: (510) 748-4100 facsimile: (510) 749-2010

For additional contact information, please visit the Wind River URL:

http://www.windriver.com

For information on how to contact Customer Support, please visit the following URL:

http://www.windriver.com/support

VxWorks Device Driver Developer's Guide, Volume 2: Writing Class-Specific Device Drivers, 6.6

# Contents

| 1 | Clas | ss-Spec | cific Driver Development                                                                         | 1           |

|---|------|---------|--------------------------------------------------------------------------------------------------|-------------|

|   | 1.1  | About   | VxBus Driver Classes                                                                             | 1           |

|   | 1.2  | Before  | You Begin                                                                                        | 2           |

|   | 1.3  | About   | this Document                                                                                    | 2           |

|   |      |         | Navigating this Documentation Set                                                                | 2           |

| 2 | Bus  | Contro  | oller Drivers                                                                                    | 3           |

|   | 2.1  | Introd  | uction                                                                                           | 3           |

|   | 2.2  | Overv   | iew                                                                                              | 4           |

|   | 2.3  | VxBus   | Driver Methods                                                                                   | 5           |

|   |      | 2.3.1   | {busCtlrCfgRead}()                                                                               | 6           |

|   |      | 2.3.2   | {busCtlrCfgWrite}()                                                                              | 7           |

|   |      | 2.3.3   | {busCtlrAccessOverride}()                                                                        | 8           |

|   |      |         | Override for (*busCfgRead)()<br>Override for (*busCfgWrite)()<br>Override for (*vxbDevControl)() | 9<br>9<br>9 |

|   |      | 2.3.4   | {busCtlrCfgInfo}()                                                                               | 10          |

|   |      | 2.3.5   | {busCtlrBaseAddrCvt}()                                                                           | 11          |

|      | 2.3.6   | {vxbDevRegMap}()                          | 11       |

|------|---------|-------------------------------------------|----------|

|      |         | Specifying a Predefined Transaction Type  | 13<br>15 |

|      | 0.07    | Providing a New Transaction Type          |          |

|      | 2.3.7   | {vxbIntDynaVecProgram}()                  | 17       |

| 2.4  | Heade   | r Files                                   | 17       |

| 2.5  | BSP C   | onfiguration                              | 17       |

|      | 2.5.1   | PCI Configuration                         | 18       |

|      | 2.5.2   | PCI Autoconfiguration                     | 19       |

| 2.6  | Availa  | ble Utility Routines                      | 20       |

|      | 2.6.1   | PCI Configuration                         | 20       |

|      | 2.6.2   | PCI Autoconfiguration                     | 21       |

|      | 2.6.3   | vxbBusAnnounce( )                         | 21       |

|      | 2.6.4   | vxbPciBusTypeInit( )                      | 22       |

|      | 2.6.5   | vxbPciDeviceAnnounce()                    | 22       |

| 2.7  | Initial | ization                                   | 23       |

|      | 2.7.1   | Initialization Example                    | 24       |

|      |         | vxbBusAnnounce( )                         | 25       |

|      |         | vxbDeviceAnnounce()                       | 26       |

|      |         | vxbDevStructAlloc()<br>vxbDevStructFree() | 26<br>26 |

|      |         | vxbDevStructFree()                        | 20       |

| 2.8  | Debu    | 3ging                                     | 26       |

| Dire | ect Men | nory Access Drivers                       | 29       |

| 3.1  | Introd  | uction                                    | 29       |

| 3.2  | Overv   | iew                                       | 30       |

| 3.3  | VxBus   | Driver Methods                            | 30       |

|      | 3.3.1   | {vxbDmaResourceGet}()                     | 30       |

|      | 3.3.2   | {vxbDmaResourceRelease}()                 | 31       |

3

|      | 3.3.3   | {vxbDmaResDedicatedGet}()                        | 31 |

|------|---------|--------------------------------------------------|----|

| 3.4  | Heade   | er Files                                         | 32 |

| 3.5  | BSP C   | onfiguration                                     | 32 |

| 3.6  | Availa  | ble Utility Routines                             | 33 |

| 3.7  | Initial | ization                                          | 33 |

| 3.8  | DMA     | System Structures and Routines                   | 33 |

|      | 3.8.1   | (*dmaRead)( )                                    | 34 |

|      | 3.8.2   | (*dmaReadAndWait)( )                             | 34 |

|      | 3.8.3   | (*dmaWrite)()                                    | 34 |

|      | 3.8.4   | (*dmaWriteAndWait)()                             | 35 |

|      | 3.8.5   | (*dmaCancel)()                                   | 35 |

|      | 3.8.6   | (*dmaPause)()                                    | 35 |

|      | 3.8.7   | (*dmaResume)()                                   | 36 |

|      | 3.8.8   | (*dmaStatus)()                                   | 36 |

| 3.9  | Debuş   | gging                                            | 36 |

| Inte | rrupt C | ontroller Drivers                                | 37 |

| 4.1  | Introd  | uction                                           | 38 |

| 4.2  | Overv   | iew                                              | 38 |

|      |         | Interrupt Identification                         | 39 |

|      |         | Interrupt Controller Driver Responsibilities     | 39 |

|      |         | Interrupt Controller Configurations              | 39 |

|      |         | Dynamic Vectors                                  | 40 |

|      |         | Interrupt Controller Drivers and Multiprocessing | 40 |

| 4.3  | VxBus   | Driver Methods                                   | 41 |

4

|     | 4.3.1  | Basic Methods                                                               | 41                   |

|-----|--------|-----------------------------------------------------------------------------|----------------------|

|     |        | <pre>{vxbIntCtlrConnect}()</pre>                                            | 41<br>41<br>42<br>42 |

|     | 4.3.2  | Dynamic Vector Methods                                                      | 43                   |

|     |        | {vxbIntDynaVecConnect}()                                                    | 43                   |

|     | 4.3.3  | Multiprocessor Methods                                                      | 43                   |

|     |        | {vxbIntCtlrIntReroute}()<br>{vxbIntCtlrCpuReroute}()<br>{vxIpiControlGet}() | 43<br>44<br>44       |

| 4.4 | Heade  | r Files                                                                     | 45                   |

|     |        | vxbIntrCtlr.h<br>vxbIntCtlrLib.h                                            | 45<br>45             |

| 4.5 | BSP C  | onfiguration                                                                | 45                   |

|     | 4.5.1  | Interrupt Input Table                                                       | 46                   |

|     | 4.5.2  | Dynamic Vector Table                                                        | 48                   |

|     | 4.5.3  | CPU Routing Table                                                           | 49                   |

|     | 4.5.4  | Interrupt Priority                                                          | 50                   |

|     | 4.5.5  | Crossbar Routing Table                                                      | 50                   |

| 4.6 | Availa | ble Utility Routines                                                        | 51                   |

|     | 4.6.1  | intCtlrHwConfGet()                                                          | 52                   |

|     | 4.6.2  | intCtlrISRAdd()                                                             | 52                   |

|     | 4.6.3  | intCtlrISRDisable()                                                         | 52                   |

|     | 4.6.4  | intCtlrISREnable()                                                          | 52                   |

|     | 4.6.5  | intCtlrISRRemove()                                                          | 53                   |

|     | 4.6.6  | intCtlrPinFind()                                                            | 53                   |

|     | 4.6.7  | intCtlrTableArgGet()                                                        | 53                   |

|     | 4.6.8  | intCtlrTableFlagsGet()                                                      | 53                   |

|     | 4.6.9  | intCtlrTableIsrGet()                                                        | 53                   |

|      | 4.6.10                                           | intCtlrHwConfShow()                                              | 53       |  |  |

|------|--------------------------------------------------|------------------------------------------------------------------|----------|--|--|

|      | 4.6.11                                           | intCtlrTableCreate()                                             | 54       |  |  |

|      | 4.6.12                                           | intCtlrTableFlagsSet()                                           | 54       |  |  |

|      | 4.6.13                                           | intCtlrTableUserSet()                                            | 54       |  |  |

|      | 4.6.14                                           | VXB_INTCTLR_ISR_CALL( )                                          | 54       |  |  |

|      | 4.6.15                                           | VXB_INTCTLR_PINENTRY_ENABLED()                                   | 55       |  |  |

|      | 4.6.16                                           | VXB_INTCTLR_PINENTRY_ALLOCATED()                                 | 55       |  |  |

|      | 4.6.17                                           | Dispatch Routines                                                | 55       |  |  |

|      |                                                  | vxbIntDynaCtlrInputInit( )<br>vxbIntDynaVecProgram( )            | 56<br>56 |  |  |

| 4.7  | Initiali                                         | zation                                                           | 56       |  |  |

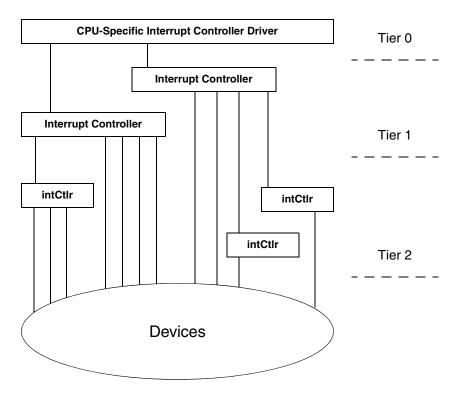

| 4.8  | Interrupt Controller Typologies and Hierarchies5 |                                                                  |          |  |  |

| 4.9  | Interrupt Priority                               |                                                                  |          |  |  |

| 4.10 | ISR Dispatch                                     |                                                                  |          |  |  |

| 4.11 | Manag                                            | ing Dynamic Interrupt Vectors                                    | 62       |  |  |

|      |                                                  | Configuring Dynamic Vectors Using the Service Driver Routines    | 63       |  |  |

|      |                                                  | Configuring Dynamic Vectors in the BSP                           | 63       |  |  |

|      |                                                  | Programming Dynamic Vectors<br>Determining Dynamic Vector Values | 64<br>65 |  |  |

|      |                                                  |                                                                  | 05       |  |  |

| 4.12 | Interna                                          | Il Representation of Interrupt Inputs                            | 65       |  |  |

| 4.13 | Multip                                           | rocessor Issues with VxWorks SMP                                 | 66       |  |  |

|      | 4.13.1                                           | Routing Interrupt Inputs to Individual CPUs                      | 67       |  |  |

|      | 4.13.2                                           | Interprocessor Interrupts                                        | 68       |  |  |

|      | 4.13.3                                           | Limitations in Multiprocessor Systems                            | 72       |  |  |

|      |                                                  |                                                                  |          |  |  |

| 5 | Mult | Multifunction Drivers |                                   |           |  |  |

|---|------|-----------------------|-----------------------------------|-----------|--|--|

|   | 5.1  | Introdu               | uction                            | 75        |  |  |

|   | 5.2  | Overvi                | iew                               | 76        |  |  |

|   | 5.3  | VxBus                 | Driver Methods                    | 76        |  |  |

|   | 5.4  | Heade                 | r Files                           | 77        |  |  |

|   | 5.5  | BSP Co                | onfiguration                      | 77        |  |  |

|   | 5.6  | Availa                | ble Utility Routines              | 78        |  |  |

|   |      |                       | vxbDevStructAlloc()               | 78        |  |  |

|   |      |                       | vxbDeviceAnnounce()               | 78        |  |  |

|   |      |                       | vxbDevRemovalAnnounce()           | 78        |  |  |

|   |      |                       | vxbDevStructFree()                | 78        |  |  |

|   |      |                       | vxbBusAnnounce()                  | 79        |  |  |

|   | 5.7  | Initiali              | zation                            | 79        |  |  |

|   | 5.8  | Device                | Interconnections                  | <b>79</b> |  |  |

|   |      | 5.8.1                 | Interleaved Registers             | 79        |  |  |

|   |      | 5.8.2                 | Shared Resources                  | 81        |  |  |

|   |      | 5.8.3                 | Other Interactions                | 81        |  |  |

|   | 5.9  | Logica                | l Location of Subordinate Devices | 81        |  |  |

|   | 5.10 | Debug                 | ging                              | 82        |  |  |

| 6 | Netv | etwork Drivers        |                                   |           |  |  |

|   | 6.1  | Introdu               | uction                            | 83        |  |  |

|   |      | 6.1.1                 | Terminology                       | 84        |  |  |

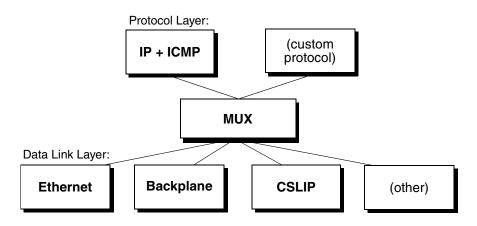

|   |      | 6.1.2                 | Networking Overview               | 84        |  |  |

|   |      |                       | Seven Layer OSI Model             | 84        |  |  |

|   |      |                       | Transmission Media and VxWorks    | 85        |  |  |

|   |      |                       | Protocols                         | 85        |  |  |

|   |      |                       |                                   |           |  |  |

| 6.2 | Network Interface Drivers |                                                                                                      |                            |  |  |

|-----|---------------------------|------------------------------------------------------------------------------------------------------|----------------------------|--|--|

|     | 6.2.1                     | Network Interface Driver Overview                                                                    | 86                         |  |  |

|     |                           | Functional Modules<br>Network Driver Interrupts                                                      | 86<br>88                   |  |  |

|     | 6.2.2                     | VxBus Driver Methods for Network Interface Drivers                                                   | 88                         |  |  |

|     |                           | <pre>{muxDevConnect}()</pre>                                                                         | 89<br>90<br>90<br>90<br>91 |  |  |

|     | 6.2.3                     | Header Files for Network Interface Drivers                                                           | 92                         |  |  |

|     | 6.2.4                     | BSP Configuration for Network Interface Drivers                                                      | 93                         |  |  |

|     | 6.2.5                     | Available Utility Routines for Network Interface Drivers                                             | 94                         |  |  |

|     |                           | MUX Interactions<br>Job Queueing<br>Buffer Management<br>DMA Support<br>PHY and MII bus interactions | 95<br>96<br>97<br>98<br>99 |  |  |

|     | 6.2.6                     | Initialization for Network Interface Drivers                                                         | 101                        |  |  |

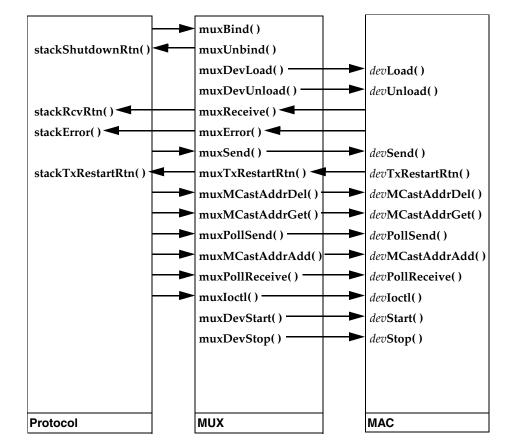

|     | 6.2.7                     | MUX: Connecting to Networking Code                                                                   | 102                        |  |  |

|     | 6.2.8                     | jobQueueLib: Deferring ISRs                                                                          | 103                        |  |  |

|     | 6.2.9                     | netBufLib: Transferring Data with mBlks                                                              | 104                        |  |  |

|     |                           | Setting Up a Memory Pool<br>Supporting Scatter-Gather                                                | 104<br>105                 |  |  |

|     | 6.2.10                    | vxbDmaBufLib: Managing DMA                                                                           | 106                        |  |  |

|     | 6.2.11                    | Protocol Impact on Drivers                                                                           | 107                        |  |  |

|     |                           | IPv4 and IPv6 Checksum Offloading                                                                    | 107                        |  |  |

|     | 6.2.12                    | Other Network Interface Driver Issues                                                                | 115                        |  |  |

|     |                           | Receive Handler Interlocking Flag<br>Fair Received Packet Handling<br>Receive Stall Handling         | 115<br>116<br>117          |  |  |

|     | 6.2.13   | Debugging Network Interface Drivers        | 118 |

|-----|----------|--------------------------------------------|-----|

|     |          | Using VxBus Show Routines                  | 118 |

|     |          | Deferring Driver Registration              | 118 |

|     |          | Pairing with a PHY instance                | 119 |

|     |          | Stress Testing                             | 120 |

|     |          | Netperf Test Suite                         | 120 |

|     |          | Interrupt Validation                       | 120 |

|     |          | Additional Tests                           | 120 |

| 6.3 | PHY D    | rivers                                     | 123 |

|     | 6.3.1    | PHY Driver Overview                        | 123 |

|     |          | PHY Device Probing and Discovery           | 124 |

|     |          | MAC and MII Bus Relationship               | 125 |

|     |          | Generic PHY Driver Support                 | 125 |

|     |          | Generic TBI Driver Support                 | 126 |

|     | 6.3.2    | VxBus Driver Methods for PHY Drivers       | 126 |

|     |          | Upper Edge Methods                         | 127 |

|     |          | Lower Edge Methods                         | 127 |

|     | 6.3.3    | Header Files for PHY Drivers               | 130 |

|     | 6.3.4    | BSP Configuration for PHY Drivers          | 130 |

|     | 6.3.5    | Available Utility Routines for PHY Drivers | 130 |

|     |          | Upper Edge Utility Routines                | 130 |

|     |          | Lower Edge Utility Routines                | 131 |

|     | 6.3.6    | Initialization for PHY Drivers             | 132 |

|     | 6.3.7    | Debugging PHY Drivers                      | 133 |

| 6.4 | Wirele   | ss Ethernet Drivers                        | 133 |

| 6.5 | Hierar   | chical END Drivers                         | 134 |

|     |          |                                            | 405 |

| Nor | n-volati | le RAM Drivers                             | 135 |

| 7.1 | Introd   | uction                                     | 135 |

|     |          | NVRAM Drivers and TrueFFS                  | 135 |

| 7.2 | Non-V    | olatile RAM Drivers                        | 136 |

7

|     | 7.2.1   | NVRAM Driver Overview                   | 136        |

|-----|---------|-----------------------------------------|------------|

|     | 7.2.2   | VxBus Driver Methods for NVRAM Drivers  | 137        |

|     |         | {nonVolGet}( )                          | 137<br>137 |

|     | 7.2.3   | Header Files                            | 137        |

|     | 7.2.4   | BSP Configuration for NVRAM Drivers     | 138        |

|     | 7.2.5   | Utility Routines for NVRAM Drivers      | 139        |

|     | 7.2.6   | Initialization for NVRAM Drivers        | 139        |

|     | 7.2.7   | NVRAM Block Sizes                       | 139        |

|     | 7.2.8   | Stacking NVRAM Instances                | 140        |

|     | 7.2.9   | Debugging NVRAM Drivers                 | 141        |

| 7.3 | Flash F | ile System Support with TrueFFS         | 141        |

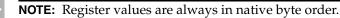

|     | 7.3.1   | TrueFFS Overview                        | 141        |

|     |         | Core Layer                              | 142        |

|     |         | MTD Layer                               | 142        |

|     |         | Socket Layer<br>Flash Translation Layer | 142<br>143 |

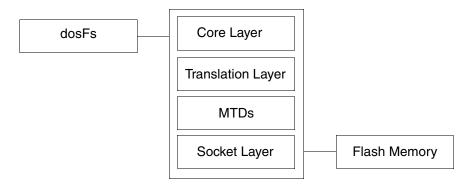

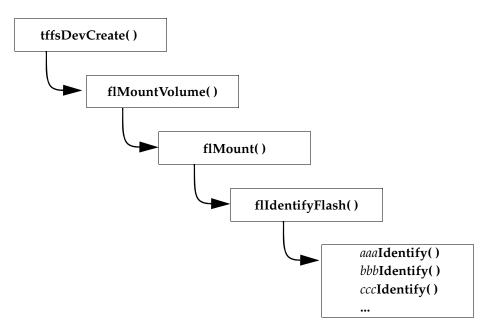

|     | 7.3.2   | TrueFFS Driver Development Process      | 143        |

|     |         | Using MTD-Supported Flash Devices       | 143        |

|     |         | Writing MTD Components                  | 148        |

|     |         | Socket Drivers                          | 157        |

|     |         | Flash Translation Layer                 | 166        |

| Res | ource D | Drivers                                 | 185        |

| 8.1 | Introdu | uction                                  | 185        |

| 8.2 | Overvi  | ew                                      | 186        |

| 8.3 | VxBus   | Driver Methods                          | 186        |

| 8.4 | Header  | r Files                                 | 187        |

| 8.5 | BSP Co  | onfiguration                            | 187        |

8

|   | 8.6 Available Utility Routines |                                                |            |  |  |

|---|--------------------------------|------------------------------------------------|------------|--|--|

|   | 8.7                            | Initialization                                 | 187        |  |  |

|   | 8.8                            | Debugging                                      | 188        |  |  |

| 9 | Seria                          | I Drivers                                      | 189        |  |  |

|   | 9.1                            | Introduction                                   | 190        |  |  |

|   | 9.2                            | Overview                                       | 190        |  |  |

|   | 9.3                            | VxBus Driver Methods                           | 190        |  |  |

|   |                                | 9.3.1 {sioChanGet}()                           | 191        |  |  |

|   |                                | 9.3.2 {sioChanConnect}()                       | 191        |  |  |

|   | 9.4                            | Header Files                                   | <b>192</b> |  |  |

|   | 9.5                            | BSP Configuration                              | 193        |  |  |

|   | 9.6                            | Available Utility Routines                     | 193        |  |  |

|   | 9.7 Initialization             |                                                |            |  |  |

|   | 9.8                            | Polled Mode Versus Interrupt-Driven Mode       | <b>194</b> |  |  |

|   | 9.9                            | SIO_CHAN and SIO_DRV_FUNCS                     | <b>194</b> |  |  |

|   | 9.10                           | WDB                                            | 197        |  |  |

|   |                                | 9.10.1 WDB and Kernel Initialization           | 197        |  |  |

|   | 9.11                           | Serial Drivers, Initialization, and Interrupts | 198        |  |  |

|   |                                | 9.11.1 WDB and Interrupts                      | 198        |  |  |

|   |                                | 9.11.2 Initialization Order and Interrupts     | 199        |  |  |

|   |                                | 9.11.3 Initialization Order                    | 199        |  |  |

|   | 9.12                           | Debugging                                      | 199        |  |  |

| 10 | Stora | Storage Drivers                     |                                                 |     |  |  |

|----|-------|-------------------------------------|-------------------------------------------------|-----|--|--|

|    | 10.1  | Introdu                             | action                                          | 201 |  |  |

|    | 10.2  | Overvi                              | ew                                              | 202 |  |  |

|    | 10.3  | VxBus                               | Driver Methods                                  | 202 |  |  |

|    | 10.4  | Heade                               | Files                                           | 202 |  |  |

|    | 10.5  | BSP Co                              | onfiguration                                    | 203 |  |  |

|    | 10.6  | Availa                              | ole Utility Routines                            | 203 |  |  |

|    |       |                                     | erfHandlerRegister() and erfHandlerUnregister() | 203 |  |  |

|    |       |                                     | erfEventRaise()                                 | 203 |  |  |

|    |       |                                     | xbdAttach()                                     |     |  |  |

|    |       |                                     | bio_done()                                      |     |  |  |

|    | 10.7  | Initiali                            | zation                                          | 204 |  |  |

|    | 10.8  | Interface with VxWorks File Systems |                                                 |     |  |  |

|    |       | 10.8.1                              | Device Creation                                 | 205 |  |  |

|    |       |                                     | ERF Registration                                | 205 |  |  |

|    |       |                                     | Advertisement of XBD Methods                    |     |  |  |

|    |       |                                     | ERF New Device Notification                     | 207 |  |  |

|    |       | 10.8.2                              | Processing                                      | 208 |  |  |

|    |       | 10.8.3                              | Event Reporting                                 | 208 |  |  |

|    | 10.9  | Writing                             | g New Storage Drivers                           | 210 |  |  |

|    | 10.10 | Debug                               | ging                                            | 211 |  |  |

| 11 | Time  | Fimer Drivers 2                     |                                                 |     |  |  |

|    | 11.1  | Introdu                             | action                                          | 214 |  |  |

|    | 11.2  | Overvi                              | ew                                              | 214 |  |  |

|    |       |                                     |                                                 |     |  |  |

|    | 11.3  | VXDUS                               | Driver Methods                                  | 215 |  |  |

|    | 11.4  | Header    | Header Files                   |            |  |  |  |  |

|----|-------|-----------|--------------------------------|------------|--|--|--|--|

|    | 11.5  | BSP Co    | BSP Configuration              |            |  |  |  |  |

|    | 11.6  | Availab   | le Utility Routines            | <b>219</b> |  |  |  |  |

|    | 11.7  | Initializ | zation                         | 219        |  |  |  |  |

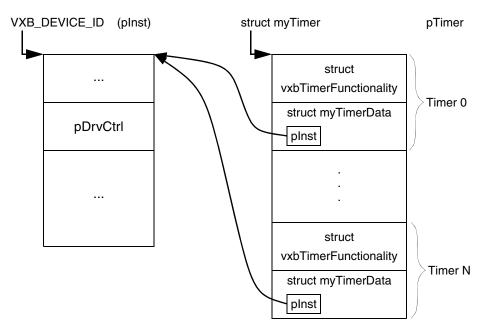

|    | 11.8  | Data St   | ructure Layout                 | 219        |  |  |  |  |

|    | 11.9  | Implem    | enting Driver Service Routines | 221        |  |  |  |  |

|    |       | 11.9.1    | (*timerAllocate)()             | 221        |  |  |  |  |

|    |       | 11.9.2    | (*timerRelease)()              | 222        |  |  |  |  |

|    |       | 11.9.3    | (*timerRolloverGet)()          | 222        |  |  |  |  |

|    |       | 11.9.4    | (*timerCountGet)()             | 223        |  |  |  |  |

|    |       | 11.9.5    | (*timerDisable)()              | 224        |  |  |  |  |

|    |       | 11.9.6    | (*timerEnable)()               | 224        |  |  |  |  |

|    |       | 11.9.7    | (*timerISRSet)()               | 225        |  |  |  |  |

|    |       | 11.9.8    | (*timerEnable64)()             | 226        |  |  |  |  |

|    |       | 11.9.9    | (*timerRolloverGet64)()        | 226        |  |  |  |  |

|    |       | 11.9.10   | (*timerCountGet64)()           | 227        |  |  |  |  |

|    | 11.10 | Integra   | ting a Timer Driver            | 228        |  |  |  |  |

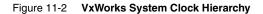

|    |       | 11.10.1   | VxWorks System Clock           | 228        |  |  |  |  |

|    |       | 11.10.2   | VxWorks Auxiliary Clock        | 230        |  |  |  |  |

|    |       | 11.10.3   | VxWorks Timestamp Driver       | 231        |  |  |  |  |

|    | 11.11 | Debugg    | zing                           | 232        |  |  |  |  |

|    | 11.12 | SMP Co    | onsiderations                  | 233        |  |  |  |  |

| 12 | USB   | Drivers   | s                              | 235        |  |  |  |  |

|    | 12.1  | Introdu   | ction                          | 235        |  |  |  |  |

|    | 12.2  | Wind R    | iver USB Overview              | 236        |  |  |  |  |

|      |                                                 | 12.2.1                       | USB Host Stack Drivers       | 236  |

|------|-------------------------------------------------|------------------------------|------------------------------|------|

|      |                                                 |                              | VxBus Model Drivers          |      |

|      |                                                 |                              | Other Host Drivers           |      |

|      |                                                 | 12.2.2                       | USB Peripheral Stack Drivers | 237  |

|      | 12.3 Host Controller and Root Hub Class Drivers |                              |                              | 237  |

|      |                                                 | 12.3.1                       | VxBus Driver Methods         | 238  |

|      |                                                 | 12.3.2                       | Header Files                 | 238  |

|      |                                                 | 12.3.3                       | BSP Configuration            | 238  |

|      |                                                 | 12.3.4                       | Available Utility Routines   | 241  |

|      |                                                 | 12.3.5                       | Initialization               | 241  |

|      |                                                 | 12.3.6                       | Debugging                    | 242  |

| 13   | Other Driver Classes                            |                              |                              | 245  |

|      | 13.1                                            | Introdu                      | iction                       | 245  |

|      |                                                 |                              |                              |      |

|      | 13.2                                            | Overview 2                   |                              |      |

|      | 13.3                                            | VxBus Driver Methods 2       |                              |      |

|      | 13.4                                            | Header Files 2               |                              |      |

|      | 13.5                                            | BSP Configuration 24         |                              |      |

|      | 13.6                                            | Available Utility Routines 2 |                              |      |

|      | 13.7                                            | 7 Initialization             |                              |      |

|      | 13.8                                            | Debug                        | ging                         | 248  |

| Δ    | Glos                                            | earv                         |                              | 2/10 |

| ~    | GIUS                                            | isai y                       |                              | 243  |

| Inde | ех                                              |                              |                              | 253  |

# 1 Class-Specific Driver Development

- 1.1 About VxBus Driver Classes 1

- 1.2 Before You Begin 2

- 1.3 About this Document 2

# 1.1 About VxBus Driver Classes

As explained in *VxWorks Device Driver Developer's Guide* (*Vol.* 1): *Device Driver Fundamentals*, devices, and the drivers that manage them, can be divided into categories or *classes* based on the particular function the device and driver are expected to perform.

For example, even though they are very different devices, a simple VGA controller (typical of older PCs) and a modern display controller running on PCI Express provide the same functionality in a system. That is, both devices are responsible for displaying graphical information on a video device. This makes both of these devices, as well as the drivers that control them, part of the same class.

# 1.2 Before You Begin

This document assumes you are familiar with the concepts presented in *VxWorks Device Driver Developer's Guide, Volume 1: Fundamentals of Writing Device Drivers.* If you are not an experienced VxWorks device driver developer or you do not have experience with the VxBus driver model, you must review the information provided in Volume 1 before using this document.

If you are migrating or maintaining VxWorks device drivers based on the legacy device driver model, see *VxWorks Device Driver Developer's Guide*, *Volume 3: Legacy Drivers and Migration*. This volume does not apply to legacy model device drivers.

# 1.3 About this Document

This document provides information on the driver requirements for specific VxBus driver classes (see 1.1 About VxBus Driver Classes, p.1). The information presented in this document is intended to supplement the information provided in VxWorks Device Driver Developer's Guide, Volume 1: Fundamentals of Writing Device Drivers.

**NOTE:** Concepts and procedures presented in Volume 1 apply to class-specific VxBus model device drivers in general, regardless of class.

#### Navigating this Documentation Set

For information on navigating this documentation set, documentation conventions, and other available documentation resources, see *VxWorks Device Driver Developer's Guide (Vol. 1): Getting Started with Device Driver Development.*

# 2 Bus Controller Drivers

- 2.1 Introduction 3

- 2.2 Overview 4

- 2.3 VxBus Driver Methods 5

- 2.4 Header Files 17

- 2.5 BSP Configuration 17

- 2.6 Available Utility Routines 20

- 2.7 **Initialization 23**

- 2.8 Debugging 26

# 2.1 Introduction

This chapter describes VxBus bus controller drivers. This chapter assumes that you are familiar with the contents of the *VxWorks Device Driver Developer's Guide*, Volume 1: Fundamentals of Writing Device Drivers, which discusses generic driver concepts as well as details of VxBus that are not specific to any driver class.

### 2.2 Overview

Bus controller drivers provide the support services that are required to enable other drivers attached to downstream devices to communicate with their associated hardware in a uniform way. Functionally, a bus controller driver acts as an abstraction layer between a device driver and the hardware that it controls, ensuring that the I/O operations that need to occur between the driver and its device occur correctly on the target hardware.

In addition, a bus controller driver provides support services to VxBus, allowing VxBus to configure the bus for proper operation, discover devices on the bus, and perform other operations that are outside the scope of normal communication that occurs between a driver and its target hardware.

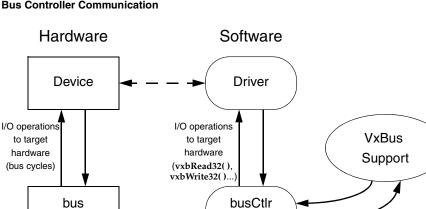

Graphically, a bus controller can be viewed as an interconnect between a driver and its target hardware, and another interconnect between VxBus and the bus being controlled. Figure 2-1 illustrates this communication.

All systems must have at least one bus controller driver. This is because even devices that are directly connected to a CPU must have a parent bus controller. The top-level bus controller is referred to as the processor local bus (PLB) bus controller.

From the PLB, subordinate bus controllers are often available to connect the CPU to devices that are not local to the CPU itself. An example of this is a PCI bus controller located on the PLB bus, which serves as a bridge between the PLB hardware and the PCI bus hardware. The PCI bus controller driver allows the CPU to access the downstream device.

Within VxBus, bus controller drivers are treated like standard drivers in most ways. However, there is a fundamental difference between bus controller drivers and standard drivers; standard drivers typically provide a service to the operating system or to middleware, while bus controller drivers provide a service to other drivers.

Bus controller drivers are relatively complex when compared with other drivers within VxWorks. While the text in this chapter provides information that is necessary in order to successfully develop a driver, you should also refer to the existing bus controller drivers, located in

*installDir*/**vxworks-6**.*x***/target/src/hwif/busCtlr**, to see actual implementations and to understand how bus controller drivers interact with VxWorks.

Driver

Figure 2-1 **Bus Controller Communication**

to target

hardware

controller

CPU

Bus (PCI, PLB, ...

# 2.3 VxBus Driver Methods

Bus controller drivers use a variety of different driver methods, depending on the type of bus that is being controlled by the driver. In this release, the majority of methods are designed for use with either the PLB or PCI bus types. Each driver method listed in this section lists the bus types that the method is designed to support. Each section also notes if support for the given driver method is optional.

Controller operations to target hardware

#### 2.3.1 {busCtlrCfgRead}()

The **{busCtlrCfgRead}()** method is used to read 8, 16, or 32-byte quantities from the configuration space of the bus. Currently, this method is used exclusively on the PCI bus by the PCI bus support code.

Within a bus controller driver, the {**busCtlrCfgRead**}() method is implemented using a driver-provided routine with the following prototype:

```

LOCAL STATUS func{busCtlrCfgRead}

(

VXB_DEVICE_ID pInst, /* device info */

int bus, /* bus number */

int dev, /* device number */

int func, /* function number */

UINT32 byteOffset, /* offset into config space */

UINT32 transactionSize,/* transaction size, in bytes */

char * pDstBuf, /* buffer to write to */

UINT32 * pFlags /* flags */

```

The parameters to func{busCtlrCfgRead}() are:

#### pInst

The VXB\_DEVICE\_ID for the bus controller instance.

#### bus

The PCI bus number of the target hardware

#### dev

The PCI device number of the target hardware

#### func

The PCI function number of the target hardware

#### byteOffset

The offset into the configuration space where the read is performed. Because non-aligned configuration accesses are not allowed, **byteOffset** must be an even multiple of the transaction size.

#### transactionSize

The data size to read, in bits. Valid values are 8, 16, and 32.

#### pDstBuf

A pointer to the buffer used to store the value read from configuration space.

#### pFlags

Reserved.

The **func{busCtlrCfgRead}()** routine performs whatever device-specific operations are required to perform the requested read operation from the bus configuration space.

#### 2.3.2 {busCtlrCfgWrite}()

The {**busCtlrCfgWrite**}() method is used to write 8, 16, or 32-byte quantities to the configuration space of the bus. Currently, this method is used exclusively on the PCI bus by the PCI bus support code.

Within a bus controller driver, the {**busCtlrCfgWrite**}() method is implemented using a driver-provided routine with the following prototype:

```

LOCAL STATUS func{busCtlrCfgWrite}

(

VXB_DEVICE_ID pInst, /* device info */

int bus, /* bus number */

int dev, /* device number */

int func, /* function number */

UINT32 byteOffset, /* offset into config space */

UINT32 transactionSize,/* transaction size, in bytes */

char * pSrcBuf, /* buffer to read from */

UINT32 * pFlags /* flags */

```

The parameters to func{busCtlrCfgWrite}() are:

#### pInst

The VXB\_DEVICE\_ID for the bus controller instance.

#### bus

The PCI bus number of the target hardware

#### dev

The PCI device number of the target hardware

#### func

The PCI function number of the target hardware

#### byteOffset

The offset into the configuration space where the write is performed. Because non-aligned configuration accesses are not allowed, **byteOffset** must be an even multiple of the transaction size.

#### transactionSize

The data size to write, in bits. Valid values are 8, 16, and 32.

#### pSrcBuf

A pointer to the data that will be written to configuration space.

pFlags

Reserved.

The **func{busCtlrCfgWrite}()** routine performs whatever device-specific operations are required to perform the requested write operation to the bus configuration space.

#### 2.3.3 {busCtlrAccessOverride}()

When a bus controller is installed into VxWorks, some service routines are automatically associated with the bus controller, and are made available to device drivers for devices that reside on the bus. These default service routines are not always appropriate for the installed bus. Therefore, you may wish to provide alternate implementations of the services in your bus controller driver. The {**busCtlrAccessOverride**}() method provides your bus controller driver with a means of overriding selected service routines.

Within a bus controller driver, the {**busCtlrAccessOverride**}() method is implemented using a driver-provided routine with the following prototype:

```

LOCAL STATUS func{busCtlrAccessOverride}()

(

VXB_DEVICE_ID pInst, /* device info */

VXB_ACCESS_LIST * pAccess /* access structure pointer */

```

A pointer to the VXB\_ACCESS\_LIST data structure is passed to the method. This allows the bus controller driver to replace any of the function pointers that are contained within this data structure with alternate implementations. VXB\_ACCESS\_LIST is declared in

installDir/vxworks-6.x/target/src/hwif/h/vxbus/vxbAccess.h.

Although VXB\_ACCESS\_LIST contains a large collection of function pointers, only three of the function pointers should be modified by the bus controller driver. These pointers are (\*busCfgRead)(), (\*busCfgWrite)(), and (\*vxbDevControl)(). Other fields are considered reserved fields and must be left unchanged by this method. The remainder of this section discusses the fields that can be overridden, reserved fields are not discussed.

#### Override for (\*busCfgRead)()

The prototype for (\*busCfgRead)() is:

This routine reads from the bus configuration space. It is used by drivers for devices that reside directly on the bus that is being controlled by the bus controller driver. The [*bus, device, function*] tuple is not provided directly. Instead, this tuple must be extracted by de-referencing the instance-specific data available using **devID**.

#### Override for (\*busCfgWrite)()

```

The prototype for (*busCfgWrite)() is:

```

This routine writes to the bus configuration space. It is used by drivers for devices that reside directly on the bus that is being controlled by the bus controller driver. The [*bus, device, function*] tuple is not provided directly. Instead, this tuple must be extracted by de-referencing the instance-specific data available using **devID**.

#### Override for (\*vxbDevControl)()

This routine provides a service similar to an **ioctl()**, allowing specialized control requests to be delivered to a bus controller driver. In previous releases of VxBus, this routine is used for interrupt management and for device register access. With VxBus version 3, these functions are provided by other modules. Because of this, the (**\*vxbDevControl)()** routine is no longer required, provided that VxBus interrupt controller drivers are used to manage interrupts.

#### The prototype for (\*vxbDevControl)() is:

```

STATUS (*vxbDevControl)

(

VXB_DEVICE_ID devID, /* device info */

pVXB_DEVCTL_HDR pBusDevControl /* parameter */

);

```

VxBus version 3 simplified the method used for register access. Because of this change, you do not need to provide support for register access routines in your bus controller driver unless some part of bus controller driver code needs to be executed in order to perform the register operation. For more information on this register access, see 2.3.6 {vxbDevRegMap}(), p.11.

In past releases, the (\*vxbDevControl)() routine was used to allow a bus controller driver to support the configuration of interrupts for devices on the bus being controlled. This service was in keeping with the design goals for bus controller drivers for several releases of VxWorks. However, in this release, bus controller drivers are not responsible for interrupt management for their subordinate devices. Instead, the responsibility for this type of operation has been migrated to interrupt controller drivers (see 4. Interrupt Controller Drivers).

#### 2.3.4 {busCtlrCfgInfo}()

VxBus provides a utility library that bus controller drivers can use to support the generation of configuration transactions on the target bus. The utility library makes use of an instance-specific data structure to accomplish its operations. The {busCtlrCfgInfo}() method provides a way for your bus controller driver to export a pointer to this data structure so that the utility library can make use of it.

Within a bus controller driver, the {**busCtlrCfgInfo**}() method is implemented using a driver-provided routine with the following prototype:

```

LOCAL STATUS {busCtlrCfgInfo}()

(

VXB_DEVICE_ID pInst, /* device info */

char * pArgs /* buffer to write to */

)

```

The implementation of {**busCtlrCfgInfo**}() is straightforward. The bus controller driver simply returns a pointer to a bus-type specific information structure. For example, see the following PCI code:

\*(struct vxbPciConfig \*) pArgs = pInst->pDrvCtrl->pPciConfig;

In this example, the bus controller driver has already allocated the **vxbPciConfig** data structure and stored a pointer to it in its **pDrvCtrl** data area. (For further

details about the use of the **vxbPciConfig** data structure, see 2.6.1 PCI Configuration, p.20.)

#### 2.3.5 {busCtlrBaseAddrCvt}()

The {**busCtlrBaseAddrCvt**}() method gives a bus controller driver the opportunity to modify the address of a bus transaction to account for address space differences that happen through the bus controller. At present, only PCI bus controllers use this service.

Within a bus controller driver, the {**busCtlrBaseAddrCvt**}() method is implemented using a driver-provided routine with the following prototype:

```

LOCAL STATUS func{busCtlrBaseAddrCvt}

(

VXB_DEVICE_ID devID, /* device info */

UINT32 * pBaseAddr /* pointer to base address */

)

```

The PCI bus is a memory-mapped bus, with the bus controller acting as an arbiter to forward memory transactions from the originating CPU across the bus so that they are delivered to the target hardware on the bus. When this forwarding occurs, it is common for some type of address translation to take place as the requested transaction crosses the PCI bus controller. The {**busCtlrBaseAddrCvt}()** method gives the PCI bus controller driver the ability to describe the address translation that takes place.

The **pBaseAddr** pointer that is passed to the method is both an input and an output parameter. On input, it contains a value from one of the base address registers (BARs) of a device on the PCI bus. The driver should modify this value so that it contains a pointer that, when de-referenced, properly points to the location in the CPU address space where the target device is mapped.

#### 2.3.6 {vxbDevRegMap}()

Device drivers use a standard set of routines to read and write to device registers. (This is described in *VxWorks Device Driver Developer's Guide* (*Vol. 1*): *Device Driver Fundamentals*.) The standard routines are:

- vxbRead8()

- vxbRead16()

- vxbRead32()

- vxbRead64()

- vxbWrite8()

- vxbWrite16()

- vxbWrite32()

- vxbWrite64()

**NOTE:** In the remainder of this section, these routines as referred to as **vxbRead**\*() and **vxbWrite**\*().

Unless an alternate implementation is explicitly specified by the bus controller driver, a default implementation for each of these routines is used.

The {vxbDevRegMap}() method is used by a bus controller driver when the driver needs to override the implementation for the various vxbRead\*() and vxbWrite\*() register access routines. Within a bus controller driver, the {vxbDevRegMap}() method is implemented using a driver-provided routine with the following prototype:

```

LOCAL STATUS func{vxbDevRegMap){}

(

VXB_DEVICE_ID pInst, /* bus controller instance */

VXB_DEVICE_ID pChild, /* instance for child of this controller */

int index, /* index into pChild->regBase[] */

void ** pHandle // buffer to store handle */

)

```

For each supported processor architecture family, the **vxbRead**\*() and **vxbWrite**\*() routines support six predefined transaction types as follows:

- memory mapped access (no ordering enforced)

- memory mapped access (ordering enforced)

- I/O space access (ordering implied)

- byte swapped memory mapped access (no ordering enforced)

- byte swapped memory mapped access (ordering enforced)

- byte swapped I/O space access (ordering implied)

When a device driver maps in a portion of its address space by calling **vxbRegMap()**, the routine checks to see if the parent bus controller associated with the driver instance supports the {**vxbDevRegMap**}() method. If the bus controller supports this method, **vxbRegMap()** invokes the bus controller method. If this method is not provided by the bus controller driver, **vxbRegMap()** provides a reasonable default implementation for the access routine. The default implementation that is chosen is dependent on the target architecture.

The bus controller method {**vxbDevRegMap**}() is responsible for creating a *handle* to describe the type of transaction to be performed when the driver makes subsequent calls to any of the **vxbRead**\*() or **vxbWrite**\*() routines.

There are two scenarios that the bus controller driver must deal with when implementing this method:

- One of the six predefined transaction types can be used. In this case, the bus controller driver only specifies which transaction type to employ.

- None of the six predefined transaction types can be used. In this case, the bus controller driver provides its own implementation of the service.

Regardless of the scenario, the bus controller is responsible for creating a handle that accurately describes the transaction type that is required to support the underlying hardware.

The handle value that is provided to the **vxbRead**\*() and **vxbWrite**\*() routines is used as an opaque value by the individual device drivers, but a bus controller driver must understand exactly how the handle is used to control the type of transaction that is performed using the **vxbRead**\*() or **vxbWrite**\*() routines. In a typical situation, the handle is treated as a **void** \* data type. Because VxWorks is a 32-bit operating system, the handle is encoded using 32-bits. If the 32 bits of the handle are cast to a **UINT32** data type, the integer value of the handle can be inspected to determine the type of transaction to perform. The available options are:

- If the handle is arithmetically less than the value 256, the handle directly encodes one of the six predefined transaction types.

- If handle is arithmetically greater than the value 256, the handle is interpreted as a pointer to a bus controller routine that is used to implement the transaction.

These two forms of support are discussed in the following sections.

#### Specifying a Predefined Transaction Type

If a bus controller driver does not provide an implementation for {vxbDevRegMap}(), a default transaction type for the eight vxbRead\*() and vxbWrite\*() routines is provided as shown in Table 2-1.

#### Table 2-1 Available Transaction Types

| Architecture               | I/O Space                  | Memory Space               |

|----------------------------|----------------------------|----------------------------|

| PowerPC                    | I/O access                 | Ordered memory access      |

| All others (little-endian) | I/O access                 | Memory access              |

| All others (big-endian)    | Byte-swapped I/O<br>access | Byte-swapped memory access |

These defaults suffice for the majority of target platforms. When these defaults are not appropriate, the bus controller must implement the {**vxbDevRegMap**}() method in order to override the default access model.

If the bus controller provides the {vxbDevRegMap}() method, this method is invoked by the vxbRegMap() utility routine whenever a device driver residing on the controlled bus invokes vxbRegMap().vxbRegMap() finds the bus controller instance, and calls the func{vxbDevRegMap}() routine using the parameter list described in the routine prototype. The index parameter passed to the method is the index into the device regBase[]. Within func{vxbDevRegMap}(), the driver must determine, based on the register window being mapped by the driver, which of the six predefined transaction types to select for access into that register window. Based on the desired access, func{vxbDevRegMap}() creates a handle value that describes the requested access type as shown in Table 2-2.

#### Table 2-2 Handle Values for Access Types

| Type of Access                   | Value for Handle                    |

|----------------------------------|-------------------------------------|

| Memory access                    | VXB_HANDLE_MEM                      |

| Ordered memory access            | VXB_HANDLE_ORDERED                  |

| I/O access                       | VXB_HANDLE_IO                       |

| Byte-swapped memory access       | VXB_HANDLE_SWAP(VXB_HANDLE_MEM)     |

| Byte-swapped order memory access | VXB_HANDLE_SWAP(VXB_HANDLE_ORDERED) |

| Byte-swapped I/O access          | VXB_HANDLE_SWAP(VXB_HANDLE_IO)      |

The preprocessor macros that are used to create the handle values are found in *installDir/*vxworks-6.*x*/target/src/hwif/h/vxbus/vxbAccess.h.

For example, if you want **func{vxbDevRegMap}()** to perform strictly ordered memory accesses for all memory regions, and simple I/O operations for all I/O regions, you can implement the following code:

```

if (pChild->regBaseFlags[index] == VXB_REG_MEM)

*pHandle = (void *) VXB_HANDLE_ORDERED;

else

*pHandle = (void *) VXB_HANDLE_IO;

```

And if you need the same condition, but with the data values swapped for a big-endian processor, you can implement the following code:

```

if (pChild->regBaseFlags[index] == VXB_REG_MEM)

*pHandle = (void *) VXB_HANDLE_SWAP(VXB_HANDLE_ORDERED);

else

*pHandle = (void *) VXB_HANDLE_SWAP(VXB_HANDLE_IO);

```

**NOTE:** If your bus controller driver advertises a **func{vxbDevRegMap}()** routine, it must return a correct handle value every time it is called. There is no way for this method to return a handle for only a subset of the device register windows.

#### Providing a New Transaction Type

For some processor architectures, none of the six predefined transaction types work correctly. For example, a hardware architecture that uses keyhole memory cannot be supported by any of the six predefined transaction types. In this situation, your bus controller driver must implement its own access routine, and provide a pointer to that access routine to its subordinate driver instances. When these driver instances perform I/O operations to the target hardware using any of the **vxbRead\*()** or **vxbWrite\*()** routines, a callback is made to the routine provided by the bus controller driver, and this callback routine implements the request.

If your bus controller driver needs to provide a custom access routine, return a pointer to the driver access routine using the **\*pHandle** parameter passed to **func{vxbDevRegMap}()**. For example:

```

if (index == KEYHOLE_MEMORY_SPACE)

*pHandle = (void *) driverAccessFunc;

else

*pHandle = VXB_HANDLE_MEM;

```

The bus controller access routine has the following prototype:

```

LOCAL VOID driverAccessFunc

(

int iodesc, /* a descriptor for the requested IO operation */

void * pBuf, /* pointer to buffer to read to or write from */

UINT8 * offset /* offset into the address space */

)

```

The **driverAccessFunc()** routine must be implemented to handle both read and write transactions, with bus widths of 8, 16, and 32 bits. If the bus supports 64-bit transactions, this routine must support 64-bit read and write transactions.

The **iodesc** parameter encodes the I/O operation to be performed. This parameter is broken apart into the **read/write** and **width** parameters using the following macros from *installDir/***vxworks-6**.*x***/target/src/hwif/h/vxbus/vxbAccess.h**:

- VXB\_HANDLE\_OP(iodesc)—indicates whether it is a read operation or a write operation.

- VXB\_HANDLE\_WIDTH(iodesc)—indicates the size to read or write, in bytes.

VXB\_HANDLE\_OP() can be used as follows:

```

If ( VXB_HANDLE_OP(iodesc) == VXB_HANDLE_OP_READ )

{

/* this is a read operation */

...

}

else if ( VXB_HANDLE_OP(iodesc) == VXB_HANDLE_OP_WRITE )

{

/* this is a write operation */

...

}

```

Once the transaction direction (read or write) and transaction width (1, 2, 4, or 8 bytes) is determined, **driverAccessFunc()** performs whatever operations are required to complete the requested operation.

**NOTE:** Device drivers can perform the various **vxbRead**\*() or **vxbWrite**\*() operations while holding a spinlock. Because nesting of spinlocks is prohibited, **driverAccessFunc()** cannot use spinlocks in its implementation.

#### 2.3.7 {vxbIntDynaVecProgram}()

Provides support for dynamic interrupt vector assignment.

```

STATUS func{vxbIntDynaVecProgram}

(

VXB_DEVICE_ID instID,

struct vxbIntDynaVecInfo * dynaVec

)

```

For more information on dynamic vectors, see *Programming Dynamic Vectors*, p.64.

# 2.4 Header Files

The following header files are typically used for all bus controller drivers:

```

#include <vxBusLib.h>

#include <hwif/vxbus/vxBus.h>

#include <hwif/vxbus/vxbPlbLib.h>

#include <hwif/vxbus/hwConf.h>

#include <hwif/util/hwMemLib.h>

#include "../h/vxbus/vxbAccess.h"

```

The following additional header files are used for PCI bus controller drivers:

#include <hwif/vxbus/vxbPciLib.h>

#include <drv/pci/pciConfigLib.h>

#include <drv/pci/pciAutoConfigLib.h>

#include <drv/pci/pciIntLib.h>

## 2.5 **BSP Configuration**

A general-purpose bus controller driver must obtain a substantial amount of information from the BSP before it can function correctly. This section describes the configuration fields that are expected by bus controller drivers.

The BSP configuration for a bus controller driver tends to be highly tailored to the needs of the particular bus controller in question. After several bus controller drivers have been developed for a particular bus type, common configuration

parameters become evident. At present, the majority of configuration parameters that are used for more than one bus controller driver are those that are used to configure the PCI bus. Table 2-3 lists the commonly used resources for the PCI bus along with a brief description of the resource. For more complete information about a particular resource, refer to the existing bus controller device drivers provided by Wind River.

| Туре         | Name        | Description                                                     |

|--------------|-------------|-----------------------------------------------------------------|

| HCF_RES_ADDR | mem32Addr   | Specifies the 32-bit pre-fetchable memory pool base address.    |

| HCF_RES_INT  | mem32Size   | Specifies the 32-bit pre-fetchable memory pool size.            |

| HCF_RES_ADDR | memIo32Addr | Specifies the 32-bit non-prefetchable memory pool base address. |

| HCF_RES_INT  | memIo32Size | Specifies the 32-bit non-prefetchable memory pool size.         |

| HCF_RES_ADDR | io32Addr    | Specifies the 32-bit I/O pool base address.                     |

| HCF_RES_INT  | io32Size    | Specifies the 32-bit I/O pool size.                             |

| HCF_RES_ADDR | io16Addr    | Specifies the 16-bit I/O pool base address.                     |

| HCF_RES_INT  | pciIo16Size | Specifies the 16-bit I/O pool size.                             |

#### Table 2-3 Common Resources for a PCI Bus

Individual bus controller drivers may define additional fields that are useful for the particular hardware. The resources that are defined by a particular bus controller driver are, by definition, tailored to the unique needs of the particular hardware.

#### 2.5.1 PCI Configuration

In order to support the generation of PCI configuration cycles according to the PCI specification, a utility library is available to bus controller drivers. This library is located in *installDir/*vxworks-6.x/target/src/hwif/vxbus/vxPci.c.

The choice of configuration method to use (method 0, method 1, or method 2) is often made configurable in the driver, so that a BSP can specify the configuration method (and perhaps also the correct addresses for the configuration registers used by these methods). If you want your bus controller driver to allow the BSP to choose the method to be used for the generation of PCI configuration cycles, be sure your driver exports the resource listed in Table 2-4.

#### Table 2-4 Configuration Resources for PCI Bus

| Туре        | Name               | Description              |

|-------------|--------------------|--------------------------|

| HCF_RES_INT | pciConfigMechanism | A value between 0 and 2. |

#### 2.5.2 PCI Autoconfiguration

PCI bus controllers often use the PCI autoconfiguration services that are included with VxWorks. If a bus controller driver uses this service, the related BSP must ensure that the resources required to support PCI autoconfiguration are defined in the BSP **hwconf.c** file. The following resources are used directly by **vxbPciAutoConfig()**:

| autoIntRouteSet         | io16Addr         | maxLatencyFuncSet |

|-------------------------|------------------|-------------------|

| bridgePostConfigFuncSet | io16Size         | mem32Addr         |

| bridgePreConfigFuncSet  | io32Addr         | mem32Size         |

| cacheSize               | io32Size         | memIo32Addr       |

| fbbEnable               | maxBusSet        | memIo32Size       |

| includeFuncSet          | maxLatAllSet     | msgLogSet         |

| intAssignFuncSet        | maxLatencyArgSet | rollcallFuncSet   |

In most cases, the bus controller does not need to manipulate these resources directly.

For details about the semantics of each of the PCI autoconfiguration resource, see the reference entry for **vxbPciAutoConfig()**.

# 2.6 Available Utility Routines

The various utility services available to bus controller drivers are described in this section. The majority of the support described in this section is for PCI bus controller drivers, because this is the most prevalent bus type used in devices today.

#### 2.6.1 PCI Configuration

A utility library is available to bus controller drivers to support the generation of PCI configuration cycles according to the PCI specification. The utility library is located in *installDir/vxworks-6.x/target/src/hwif/vxbus/vxPci.c*. To initialize the library, the bus controller driver must call vxbPciConfigLibInit(). The prototype for vxbPciConfigLibInit() is as follows:

```

STATUS vxbPciConfigLibInit

(

struct vxbPciConfig *pPciConfig,

int    pciConfAddr0,  /* used by method 1 & method 2 */

int    pciConfAddr1,  /* used by method 1 & method 2 */

int    pciConfAddr2,  /* used by method 2 only */

int    pciConfigMech,  /* 1=method-1, 2=method-2 */

int    pciMaxBus    /* Max number of sub-busses */

)

```

vxbPciConfigLibInit() initializes the memory pointed to by pPciConfig, so that this data structure can be used by the utility library when the utility library generates PCI configuration cycles. The bus controller driver is responsible for allocating the memory area used to store this data structure. After this data structure is initialized, the utility library can invoke the driver {busCtlrCfgInfo}() method in order to retrieve the pointer to the data structure.

VxBus utility services that perform PCI autoconfiguration expect to be able to use PCI configuration utility services to perform the required configuration cycles. If PCI autoconfiguration is supported by the bus controller driver, the PCI configuration library must be properly initialized before autoconfiguration is performed.

For further details on the use of the PCI configuration library, see the reference entry for **vxbPci**.

### 2.6.2 PCI Autoconfiguration

On some hardware platforms, the devices that are available on the PCI bus are initialized before VxWorks begins operation. In other environments, device configuration is performed by VxWorks. Bus controller drivers for the PCI bus should support the configuration of the devices on the bus, unless they will only be executed in hardware environments where the PCI bus is configured before VxWorks starts.

The interface to PCI autoconfiguration is straightforward, consisting of only a single call to **vxbPciAutoConfig()**. The prototype for **vxbPciAutoConfig()** is:

```

STATUS vxbPciAutoConfig

(

VXB_DEVICE_ID busCtrlID

)

```

The simplicity of this interface hides a great deal of configurability and complexity. As seen in 2.5.2 *PCI Autoconfiguration*, p. 19, PCI autoconfiguration requires a large number of configuration resources from the BSP. As such, many of the configuration requirements for PCI autoconfiguration are BSP requirements instead of bus controller driver requirements. If a bus controller driver makes use of PCI autoconfiguration, this creates an implicit dependency on the resources that PCI autoconfiguration requires.

### 2.6.3 vxbBusAnnounce()

Each bus controller driver must inform VxBus that there is a bus downstream from it. This must occur early in the initialization process, typically during phase 1 initialization immediately after it allocates and initializes the per-driver data structures that it wants to maintain. The call to make VxBus aware of the downstream bus is **vxbBusAnnounce()**. The prototype for **vxbBusAnnounce()** is:

```

STATUS vxbBusAnnounce

(

VXB_DEVICE_ID pBusDev, /* bus controller */

UINT32 busID /* bus type */

)

```

The **pBusDev** parameter refers to the bus controller instance, and is provided to the initialization routine that invokes **vxbBusAnnounce()**. The second parameter (**busID**) identifies the type of bus being announced. Table 2-5 lists the available macros and their descriptions.

Table 2-5 Bus Type Macros

| Name              | Description                       |

|-------------------|-----------------------------------|

| VXB_BUSID_PLB     | Processor Local Bus               |

| VXB_BUSID_PCI     | PCI                               |

| VXB_BUSID_RAPIDIO | RapidIO                           |

| VXB_BUSID_MII     | Media Independent Interface (MII) |

| VXB_BUSID_VIRTUAL | virtual bus                       |

The list of supported bus types is likely to increase in future releases. For a complete list of the available bus types, refer to the **BUSID** definitions found in *installDir/***vxworks-6.***x***/target/h/hwif/vxbus/vxBus.h**.

### 2.6.4 vxbPciBusTypeInit()

Once a PCI bus is configured so that subordinate devices on the bus are visible, each bus controller driver must call **vxbPciBusTypeInit()**, to allow VxBus to perform any required connection operations to associate the discovered devices with their bus controller. The prototype for **vxbPciBusTypeInit()** is:

```

STATUS vxbPciBusTypeInit

(

VXB_DEVICE_ID pBusDev

)

```

The **pBusDev** parameter refers to the bus controller instance, and is provided to the initialization routine that invokes **vxbPciBusTypeInit()**.

### 2.6.5 vxbPciDeviceAnnounce()

Once **vxbPciBusTypeInit()** is invoked, the bus controller driver invokes **vxbPciDeviceAnnounce()** in order to make the discovered devices on the bus visible to VxBus. The prototype for **vxbPciDeviceAnnounce()** is:

```

STATUS vxbPciDeviceAnnounce

(

VXB_DEVICE_ID pBusDev

)

```

The **pBusDev** parameter refers to the bus controller instance, and is provided to the initialization routine that invokes **vxbPciDeviceAnnounce()**.

# 2.7 Initialization

The initialization steps for a bus controller are similar, but not identical, to the initialization steps that occur for other drivers. This section discusses the various steps in the initialization of a bus controller driver.

Bus controller drivers must register themselves with VxBus during the boot process, as is the case with all VxBus drivers. The primary difference between bus controller drivers and other drivers is that bus controller drivers describe themselves differently in their **vxbDevRegInfo** initialization structure. Whereas most drivers declare themselves as being of type **VXB\_DEVID\_DEVICE**, bus controllers describe themselves as **VXB\_DEVID\_BUSCTRL**.

As with service drivers (see *A. Glossary*), bus controller drivers are initialized in three distinct phases. Typically, bus controller drivers are initialized during system boot. However, during early development, you may choose to delay the initialization of a bus controller driver until after the system is running. This provides a more robust debugging environment during bus controller driver development. When debugging is complete, be sure to restore your driver initialization to the earliest possible initialization phase. For more information, see 2.8 Debugging, p.26.

The initialization of a bus controller can be thought of in terms of a driver's internal requirements, and of external requirements that are imposed on the driver by the VxBus bus controller driver model. Internal requirements are operations that the bus controller needs to perform in order to create a suitable run-time environment for itself. This typically includes:

- Allocating memory to hold per-instance data structures, and initializing them

according to the driver's unique requirements.

- Reading in resource information from the environment, and programming the bus controller hardware to reflect the desired configuration.

- Initializing utility libraries that the bus controller driver will put to subsequent use within the driver.

Note that this list is not meant to be exhaustive. In some cases, device drivers will have unique requirements that occur along with the above examples.

In addition to the internal requirements of the bus controller driver, bus controller drivers have additional requirements in the way that they connect themselves to VxBus. This includes:

- Announcing the availability of the bus to VxBus.

- Scanning the bus (where possible), in order to find devices that are available on the bus, so that they can be paired with drivers to form additional instances.

- Performing bus-type specific operations, such as announcing the availability of a new PCI bus to VxBus.

VxWorks provides utility routines that help to provide support for a PCI bus. More specifically, utility services are provided to support PCI bus configuration. For more information on these utility services, see 2.6 *Available Utility Routines*, p.20.

### 2.7.1 Initialization Example

While each bus controller driver may have unique initialization requirements, most requirements fall broadly into the steps outlined in this section.

For this example, the following steps are taken from the **g64120aPci.c** bus controller:

1. Allocate the per-instance data area used by the driver.

pDrvCtrl = hwMemAlloc (sizeof(\*pDrvCtrl));

2. Query required resources from the BSP, and store them locally.

/\* etc. \*/