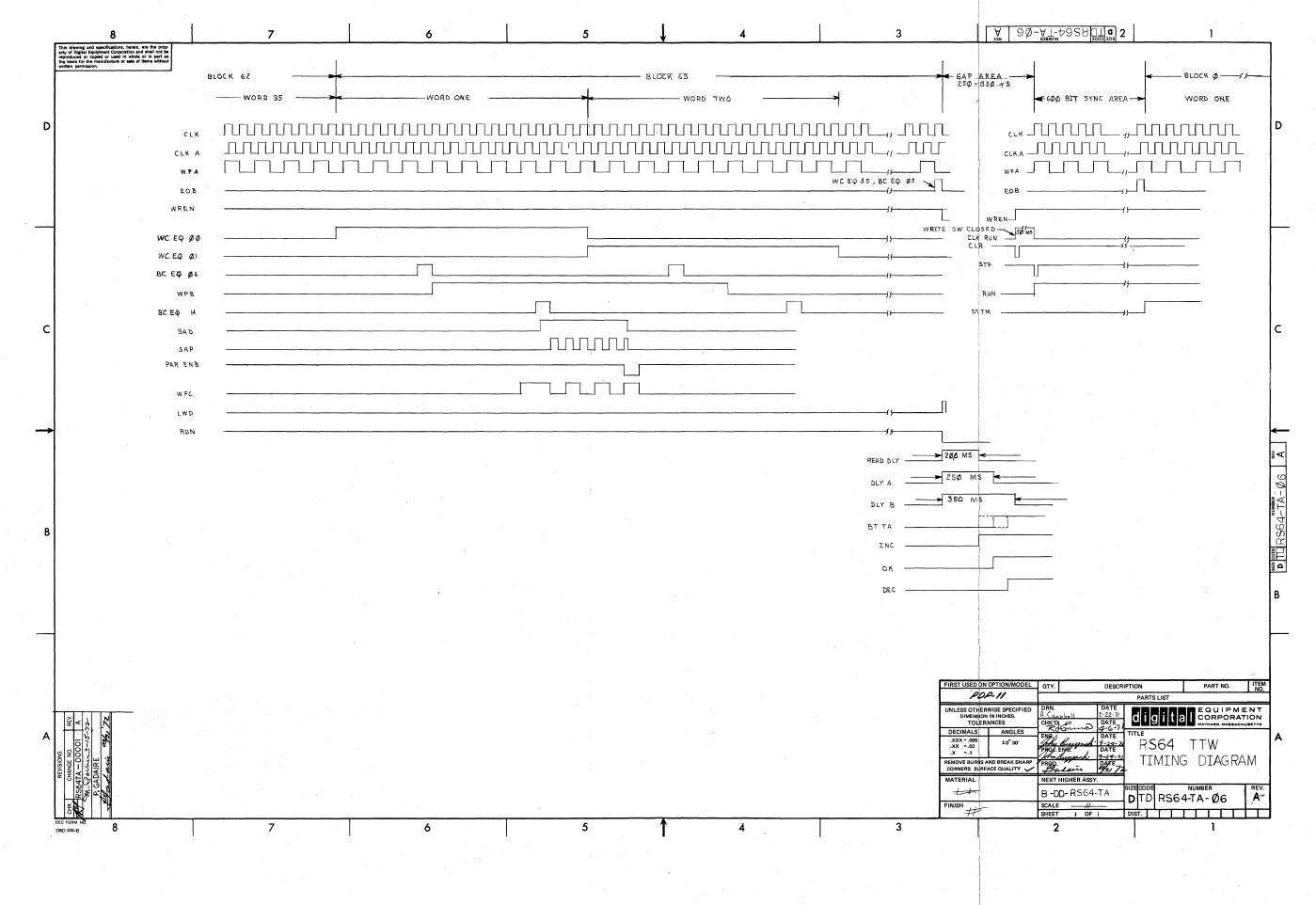

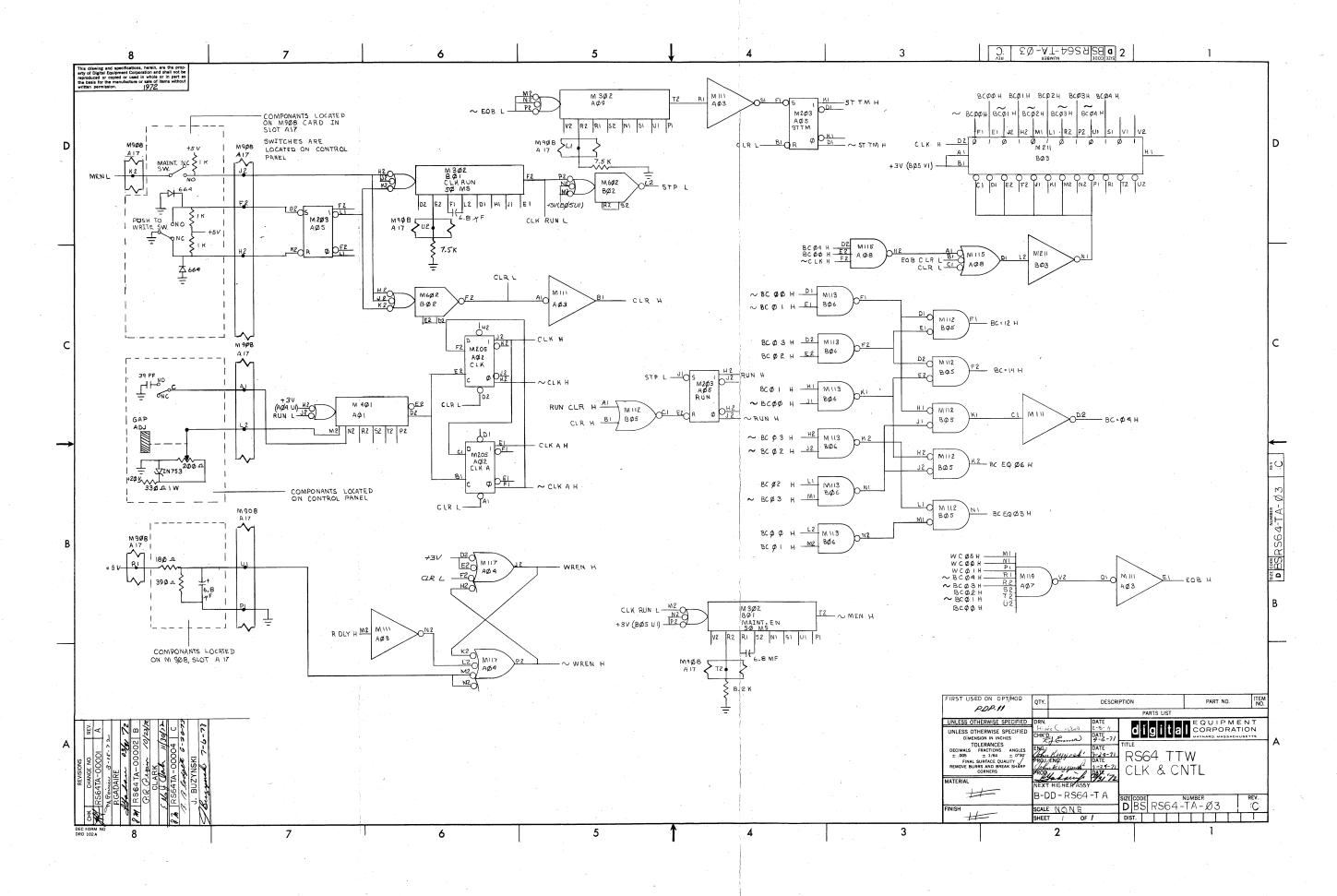

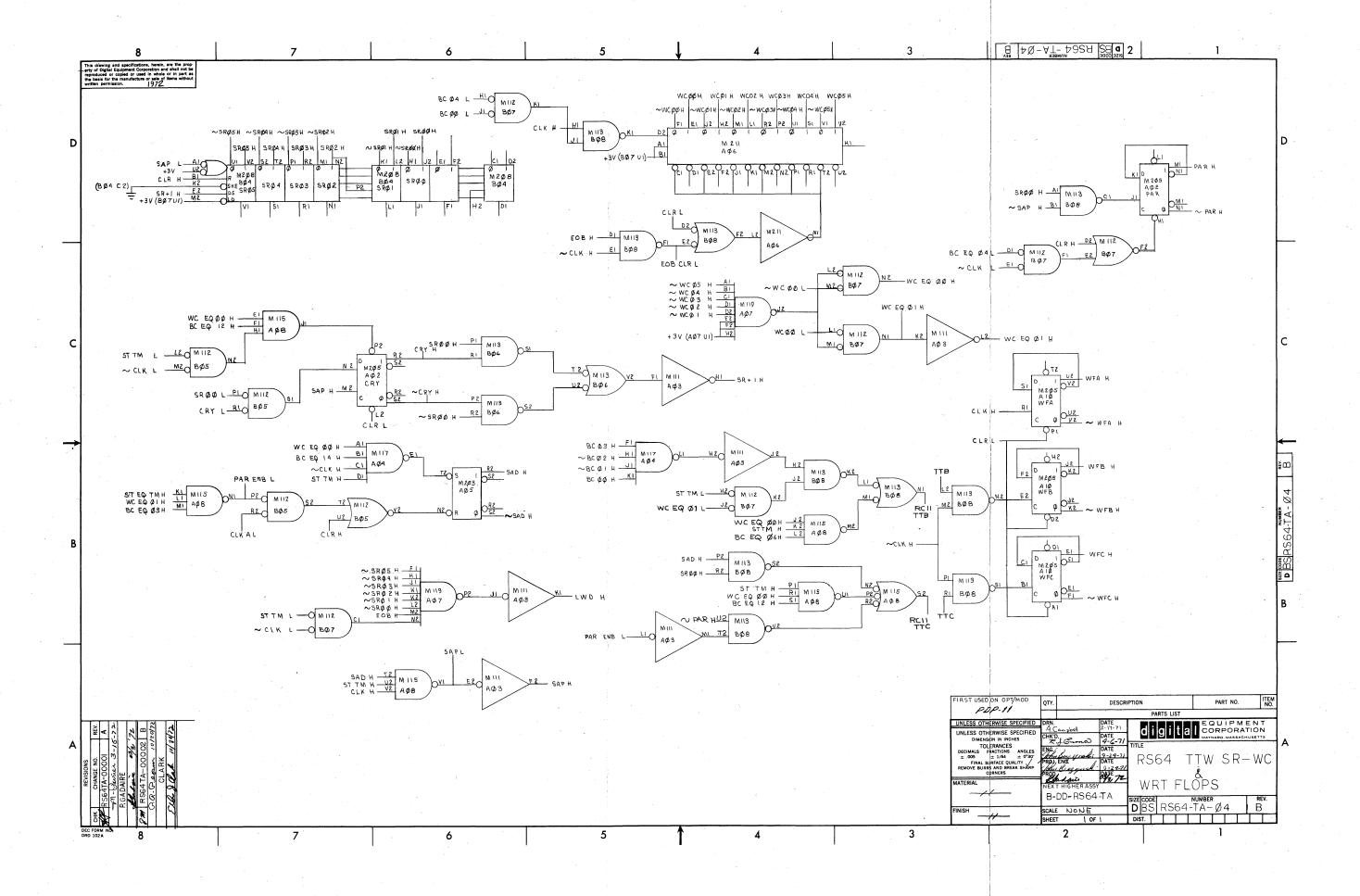

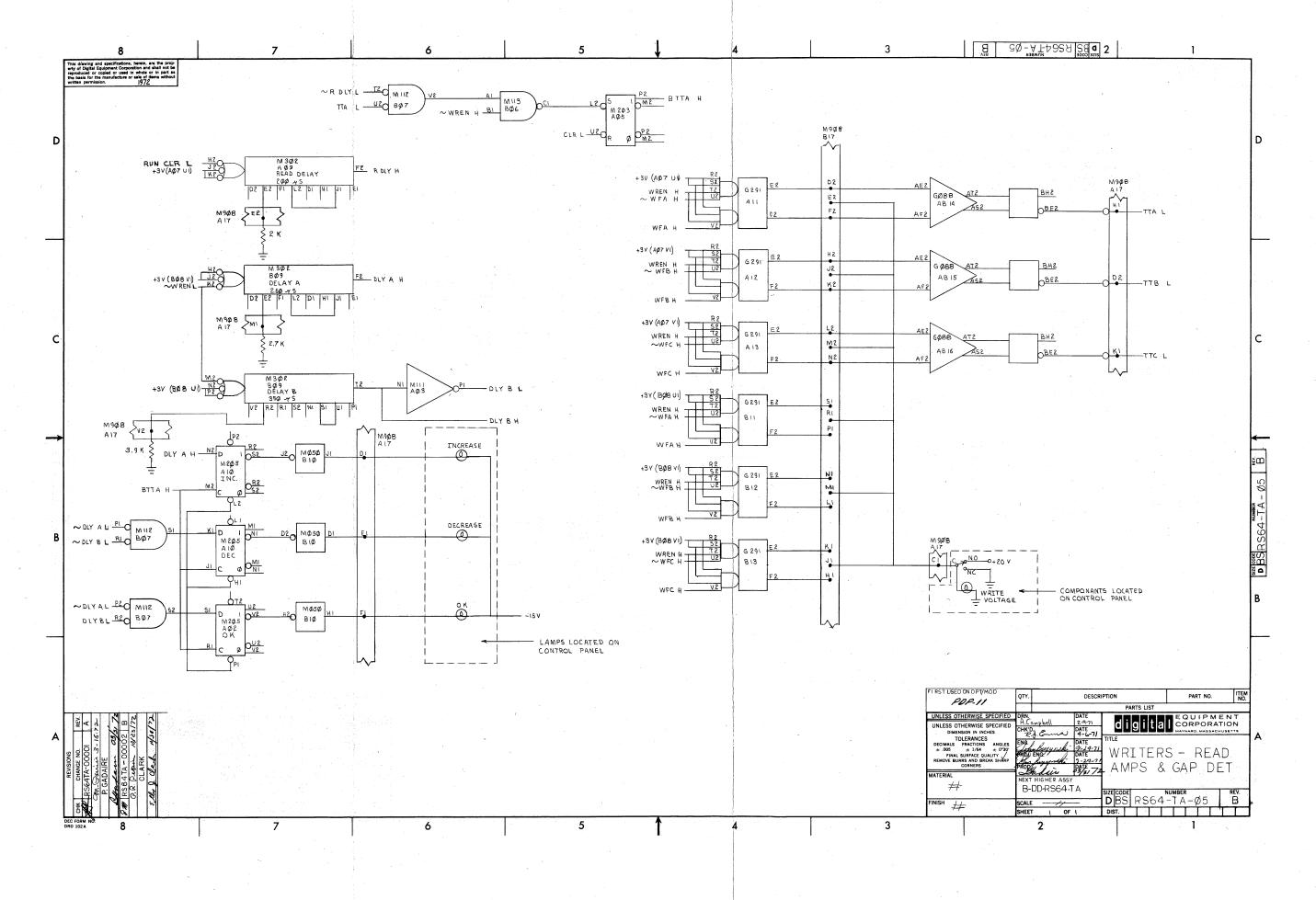

RS64 Timing

Track Writer

Maintenance Manual

### Copyright © 1974 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

**COMPUTER LAB**

## CONTENTS

| 1.1   INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | rage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CHAPTER 1 | GENERAL INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.1       | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

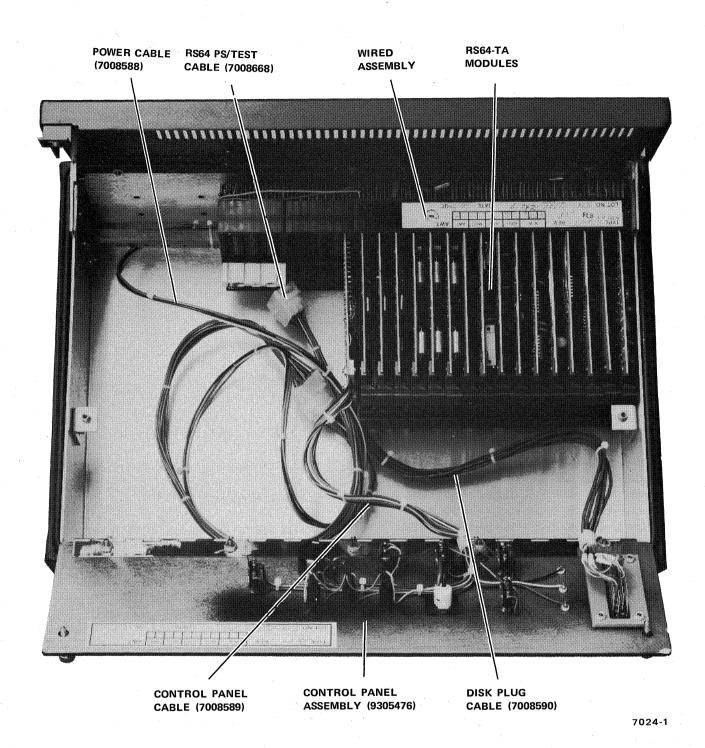

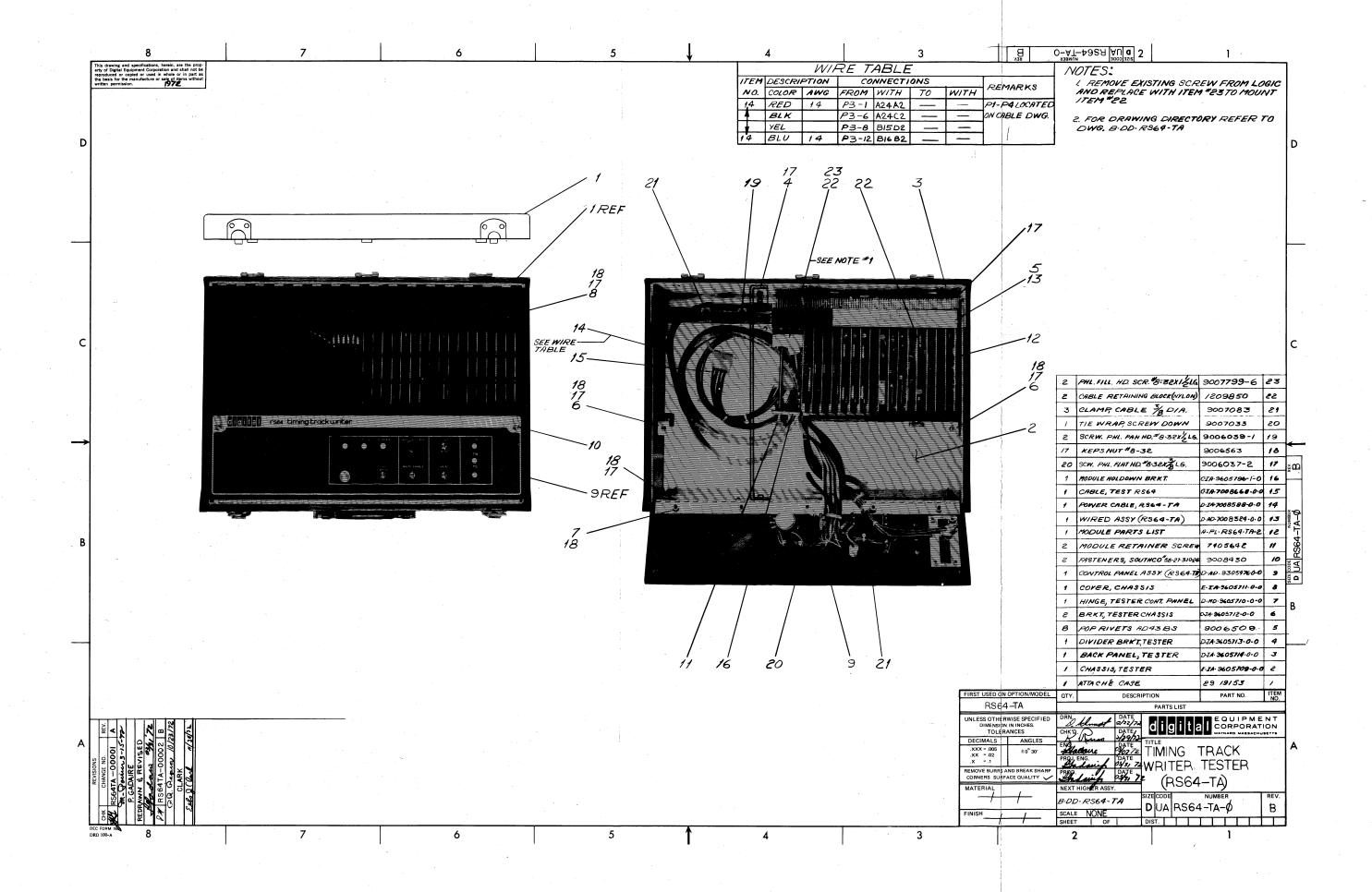

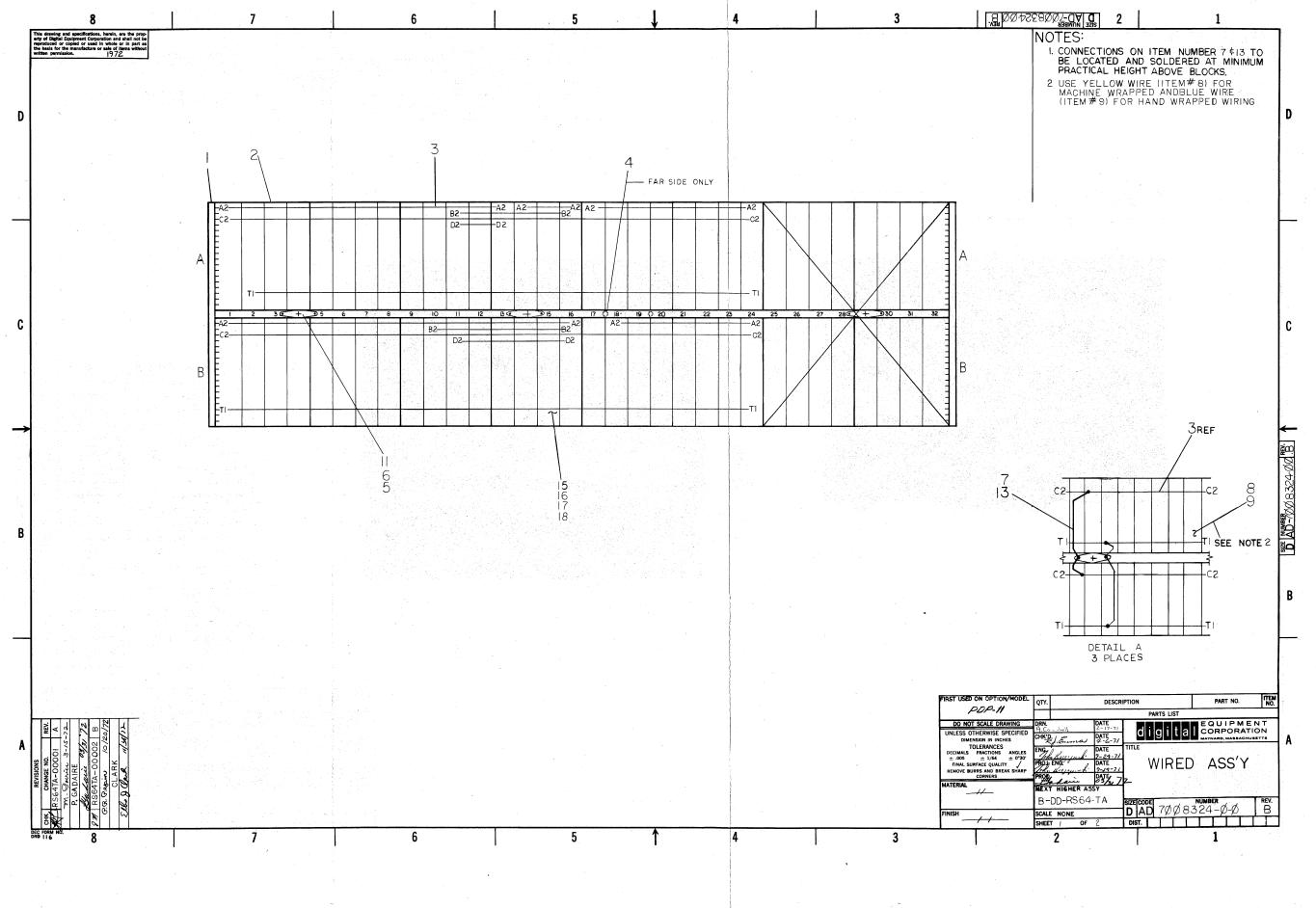

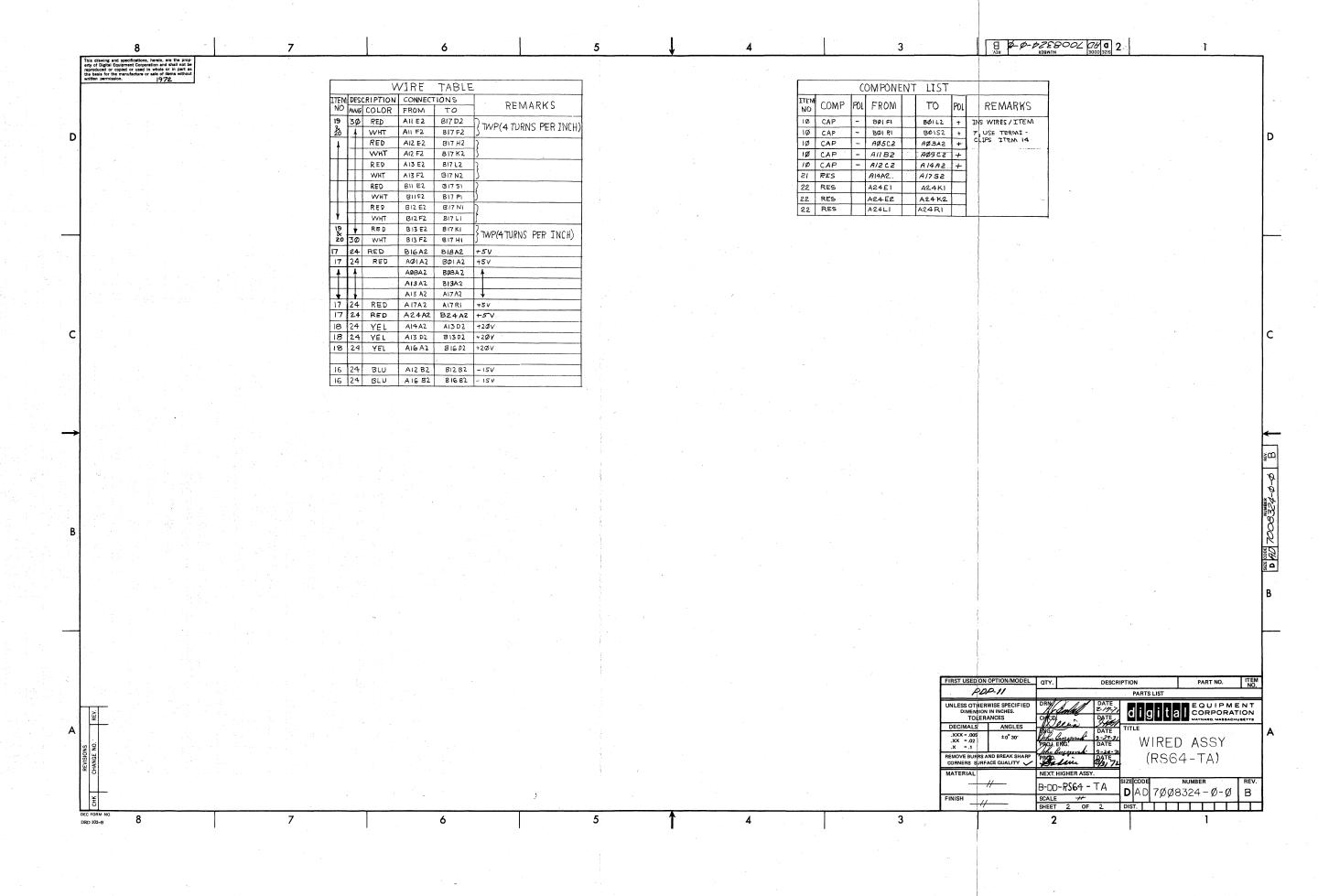

| 1.3.1   Control Panel Assembly   1.3     1.3.2   Disk Plug Cable   1.3     1.3.3   Control Panel Cable   1.3     1.3.4   RS64 PS/Test Cable   1.3     1.3.5   Power Cable   1.3     1.3.6   RS64-TA Modules   1.3     1.4   SPECIFICATIONS   1.3     1.4.1   Environmental   1.3     1.4.2   Power Requirements   1.3     1.4.3   Packaging   1.3    CHAPTER 2   UNPACKING, ACCEPTANCE TESTING, AND SETUP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.2       | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

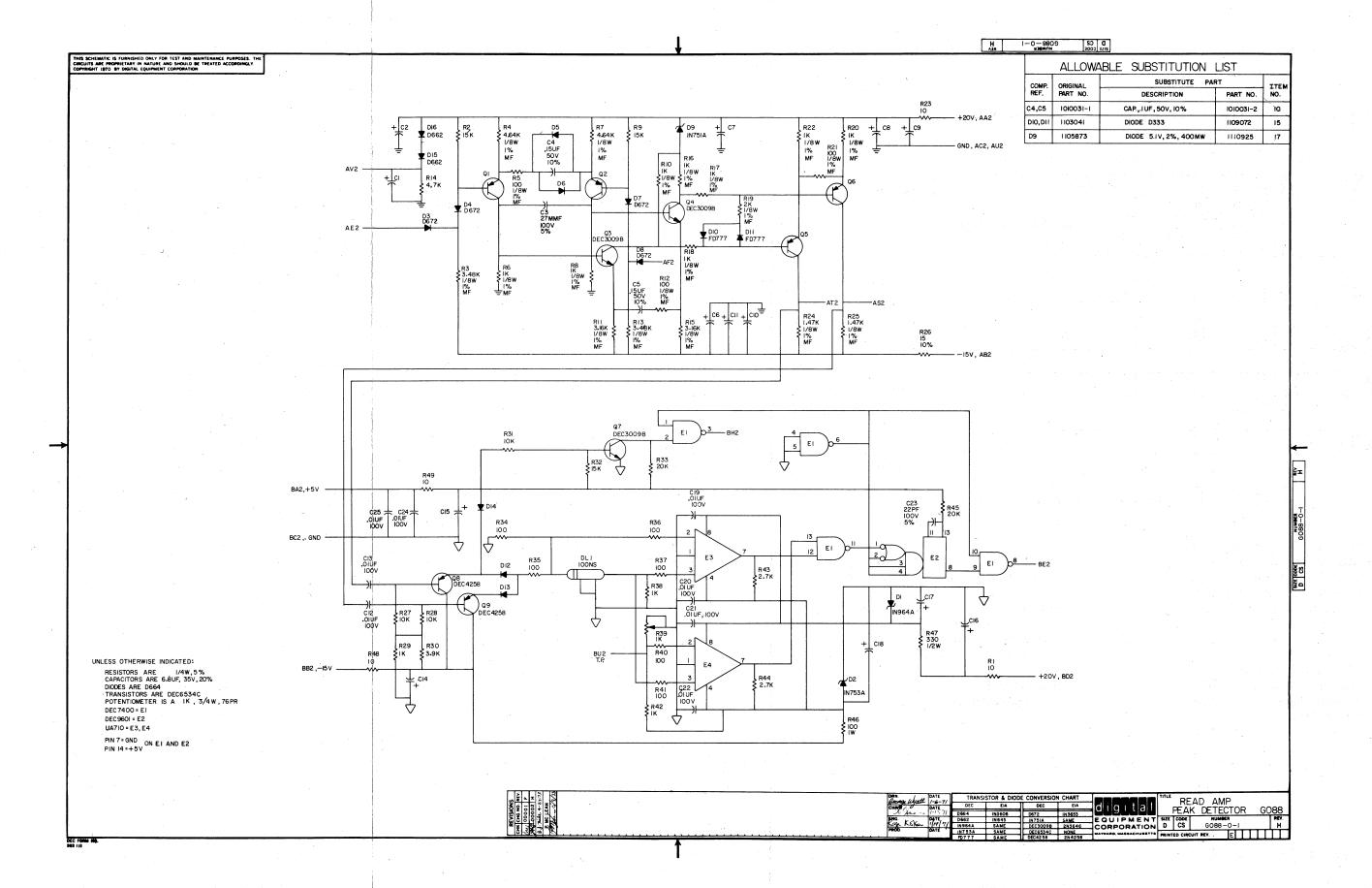

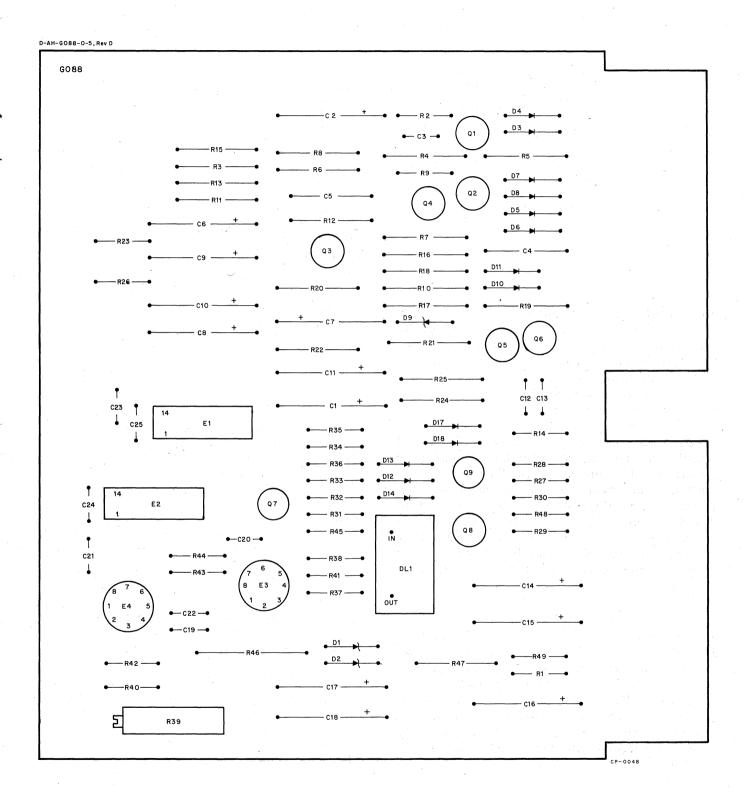

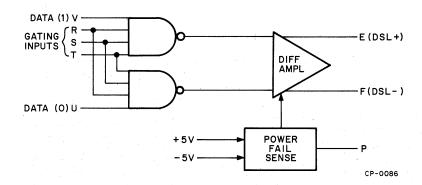

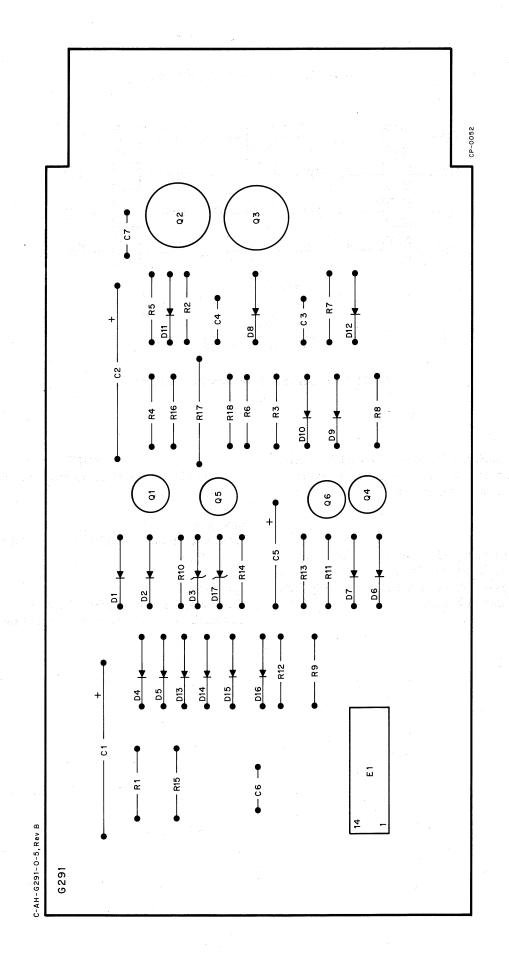

| 1.3.2       Disk Plug Cable       1-3         1.3.3       Control Panel Cable       1-3         1.3.4       R 564 PS/Test Cable       1-3         1.3.5       Power Cable       1-3         1.3.6       R 564-TA Modules       1-3         1.4       SPCEIFICATIONS       1-3         1.4.1       Environmental       1-3         1.4.2       Power Requirements       1-3         1.4.3       Packaging       1-3         CHAPTER 2       UNPACKING, ACCEPTANCE TESTING, AND SETUP         2.1       UNPACKING PROCEDURE       2-1         2.2       ACCEPTANCE TEST PROCEDURE       2-1         2.3       SETUP PROCEDURE       2-2         2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION       3-1         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2 <t< td=""><td>1.3</td><td>PHYSICAL DESCRIPTION</td></t<>                                | 1.3       | PHYSICAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

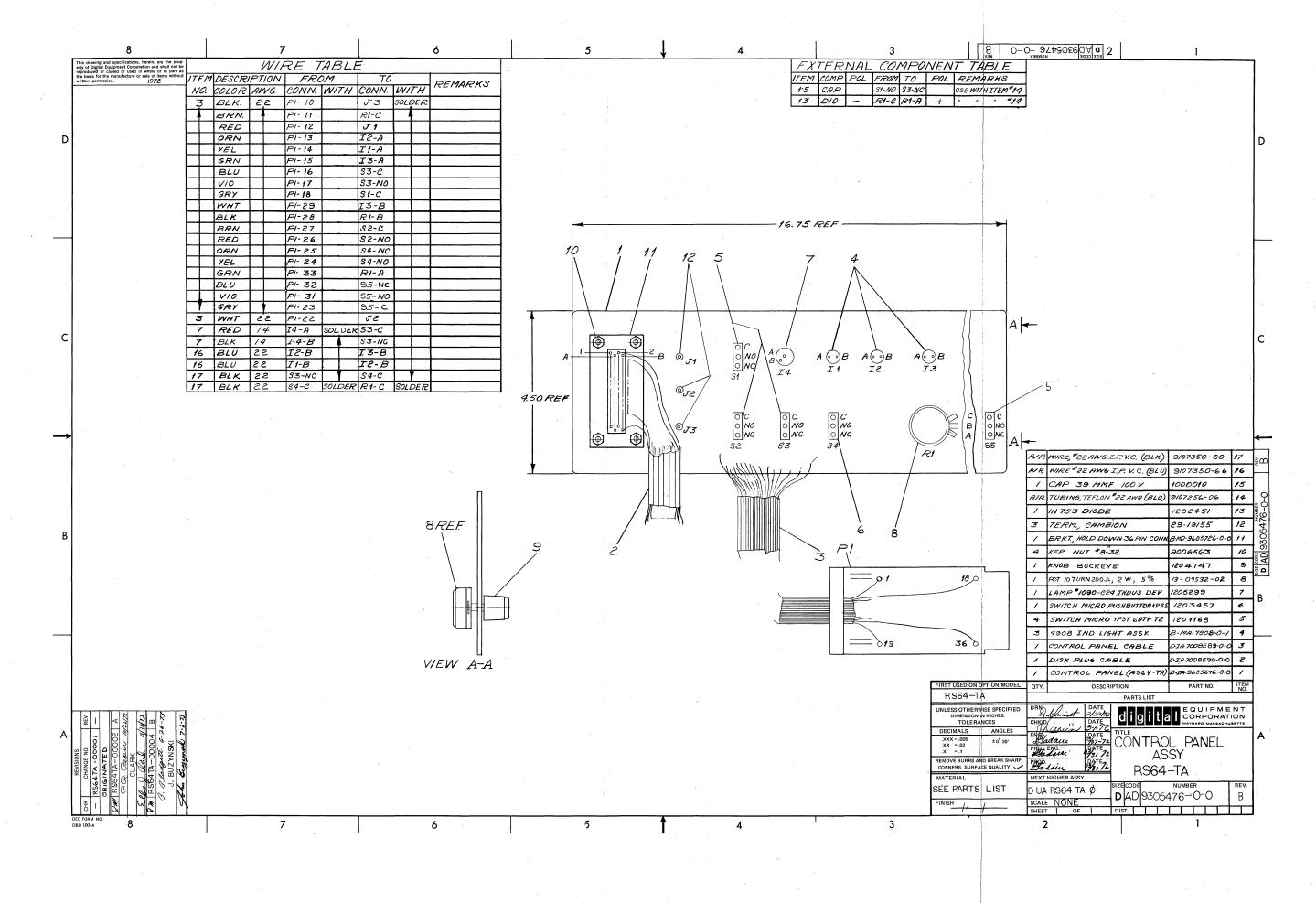

| 1.3.3       Control Panel Cable       1-3         1.3.4       RS64 PS/Test Cable       1-3         1.3.5       Power Cable       1-3         1.3.6       RS64-TA Modules       1-3         1.4       SPECIFICATIONS       1-3         1.4.1       Environmental       1-3         1.4.2       Power Requirements       1-3         1.4.3       Packaging       1-3         CHAPTER 2       UNPACKING, ACCEPTANCE TESTING, AND SETUP         2.1       UNPACKING PROCEDURE       2-1         2.2       ACCEPTANCE TEST PROCEDURE       2-1         2.3       SETUP PROCEDURE       2-2         2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Tracks       3-1         3.3.1.       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4                                                                                          | 1.3.1     | Control Panel Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

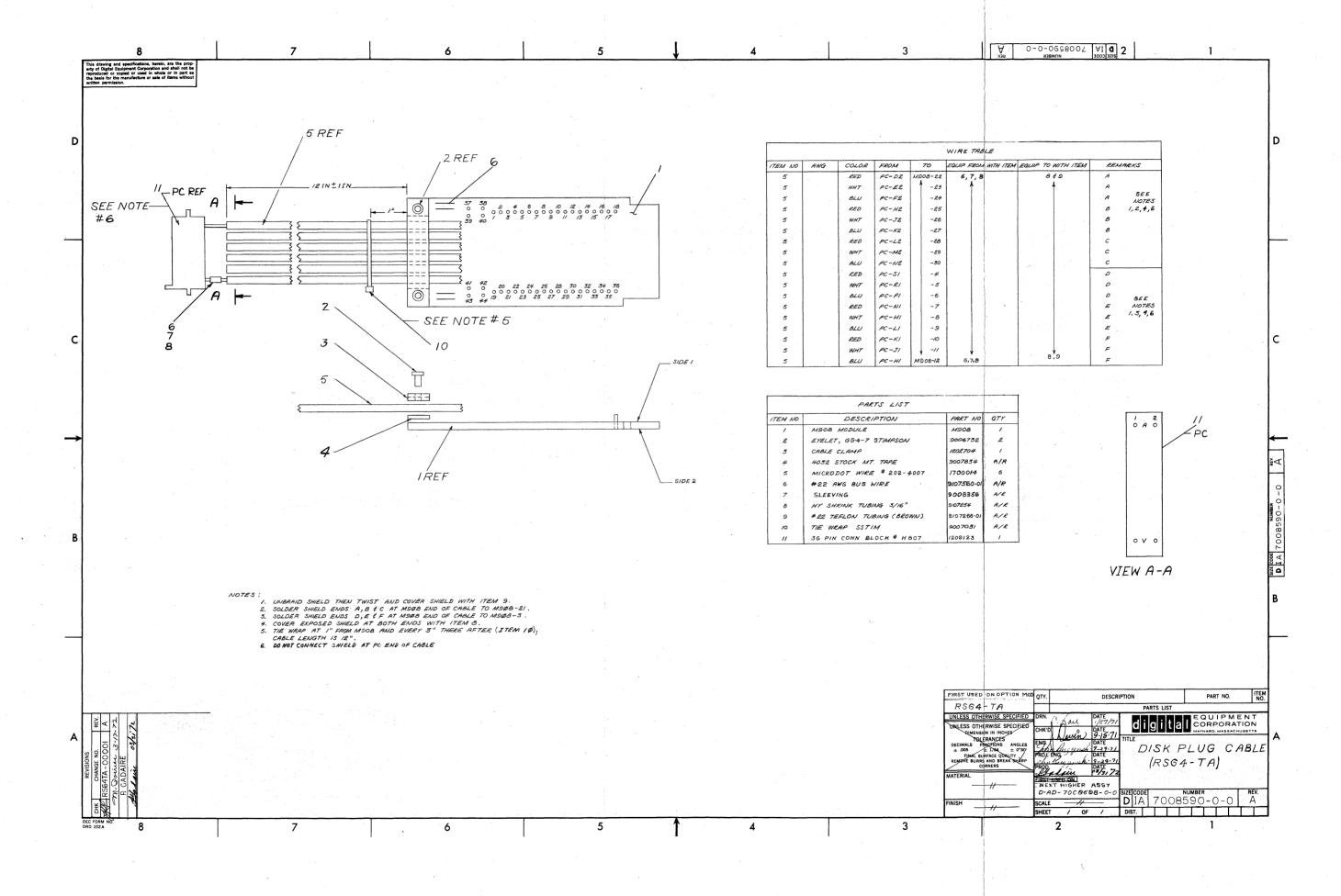

| 1.3.3       Control Panel Cable       1-3         1.3.4       RS64 PS/Test Cable       1-3         1.3.5       Power Cable       1-3         1.3.6       RS64-TA Modules       1-3         1.4       SPECIFICATIONS       1-3         1.4.1       Environmental       1-3         1.4.2       Power Requirements       1-3         1.4.3       Packaging       1-3         CHAPTER 2       UNPACKING, ACCEPTANCE TESTING, AND SETUP         2.1       UNPACKING PROCEDURE       2-1         2.2       ACCEPTANCE TEST PROCEDURE       2-1         2.3       SETUP PROCEDURE       2-2         2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Tracks       3-1         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4                                                                                         | 1.3.2     | Disk Plug Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

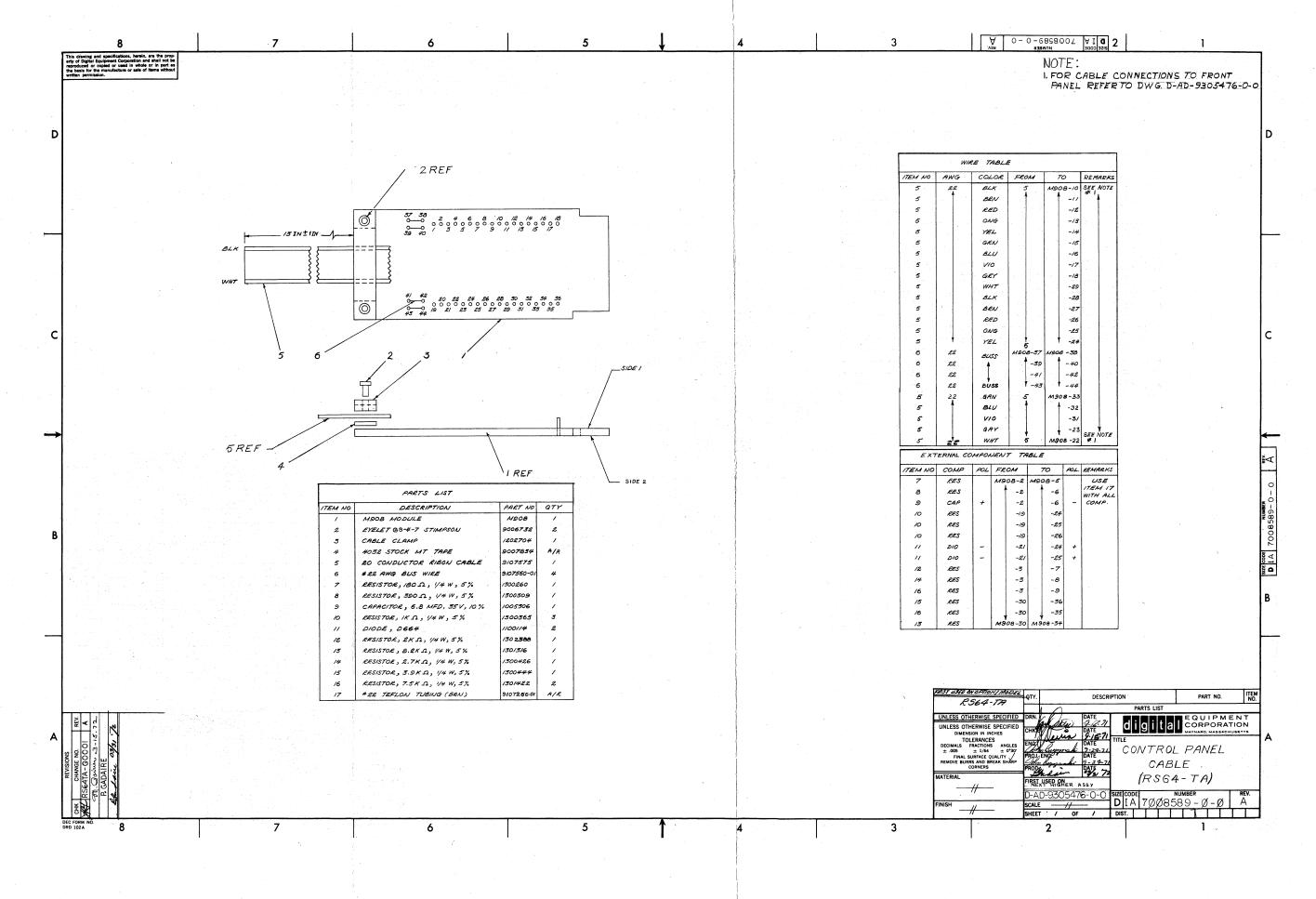

| 1.3.4       RS64 PS/Test Cable       1-3         1.3.5       Power Cable       1-3         1.3.6       RS64-TA Modules       1-3         1.4       SPECIFICATIONS       1-3         1.4.1       Environmental       1-3         1.4.2       Power Requirements       1-3         1.4.3       Packaging       1-3         CHAPTER 2       UNPACKING, ACCEPTANCE TESTING, AND SETUP         2.1       UNPACKING PROCEDURE       2-1         2.2       ACCEPTANCE TEST PROCEDURE       2-1         2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Tracks       3-1         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DES                                                                                          | 1.3.3     | Control Panel Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

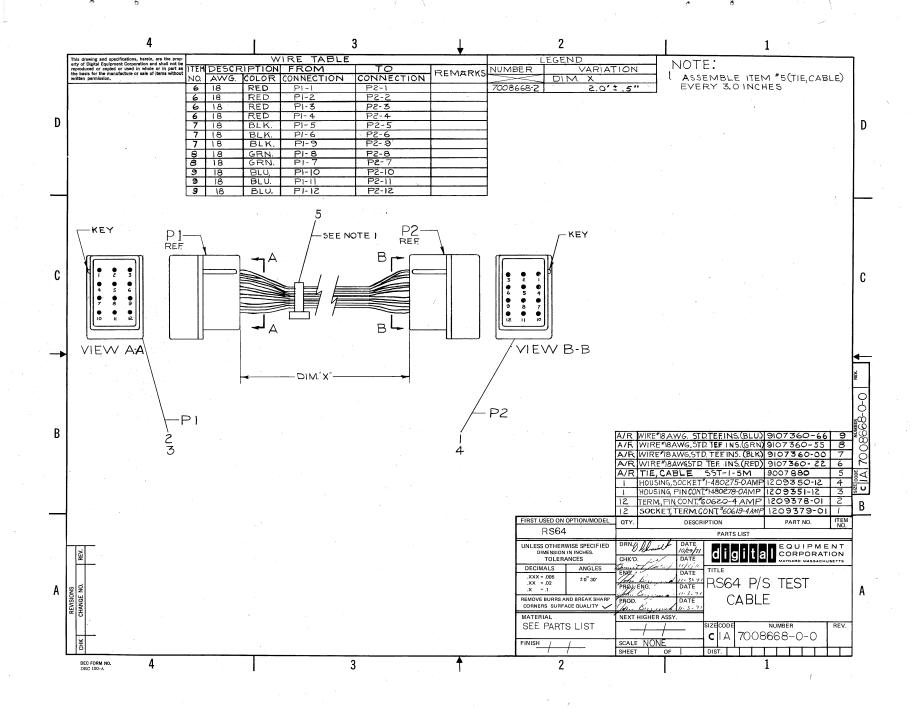

| 1.3.5       Power Cable       1-3         1.3.6       RS64-TA Modules       1-3         1.4       SPECIFICATIONS       1-3         1.4.1       Environmental       1-3         1.4.2       Power Requirements       1-3         1.4.3       Packaging       1-3         CHAPTER 2       UNPACKING, ACCEPTANCE TESTING, AND SETUP         2.1       UNPACKING PROCEDURE       2-1         2.2       ACCEPTANCE TEST PROCEDURE       2-1         2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Tracks       3-1         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2.2       Functional Block Description       4-1         4.2.1       In                                                                                          | 1.3.4     | RS64 PS/Test Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

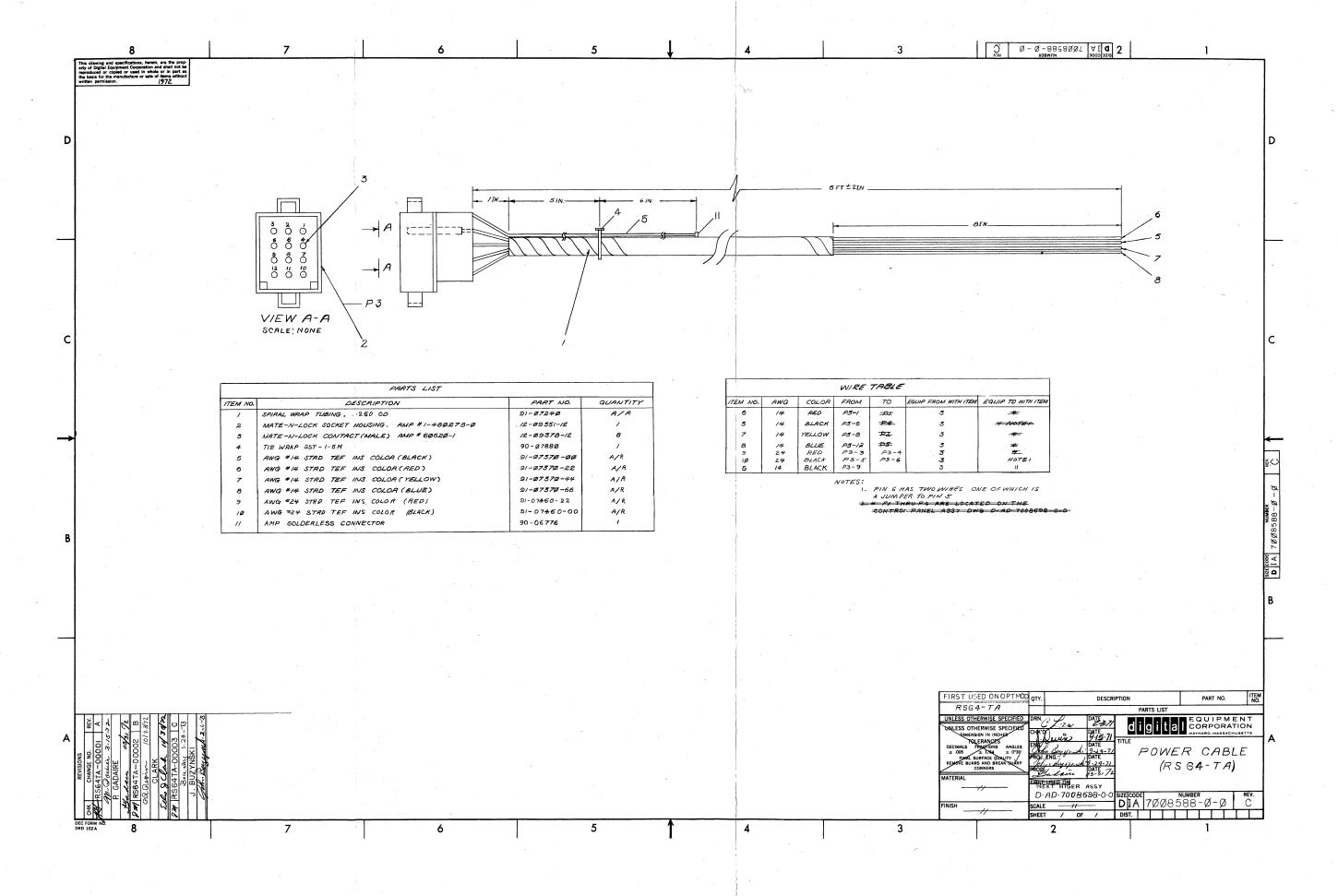

| 1.3.6       RS64-TA Modules       1-3         1.4       SPECIFICATIONS       1-3         1.4.1       Environmental       1-3         1.4.2       Power Requirements       1-3         1.4.3       Packaging       1-3         CHAPTER 2       UNPACKING, ACCEPTANCE TESTING, AND SETUP         2.1       UNPACKING PROCEDURE       2-1         2.2       ACCEPTANCE TEST PROCEDURE       2-2         2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       4.2.1       Introduction       4-1         4.2.2       FUNCTIONAL DESCRIPTION       4-5         4.3.1       Write Enable Logic       4-5     <                                                                     | 1.3.5     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

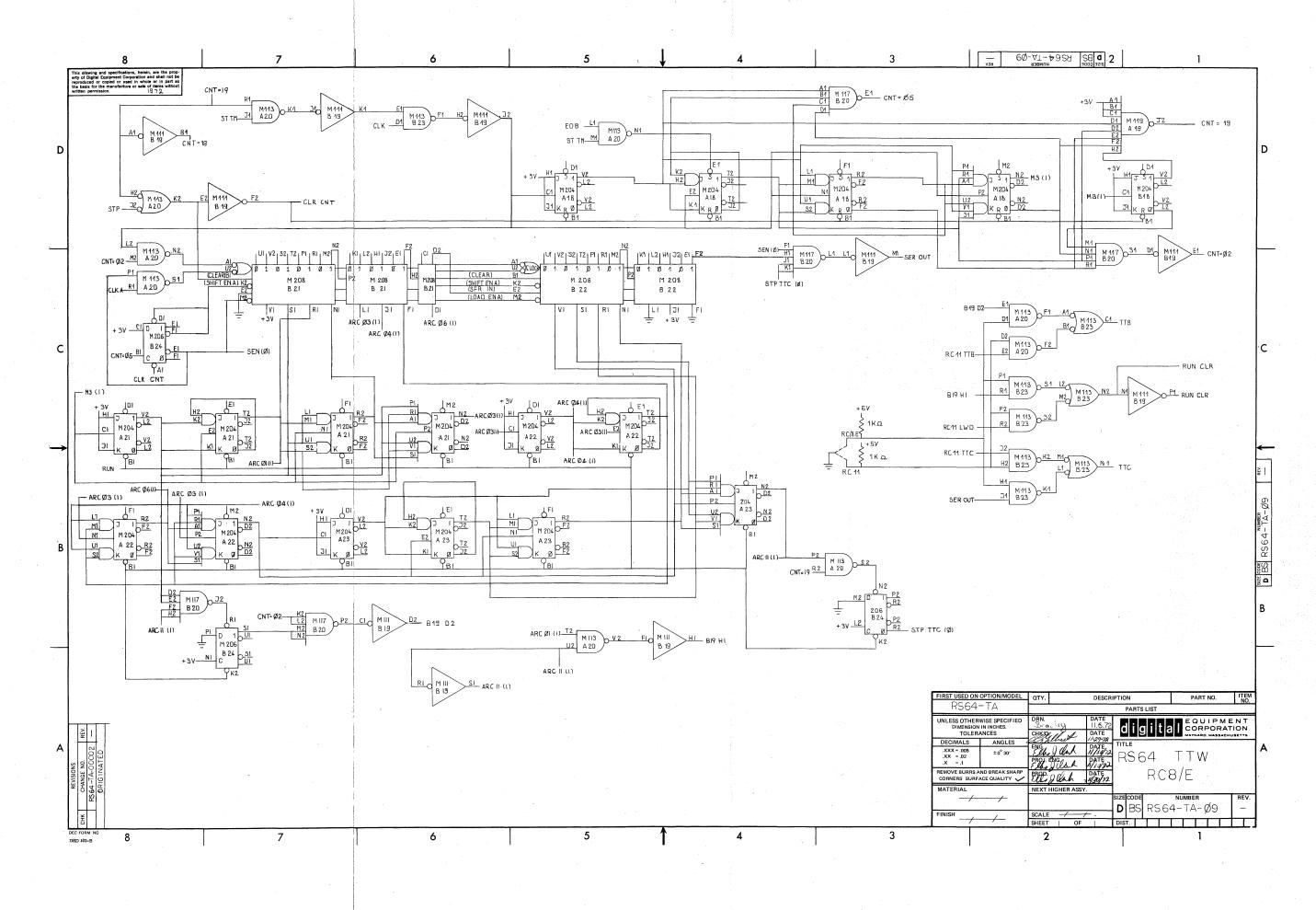

| 1.4       SPECIFICATIONS       1-3         1.4.1       Environmental       1-3         1.4.2       Power Requirements       1-3         1.4.3       Packaging       1-3         CHAPTER 2       UNPACKING, ACCEPTANCE TESTING, AND SETUP         2.1       UNPACKING PROCEDURE       2-1         2.2       ACCEPTANCE TEST PROCEDURE       2-2         2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Tracks Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2.2       Functional Block Description       4-1         4.2.1       Introduction       4-1         4.2.2       Functional Block Description       4-5                                                                                | 1.3.6     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.4.1       Environmental       1-3         1.4.2       Power Requirements       1-3         1.4.3       Packaging       1-3         CHAPTER 2       UNPACKING, ACCEPTANCE TESTING, AND SETUP         2.1       UNPACKING PROCEDURE       2-1         2.2       ACCEPTANCE TEST PROCEDURE       2-1         2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DESCRIPTION       4-1         4.2.1       Introduction       4-1         4.2.2       Functional Block Description       4-5         4.3.1       Write Enable Logic       4-5                                                                                   | 1.4       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.4.2       Power Requirements       1.3         1.4.3       Packaging       1-3         CHAPTER 2       UNPACKING, ACCEPTANCE TESTING, AND SETUP         2.1       UNPACKING PROCEDURE       2-1         2.2       ACCEPTANCE TEST PROCEDURE       2-1         2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DESCRIPTION       4-1         4.2.1       Introduction       4-1         4.2.2       FUNCTIONAL DESCRIPTION       4-5         4.3.1       Write Enable Logic       4-5         4.3.2       Clock Logic       4-5         4                                                                                 | 1.4.1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CHAPTER 2         UNPACKING, ACCEPTANCE TESTING, AND SETUP           2.1         UNPACKING PROCEDURE         2-1           2.2         ACCEPTANCE TEST PROCEDURE         2-1           2.3         SETUP PROCEDURE         2-3           CHAPTER 3         OPERATION AND UTILIZATION           3.1         SCOPE         3-1           3.2         CONTROLS AND INDICATORS         3-1           3.3         UTILIZATION PROCEDURE         3-1           3.3.1         Procedure for Writing Timing Tracks         3-1           3.2.2         Verification of Timing Track Writer Performance         3-4           3.3.2.1         Read Amplifier-Peak Detector Adjustments         3-4           3.3.2.2         Verification of Timing Tracks         3-5           CHAPTER 4         THEORY OF OPERATION           4.1         SCOPE         4-1           4.2         FUNCTIONAL DESCRIPTION         4-1           4.2.2         Functional Block Description         4-3           4.3         DETAILED LOGIC DESCRIPTION         4-5           4.3.1         Write Enable Logic         4-5           4.3.2         Clock Logic         4-5           4.3.3         Bit Counter and Bit Count      | 1.4.3     | Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1       UNPACKING PROCEDURE       2-1         2.2       ACCEPTANCE TEST PROCEDURE       2-1         2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DESCRIPTION       4-1         4.2.1       Introduction       4-1         4.2.2       FUNCTIONAL DESCRIPTION       4-1         4.3.3       DETAILED LOGIC DESCRIPTION       4-1         4.3.1       Write Enable Logic       4-5         4.3.2       Clock Logic       4-5         4.3.3       Bit Counter and Bit Count Decode Logic       4-6         4.3.4       Word Counter and Word Count Decode Logic <td< td=""><td>CHADTED 2</td><td></td></td<>             | CHADTED 2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2       ACCEPTANCE TEST PROCEDURE       2-1         2.3       SETUP PROCEDURE       2-3         CCHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DESCRIPTION       4-1         4.2.1       Introduction       4-1         4.2.2       FUNCTIONAL DESCRIPTION       4-1         4.3.3       DETAILED LOGIC DESCRIPTION       4-1         4.3.1       Write Enable Logic       4-5         4.3.2       Clock Logic       4-5         4.3.3       Bit Counter and Bit Count Decode Logic       4-6         4.3.4       Word Counter and Word Count Decode Logic       4-7         4.3.5       Block Address Shift Register Lo                                           |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.3       SETUP PROCEDURE       2-3         CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DESCRIPTION       4-1         4.2.1       Introduction       4-1         4.2.2       Functional Block Description       4-3         4.3       DETAILED LOGIC DESCRIPTION       4-3         4.3.1       Write Enable Logic       4-5         4.3.2       Clock Logic       4-5         4.3.3       Bit Counter and Bit Count Decode Logic       4-5         4.3.4       Word Counter and Word Count Decode Logic       4-7         4.3.5       Block Address Shift Register Logic       4-7         4.3.6       Write Control and Read Logic<                               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CHAPTER 3         OPERATION AND UTILIZATION           3.1         SCOPE         3-1           3.2         CONTROLS AND INDICATORS         3-1           3.3         UTILIZATION PROCEDURE         3-1           3.3.1         Procedure for Writing Timing Tracks         3-1           3.3.2         Verification of Timing Track Writer Performance         3-4           3.3.2.1         Read Amplifier-Peak Detector Adjustments         3-4           3.3.2.2         Verification of Timing Tracks         3-5           CHAPTER 4         THEORY OF OPERATION           4.1         SCOPE         4-1           4.2         FUNCTIONAL DESCRIPTION         4-1           4.2.1         Introduction         4-1           4.2.2         Functional Block Description         4-3           4.3         DETAILED LOGIC DESCRIPTION         4-5           4.3.1         Write Enable Logic         4-5           4.3.2         Clock Logic         4-5           4.3.3         Bit Counter and Bit Count Decode Logic         4-5           4.3.4         Word Counter and Word Count Decode Logic         4-7           4.3.5         Block Address Shift Register Logic         4-7           4.3.6 |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CHAPTER 3       OPERATION AND UTILIZATION         3.1       SCOPE       3-1         3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DESCRIPTION       4-1         4.2.1       Introduction       4-1         4.2.2       Functional Block Description       4-3         4.3       DETAILED LOGIC DESCRIPTION       4-5         4.3.1       Write Enable Logic       4-5         4.3.2       Clock Logic       4-5         4.3.3       Bit Counter and Bit Count Decode Logic       4-5         4.3.4       Word Counter and Word Count Decode Logic       4-7         4.3.5       Block Address Shift Register Logic       4-7         4.3.6       Write Control and Read Logic       4-10         4.3.7                                                   | 2.3       | BEIOI INCOME CITE TO THE STATE OF THE STATE |

| 3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DESCRIPTION       4-1         4.2.1       Introduction       4-1         4.2.2       Functional Block Description       4-3         4.3       DETAILED LOGIC DESCRIPTION       4-5         4.3.1       Write Enable Logic       4-5         4.3.2       Clock Logic       4-5         4.3.3       Bit Counter and Bit Count Decode Logic       4-5         4.3.3       Bit Counter and Bit Count Decode Logic       4-6         4.3.4       Word Counter and Word Count Decode Logic       4-7         4.3.5       Block Address Shift Register Logic       4-7         4.3.6       Write Control and Read Logic       4-10         4.3.7       Gap Detect Logic       4-12                                | CHAPTER 3 | OPERATION AND UTILIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.2       CONTROLS AND INDICATORS       3-1         3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DESCRIPTION       4-1         4.2.1       Introduction       4-1         4.2.2       Functional Block Description       4-3         4.3       DETAILED LOGIC DESCRIPTION       4-5         4.3.1       Write Enable Logic       4-5         4.3.2       Clock Logic       4-5         4.3.3       Bit Counter and Bit Count Decode Logic       4-5         4.3.3       Bit Counter and Bit Count Decode Logic       4-6         4.3.4       Word Counter and Word Count Decode Logic       4-7         4.3.5       Block Address Shift Register Logic       4-7         4.3.6       Write Control and Read Logic       4-10         4.3.7       Gap Detect Logic       4-12                                | 3.1       | SCOPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

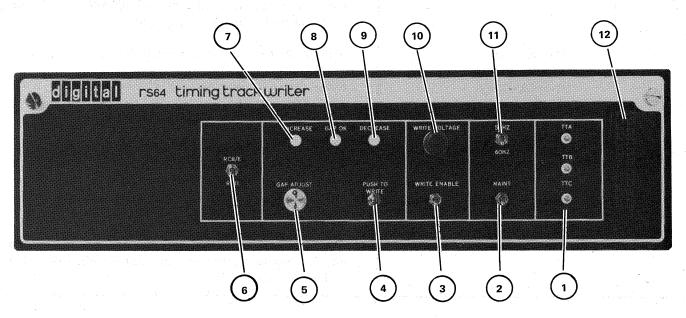

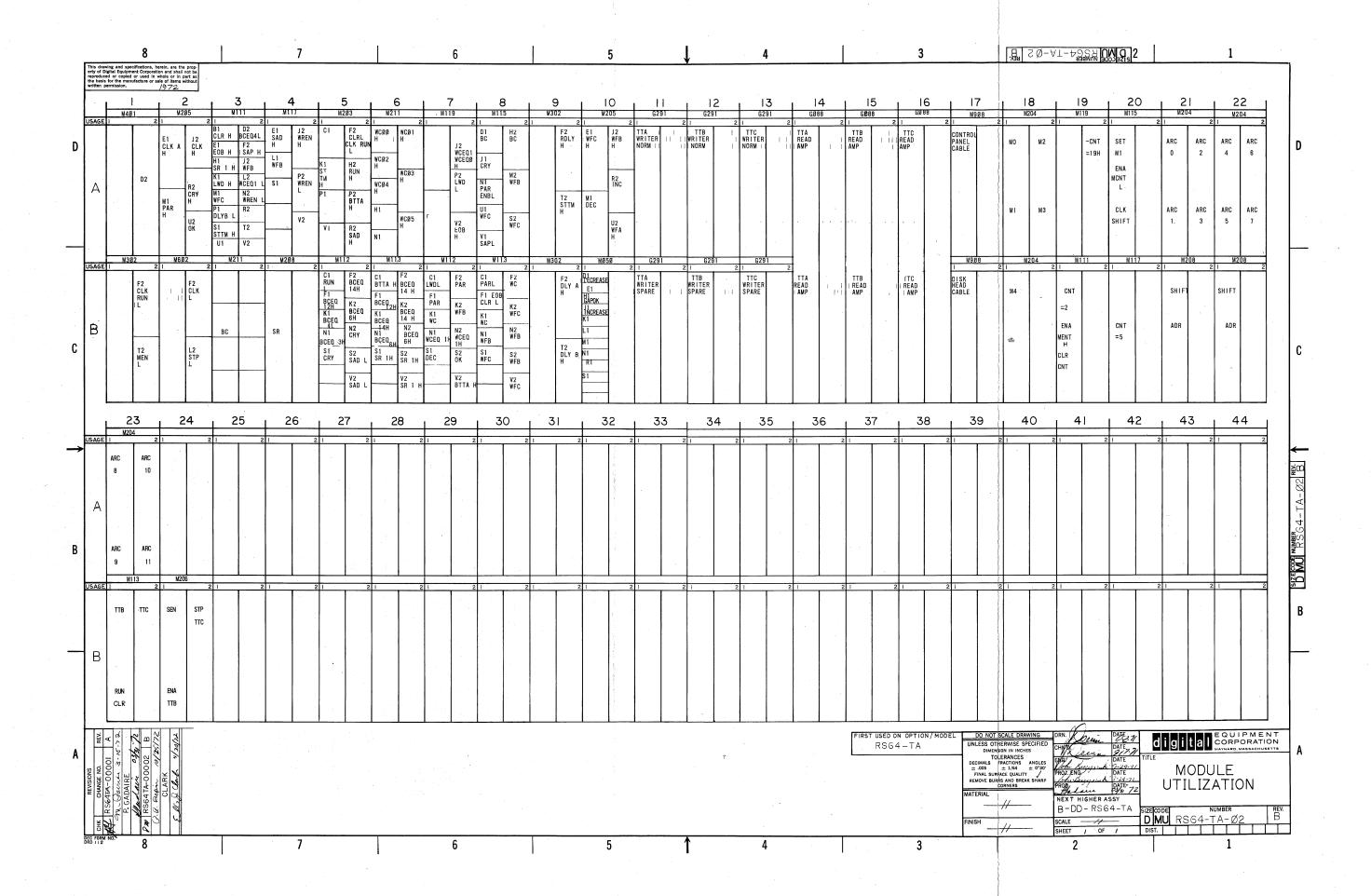

| 3.3       UTILIZATION PROCEDURE       3-1         3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DESCRIPTION       4-1         4.2.1       Introduction       4-1         4.2.2       Functional Block Description       4-3         4.3       DETAILED LOGIC DESCRIPTION       4-5         4.3.1       Write Enable Logic       4-5         4.3.2       Clock Logic       4-5         4.3.3       Bit Counter and Bit Count Decode Logic       4-6         4.3.4       Word Counter and Word Count Decode Logic       4-7         4.3.5       Block Address Shift Register Logic       4-7         4.3.6       Write Control and Read Logic       4-10         4.3.7       Gap Detect Logic       4-12                                                                                                                                                         | 3.2       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

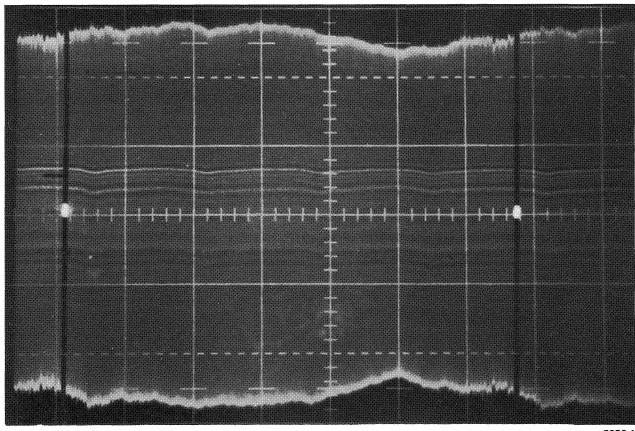

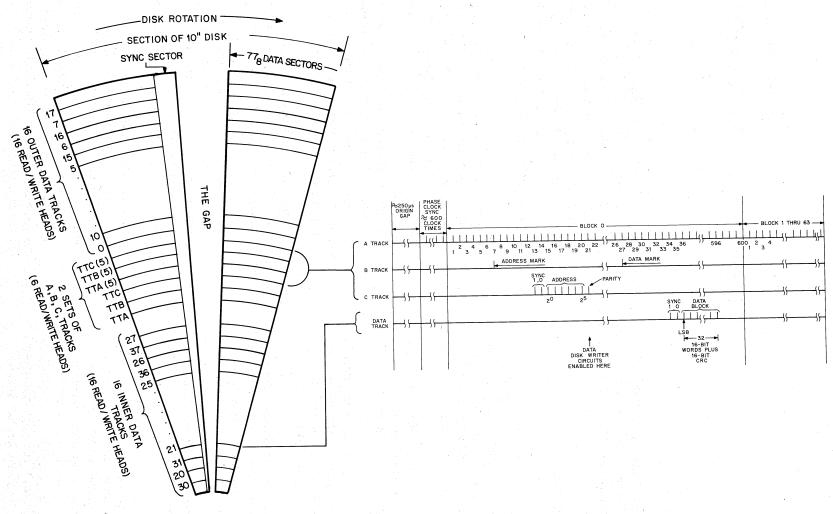

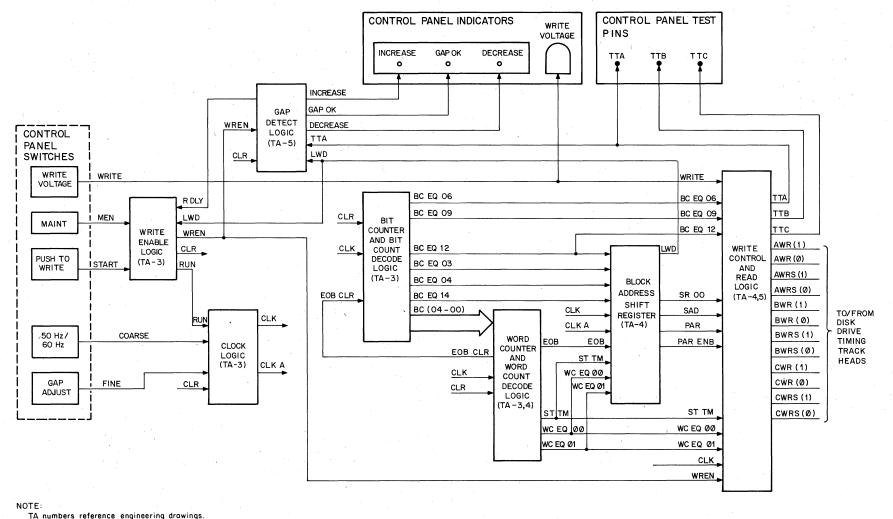

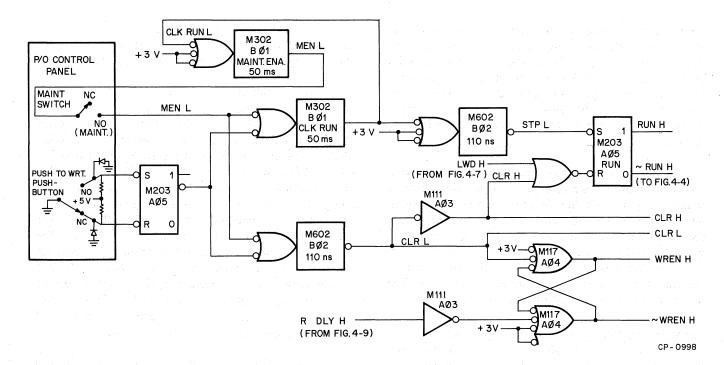

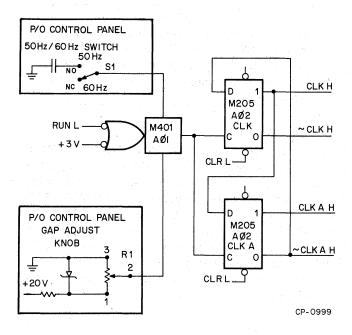

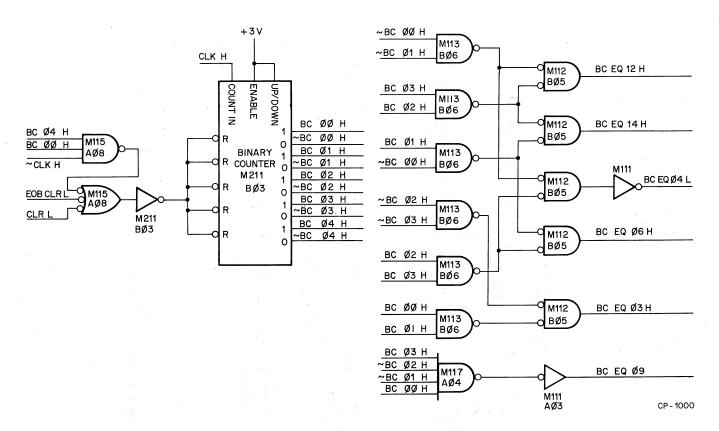

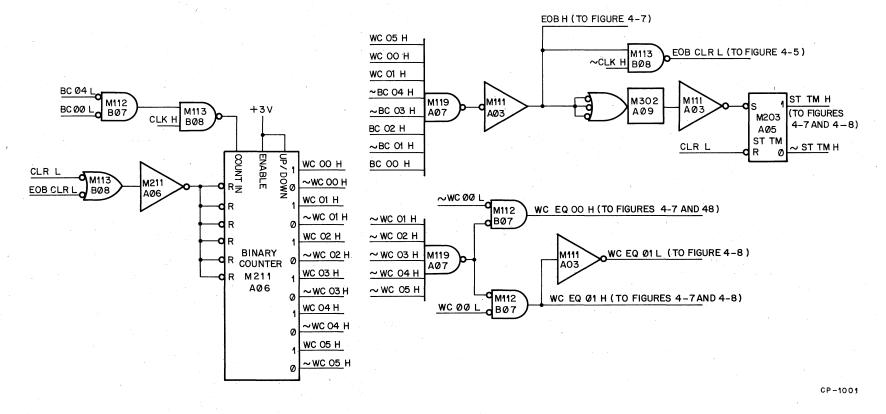

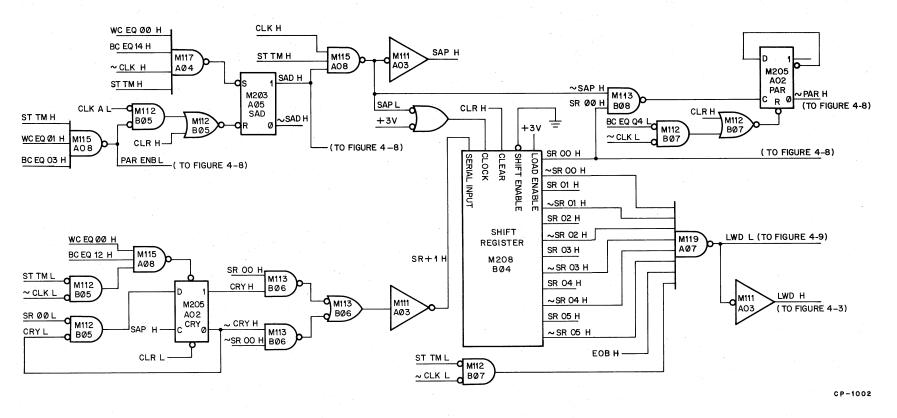

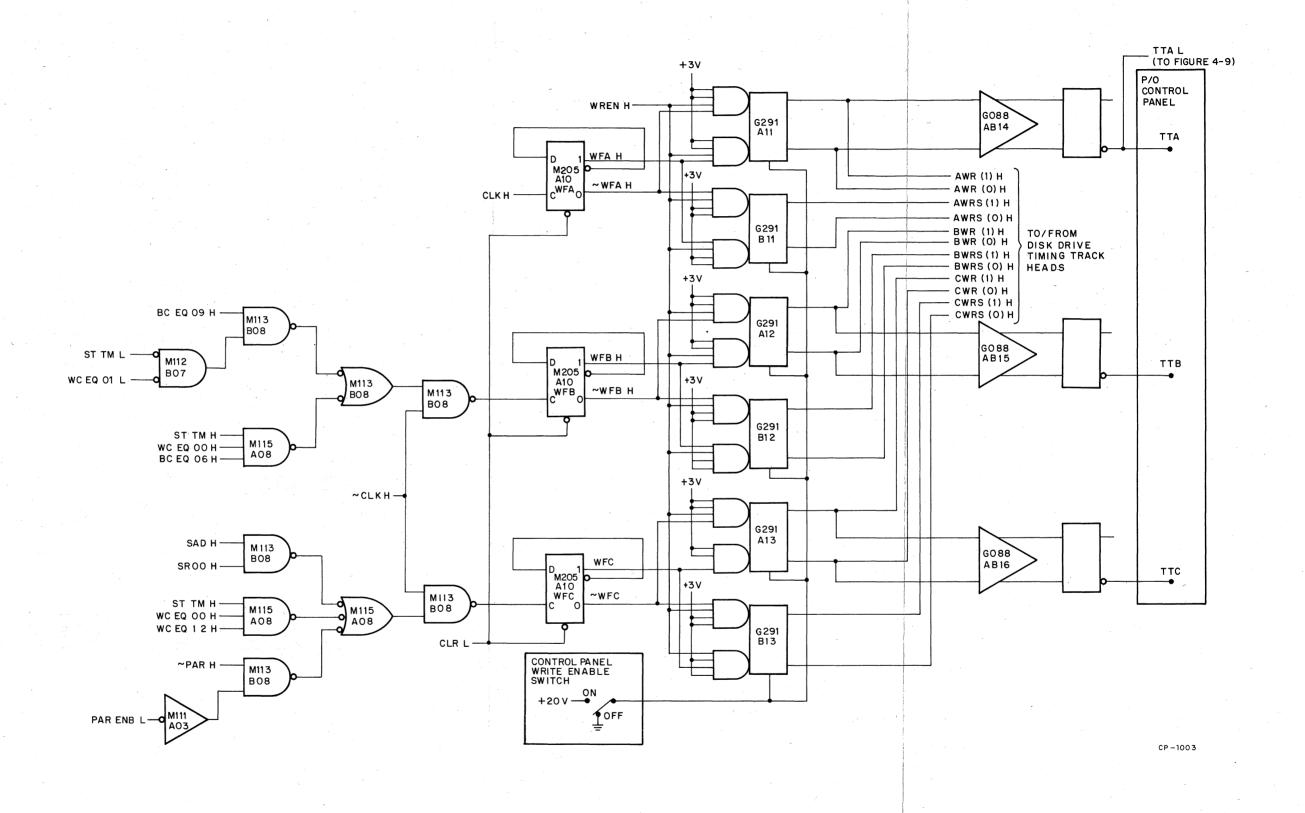

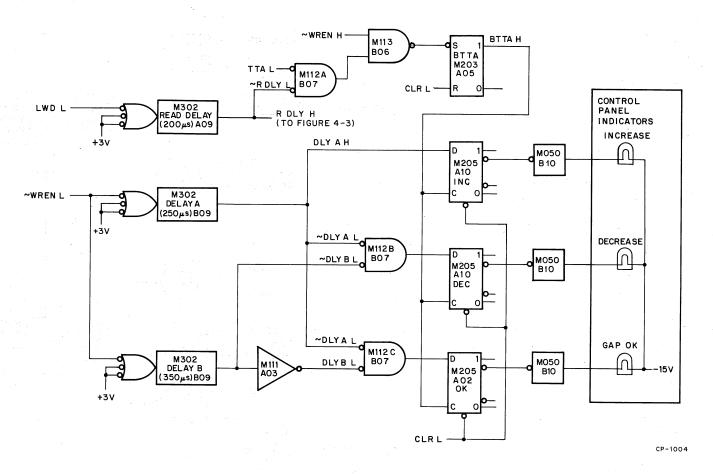

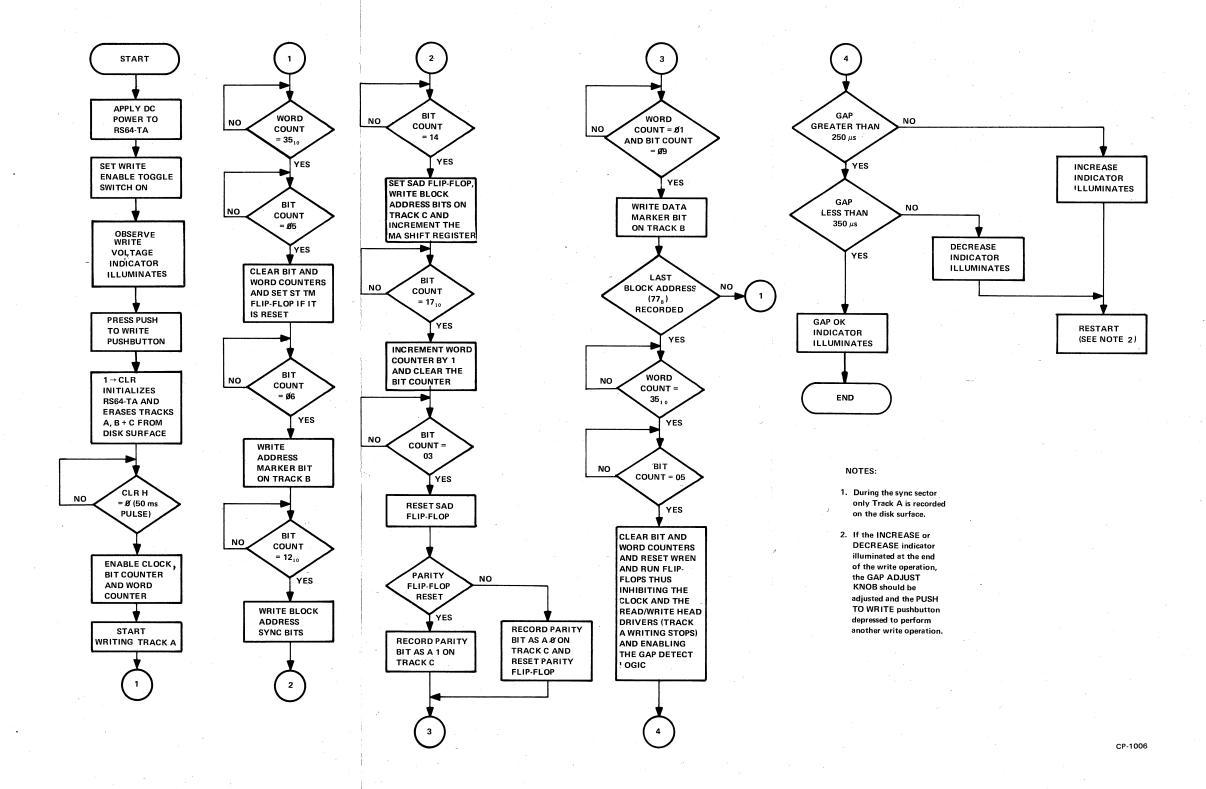

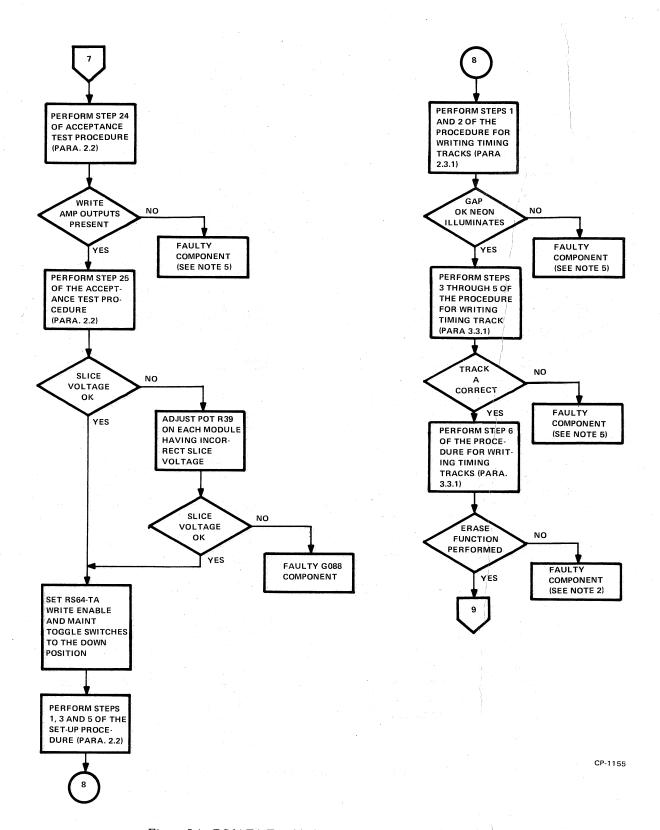

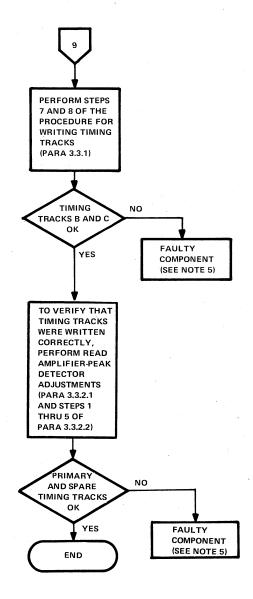

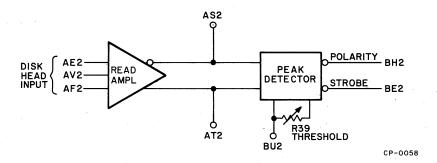

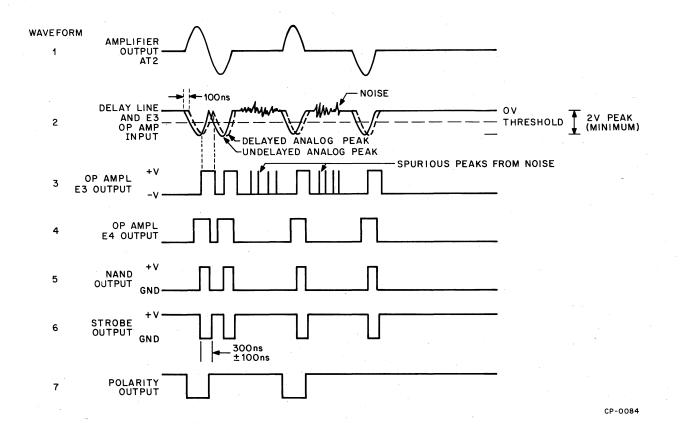

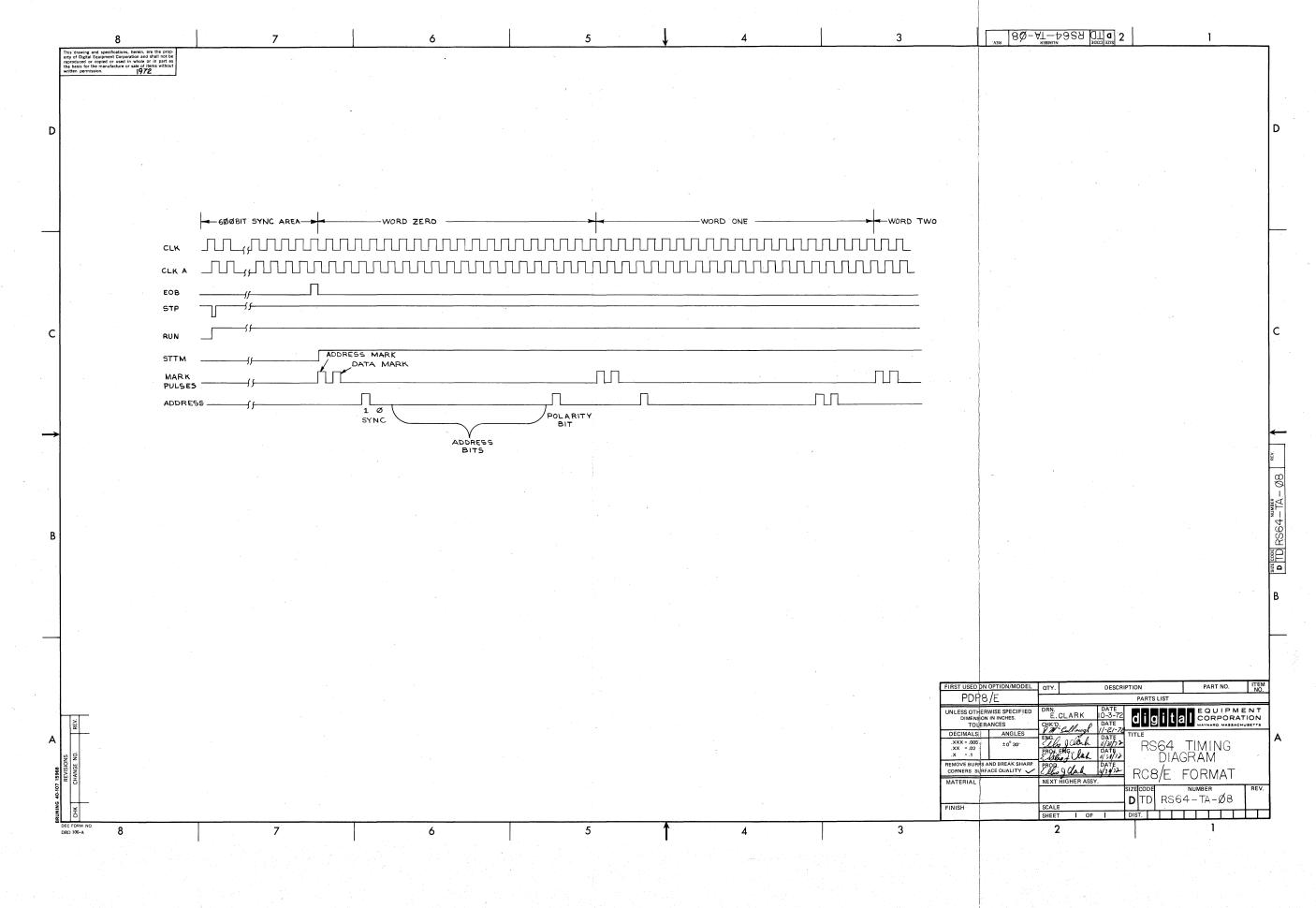

| 3.3.1       Procedure for Writing Timing Tracks       3-1         3.3.2       Verification of Timing Track Writer Performance       3-4         3.3.2.1       Read Amplifier-Peak Detector Adjustments       3-4         3.3.2.2       Verification of Timing Tracks       3-5         CHAPTER 4       THEORY OF OPERATION         4.1       SCOPE       4-1         4.2       FUNCTIONAL DESCRIPTION       4-1         4.2.1       Introduction       4-1         4.2.2       Functional Block Description       4-3         4.3       DETAILED LOGIC DESCRIPTION       4-5         4.3.1       Write Enable Logic       4-5         4.3.2       Clock Logic       4-5         4.3.3       Bit Counter and Bit Count Decode Logic       4-6         4.3.4       Word Counter and Word Count Decode Logic       4-7         4.3.5       Block Address Shift Register Logic       4-7         4.3.6       Write Control and Read Logic       4-10         4.3.7       Gap Detect Logic       4-12                                                                                                                                                                                                           | 3.3       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |