PERKIN-ELMER

# INTELLIGENT DISK CONTROLLER (IDC) DISK SYSTEM

Installation and Maintenance Manual

The information in this document is subject to change without notice and should not be construed as a commitment by The Perkin-Elmer Corporation. The Perkin-Elmer Corporation assumes no responsibility for any errors that may appear in this document.

The hardware description in this document is intended solely for use in operation, installation, maintenance, or repair of Perkin-Elmer equipment. Use of this document for all other purposes, without prior written approval from Perkin-Elmer is prohibited.

Any approved copy of this manual must include the Perkin-Elmer copyright notice.

Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

The Perkin-Elmer Corporation, Data Systems Group, 2 Crescent Place, Oceanport, New Jersey 07757

© 1982, 1984 by The Perkin-Elmer Corporation

Printed in the United States of America

#### PREFACE

This manual documents the installation, operation and maintenance of a Perkin-Elmer Intelligent Disk Controller (IDC) Disk System. An IDC disk system is a Mass Storage Module (MSM) system or a Medium Capacity - Cartridge Disk Drive (MC-CDD) system having as its controller a printed circuit board referred to as the IDC.

Chapters 1 and 2 are directed towards all users, e.g., sales personnel, instructors, customer engineers, technicians and programmers. Chapter 1 defines what an IDC disk system is. Chapter 2 presents detailed parts lists for possible IDC disk systems and discusses procedures for installing an IDC disk system. Chapters 3 and 4 are directed to customer engineers, technicians and programmers. Chapter 3 describes the operation of the IDC board at the block-diagram level. Chapter 4 presents detailed information necessary for the maintenance of an IDC disk system.

Revisions 10, 11, 12 and 13 include text and drawing changes. Information on the CDD 50 Disk System has also been added.

For information on the contents of all Perkin-Elmer 32-bit manuals, see the 32-Bit Systems User Documentation Summary.

## TABLE OF CONTENTS

| Chapter/<br>Section                     | Title                                   | Page                 |   |

|-----------------------------------------|-----------------------------------------|----------------------|---|

| 1                                       | OVERVIEW                                | 1-1                  |   |

| 1-1.                                    | DESCRIPTION OF AN IDC DISK SYSTEM       | 1-1                  | 1 |

| 1-2                                     | LIST OF RELATED PUBLICATIONS            | 1-5                  | } |

| •                                       |                                         |                      |   |

| 2                                       | INSTALLATION                            | 2-1                  |   |

| 2-1                                     | INTRODUCTION                            | 2-1                  |   |

| 2-2<br>2-2.1                            | DETAILED PARTS LISTS                    |                      |   |

| 2-3                                     | UNPACKING INSTRUCTIONS                  | 2-21                 |   |

| 2-4<br>2-4.1<br>2-4.2                   | INSTALLING AN IDC DISK SYSTEM           | 2-21                 | 1 |

| 2-5<br>2-5.1<br>2-5.2<br>2-5.3<br>2-5.4 | INSTALLING DUAL-PORT OPTIONS  IDC Board | 2-25<br>2-25<br>2-25 |   |

| 2-6                                     | AC-POWER REQUIREMENTS                   | 2-27                 |   |

| 2-7<br>2-7.1<br>2-7.2                   | APPLICATION OF AC POWER                 | 2-29                 |   |

| 2-8                                     | IDC TESTING AND FORMATTING              | 2-30                 |   |

| 3                                       | THEORY OF OPERATION                     | 3-1                  |   |

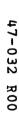

| 3-1<br>3-1.1<br>3-1.2<br>3-1.3          | BLACKBOX OVERVIEW OF IDC BOARD          | 3-3<br>3-6           |   |

| 3-2<br>3-2.1<br>3-2.2<br>3-2.3          | I/O LINES OF THE IDC BOARD              | 3-15<br>3-18         |   |

# TABLE OF CONTENTS (Continued)

| Chapter/<br>Section                                                                                                                 | Title                                                                                                                                                                                                                                                                                | Page                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

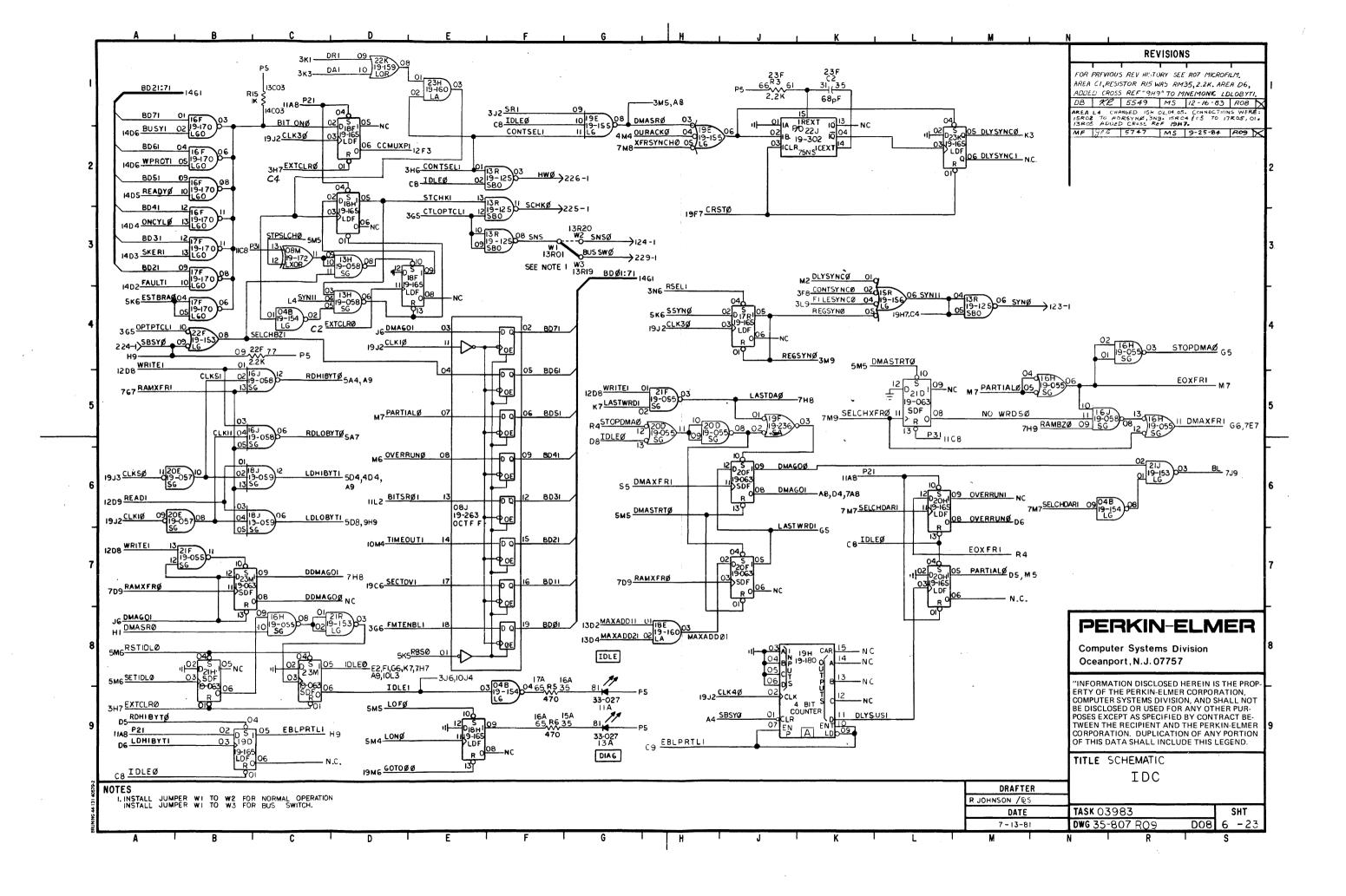

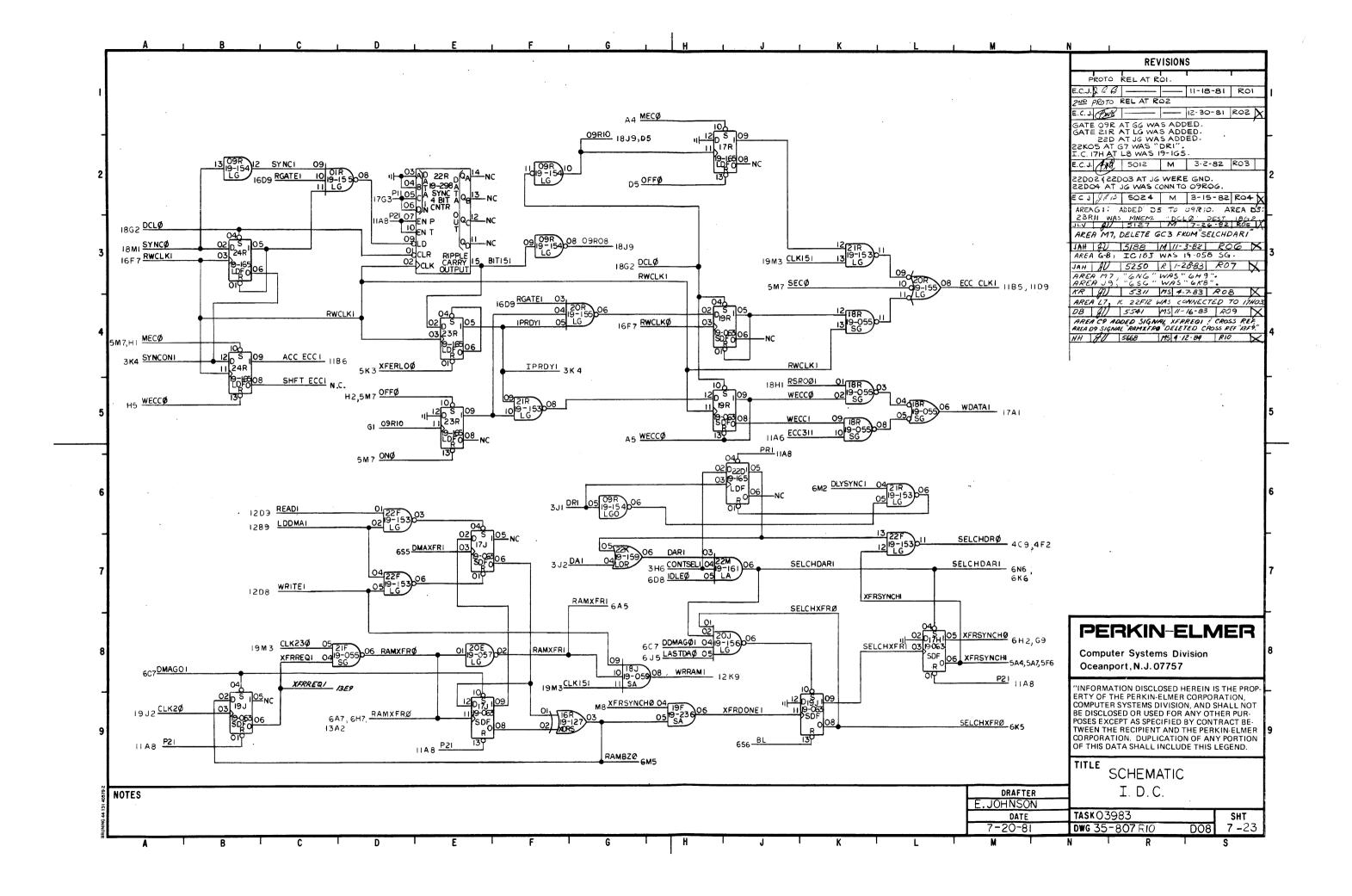

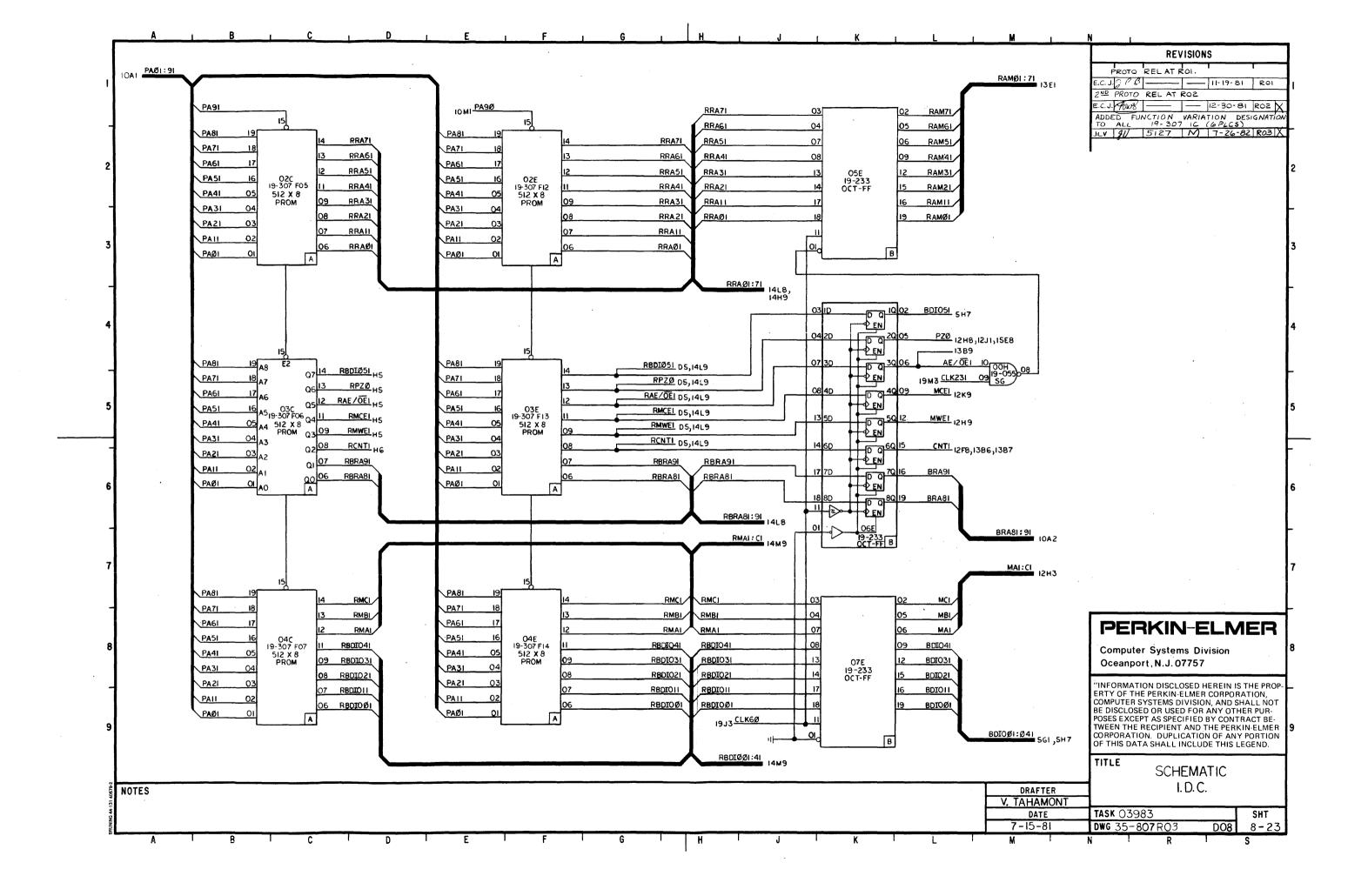

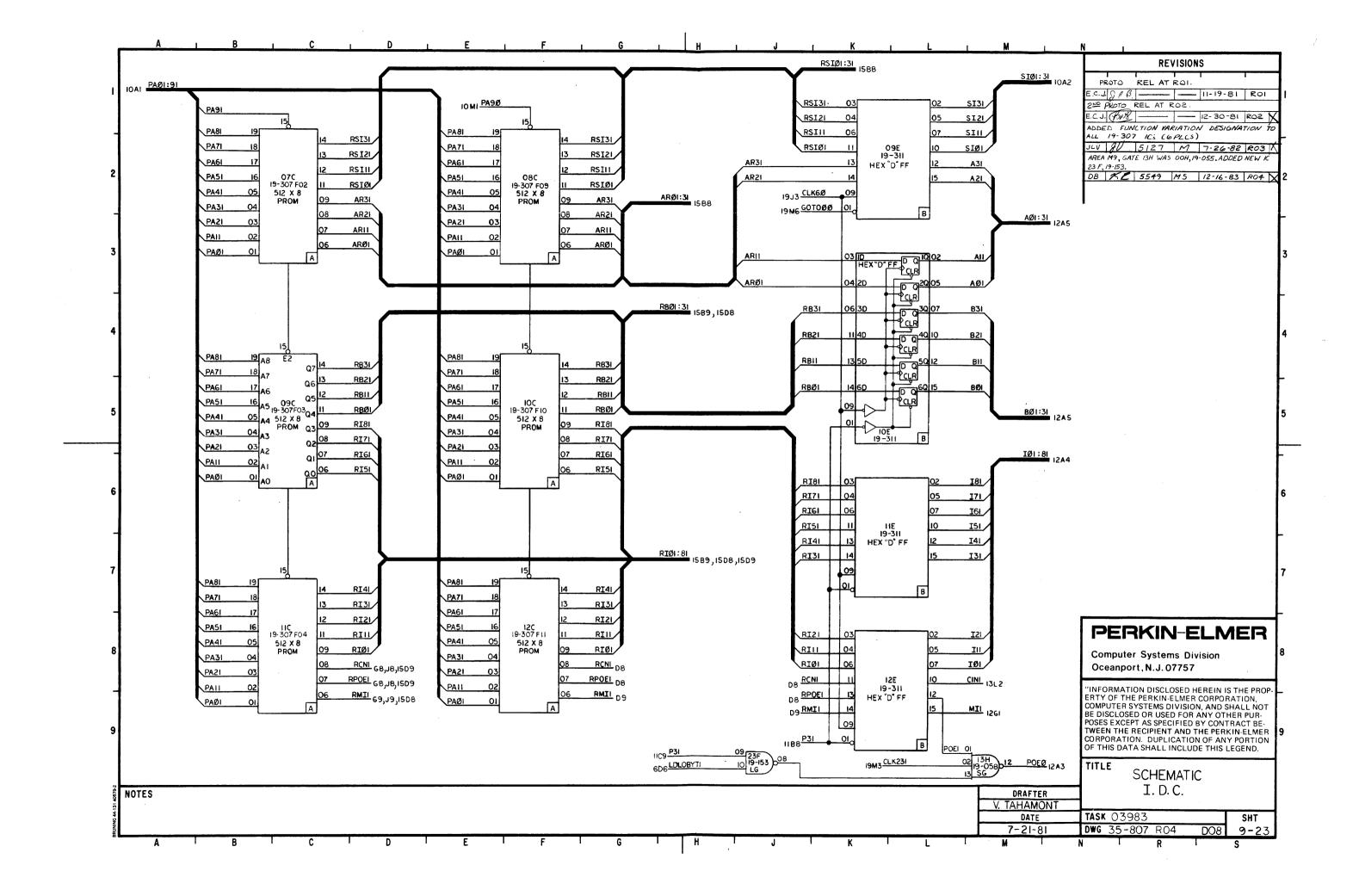

| 3-3<br>3-3.1<br>3-3.2<br>3-3.3                                                                                                      | BLOCK-DIAGRAM ANALYSIS OF IDC                                                                                                                                                                                                                                                        | 3-28<br>3-39                                                             |

| 4                                                                                                                                   | HAINTENANCE                                                                                                                                                                                                                                                                          | 4-1                                                                      |

| 4-1                                                                                                                                 | INTRODUCTION                                                                                                                                                                                                                                                                         | 4-1                                                                      |

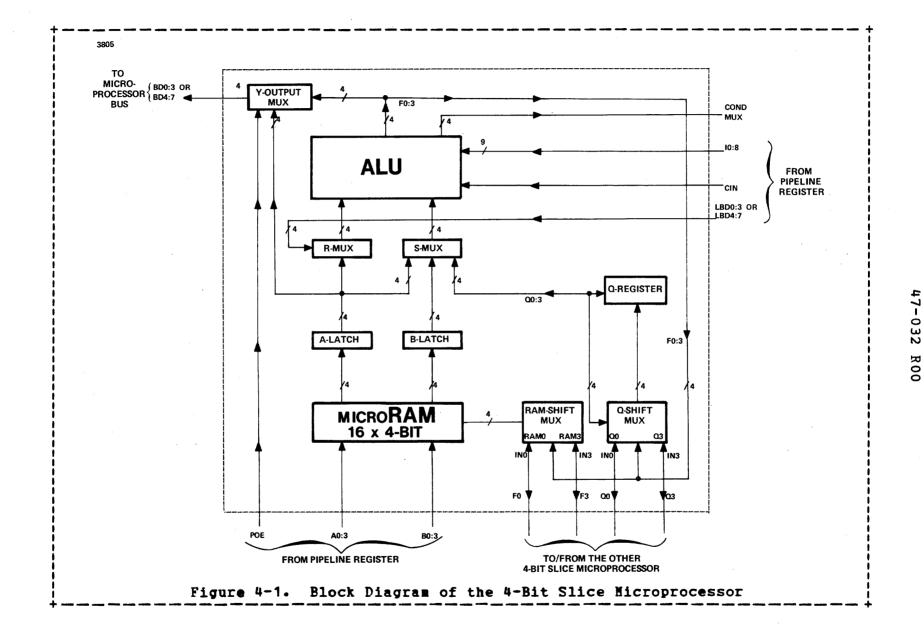

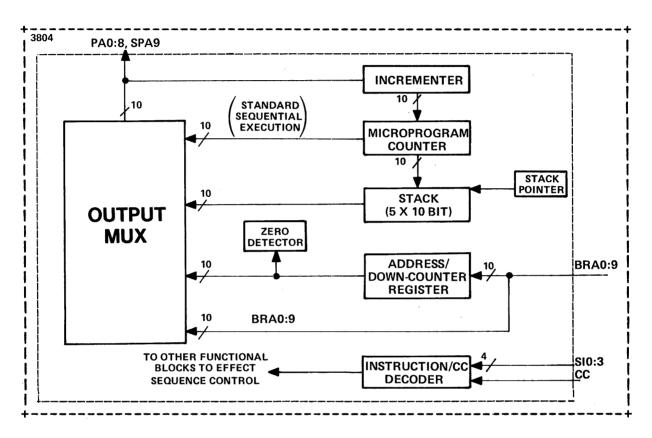

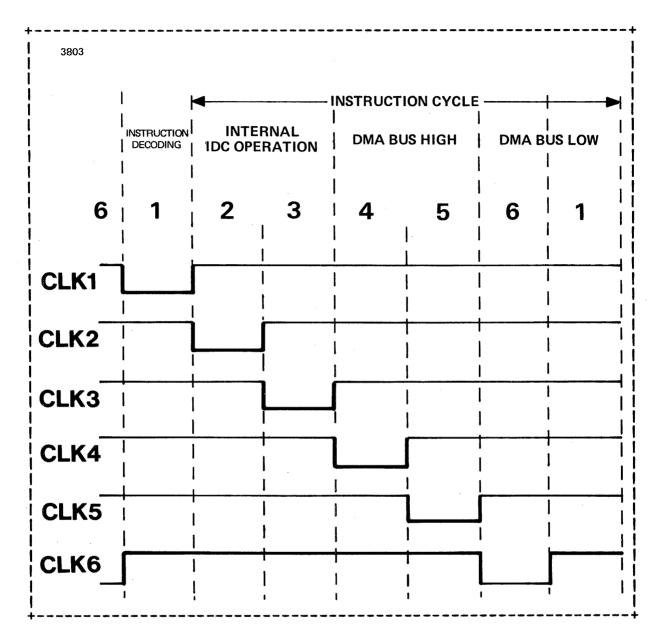

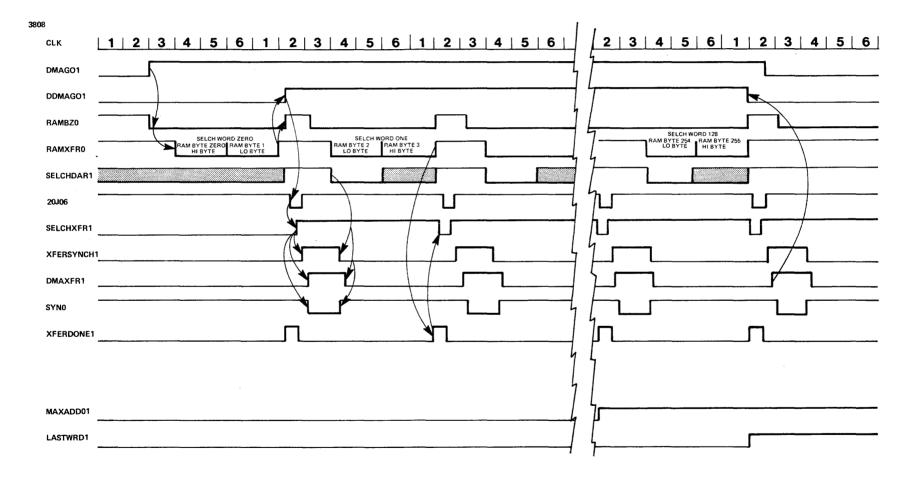

| 4-2<br>4-2.1.1<br>4-2.1.2<br>4-2.1.3<br>4-2.1.4<br>4-2.1.5<br>4-2.2<br>4-2.2.1<br>4-2.3<br>4-2.3.1<br>4-2.4.1<br>4-2.4.2<br>4-2.4.5 | The 4-Bit Slice Microprocessors                                                                                                                                                                                                                                                      | 4-2<br>4-4<br>4-8<br>4-8<br>4-13<br>4-13<br>4-18<br>4-24<br>4-24<br>4-24 |

| 4-3<br>4-3.1<br>4-3.2<br>4-3.2.1<br>4-3.2.2<br>4-4<br>4-4.1<br>4-4.2<br>4-4.3<br>4-4.4<br>4-4.5<br>4-4.6                            | SELCH/MUX BUS INTERFACE  Programmed I/O  DMA I/O  DMA Read Operation  DMA Write Operation  DISK FILE INTERFACE  Unit Selection  Selecting Disk File Cylinder and Head  Disk File Status Check  Decoding Index and Sector Pulses  Disk File Pead Data Path  Disk File Write Data Path | 4-31<br>4-33<br>4-34<br>4-36<br>4-40<br>4-40<br>4-41<br>4-41             |

| 4-5                                                                                                                                 | ERROR CORRECTION CODE (ECC) CIRCUITRY                                                                                                                                                                                                                                                | 4-42                                                                     |

# TABLE OF CONTENTS (Continued)

| Appendix |                                         |                                         | Title                                   |                                         | Page    |

|----------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|---------|

| A        | Table of                                | Mnemonics                               | • • • • • • • • • • •                   | • • • • • • • • • • • • • • • • • • • • | A-1     |

| Index    | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | ••••••                                  | Index-l |

| Drawings |                                         |                                         |                                         |                                         |         |

|          |                                         |                                         |                                         |                                         |         |

#### LIST OF ILLUSTRATIONS

| Figure     | Title                                              | Page  |

|------------|----------------------------------------------------|-------|

| 1-1<br>1-2 | Basic IDC Disk System                              |       |

|            |                                                    |       |

| 2-1        | Installation of an IDC Disk System                 |       |

| 2-2        | Controller Address Switch                          |       |

| 2-3        | File-0 Address Switch                              | 2-20  |

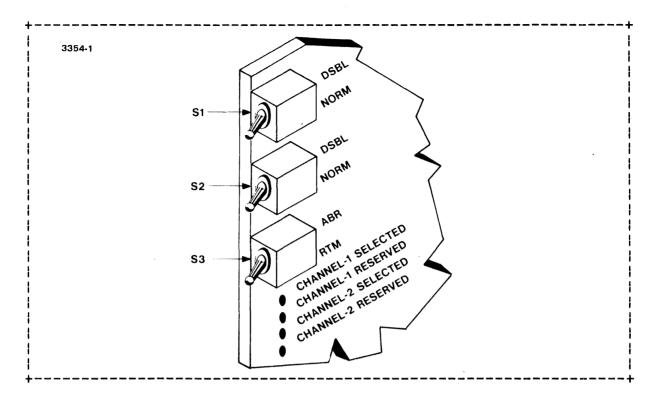

| 2-4        | Switches and Indicators on Dual-Port Steering      |       |

|            | Card                                               | 2-22  |

| 3-1        | Blackbox Diagram of IDC Logic                      | 3-2   |

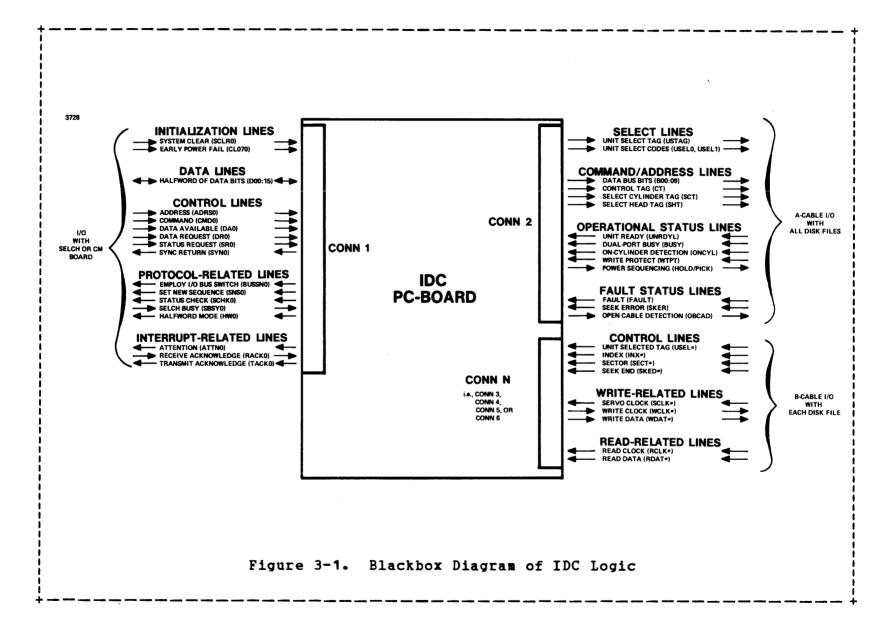

| 3-2        | Connectors on IDC Board                            |       |

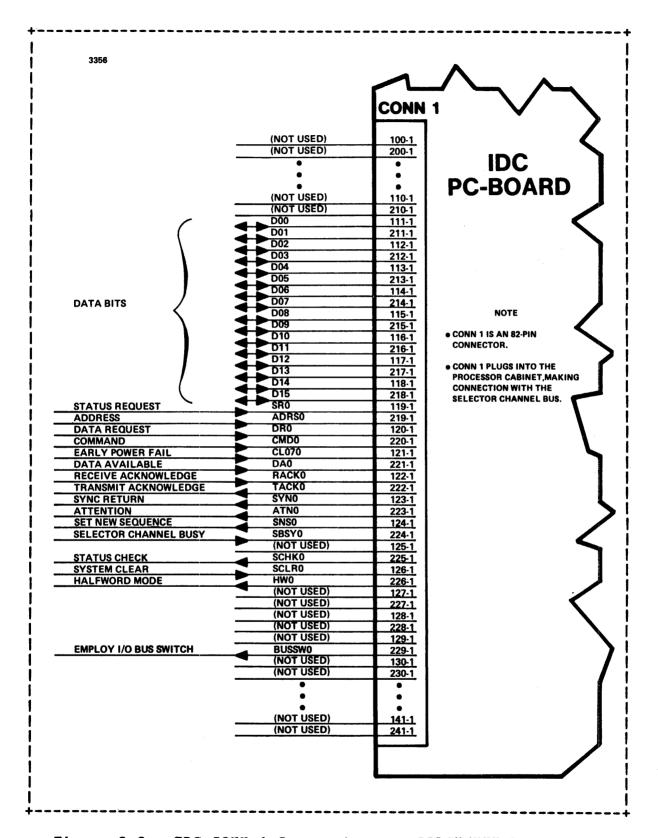

| 3-2<br>3-3 | IDC CONN-1 Connections to SELCH/MUX Bus            |       |

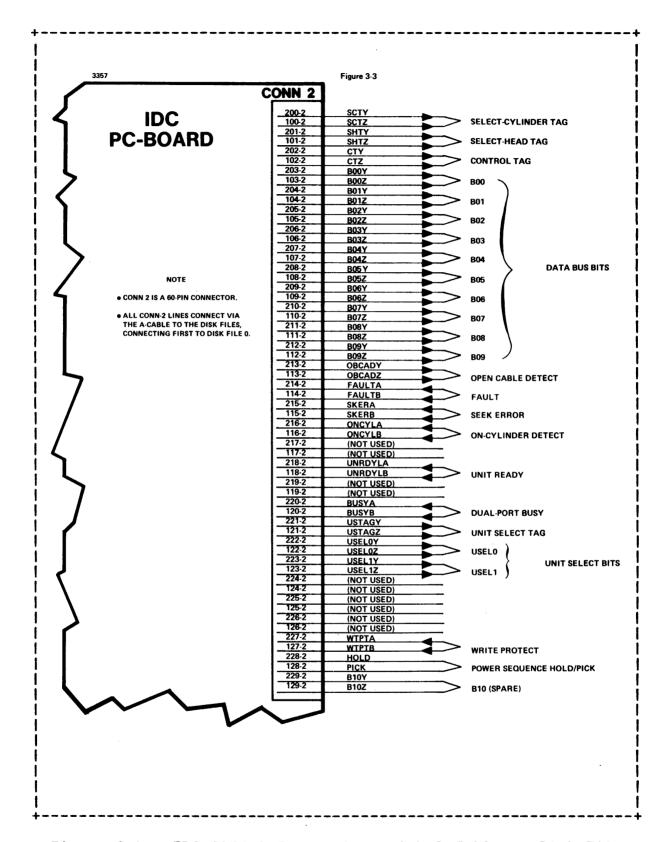

| 3-3<br>3-4 | IDC CONN-2 Connections with A-Cable to Disk        | 5 12  |

| 3 4        | Files                                              | 3-13  |

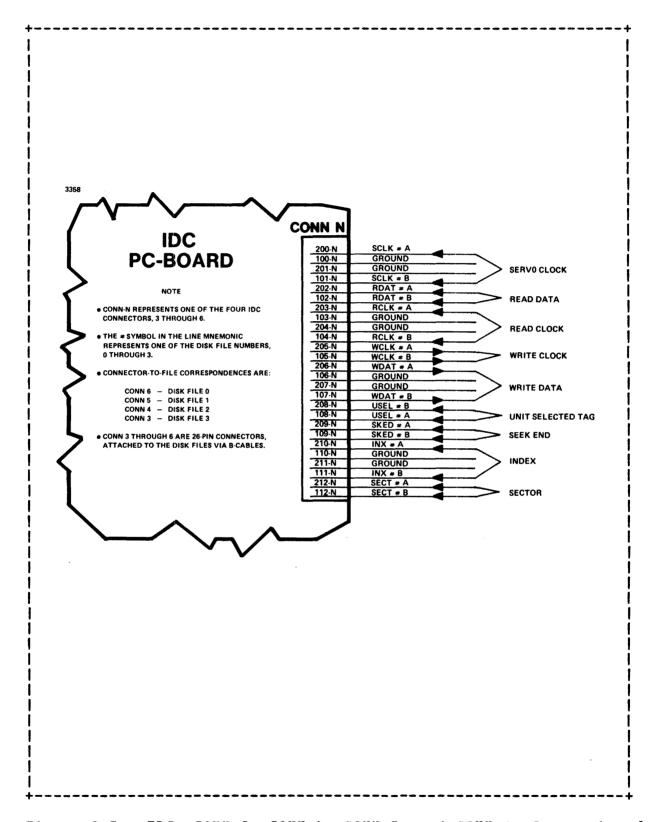

| 3-5        | IDC CONN-3, CONN-4, CONN-5, and CONN-6 Connections | J 1 J |

| 3-5        | with B-Cables to Disk Files                        | 2-11  |

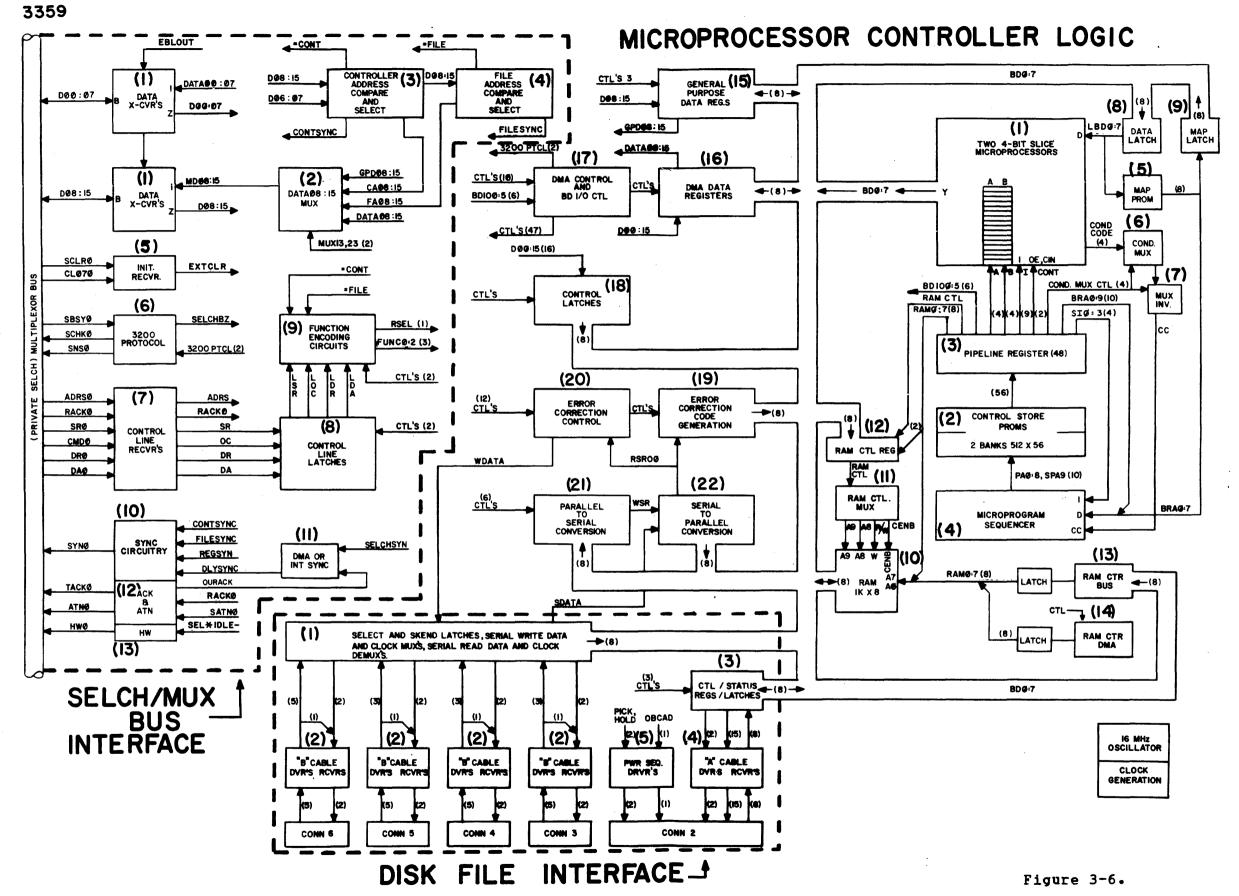

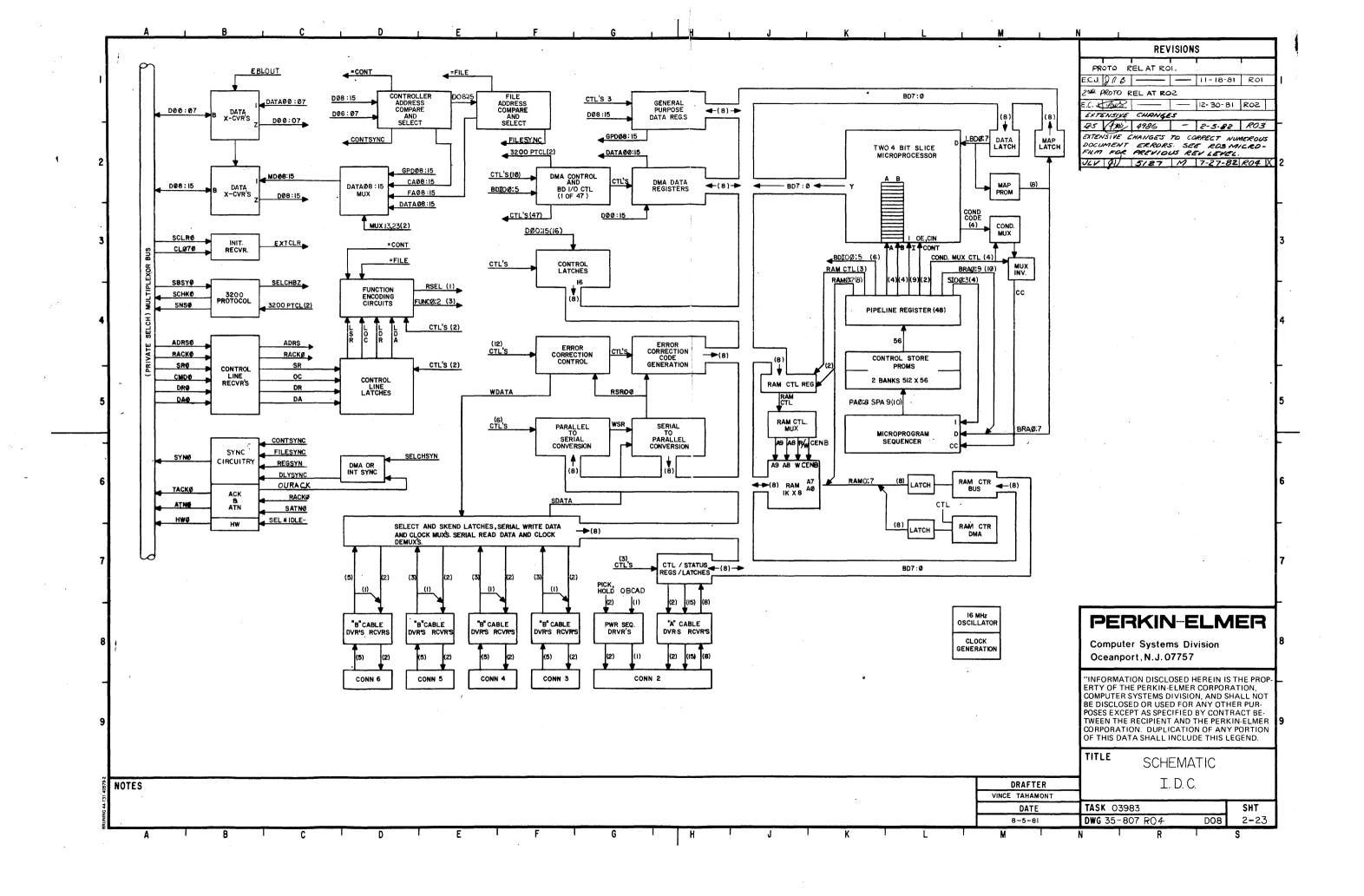

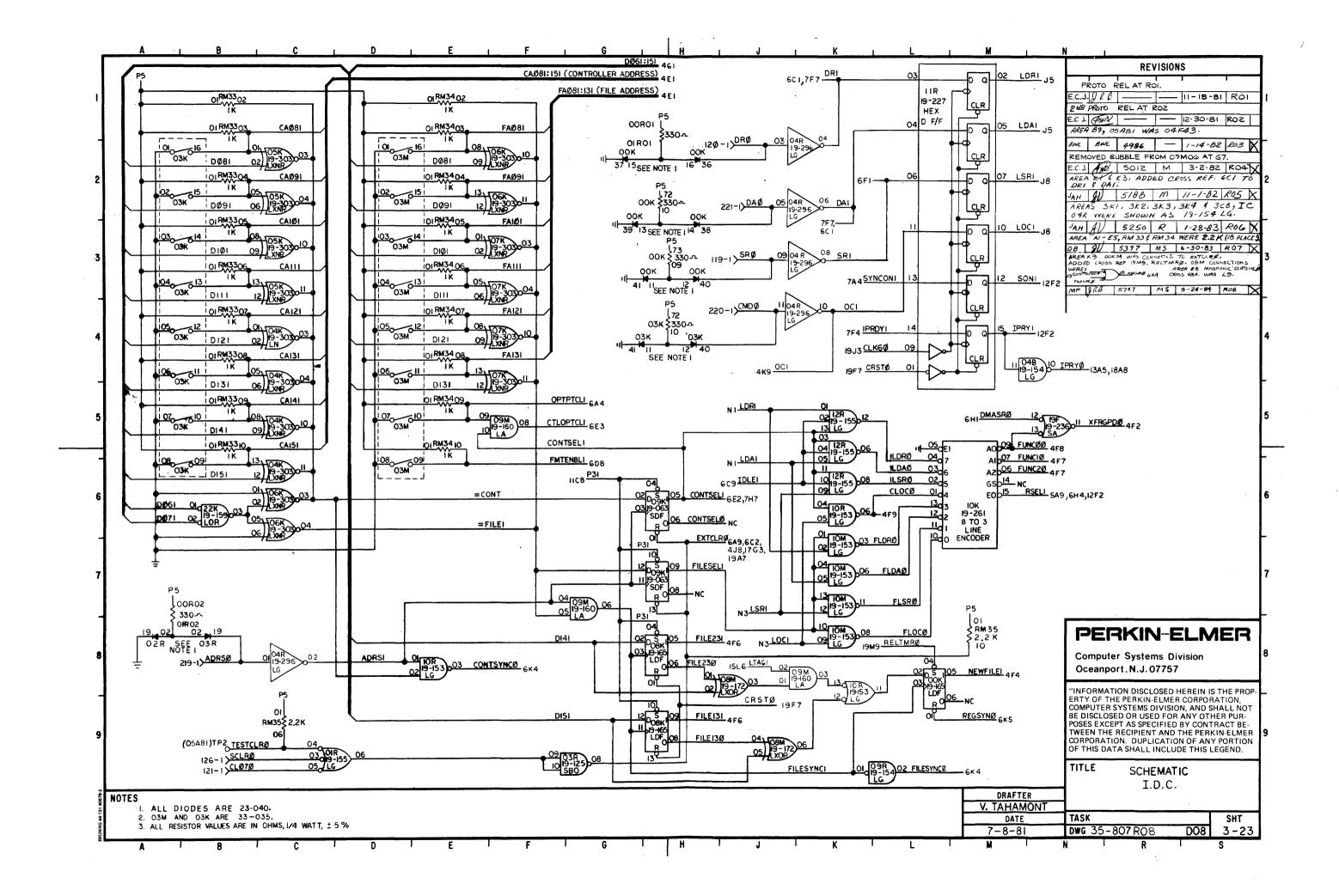

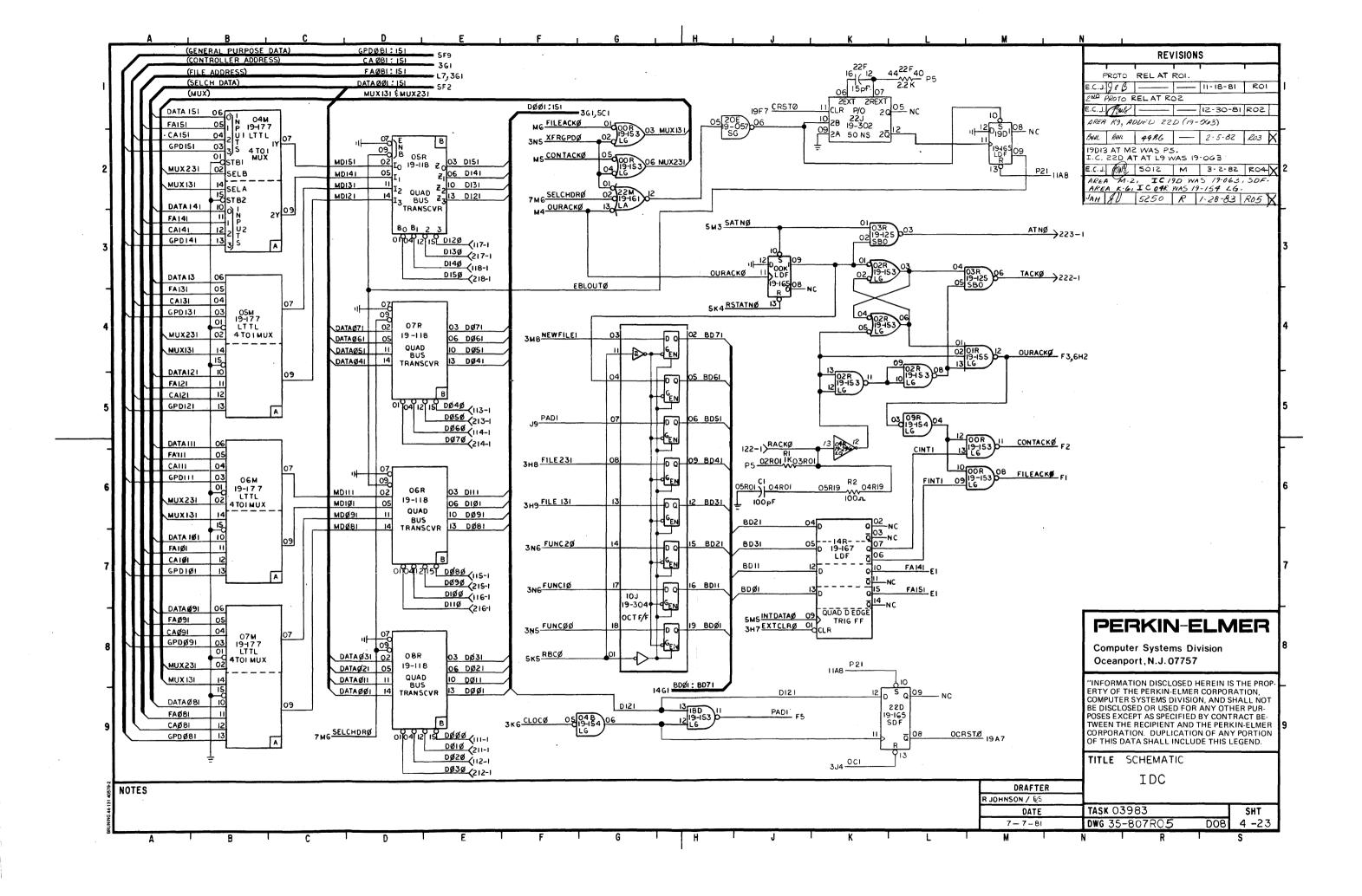

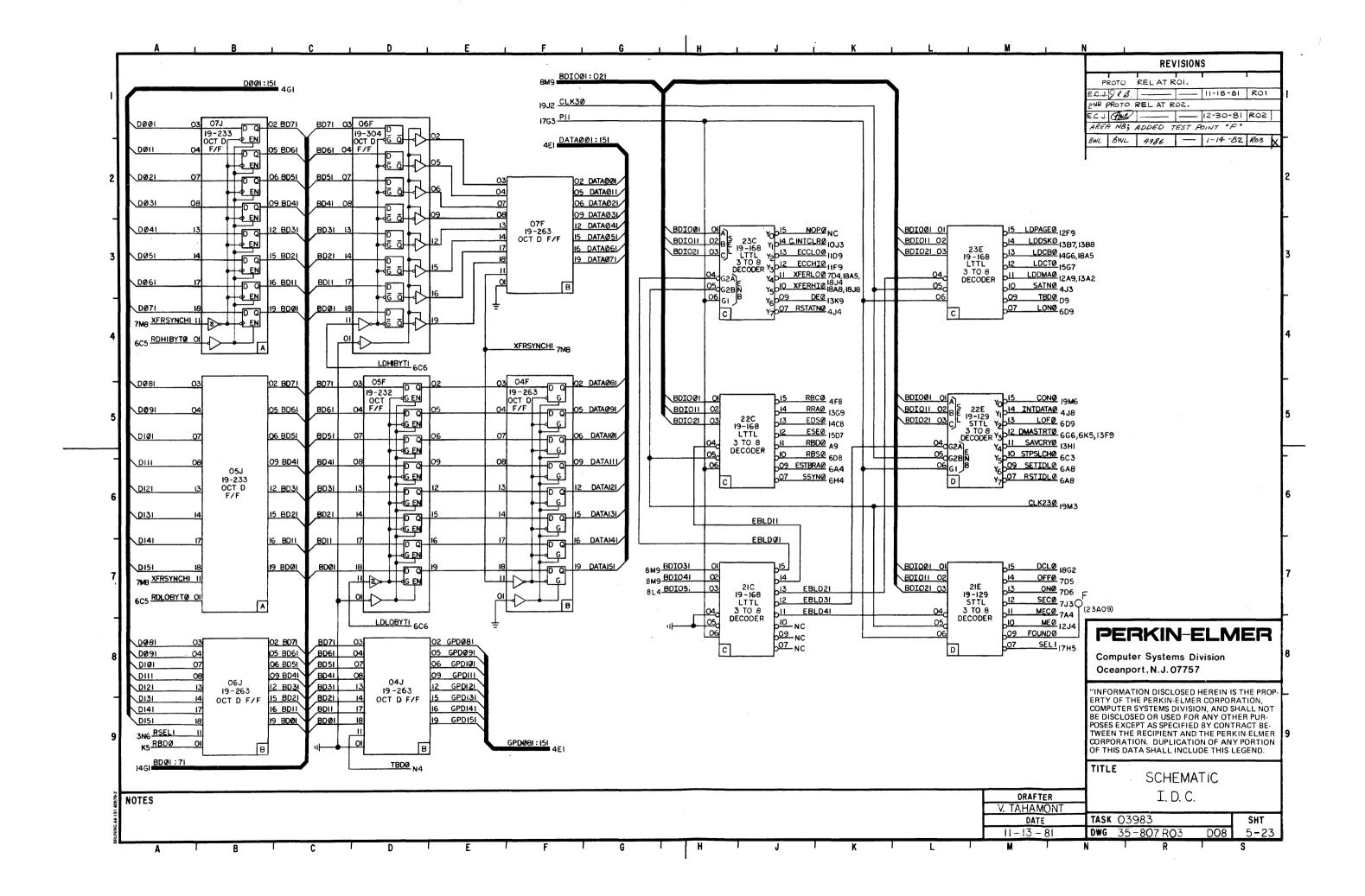

| 3-6        | Block Diagram of the IDC Logic                     |       |

| 3-6        | block blagfam of the ibc Logic                     | 3-20  |

| 4-1        | Block Diagram of the 4-Bit Slice Microprocessor    | 4-11  |

| 4-2        | Block Diagram of the Microprogram Sequencer        |       |

| 4-3        | IDC Operational Cycle                              |       |

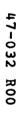

| 4-4        | Timing Signals for a DMA Read Operation            |       |

| 4-5        | Timing Signals for a DMA Write Operation           |       |

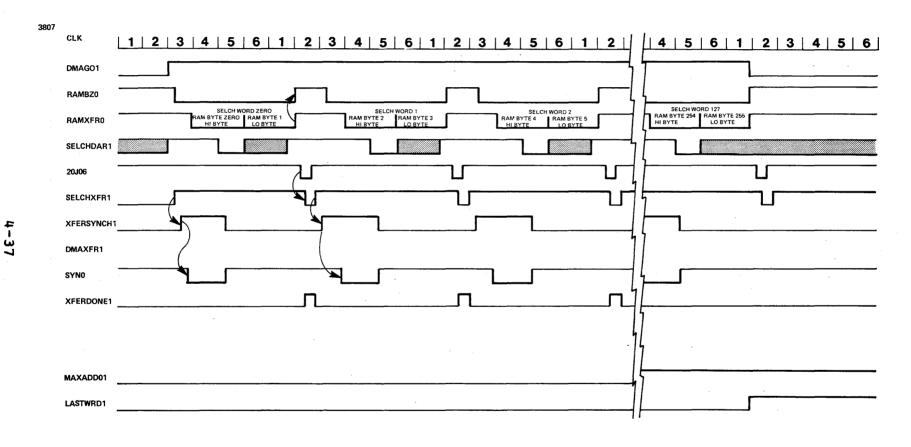

| 4-6        | Tag and Bus Timing                                 |       |

#### LIST OF TABLES

| Table | Title                                              | Page |

|-------|----------------------------------------------------|------|

| 1-1   | List of Related Publications                       | 1-5  |

| 2-1   | Removable-Media 67-Mb MSM Disk System, 60 Hz       | 2-2  |

| 2-2   | Removable-Media 67-Mb MSM Disk System, 50 Hz       |      |

| 2-3   | Fixed-Media 67-Mb MSM Disk System, 60 Hz           |      |

| 2-4   | Fixed-Media 67-Mb MSM Disk System, 50 Hz           |      |

| 2-5   | Fixed-Media 67-Mb MSM Disk System, 60 Hz,          |      |

|       | with HPT                                           | 2-6  |

| 2-6   | Fixed-Media 67-Mb MSM Disk System, 50 Hz, with HPT | 2-7  |

| 2-7   | Removable-Media 256-Mb MSM Disk System, 60 Hz      |      |

| 2-8   |                                                    |      |

|       | Removable-Media 256-Mb MSM Disk System, 50 Hz      |      |

| 2-9   | 27-Mb MC-CDD System, 60 Hz                         |      |

| 2-10  | 27-Mb MC-CDD System, 50 Hz                         |      |

| 2-11  | 54-Mb MC-CDD System, 60 Hz                         |      |

| 2-12  | 54-Mb MC-CDD System, 50 Hz                         |      |

| 2-13  | 81-Mb MC-CDD System, 60 Hz                         |      |

| 2-14  | 81-Mb MC-CDD System, 50 Hz                         |      |

| 2-15  | Fixed-Media 330-Mb Disk System, 60 Hz              |      |

| 2-16  | Fixed-Media 330-Mb Disk System, 50 Hz              |      |

| 2-17  | CDD 50 Disk System 60 Hz                           |      |

| 2-18  | CDD 50 Disk System 50 Hz                           |      |

| 2-19  | Standard Cabling Supplied with IDC Disk Systems    | 2-20 |

| 2-20  | Switches and Indicators on Dual-Port Steering Card | 2-26 |

| 2-21  | AC Voltage and Current Requirements for Disk       | 2-20 |

|       | Files                                              | 2-28 |

|       |                                                    |      |

| 3-1   | Bus Line Contents Corresponding to Active          |      |

| • •   | Output Tag                                         | 3-19 |

| 3-2   | Control Functions Activated by Control Tag         |      |

|       | CTY/CTZ                                            | 3-20 |

| 4-1   | Dib Definitions of the EE Dib Misselmstanding      | 4 2  |

| 4-1   | Bit Definitions of the 56-Bit Microinstruction     |      |

|       | BDIO0:5 Values for Microprocessor Bus Functions    |      |

| 4-3   | MA:MC Values for CC Output                         | 4-9  |

| 4-4   | Microinstruction Bits IO:2 for ALU Source Control  | 4-14 |

| 4-5   | Microinstruction Bits I3:5 for ALU Functions       | 4-15 |

| 4-6   | Source-Function Matrix for Microinstruction        |      |

|       | Bits I0:5                                          | 4-16 |

| 4-7   | Microinstruction Bits I6:8 for ALU Destination     |      |

|       | Control                                            |      |

| 4-8   | SIO:3 Input to Microprogram Sequencer              |      |

| 4-9   | FUNCO: 2 Values for Encoded MUX Bus Functions      | 4-32 |

#### CHAPTER 1

#### OVERVIEW

#### 1-1 DESCRIPTION OF AN IDC DISK SYSTEM

A disk system, as defined here, is the hardware that provides a processor with disk support. That is, it provides a processor with the capability of writing to and reading from disk media. And, basically, a disk system consists of these hardware components:

- (a) one or more disk files (a disk file is a disk drive with removable or fixed disk media);

- (b) a controller for interfacing these disk files to the processor; and

- (c) necessary cabling for interconnecting the controller hardware and disk files.

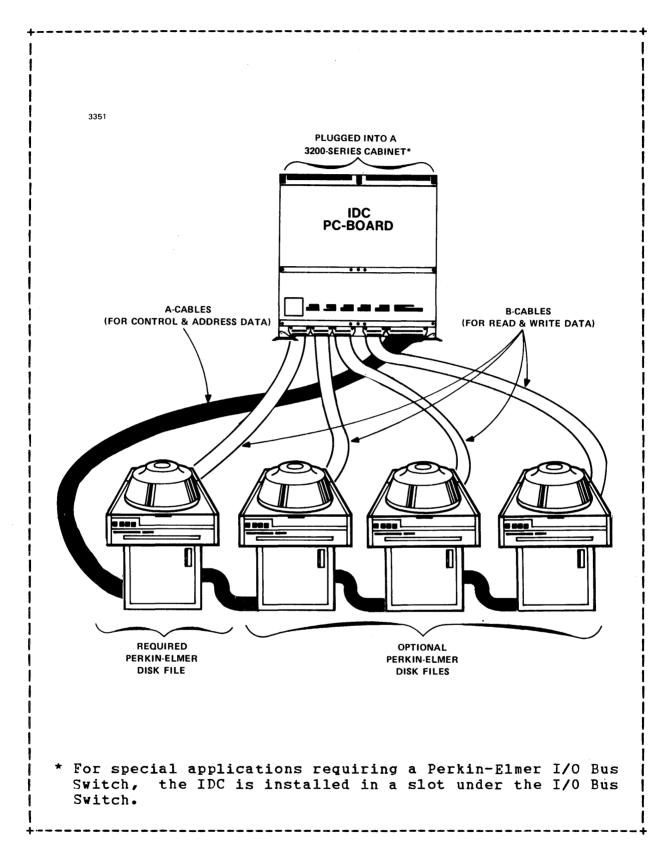

A Perkin-Elmer Intelligent Disk Controller (IDC) Disk System, then, is hardware that provides a Perkin-Elmer 3200-Series processor with support for direct-access devices, or disk files. Chapter 2 specifies all components of the various IDC disk systems. But, as basically shown in Figure 1-1, an IDC disk system consists of:

- (a) one controller board, a printed circuit (PC) board referred to as the IDC;

- (b) one to four Perkin-Elmer disk files, with specially formatted disk media; and

- (c) necessary cabling for connecting the IDC and disk files.

Figure 1-2 shows the IDC PC-board. This board contains microprocessor logic for directly interfacing disk files with the 3200-Series processor. Data transfer to and from the processor, via a Direct Memory Access (DMA) port, is through either a 3200 Selector Channel (SELCH) or Channel Manager (CM). For data recovery from disk read errors, the IDC has the capability of performing strobe-offset or track-offset sequences. It also has an automatic error-correction capability for correcting error bursts of up to 11 bits in length. For detailed programming information on the characteristics of the IDC, refer to Perkin-Elmer Publication 50-007; see Table 1-1.

The IDC can interface a maximum of four disk files to the 3200-Series processor, with overlapping seek and restore operations. These can be any combination of Perkin-Elmer disk files, i.e., Mass Storage Modules (MSMs) and/or Medium Capacity - Cartridge Disk Drives (MC-CDDs). For example, four interfaced files might be this combination: 67-Megabyte (Mb) MSM, 256-Mb MSM, 256-Mb MSM, and 81-Mb CDD; or, this combination: 256-Mb MSM, 256-Mb MSM, and 54-Mb CDD; or, this: 27-Mb CDD, 54-Mb CDD, 81-Mb CDD, and 256-Mb MSM. The IDC board will also support future Perkin-Elmer disk files. For performance data and other information on the supported disk files, refer to the vendor manuals listed in Table 1-1.

#### NOTE

The disk media of an IDC system have a physical format that is different from and incompatible with the format of MSM disk media. For additional information on these differences, refer to Perkin-Elmer Publication 50-007.

MSM disk drives allow installation of a dual-port option which permits two controllers to share a single disk file; these two controllers can be in the same processor cabinet or in separate processor cabinets. The MC-CDD and CDD 50 systems are not capable of dual-port operation.

Cabling from the IDC board to the disk files is simple and direct because there is no interface, like a control panel, between the board and interfaced files.

Figure 1-1. Basic IDC Disk System

5001

Figure 1-2. IDC PC-Board

#### 1-2 LIST OF RELATED PUBLICATIONS

Table 1-1 lists the Perkin-Elmer manuals related to IDC disk systems.

Table 1-1. List of Related Publications

| ++                        |                                                                                                                             |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| PUBLICATION  <br>  NUMBER | PERKIN-ELMER MANUAL                                                                                                         |

| 29-356                    | M48-018 Input/Output Bus Switch Manual-Control<br>Panel Installation Manual                                                 |

| 29-585                    | 80-Mb Maintenance Manual Package (This package contains vendor manuals for the 67-Mb MSM removable-media disk systems.)     |

| 29-586                    | 300-Mb Maintenance Manual Package (This package contains vendor manuals for the 256-Mb MSM removable-media disk systems.)   |

| 29-727                    | Model 3200 Selector Channel (SELCH) Maintenance<br>Manual                                                                   |

| 29-729                    | 80-Mb (Fixed) Maintenance Manual Package (This package contains vendor manuals for the 67-Mb MSM fixed-media disk systems.) |

| 29-749                    | Vendor Manual Cartridge Disk Drive (This manual is for the 27-Mb, 54-Mb, and 81-Mb MC-CDD systems.)                         |

| 47-016                    | Channel Manager (CM)                                                                                                        |

| 50-007                    | Intelligent Disk Controller (IDC) Programmer<br>Reference Manual (includes CDD 50 system)                                   |

| 51-041                    | 330-Mb Disk Drive Vendor Manual                                                                                             |

#### CHAPTER 2

#### INSTALLATION

1

#### 2-1 INTRODUCTION

This chapter gives detailed parts lists and instructions for installing an intelligent disk controller (IDC) system. Before reading it, you should be familiar with Chapter 1.

#### 2-2 DETAILED PARTS LISTS

Tables 2-1 through 2-18 in this section list the components and give a product number-to-part number cross reference for the disk systems supported by the IDC. Corresponding to these tables are the 18 IDC disk systems:

|       | DISK   |                                                                                                                                       |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| TABLE | SYSTEM | DESCRIPTION                                                                                                                           |

|       |        |                                                                                                                                       |

|       | 1      | Removable-Media 67-Mb MSM Disk System, 60 Hertz (Hz)                                                                                  |

| 2-2   | 2      | Removable-Media 67-Mb MSM Disk System, 50 Hz                                                                                          |

| 2-3   | 3      | Removable-Media 67-Mb MSM Disk System, 50 Hz<br>Fixed-Media 67-Mb MSM Disk System, 60 Hz                                              |

| 2-4   | 4      | Fixed-Media 67-Mb MSM Disk System, 50 Hz                                                                                              |

| 2-5   | 5      | Fixed-Media 67-Mb MSM Disk System, 60 Hz Fixed-Media 67-Mb MSM Disk System, 50 Hz Fixed-Media 67-Mb MSM Disk System, 60 Hz, with HPT* |

| 2-6   | 6      | Fixed-Media 67-Mb MSM Disk System, 50 Hz, with HPT*                                                                                   |

| 2-7   | 7      | Removable-Media 256-Mb MSM Disk System, 60 Hz                                                                                         |

| 2-8   | 8      | Removable-Media 256-Mb MSM Disk System, 60 Hz<br>Removable-Media 256-Mb MSM Disk System, 50 Hz<br>27-Mb MC-CDD System, 60 Hz          |

| 2-9   | 9      | 27-Mb MC-CDD System, 60 Hz                                                                                                            |

| 2-10  | 10     | 27-Mb MC-CDD System, 50 Hz                                                                                                            |

| 2-11  | 11     | 54-Mb MC-CDD System, 60 Hz                                                                                                            |

|       |        | 54-Mb MC-CDD System, 50 Hz                                                                                                            |

|       |        | 81-Mb MC-CDD System, 60 Hz                                                                                                            |

|       |        | 81-Mb MC-CDD System, 50 Hz                                                                                                            |

| 2-15  | 15     | Fixed-Media 330-Mb Disk System, 60 Hz                                                                                                 |

|       |        | Fixed-Media 330-Mb Disk System, 50 Hz                                                                                                 |

|       |        | CDD 50 Disk System, 60 Hz                                                                                                             |

|       |        | CDD 50 Disk System, 50 Hz                                                                                                             |

See Section 2-2.1 for additional cabling information.

<sup>\*</sup> HPT refers to the Head Per Track option available with the 67-Mb fixed-media disk.

Table 2-1. Removable-Media 67-Mb MSM Disk System, 60 Hz

| PRODUCT NO                                                             |                                                                                                                                                                                                                                              | PART  <br>NUMBER                                                                                                                 |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| (1)<br>  (1)                                                           | •                                                                                                                                                                                                                                            | 02-798F01<br>47-032<br>29-585<br>50-007<br>06-267<br>06-268<br>17-295F01<br>27-081F04<br>17-447<br>24-080F02<br>35-636<br>35-807 |

| M60-110<br>  (1)<br>  (1)<br>  (1)<br>  (1)<br>  (1)<br>  (1)<br>  (1) | Expansion Drive, 60 Hz  Vendor Maintenance Manual Package Ground Strap, 4.57 m (15 ft) Ground Strap, 9.14 m (30 ft) External B-Cable, 9.14 m (30 ft) 67-Mb Disk Drive, 60 Hz, and Cable External A-Cable, 4.57 m (15 ft) Formatted Disk Pack | 02-801F01                                                                                                                        |

| M60-116                                                                | 67-Mb Formatted Disk Pack                                                                                                                                                                                                                    |                                                                                                                                  |

Table 2-2. Removable-Media 67-Mb MSM Disk System, 50 Hz

| PRODUCT NO  <br>  (QUANTITY) |                                                                                                                                                                                                                                                                                                                    | PART  <br>NUMBER                                                                                                                 |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| (1)<br>  (1)<br>  (1)        | Single Drive System, 50 Hz, 220 V  IDC Installation/Maintenance Manual Vendor Maintenance Manual Package IDC Programming Manual Test Program Format Program Ground Strap, 9.14 m (30 ft) 67-Mb Disk Drive, 50 Hz, and Cable Ext A- and B-Cable, 9.14 m (30 ft) Formatted Disk Pack Disk-Drive Terminator IDC Board | 02-798F02<br>47-032<br>29-585<br>50-007<br>06-267<br>06-268<br>17-295F01<br>27-081F05<br>17-448<br>24-080F02<br>35-636<br>35-807 |

| (1)                          | Expansion Drive, 50 Hz  Vendor Maintenance Manual Package Ground Strap, 4.57 m (15 ft) Ground Strap, 9.14 m (30 ft) External B-Cable, 9.14 m (30 ft) 67-Mb Disk Drive, 50 Hz, and Cable External A-Cable, 4.57 m (15 ft) Formatted Disk Pack                                                                       | 02-801F02                                                                                                                        |

| <br>  M60-116                | 67-Mb Formatted Disk Pack                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

Table 2-3. Fixed-Media 67-Mb MSM Disk System, 60 Hz

| PRODUCT NO  <br>  (QUANTITY)                                       | ·                                                                                                                                                                                                                                                                                                                                                                  | PART  <br>NUMBER                                                                                                                    |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| (1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | MSM 80-F, 60 Hz, 115 V  IDC Installation/Maintenance Manual Vendor Maintenance Manual Package IDC Programming Manual Test Program Format Program Ground Strap, 1.83 m (6 ft) 67-Mb Fixed-Media Disk Drive, 115 V Heavy-Duty Shielded MSM A-Cable, 60 pins, 4.57 m (15 ft) Heavy-Duty Shielded MSM B-Cable, 26 pins, 4.57 m (15 ft) Disk-Drive Terminator IDC Board | 02-799F01<br>47-032<br>29-729<br>50-007<br>06-267<br>06-268<br>17-295F04<br>27-115F05<br>17-521F01<br>17-520F01<br>35-636<br>35-807 |

| M60-112<br>  (1)<br>  (1)<br>  (1)<br>  (1)<br>  (1)               | MSM 80-F Expansion, 60 Hz, 115 V  Vendor Maintenance Manual Package Chassis Ground Strap, 1.83 m (6 ft) 67-Mb Fixed-Media Disk Drive, 115 V Heavy-Duty Shielded MSM A-Cable, 60 Pins, 2.44 m (8 ft) Heavy-Duty Shielded MSM B-Cable, 26 Pins, 4.57 m (15 ft)                                                                                                       | 02-802F01<br>29-729<br>17-295F04<br>27-115F05<br>17-521F02                                                                          |

Table 2-4. Fixed-Media 67-Mb MSM Disk System, 50 Hz

| PRODUCT NO  <br>  (QUANTITY) |                                                                                                                                                                                                                                                                                                                                                                    | PART  <br>NUMBER                                                                                                                    |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| M60-105                      | MSM 80-F, 50 Hz, 220 V  IDC Installation/Maintenance Manual Vendor Maintenance Manual Package IDC Programming Manual Test Program Format Program Ground Strap, 1.83 m (6 ft) 67-Mb Fixed-Media Disk Drive, 220 V Heavy-Duty Shielded MSM A-Cable, 60 pins, 4.57 m (15 ft) Heavy-Duty Shielded MSM B-Cable, 26 pins, 4.57 m (15 ft) Disk-Drive Terminator IDC Board | 02-799F02<br>47-032<br>29-729<br>50-007<br>06-267<br>06-268<br>17-295F04<br>27-115F06<br>17-521F01<br>17-520F01<br>35-636<br>35-807 |

| M60-113  (1) (1) (1) (1) (1) | MSM 80-F Expansion, 50 Hz, 220V  Vendor Maintenance Manual Package Chassis Ground Strap, 1.83 m (6 ft) 67-Mb Fixed-Media Disk Drive, 220 V Heavy-Duty Shielded MSM A-Cable, 60 Pins, 2.44 m (8 ft) Heavy-Duty Shielded MSM B-Cable, 26 Pins, 4.57 m (15 ft)                                                                                                        |                                                                                                                                     |

Table 2-5. Fixed-Media 67-Mb MSM Disk System, 60 Hz, with HPT

| PRODUCT NO  <br>  (QUANTITY)                                       | •                                                                                                                                                                                                                                                                                                                                                           | PART  <br>NUMBER                                                                                                       |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| <br>  M60-106                                                      | MSM 80-F w/HPT Option, 60 Hz, 115 V                                                                                                                                                                                                                                                                                                                         | 02-799 <b>F</b> 03                                                                                                     |

| (1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | IDC Installation/Maintenance Manual Vendor Maintenance Manual Package IDC Programming Manual Test Program Format Program Ground Strap, 1.83 m (6 ft) 67-Mb Fixed-Media Disk Drive, with 1.6-Mb HPT, 115 V Heavy-Duty Shielded MSM A-Cable, 60 pins, 4.57 m (15 ft) Heavy-Duty Shielded MSM B-Cable, 26 pins, 4.57 m (15 ft) Disk-Drive Terminator IDC Board | 47-032<br>29-729<br>50-007<br>06-267<br>06-268<br>17-295F04<br>27-115F07<br>17-521F01<br>17-520F01<br>35-636<br>35-807 |

| M60-114 (1) (1) (1) (1) (1)                                        | MSM 80-F Expansion with HPT, 60 Hz, 115 V  Vendor Maintenance Manual Package Chassis Ground Strap, 1.83 m (6 ft) 67-Mb Fixed-Media Disk Drive, with 1.6-Mb HPT, 115 V Heavy-Duty Shielded MSM A-Cable, 60 Pins, 2.44 m (8 ft) Heavy-Duty Shielded MSM B-Cable, 26 Pins, 4.57 m (15 ft)                                                                      | 02-802F03<br>29-729<br>17-295F04<br>27-115F07<br>17-521F02                                                             |

Table 2-6. Fixed-Media 67-Mb MSM Disk System, 50 Hz, with HPT

| PRODUCT NO  <br>  (QUANTITY)                                       | ·                                                                                                                                                                                                                                                                                                                                                           | PART  <br>NUMBER                                                                                                       |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| M60-107                                                            | MSM 80-F w/HPT Option, 50 Hz, 220 V                                                                                                                                                                                                                                                                                                                         | 02-799F04                                                                                                              |

| (1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | IDC Installation/Maintenance Manual Vendor Maintenance Manual Package IDC Programming Manual Test Program Format Program Ground Strap, 1.83 m (6 ft) 67-Mb Fixed-Media Disk Drive, with 1.6-Mb HPT, 220 V Heavy-Duty Shielded MSM A-Cable, 60 pins, 4.57 m (15 ft) Heavy-Duty Shielded MSM B-Cable, 26 pins, 4.57 m (15 ft) Disk-Drive Terminator IDC Board | 47-032<br>29-729<br>50-007<br>06-267<br>06-268<br>17-295F04<br>27-115F08<br>17-521F01<br>17-520F01<br>35-636<br>35-807 |

| (1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)                             | MSM 80-F Expansion with HPT, 50 Hz, 220 V  Vendor Maintenance Manual Package Chassis Ground Strap, 1.83 m (6 ft) 67-Mb Fixed-Media Disk Drive, with 1.6-Mb HPT, 220 V Heavy-Duty Shielded MSM A-Cable, 60 Pins, 2.44 m (8 ft) Heavy-Duty Shielded MSM B-Cable, 26 Pins, 4.57 m (15 ft)                                                                      | 02-802F04<br>29-729<br>17-295F04<br>27-115F08<br>17-521F02<br>17-520F01                                                |

Table 2-7. Removable-Media 256-Mb MSM Disk System, 60 Hz

| PRODUCT NO  <br>  (QUANTITY)                     |                                                                                                                                                                                                                                                                                                  | PART  <br>  NUMBER                                                                                                               |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| (1)<br>  (1)<br>  (1)<br>  (1)<br>  (1)<br>  (1) | Single Drive System, 60 Hz, 115 V  IDC Installation/Maintenance Manual Vendor Maintenance Manual IDC Programming Manual Test Program Format Program Ground Strap, 9.14 m (30 ft) 256-Mb Disk Drive, 60 Hz Ext A- and B-Cable, 9.14 m (30 ft) Formatted Disk Pack Disk-Drive Terminator IDC Board | 02-797F01<br>47-032<br>29-586<br>50-007<br>06-267<br>06-268<br>17-295F01<br>27-082F04<br>17-447<br>24-079F02<br>35-636<br>35-807 |

| (1)<br>  (1)<br>  (1)<br>  (1)                   | Expansion Drive, 60 Hz  Vendor Maintenance Manual Ground Strap, 4.57 m (15 ft) Ground Strap, 9.14 m (30 ft) External B-Cable, 9.14 m (30 ft) 256-Mb Disk Drive, 60 Hz External A-Cable, 4.57 m (15 ft) Formatted Disk Pack                                                                       | 02-800F01                                                                                                                        |

| <br>  M60-117                                    | 256-Mb Formatted Disk Pack                                                                                                                                                                                                                                                                       |                                                                                                                                  |

Table 2-8. Removable-Media 256-Mb MSM Disk System, 50 Hz

| +                                                    |                                                                                                                                                                                                                                       | PART  <br>NUMBER                                                                                                                 |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| (1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | 256-Mb Disk Drive, 50 Hz                                                                                                                                                                                                              | 02-797F02<br>47-032<br>29-586<br>50-007<br>06-267<br>06-268<br>17-295F01<br>27-082F05<br>17-447<br>24-079F02<br>35-636<br>35-807 |

| (1)<br>(1)<br>(1)<br>(1)                             | Expansion Drive, 50 Hz  Vendor Maintenance Manual Ground Strap, 4.57 m (15 ft) Ground Strap, 9.14 m (30 ft) External B-Cable, 9.14 m (30 ft) 256-Mb Disk Drive, 50 Hz, and Cable External A-Cable, 4.57 m (15 ft) Formatted Disk Pack | 02-800F02<br>  29-586<br>  17-295F03<br>  17-295F01<br>  17-448<br>  27-082F05<br>  17-449<br>  24-079F02                        |

| <br>  M60-117                                        | 256-Mb Formatted Disk Pack                                                                                                                                                                                                            |                                                                                                                                  |

Table 2-9. 27-Mb MC-CDD System, 60 Hz

| +                        |                                                                                                                                                                                                                                                                 | PART  <br>NUMBER                                                                                                                             |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| M46-770                  | MC-CDD 27, 60 Hz, 115 V                                                                                                                                                                                                                                         | 02-777F03                                                                                                                                    |

| (1)<br>(1)<br>(1)<br>(1) | IDC Installation/Maintenance Manual Vendor Maintenance Manual IDC Programming Manual Test Program Format Program Ground Strap, 1.07 m (42 in) 27-Mb MC-CDD, 60 Hz, 115 V Ext A- and B-Cable, 4.57 m (15 ft) Disk-Drive Terminator IDC Board Mounting Kit        | 47-032<br>  29-749<br>  50-007<br>  06-267<br>  06-268<br>  17-295F05<br>  27-131F03<br>  17-447F01M01  <br>  35-815<br>  35-807<br>  16-876 |

| M46-732                  | Expansion Drive, MC-CDD 27, 60 Hz                                                                                                                                                                                                                               | 02-761F01                                                                                                                                    |

| (1)<br>(1)<br>(1)        | Vendor Maintenance Manual Ground Strap, 1.07 m (42 in) Ground Strap, 1.83 m (6 ft) External B-Cable, 4.57 m (15 ft) 27-Mb MC-CDD, 60 Hz, 115 V External A-Cable, 1.07 m (42 in) External A-Cable, 4.57 m (15 ft) Formatted Disk Cartridge, 13.5 Mb Mounting Kit | 29-749<br>  17-295F05<br>  17-295F04<br>  17-448F01<br>  27-131F03<br>  17-411F03M01<br>  17-449<br>  24-104F02<br>  16-876                  |

| M46-776                  | l3.5-Mb Formatted Disk Cartridge                                                                                                                                                                                                                                |                                                                                                                                              |

Table 2-10. 27-Mb MC-CDD System, 50 Hz

| PRODUCT NO  <br>  (QUANTITY) |                                                                                                                                                                                                                                                                                                    | PART  <br>NUMBER                                                                                                         |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| (1)                          | MC-CDD 27, 50 Hz, 220 V  IDC Installation/Maintenance Manual Vendor Maintenance Manual IDC Programming Manual Test Program Format Program Ground Strap, 1.07 m (42 in) 27-Mb MC-CDD, 50 Hz, 220 V Ext A- and B-Cable, 4.57 m (15 ft) Disk-Drive Terminator IDC Board                               | 02-777F04                                                                                                                |

| (1)                          | Mounting Kit                                                                                                                                                                                                                                                                                       | 16-876  <br>                                                                                                             |

|                              | Expansion Drive, MC-CDD 27, 50 Hz  Vendor Maintenance Manual Ground Strap, 1.07 m (42 in) Ground Strap, 1.83 m (6 ft) External B-Cable, 4.57 m (15 ft) 27-Mb MC-CDD, 50 Hz, 220 V External A-Cable, 1.07 m (42 in) External A-Cable, 4.57 m (15 ft) Formatted Disk Cartridge, 13.5 Mb Mounting Kit | 02-761F02<br>29-749<br>17-295F05<br>17-295F04<br>17-448F01<br>27-131F04<br>17-411F03M01<br>17-449<br>24-104F02<br>16-876 |

Table 2-11. 54-Mb MC-CDD System, 60 Hz

| +          |                                                      | <b>+</b>     |

|------------|------------------------------------------------------|--------------|

| PRODUCT NO | DESCRIPTION                                          | PART         |

| (QUANTITY) |                                                      | NUMBER       |

| +========  | - 2. 本华区比较,12. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2 | +======+     |

|            |                                                      | 1            |

| M46-772    | MC-CDD 54, 60 Hz, 115 V                              | 02-778F03    |

|            |                                                      |              |

| (1)        | IDC Installation/Maintenance Manual                  | 47-032       |

| (1)        | Vendor Maintenance Manual                            | 29-749       |

| (1)        | IDC Programming Manual<br>  Test Program             | 1 06-267     |

| (1)        | Format Program                                       | 1 06-268     |

|            | Ground Strap, 1.07 m (42 in)                         | 17-295F05    |

|            | 54-Mb MC-CDD, 60 Hz, 115 V                           | 27-130F03    |

|            |                                                      | 17-447F01M01 |

| (1)        | Disk-Drive Terminator                                | 35-815       |

| (1)        | IDC Board                                            | 35-807       |

| (1)        | Mounting Kit                                         | 16-876       |

| +          | <br>                                                 | <br>++       |

| 1 246 704  | , , , , , , , , , , , , , , , , , , ,                |              |

| M46-734    | Expansion Drive, MC-CDD 54, 60 Hz                    | 02-762F01    |

| (1)        | Vendor Maintenance Manual                            |              |

| (1)        | Ground Strap, 1.07 m (42 in)                         | 17-295F05    |

| (1)        | Ground Strap, 1.83 m (6 ft)                          | 17-295F04    |

| (1)        | External B-Cable, 4.57 m (15 ft)                     | 17-448F01    |

| (1)        | 54-Mb MC-CDD, 60 Hz, 115 V                           | 27-130F03    |

| (1)        | External A-Cable, 1.07 m (42 in)                     | 17-411F03M01 |

| • •        | External A-Cable, 4.57 m (15 ft)                     | 17-449       |

| (1)        | Formatted Disk Cartridge, 13.5 Mb                    | 24-104F02    |

| (1)        | Mounting Kit                                         | 16-876       |

|            |                                                      |              |

| +          | <del> </del>                                         | ++           |

Table 2-12. 54-Mb MC-CDD System, 50 Hz

| PRODUCT NO |                                                                                                                                                                                                                                                                                                    | PART  <br>NUMBER                                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| (1)        | MC-CDD 54, 50 Hz, 220 V  IDC Installation/Maintenance Manual Vendor Maintenance Manual IDC Programming Manual Test Program Format Program Ground Strap, 1.07 m (42 in) 54-Mb MC-CDD, 50 Hz, 220V Ext A- and B-Cable, 4.57 m (15 ft) Disk-Drive Terminator IDC Board Mounting Kit                   | 02-778F04<br>47-032<br>29-749<br>50-007<br>06-267<br>06-268<br>17-295F05<br>27-130F04<br>17-447F01M01<br>35-815<br>35-807<br>16-876 |

| M46-735    | Expansion Drive, MC-CDD 54, 50 Hz  Vendor Maintenance Manual Ground Strap, 1.07 m (42 in) Ground Strap, 1.83 m (6 ft) External B-Cable, 4.57 m (15 ft) 54-Mb MC-CDD, 50 Hz, 220 V External A-Cable, 1.07 m (42 in) External A-Cable, 4.57 m (15 ft) Formatted Disk Cartridge, 13.5 Mb Mounting Kit | 02-762F02                                                                                                                           |

Table 2-13. 81-Mb MC-CDD System, 60 Hz

| PRODUCT NO                                           |                                                                                                                                                                                                                                                                                                    | PART  <br>NUMBER                                                                                                                    |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| (1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | MC-CDD 81, 60 Hz, 115 V  IDC Installation/Maintenance Manual Vendor Maintenance Manual IDC Programming Manual Test Program Format Program Ground Strap, 1.07 m (42 in) 81-Mb MC-CDD, 60 Hz, 115V                                                                                                   | 02-779F03<br>47-032<br>29-749<br>50-007<br>06-267<br>06-268<br>17-295F05<br>27-129F03<br>17-447F01M01<br>35-815<br>35-807<br>16-876 |

| (1)                                                  | Expansion Drive, MC-CDD 81, 60 Hz  Vendor Maintenance Manual Ground Strap, 1.07 m (42 in) Ground Strap, 1.83 m (6 ft) External B-Cable, 4.57 m (15 ft) 81-Mb MC-CDD, 60 Hz, 115 V External A-Cable, 1.07 m (42 in) External A-Cable, 4.57 m (15 ft) Formatted Disk Cartridge, 13.5 Mb Mounting Kit | 02-763F01                                                                                                                           |

Table 2-14. 81-Mb MC-CDD System, 50 Hz

| PRODUCT NO  <br>  (QUANTITY) |                                                                                                                                                                                                                                                                                                    | PART  <br>NUMBER                                                                                                         |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| (1)                          | 81-Mb MC-CDD, 50 Hz, 220 V                                                                                                                                                                                                                                                                         | 02-779F04   47-032   29-749   50-007   06-267   06-268   17-295F05   27-129F04   17-447F01M01   35-815   35-807   16-876 |

| M46-737                      | Expansion Drive, MC-CDD 81, 50 Hz  Vendor Maintenance Manual Ground Strap, 1.07 m (42 in) Ground Strap, 1.83 m (6 ft) External B-Cable, 4.57 m (15 ft) 81-Mb MC-CDD, 50 Hz, 220 V External A-Cable, 1.07 m (42 in) External A-Cable, 4.57 m (15 ft) Formatted Disk Cartridge, 13.5 Mb Mounting Kit | 02-763F02                                                                                                                |

Table 2-15. Fixed-Media 330-Mb Disk System 60 Hz

| PRODUCT NO  <br>  (QUANTITY) |                                                                                                                                                                                                                                                                                  | PART  <br>NUMBER                                                                                    |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| M60-120                      | MSM300F Disk System 115 V,60 Hz  IDC Disk Test Program IDC Disk Format Program Installation Kit Ground Strap, 9.14 m (30 ft) Ext A- and B-Cable, 4.57 m (15 ft) 330-Mb Disk Drive 115 V, 60 Hz Intelligent Disk Controller Disk-Drive Terminator Installation/Maintenance Manual | 02-830F01   06-267   06-268   16-932   17-295F01   17-447F01   27-148F01   35-807   35-852   47-032 |

| (1)                          | IDC Programming Manual<br>Vendor Maintenance Manual                                                                                                                                                                                                                              | 50-007<br>51-041                                                                                    |

| M60-122                      | MSM300FE Disk Exp. 115 V, 60 Hz  IDC Disk Test Program IDC Disk Format Program Installation Kit Ground Strap, 9.14 m (30 ft) External A-Cable, 2.44 m (8 ft) External B-Cable, 4.57 m (15 ft) 330-Mb Disk Drive 115 V, 60 Hz Vendor Maintenance Manual                           | 02-831F01   06-267   06-268   16-932   17-295F01   17-449F01   17-448F01   27-148F01   51-041       |

Table 2-16. Fixed-Media 330-Mb Disk System, 50 Hz

| PRODUCT NO  <br>  (QUANTITY)                                                    |                                                                                                                                                                                                                                                        | PART  <br>NUMBER                                                                                      |

|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| M60-121                                                                         | MSM300F Disk System 230 V, 50 Hz  IDC Disk Test Program IDC Disk Format Program Installation Kit Ground Strap, 9.14 m (30 ft) Ext A- and B-Cable, 4.57 m (15 ft) 330 Mb Disk Drive 230 V, 50 Hz Intelligent Disk Controller Disk-Drive Terminator      | 02-830F02                                                                                             |

| (1)                                                                             | Installation/Maintenance Manual IDC Programming Manual Vendor Maintenance Manual                                                                                                                                                                       | 47-032<br>50-007<br>51-041                                                                            |

| M60-123<br>  (1)<br>  (1)<br>  (1)<br>  (1)<br>  (1)<br>  (1)<br>  (1)<br>  (1) | MSM300FE Disk Exp. 230 V, 50 Hz  IDC Disk Test Program IDC Disk Format Program Installation Kit Ground Strap, 9.14 m (30 ft) External A-Cable, 2.44 m (8 ft) External B-Cable, 4.57 m (15 ft) 330-Mb Disk Drive 230 V, 50 Hz Vendor Maintenance Manual | 02-831F02<br>06-267<br>06-268<br>16-932<br>17-295F01<br>17-449F01<br>17-448F01<br>27-148F02<br>51-041 |

Table 2-17. CDD 50 Disk System 60 Hz

| +              |                                                   |                         |  |

|----------------|---------------------------------------------------|-------------------------|--|

| PRODUCT NO     | RODUCT NO DESCRIPTION                             |                         |  |

| (QUANTITY)     |                                                   | NUMBER                  |  |

| +======+       |                                                   |                         |  |

| M60-140        | CDD 50 Disk System 115 V, 60 Hz                   | <br>  02-841F01         |  |

| MOU-140        | CDD 50 DISK System II5 V, 60 HZ                   | U2-041FU1               |  |

| (1)            | Disk Test Program                                 | 06-267                  |  |

| (1)            | IDC Disk Format Program                           | 06-268                  |  |

| (1)            | Installation Kit                                  | 16-942F01               |  |

| (1)            | Intelligent Disk Controller                       | 02-734                  |  |

| (1)            | Disk Drive 50Mb (115 V AC)                        | 27-149F01               |  |

| (1)            | Cartridge Disk-25 Mb                              | 24-109                  |  |

| (1)            | Terminator Board                                  | 35-876                  |  |

| (1)            | A/B Cable (shielded)                              | 17-663                  |  |

| (1)            | 10" Ground Cable                                  | 17-584F01               |  |

|                | 24" Ground Cable                                  | 17-584F02               |  |

|                | 36" Ground Cable                                  | 17-585F02               |  |

| (1)            | Manual, Installation & Maintenance                | 47-032  <br>  50-007    |  |

| (1)  <br>  (1) | Manual, Programming<br>Manual, Vendor Maintenance | 1 51-054 1              |  |

| +              | Manual, Vendol Maintenante<br>                    |                         |  |

|                |                                                   |                         |  |

| M60-142        | CDD 50E Disk System 115 V, 60 Hz                  | 02-842F01               |  |

| 1              |                                                   | 1                       |  |

| (1)            | IDC Disk Test Program                             | 06-267                  |  |

| (1)            | IDC Disk Format Program                           | 06-268                  |  |

| (1)            | Installation Kit                                  | 16-942F02               |  |

| (1)            | Disk Drive 50 Mb (115 V AC)                       | 27-149F01               |  |

| (1)            | Cartridge Disk-25 Mb                              | 24-109F01  <br>  17-664 |  |

| (1)            |                                                   |                         |  |

| (1)            | "B" Cable   17-665<br>10" Ground Cable   17-584F0 |                         |  |

| (1)            | 24" Ground Cable   17-584F01   17-584F02          |                         |  |

| (1)            | 36" Ground Cable   17-585F02                      |                         |  |

| (1)            | Manual, Vendor Maintenance                        | 51-054                  |  |

| +              |                                                   | ,                       |  |

1

| PRODUCT NO  <br>  (QUANTITY)                    | ·                                                                                                                                                                                                                                                                                                                      | PART  <br>NUMBER                                                                                                                                           |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M60-141                                         | CDD 50 Disk System 230 V, 50 Hz                                                                                                                                                                                                                                                                                        | 02-841F02                                                                                                                                                  |

| (1)                                             | IDC Disk Test Program IDC Disk Format Program Installation Kit Intelligent Disk Controller Disk Drive 50 Mb (230 V AC) Cartridge Disk-25 Mb Terminator Board A/B Cable (shielded) 10" Ground Cable 24" Ground Cable 36" Ground Cable Manual, Installation & Maintenance Manual, Programming Manual, Vendor Maintenance | 06-267<br>06-268<br>16-942F01<br>02-734<br>27-149F02<br>24-109F01<br>35-876<br>17-663<br>17-584F01<br>17-584F02<br>17-585F02<br>47-032<br>50-007<br>51-054 |

| M60-143  (1) (1) (1) (1) (1) (1) (1) (1) (1) (1 | CDD 50E Disk System 230 V, 50 Hz  IDC Disk Test Program IDC Disk Format Program Installation Kit Disk Drive 50 Mb (230 V AC) Cartridge Disk-25 Mb "A" Cable "B" Cable 10" Ground Cable 24" Ground Cable 36" Ground Cable Manual, Vendor Maintenance                                                                    | 02-842F02<br>06-267<br>06-268<br>16-942F02<br>27-149F02<br>24-109F01<br>17-664<br>17-665<br>17-584F01<br>17-584F02<br>17-585F02<br>51-054                  |

#### 2-2.1 Additional Cabling Information

Table 2-19 is a summary of all the cables and straps associated with the IDC disk systems. As listed in the table, those cables and straps having a functional variation with the part number are selectable for your particular system. For example, instead of installing the 15-ft A-cable numbered 17-521F01, you can select the 8-ft A-cable numbered 17-521F02.

Table 2-19. Standard Cabling Supplied with IDC Disk Systems

| +                        | <br>CABLE/STRAP                                              | DESCRIPTION {                                                                                           |

|--------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| NO.                      | ,<br> <br> -==================================               | <br>                                                                                                    |

| 17-447<br> <br>          | External A-Cable<br>and B-Cable                              | Shielded, 9.14m (30 ft), for 1st   drive of all removable-media   systems.                              |

| •                        | External A-Cable and B-Cable                                 | Shielded, 4.57m (15 ft), for lst   drive of all MC-CDD systems.                                         |

| 17- <b>44</b> 8<br>      | External B-Cable                                             | Shielded, 9.14m (30 ft), for 2nd, 3rd, and 4th drives of all removable-media disk systems.              |

| 17- <b>44</b> 8F01       | External B-Cable                                             | Shielded, 4.57m (15 ft), for 2nd, 3rd, and 4th drives of all MC-CDD systems.                            |

| 17- <b>44</b> 9<br>      | External A-Cable                                             | Shielded, 4.57m (15 ft), for 2nd   3rd, and 4th drives of all   removable-media disk systems.           |

| 17-520F01<br> <br>       | External B-Cable                                             | Heavy-duty, shielded, 4.57m (15 ft), for all drives of fixed-media 67-Mb systems.                       |

| 17-521F01<br> <br>       | External A-Cable                                             | Heavy-duty, shielded, 4.57m<br>(15 ft), for first drive of<br>fixed-media 67-Mb systems.                |

| 17-521F02                | External A-Cable                                             | Heavy-duty, shielded, 2.44m<br>(8 ft), for 2nd, 3rd, and 4th<br>drives of fixed-media 67-Mb<br>systems. |

| 17-411F03<br>M01         | External A-Cable                                             | Heavy-duty, shielded, 1.07m<br>(42 in), for 2nd, 3rd, and 4th<br>drives of MC-CDD systems.              |

| 17-663                   | External A-Cable and B-Cable                                 | Shielded, l.52m (5 ft), for lst   drive of CDD 50 systems.                                              |

| 17-664                   | External A-Cable                                             | Shielded, 1.07m (3.5 ft), for all drives of CDD 50 systems.                                             |

| 17-665                   | External B-Cable                                             | Shielded, 1.52m (5 ft), for all drives of CDD 50 systems.                                               |

| 17-295F03 <br> 17-295F04 | Ground Strap<br>Ground Strap<br>Ground Strap<br>Ground Strap | 9.14m (30 ft)<br>4.57m (15 ft)<br>1.83m (6 ft)<br>1.07m (42 in)                                         |

#### 2-3 UNPACKING INSTRUCTIONS

For instructions on how to unpack your particular IDC disk system, see the supplied vendor manuals. These manuals are listed in Table 1-1 and in the tables of Section 2-2.

#### 2-4 INSTALLING AN IDC DISK SYSTEM

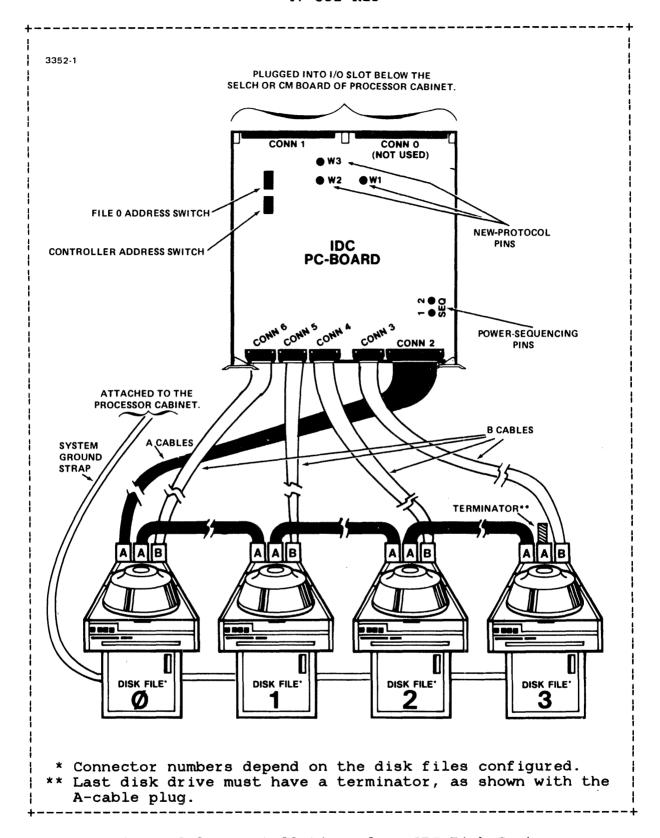

Figure 2-1 is a general illustration of how to install a normal IDC disk system. A normal IDC disk system is one which has the IDC board plugged into the processor cabinet and employs the normal SELCH protocol. IDC (35-807) revision level 10 and above must have its backpanel pin 224-1 wired to its SELCH backpanel pin 224-1. But if the IDC board for your system is installed with a Perkin-Elmer I/O Bus Switch, and consequently employs the "new" high-speed SELCH protocol, then your system is not normal. Its installation requires the additional information presented in Perkin-Elmer Publication 29-356.

Along with the applicable vendor manuals listed in Table 1-1 and the relevant tables in Section 2-2, Figure 2-1 should enable you to install your particular IDC disk system. However, before plugging in your IDC board and connecting the cables as shown in the figure, you must set two address switches; see Section 2-4.1. For optional IDC board strapping, see Section 2-4.2.

Refer to Section 2-5 if one or more of your disk drives are to be equipped with a dual-port option.

#### 2-4.1 Setting the Address Switches on the IDC Board

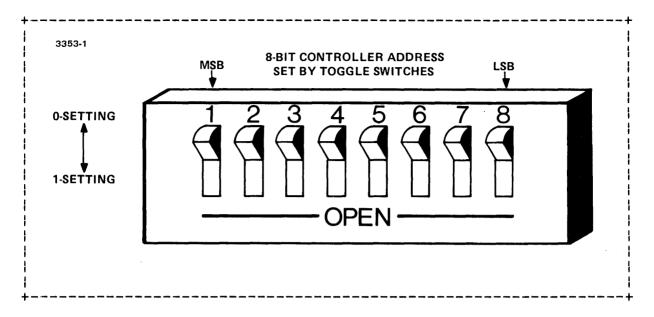

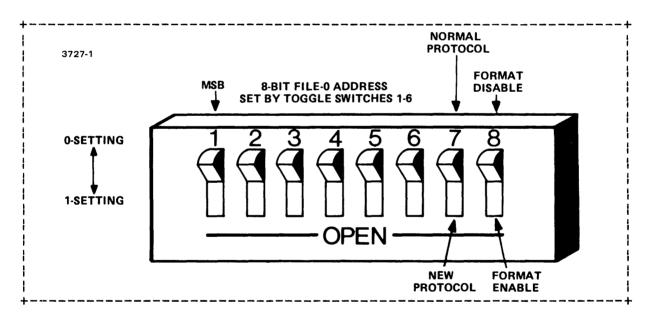

As seen from Figures 1-2 and 2-1, the IDC board has two address switches in its upper-left corner:

- (1) Controller Address Switch (or Device Address Switch)

- (2) File-0 Address Switch

Figures 2-2 and 2-3 present an up-close view of these switches. As shown in Figure 2-2, the Controller Address Switch has eight toggles, numbered 1 through 8, each with two possible settings: 0 or 1. Each toggle setting represents a bit in a 1-byte controller address, with toggle-1 being the most significant bit (MSB) and toggle-8 being the least significant bit (LSB). You must set the toggles to the address wanted for your IDC.

As shown in Figure 2-3, the File-O Address Switch also has eight toggles, numbered 1 through 8, each with two possible settings: 0 or 1. Toggles 1 through 6 represent six bits in a 1-byte address for your disk file 0, with toggle-1 being the MSB. The other two bits of the 1-byte address are always considered as zero. Toggles 7 and 8, which will be discussed shortly, are for selecting the new high-speed SELCH protocol and for enabling or disabling IDC formatting capability. They are not used for addressing.

Figure 2-1. Installation of an IDC Disk System

Figure 2-2. Controller Address Switch

Figure 2-3. File-0 Address Switch

As an example for setting addresses on these switches, suppose you have an IDC system consisting of one IDC board and four disk files. You want the controller address to be X'FB' and the four disk file addresses to be X'FC' through X'FF'. Before installing the IDC board, you would set the Controller Address Switch to the binary value of 'lllll0ll' (for X'FB') and the File-O Address Switch to 'llllll00' (for X'FC'). Disk files I through 3 are automatically addressed at X'FD', X'FE' and X'FF', respectively.

Now, with the wanted addresses set on the two switches, you have the option of setting toggle-7 and/or toggle-8 in the File-0 Address Switch. If you want to employ the normal SELCH protocol, you push toggle-7 up to the 0-setting. But if your IDC is plugged into the 25-foot cable of an I/O Bus Switch, you must push toggle-7 down to the 1-setting, thereby employing the "new" high-speed SELCH protocol. For additional information on the I/O Bus Switch, see Perkin-Elmer Publication 29-356. (Also, as discussed in Section 2-4.2, the new-protocol pins Wl and W3 should be strapped when toggle-7 is at the 1-setting.) In summary, then, place toggle-7 in the 0-setting when your IDC board is plugged into the processor cabinet; place toggle-7 in the 1-position when your IDC board is plugged into the I/O Bus Switch.

Toggle-8 of the File-0 Address Switch is usually left in the l-setting to enable IDC formatting. That is, if you want the capability of formatting an unformatted disk according to IDC format, leave toggle-8 down. Perkin-Elmer Publication 50-007 describes the IDC disk-media format in detail. But if, for some reason, you want to disable the IDC formatting capability, push toggle-8 up to the 0-position.

## 2-4.2 IDC Strapping Information

As shown in Figures 2-1 and 1-2, the IDC board has two sets of pins:

- (1) Power Sequencing (SEQ) Pins 1 and 2

- (2) New-Protocol Pins Wl thru W3

Power sequencing refers to the serial application of power to the disk files once the processor is turned on, where: after disk file 0 is powered and comes up to speed, disk file 1 is powered up; after disk file 1 comes up to speed, disk file 2 is powered When you want your disk files to power up up; and so forth. sequentially, do not place a jumper wire across the Power Sequencing (SEQ) Pins 1 and 2. Also ensure that the Local/Remote Switch on each attached disk file is in the Remote position. Subsequently, when the processor is turned off, the disk files power down simultaneously. When pins 1 and 2 are strapped, or when the Local/Remote Switch on each attached disk file is in the Local position, the disk files can be simultaneously powered up -- in parallel, as opposed to serial. Occasionally, simultaneous application of power to the disk files causes an excessive power surge. To determine the advisability of power sequencing to prevent this, refer to the AC power requirements presented in Section 2-6.

The New-Protocol Pins Wl, W2, and W3 apply to the use of the "new" high-speed SELCH protocol for special applications. When your IDC is installed under an I/O Bus Switch, and when toggle-7 of the File-O Address Switch is down in the l-setting, you must strap pins Wl and W3.

## 2-5 INSTALLING DUAL-PORT OPTIONS

Only the 67-Mb and 256-Mb removable-media disk systems can be equipped for dual-port operation. Hardware for the dual-port option consists of four items:

- (1) IDC Board

- (2) Dual-Port Kit

- (3) A-Cable and B-Cable

- (4) Disk-Drive Terminator

Sections 2-5.1 thru 2-5.4 discuss the installation of these items.

## 2-5.1 IDC Board