# **REFERENCE MANUAL**

#### SYSTEMS 32/70 SERIES

Computer

## Supersedes 301-320070-000

Specifications Subject to Change Without Notice

O 1979 Systems Engineering Laboratories, Incorporated

Printed in USA Publication Number 301-320070-001

## 32/70 SERIES INSTRUCTIONS BY CATEGORY

| OP CODE      | MNEMONIC      | DESCRIPTION                                                                                                  | PAGE           | OP CODE      | MNEMONIC        | DESCRIPTION                                                                       | PAGE           |

|--------------|---------------|--------------------------------------------------------------------------------------------------------------|----------------|--------------|-----------------|-----------------------------------------------------------------------------------|----------------|

|              |               | LOAD INSTRUCTIONS                                                                                            |                |              |                 | SHIFT INSTRUCTIONS                                                                |                |

| AC08<br>AC00 | LB<br>LH      | LOAD BYTE<br>Load Halfword                                                                                   | 6-10<br>6-11   | 6000         | NOR             | NORMALIZE                                                                         | 6-113          |

| AC00<br>AC00 | LW            | LOAD WORD<br>LOAD DOUBLEWORD                                                                                 | 6-12<br>6-13   | 6400<br>6800 | NORD<br>SCZ     | NGRHALIZE DOUBLE<br>SHIFT AND COUNT ZEROS                                         | 6-114<br>6-115 |

| 8008         | LMB           | LOAD MASKED BYTE<br>LOAD MASKED HALFWORD                                                                     | 6-14<br>6-15   | 6C40<br>7040 | SLA<br>SLL      | SHIFT LEFT ARITHMETIC<br>SHIFT LEFT LOGICAL                                       | 6-116<br>6-117 |

| 8000<br>8000 | LIW           | LOAD MASKED WORD                                                                                             | 6-16           | . 1          | SLC             | SHIFT LEFT CIRCULAR                                                               | 6-118          |

| 8000<br>8408 | LMD<br>LNB    | LOAD MASKED DOUBLEWORD<br>LOAD NEGATIVE BYTE                                                                 | 6-17<br>6-18   | 7840<br>7C40 | SLAD            | SHIFT LEFT ARITHMETIC DOUBLE<br>SHIFT LEFT LOGICAL DOUBLE                         | 6-119<br>6-120 |

| 8400<br>8400 | LNH<br>LNW    | LOAD NEGATIVE HALFWORD<br>LOAD NEGATIVE WORD                                                                 | 6-19<br>6-20   | 6CC0<br>7000 | SRA<br>SRL      | SHIFT RIGHT ARITHMETIC<br>Shift Right Logical                                     | 6-121<br>6-122 |

| 8400         | LND           | LOAD NEGATIVE DOUBLEWORD<br>LOAD IMMEDIATE                                                                   | 6-21           | 7400<br>7800 | SRC<br>SRAD     | SHIFT RIGHT CIRCULAR<br>SHIFT RIGHT ARITHMETIC DOUBLE                             | 6-123<br>6-124 |

| C800<br>D000 | LI<br>LEA     | LOAD EFFECTIVE ADDRESS                                                                                       | 6-22<br>6-23   | 7000         | SRLD            | SHIFT RIGHT LOGICAL DOUBLE                                                        | 6-125          |

| 8000<br>3400 | LEAR<br>LA    | LOAD EFFECTIVE ADDRESS REAL *<br>LOAD ADDRESS*                                                               | 6-24<br>6-25   |              |                 |                                                                                   |                |

| . ~          |               |                                                                                                              |                |              |                 | BIT MANIPULATION INSTRUCTIONS                                                     |                |

| CC00         | LF -          | LOAD FILE                                                                                                    | 6-28           | 9808<br>1800 | SBM<br>SBR      | SET BIT IN MEMORY<br>SET BIT IN REGISTER                                          | 6-128<br>6-129 |

|              |               | STORE INSTRUCTIONS                                                                                           |                | 9008         | ZBM             | ZERO BIT IN MEMORY                                                                | 6-130          |

| D408         | STB           | STORE BYTE                                                                                                   | 6-29           | 1C00<br>A008 | ZBR<br>ABM      | ZERO BIT IN REGISTER<br>ADD BIT IN MEMORY                                         | 6-131<br>6-132 |

| D400<br>D400 | STH<br>STW    | STORE HALFWORD                                                                                               | 6-30<br>6-31   | 2000<br>A408 | ABR<br>TBM      | ADD BIT IN REGISTER<br>TEST BIT IN MEMORY                                         | 6-133<br>6-134 |

| D400<br>D808 | STD<br>STMB   | STORE DOUBLEWORD<br>STORE MASKED BYTE                                                                        | 6-32<br>6-33   | 2400         | TBR             | TEST BIT IN REGISTER                                                              | 6-135          |

| D800         | STMH          | STORE MASKED HALFWORD<br>STORE MASKED WORD                                                                   | 6-34<br>6-35   |              |                 | FIXED-POINT ARITHMETIC INSTRUCTIONS                                               |                |

| 0800<br>0800 | STMW          | STORE MASKED DOUBLEWORD                                                                                      | 6-36           |              |                 |                                                                                   | <i>c</i>       |

| 0000         | STF           | STORE FILE                                                                                                   | 6-37           | 8808<br>8800 | ADMB<br>ADMH    | ADD MEMORY BYTE<br>ADD MEMORY HALFWORD                                            | 6-140<br>6-141 |

|              |               | ZERO INSTRUCTIONS                                                                                            |                | 8800<br>8800 | ADMW<br>ADMD    | ADD MEMORY WORD<br>ADD MEMORY DOUBLEWORD                                          | 6-142<br>6-143 |

| F808         | ZMB           | ZERO MEMORY BYTE                                                                                             | 6-39           | 3800<br>3808 | ADR<br>ADRM     | ADD REGISTER TO REGISTER<br>ADD REGISTER TO REGISTER MASKED                       | 6-144<br>6-145 |

| F800         | ZMH           | ZERO MEMORY HALFWORD                                                                                         | 6-40<br>6-41   | E808<br>E800 | ARMB            | ADD REGISTER TO MEMORY BYTE<br>ADD REGISTER TO MEMORY HALFWORD                    | 6-146<br>6-147 |

| F800<br>F800 | ZMW<br>ZMD    | ZERO MEMORY WORD<br>ZERO MEMORY DOUBLEWORD                                                                   | 6-42           | E800         | ARMW            | ADD REGISTER TO MEMORY WORD                                                       | 6-148          |

| 0000         | ZR            | ZERO REGISTER                                                                                                | 6-43           | E800<br>C801 | ARMD<br>ADI     | ADD REGISTER TO MEMORY DOUBLEWORD<br>ADD IMMEDIATE                                | 6-149<br>6-150 |

|              |               | TRANSFER INSTRUCTIONS                                                                                        |                | 8C08<br>8C00 | SUMB<br>SUMH    | SUBTRACT MEMORY BYTE<br>SUBTRACT MEMORY HALFWORD                                  | 6-151<br>6-152 |

| 0005         | 7000          |                                                                                                              | 6-45           | BC00<br>BC00 | SUMW<br>SUMD    | SUBTRACT MEMORY WORD<br>SUBTRACT MEMORY DOUBLEWORD                                | 6-153<br>6-154 |

| 2C0F<br>2C0E | TSCR<br>TRSC  | TRANSFER SCRATCHPAD TO REGISTER<br>TRANSFER REGISTER TO SCRATCHPAD                                           | 6-46           | 3C00         | SUR             | SUBTRACT REGISTER FROM REGISTER                                                   | 6-155          |

| 2C00<br>2C08 | TRR<br>TRRM   | TRANSFER REGISTER TO REGISTER<br>TRANSFER REGISTER TO REGISTER MASKED                                        | 6-47<br>6-48   | 3C08<br>C802 | SURM<br>SUI     | SUBTRACT REGISTER FROM REGISTER MASKED<br>SUBTRACT IMMEDIATE                      | 6-156<br>6-157 |

| F800<br>F800 | TRP<br>TPR    | TRANSFER REGISTER TO PROTECT REGISTER<br>TRANSFER PROTECT REGISTER TO REGISTER<br>TRANSFER REGISTER NEGATIVE | 6-49<br>6-50   | C008<br>C000 | MPMB<br>MPMH    | MULTIPLY BY MEMORY BYTE<br>MULTIPLY BY MEMORY HALFWORD                            | 6-158<br>6-159 |

| 2C04<br>2C0C | TRN           | TRANSFER REGISTER NEGATIVE<br>TRANSFER REGISTER NEGATIVE MASKED                                              | 6-51<br>6-52   | C000<br>4000 | MPMW<br>MPR     | MULTIPLY BY MEMORY WORD<br>MULTIPLY REGISTER BY REGISTER                          | 6-160<br>6-161 |

| 2C03         | TRC           | TRANSFER REGISTER COMPLEMENT<br>TRANSFER REGISTER COMPLEMENT MASKED                                          | 6-53<br>6-54   | C803<br>C408 | MPI<br>DVMB     | MULTIPLY IMMEDIATE                                                                | 6-162<br>6-163 |

| 2C0B<br>2C05 | TRCM<br>XCR   | EXCHANGE REGISTERS                                                                                           | 6-55           | C400<br>C400 | DVMH            | DIVIDE BY MEMORY BYTE<br>DIVIDE BY MEMORY HALFWORD<br>DIVIDE BY MEMORY WORD       | 6-164          |

| 2COD<br>2800 | XCRM<br>TRSW  | EXCHANGE REGISTERS MASKED<br>TRANSFER REGISTER TO PSWR                                                       | 6-56<br>6-57   | 4400         | DVR             | DIVIDE REGISTER BY REGISTER                                                       | 6-165<br>6-166 |

|              |               | MEMORY MANAGEMENT INSTRUCTIONS                                                                               |                | C804<br>0004 | DVI<br>ES       | DIVIDE IMMEDIATE<br>Extend Sign                                                   | 6-167<br>6-168 |

|              |               | SET EXTENDED ADDRESSING                                                                                      | 6-59           | 0005         | RND             | ROUND REGISTER                                                                    | 6-169          |

| 0000<br>000F | SEA           | CLEAR EXTENDED ADDRESSING                                                                                    | 6-60<br>6-61   |              |                 | FLOATING-POINT ARITHMETIC INSTRUCTIONS                                            |                |

| 2A07<br>2C0A | LMAP<br>TMAPR | LOAD MAP*<br>TRANSFER MAP TO REGISTER*                                                                       | 6-62           | E008         | ADFW            |                                                                                   | 6 170          |

|              |               | WRITABLE CONTROL STORAGE INSTRUCTIONS                                                                        |                | E008         | ADFD            | ADD FLOATING-POINT WORD<br>ADD FLOATING-POINT DOUBLEWORD                          | 6-172<br>6-173 |

| 000C         | WWCS          | WRITE WRITABLE CONTROL STORAGE                                                                               | 6-65           | E000<br>E000 | SUFW<br>SUFD    | SUBTRACT FLOATING-POINT WORD<br>SUBTRACT FLOATING-POINT DOUBLEWORD                | 6-174<br>6-175 |

| 0008         | RWCS          | READ WRITABLE CONTROL STORAGE<br>JUMP TO WRITABLE CONTROL STORAGE                                            | 6-66<br>6-67   | E408<br>E408 | MPFW<br>MPFD    | MULTIPLY FLOATING-POINT WORD⊷<br>MULTIPLY FLOATING-POINT DOUBLEWORD               | 6-176<br>6-177 |

| FA00         | JWLS          | BRANCH INSTRUCTIONS                                                                                          | 0.07           | E400<br>E400 | DVFW<br>DVFD    | DIVIDE FLOATING-POINT WORD<br>DIVIDE FLOATING-POINT DOUBLEWORD                    | 6-178<br>6-179 |

|              |               |                                                                                                              | 6.70           | 2,000        |                 |                                                                                   | 0 1/5          |

| EC00<br>F000 | BU<br>BCF     | BRANCH UNCONDITIONALLY<br>BRANCH CONDITION FALSE                                                             | 6-72<br>6-73   |              |                 | CONTROL INSTRUCTIONS                                                              |                |

| EC00<br>F000 | BCT<br>BFT    | BRANCH CONDITION TRUE<br>BRANCH FUNCTION TRUE                                                                | 6-74<br>6-75   | F900         | BRI             | BRANCH AND RESET INTERRUPT                                                        | 6-181          |

| F880<br>F400 | BL<br>BIB     | BRANCH AND LINK<br>Branch After Incrementing Byte                                                            | 6-76<br>6-77   | F980<br>FA80 | LPSD<br>LPSDCM  | LOAD PROGRAM STATUS DOUBLEWORD*<br>LOAD PROGRAM STATUS DOUBLEWORD AND CHANGE MAP* | 6-182<br>6-183 |

| F420         | BIH           | BRANCH AFTER INCREMENTING HALFWORD<br>BRANCH AFTER INCREMENTING WORD                                         | 6-78<br>6-79   | 0003<br>C807 | LCS<br>EXR      | LOAD CONTROL SWITCHES<br>EXECUTE REGISTER                                         | 6-184<br>6-185 |

| F440<br>F460 | BIW<br>BID    | BRANCH AFTER INCREMENTING WORD                                                                               | 6~80           | C807         | EXRR            | EXECUTE REGISTER RIGHT                                                            | 6-186          |

|              |               | COMPÁRE INSTRUCTIONS                                                                                         |                | A800<br>0000 | EXM<br>HALT     | EXECUTE MEMORY<br>HALT                                                            | 6-187<br>6-188 |

| 9008         | CAMB          | COMPARE ARITHMETIC WITH MEMORY BYTE                                                                          | 6-83           | 0001<br>0002 | WAIT<br>NOP     | WAIT<br>NO OPERATION                                                              | 6-189<br>6-190 |

| 9000<br>9000 | CAMH<br>CAMW  | COMPARE ARITHMETIC WITH MEMORY HALFWORD<br>COMPARE ARITHMETIC WITH MEMORY WORD                               | 6-84<br>6-85   | 000A<br>3000 | SIPU<br>CALM    | Signal IPU<br>CALL MONITOR                                                        | 6-191<br>6-192 |

| 9000         | CAMD          | COMPARE ARITHMETIC WITH MEMORY DOUBLEWORD<br>COMPARE ARITHMETIC WITH REGISTER                                | 6-86<br>6-87   | C806         | SVC<br>SETCPU   | SUPERVISOR CALL*<br>SET CPU MODE                                                  | 6-193<br>6-194 |

| 1000<br>C805 | CAR<br>CI     | COMPARE IMMEDIATE                                                                                            | 6-88           | 2C09<br>0009 | RDSTS           | READ CPU STATUS WORD*                                                             | 6-195          |

| 9408<br>9400 | CMMB<br>CMMH  | COMPARE MASKED WITH MEMORY BYTE<br>COMPARE MASKED WITH MEMORY HALFWORD                                       | 6-89<br>6-90   | 0008<br>000E | EAE<br>DAE      | ENABLE ARITHMETIC EXCEPTION TRAP*<br>DISABLE ARITHMETIC EXCEPTION TRAP*           | 6-197<br>6-198 |

| 9400<br>9400 | CMMW<br>CMMD  | COMPARE MASKED WITH MEMORY WORD<br>COMPARE MASKED WITH MEMORY DOUBLEWORD                                     | 6-91<br>6-92   |              |                 |                                                                                   |                |

| 1400         | CMR           | COMPARE MASKED WITH REGISTER                                                                                 | 6-93           | •            |                 | INTERRUPT INSTRUCTIONS                                                            |                |

|              |               | LOGICAL AND INSTRUCTIONS                                                                                     |                | FC00<br>FC02 | EI<br>RI        | ENABLE INTERRUPT<br>REQUEST INTERRUPT                                             | 6-202<br>6-203 |

| 8408         | ANMB          | AND MEMORY BYTE                                                                                              | 6-95<br>6-96   | FC.03        | AI.             | ACTIVATE INTERRUPT                                                                | 6-204<br>6-205 |

| 8400<br>8400 | ANMH<br>ANMW  | AND MEMORY HALFWORD<br>AND MEMORY WORD                                                                       | 6-97           | FC01<br>FC04 | DI<br>DAI       | DISABLE INTERRUPT<br>DEACTIVATE INTERRUPT                                         | 6-206          |

| 8400<br>0400 | ANMD          | AND MEMORY DOUBLEWORD<br>AND REGISTER AND REGISTER                                                           | 6-98<br>6-99   | FC77<br>FC67 | ACI<br>ECI      | ACTIVATE CHANNEL INTERRUPT*<br>ENABLE CHANNEL INTERRUPT*                          | 6-207<br>6-208 |

|              |               | LOGICAL OR INSTRUCTIONS                                                                                      |                | FC6F<br>FC7F | DCI<br>DACI     | DISABLE CHANNEL INTERRUPT*<br>DEACTIVATE CHANNEL INTERRUPT*                       | 6-209<br>6-210 |

| 0000         | ORMB          |                                                                                                              | 6-100          | 0006<br>000E | BEI<br>UEI      | BLOCK EXTERNAL INTERRUPTS*                                                        | 6-211<br>6-212 |

| 8808<br>8800 | ORMH          | OR MEMORY BYTE<br>OR MEMORY HALFWORD                                                                         | 6-101          | UUVE         | UEI             | AND                                           |                |

| 8800<br>8800 | ORMW          | OR MEMORY WORD<br>OR MEMORY DOUBLEWORD                                                                       | 6-102<br>6-103 |              |                 | INPUT/OUTPUT INSTRUCTIONS                                                         |                |

| 0800 0808    | ORR           | OR REGISTER AND REGISTER<br>OR REGISTER AND REGISTER MASKED                                                  | 6-104<br>6-105 | FC06         | CD              | COMMAND DEVICE                                                                    | 6-216          |

|              |               | LOGICAL EXCLUSIVE OR INSTRUCTIONS                                                                            |                | FC05<br>FC17 | TD<br>SIO       | TEST DEVICE<br>START I/O*                                                         | 6-217<br>6-218 |

| 90.00        | COMP          |                                                                                                              | 6-106          | FC1F         | TIO             | TEST I/0*<br>STOP I/0*                                                            | 6-219<br>6-220 |

| 8C08<br>8C00 | EOMB<br>EOMH  | EXCLUSIVE OR MEMORY BYTE<br>Exclusive or memory halfword                                                     | 6-107          | FC27<br>FC2F | STPIO<br>RSCHNL | RESET CHANNEL*                                                                    | 6-221          |

| 8C00<br>8C00 | EOMW          | EXCLUSIVE OR MEMORY WORD<br>Exclusive or memory doubleword                                                   | 6-108<br>6-109 | FC37<br>FC3F | HIO<br>GRIO     | HALT I/O*<br>GRAB CONTROLLER *                                                    | 6-222<br>6-223 |

| 0000         | EOR<br>EORM   | EXCLUSIVE OR REGISTER AND REGISTER<br>EXCLUSIVE OR REGISTER AND REGISTER MASKED                              | 6-110<br>6-111 | FC47<br>FC4F | RSCTL<br>ECWCS  | RESET CONTROLLER*<br>ENABLE CHANNEL WCS LOAD*                                     | 6-224          |

|              |               |                                                                                                              |                | FC5F         | WCWCS           | WRITE CHANNEL WCS*                                                                | 6-226          |

|              |               |                                                                                                              |                | *PSD mode    | instructions    | ORIV                                                                              |                |

\*PSD mode instructions only

#### **REVISION INSTRUCTIONS AND MANUAL HISTORY**

EQUIPMENT: 32/70 Series Computer

301-320070-001 PUBLICATION NO.

PURPOSE: This reissue upgrades the manual reflecting the requirements of the Model 2005 Internal Processing Unit (IPU)

#### **REVISION INSTRUCTIONS:** Delete and add pages as shown on the following table.

| DELETE | ADD |

|--------|-----|

|        |     |

|        |     |

| N/A    | N/A |

| N/A    | N/A |

|        |     |

|        |     |

|        |     |

|        |     |

NOTE: Revised pages are marked with the Rev. No. in the upper unbound corner. Revised areas are marked with a vertical bar.

#### MANUAL HISTORY

| REV.         | REV. | DATE         | CONTROL  | ECL |

|--------------|------|--------------|----------|-----|

| TYPE         | NO.  | ISSUED       | DOC. NO. |     |

| 1st Ptg<br>R | -    | 1/79<br>1/80 |          |     |

| - | - 1 | N | ľ | Г | Е | R | I | N | R | E | ٧ | 1 | S | I | 0 | N | l |

|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

F = FORMAL REVISION R = REISSUE A = ADDENDUM

| REV.<br>TYPE | REV.<br>NO. | DATE<br>ISSUED | CONTROL<br>DOC. NO. | ECL |

|--------------|-------------|----------------|---------------------|-----|

|              |             |                |                     |     |

|              |             |                |                     |     |

|              |             |                |                     |     |

|              |             |                | н.<br>К.            |     |

#### LIST OF EFFECTIVE PAGES

The total number of pages is in this manual is 398 consisting of the following:

| Page                                                                                                                                                                                                                                                                                                                                        | Issue                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title<br>Instructions<br>iii through xiv<br>Frontispiece<br>1-1 through 1-18<br>2-1 through 2-32<br>3-1 through 3-12<br>4-1 through 3-12<br>4-1 through 4-22<br>5-1 through 4-22<br>6-1 through 5-22<br>6-1 through 5-28<br>7-1 through 7-18<br>8-1 through 8-6<br>A-1 through 8-6<br>B-1 through 8-6<br>B-1 through B-8<br>C-1 through D-2 | Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original |

| E-1 through E-2<br>F-1 through F-2<br>G-1 through G-2                                                                                                                                                                                                                                                                                       | Original<br>Original<br>Original                                                                                                                                                             |

| OP Codes                                                                                                                                                                                                                                                                                                                                    | Original                                                                                                                                                                                     |

## SECTION I GENERAL DESCRIPTION

| Introduction                            | .1-1   |

|-----------------------------------------|--------|

| System Overview                         | .1-1   |

| General Characteristics                 | .1-1   |

| Standard and Optional Features          | 1-4    |

| General Purpose Features                |        |

| Real-Time Features                      |        |

| Multiusage Features                     |        |

| Multiprocessing Features                |        |

| Functional Description                  |        |

| Major System Elements                   |        |

| SeiBUS                                  |        |

| Central Processor Unit                  | 1-11   |

| General Purpose Registers               |        |

| Floating-Point Arithmetic Processor     |        |

| CPU Modes                               |        |

| Control Modes                           |        |

| Addressing Modes                        |        |

| Address Submodes                        |        |

| Hardware Memory Management.             |        |

| Memory Map                              |        |

| Write Protection                        |        |

| Optional Writable Control Storage       |        |

| Optional High-Speed Floating-Point Unit |        |

| Real-Time Option Module                 | .1-15  |

| Interval Timer                          |        |

| >Main Memory                            | .1-15  |

| Memory Unit                             | .1-15  |

| Memory Module                           | .1-16  |

| Memory Interleaving                     |        |

| Memory Unit Address Identity            | .1-16  |

| Memory Bus Controllers                  | .1-16  |

| Memory Lock and Unlock                  |        |

| Private Memory                          |        |

| Input/Output Subsystem                  | . 1-17 |

| IOM                                     |        |

| Regional Processing Unit                | . 1-17 |

| General Purpose Multiplexer Controller  | .1-18  |

#### SECTION II CENTRAL PROCESSOR

| Introduction              | 2.   | -1 |

|---------------------------|------|----|

| Instruction Repertoire    | . 2. | -1 |

| General Purpose Registers | . 2. | -2 |

| CPU Control Modes         | 2    | -2 |

۷

Page

## TABLE OF CONTENTS (Cont'd)

# SECTION II CENTRAL PROCESSOR (Cont'd)

Page

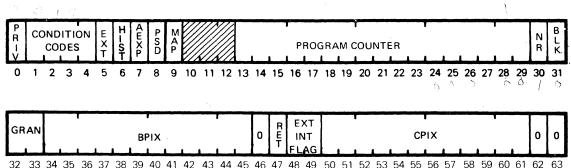

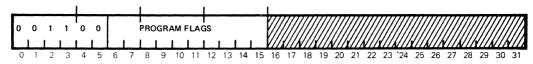

| Program Status Word                                         | 2-2    |

|-------------------------------------------------------------|--------|

| Program Status Doubleword                                   | 2-2    |

| Condition Codes                                             | 2-2    |

| Privileged and Unprivileged Operation                       | 2-2    |

| CPU Addressing Modes                                        | 2-6    |

| 512 KB Mode                                                 | 2-7    |

| 512 KB Extended Mode                                        | 2-7    |

| 512 KB Mapped Mode                                          | . 2-7  |

| Mapped Extended Mode                                        |        |

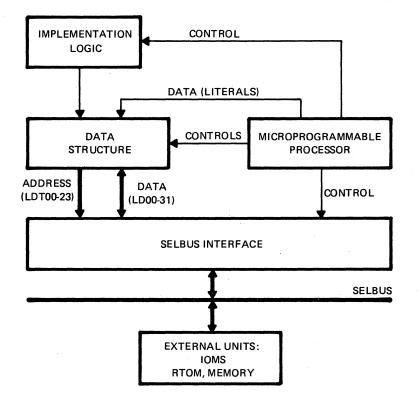

| CPU Major Elements                                          |        |

| CPU Data Structure                                          |        |

| CPU Microprogrammable Processor                             |        |

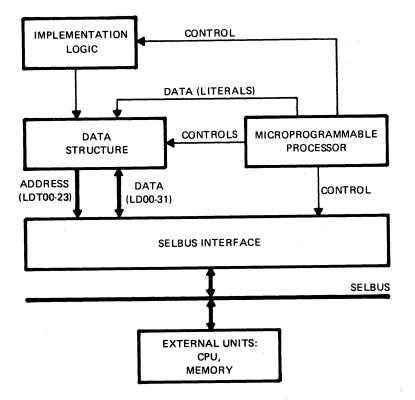

| Implementation Logic                                        |        |

| SelBUS Interface.                                           |        |

| Optional Writable Control Storage                           | 2-9    |

| Optional High-Speed Floating-Point Unit                     |        |

| Internal Processing Unit                                    |        |

| Introduction                                                |        |

| General                                                     |        |

| General Characteristics                                     |        |

| Instruction Repertoire                                      | 2_15   |

| General Purpose Registers                                   | 2-16   |

| IPU Control Mode.                                           | 2_16   |

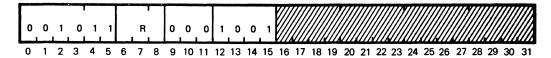

| Program Status Doubleword                                   | 2_16   |

| Condition Codes                                             | 2_16   |

| Privileged and Unprivileged Operation                       | 2_16   |

| IPU Addressing Modes                                        | 2_10   |

| 512-KB Mode.                                                | 2 10   |

| 512-KB Extended Mode                                        | 2 10   |

| 512-ND Extended Mode                                        | 2 10   |

| 512-KB Mapped Mode                                          |        |

| Mapped Extended Mode                                        | 2-19   |

| Functional Description                                      | 2-19   |

| Major System Elements                                       |        |

| Central Processing Unit                                     |        |

| IPU Major Elements.                                         | ··/-/1 |

| IPU Data Structure                                          |        |

| IPU Microprogrammable Processor                             | ••2=22 |

| Implementation Logic                                        |        |

| SelBUS Interface<br>Optional High-Speed Floating-Point Unit | ••८=८८ |

| Optional High-Speed Floating-Point Unit                     | ••     |

| Optional Scientific Accelerator                             |        |

| Optional Writable Control Storage                           |        |

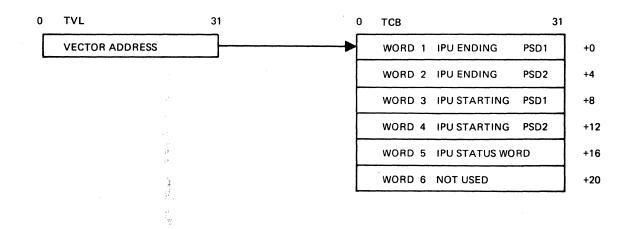

| Traps                                                       | ••2-24 |

| New Traps                                                   | 2-24   |

| Operating Mode                                              | ••2-24 |

| Trap Context Switching                                      | 2-24   |

| Trap Format                                                 | 2-24   |

| IPU Status Word                                             |        |

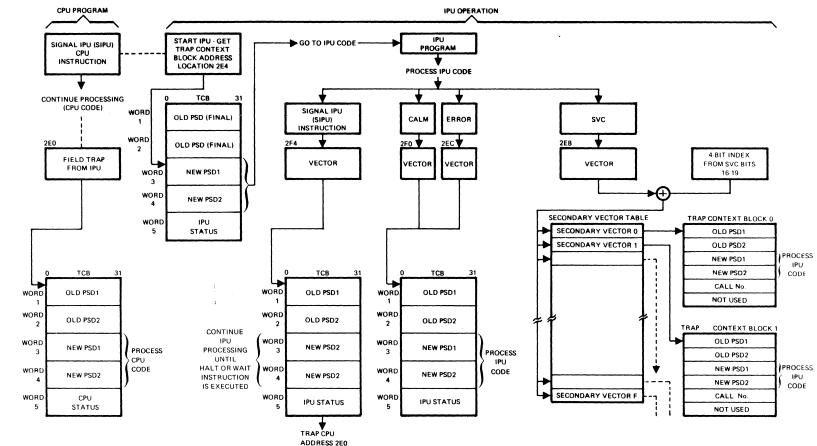

| CPU/IPU Interface Operation                                 | ••2-27 |

| Start IPU Trap (Vector Address 2E4)                         |        |

| Restart IPU                                                 | 2-28   |

## SECTION II CENTRAL PROCESSOR (Cont'd)

| P  | а | n | ρ |

|----|---|---|---|

| F. | α | u | C |

| IPU Error Condition Trap (Vector Address 2EC).<br>IPU Call Monitor Trap (Vector Address 2F0).<br>IPU Supervisor Call Trap (Vector Address 2E8).<br>Stop IPU Trap Vector Address 2F4.<br>CPU (End IPU Processing) Trap (Vector Address 2E0).<br>Memory Management.<br>Input/Output System.<br>Scratchpad Memory.<br>Initial ization.<br>Introduction.<br>Initial Program Load | 2-31<br>2-31<br>2-31<br>2-31<br>2-31<br>2-32<br>2-32<br>2-32<br>2-32 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Introduction<br>Initial Program Load<br>Power Fail-Safe Feature                                                                                                                                                                                                                                                                                                              | 2-32                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

#### SECTION III TRAPS AND INTERRUPTS

| Introduction                    | 3-1  |

|---------------------------------|------|

| Traps                           | 3-1  |

| Interrupts                      | 3-1  |

| Operating Modes                 |      |

| PSW Mode                        |      |

| PSD Mode                        |      |

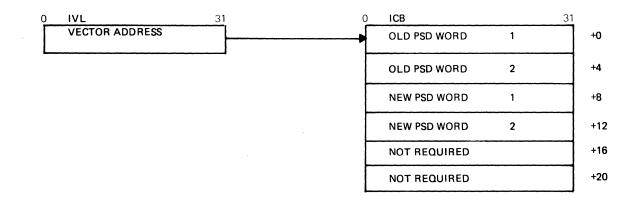

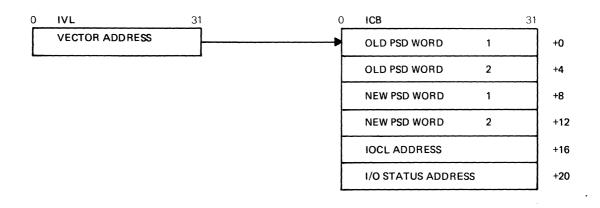

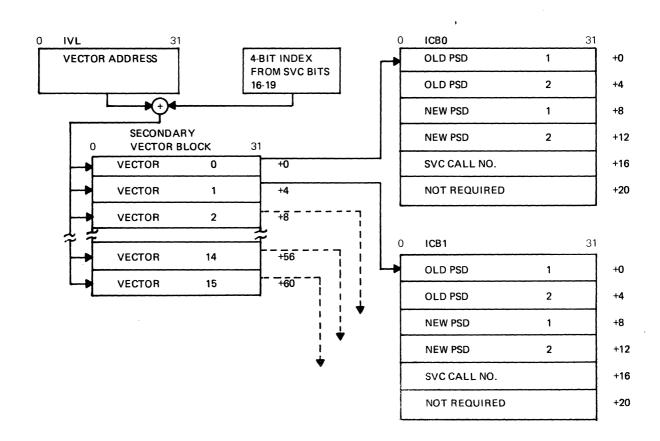

| IVL and ICB                     | 3-6  |

| ICB Formats                     |      |

| 01d and New PSD                 | 3-6  |

| External and Non-Class F Format | 3-6  |

| Trap Format                     | 3-6  |

| Class F I/O Format              | 3-8  |

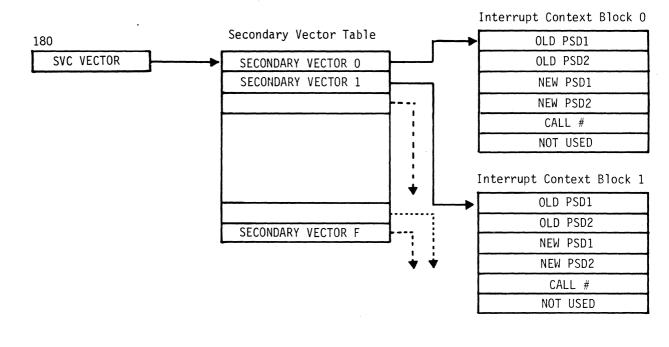

| Supervisor Call Format          | 3-8  |

| PSD Macro Instructions          |      |

| Automatic Trap Halts            | 3-10 |

| PSW Trap Halts                  |      |

| PSD Trap Halts                  | 3-10 |

| Machine Check Trap              | 3-10 |

| System Check Trap               | 3-11 |

| Block Mode Time-Out Trap        | 3-11 |

| PSD Trap Halt Implementation    |      |

## TABLE OF CONTENTS (Cont'd)

## SECTION IV MEMORY MANAGEMENT

| ~ |   |   |   |

|---|---|---|---|

| v | - | ~ | 0 |

| F | α | u |   |

| Introduction                     | 4-1  |

|----------------------------------|------|

| 0verview                         |      |

| MOS and Core Memory              | 4-1  |

| 600/900 ns Core Memory Modules4  | 1-2  |

| Mixed Memory Rules               | 1-2  |

| Memory Reference Instructions    | 4-3  |

| F- and C-Bits                    | 4-4  |

| Direct Addressing4               |      |

| Indirect and Indexed Addressing4 |      |

| Indexed Addressing               |      |

| Indirect Addressing              |      |

| Words, Halfwords, and Bytes      | 4-6  |

| Word and Doubleword Operands     |      |

| Hardware Memory Management       |      |

| Addressing Modes                 |      |

| 512 KB Mode                      |      |

| 512 KB Extended Mode             |      |

| 512 KB Mapped Mode               |      |

| Mapped Extended Mode             |      |

| Memory Mapping                   |      |

| Memory Protection.               |      |

| Program Status Doubleword        |      |

| PSD Fields                       |      |

| Condition Codes                  |      |

| MAP Description.                 |      |

| Master Process List              |      |

| Address Generation               |      |

| Auuress ucherativn               | +-1/ |

# SECTION V INPUT/OUTPUT SYSTEM

| Introduction                                       |    |

|----------------------------------------------------|----|

| I/O Processor Classifications                      | 4  |

| Operation With Class 0, 1, 2, and E I/O Processors | 4  |

| Command Device Instruction                         |    |

| Transfer Control Word                              |    |

| Test Device Instruction5-                          |    |

| Input/Output Processor5-:                          | 10 |

| SelBUS Interface                                   |    |

| Transfer Responses5-:                              | 11 |

| IOM Data Structure                                 |    |

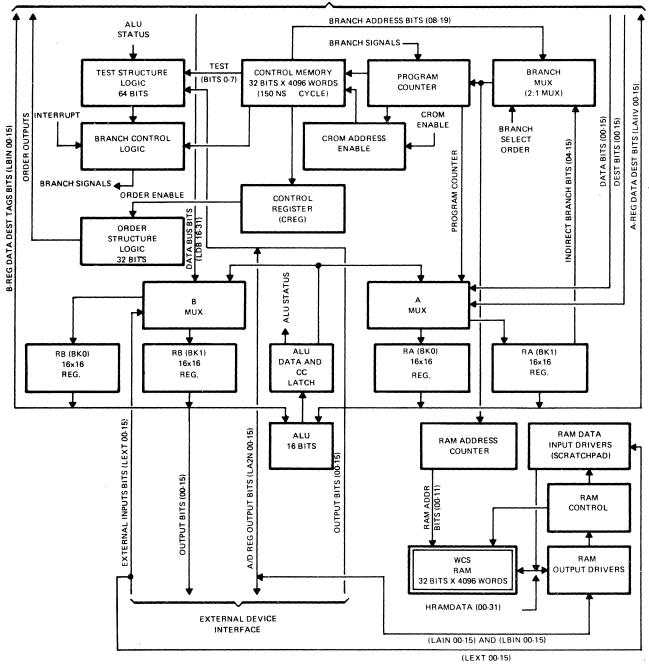

| Arithmetic Logic Unit5-:                           |    |

| Data Structure Control5-                           |    |

| Test Structure                                     | 11 |

# SECTION V INPUT/OUTPUT SYSTEM (Cont'd)

|                                   | Page   |

|-----------------------------------|--------|

| Interrupts                        | 5-11   |

| Class F I/O Operation             | 5-11   |

| Class F I/O Processor             | 5-12   |

| Memory Addressing Method.         |        |

| PSD Mode I/O Instructions         |        |

| Start I/O                         |        |

| Test I/0                          |        |

|                                   |        |

| Halt I/0                          |        |

| Enable Channel WCS Load           |        |

| Write Channel WCS                 |        |

| Enable Channel Interrupt          |        |

| Disable Channel Interrupt         |        |

| Activate Channel Interrupt        |        |

| Deactivate Channel Interrupt      |        |

| Reset Channel Interrupt           |        |

| Stop I/0                          |        |

| Reset Controller                  | . 5-17 |

| Grab Controller                   |        |

| Input/Output Command List Address | .5-17  |

| Input/Output Command Doubleword   | . 5-17 |

| Input/Output Commands             | . 5-18 |

| Write                             |        |

| Read                              | . 5-18 |

| Read Backword                     |        |

| Control                           |        |

| Sense                             |        |

| Transfer In Channel               |        |

| Channel Control                   |        |

| Input/Output Termination          |        |

| Input/Output Status Words         |        |

| Input/Output Status words         |        |

| Input/Vutput InterTupt5           | . 5-20 |

## SECTION VI INSTRUCTION REPERTOIRE

| Introduction                                  | .6-1 |

|-----------------------------------------------|------|

| Instruction Name                              | .6-1 |

| Operation Code<br>Format                      |      |

| Definition                                    | .6-1 |

| Summary ExpressionAssembly Coding Conventions | .6-1 |

| Condition Code Results                        | .6-4 |

## TABLE OF CONTENTS (Cont'd)

## SECTION VI INSTRUCTION REPERTOIRE (Cont'd)

| Examples                                    |

|---------------------------------------------|

| Instruction Mnemonics                       |

| Assembler Coding Conventions                |

| Instruction Definition Format               |

| Load/Store Instructions                     |

| Register Transfer Instructions              |

| Memory Management Instructions              |

| Writable Control Storage (WCS) Instructions |

| Branch Instructions                         |

| Branch Programming                          |

| Compare Instructions                        |

| Logical Instructions                        |

| Shift Operation Instructions                |

| Bit Manipulation Instructions               |

| Fixed-Point Arithmetic Instructions6-136    |

| Floating-Point Arithmetic Instructions6-170 |

| Control Instructions                        |

| Interrupt Instructions                      |

| Input/Output Instructions                   |

| Class F I/0 Instructions                    |

| IOCD Format for Class F I/O WCS6-227        |

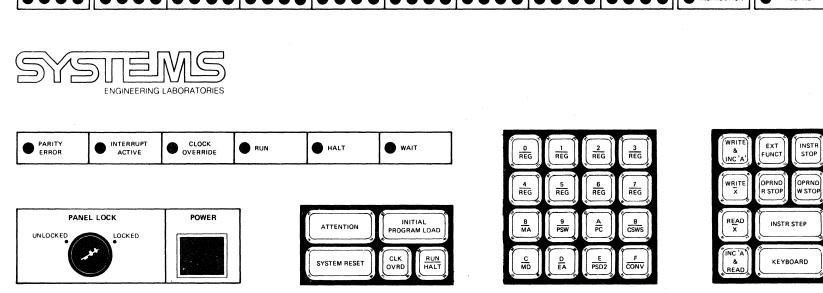

#### SECTION VII CONTROL PANEL

| General                   | -1 |

|---------------------------|----|

| Run/Halt                  | -1 |

| System Reset              |    |

| Attention                 |    |

| Initial Program Load      |    |

| Clock Override            | -1 |

| Operation/Mode Indicators | ٠Ļ |

| Parity Error              |    |

| Clock Override            | -3 |

| Run                       |    |

| Halt                      |    |

| Wait                      |    |

| Keyboards                 |    |

| Hexadecimal Keyboard      |    |

| Function Keyboard         | -4 |

## SECTION VII CONTROL PANEL (Cont'd)

|                                  | Page  |

|----------------------------------|-------|

| WRITE Key                        | . 7-4 |

| Х<br><u>READ</u> Кеу             | 7-4   |

| X<br>WRITE & INC 'A' Key         | .7-4  |

| INC 'A' & READ Key               |       |

| EXT FUNCT Key                    | . 7-5 |

| INSTR STOP Key                   | .7-5  |

| OPRND R STOP Key                 | . 7-5 |

| OPRND W STOP Key                 |       |

| INSTR STEP Key                   | . 7-5 |

| KEYBOARD Key                     |       |

| Panel Displays                   | . 7-6 |

| A-Display                        | .7-6  |

| B-Display                        |       |

| Odd/Even Indicators              |       |

| EVEN REGISTER Indicator          | .7-8  |

| ODD REGISTER Indicator           |       |

| Miscellaneous Indicators         |       |

| MEMORY ADDRESS Indicator         |       |

| PSW Indicator.                   |       |

| PROGRAM COUNTER Indicator        |       |

| OPERATOR FAULT Indicator         |       |

| MEMORY DATA Indicator.           |       |

| EFFECTIVE ADDRESS Indicator      |       |

| ERROR Indicator.                 |       |

| CONTROL SWITCHES Indicator       |       |

| KEYBOARD Indicator.              |       |

| INSTRUCTION Indicator            |       |

| STOP Indicator.                  |       |

| INSTR STOP Indicator             | 7-10  |

|                                  |       |

| OPERAND WRITE STOP Indicator     |       |

| OPERATOR FAULT Indicator         |       |

| Miscellaneous Indications        | 7-11  |

| Operating Instructions           | 7-11  |

| Load B-Display From Hex Keyboard | 7-11  |

| Load A-Display                   | 7-11  |

| Write Memory Address             | 7-12  |

|                                  | 7-12  |

| Read PSW                         |       |

| Write PSD2                       |       |

| Read PSD2                        |       |

| Write Program Counter            | .7-13 |

| Read Program Counter             | 7-13  |

| Write Memory (Single Address)    | .7-14 |

| Read Memory (Single Address)     | .7-14 |

| Instruction Step                 | .7-15 |

| Read Effective Address           |       |

xi

## TABLE OF CONTENTS (Cont'd)

# SECTION VII CONTROL PANEL (Cont'd)

| P | 'n | a | P |

|---|----|---|---|

|   | α  | м | C |

| Convert Address               |  |

|-------------------------------|--|

| Stop Sequence                 |  |

| Control Switches Sequence     |  |

| Write Control Switches        |  |

| Read Control Switches         |  |

| Initial Program Load Sequence |  |

#### SECTION VIII SYSTEM INITIALIZATION

| Initial Program Load (IPL)8-1                         | L |

|-------------------------------------------------------|---|

| Formats of the Initial Configuration Load (ICL)8-1    | L |

| Format #1                                             | 2 |

| Format #2                                             | 3 |

| Format #3                                             | 3 |

| Examples of Initial Configuration Load (ICL) Records) | 3 |

#### APPENDICES

| APPENDIX A | Instruction Set (Functionally Grouped)A-1              |

|------------|--------------------------------------------------------|

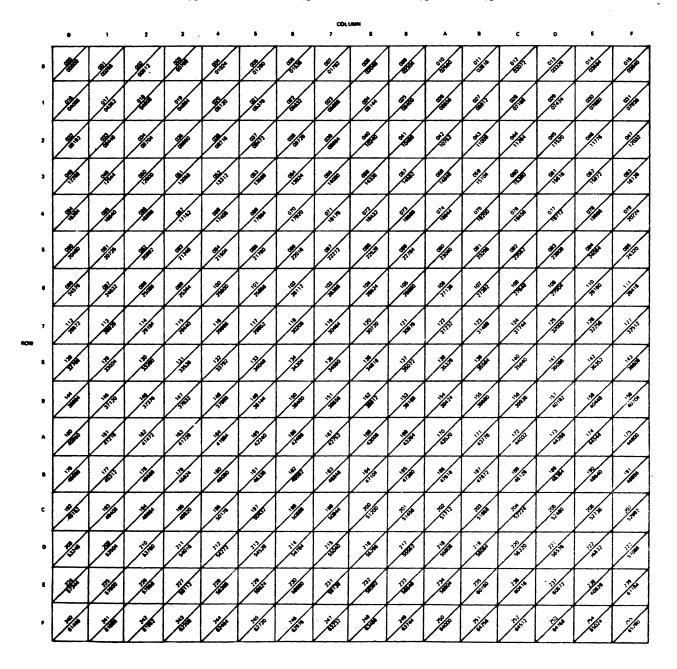

| APPENDIX B | Hexadecimal-Decimal Conversion TableB-1                |

| APPENDIX C | Hexadecimal Conversion TableC-1                        |

| APPENDIX D | Hexadecimal AdditionsD-1                               |

| APPENDIX E | Numerical InformationE-1                               |

|            | Table of Powers of Sixteen and Tables of Powers of Ten |

| APPENDIX G | ASCII Interchange Code Set with Card Punch Codes       |

Figure

| rigure       | i uge                                                                 |

|--------------|-----------------------------------------------------------------------|

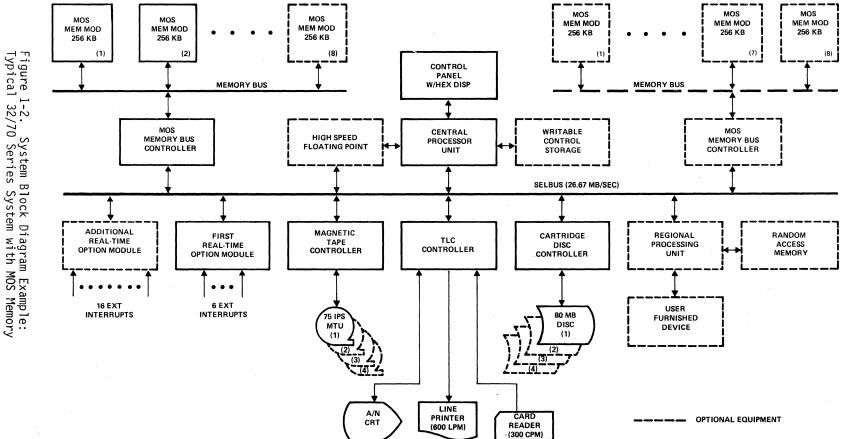

| 1-1          | System Block Diagram Example: Typical 32/70 Series System with        |

|              | Core Memory                                                           |

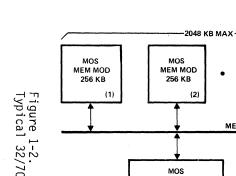

| 1-2          | MOS Memory                                                            |

| 2-1          | Program Status Word (PSW) Format2-4                                   |

| 2-2          | Program Status Doubleword (PSD) Format                                |

| 2-3          | CPU - Simplified Block Diagram2-8                                     |

| 2-4          | Microinstruction Format                                               |

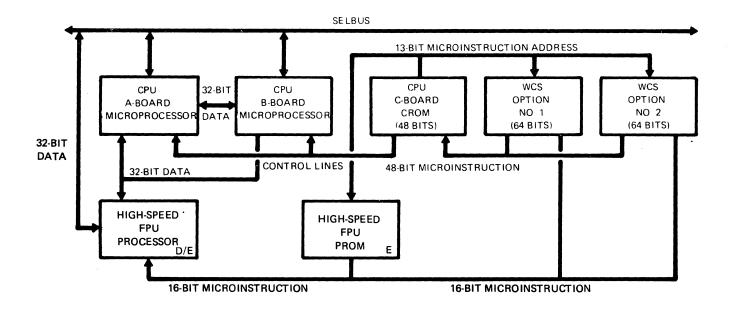

| 2-5          | Functional Interrelationship: CPU, WCS, and High-Speed FPU            |

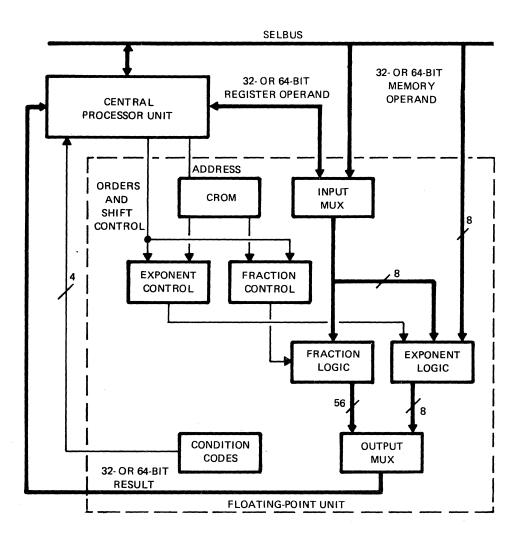

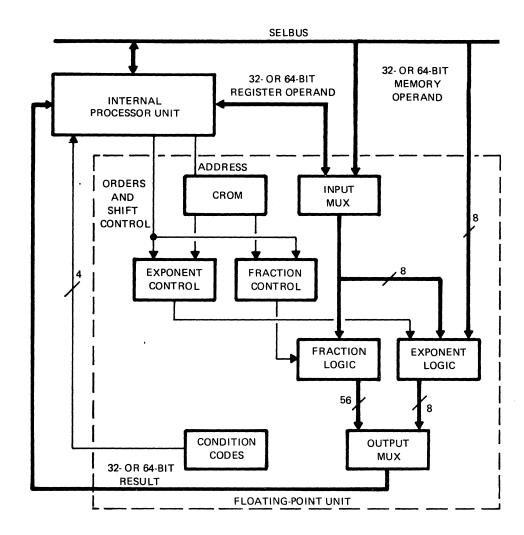

| 2-6          | Optional High-Speed Floating-Point Unit2-13                           |

| 2-7          | Program Status Doubleword (PSD) Format2-17                            |

| 2-8          | System Block Diagram2-20                                              |

| 2-9          | IPU Simplified Block Diagram2-21                                      |

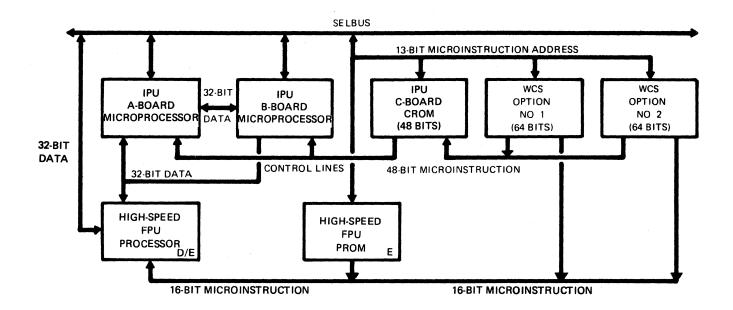

| 2-10         | Microinstruction Format                                               |

| 2-11         | Optional High-Speed Floating-Point Unit2-25                           |

| 2-12         | Functional Interrelationship of the IPU, WCS, and High-Speed Floating |

| L 16         | Point Unit                                                            |

| 2-13         | Trap Context Block Format (Internal Processing Unit)2-28              |

| 2-14         | CPU/IPU Interface Operational Flow                                    |

| 3-1          | Interrupt Context Block Format - External Interrupts and Non-Class    |

| J-1          | F I/O Interrupts                                                      |

| 3-2          | Tran Context Block Format                                             |

| 3-3          | Trap Context Block Format                                             |

| 3-4          | Supervisor Call (SVC) Trap Context Block Format                       |

| 4-1          | Information Boundaries in Memory                                      |

| 4-2          | Map Image Descriptor List                                             |

| 4-3          | Memory Management Components                                          |

| 4-4          | Formats for PSD1 and PSD2                                             |

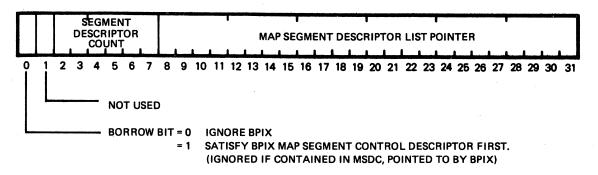

| 4-5          | Map Segment Control Descriptor (MSCD)                                 |

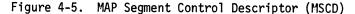

| 4-6          | Map Segment Descriptor (MSD)                                          |

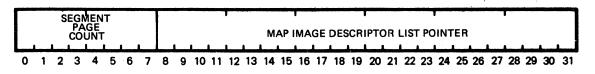

| 4-7          | Map Image Descriptor (MID)                                            |

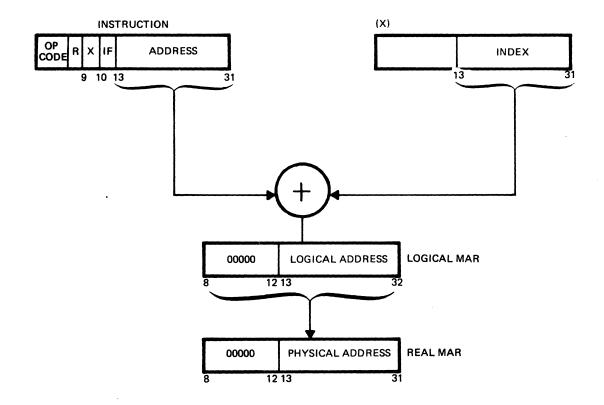

| 4-8          | Address Generation (512 KB Mode)                                      |

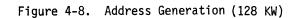

| 4-9          | Address Generation (512 KB Extended Mode)                             |

| <b>4-</b> 10 | Address Generation (512 KB Mapped Mode)4-21                           |

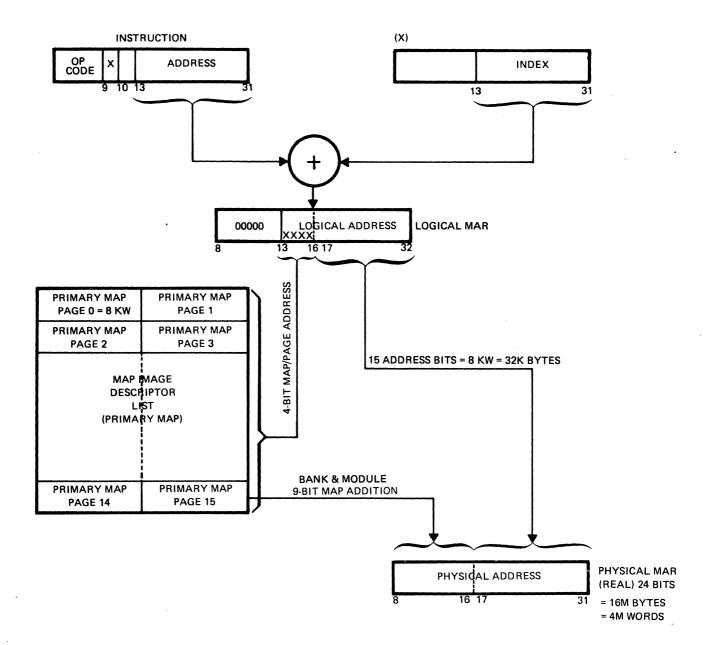

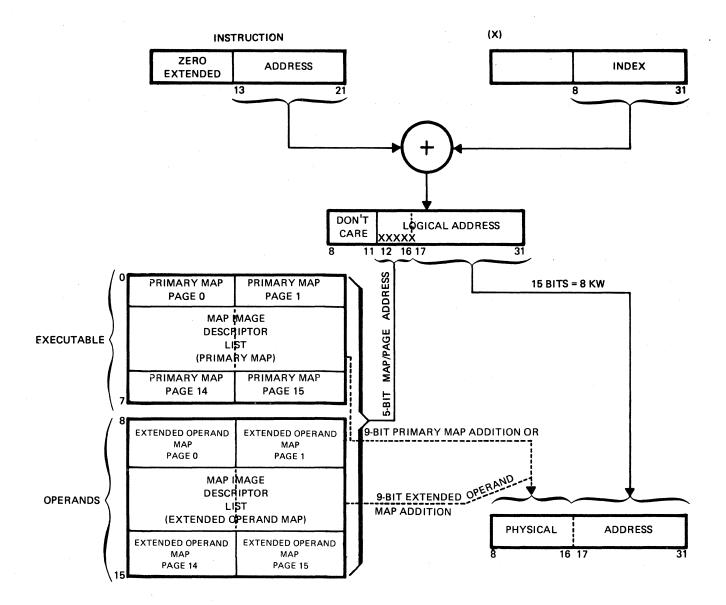

| 4-11         | Address Generation (Mapped, Extended Mode)                            |

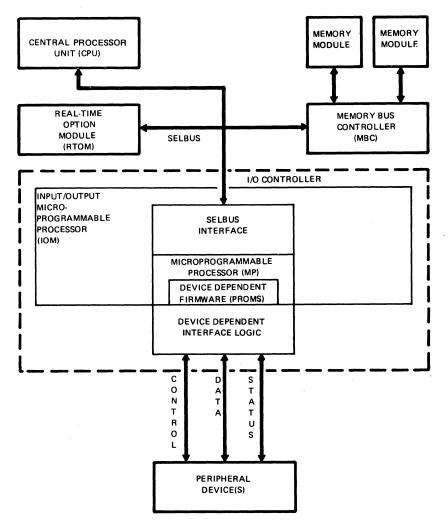

| 5 <b>-</b> 1 | 32/70 Series Input/Output Organization                                |

| 5-2          | Block Diagram - Regional Processing Unit (RPU)                        |

| 5-3          | Class 0, 1, 2, and E I/O Organization $5-6$                           |

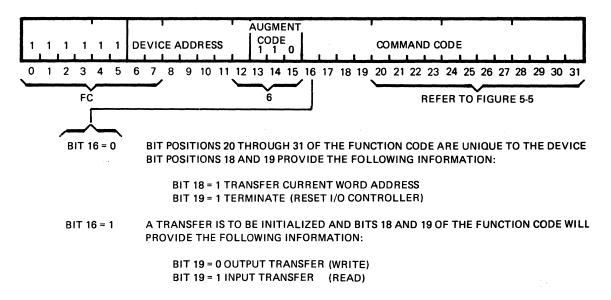

| 5-4          | Command Device Instruction Format                                     |

| 5-5          | Command Device Function Bit Format for Peripheral Devices             |

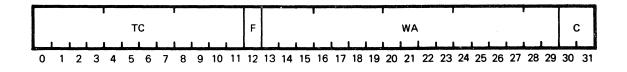

| 5-5<br>5-6   | Transfer Control Word Format                                          |

| 5-0<br>5-7   | Test Device Instruction Format                                        |

| 5-8          | Test Device 2000 Status Information                                   |

| 5-9          | Block Diagram - I/O Microprogrammable Processor                       |

| 5-10         | System Configuration With Class F I/O Processor                       |

| 5-11         | I/O Control Words (Class F)                                           |

| 5-12         | Input/Output Command Doubleword (IOCD)                                |

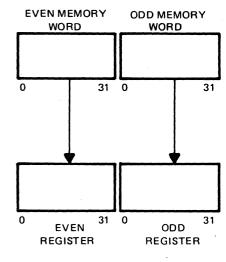

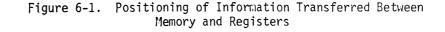

| 6-1          | Positioning of Information Transferred Between Memory and Registers   |

| 7-1          | 32/70 Series Serial Control Panel                                     |

| 8-1          | System Initial Configuration Load (ICL) Deck                          |

| 0-1          | System Initial contriguration Load (ICL) DECK                         |

#### LIST OF TABLES

6-2 6-3

#### Table Relationship of CPU Modes.1-12PSW and PSD Modes:Functional Differences.PSD Mode (IPU).2-18CPU/IPU Communication Traps.2-27IPU Status Word Bit Definitions.2-30PSW/PSD Mode Relative Trap/Interrupt Priorities.3-2Transfor Control Word Format Code5 1-1 2-1 2-2 2-3 2-4 3-1 5-1 6-1

Page

WARNING

This equipment generates, uses, and can radiate radio frequency energy, and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. As temporarily permitted by regulation it has not been tested for compliance with the limits for Class A computing devices pursuant to subpart J of part 15 of FCC rules, which are designated to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

#### SECTION I

#### **GENERAL DESCRIPTION**

#### INTRODUCTION

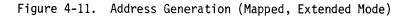

SYSTEM OVERVIEW The 32/70 Series computer systems are high-speed, general purpose, digital systems that are designed for a variety of scientific, data acquisition, and real-time applications. A basic system includes a central processor, main memory subsystem, and microprogrammed input/ output controllers. Each major system element operates semi-independently with respect to the other elements.

The basic system can be readily expanded to accommodate the user's requirements. Main memory (Core or MOS) has addressing space for 16 million bytes. In a multiprocessor environment, memory can be configured with up to 20 access routes. Input/output capability can be increased by adding more I/O Micro-programmable Processors (IOMs), Regional Processing Units (RPUs), multiplexers, device controllers, and I/O devices.

The CPU has a large instruction set that includes fixed- and floatingpoint arithmetic instructions. A special lookahead feature enables the CPU to overlap instruction execution with memory accessing, thereby reducing program execution time. A large main memory of up to 16 million bytes (4M words) is available. The memory can consist of up to 16 module increments on each of up to 16 memory buses. Memory can be shared by up to eight CPUs and their associated I/O processors.

Each memory module operates independently of all others and address interleaving can be provided between adjacent modules. This multiaccess memory subsystem with interleaving provides system performance far superior to other design concepts. A 32/70 Series system can support up to 16 independent I/O processors of four types - IOMs, RPUs, multiplexers, and high-speed data interfaces - with a maximum aggregate data transfer rate of up to 16.67 million bytes per second, concurrent with CPU instruction execution.

The existing 32/35 and 32/55 programs can be run on a 32/70 Series computer in the PSW mode. The upward compatibility of the software (assemblers, compilers, mathematical and utility routines, and application packages) virtually eliminates reprogramming.

<u>GENERAL CHAR-</u> <u>ACTERISTICS</u> All 32/70 Series computer systems contain features and functional characteristics that promote efficient operation in general purpose, multiprocessing, real-time, and multiusage environments.

- Byte-oriented memory (8-bit byte plus one parity bit) which can be addressed and altered as bit, byte (8-bit), halfword (2-byte), word (4-byte), and doubleword (8-byte) quantities.

- 600- or 900-nanosecond core memory.

- 900-nanosecond MOS memory with error checking and correction.

1-1

- Both core and MOS memory expandable to 16,777,216 (16M) bytes in some models.

- Indexed addressing capability (PSW or PSD mode with extended addressing) of entire memory.

- Multilevel indirect addressing with indexing at each level.

- Immediate operand instructions for greater storage efficiency and increased speed.

- Eight general purpose registers that may be used for arithmetic, logical, and shift operations, as well as masking, linking, and indexing.

- Hardware memory mapping to reduce memory fragmentation and to provide dynamic program relocation.

- Memory write protection to prevent inadvertent destruction of critical areas of memory.

- Real-time priority interrupt system of up to 112 levels with automatic identification and priority assignment; external interrupt levels which can be individually enabled, disabled and requested by program.

- Automatic traps (for error or fault conditions) that have masking capability and maximum recoverability under program control.

- Power fail-safe for automatic shutdown in the event of power failure and resumption of processing after power is restored.

- Multiple interval timers with a choice of resolutions for independent time bases.

- Privileged instruction logic for program integrity in multiusage environments.

- A complete instruction set that includes the following:

- Bit, byte, halfword, word, and doubleword operations.

- Register-to-register operations with halfword instructions to improve program execution time.

- Fixed-point integer arithmetic operations on byte, halfword, word, and doubleword operands.

- Floating-point arithmetic operations in single and double precision formats.

- Full complement of logical operations (AND, OR, Exclusive OR) for bytes, halfwords, words, and doublewords.

- Comparison operations for bit, byte, halfword, word, and doubleword operands.

- Call Monitor and Supervisory Call instructions that allow a program access to operating system functions.

- Shift operations (left and right) of word or doubleword, including logical, circular, and arithmetic shifts.

- Built-in reliability and maintainability features:

- Full parity checking of all memory accesses.

- Address stop feature that permits operator or maintenance personnel to:

Stop on any instruction address. Stop on any memory read reference address. Stop on any memory write reference address.

- CPU traps, which provide for detection of a variety of CPU and system fault conditions, designed to enable a high degree of system recoverability.

- Independently operating I/O system with up to 16 I/O processors per CPU.

- General Purpose Multiplexer Controller (GPMC) that provides for the concurrent operation of up to 16 devices on one I/O processor.

- High-Speed Data interface (HSD) for use with high-speed devices, that allows data transfer rates of up to 3.2 million bytes per second.

- Comprehensive software that is upward program compatible with the 32/35 and 32/55 computers.

- Expands in capability and speed as system grows.

- Real-Time Monitor (RTM and Mapped Programming Executive (MPX32)).

- Language processors that include: Extended FORTRAN IV, ANS COBOL, BASIC, assembler, utilities, and applications software for real-time and scientific users.

- Standard and special purpose peripheral equipment:\*

- Cartridge Disc Units 10 million byte capacity per unit, peak transfer rate of 312K bytes per second, average access time of 35 milliseconds.

- Moving-Head Fixed Media Disc 24 million byte capacity per unit, transfer rates of 1.2 million bytes per second, average access time of 40 milliseconds.

- Moving-Head Disc Units available with 40, 80, or 300 million byte per unit capacity, transfer rates of 1.2 million bytes per second, average access time of 30 milliseconds.

- Magnetic Tape Units 9-track, 800/1600 bpi, IBM compatible, high-speed units operating at 75 inches per second with transfer rates up to 120,000 bytes per second; other units operating at 45 inches per second with transfer rates up to 72,000 bytes per second.

- Card Equipment Reading speeds up to 1,000 cards per minute.

- Line Printers Fully buffered with speeds up to 900 lines per minute, 132 print positions with 64 characters.

- Keyboard/Printers 30 characters per second.

- Paper Tape Equipment Readers with speeds up to 300 characters per second, punches with speeds up to 120 characters per second.

- Data Communications Equipment Asynchronous, synchronous, and bisynchronous communications equipment to connect remote user terminals to the computer system via common carrier lines and local terminals directly.

- \* Some packaged 32/70 Series systems are restricted in regard to peripherals due to environmental requirements.

A basic 32/70 Series System has the following standard features:

- A CPU that includes:

- Floating-point arithmetic

- Memory map with access protection

- Memory write protection

- Power fail-safe

Real-Time Option Module that includes:

- A real-time clock

- A programmable interval timer

- Sixteen interrupt levels

- Core or MOS memory (maximum amount and type varies depending on model).

- Teletype, Line Printer, and Card Reader (TLC) controller with three subchannels.

A 32/70 Series system can have the following optional features:

High-Speed Floating-Point option with up to four times the performance of the standard unit for both single and double precision operands.

- Six additional Real-Time Option Modules

- Writable Control Storage (WCS): up to 4,096 64-bit words.

- An additional 96 external priority interrupts per CPU.

- Up to 13 High-Speed Data interfaces (HSD)

- Up to five General Purpose Multiplexer Controllers (GPMCs).

- Memory shared by up to eight CPUs.

- Up to 16 device controllers with each GPMC.

- Up to 13 user-microprogrammable General Purpose I/O modules (GPIOs) and Regional Processing Units (RPUs).

- Up to 13 high-speed controllers, such as magnetic tape and disc.

GENERAL PURPOSE FEATURES All 32/70 Series Computer systems include the following general purpose features:

Floating-point instructions are available in both single (32-bit) and double (64-bit) precision formats.

<u>Indirect addressing</u> facilitates table linkages and permits keeping data sections of a program separate from procedure sections for ease of maintenance

The large instruction set (up to 189 instructions in some models) permits short, highly optimized programs to be written that minimize both program space and execution time.

<u>Monitor and Supervisory Call instructions</u> permit access to specified operating system services.

<u>A four-bit condition code</u> simplifies the checking of results by automatically providing information on instruction execution. It includes indicators for arithmetic exception, zero, minus, and plus, as appropriate.

<u>Regional Processing Units (RPU)</u> implement intelligent I/O controllers. Once initialized, an RPU operates independently of the CPU, leaving it free to provide fast response to system needs. The RPU requires minimal interaction with the CPU. Thus, many I/O devices can operate simultaneously without overloading the CPU.

<u>The High-Speed Data Interface (HSD)</u> is a single channel parallel controller that interfaces directly to the SelBUS. Once initiated, I/O operations proceed independently of the CPU. The HSD sustains a data transfer rate of up to three million bytes per second.

<u>Hardware Memory Management</u> of 32/70 Series core or MOS memory - which is available in sizes up to 16 million bytes and provides the needed capacity while assuring the potential for expansion - makes efficient use of available memory. The memory map hardware permits storing a user's program in segments of 8,192 words, wherever space is available. All segments appear as a single, contiguous block of storage at execution time. The memory map also automatically handles dynamic program relocation so the program appears to be stored in a standard way at execution time. Actually, it can be stored in a different set of locations each time it is brought into memory.

REAL-TIME FEATURES Real-time applications require: (1) hardware to respond quickly to an external environment, (2) speed to keep up with the real-time process and (3) input/output flexibility to handle a wide variety of data types at varying speeds. A 32/70 Series system provides the following real-time computing features:

<u>Multilevel, Priority Interrupt Structure</u> of the real-time oriented 32/70 Series systems provides a quick response to interrupts with a maximum of 112 interrupt levels. The source of each interrupt is automatically identified and responded to according to its priority. For further flexibility, each level can be individually disabled to discontinue input acceptance and to defer responses.

The way interrupt levels are programmed is not affected by the priority assignment.

Programs that deal with interrupts from special purpose devices often require checkout before the equipment is actually available. To simulate special equipment, any external interrupt level can be requested by the CPU by executing a single Request Interrupt (RI) instruction. This capability is also useful in establishing a modified hierarchy of responses. For example, when servicing a high-priority interrupt and the urgent processing is finished, it is often desirable to assign a lower priority to the rest of the service routine so that the interrupt system can respond to other critical stimuli. A service routine can do this by requesting a lower-priority interrupt level, and thereby process the remaining data after other interrupts have been serviced.

<u>Real-Time Clocks</u> are needed to handle the real-time functions that must be timed to occur at specific instants. Other timing information is also needed, such as elapsed time since a given event or the current time of day. Clocks also allow easy handling of separate time bases and relative time priorities. A 32/70 can support up to seven real-time clocks synchronized to a line frequency of 50 Hz or 60 Hz. The clocks can also run at twice the line frequency, 100 Hz or 120 Hz, or on an external source.

<u>Programmable Interval Timers</u> can be set to request an interrupt after any specified time period with a 300-nanosecond resolution. In addition to the real-time clocks, the system can support seven programmable interval timers.

<u>Context Switching</u> must be done quickly with a minimum of time overhead. When responding to a new set of interrupt-initiated circumstances, a computer system must preserve the current operating environment, so the program can continue later, while setting up the new environment. In a 32/70 Series system, all relevant information about the current environment (instruction address, privilege state, condition codes, address modes, etc.) is kept in a 32-bit Program Status Word (PSW) or 64-bit Doubleword (PSD). When an interrupt occurs, the CPU stores the current PSW or PSD in the memory location(s) selected by the interrupt level and loads a new PSW or PSD to establish a new environment.

Every 32/70 Series system also includes a Load File and Store File instruction so that the entire set of general purpose registers can be loaded or stored with one instruction. These instructions help make context switching fast and easy.

<u>Quick Response</u> is a 32/70 Series feature which involves the following combination: rapid context switching, store file and load file instructions, and a priority interrupt system. These features benefit all users because more of the system's resources are available for usesful work at any given time.

<u>Memory Protection</u> features that protect each user from every unprivileged user also guarantee the integrity of programs essential to critical real-time applications.

<u>Input/Output</u> requirements are available for a wide range of capacities and speeds. The 32/70 Series I/O system satisfies the needs of many different application areas economically and efficiently in terms of equipment and programming.

MULTIUSAGE FEATURES A 32/70 Series system can run programs from two or more computer application areas concurrently. The most difficult general computing problem is the real-time application because it has several requirements. The most difficult multiusage problem is a terminal-oriented application that includes one or more real-time processes. Because the 32/70 Series systems have been designed on a real-time base, they are uniquely qualified for a mixture of applications in a multiusage environment. Many hardware features that prove valuable for one application area are useful in others, although in different ways. This multiple capability makes a 32/70 Series system particularly effective in multiusage applications.

<u>The Instruction Set</u> is large enough to provide the computational and data-handling capabilities required for widely differing application areas. This allows user programs to be short and fast.

<u>Memory Protection</u> makes it possible to run both real-time and batch programs concurrently in a 32/70 Series system. Real-time programs are protected against destruction by unchecked batch programs. Under Real-Time Monitor Control, the memory write-protection feature prevents destruction of information in protected memory.

<u>Variable Precision Arithmetic</u> is important in real-time systems where the data encountered is often 16 bits or less. To process this data efficiently, as well as the data in a batch environment, the 32/70 Series computers provide bit, byte, halfword, word, and doubleword arithmetic.

<u>Priority Interrupts</u> are especially useful because they make it possible for many elements to operate simultaneously and asynchronously. An interrupt system allows the computer to respond quickly and in proper sequence to the many demands made upon it.

#### MULTIPROCESSING FEATURES

Every 32/70 Series computer is designed to function as a shared-memory, multiprocessor system. It can support up to 20 Central Processor Units that share memory, and may have up to 16 Input/Output Microprogrammable Processors per CPU. All processors in a 32/70 Series system can address shared memory using identical addresses.

The 32/70 Series computers have the following major features that allow expansion of a single processor to a multiprocessor system:

<u>Multiprocessor Interlock.</u> In a multiprocessor system, a Central Processor Unit (CPU) often needs exclusive control of a system resource. This resource can be a region of memory, a particular peripheral device, or in some cases, a specific software routine. The 32/70 Series computers have a special set of instructions to provide this required multiprocessor interlock. The special instructions are Set Bit in Memory, Reset Bit in Memory, Test Bit in Memory, and Add Bit in Memory. The Set Bit in Memory instruction sets a bit in the selected position of the referenced memory location before other CPUs are allowed to access that memory location. If this bit had been previously set by another CPU, the interlock is set and the testing program proceeds to another task. On the other hand, if the bit of the tested location is a zero, the resource is allocated to the testing CPU. Simultaneously, the interlock can be set to lock out any other CPU.

<u>Private Memory</u>. Each CPU in a multiprocessor system must retain some private memory for its trap and interrupt locations, I/O communication locations, and other dedicated locations. This private memory consists of at least 8,192 words for each CPU. This private memory must begin with real address zero. The implicitly assigned trap locations and interrupt locations occupy the first 1,096 words of private memory. The remaining words in private memory can be used as private, independent storage by the CPU.

# FUNCTIONAL DESCRIPTION

#### MAJOR SYSTEM ELEMENTS

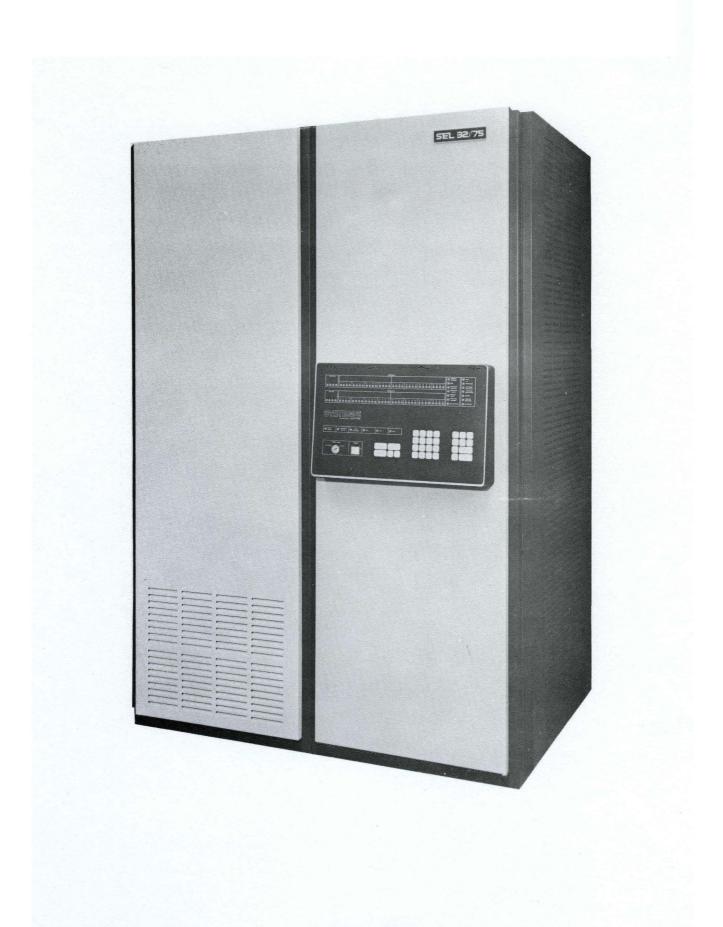

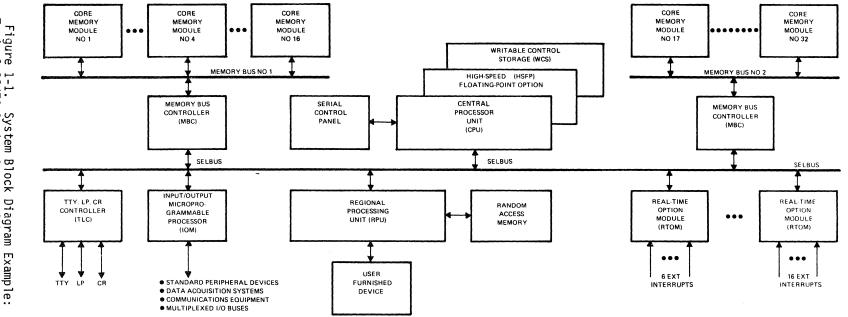

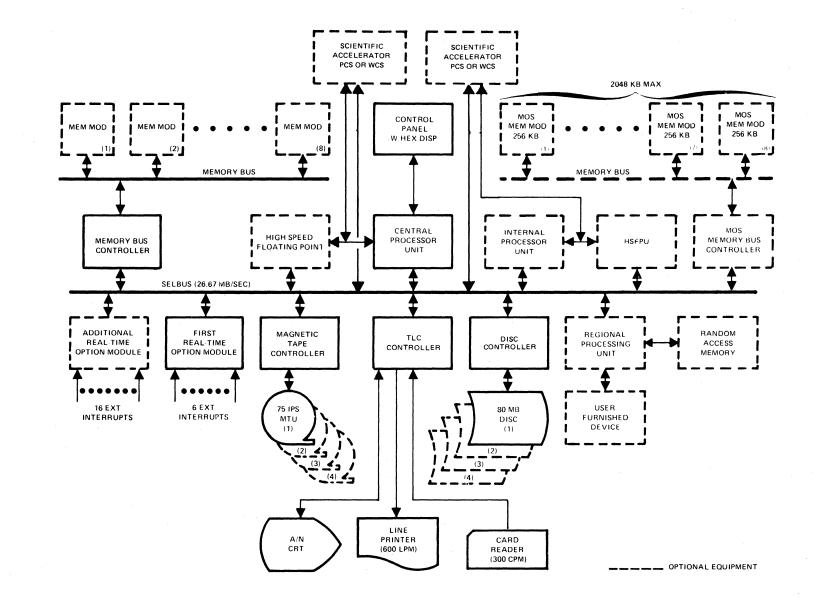

The major elements of a typical 32/70 Series computer system include: the SelBUS, a Central Processor Unit, a Real-Time Option Module, main memory, an input/output subsystem, and a System Control Panel (see Figures 1-1 and 1-2 for system block diagram examples). The overall computer system can be viewed as a group of program-controlled subsystems communicating with a common memory. Each subsystem operates semi-independently with automatic overlap of subsystem operation occurring when conditions permit. This overlap greatly enhances the speed of operation. The major elements are listed below along with a brief functional description.

- 1. SelBUS provides for high-speed communication between the major system elements.

- Central Processor Unit performs overall control and data reduction tasks.

- Real-Time Option Module implements internal and external interrupts and traps.

- 4. Main Memory provides for private and shared storage.

1

•

Figure 1-1. System Block Diagram Example: Typical 32/70 Series System with Core Memory

1-9

- 2048 KB MAX --

1-10

- 5. Input/Output Subsystem - enables information exchange between memory and selected peripheral devices.

- System Control Panel provides for user interaction 6. with the system.

Se1BUS The SelBUS is a 184-line bidirectional bus that sends and receives data between the CPU, the memory subsystem, the Regional Processing Unit (RPU), the Input/Output Microprogrammable Processors (IOMs) on 32 data lines at a continuous data rate of 26.67 million bytes per second. Twenty-four address lines are used to address the selected IOM or memory interface for a read or write operation. Both data and address lines operate concurrently, and the transfers occur every 150 nanoseconds.

> In a multiprocessor or special system configurations, remote memory subsystems, dual-processor shared-memory options, and memory ports may be connected to the SelBUS to support remote, shared, or private memory.

CENTRAL PRO-The 32/70 Series Central Processor Unit (CPU) is contained on three plug-in circuit boards. Two of the boards are the Micro Arithmetic/ Logic Unit. The third board is the Micro Control Unit, which is some-CESSOR UNIT times referred to as the personality board.

> Instructions on a 32/70 Series computer are continuously and automatically fetched for processing. This occurs concurrently with execution and decoding of previous instructions. Decoding is by proprietary parsing logic which employs parallel Read-Only Memories (ROMs) for high-speed decoding.

GENERAL Eight integrated-circuit, 32-bit general purpose registers (GPRs) are used by the CPU. These eight registers of fast memory are referred to PURPOSE as the general purpose file. REGISTERS

> Each general purpose register is identified by a 3-bit code in the range 000 through 111 (0 through 7 in decimal). Any general purpose register can be used as a fixed-point accumulator, floating-point accumulator, or temporary data storage location. A register can also contain control information such as a data address, count, or pointer. General purpose registers 1 through 3 can be used as index registers. Register 4 can be used as a mask register. Register 0 is a link register and an interval timer count.

A firmware floating-point arithmetic processor is standard with the Central Processor Units. The firmware floating-point arithmetic processor executes all floating-point instructions significantly faster than normal software floating-point routines.

A 32/70 Series computer can operate in eight different modes: four control modes (PSW-Privileged, PSW-Unprivileged, PSD-Privileged, PSD-Unprivileged) and four addressing modes (512 KB, 512 KB Extended, 512 KB Mapped, Mapped Extended).

The Extended mode can mean either 1 megabyte or 16 megabytes depending on the mapping mode. Table 1-1 shows the interrelationships among the control and address modes.

FLOATING-POINT ARITHMETIC PROCESSOR

CPU MODES

| Control<br>Modes    | PSW        |              | PSD        |              |

|---------------------|------------|--------------|------------|--------------|

| Addressing<br>Modes | Privileged | Unprivileged | Privileged | Unprivileged |

| Unmapped            |            |              |            |              |

| 512 KB              | Х          | x            | x          | Х            |

| 512 KB Extended     | X          | x            | X          | X            |

| Mapped              |            |              |            |              |

| 512 KB              | NA         | NA           | <b>X</b> - | X            |

| Extended            | NA         | NA           | X          | X            |

|                     |            |              |            |              |

# Table 1-1. Relationship of CPU Modes

Control Modes

The basic control mode is designated either Program Status Word (PSW) or Program Status Doubleword (PSD) mode. The PSW mode allows a 32/70 Series computer to emulate the environment required to run the Real-Time Monitor (RTM); whereas the PSD mode makes it possible to create the environment required to run the Mapped Programming Executive (MPX).

The CPU, when in the PSW mode or PSD mode, can run in either the Privileged or Unprivileged mode.

Privileged operation allows the CPU to perform all of its control functions and to modify any part of the system. It is assumed that the resident operating system (operating in the Privileged mode) controls and supports the execution of other programs (which can operate in the Privileged or Unprivileged mode).

Unprivileged operation is the problem-solving mode of the CPU. In this mode, memory protection is in effect, and all privileged operations are prohibited. Privileged operations are those relating to input/output and to changes in the basic control state of the computer. All privileged operations are performed by a group of privileged instructions. Any attempt by a program to execute a privileged instruction while the computer is in the Unprivileged mode results in a trap.

The Privileged/Unprivileged mode control bit can be changed when the computer is in the Privileged mode. An Unprivileged mode program can gain direct access to certain executive program operations by means of Supervisory Call or Call Monitor instructions. The operations available through these instructions are established by the resident operating system.

Addressing Modes The basic addressing modes are designated either Unmapped or Mapped. Addressing submodes are 512 KB or extended addressing (refer to Table 1-1).

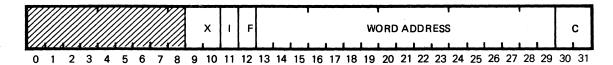

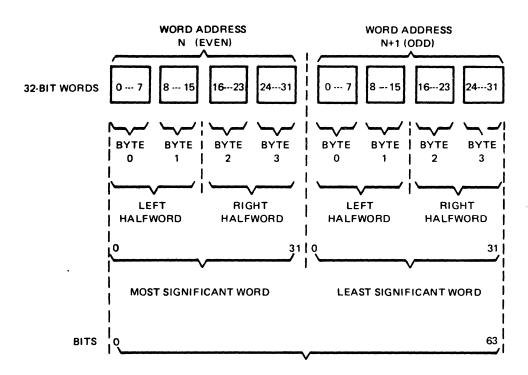

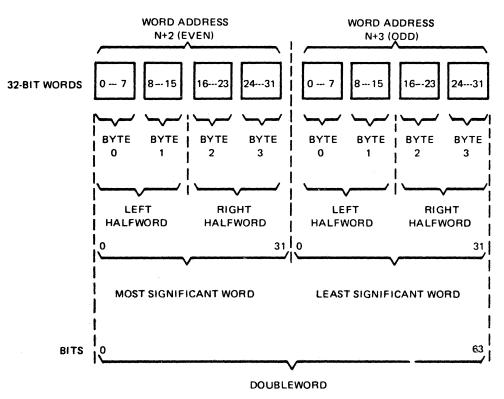

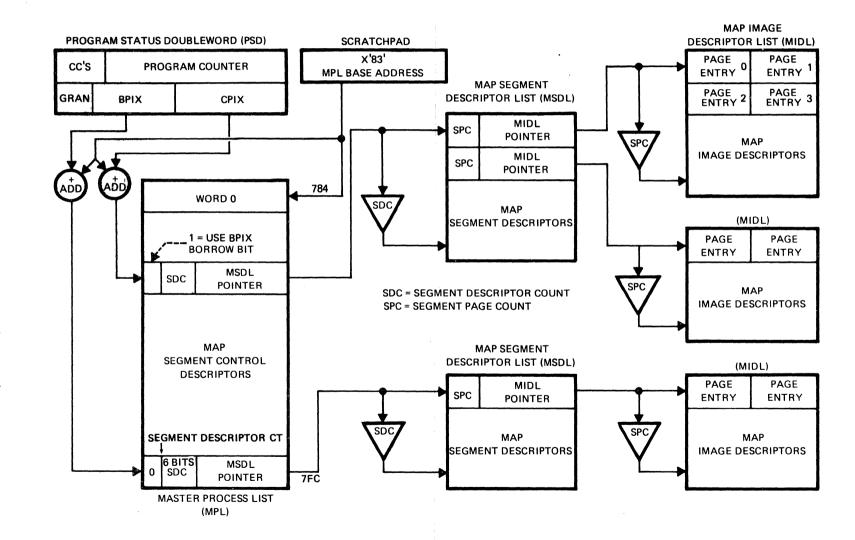

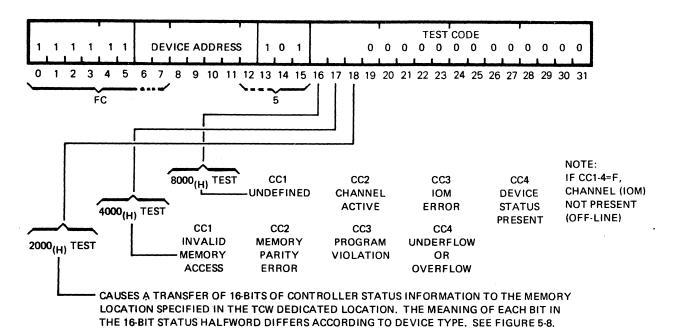

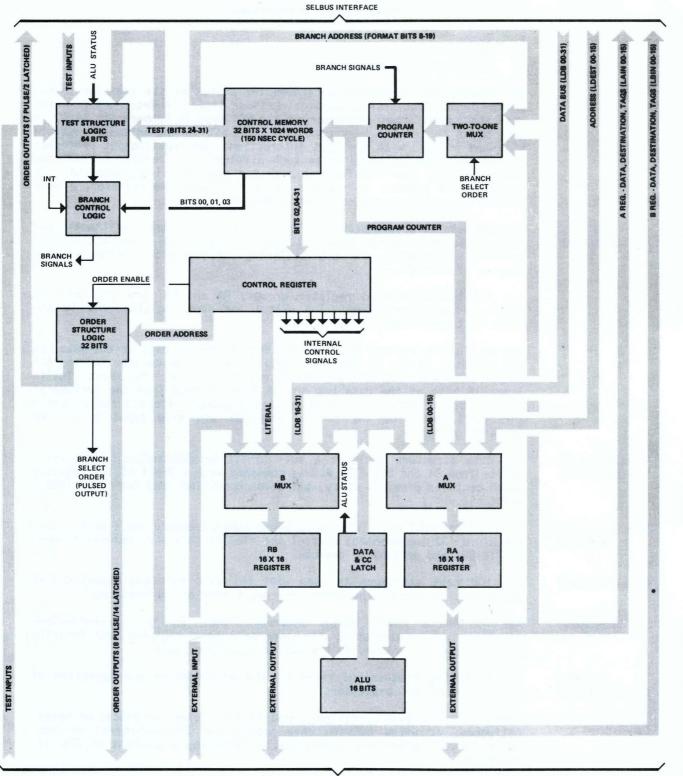

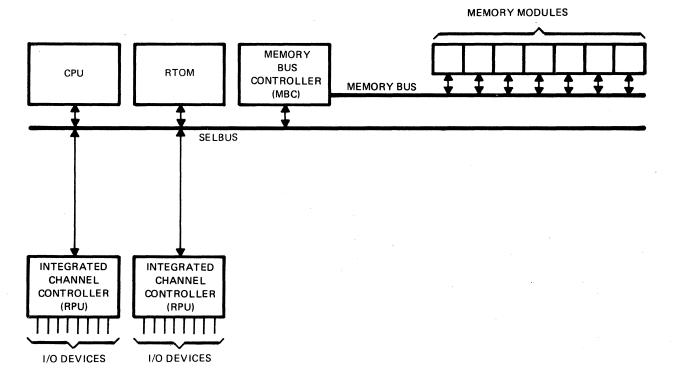

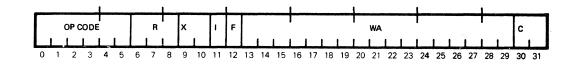

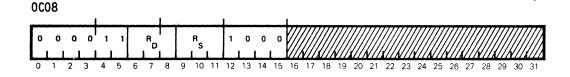

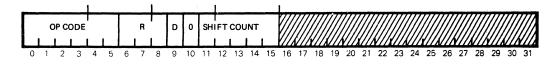

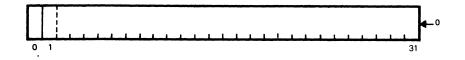

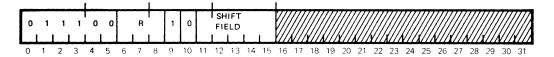

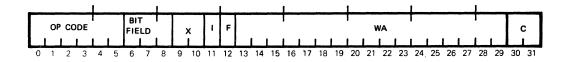

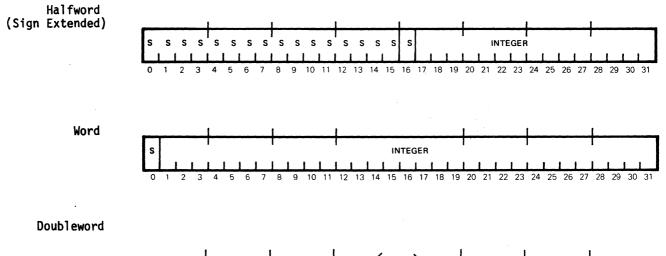

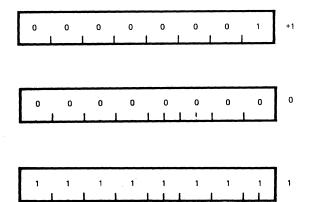

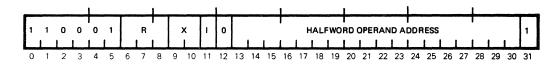

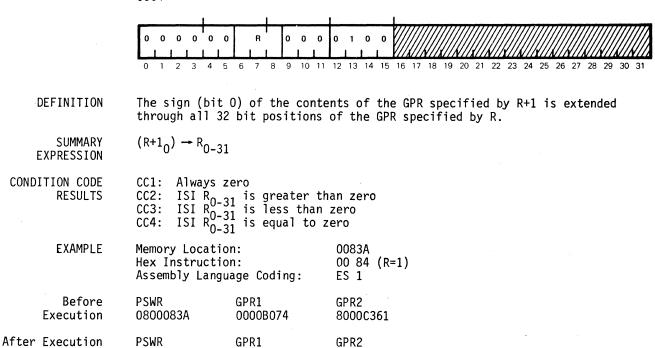

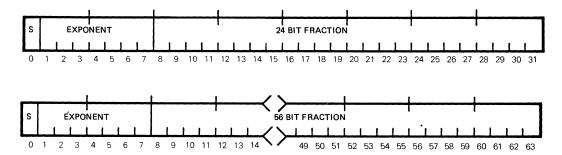

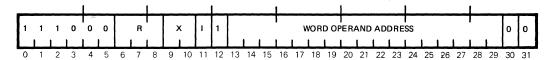

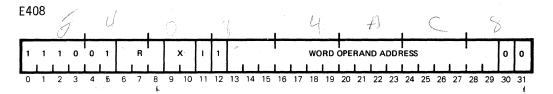

Unmapped addressing establishes a one-to-one relationship between the effective virtual address of each operand or instruction and the physical address in memory.