# IBM Customer Engineering Manual of Instruction

| Issued to:                                                                  |

|-----------------------------------------------------------------------------|

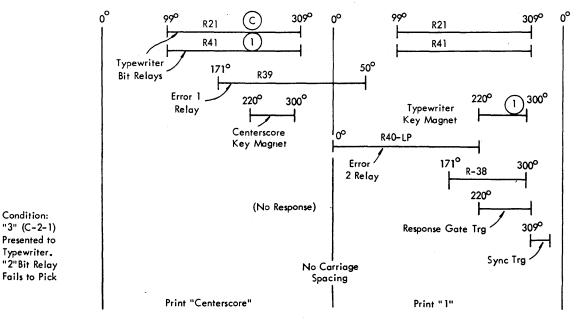

| Branch Office:                                                              |

| Department:                                                                 |

| Address:                                                                    |

| If this manual is misplaced, it should<br>be returned to the above address. |

# 1620 Data Processing System

E Level

This manual describes the IBM 1620 Data Processing System (serial No. 10701 and up) and associated Input/Output equipment. For machines prior to the E-level suffix (below serial No. 10700), order Form 227-5507-1.

● 1962 by International Business Machines Corporation

International Business Machines Corp., Product Publications Dept., San Jose, Calif.

# Contents

| P                                                                                                       | age      |

|---------------------------------------------------------------------------------------------------------|----------|

| Section 1—General Information                                                                           |          |

| Machine Language                                                                                        | 6        |

| Section 2—Memory Addressing and Data Flow                                                               |          |

| Memory<br>Sense Amplifiers and Memory Buffer Register (MBR)                                             | 11       |

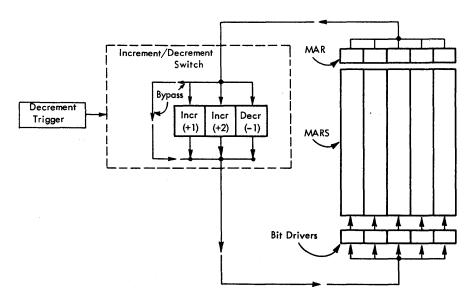

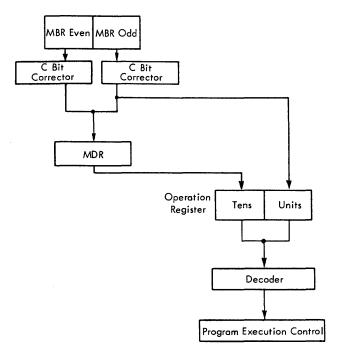

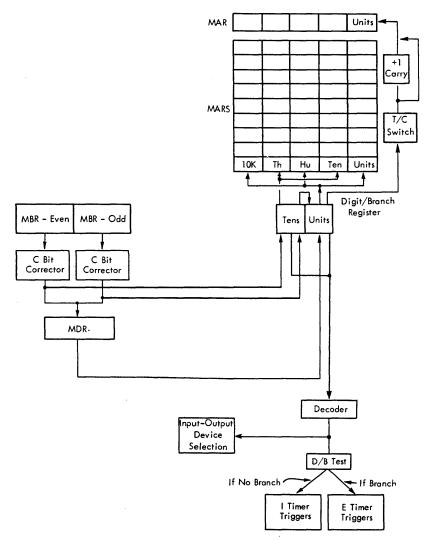

| Memory Data Register (MDR)<br>Memory Address Register Storage (MARS)<br>Increment/Decrement Switch      | 13       |

| Section 3—Programming<br>Development of a Program                                                       |          |

| Insertion of a Program into Memory (Typewriter Keyboard)<br>Execution of a Program                      | 17       |

| Automatic Program Repetition (Program Loop)<br>Insertion of a Program into Memory (Paper Tape Reader) . |          |

| Section 4—Components and Power Supply                                                                   |          |

| Component Circuits<br>Power Supplies                                                                    | 22       |

| Section 5—Functional Units                                                                              |          |

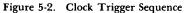

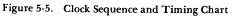

| Clock and Timing Chart                                                                                  | 40       |

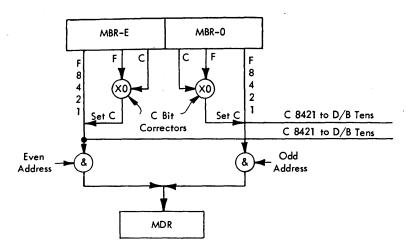

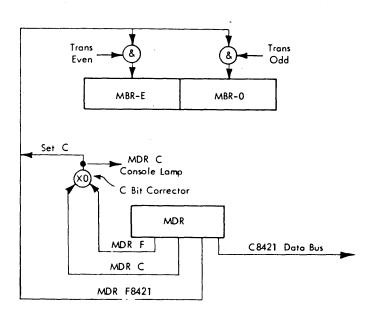

| Memory Buffer Register (мвк)<br>Memory Data Register (мок)                                              | 49       |

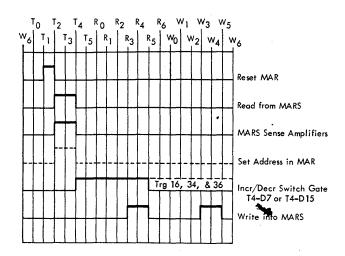

| Memory Address Register Storage (MARS)                                                                  | 49       |

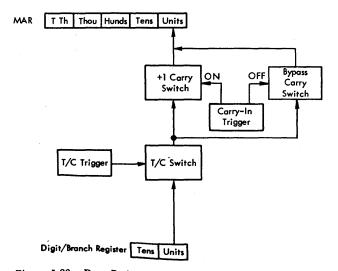

| Memory Address Register (MAR)<br>Increment/Decrement Switch                                             | 53       |

| Operation Register and Decoder<br>Digit/Branch Register and Decoder                                     | 55       |

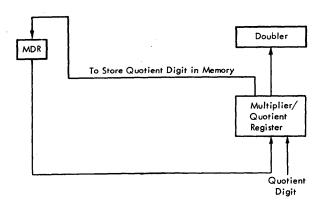

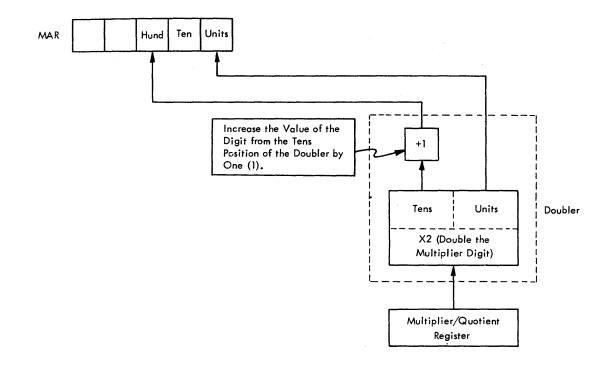

| True/Complement (T/C) Switch<br>Multiplier/Quotient Register                                            | 55<br>56 |

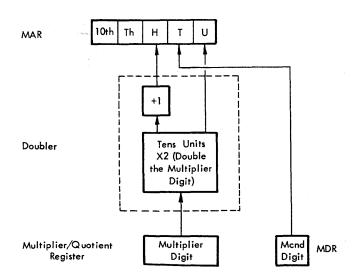

| Doubler                                                                                                 | 57       |

| Section 6—Console and CE Panel                                                                          |          |

| Customer Engineering Panel                                                                              |          |

| Section 7—Instruction Cycle<br>Objectives                                                               |          |

| Functions                                                                                               | • •      |

| Section 8—Execution Cycle<br>Objective                                                                  | 76<br>76 |

| Functions                                                                                               |          |

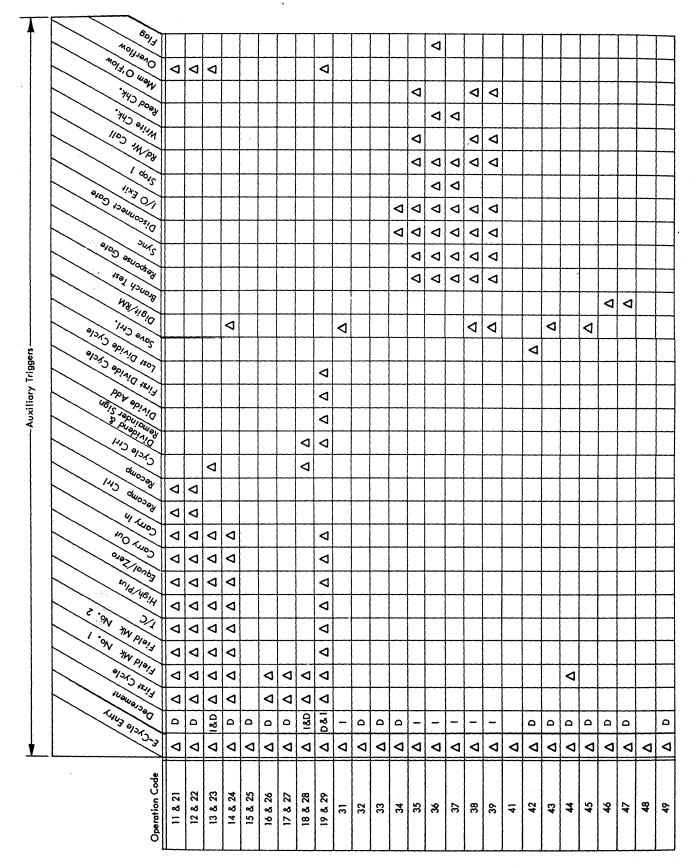

| Auxiliary Triggers                                                                                      | 76       |

| Block Memory Sense Amplifiers<br>Significance of P & Q Parts of Instructions                            | 80       |

| Section 9—Internal Transmission Operations                                                              | 82       |

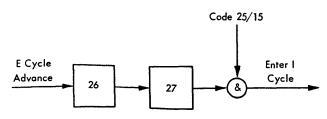

| Transmit Digit (Code 25 - тр)<br>Transmit Digit Immediate (Code 15 - трм)                               | 82       |

| Transmit Field (Code 26 - TF)<br>Transmit Field Immediate (Code 16 - TFM)                               | 82       |

| Transmit Record (Code 31 - Mnemonic TR)                                                                 | 84       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 10—Arithmetic Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 85                                                                                                                                                                                           |

| Add (Code 21 - A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85                                                                                                                                                                                           |

| Add Immediate (Code 11 - AM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                              |

| Subtract (Code 22 - s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                              |

| Subtract Immediate (Code 12 - SM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                              |

| Compare (Code 24 - c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                              |

| Compare Immediate (Code 14 - см)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                              |

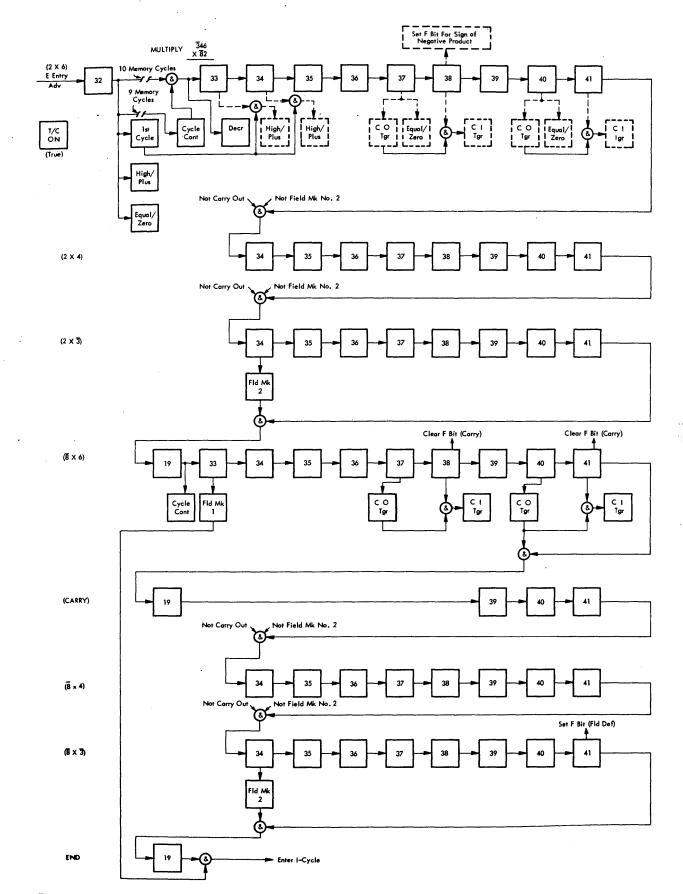

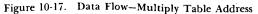

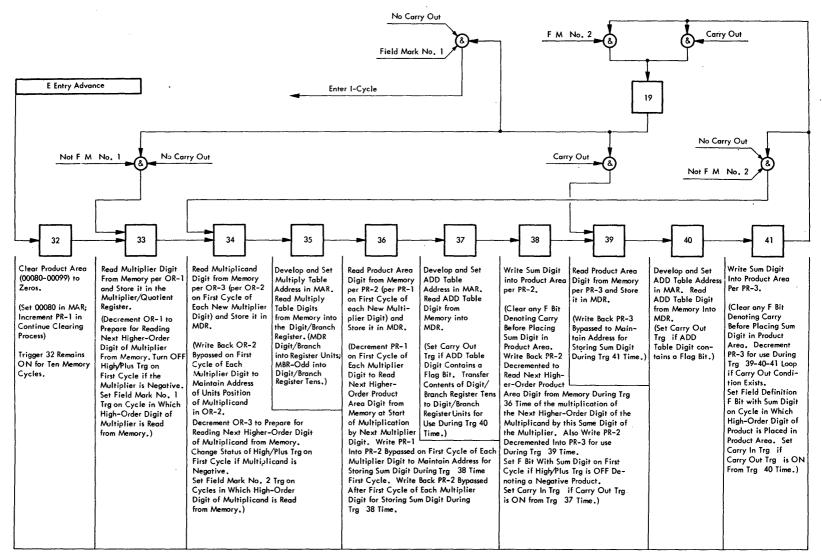

| Multiply (Code 23 - м)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                              |

| Multiply Immediate (Code 13 - мм)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                              |

| Load Dividend (Code 28 - LD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 109                                                                                                                                                                                          |

| Load Dividend Immediate (Code 18 - LDM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                              |

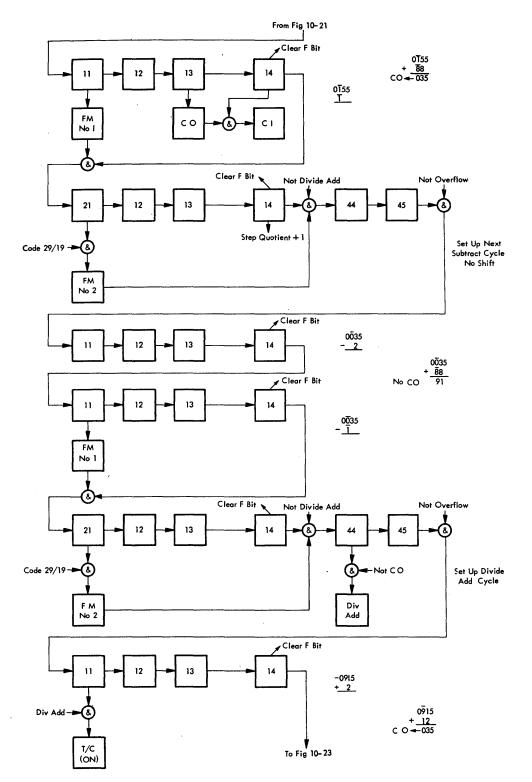

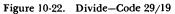

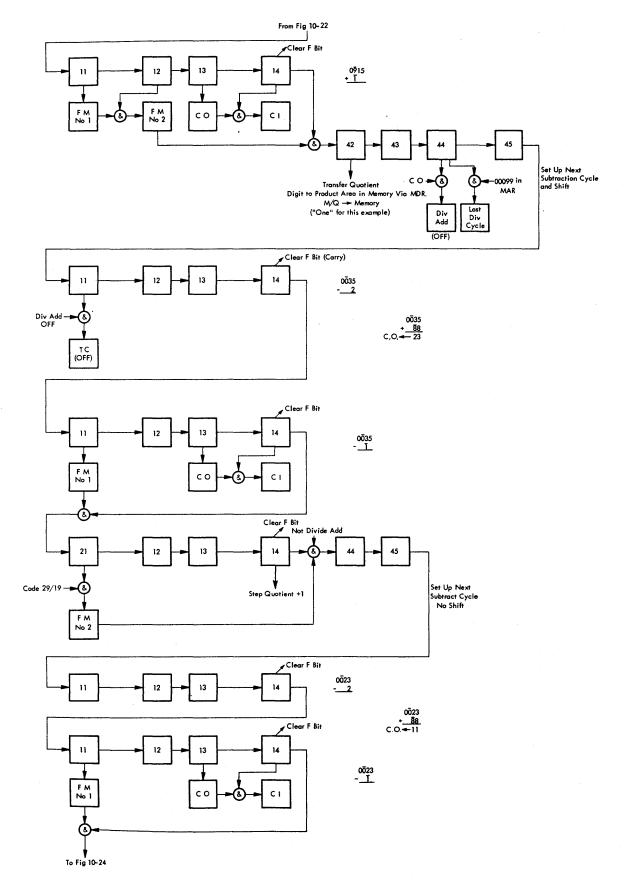

| Divide (Code 29 - D)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                              |

| Divide Immediate (Code 19 - DM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 120                                                                                                                                                                                          |

| Section 11—Branch Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 199                                                                                                                                                                                          |

| Branch (Code 49 - B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                              |

| Branch and Transmit (Code 27 - BT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 199                                                                                                                                                                                          |

| Branch and Transmit (Code 27 - 51)<br>Branch and Transmit Immediate (Code 17 - втм)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                              |

| Branch Back (Code 42 - BB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                              |

| Branch On Digit (Code 43 - BD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 194                                                                                                                                                                                          |

| Branch No Flag (Code 44 - BNF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105                                                                                                                                                                                          |

| Branch No Record Mark (Code 45 - BNR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100                                                                                                                                                                                          |

| Branch Indicator (Code 46 - BI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 107                                                                                                                                                                                          |

| Branch No Indicator (Code 47 - BNI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .150                                                                                                                                                                                         |

| Section 12—Miscellaneous Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 131                                                                                                                                                                                          |

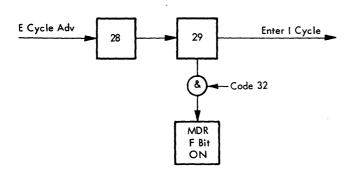

| Set Flag (Code 32 - sF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                              |

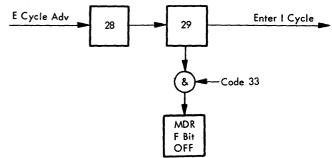

| Clear Flag (Code 33 - CF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

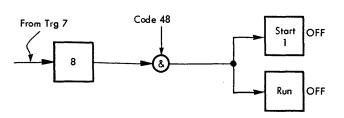

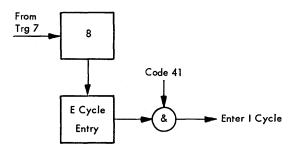

| Halt (Code 48 - н)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                              |

| No Operation (Code 41 - NOP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |

| Section 13—Input-Output Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 199                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 3 3                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |

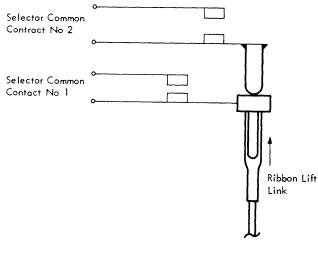

| Typewriter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .133                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .133                                                                                                                                                                                         |

| Typewriter<br>Івм 1621 Paper Tape Reader<br>Івм 1624 Paper Tape Punch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .133<br>.133<br>.143                                                                                                                                                                         |

| Туреwriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 133<br>. 133<br>. 143                                                                                                                                                                      |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations.<br>General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 133<br>. 133<br>. 143<br>. 143<br>. 151<br>. 151                                                                                                                                           |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 133<br>. 133<br>. 143<br>. 151<br>. 151<br>. 151                                                                                                                                           |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 133<br>. 133<br>. 143<br>. 151<br>. 151<br>. 151<br>. 152                                                                                                                                  |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 133<br>. 133<br>. 143<br>. 151<br>. 151<br>. 151<br>. 152<br>. 153                                                                                                                         |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .133<br>.133<br>.143<br>.151<br>.151<br>.151<br>.152<br>.153<br>.153                                                                                                                         |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 133<br>. 133<br>. 143<br>. 151<br>. 151<br>. 151<br>. 151<br>. 152<br>. 153<br>. 153<br>. 153                                                                                              |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)                                                                                                                                                                                                                                                                                                                                                                      | . 133<br>. 133<br>. 143<br>. 151<br>. 151<br>. 151<br>. 151<br>. 152<br>. 153<br>. 153<br>. 153<br>. 158                                                                                     |

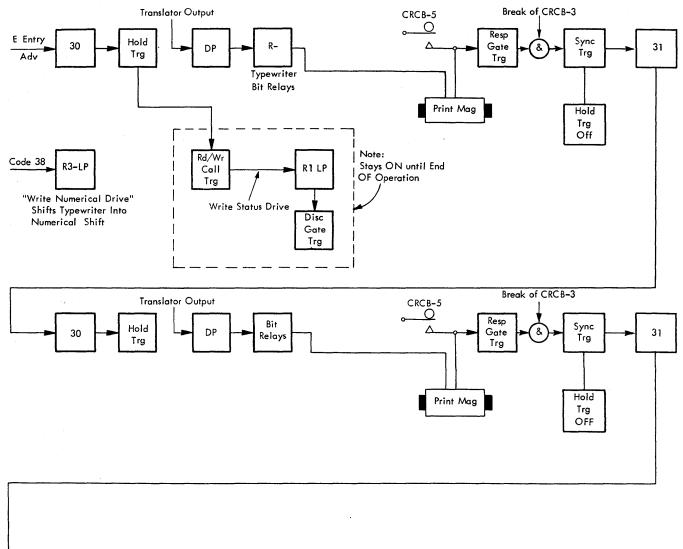

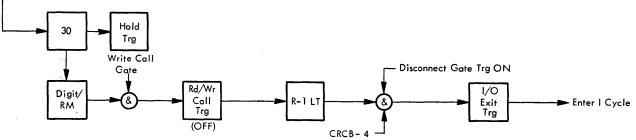

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)                                                                                                                                                                                                                                                                                                                                                                        | . 133<br>. 133<br>. 143<br>. 143<br>. 151<br>. 151<br>. 151<br>. 152<br>. 153<br>. 153<br>. 153<br>. 158<br>. 159                                                                            |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 35 - DN)                                                                                                                                                                                                                                                                                                                                     | . 133<br>. 133<br>. 143<br>. 151<br>. 151<br>. 151<br>. 151<br>. 153<br>. 153<br>. 153<br>. 158<br>. 159<br>. 166                                                                            |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 35 - DN)<br>Write Alphamerically (Code 39 - WA)                                                                                                                                                                                                                                                                                      | . 133<br>. 133<br>. 143<br>. 151<br>. 151<br>. 151<br>. 151<br>. 152<br>. 153<br>. 153<br>. 153<br>. 158<br>. 159<br>. 166<br>. 169                                                          |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 35 - DN)                                                                                                                                                                                                                                                                                                                                     | . 133<br>. 133<br>. 143<br>. 151<br>. 151<br>. 151<br>. 151<br>. 152<br>. 153<br>. 153<br>. 153<br>. 158<br>. 159<br>. 166<br>. 169                                                          |

| Typewriter<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 35 - DN)<br>Write Alphamerically (Code 39 - WA)<br>Control (Code 34 - K)                                                                                                                                                                                                                                                             | . 133<br>. 133<br>. 143<br>. 143<br>. 151<br>. 151<br>. 151<br>. 152<br>. 153<br>. 153<br>. 153<br>. 158<br>. 159<br>. 166<br>. 169<br>. 170                                                 |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 35 - DN)<br>Write Alphamerically (Code 39 - WA)<br>Control (Code 34 - K)<br>Section 15—Appendices                                                                                                                                                                                                     |                                                                                                                                                                                              |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 38 - WN)<br>Dump Numerically (Code 38 - WN)<br>Control (Code 34 - K)<br>Section 15—Appendices<br>A. Abbreviations and Terms                                                                                                                                                                           | .133<br>.133<br>.143<br>.143<br>.151<br>.151<br>.151<br>.152<br>.153<br>.153<br>.153<br>.158<br>.159<br>.166<br>.169<br>.170                                                                 |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter.<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 38 - WN)<br>Dump Numerically (Code 39 - WA)<br>Control (Code 34 - K)<br>Section 15—Appendices<br>A. Abbreviations and Terms<br>B. Character Code Chart                                                                                                           | .133<br>.133<br>.143<br>.151<br>.151<br>.151<br>.152<br>.153<br>.153<br>.153<br>.158<br>.159<br>.166<br>.169<br>.170                                                                         |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 36 - RN)<br>Write Numerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 38 - WN)<br>Dump Numerically (Code 38 - WN)<br>Control (Code 34 - K)<br>Section 15—Appendices<br>A. Abbreviations and Terms<br>B. Character Code Chart<br>C. Numbered Triggers                                                                                    | .133<br>.133<br>.143<br>.151<br>.151<br>.151<br>.152<br>.153<br>.153<br>.153<br>.153<br>.158<br>.169<br>.170<br>.173<br>.173                                                                 |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter.<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 36 - RN)<br>Write Numerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 38 - WN)<br>Dump Numerically (Code 38 - WN)<br>Control (Code 34 - K)<br>Section 15—Appendices<br>A. Abbreviations and Terms<br>B. Character Code Chart<br>C. Numbered Triggers<br>D. Named Triggers                                                              | .133<br>.133<br>.143<br>.151<br>.151<br>.151<br>.152<br>.153<br>.153<br>.153<br>.153<br>.159<br>.166<br>.169<br>.170<br>.173<br>.173<br>.174                                                 |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 39 - WA)<br>Control (Code 34 - K)<br>Section 15—Appendices<br>A. Abbreviations and Terms<br>B. Character Code Chart<br>C. Numbered Triggers<br>D. Named Triggers<br>E. Register Triggers     | .133<br>.133<br>.143<br>.143<br>.151<br>.151<br>.152<br>.153<br>.153<br>.153<br>.153<br>.153<br>.153<br>.159<br>.166<br>.169<br>.170<br>.173<br>.173<br>.174<br>.175                         |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 39 - WA)<br>Control (Code 34 - K)<br>Section 15—Appendices<br>A. Abbreviations and Terms<br>B. Character Code Chart<br>C. Numbered Triggers<br>D. Named Triggers<br>F. E-Timer Trigger Chart | .133<br>.133<br>.143<br>.143<br>.151<br>.151<br>.152<br>.153<br>.153<br>.153<br>.153<br>.153<br>.153<br>.159<br>.166<br>.169<br>.170<br>.173<br>.173<br>.174<br>.175<br>.176                 |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 39 - WA)<br>Control (Code 34 - K)<br>Section 15—Appendices<br>A. Abbreviations and Terms<br>B. Character Code Chart<br>C. Numbered Triggers<br>D. Named Triggers<br>E. Register Triggers     | .133<br>.133<br>.143<br>.143<br>.151<br>.151<br>.152<br>.153<br>.153<br>.153<br>.153<br>.153<br>.153<br>.159<br>.166<br>.169<br>.170<br>.173<br>.173<br>.174<br>.175<br>.176                 |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 38 - WN)<br>Dump Numerically (Code 37 - NA)<br>Write Alphamerically (Code 39 - WA)<br>Control (Code 34 - K)<br>Section 15—Appendices<br>A. Abbreviations and Terms<br>B. Character Code Chart<br>C. Numbered Triggers<br>D. Named Triggers<br>F. E-Timer Trigger Chart<br>G. Auxiliary Trigger Chart.                               | .133<br>.133<br>.143<br>.143<br>.151<br>.151<br>.152<br>.153<br>.153<br>.153<br>.153<br>.153<br>.153<br>.153<br>.159<br>.166<br>.169<br>.170<br>.173<br>.174<br>.175<br>.175<br>.175<br>.177 |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 39 - WA)<br>Control (Code 34 - K)<br>Section 15—Appendices<br>A. Abbreviations and Terms<br>B. Character Code Chart<br>C. Numbered Triggers<br>D. Named Triggers<br>F. E-Timer Trigger Chart | .133<br>.133<br>.143<br>.143<br>.151<br>.151<br>.152<br>.153<br>.153<br>.153<br>.153<br>.153<br>.153<br>.153<br>.159<br>.166<br>.169<br>.170<br>.173<br>.174<br>.175<br>.175<br>.175<br>.177 |

| Typewriter.<br>IBM 1621 Paper Tape Reader<br>IBM 1624 Paper Tape Punch<br>Section 14—Input-Output Operations<br>General<br>Typewriter<br>Paper Tape<br>IBM 1621 Paper Tape Reader<br>IBM 1621 Paper Tape Punch<br>Read Numerically (Code 36 - RN)<br>Read Alphamerically (Code 37 - RA)<br>Write Numerically (Code 38 - WN)<br>Dump Numerically (Code 38 - WN)<br>Dump Numerically (Code 37 - NA)<br>Write Alphamerically (Code 39 - WA)<br>Control (Code 34 - K)<br>Section 15—Appendices<br>A. Abbreviations and Terms<br>B. Character Code Chart<br>C. Numbered Triggers<br>D. Named Triggers<br>F. E-Timer Trigger Chart<br>G. Auxiliary Trigger Chart.                               | .133<br>.133<br>.143<br>.143<br>.151<br>.151<br>.152<br>.153<br>.153<br>.153<br>.153<br>.153<br>.153<br>.153<br>.159<br>.166<br>.169<br>.170<br>.173<br>.174<br>.175<br>.175<br>.176<br>.177 |

# IBM 1620 Data Processing System

8 cystem

### **Description of System**

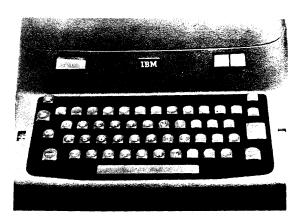

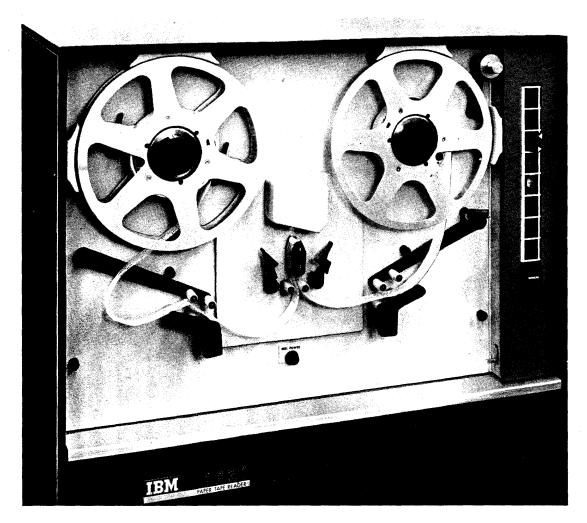

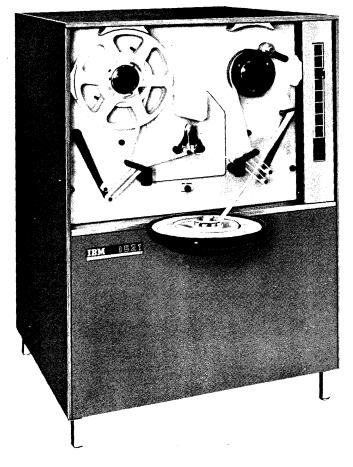

The IBM 1620 Data Processing System is a solid-state electronic computer system, designed specifically for technological applications. The system is composed of separate units: the 1620 Computer Unit, the 1621 Paper Tape Reader which provides space for the 1624 Paper Tape Punch, the 1622 Card Read Punch, and the 1623 Core Storage unit. The 1621, 1622, and the 1624 are input-output units available for various customer applications. The 1623 is available if additional core storage is desired. Information on the 1622 and 1623 units is included in the IBM Customer Engineering Manual of Instruction, 1620 Data Processing System, Additional Features (Form 227-5513). The computer unit contains the logic circuitry, the 20,000 position core storage unit, the console panel, and a typewriter.

Data and instructions entered into the system are placed in memory as decimal digits. Each of the 20,-000 positions of core storage (memory) can be addressed individually by a 5-digit address and can store one digit of information. Memory addresses extend from 00000 to 19999. The addressing system provides for the selection of any digit or group of digits within memory. The 1620 Computer processes numerical, alphabetic and special characters.

The computer is capable of performing more than thirty different operations. Each operation is specified by a 12-digit instruction which contains a two-digit operation code and two 5-digit addresses. Instructions comprising a program are normally stored in consecutive locations in memory and executed sequentially. However, the sequence of operations may be altered at any point in the program by conditional branch instructions. Conditional branch instructions make logical decisions by performing tests on indicators or switches set by the computer or the operator.

Arithmetic operations are accomplished by a table method. Three hundred twenty (320) positions of memory are assigned for use in arithmetic operations. Twenty (20) positions, 00080 through 00099, are used to store products or quotients. Two hundred (200) positions, 00100 through 00299, are assigned for the storage of a Multiply Table. The Multiply Table contains all possible two-digit products. One hundred (100) positions, 00300 through 00399, are assigned for storage of an Add Table used in all arithmetic operations. The Add Table contains all possible two-digit sums, with carries indicated. The memory positions containing the table data are addressable.

The 1620 is a variable field length computer. The shortest admissible field is two digits; the longest can be any number of digits within the capacity of memory. Accuracy of data is ensured by the parity check which is made when the data enters, exits, or is manipulated inside the system.

The console of the 1620 consists of control keys, switches, an indicator panel, and a typewriter. The control keys and switches are used to control operation of the system. The console panel provides a visual indication of the contents of various registers and the status of control circuitry within the computer. The typewriter keyboard is used for manual entry of data and instructions into memory.

Information is entered into the system by the typewriter, 1621 Paper Tape Reader, and the 1622 Card Read Punch. The 1621 reads an eight-channel tape at a rate of 150 characters per second. The 1622 reads 80column IBM cards at a rate of 250 cards per minute. Output data is recorded by the typewriter, 1622 Card Read Punch, and the 1624 Paper Tape Punch. The typewriter prints at the rate of 10 characters per second. The 1622 punches data into 80-column IBM cards at the rate of 125 cards per minute. The 1624 punches data into eight-channel paper tape at the rate of 15 characters per second.

When the computer is reading from or writing on an input-output device and is in the numerical mode, each character received from or sent to the inputoutput device is represented in memory as a single digit and occupies one memory position. In the numerical mode, data must consist of numerical characters only. When the computer is reading from or writing on an input-output device and is in the alphameric mode, each character received from or sent to the input-output device is represented in memory as two digits occupying two adjacent memory positions. In the alphameric mode, data may consist of numerical, alphabetic, and special characters. The digits for numerical characters, in the alphameric mode, consist of an arbitrarily assigned digit (zone digit) and a second digit (numerical digit) representing the true decimal value of the numerical character. Alphabetic and special characters are represented by two arbitrarily assigned digits.

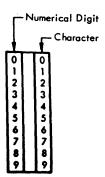

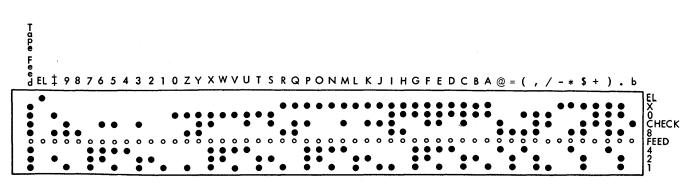

Figures 1-1 and 1-2 illustrate all characters and their assigned digital values for both numerical and alphameric modes.

#### Machine Language

#### **Character Code**

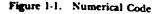

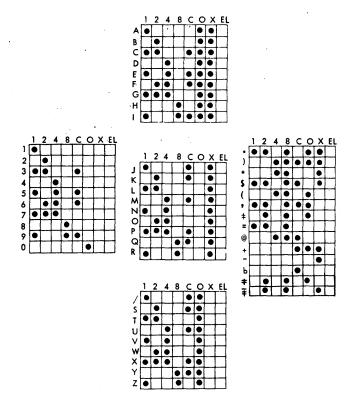

All data stored, transferred, and processed within the computer is represented as decimal digits in binary coded decimal (BCD) form. A digit is represented by a particular combination of bits. The bit positions of each digit consist of four numerical bits (8, 4, 2, and 1), one flag (F) bit, and one check (C) bit (see Figure 1-3). The value of a significant digit is the sum represented by the bits present in the 8, 4, 2, and 1 numerical bit positions. A zero is represented by a C bit alone. Only bit combinations whose sum is nine or less are used. Considering only the numerical bit positions, the digit 6 is represented by a 4 bit and a 2 bit; the digit 7 by a 4 bit, a 2 bit, and a 1 bit; and the digit 8 by an 8 bit alone (see Figure 1-4).

The flag (F) bit is used in three ways. The presence or absence of the flag bit in the units position of a numerical field determines the sign of the field. Absence of the flag bit is interpreted as a field signed plus. The presence of the flag bit is interpreted as a field signed minus. The flag bit is also used as a field mark defining the high-order position of a numerical field. A flag bit with a digit of the add table indicates a carry in arithmetic operations.

The C bit is used for parity checking purposes. Each digit within the computer must consist of an odd total number of bits, or a parity error will be indicated. The C bit will be present in a digit when the number of bits present in the numerical bit positions and the F bit position consists of an even number of bits.

A special combination consisting of the C bit, 8 bit, and 2 bit is used as a record mark.

# Instruction Format

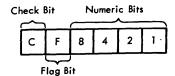

The IBM 1620 uses a 12-digit instruction divided into three parts; a two-digit operation code, a five-digit "P part", and a five digit "Q part" (see Figure 1-5).

The operation codes consist of two digits (00 through 99) which specify the operation to be performed. Figure 1-6 is a chart of operation codes and their associated mnemonics.

|          | e Dig<br>meri         | git<br>cal Digit<br>Character |

|----------|-----------------------|-------------------------------|

| 11       | <br>                  | · ·                           |

| 00       | b                     |                               |

| 03       | •                     |                               |

| 04       | )                     |                               |

| 10       | )<br>+                |                               |

| 13       | 5                     |                               |

| 14       | *                     |                               |

| 20       | _                     |                               |

| 21       | 1                     |                               |

| 23       | /                     |                               |

| 23       |                       |                               |

| 24<br>33 | \$ * - / , ( =        |                               |

| 33<br>34 | -                     |                               |

|          | @                     |                               |

| 41       | A                     |                               |

| 42       | Β.                    |                               |

| 43       | C<br>D                |                               |

| 44       | D                     |                               |

| 45       | E                     |                               |

| 46       | F<br>G                |                               |

| 47       | G                     |                               |

| 48       | н                     |                               |

| 49       | Ļ                     |                               |

| 50       | ō                     |                               |

| 51       | J                     |                               |

| 52       | ĸ                     |                               |

| 53       | L                     |                               |

| 54       | м                     |                               |

| 55       | N                     |                               |

| 56       | 0                     |                               |

| 57       | Р                     |                               |

| 58       | Q                     |                               |

| 59       | R                     |                               |

| 62       | S                     |                               |

| 63       | T                     |                               |

| 64       | S<br>T<br>U<br>V      |                               |

| 65       | V                     |                               |

| 66       | w                     |                               |

| 67       | х                     |                               |

| 68       | Y                     |                               |

| 69       | z                     |                               |

| 70       | 0<br>1                |                               |

| 71       |                       |                               |

| 72       | 2<br>3                |                               |

| 73       | 3                     |                               |

| 74       | 4                     |                               |

| 75       | 5                     |                               |

| 76       | 6                     |                               |

| 77       | 4<br>5<br>6<br>7<br>8 |                               |

| 78       | 8                     |                               |

| 79       | 9                     |                               |

|          |                       |                               |

Figure 1-2. Alphameric and Special Character Codes

Figure 1-3. Bit Positions

The functions of the P and Q parts of an instruction are dependent upon the particular operation to be performed. The P part of an instruction can represent the address in memory of a digit, a field, a record, or another instruction. The Q part can represent the address in memory of a digit, field, or record; a data field itself; the "address" of an input-output device; the control function to be performed by an inputoutput device together with the "address" of the device; or the code for a switch or indicator. The specific use of the P and Q parts will be discussed with each operation.

#### **Data Format**

Data is stored in memory to form fields or records that can be of any length within the capacity of memory. Data can be classified as digits, fields or records depending upon how they are addressed and the limiting factor of the data.

A digit occupies one memory position and is addressed individually.

Fields in memory consist of a number of consecutive digits and are composed of data related to arithmetic operations and internal field transmission. A field is addressed by its rightmost (low-order) position which occupies the highest numbered memory position of the field. Fields are processed from right to left into suc-

|   | С | F | 8 | 4 | 2 | 1 |

|---|---|---|---|---|---|---|

| 0 | х |   |   |   |   |   |

| 1 |   |   |   |   |   | х |

| 2 |   |   |   |   | х |   |

| 3 | х |   |   |   | х | х |

| 4 |   |   |   | х |   |   |

| 5 | х |   |   | Х |   | х |

| 6 | х |   |   | х | х |   |

| 7 |   |   |   | х | х | х |

| 8 |   |   | х |   |   |   |

| 9 | х |   | х |   |   | х |

Figure 1-4. Bit Configuration-Decimal Digits 0-9

| 00  | 0 <sub>1</sub> | P <sub>2</sub> | P3 | P4    | P <sub>5</sub> | P <sub>6</sub> | Q7 | Q <sub>8</sub> | Q9    | Q <sub>10</sub> | Q <sub>11</sub> |

|-----|----------------|----------------|----|-------|----------------|----------------|----|----------------|-------|-----------------|-----------------|

| - C | )P — ►<br>xde  |                | P  | Addre | 55             |                |    | (              | Q Add | ress            |                 |

Figure 1-5. Instruction Format

cessively lower memory positions until a digit with a flag bit is sensed. The shortest admissible field consists of two digits, the addressed digit and the adjacent digit containing the field definition flag bit. Numerical fields are signed minus by a flag bit present in the units position. The absence of a flag bit in the units position is interpreted as a field signed plus.

Record in memory consists of a field or fields of data related to input-output operations and internal record transmission. A record in memory is addressed at the leftmost (high-order) position, which occupies the lowest numbered memory position of the record. Records are processed serially from left to right into successively higher memory positions. Output and internal record transmission operations are terminated whenever a record mark is sensed. For memory to receive a record, data is entered starting at the addressed position and continuing from left to right into successively higher memory locations until terminated by an end-of-record signal from the input unit.

#### Stored Program Concept

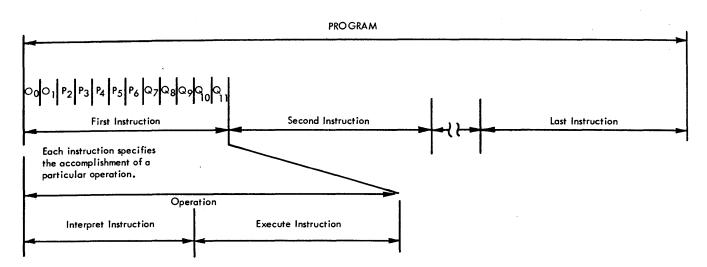

To solve a problem or to process data, a programmer selects from the different operations which the system is capable of performing, those which are required to accomplish the desired results. The series of instructions which designate the operations to be performed is called a program. Because the instructions comprising a program are written into memory from an input device and read from memory for interpretation and execution, the 1620 is called a stored program computer.

For interpretation by the computer, an instruction must be read from memory to registers, starting with the high-order digit and continuing through successively higher memory locations until all twelve digits have been read.

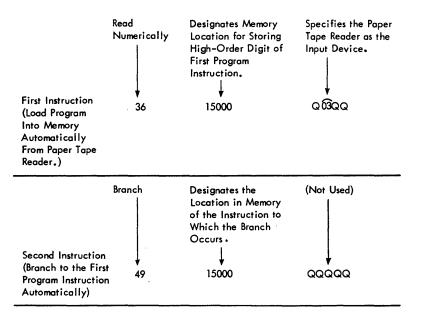

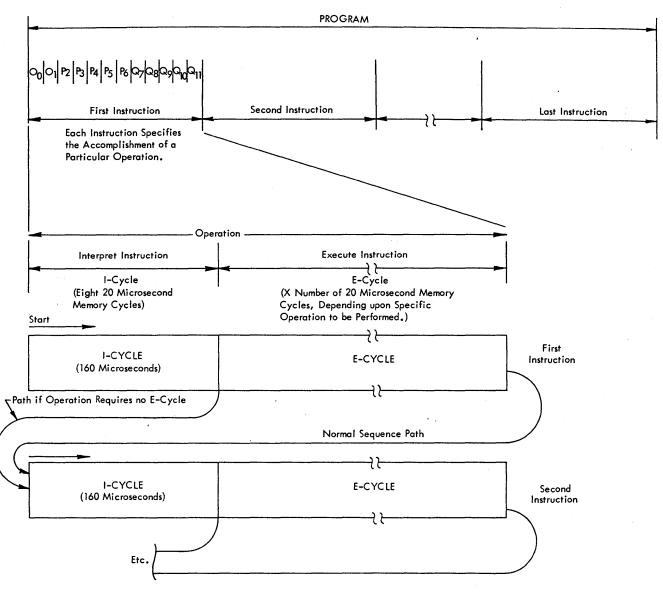

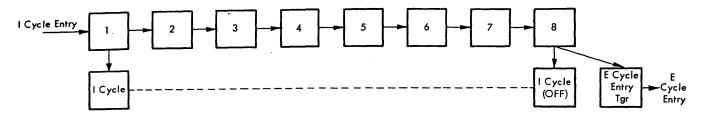

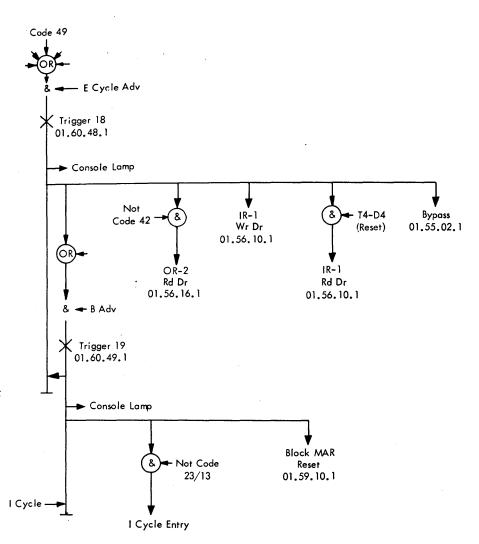

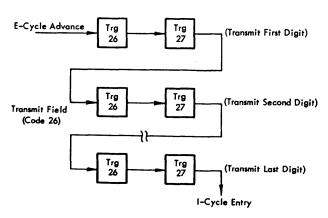

Instructions within a program are normally interpreted and executed sequentially; that is, execution of the first instruction is followed by interpretation and execution of the second instruction, etc. (see Figure 1-7). However, this sequence can be altered by the use of conditional branch instructions that direct the computer to an instruction located at other than the next sequential position.

| Arithmetic Instructions : | MNEMONIC | COD |

|---------------------------|----------|-----|

| Add                       | A        | 21  |

| Add Immediate             | AM       |     |

| Subtract                  | S        | 22  |

| Subtract Immediate        | SM       | 12  |

| Compare                   |          |     |

| Compare Immediate         |          |     |

| Multiply                  |          | 23  |

| Multiply Immediate        | MM       | 13  |

| Load Dividend             |          |     |

| Load Dividend Immediate   | LDM      | 18  |

| Divide                    | D        |     |

| Divide Immediate          | DM       | 19  |

Internal Data Transmission Instructions:

| Transmit Digit             | TD  | 25 |

|----------------------------|-----|----|

| Transmit Digit Immediate   |     |    |

| Transmit Field             | TF  | 26 |

| Transmit Field Immediate   | TFM |    |

| Transmit Record            | TR  | 31 |

| * Transfer Numerical Strip | TNS | 72 |

| * Transfer Numerical Fill  | TNF | 73 |

#### Branch Instructions:

| Branch                        | B    | 49 |

|-------------------------------|------|----|

| Branch No Flag                | BNF  | 44 |

| Branch No Record Mark         |      |    |

| Branch On Digit               | BD   | 43 |

| Branch Indicator              |      |    |

| Branch No Indicator           | BNI  | 47 |

| Branch and Transmit           | ВТ   | 27 |

| Branch and Transmit Immediate | BT.M | 17 |

| Branch Back                   | BB   | 42 |

#### Input-Output Instructions:

| Read Numerically     | RN | 36 |

|----------------------|----|----|

| Write Numerically    | WN | 38 |

| Dump Numerically     | DN | 35 |

| Read Alphamerically  |    | 37 |

| Write Alphamerically |    |    |

| Control              |    | 34 |

•

#### Miscellaneous Instructions:

8

| Set Flag             | SF  | 32 |

|----------------------|-----|----|

| Clear Flag           | C F | 33 |

| * Move Flag          |     | 71 |

| Halt                 | H   | 48 |

| No Operation         | NOP | 41 |

| * Additional Feature |     |    |

Figure 1-6. Operation Codes and Mnemonics

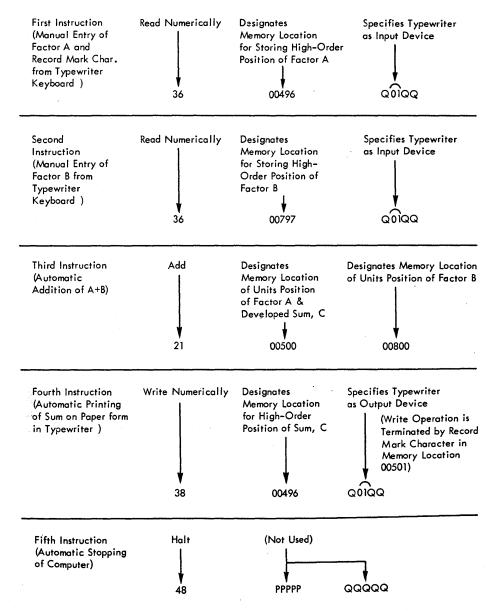

Figure 1-7. Program

Additional instructions and/or data may be inserted into memory from an input device during the solution of a problem.

The only distinction between instructions and data, in memory, is the manner in which they are interpreted by the computer. If for any reason data was placed in memory locations assigned to instructions, the data would be acted upon as instructions. Conversely, the operation code or either address part of an instruction may be modified by treating the instruction parts as data. Flag bits may be stored with the digits of an instruction to permit operation on the instruction as data. The flag bits are ignored during interpretation of the instruction except when Indirect Addressing, an additional feature, is installed in the 1620. The functions of Indirect Addressing are given in the IBM Customer Engineering Manual of Instruction, 1620 Data Processing System, Additional Features (Form 227-5513).

. .

#### Introduction

The IBM 1620 Computer normally processes data serially by digit, parallel by bit. However, the two digits which are read from memory for each address, are processed simultaneously under certain conditions.

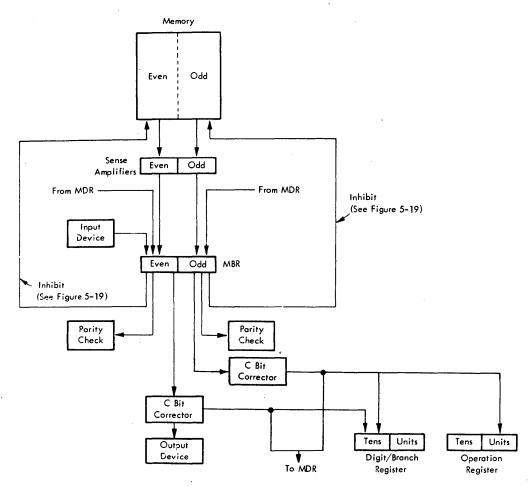

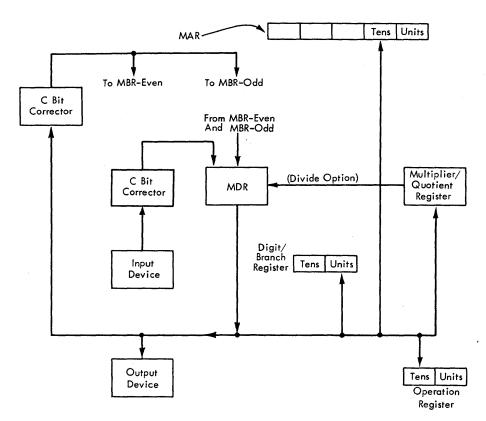

Data, as such, is confined to memory, memory buffer register (MBR), memory data register (MDR), and input-output areas. Digits of data which are presented to other registers by MBR and/or MDR are used to develop memory addresses or to control program execution.

Each instruction of a program is interpreted and executed by a series of machine cycles. A machine cycle consists essentially of: addressing memory, reading out of a memory location, and writing into a memory location. Digits read from memory, that are to be used for addressing or control purposes, are set into registers from MBR and/or MDR within the cycle. Digits are presented to an output device or received from an input device within the machine cycle.

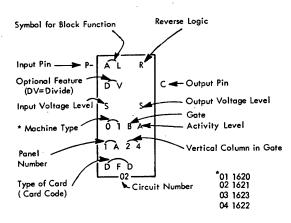

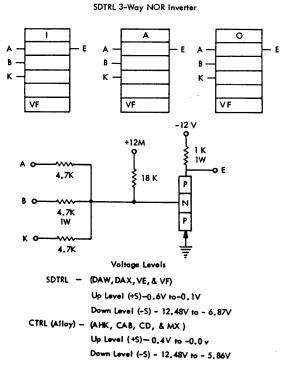

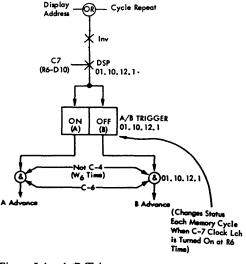

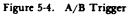

NOTE: The original design concepts of this system made extensive use of triggers. Therefore the functional nomenclature chosen included the term trigger (trigger 21, first cycle trigger, I-cycle trigger). Subsequent Engineering changes have replaced all triggers with latches except in four cases. The True/Complement, High/ Plus, Clock drive, and A/B triggers are still binary connected triggers. The system diagrams still maintain the original "trigger" designation for many of the latches and line names. For this reason the terms trigger and latch are generally used synonymously throughout this manual. These terms are not intended to designate the actual type of component used. The functions of sms card types used in the 1620 system are given in Section 4 of this manual.

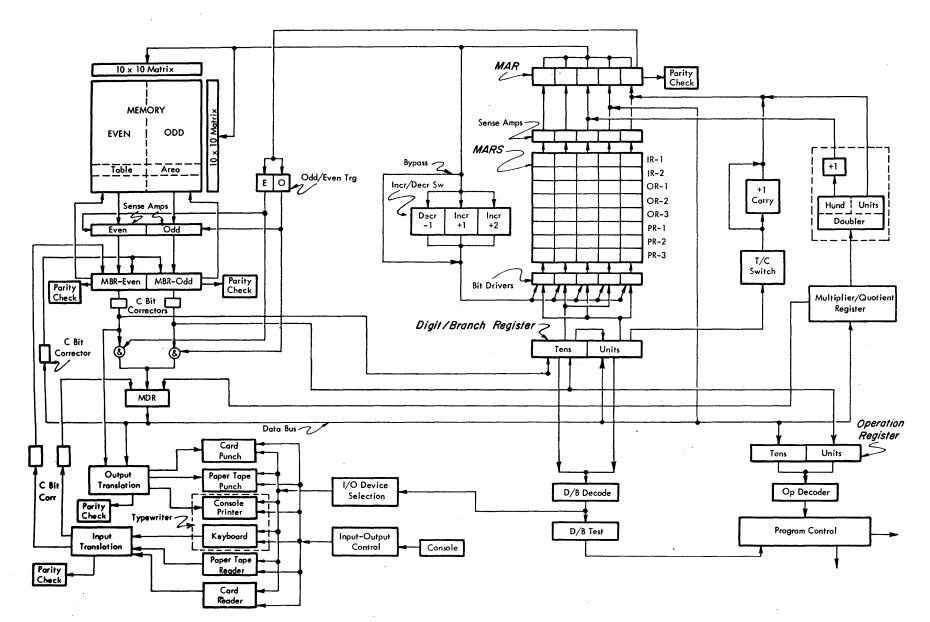

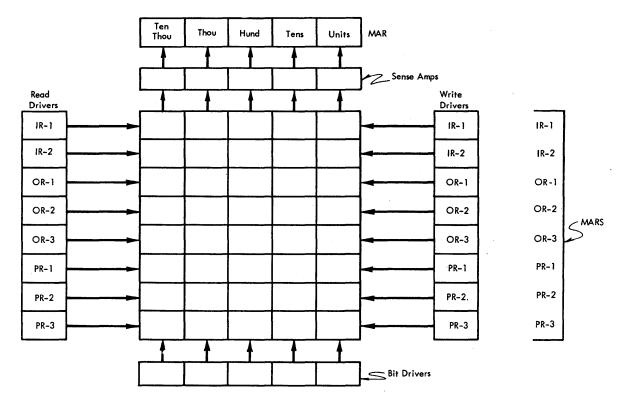

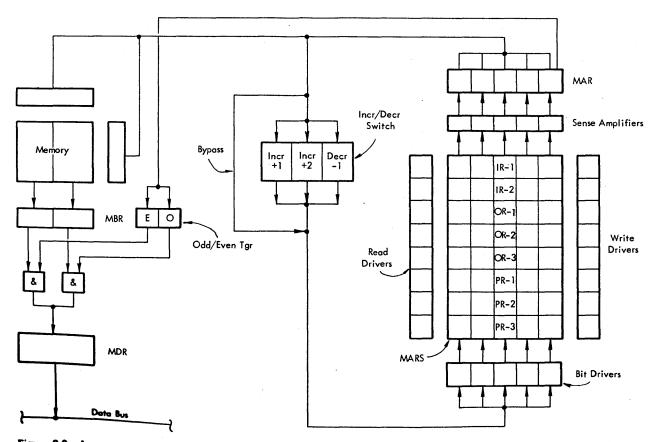

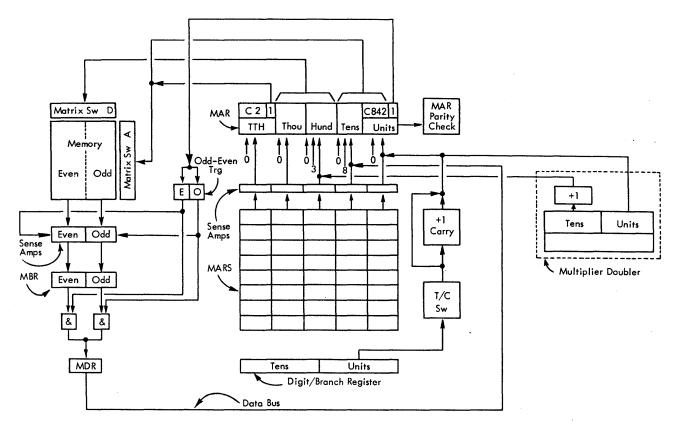

Refer to Figure 2-1 for the following discussion of data flow.

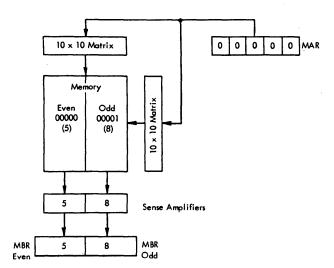

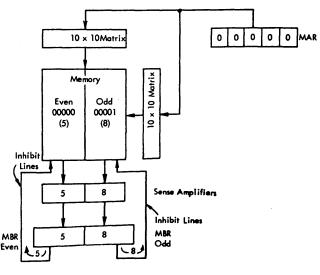

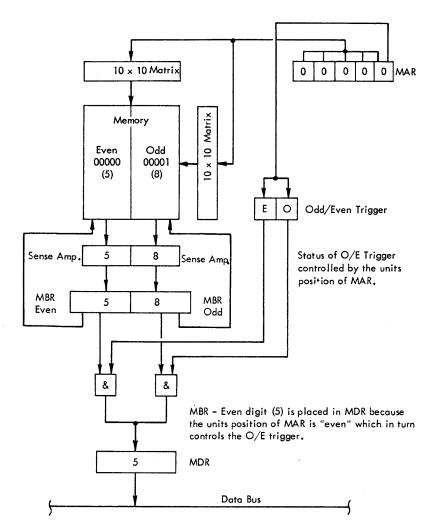

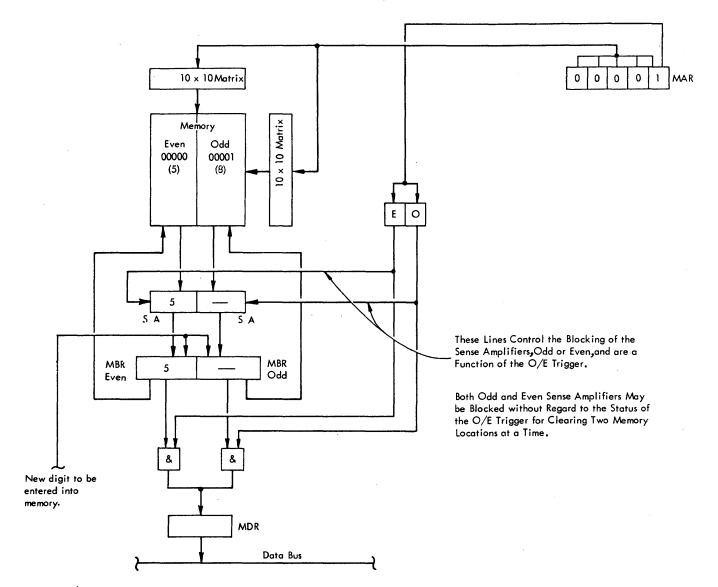

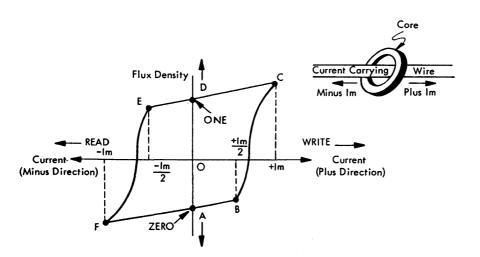

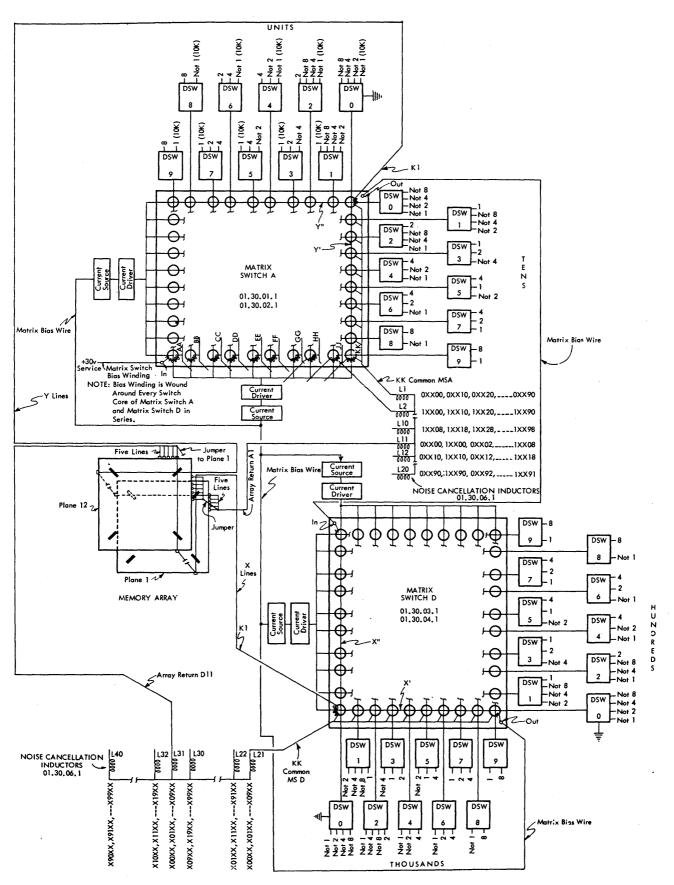

#### Memory

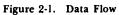

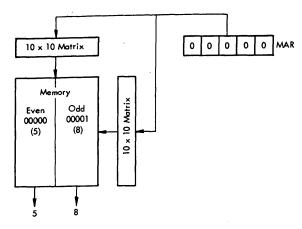

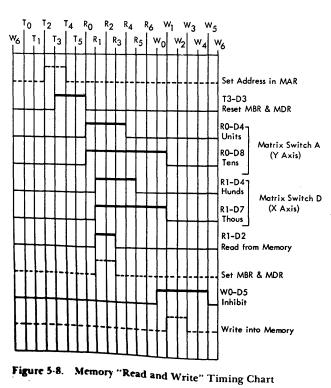

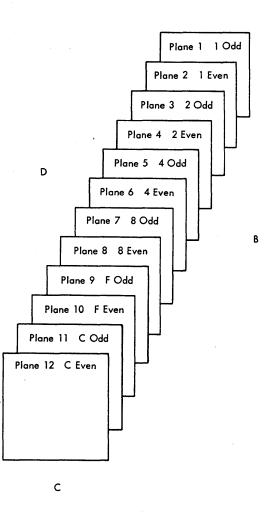

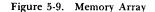

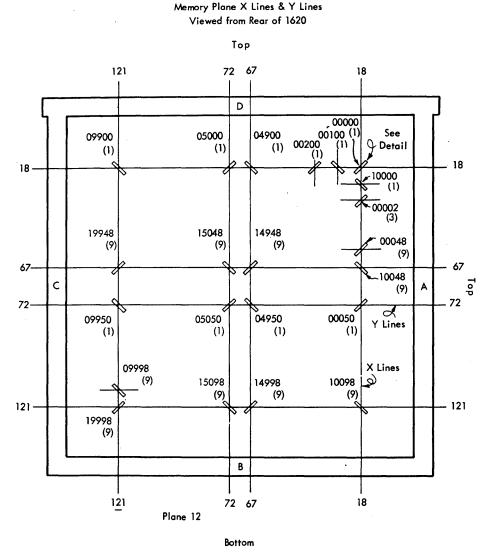

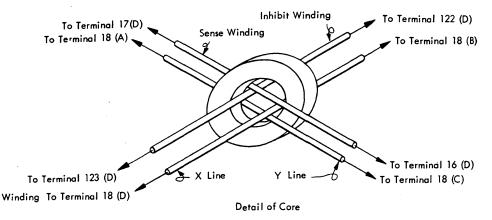

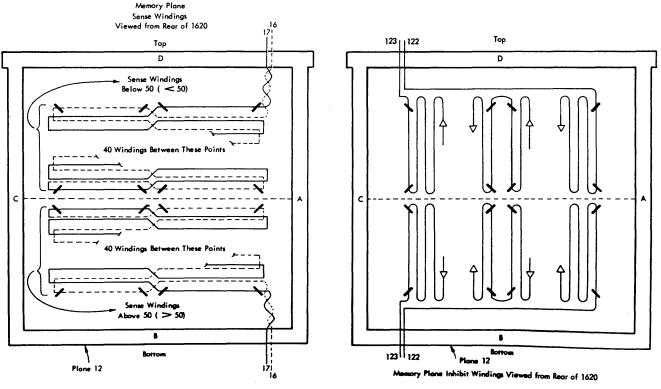

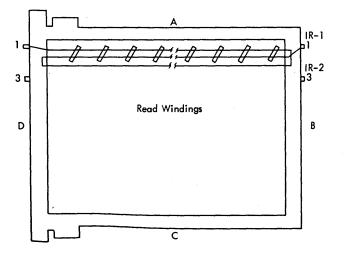

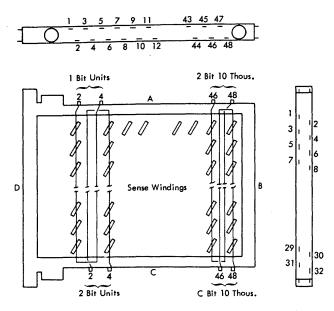

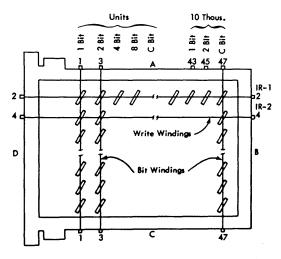

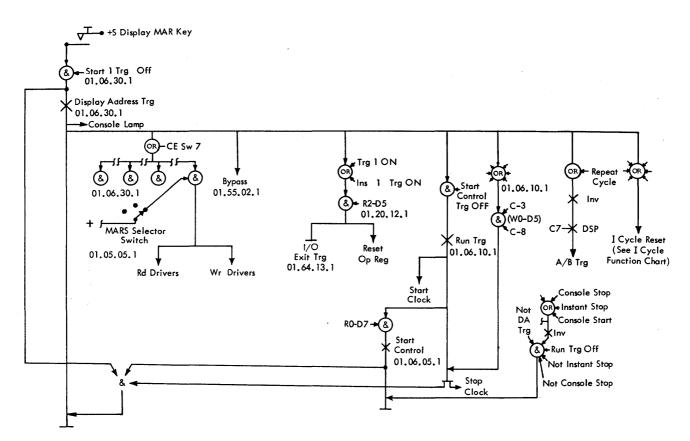

Memory is addressed by means of two matrix switches which select one "column" of 12 cores (one core in the same position in each plane). Since each digit position in memory consists of six bits (C, F, 8, 4, 2, 1), it follows that in selecting one column of 12 cores, two digits will be read out each time memory is addressed. Addressing is in the form of five digits (00000 to 19999) and is from a single register, memory address register (MAR). Memory is divided into two sections, even and odd, by the wiring scheme. If memory is addressed per 00000, the digit at 00000 and at 00001 will be read out (see Figure 2-2). If the address is 00001 the digit at 00001 and the digit at 00000 will be read out (see Figure 2-3).

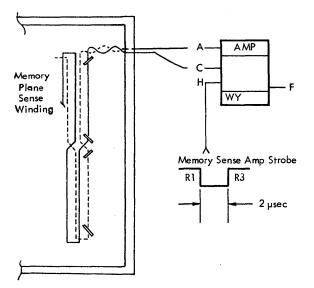

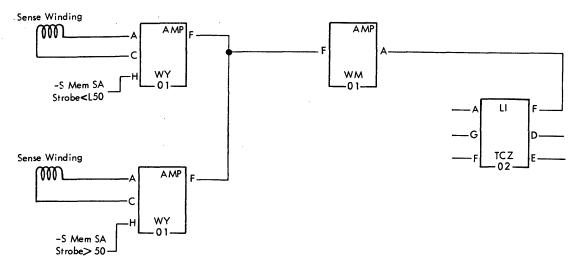

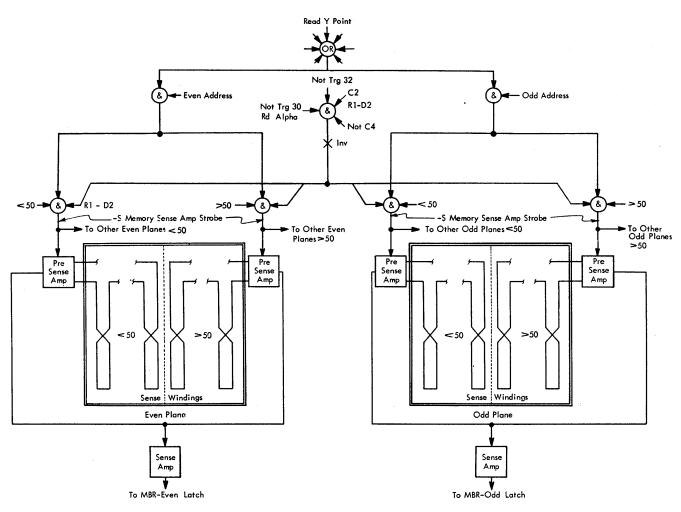

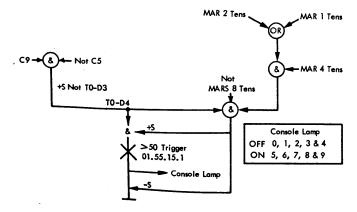

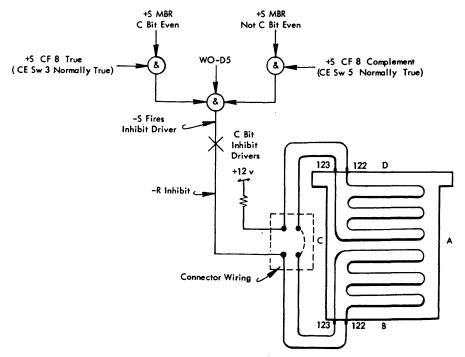

# Sense Amplifiers and Memory Buffer Register (MBR)