# TMS380 Adapter Chipset User's Guide Supplement

## Local Area Network Products

## TMS380 Adapter Chipset User's Guide Supplement

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes in the devices or the device specifications identified in this publication without notice. TI advises its customers to obtain the latest version of device specifications to verify, before placing orders, that the information being relied upon by the customer is current.

TI warrants that the software content of the TMS38020 or TMS38021 device is a faithful reproduction of the software developed by TI and IBM for this chipset.<sup>†</sup> This is the only warranty with regard to the software and all other warranties, whether express or implied and including any implied warranties of merchantability and fitness for a particular purpose, are disclaimed. TI reserves the right to offer the TMS38020 or TMS38021 or a derivative product with different software contained in the chip. TI has no responsibility to upgrade or replace products previously sold if different versions of the product and software are offered. TI shall not be liable for incidental or consequential damages arising from the software or its use or modification.

In the absence of written agreement to the contrary, TI assumes no liability for TI applications assistance, customer's product design, or infringement of patents or copyrights of third parties by or arising from use of semiconductor devices described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

<sup>†</sup>Copyright © 1986 by Texas Instruments Incorporated and International Business Machines, all rights reserved.

iAPX 86 is a registered trademark of the Intel Corporation.

IBM, IBM PC, PC/XT, PC AT, and VM are registered trademarks of International Business Machines Corporation.

UNIX is a trademark of AT&T Bell Laboratories.

MS-DOS is a trademark of Microsoft Corporation.

Copyright © 1987, Texas Instruments Incorporated

## Contents

| 1              | Introduction                             | -1  |

|----------------|------------------------------------------|-----|

| 2              | DLC System Software Interface            | -1  |

| 2.1<br>2.1.1   | Logical Link Control                     |     |

| 2.1.2          | Type 2 — Connection - Oriented LLC       |     |

| 2.1.3          | Type 3 — Connectionless-Acknowledged LLC |     |

| 2.1.4          | LLC Frames                               |     |

| 2.1.5          | LLC Protocol States                      |     |

| 2.1.6          | LLC Parameters                           |     |

| 2.2            | System Memory Requirements               |     |

| 2.2.1          | System Command Block                     |     |

| 2.2.2          | System Status Block                      |     |

| 2.2.3          | Frame Buffers                            |     |

| 2.2.4          | Command Parameter Block                  | -15 |

| 2.2.5          | Transmit Parameter List                  | -15 |

| 2.2.6          | Receive Parameter List                   | -15 |

| 2.2.7          | Product ID Block                         |     |

| 2.3            | Adapter Memory                           |     |

| 2.4            | Register Descriptions                    |     |

| 2.4.1          | SIF Interrupt Register                   |     |

| 2.4.2          | SIF Address Register                     |     |

| 2.4.3          | Data Register                            |     |

| 2.4.4          | Data Register with Auto-Increment2       |     |

| 2.5            | Adapter to System Interrupts             |     |

| 2.5.1          | Interrupt Handling                       |     |

| 2.5.2          | RING.STATUS                              |     |

| 2.5.3          | COMMAND.REJECT                           |     |

| 2.5.4          | ADAPTER.CHECK                            |     |

| 2.5.5          | SCB.CLEAR                                |     |

| 2.5.6          | RECEIVE.STATUS                           |     |

| 2.5.7<br>2.5.8 | COMMAND.STATUS                           |     |

| 2.5.8          | RECEIVE.PENDING                          |     |

| 2.5.9          |                                          |     |

| 2.5.10         | TIMER                                    |     |

| 2.5.11         | Interface Control Block                  |     |

| 2.7            | Adapter Initialization                   |     |

| 2.7.1          | Bring-Up Diagnostics                     |     |

| 2.7.2          | Adapter Initialization                   |     |

| 2.8            | Adapter Command Set                      |     |

| 2.9            | OPEN Command                             |     |

| 2.9.1          | Command Initiation                       |     |

| 2.9.2          | Command Completion                       |     |

| 2.10           | CLOSE Command                            |     |

| 2.10.1         | Command Initiation                       |     |

| 2.10.2         |                                          |     |

|                |                                          |     |

| 2.11   | SET.GROUP.ADDRESS Command       | . 2-47 |

|--------|---------------------------------|--------|

| 2.11.1 | Command Initiation              | . 2-47 |

| 2.11.2 | Command Completion              |        |

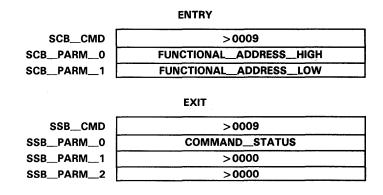

| 2.12   | SET.FUNCTIONAL.ADDRESS Command  | . 2-48 |

| 2.12.1 | Command Initiation              |        |

| 2.12.2 | Command Completion              |        |

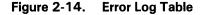

| 2.13   | READ.ERROR.LOG Command          |        |

| 2.13.1 | Command Initiation              |        |

| 2.13.2 | Command Completion              |        |

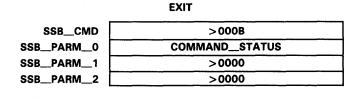

| 2.14   | READ.ADAPTER Command            |        |

| 2.14.1 | Command Initiation              |        |

| 2.14.2 | Command Completion              |        |

| 2.15   | MODIFY.OPEN.PARAMETERS Command  |        |

| 2.15.1 | Command Initiation              |        |

| 2.15.2 | Command Completion              |        |

| 2.16   | RESTORE.OPEN.PARAMETERS Command |        |

| 2.16.1 | Command Initiation              |        |

| 2.16.2 | Command Completion              |        |

|        | LLC.RESET Command               |        |

| 2.17.1 | Command Initiation              |        |

| 2.17.2 | Command Completion              | . 2-56 |

| 2.18   | OPEN.SAP Command                |        |

| 2.18.1 | Command Initiation              |        |

| 2.18.2 | Command Completion              |        |

| 2.19   | CLOSE.SAP Command               |        |

| 2.19.1 | Command Initiation              | . 2-61 |

| 2.19.2 | Command Completion              |        |

| 2.20   | OPEN.STATION Command            |        |

| 2.20.1 | Command Initiation              | . 2-62 |

| 2.20.2 | Command Completion              | . 2-64 |

| 2.21   | CLOSE.STATION Command           | . 2-65 |

| 2.21.1 | Command Initiation              | . 2-65 |

| 2.21.2 | Command Completion              |        |

| 2.22   | CONNECT.STATION Command         |        |

| 2.22.1 | Command Initiation              |        |

| 2.22.2 | Command Completion              |        |

| 2.23   | MODIFY.LLC.PARMS Command        |        |

| 2.23.1 | Command Initiation              | . 2-68 |

| 2.23.2 | Command Completion              | . 2-70 |

| 2.24   | FLOW.CONTROL Command            | . 2-71 |

| 2.24.1 | Command Initiation              | . 2-71 |

| 2.24.2 | Command Completion              | . 2-71 |

| 2.25   | LLC.STATISTICS Command          | . 2-72 |

| 2.25.1 | Command Initiation              | . 2-72 |

| 2.25.2 | Command Completion              | . 2-74 |

| 2.26   | DIR.INTERRUPT Command           |        |

| 2.26.1 | Command Initiation              |        |

| 2.26.2 | Command Completion              |        |

| 2.27   | CONFIG.BRIDGE.PARMS Command     | . 2-76 |

| 2.27.1 | Command Initiation              |        |

| 2.27.2 | Command Completion              | . 2-76 |

|        |                                 |        |

| 2.28     | LLC.REALLOCATE Command                  | 2-77   |

|----------|-----------------------------------------|--------|

| 2.28.1   | Command Initiation                      |        |

| 2.28.2   |                                         |        |

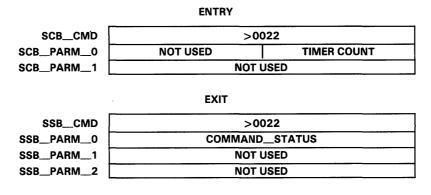

| 2.29     | TIMER.SET Command                       |        |

| 2.29.1   | Command Initiation                      |        |

| 2.29.1   |                                         |        |

| 2.29.2   | · · · · · · · · · · · · · · · · · · ·   |        |

|          | Transmit Operation                      |        |

| 2.31     | TRANSMIT Command                        |        |

| 2.31.1   | Command Initiation                      |        |

| 2.31.2   |                                         |        |

| 2.31.3   |                                         |        |

| 2.32     | TRANSMIT.HALT Command                   |        |

| 2.32.1   | Command Initiation                      |        |

| 2.32.2   | Command Completion                      | . 2-89 |

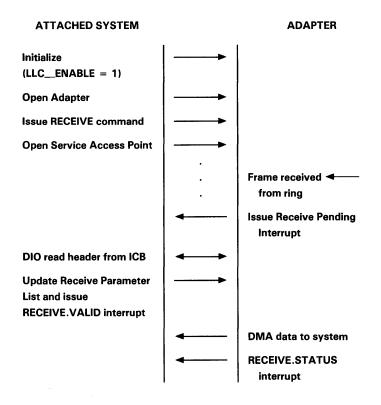

| 2.33     | RECEIVE Command                         | . 2-90 |

| 2.33.1   | Command Initiation                      | . 2-90 |

| 2.33.2   | Command Completion                      | . 2-92 |

| 2.33.3   | RECEIVE.STATUS Interrupt                | . 2-93 |

|          |                                         |        |

| 3        | EPROM-Based Adapters                    | . 3-1  |

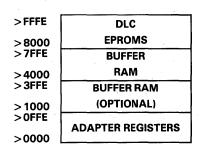

| 3.1      | EPROM Memory Map                        |        |

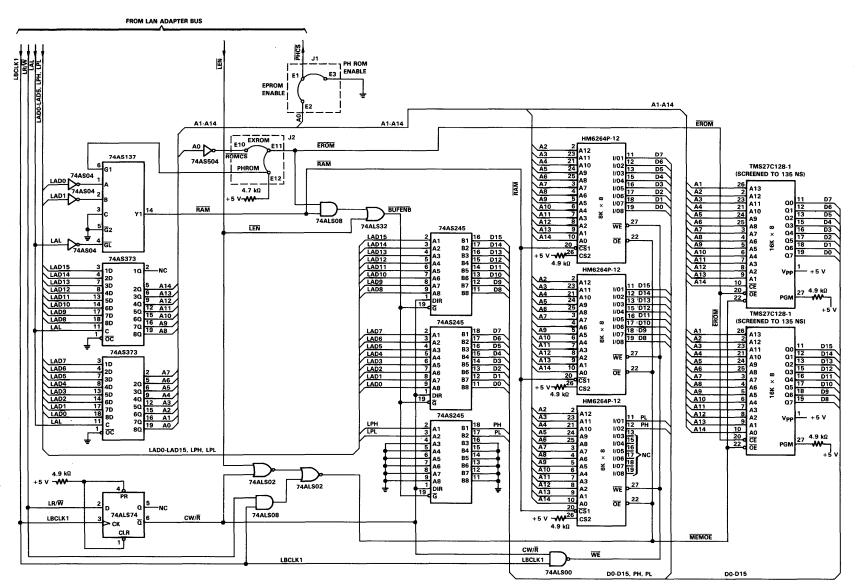

| 3.2      | EPROM Schematic                         |        |

| 3.3      | Debug Methodology                       |        |

| 3.3.1    | ADS Installation                        |        |

| 5.5.1    |                                         | . 3-3  |

| 4        | DRAM-Based Adapters                     | 4 1    |

| 4<br>4.1 |                                         |        |

|          | Memory Map                              |        |

| 4.2      | DRAM Schematic                          |        |

| 4.3      | Code DownLoad                           |        |

| 4.3.1    | Object File Format                      |        |

| 4.3.2    | Download State                          |        |

| 4.3.3    | Download and Execute                    |        |

| 4.4      | Debug Methodology                       | . 4-9  |

|          |                                         |        |

| 5        | Adapter Debug Software                  |        |

| 5.1      | Stage 1: LAN Adapter Bus Verification   |        |

| 5.1.1    | Phase Completion Reporting              | . 5-1  |

| 5.1.2    | The Five Verification Phases            | . 5-2  |

| 5.1.3    | Phase 1                                 | . 5-3  |

| 5.1.4    | Phase 2                                 | . 5-5  |

| 5.1.5    | Phase 3                                 |        |

| 5.1.6    | Phase 4                                 |        |

| 5.1.7    | Phase 5                                 |        |

| 5.1.8    | Direct I/O Interface to Attached System |        |

| 5.1.9    | Bring-Up Diagnostics                    |        |

| 5.1.9    | Stage 2: ADS Command Set                |        |

|          | 0                                       |        |

| 5.2.1    | ADS Command                             |        |

| 5.2.2    | Command >81 - Clear RAM                 |        |

| 5.2.3    | Command >82 - Fill RAM with Pattern     |        |

| 5.2.4    | Command >83 — Set Interrupt Active      |        |

| 5.2.5    | Command >84 — Test DMA to Adapter       |        |

| 5.2.6    | Command >85 — Test DMA from Adapter     |        |

| 5.2.7    | Command >90 — Test Expansion Memory     | . 5-15 |

|          |                                         |        |

| 5.2.8            | Command >91 – Test Wrap Function                             |

|------------------|--------------------------------------------------------------|

| 5.2.9            | Command $>92$ — Test Whip Function                           |

| 5.2.10           |                                                              |

| 5.2.11           |                                                              |

| 5.2.12           |                                                              |

| 5.2.12           |                                                              |

|                  |                                                              |

| 5.2.14<br>5.2.15 |                                                              |

|                  |                                                              |

| 5.2.16           | Command >9A — Test Insert Function with Insertion Delay      |

| 6                | Ding Interface Lowert Outdelines                             |

| 6<br>6.1         | Ring Interface Layout Guidelines                             |

|                  | Ring Interface Signal Classification                         |

| 6.2              | Layout Guidelines                                            |

| 6.2.1            | Differential Data                                            |

| 6.2.2            | Digital Control                                              |

| 6.2.3            | Digital Data                                                 |

| 6.2.4            | Analog                                                       |

| 6.3              | Power and Ground                                             |

| _                |                                                              |

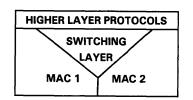

| 7                | TMS38021 Bridge Application                                  |

| 7.1              | TMS380 Bridging Applications — General                       |

| 7.1.1            | MAC Layer Bridge Alternatives                                |

| 7.1.2            | Adaptive Bridging                                            |

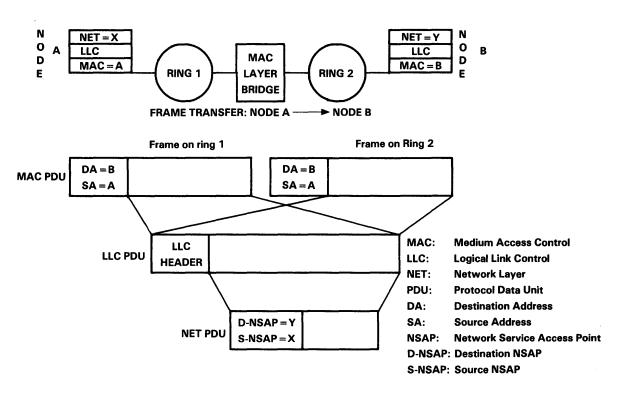

| 7.1.3            | Source Routing Bridging                                      |

| 7.1.4            | Source Routing Bridges and the TMS380                        |

| 7.2              | TMS38021 Protocol Handler                                    |

| 7.2.1            | Addressing — The TMS38020                                    |

| 7.2.2            | Addressing — The TMS38021                                    |

| 7.2.3            | Obtaining Universal Address Block Assignments                |

| 7.2.4            | External Copy Hardware Option7-10                            |

| 7.2.5            | Other Hardware Differences Between the TMS38020 and TMS38021 |

| 7.2.6            | Electrical Specifications                                    |

| 7.3              | Bridge Options Software                                      |

| 7.4              | PASS CRC Option                                              |

| 7.5              | Transmit Source Address Option                               |

| 7.6              | Allowed Transmit Priorities                                  |

| 7.7              | Added Functional Addresses                                   |

| 7.8              | Added Transmit Source Classes                                |

| 7.9              | MODIFY.OPEN.PARAMETERS Command7-17                           |

| 7.10             | Extended Receive Open Options                                |

| 7.11             | Miscellaneous Differences                                    |

| 7.12             | Software/Hardware-Based Source Routing Bridge                |

| 7.12.1           |                                                              |

| 7.12.2           |                                                              |

| 7.12.3           |                                                              |

| 7.13             | Hardware-Based Source Routing Bridge Example                 |

| 7.13.1           |                                                              |

| 7.13.2           |                                                              |

| 7.13.3           |                                                              |

|                  | · · · · · · · · · · · · · · · · · · ·                        |

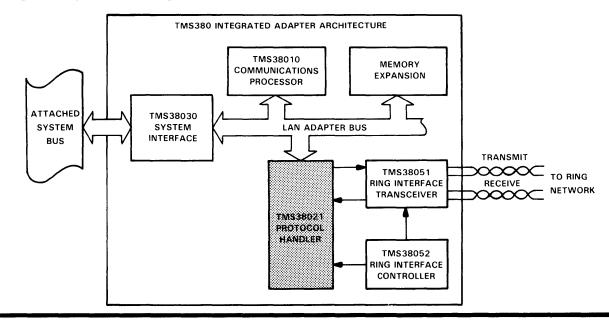

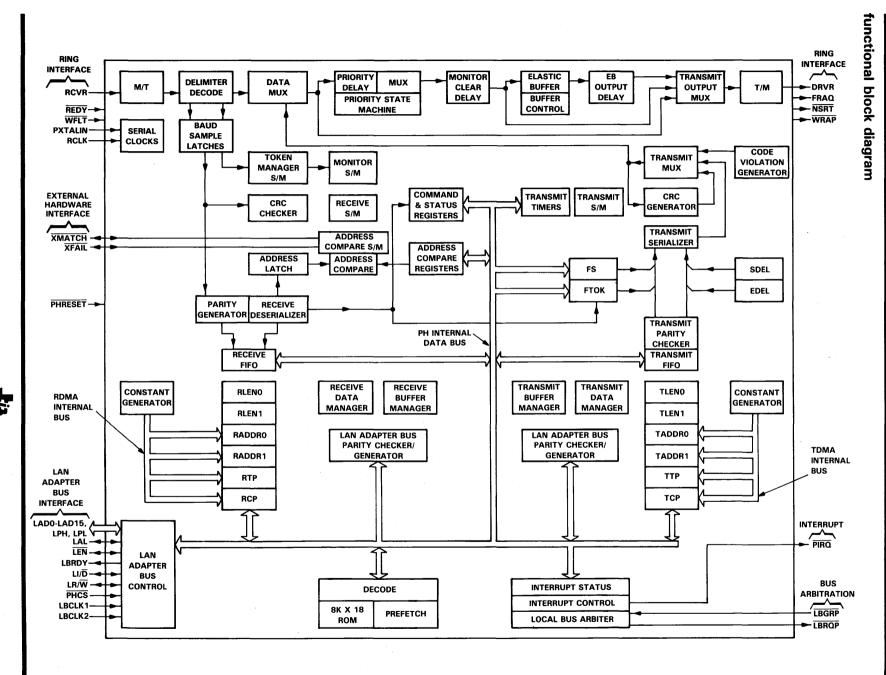

| Α | TMS38021 Protocol Handler Data Sheet            Errata to TMS380 Adapter Chipset User's Guide |     |

|---|-----------------------------------------------------------------------------------------------|-----|

| В | Change to TMS380 PC Family Card                                                               | B-1 |

| С | Sample Download Driver                                                                        | C-1 |

| D | Comparison to IBM Commands                                                                    | D-1 |

## **Tables**

| Table |                                           | Page |

|-------|-------------------------------------------|------|

| 0.1   | Transmit Data                             | 0 15 |

| 2-1.  |                                           |      |

| 2-2.  | Interrupt Register Write Bit Functions    |      |

| 2-3.  | Interrupt Register Read Bit Functions     |      |

| 2-4.  | Receiver Frame Types                      |      |

| 2-5.  | Bring-Up Diagnostic Error Codes           |      |

| 2-6.  | Adapter Initialization Errors             |      |

| 2-7.  | LLC Open Error Codes                      |      |

| 2-8.  | CLOSE Return Codes                        |      |

| 2-9.  | SET.GROUP.ADDRESS Return Codes            |      |

|       | SET.FUNCTIONAL.ADDRESS Return Codes       |      |

|       | READ.ERROR.LOG Return Codes               |      |

|       | READ.ADAPTER. Return Codes                |      |

|       | MODIFY.OPEN.PARAMETERS Return Codes       |      |

|       | RESTORE.OPEN.PARAMETERS Return Codes      |      |

|       | LLC.RESET Return Codes                    |      |

|       | OPEN.SAP Return Codes                     |      |

|       | CLOSE.SAP Return Codes                    |      |

|       | OPEN.STATION Return Codes                 |      |

|       | CLOSE.STATION Return Codes                |      |

|       | CONNECT.STATION Return Codes              |      |

|       | MODIFY.LLC.PARMS Return Codes             |      |

|       | FLOW.CONTROL. Return Codes                |      |

|       | STATION.STATS Return Codes                |      |

|       | DIR.INTERRUPT Return Codes                |      |

|       | CONFIG.BRIDGE.PARMS Return Codes          |      |

|       | LLC.REALLOCATE Return Codes               |      |

|       | TIMER_SET Return Codes                    |      |

|       | Transmit Frame Types                      |      |

|       | Transmit Error Codes                      |      |

| 5-1.  | Verification Phase Status Posting         |      |

| 5-2.  | Bring-Up Diagnostic Error Codes           |      |

| 5-3.  | ADS Commands                              |      |

| 5-4.  | Command >81 Parameters                    |      |

| 5-5.  | >7X Error Codes                           |      |

| 5-6.  | Command >82 Parameters                    |      |

| 5-7.  | Command >84 Parameters                    |      |

| 5-8.  | Command >85 Parameters                    |      |

| 5-9.  | Command >90 Parameters                    |      |

| 6-1.  | Ring Interface Signal Classification      |      |

| 6-2.  | Discrete Components – Differential Data   |      |

| 6-3.  | Discrete Components-Analog                |      |

| 7-1.  | XMATCH, XFAIL Pin Functions               |      |

| 7-2.  | Receive Status Bit Functions              |      |

| 7-3.  | Revised Receive Option Codes              |      |

| 7-4.  | Transmit and Receive CSTAT Fields—Summary |      |

| 7-5.  | Address Complete                          |      |

| 7-7.  | ECH PAL Equations                         |      |

| D1.   | Comparison to TOKREUI Commands            |      |

| D2.   | Comparison to IBM Hardware SRB Commands   | D-3  |

## Illustrations

### Figure

| 2-1.  | Open Systems Interconnect Model                          |        |

|-------|----------------------------------------------------------|--------|

| 2-2.  | A Typical LLC Session                                    |        |

| 2-3.  | SAP/Link Station Association                             |        |

| 2-4.  | LLC Frame                                                | . 2-5  |

| 2-5.  | System Command Block Format                              | . 2-12 |

| 2-6.  | System Station Block Format                              | . 2-13 |

| 2-7.  | Attached Systems Logical Frame Format                    | . 2-13 |

| 2-8.  | SIF Interrupt Register                                   | . 2-17 |

| 2-9.  | Interface Control Block                                  | . 2-28 |

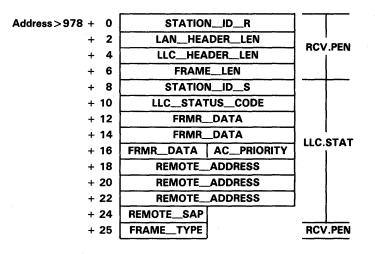

| 2-10. | Initialization Parameter Block                           | . 2-32 |

| 2-11. | TMS380 Adapter Command Set                               | . 2-36 |

|       | Open Parameter Block                                     |        |

| 2-13. | OPEN Phases and OPEN Error Codes                         | . 2-44 |

| 2-14. | Error Log Table                                          | . 2-49 |

| 2-15. | Data Area Format                                         | . 2-52 |

| 2-16. | SAP Parameter Block                                      | . 2-57 |

| 2-17. | Station Parameter Block                                  | . 2-62 |

| 2-18. | Correct Parameter Block                                  | . 2-66 |

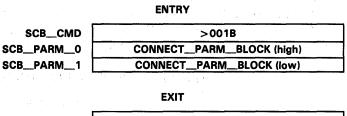

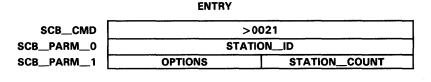

| 2-19. | Modify Parameter Block                                   | . 2-68 |

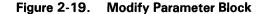

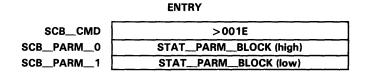

| 2-20. | Statistics Parameter Block                               | . 2-72 |

| 2-21. | TRANSMIT Parameter List                                  | . 2-80 |

| 2-22. | RECEIVE Parameter List                                   | . 2-89 |

| 2-23. | LLC RECEIVE Command Flow                                 | . 2-92 |

| 3-1.  | EPROM-Based Memory Map                                   | . 3-1  |

| 3-2.  | EPROM-Based Adapter Bus Schematic                        | . 3-2  |

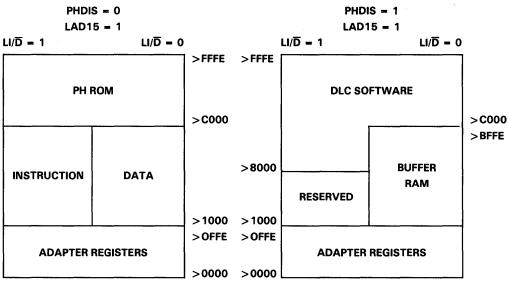

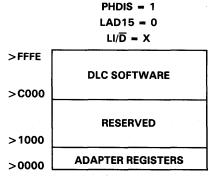

| 4-1.  | DRAM-Based Memory Map                                    | . 4-2  |

| 4-2.  | Download State at DRAM Memory Map                        | . 4-2  |

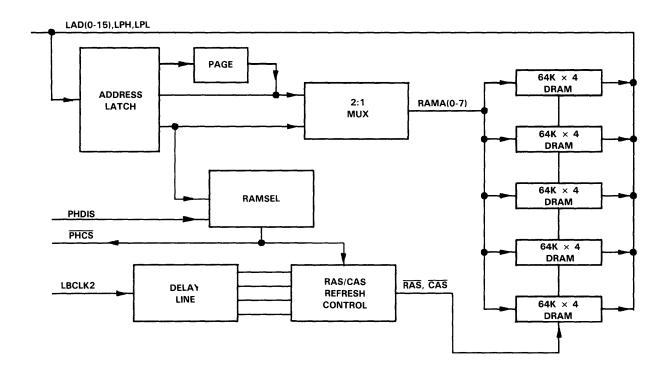

| 4-3.  | DRAM Interface Block Diagram                             | . 4-3  |

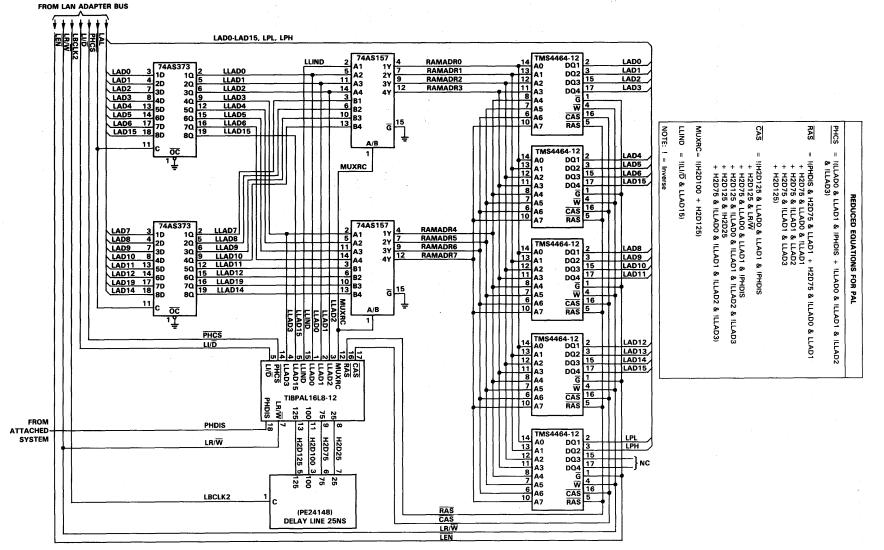

| 4-4.  | DRAM Schematic                                           | . 4-4  |

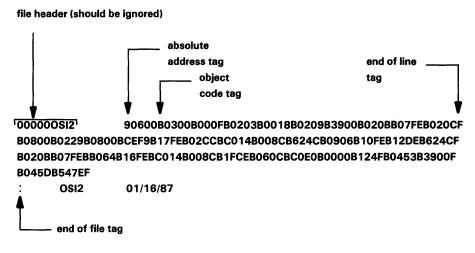

| 4-5.  | Tagged Object Code Format                                | . 4-6  |

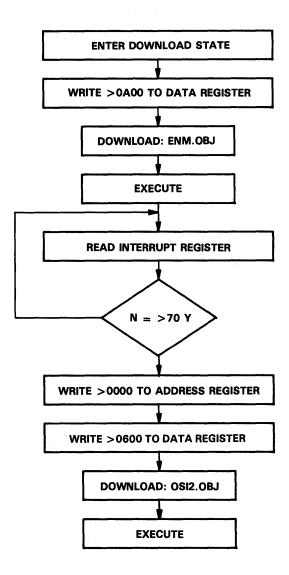

| 4-6.  | Flow Diagram for Downloading a Subroutine                | . 4-8  |

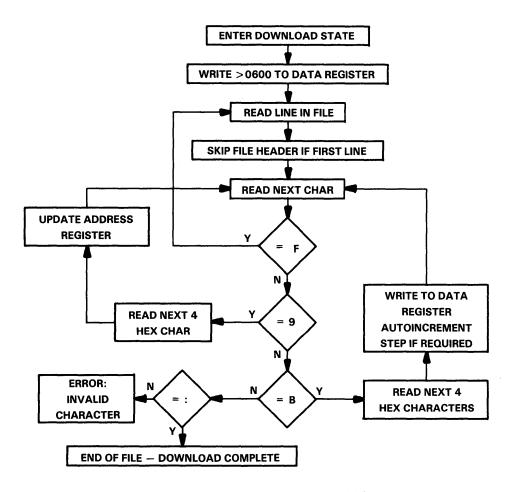

| 4-7.  | General Download Flow Diagram                            |        |

| 5-1.  | Bus Cycles Following LRESET when Executing Out of PH ROM | . 5-4  |

| 5-2.  | PH Jumper Configuration                                  | . 5-18 |

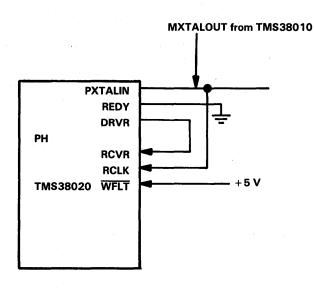

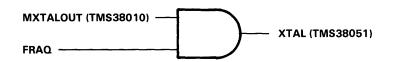

| 6-1.  | XTAL Gating Configuration                                | . 6-3  |

| 7-1.  | Generic MAC Layer Bridge                                 | . 7-1  |

| 7-2.  | MAC Layer Bridge                                         |        |

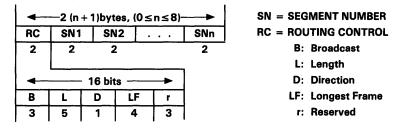

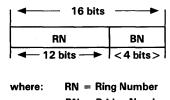

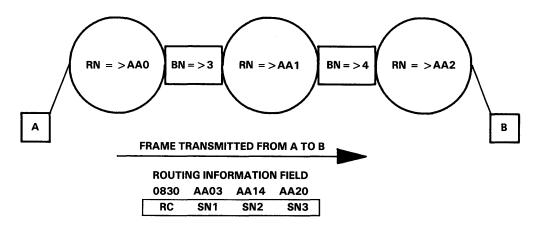

| 7-3.  | Routing Information Field Format                         | . 7-4  |

| 7-4.  | Segment Number Field                                     |        |

| 7-5.  | Example Routing Between Station A and Station B          | . 7-6  |

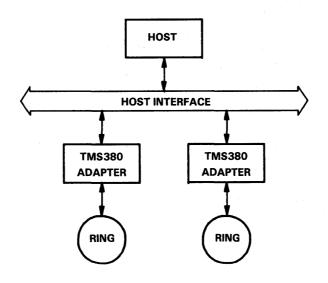

| 7-6.  | Design Examples MAC Bridge                               |        |

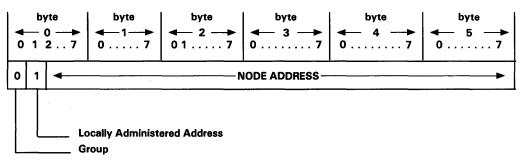

| 7-7.  | Ring Station Address – TMS38020                          |        |

| 7-8.  | Ring Station Address-TMS38021                            |        |

| 7-9.  | TMS38021 External Copy Hardware Interface Pins           | . 7-11 |

|       |                                                          |        |

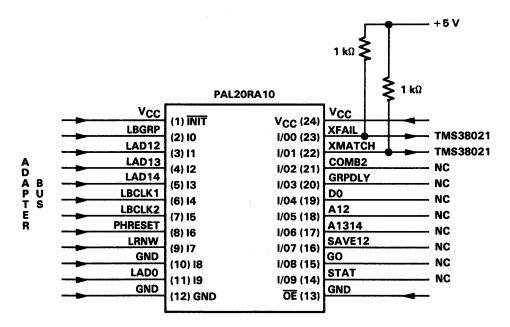

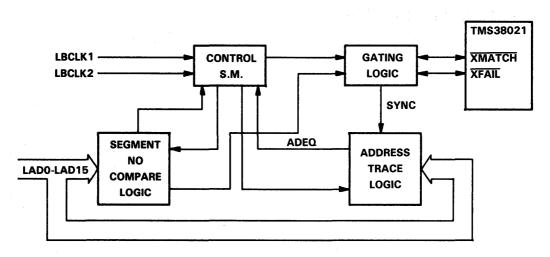

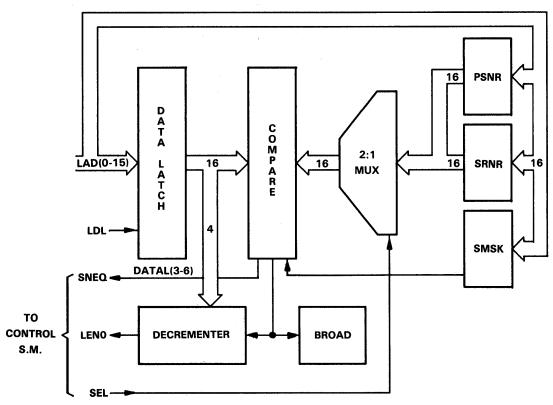

| 7-13. | TMS380 and ECH Block Diagram               | ) |

|-------|--------------------------------------------|---|

| 7-14. | ECH PAL Implementation                     | ) |

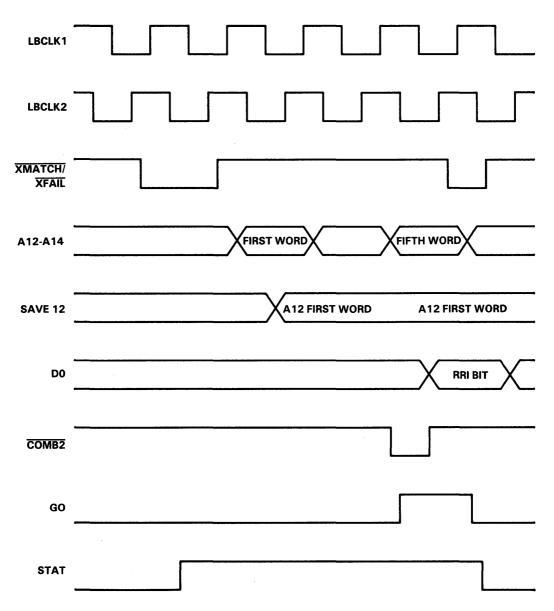

| 7-15. | ECH Timing Diagrams                        | 2 |

| 7-16. | Source Routing ECH Block Diagram7-24       | ÷ |

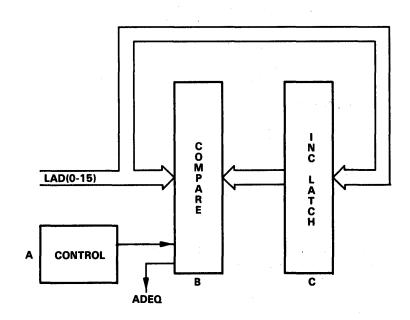

| 7-17. | Address Trace Logic                        | j |

| 7-18. | Segment Number Compare Logic               | j |

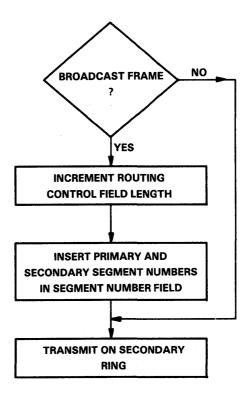

| 7-19. | Bridge Host Software Flowchart             | 1 |

| B-1.  | Inverter in Socket                         |   |

| B-2.  | PC Family Card Logic with ModificationsB-3 |   |

|       |                                            |   |

|       |                                            |   |

х

## 1. Introduction

This supplement to the *TMS380 Adapter Chipset User's Guide* is provided to supply information on recently announced TMS380 Token Ring Adapter Chipset hardware and software enhancements. Included in this supplement are:

- TMS380-based Data Link Control (DLC) extended software interface provided when the IEEE 802.2 Logical Link Control (LLC) and IEEE 802.5 Medium Access Control (MAC) are resident.

- EPROM-based adapter bus expansion for LLC support.

- DRAM-based adapter bus expansion for LLC support.

- Updated adapter design and bring-up guidelines, including Adapter Debug Software and Ring Interface layout.

- TMS38021 Bridge Application.

Additionally, the appendices within this supplement provide:

- Complete errata for the TMS380 Adapter Chipset User's Guide (SPWU001D).

- Detailed engineering change notice for altering the Texas Instruments TMDS380PCF-1 PC Family Token Ring development card to allow it to operate with the TMS380-based Logical Link Control.

- Sample download driver program to allow the TMS380-based Logical Link Control to be downloaded into RAM on the TMS380 Adapter Bus.

- Command comparison at the TMS380 DLC interface with the commands at IBM's PC adapter hardware interface.

The reader is assumed to be familiar with information in the following references:

- TMS380 Adapter Chipset User's Guide, Revision D (TI, SPWU001D)

- IBM Token-Ring Network Architecture Reference (IBM, #6165877)

- IBM Token-Ring Network PC Adapter Technical Reference (IBM, #69X7862)

- ANSI/IEEE Standard 802.2-1985

- Token Ring Access Method and Physical Layer Specification, ANSI/IEEE Standard 802.5-1985, ISO Draft Proposal 880215, approved 12/13/85.

## 2. DLC System Software Interface

This section describes the extended DLC software interface presented by the TMS380 when the IEEE 802.2 Logical Link Control (LLC) software is resident on the adapter. This interface controls the operation of the adapter to effect data transfer to and from the network. Data and control information are passed between the adapter and the attached system by both Direct Input/Output (DIO) and Direct Memory Access (DMA) operations. Four System Interface Registers and a 26-byte Interface Control Block (ICB) are accessed via DIO. The DMA channel is used to pass commands, parameters, and frames to and from attached system memory.

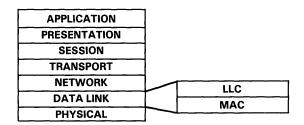

The TMS380 adapter with LLC provides a Data Link Control interface encompassing both the IEEE 802.2 LLC and IEEE 802.5 MAC protocols (see Figure 2-1). This section describes both of these interfaces. The MAC interface described is the same as the Medium Access Control interface described in Section 4 of the *TMS380 Adapter Chipset User's Guide*. Therefore, software written for the MAC-level TMS380 will continue to run to this interface.

Figure 2-1. Open Systems Interconnect Model

Users programming to the adapter may choose to use only the MAC interface or may take advantage of the higher functionality that the LLC interface provides. The LLC interface supports both Type 1 and Type 2 protocols.

**The Adapter Advantage.** Because of its use by IBM, and other major implementers of communications protocols, Logical Link Control software has become an important factor on the token ring. LLC is the cornerstone on which IBM's Netbios and APPC, and MAP/TOP's OSI protocols are based.

LLC software executing on the TMS380 adapter has several advantages over LLC on the attached system. First, with the LLC on the TMS380, a user can guarantee the same LLC across an entire product line. For host-based LLC, different code would have to be developed for different hosts, thus introducing the possibility of incompatibilities. TI has provided, on the TMS380, a single version of LLC for compatibility and portability across all product lines, including different host processors and operating systems, such as MS-DOS, UNIX, and VM. Thus, equipment developers using the TMS380 are spared significant development costs through simplified system integration. With LLC on the TMS380, the LAN protocols are independent of the attached product and operating system.

A second advantage of having the LLC on the adapter is that system performance can be increased up to 100% over host-based solutions. This increased performance results largely from the decreased data movement. With host-based LLC, received frames must be transferred to the attached system, an acknowledgment packet built in the attached system, and the acknowledgment packet transferred to the adapter for transmission. With LLC in the adapter, received frames are examined while still in the adapter, and acknowledgment packets are built and sent from within the adapter. This decreased data movement increases overall network throughput.

Another factor in performance improvement is increased available processing time for the attached system. When the attached system is relieved of the LLC protocols, more bandwidth is available for data processing. Thus, frames are queued to the adapter for transmission faster than when the LLC is host-resident. Because the LLC protocols can be handled on the adapter, the attached system is freed from time consuming operations such as sequencing, acknowledgments, link session control, and automatic retries. Therefore, more of the attached system's processor power and memory space is available for user functions.

By putting 802.2 Logical Link Control on the TMS380 adapter, TI has increased performance, confidence of compatibility, portability, and ease of use of the protocols.

#### 2.1 Logical Link Control

This section describes the Logical Link Control functions and parameters necessary to use the LLC programming interface. For more detailed information on the LLC protocols, refer to the *IBM Token Ring Architecture Reference* (IBM, 1986), and the IEEE/ANSI Standard 802.2-1985.

The IEEE 802.2 Logical Link Control sublayer is the top sublayer in the Data Link Layer of the OSI Reference Model. The LLC sublayer is common to all the IEEE 802 Medium Access Control layers. The LLC sublayer provides services for the Network layer protocol. There are currently three types of Logical Link Control operation defined by the IEEE 802 standard. These include Type 1, Type 2, and Type 3. They are provided to satisfy a broad range of applications.

#### 2.1.1 Type 1 — Connectionless LLC

Type 1 LLC provides a connectionless data link service. This type of protocol provides a data link with minimum protocol complexity. Type 1 LLC could be used where the upper layers provide sufficient error detection and recovery, and the user does not wish to duplicate these functions at the data link layer. Type 1 LLC could be used in an application where it is not necessary to guarantee all data link layer transmissions. Type 1 LLC also includes the protocols for determining which type of LLC protocol a node supports. Type 1 is used in the MAP/TOP implementation of ISO protocols.

When using Type 1 communications, each node must open a Service Access Point (SAP) through which communication takes place. A separate SAP is opened for each protocol stack running above the LLC in a node. The SAP is an identifier for the LLC, a pointer to the application above it. When a SAP is opened, the attached system indicates the SAP\_\_VALUE which is to be used. This SAP\_\_VALUE is placed in the Source SAP location of each frame sent from this SAP, and is compared against the Destination SAP in received frames. In turn, when the SAP is opened, the adapter provides a STATION\_\_ID to the attached system. This STATION\_\_ID is used for communications between the attached system and the adapter. It is used in commands in both directions between the adapter and attached system as an identifier. The STATION\_\_ID consists of two

bytes. The first byte indicates a SAP, and the second indicates a Link Station. Link Stations will be discussed later. The adapter assigns the STATION\_ID in a round robin fashion. For example, the first SAP opened will have the STATION\_ID of >0100.

When a SAP is opened, the user has several configuration options for that SAP. The first is a choice of whether the adapter will respond to XID command frames for this SAP, or whether these frames should be passed on to the host. This is controlled by the XID\_HANDLER bit in the OPEN.SAP options. See the description of the OPEN.SAP command for more details. If the attached system selects to receive XID frames, then all received XID commands are passed to the attached system. Conversely, if the SAP is opened such that the adapter will respond to XID commands, then the adapter will respond to all XID commands. All XID response frames received will be passed to the attached system regardless of the state of the XID\_HANDLER bit.

The other option a user has when opening a SAP is whether the group SAP corresponding to this SAP should be opened. A group SAP is indicated by a one in the least significant bit of the SAP\_\_VALUE. A group SAP can be used in the destination SAP field of a frame to send frames to more than one SAP at a node. When a frame to a group SAP is received, the adapter duplicates the frame and issues a RECEIVE.PENDING interrupt to each of the individual SAPs belonging to the group SAP.

Once the SAP has been opened, the user of that SAP can transmit and receive any Type 1 frame through that SAP. Type 1 frames are listed below. The frames are described later.

- XID

- TEST

- UI

All communication directly through the SAP is connectionless.

#### 2.1.2 Type 2 – Connection-Oriented LLC

For connection-oriented services, the attached system must open further connections after opening the SAP.

IEEE 802.2 Type 2 LLC provides a connection-oriented data link service. Type 2 LLC is similar to HDLC protocols in use today. Type 2 LLC guarantees the delivery of all data link transmissions with sequencing, acknowledgments, and automatic retries. With Type 2 LLC, connections are established between nodes wishing to communicate prior to any data transmissions. These are referred to as ''link stations''. Type 2 LLC is the data link layer of IBM's protocols for local area networks.

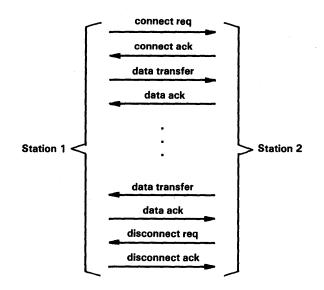

For illustration, a typical LLC Type 2 session is shown in Figure 2-2. A station wishing to communicate (station 1) sends out a connection request frame to the station with which it wants to communicate (station 2). If station 2 is able (has the resources, is authorized) to establish communications, then station 2 returns a positive acknowledgment to the connection request. Otherwise, a negative acknowledgment is returned and no communication link is established. Assuming that the acknowledgment is positive, the link is established, and data transfer, single or multiple, can take place in either direction. All data is acknowledgment. A single acknowledgment may acknowledge multiple packets, and acknowledgments can be piggybacked onto data packets. Once all data has been transferred, either station can send a disconnect request to close the link. This frees resources in both stations for other communications.

Figure 2-2. A Typical LLC Session

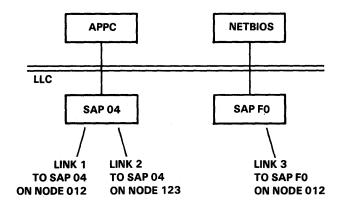

To establish communications for Type 2 operation, the attached system must open a SAP and then open a Link Station associated with that SAP. The link station creates a link from the SAP in this node to another SAP in a different node. One link station can be associated with only one local SAP and only one remote SAP on one remote node. A SAP may have multiple link stations associated with it. This hierarchy is illustrated in Figure 2-3.

Figure 2-3. SAP/Link Station Association

As with the opening of SAPs, when the attached system opens a link station, the adapter assigns a STATION\_ID for use in commands between the attached system and the adapter. The first byte of this STATION\_ID will be the SAP STATION\_ID, and the second will be the Link Station identifier. That is, a STATION\_ID of >0102 indicates the second link station opened, and indicates that it was opened under the first SAP.

#### 2.1.3 Type 3 – Connectionless-Acknowledged LLC

The third type of LLC is specifically intended for use in manufacturing applications. Type 3 is known as "connectionless acknowledged" service. Type 3 supports a protocol where packets are sent and acknowledged one at a time, without establishing the link stations of Type 2. This provides a certainty of delivery without the overhead of a Type 2 link station. For traffic that tends to be bursts of one frame, this type of protocol is suitable. The TMS380 DLC software does not implement Type 3 LLC.

#### 2.1.4 LLC Frames

The following is a description of the frames used for communications with LLC. The LLC frame has the format shown in Figure 2-4.

| MAC HEADER | DSAP | SSAP | LLC CONTROL | DATA | MAC TRAILER |

|------------|------|------|-------------|------|-------------|

|            |      |      |             |      |             |

#### Figure 2-4. LLC Frame

The MAC HEADER consists of the Starting Delimiter (SDEL), Access Control (AC), Frame Control (FC), Destination Address (DA), Source Address (SA), and Routing Information (RI) fields. The MAC TRAILER consists of the Frame Check Sequence (FCS) and Ending Delimiter (EDEL) fields. These fields are described in the *TMS380Adapter Chipset User's Guide*. The LLC Header consists of the Destination SAP (DSAP), the Source SAP (SSAP), and the LLC Control fields. These fields are described below:

- DSAP: This byte indicates the SAP to which the frame is destined. The receiving node copies the frame due to an address match on the Destination Address (DA), and then routes the frame to the appropriate attached system software based on the DSAP field value.

- SSAP: This byte indicates the SAP from which the frame originated. By examining the SSAP and Source Address (SA) fields, the adapter can determine to which link station under the DSAP the frame is destined. Since the source SAP may only be an individual SAP, the least significant bit of the SSAP field is used to distinguish commands from responses. If this bit is zero, the frame is a command. If the bit is one, the frame is a response.

- LLC CONTROL: This field is either one or two bytes in length. For unnumbered LLC frames it is one byte; for numbered frames it is two bytes. This field is the "command" field of the LLC. It determines what type of LLC frame this is. The LLC Control field can take on the values described in the following pages. For more information on these frames, see the IEEE/ANSI Standard 802.2 -1985 and the *IBM Token-Ring Network Architecture Reference* (IBM, 1986).

**Unnumbered Information.** The Unnumbered Information (UI) frame is the means of transferring data in a Type 1 environment. For this frame, the LLC Control field takes on the binary value b'00000011'.

**Exchange Identification.** The Exchange ID (XID) is a frame used by LLC to identify the properties of a SAP and request the properties of a remote SAP. This frame identifies the type(s) of LLC that are supported by a SAP, and also identifies the receive window size (N3), which will be discussed later. The LLC Control field for this frame contains the binary value b'101p1111'. The "p" value is the poll/final bit of LLC. The poll/final bit is used to check that the remote station is responding to frames. If the poll bit in a command is set to one, then the final bit (same bit position) in the response to that command must also be set to one. This mechanism can be used to match a response with the polled command. The least significant bit of the SSAP field will be zero, indicating a command, in the command XID. The bit will be a one in the response XID. For more information on the poll/final bit and the XID command, see the *IBM Token-Ring Network Architecture Reference* (IBM, 1986) and the IEEE/ ANSI Standard 802.2-1985.

**Test.** The Test Command frame is sent to cause the remote station to send a Test Response. Any data sent in a Test Command is echoed in the Test Response. For the Test frame, the LLC Control field takes on the value b'111p0011', where the "p" bit is the poll/final bit. The least significant bit of the SSAP field will be zero to indicate a command, or one to indicate a response, as appropriate.

**Set Asynchronous Balanced Mode Extended.** The Set Asynchronous Balanced Mode Extended (SABME) frame is sent to initiate a link station between two SAPs. This frame is sent as a result of a CONNECT.STATION command issued by the attached system. The value of the LLC Control field is b'011p1111'.

**Disconnect.** The Disconnect command (DISC) is sent to request that a link between two SAPs be shut down. This frame is sent as a result of a CLOSE.STATION command from the attached system, or various error conditions in the link station. The LLC Control field for the DISC is b'010p0011'.

**Unnumbered Acknowledgment.** The Unnumbered Acknowledgment (UA) is a response sent to positively acknowledge received unnumbered commands. The UA is sent as a response to the SABME and DISC commands. The LLC Control field for the UA response is b'011f0011'. The ''f' bit is the poll/final bit described earlier.

**Disconnected Mode.** The Disconnected Mode (DM) frame is a response sent to negatively acknowledge received unnumbered commands. The DM is sent as a response to the SABME when resources are not available to establish the requested link. The DM is sent as a response to the DISC command when the receiving adapter is in the Disconnected mode. This usually has resulted from error conditions in the link station. The LLC Control field for the DM response is b'000f1111'.

**Frame Reject.** The Frame Reject (FRMR) is a response sent when an illegal frame is received. An illegal frame is one of the following:

- 1. An information field in a UA, DM, SABME, or DISC frame, which do not allow information fields.

- 2. The final bit set to one when no poll bit was set.

- 3. An unsolicited UA frame.

- 4. An invalid N(R) from the remote station.

- 5. An unexpected N(S) from the remote station.

The LLC Control field for the FRMR response is b'100f0111'.

**Information Frame.** The I Frame is used to transfer data in an LLC Type 2 connection. Each I Frame contains a send sequence number, N(S), that is the sequence number of this I Frame. It also contains a received sequence number, N(R), which has the same meaning as in the RR and RNR frames. Thus, acknowledgments can be piggy-backed on I Frames. The format of the I Frame is shown below. Note that bit 7 of the Control field set to zero indicates an I Frame.

| BIT | 0 | 1 | 2        | 3    | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11   | 12 | 13 | 14 | 15  |

|-----|---|---|----------|------|---|---|---|---|---|---|----|------|----|----|----|-----|

|     |   |   | <u> </u> | I(S) |   |   |   | 0 |   |   |    | N(R) |    |    |    | p/f |

**Receive Ready.** The Receive Ready (RR) response is sent in response to a received I Frame. This response acknowledges receipt of the frame, and indicates that the receiving adapter is ready to receive additional frames. Contained within the RR frame is the N(R) number, which is the sequence number of the I Frame that the station expects to receive next. That is, an RR frame with N(R) = 3 acknowledges all I Frames through the I Frame to periodically check that the link station is still functioning. This process is known as checkpointing and is described later. The format of the RR frame is shown below. The p/f bit is the poll/final bit.

| BIT | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11   | 12 | 13 | 14 | 15  |

|-----|---|---|---|---|---|---|---|---|---|---|----|------|----|----|----|-----|

| Ľ   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |   |   |    | N(R) |    |    |    | p/f |

**Receive Not Ready.** The Receive Not Ready (RNR) response is sent in response to a received I Frame. This response acknowledges receipt of the frame, and indicates that the receiving adapter is not ready to receive additional frames. Contained within the RNR frame is the N(R) number, which is the sequence number of the I Frame that the station expects to receive next. That is, an RNR frame with N(R) = 3 acknowledges all I Frames through the I Frame with sequence number 2. The RNR frame can also be used in the checkpointing process. The format of the RNR frame is shown below.

| BIT | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11   | 12 | 13 | 14 | 15  |

|-----|---|---|---|---|---|---|---|---|---|---|----|------|----|----|----|-----|

| ſ   | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |   |   |    | N(R) |    |    |    | p/f |

**Reject.** The Reject (REJ) response is sent to request the retransmission of I frames beginning with the frame whose sequence number is contained in the N(R) field. The format of the REJ frame is shown below.

| BIT | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11   | 12 | 13 | 14 | 15  |

|-----|---|---|---|---|---|---|---|---|---|---|----|------|----|----|----|-----|

|     | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |   |   |    | N(R) |    |    |    | p/f |

#### 2.1.5 LLC Protocol States

In Type 2 communications, link stations can take on any of eight (8) primary and seven (7) secondary states. The descriptions of these states follows. For further information on link station states, the user should refer to the *IBM Token-Ring Architecture Reference* (IBM, 1986).

**Closed.** This is the default state of all non-existent link stations. In this state, all received frames except the SABME will be ignored. This state is entered when:

1. A CLOSE.STATION command issued by the attached system is completed.

2. The attached system issues an LLC.RESET command.

This state is exited to the Disconnected state when the attached system issues an OPEN.STATION command or a SABME has been received and the adapter is waiting for the attached system's response to the connection request.

**Disconnected.** This state is entered when:

- 1. The attached system issues an OPEN.STATION command.

- 2. The adapter has received a SABME frame and opened the station.

- 3. A DISC command has been received from the remote node, and a UA response has been sent.

- 4. A DM response to a transmitted DISC command is received from the remote node.

- 5. The TI timer expires when in the Disconnecting state.

This state is exited to the Opening state when the attached system issues a CONNECT.STATION command, or when a SABME is received; the state is exited to the Closed state when the attached system issues a CLOSE.STATION command.

**Disconnecting.** This state is entered when:

- 1. The attached system issues a CLOSE.STATION command, and a DISC command has been transmitted.

- 2. The remote node has responded to transmitted I frames but has not accepted them, and the retry counts have been exceeded.

This state is exited to the Disconnected state if TI expires or a response has been received to the transmitted DISC command.

**Opening.** This state is entered when the attached system issues a CONNECT.STATION command, and the adapter has either transmitted an SABME or a UA response to an SABME from the remote node. This state is exited to Opened when an I Frame or RR response is received from the remote node. Since I Frames can be transmitted only in the Opened state, the two adapters in the Opening state will exchange a pair of RR frames before I Frame transmission begins.

**Resetting.** This state is entered when the adapter receives a SABME frame for an opened link station. This state is exited to the Opening state when a response to the SABME is transmitted. Exit is to the Disconnected state when a CLOSE.STATION command is issued, or a DISC command or DM response is received.

**Frame Reject Sent.** This state is entered when an illegal frame has been received and a FRMR frame has been sent. This state is exited to the Opening state if an SABME is received. It is exited to the Disconnecting state if TI expires, or if the attached system issues a CLOSE.STATION command. Exit is to the Disconnected state if a DISC command or DM response is received.

**Frame Reject Received.** This state is entered when a FRMR frame has been received in response to a sent I Frame. This state is exited to the Opening state if an SABME is received. It is exited to the Disconnecting state if TI expires or if the attached system issues a CLOSE.STATION command. Exit is to the Disconnected state if a DISC command or DM response is received. **Opened.** This state is entered when the SABME/UA sequence is completed after the attached system issues a CONNECT.STATION command. This is the only state in which data transfer can occur. When in the Opened state, a link station may be in any of seven secondary states. If it is in any of these secondary states, then I Frame transmission is temporarily suspended.

*Checkpointing.* The Checkpointing state is entered due to a period of inactivity in the link station. When this state is entered, an RR command (or RNR if in local busy) with the poll bit set to one is transmitted. The adapter waits to receive an RR (or RNR) response with the final bit set to one before resuming I Frame transmission.

*Local Busy(user).* This state indicates that the attached system on the local node is temporarily unable to receive frames. This state is entered when a FLOW.CONTROL command with local\_busy\_status = 0 option is issued by the attached system.

*Local Busy(buffer).* This state indicates that the attached system on the local node is temporarily unable to receive frames. This state is entered when a frame has been canceled by the attached system, indicating that the SAP is out of buffers.

*Remote Busy.* This state indicates that the remote node of a link station is temporarily unable to receive frames. This condition is indicated by the receipt of an RNR frame from the remote station. This state will be exited when an RR frame is received from the remote node.

*Rejection.* An REJ frame has been sent to the remote station. This state is cleared when the requested I Frame is received.

*Clearing.* This state is entered when a local busy condition is cleared, yet the link is in a checkpointing state and so cannot inform the remote station of the cleared local busy condition. As soon as the response is received removing the station from the checkpointing state, the remote station will be notified of the local busy clear condition.

*Dynamic Window.* The station is processing the Dynamic Window algorithm. This occurs when the remote station is on another ring and there is congestion in the bridge.

#### 2.1.6 LLC Parameters

In order to understand the programming interface to LLC, the user should be familiar with some of the operational parameters of LLC. The following section describes those parameters. For further information on the LLC parameters, the user should refer to the *IBM Token-Ring Architecture Reference* (IBM, 1986), the *IBM Token-Ring PC Adapter Technical Reference* (IBM, 1986), and the IEEE/ANSI Standard 802.2-1985.

#### 2.1.6.1 Timers

The LLC protocols make use of three timers:

- The Response Timer, T1

- The Acknowledgment Timer, T2

- The Inactivity Timer, TI.

The T1 timer is started by a link station whenever an I Frame is transmitted. If the timer expires before an acknowledgment to the I Frame is received, then the station enters a checkpointing state and transmits an RR frame (or RNR frame) with the poll bit set to 1. The T1 timer should be set greater than the expected delay of the network in order to avoid unnecessary polls. Normal setting for the T1 timer is 1-2 seconds.

The T2 timer is started by a link station whenever an I Frame is received and the maximum number of I Frames that can be received (N3) has not been reached. If this timer expires before N3 has been reached, then an acknowledgment is sent to the transmitting station. The value of T2 must be less than the value of T1. Normal values for T2 are 80-256 milliseconds.

The TI timer is running whenever T1 is not running. If TI expires, the checkpointing state is entered, and an RR frame (or RNR frame) is sent to the remote station with the poll bit set to 1. This solicits a response from the remote station, and ensures that the link is still active. The TI timer should be 5-10 times greater than T1. Normal values for the TI timer are 5-20 seconds.

When timers are set at the software interface, the timer value is selected in increments of a "tick count". The tick counts are set by the OPEN.ADAPTER command. The tick counts themselves are numbers of 40-millisecond intervals. See the section on OPEN.ADAPTER command for further details. When selecting a timer value, the attached system selects a number of tick counts. The timer value parameters are a number between 1 and 10. If a number between 1 and 5 is selected, the number is multiplied by the short tick count and by 40 milliseconds to achieve the timer value. If a number between 6 and 10 is selected, the number minus 5 is multiplied by the long tick count and by 40 milliseconds to reach the timer value. For example, if in the OPEN.ADAPTER command, the attached system sets the TIMER\_T1\_2 parameter to 25, and the TIMER\_T1 parameter in the OPEN.SAP command to 10, then the value of the T1 timer is:

$(10-5) \times 25 \times 40 = 5$  seconds.

#### 2.1.6.2 Numbers

The LLC protocols use six number parameters, mostly used as counters. These parameters are:

- The Maximum I frame length, N1

- The Maximum number of retransmissions, N2

- The Maximum number of received I frames, N3

- The Maximum number of outstanding I frames, Tw

- The Working Window, Ww

- The Window increment, Nw.

The Maximum Length of an I Frame (N1) is the maximum frame size of I Frames for a given SAP. This value is set when the SAP is opened. By using this value, upper layer protocols can determine the maximum frame size on a link.

The Maximum Number of Retransmissions (N2) defines the maximum number of times an adapter will try the checkpointing poll when T1 expires. If the N2 count is exceeded without a successful poll, then the link is closed. This parameter is set in the OPEN.SAP and OPEN.STATION commands. Normal values for N2 will be less than 10.

The Maximum Number of Received I Frames (N3) is the number of I Frames that a link station can receive without transmitting a response. This number must always be less than or equal to the Tw value. This number should be set low enough, so that the adapter has enough receive buffers to hold all received frames.

The Maximum number of outstanding I Frames (Tw) is the number of I Frames that a link station can transmit without receiving an acknowledgment. This number should be set so that the receiving adapter can hold all the transmitted I Frames in its buffers, to avoid unnecessary retransmissions. This number should always be greater than or equal to the N3 value.

The Working window (Ww) and Window increment (Nw) are two counts associated with the dynamic windowing algorithm. The dynamic windowing algorithm alters the maximum number of outstanding I Frames when congestion on a network is detected. When congestion is detected, the maximum number of outstanding I Frames value, held temporarily in the working window (Ww), is set to one. As conditions improve, the Ww is incremented each time Nw frames are acknowledged. When Ww is equal to Tw, the dynamic windowing state is exited.

#### 2.2 System Memory Requirements

The integration of the adapter into an attached system requires that several system memory buffers be allocated and reserved for adapter use. All data buffers created by the attached system must be aligned on a word (even address) boundary. The following data structures listed below are those that must be created by the attached system.

- System Command Block

- System Status Block

- Frame Buffers

- Command Parameter Blocks

- Transmit Parameter List

- Receive Parameter List

- Product ID Block

#### Note:

When in 808X mode, care must be excercised in maintaining the proper orientation of bytes which are DMA read by the adapter as parameters. When these parameters are manipulated as words, the user must ensure that the byte order in memory is that order desired in the adapter. The byte-swapping hardware, enabled when in 808X mode, will maintain proper orientation of character string data types.

#### 2.2.1 System Command Block

The attached system issues a command to the adapter by loading the request in the System Control Block (SCB) and interrupting the adapter. The adapter will then download the command (and any required parameters) through the System Interface DMA channel. This interrupt may be used as an indication that the SCB is available for additional commands. The SCB is six bytes in length and the adapter will always DMA read six bytes. The SCB format is shown in Figure 2-5.

| SCB Address | + | 0 | SCB_CMD    |

|-------------|---|---|------------|

|             | + | 2 | SCB_PARM_0 |

|             | + | 4 | SCBPARM1   |

Figure 2-5. System Command Block Format

The SCB\_\_CMD field contains the 16-bit command code request to the adapter. The SCB\_\_PARM\_\_0 and SCB\_\_PARM\_\_1 fields are used to hold command dependent parameters. Usually, SCB\_\_PARM\_\_0 and SCB\_\_PARM\_\_1 are used as a 32-bit address field containing a 24-bit pointer to a Command Parameter Block. In this case the high-order byte of this field is read but ignored. Some commands do not have additional parameters and only the 16-bit command code must be written.

The attached system initiates an adapter command by following the sequence shown below:

- 1. The attached system writes the command request code into SCB\_\_CMD and any necessary parameters to SCB\_PARM\_0 and SCB\_PARM\_1.

- The attached system writes to the adapter's Interrupt Register and sets the INTERRUPT\_ADAPTER, EXECUTE, and SYSTEM\_INTERRUPT bits to one. Bit 8 (SYSTEM\_INTERRUPT) should be set to one so that incoming interrupts from the adapter are not accidentally reset.

This sequence will cause an interrupt internal to the adapter. The adapter will DMA read the SCB and, if specified, the Command Parameter Block. Once the SCB is downloaded, the adapter will write a zero to the SCB\_\_CMD field. This may be used as an indication that the command has been recognized and the attached system may write to the SCB. If the SCB\_\_REQUEST bit (bit 4) of the adapter Interrupt Register is set to one, an adapter-to-system interrupt will be posted after the parameters are read into the adapter. In most cases, this interrupt will occur on command completion. The attached system is responsible for clearing this interrupt by writing a zero to the SYSTEM\_\_INTERRUPT bit (bit 8) of the adapter Interrupt Register.

There may not be more than one Transmit or Receive command executed at one time. Multiple CONNECT.STATION or CLOSE.STATION commands may be executing. One other command may be executing while these commands are active. Thus the adapter can support a TRANSMIT command, a RECEIVE command, multiple CLOSE.STATION commands, multiple CONNECT.STATION commands, and one other command, simultaneously.

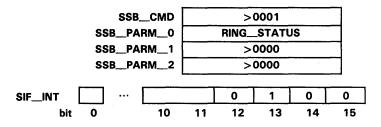

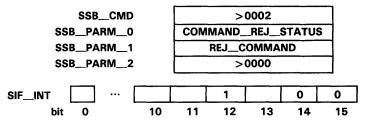

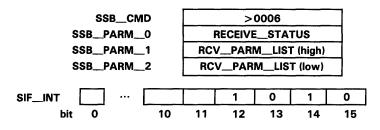

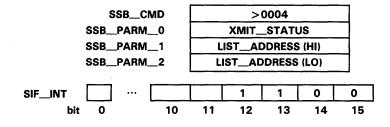

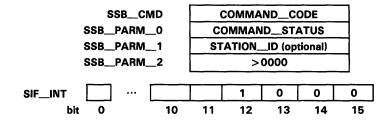

#### 2.2.2 System Status Block

When the status of any command is to be returned to the attached system, the adapter will DMA write this information to the System Status Block (SSB). An interrupt will then be posted (if enabled). After the attached system has read the SSB, the adapter must be notified that the SSB is clear and available for additional status posting. This is done by writing a one to the INTERRUPT\_\_ADAPTER (bit 0) and the SSB\_\_CLEAR bit (bit 2) of the adapter's Interrupt Register. The SSB is eight bytes in length and the adapter will always DMA write the entire eight bytes regardless of the actual length of the returned status. The SSB format is defined in Figure 2-6.

| SSB Address | + | 0 | SSBCMD     |

|-------------|---|---|------------|

|             | + | 2 | SSB_PARM_0 |

|             | + | 4 | SSB_PARM_1 |

|             | + | 6 | SSB_PARM_2 |

Figure 2-6. System Status Block Format

The SSB\_\_CMD field contains a 16-bit code which reflects the status type being returned. Valid status types which may be returned to the SSB are RING\_\_STATUS, COMMAND\_\_REJ\_\_STATUS, COMMAND\_\_STATUS, XMIT\_\_STATUS, or RCV\_\_STATUS. The command status field will be written to SSB\_\_PARM\_\_0. The bit field definitions for the different status types may be found in the descriptions of the following interrupts and commands: RING.STATUS, COMMAND.STATUS, COMMAND.REJECT, TRANSMIT, and RECEIVE.

#### 2.2.3 Frame Buffers

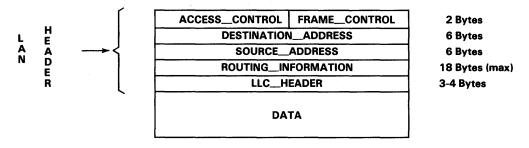

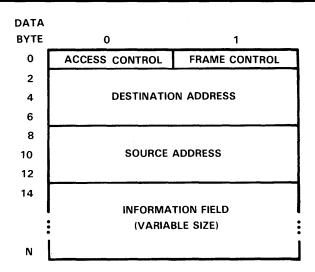

The attached system must allocate a portion of its memory for frame buffering. The amount of memory allocated will vary according to the application. All frames, except LLC Type 2 I-frames, are constructed according to the Logical Frame Format defined in Figure 2-7. I-frames consist of only the DATA field, the adapter is responsible for attaching the LAN header. Table 2-1 summarizes the data that the attached system must provide to the adapter for various frame types.

Figure 2-7. Attached System Logical Frame Format

#### Attached System Frame Fields.

ACCESS\_CONTROL: This control field consists of the following bit functions:

BITS 0-2 (ACCESS\_PRIORITY) - Selects the Access Priority for the frame. This value (0-7) must be less than or equal to the Authorized Access Priority. The adapter's Authorized Access Priority is 6 unless modified by network management.

BITS 3-7 (RESERVED) - These should be set to zero.

For all type 1 frames, the adapter will fill in the correct value for the AC byte, though the attached system must leave space for the AC in the MAC header.

FRAME\_CONTROL:

DL: This 8-bit field is defined in Chapter 3 of the *TMS380 Adapter Chipset User's Guide*. If the MAC Indicator bit is set to zero, the Authorized Function Class parameter is used to validate the Major Vector Source Class. MAC frames must be sent through the direct station. For all type 1 frames, the adapter will fill in the correct value for the FC byte, though the attached system must leave space for the FC in the MAC header.

DESTINATION\_\_ADDRESS: This field is 48 bits wide and contains the address of the destination. The address format for this field is defined in Chapter 3 of the *TMS380 Adapter Chipset User's Guide*.

SOURCE\_ADDRESS: Unless the PASS\_SOURCE\_ADDRESS option is selected, the Adapter will store the Node Address into the six bytes of the SOURCE\_ADDRESS with the exception of byte 0 bit 0 (the Routing Information Indicator). The Node Address is that address supplied by the Burned-in Address (BIA) or passed during the OPEN command.

ROUTING\_INFORMATION: This field must be included if bit 0 of SOURCE\_ADDRESS is set to one. The format of the ROUTING\_INFORMATION is described in Section 7 of this book.

LLC\_\_HEADER:

DATA:

n transformer i Stationer († 1999) 1999 - Langelsen i Stationer 1999 - Palet Stationer († 1999) 1999 - Stationer († 1999) This field consists of the DSAP, SSAP, and LLC Control fields as described earlier in this section. This field is provided by the adapter, and is not present in direct frames. Space does not need to be provided for this header in attached system memory.

The Data portion of the frame is transmitted as specified by the attached system. The CRC, Ending Delimiter, and Frame Status (FS) are appended to the data by the Adapter. Note that if the attached system selects the TRANSMIT\_CRC option, then the CRC must be included at the end of the DATA field and not appended by the adapter. See the section on TRANSMIT for more information.

| FRAME TYPE             | MAC HEADER<br>SUPPLIED BY | LLC HEADER<br>SUPPLIED BY | DATA FIELD<br>SUPPLIED BY           |

|------------------------|---------------------------|---------------------------|-------------------------------------|

| Direct Frame           | Attached System           | not used                  | Attached System                     |

| UI Frame               | Attached System           | Adapter (note 1)          | Attached System                     |

| XID Command            | Attached System           | Adapter (note 1)          | Attached System or Adapter (note 2) |

| XID Response Final     | Attached System           | Adapter (note 1)          | Attached System                     |

| XID Response Not Final | Attached System           | Adapter (note 1)          | Attached System                     |

| TEST Command           | Attached System           | Adapter (note 1)          | Attached System (optional)          |

| I Frame                | Adapter (note 3)          | Adapter (note 3)          | Attached System                     |

Table 2-1. Transmit Data

NOTES: 1. The adapter constructs the LLC header information from the STATION\_ID parameter and the REMOTE\_SAP parameter in the transmit list.

If the XID\_\_HANDLER bit in the OPEN.SAP command parameters list was set, the attached system

must provide the XID data field. If this bit was not set, the adapter will write over the first three bytes

of the data field provided by the attached system. The attached system should take care to save these

three bytes of space for the adapter.

3. I Frames may not be transmitted until the attached system has issued a CONNECT.STATION command. The adapter constructs the MAC and LLC headers from information provided in the OPEN.STATION and CONNECT.STATION commands.

#### 2.2.4 Command Parameter Block

Certain commands (e.g., the OPEN command) require that a block of memory be designated as a parameter block. This block of memory will be DMA read into adapter memory after the SCB has been read. Once the command has completed execution, this buffer may be released for other uses. The Command Parameter Block definitions are listed with the command descriptions later in this section.

#### 2.2.5 Transmit Parameter List

The TRANSMIT command requires that Transmit Parameter List(s) be allocated within attached system memory. The amount of memory allocated is dependent upon the size and number of lists used in the application. The size of a Transmit List may be selected upon adapter initialization to be either 14, 20, or 26 bytes in length. The adapter automatically adds four bytes to these values for a start-of- frame list when using the LLC interface. This is to accommodate the extra LLC transmit parameters. The Transmit Parameter List is defined in the TRANSMIT command discussion.

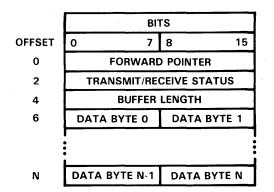

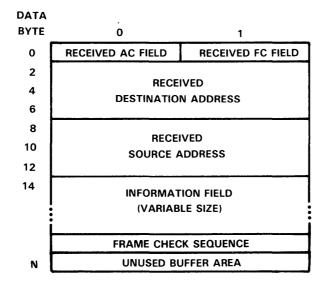

#### 2.2.6 Receive Parameter List

The RECEIVE command requires that Receive Parameter List(s) be allocated within system memory. The memory allocation size is dependent upon the size and number of lists used in the application. The size of a receive list may be selected upon adapter initialization to be either 14, 20, or 26 bytes in length. The Receive Parameter List is defined in the RECEIVE command discussion.

#### 2.2.7 Product ID Block

The OPEN command requires a pointer to an 18-byte Product Identification block as part of the open parameters. The system software designer should reserve 18 bytes of system memory for this function. This Product ID is described further in IBM's *Token-Ring Network PC Adapter Technical Reference* (IBM, 1986).

#### 2.3 Adapter Memory

The adapter contains some amount of memory on its own bus. This memory varies with the application, and is defined by the DATA\_RAM\_START\_ADDRESS and DATA\_RAM\_END\_ADDRESS parameters of the OPEN.ADAPTER command. The amount of RAM on the adapter bus determines the number of SAPs and link stations and the values of N3 and Tw that the adapter can support.

The adapter RAM is configured at the time of the OPEN.ADAPTER command. The following blocks are defined.

- 1. SAP Control Blocks. These blocks require 52 bytes of memory each. The number reserved is set by the MAX\_SAPS parameter of the OPEN.ADAPTER command.

- Group SAP Control Blocks. These blocks require 2 bytes, plus 2 bytes times the MAX\_MEMBERS parameter.

- 3. Link Station Control Blocks. These blocks require 176 bytes each. The number is set by the MAX\_STATIONS parameter.

The remaining RAM is configured for receive and transmit buffers. The number of transmit buffers is manipulated by the TRANSMIT\_MIN\_COUNT and TRANSMIT\_MAX\_COUNT parameters.

When a link station is opened, the adapter expects to have enough transmit buffers to be able to hold I Frames, up to the Transmit Window (set by the MAXOUT parameter in the OPEN.SAP or OPEN.STATION command). The attached system must assure that there is ample RAM space for these frames.

The adapter's workspace is contained in Communications Processor RAM, and is therefore not a part of the DATA\_RAM as defined by the user.

#### 2.4 Register Descriptions

The System Interface (SIF) contains four registers used for communication with the attached system. This section will describe in detail the functions performed by these registers.

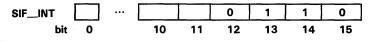

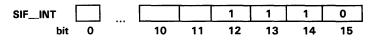

#### 2.4.1 SIF Interrupt Register

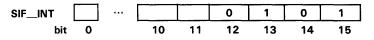

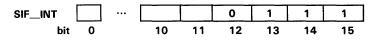

The SIF Interrupt Register is used to post interrupts to the adapter and to read interrupt status information from the adapter. The function performed by each bit of the Interrupt Register depends on whether a bit is read or written by the attached system. Bits 0-7 can be set to one but not reset to zero by the attached system. These bits can be cleared only by the Communications Processor. Likewise, bit 8 can be reset to zero only by the attached system and can be set to one only by the Communications Processor. Bits 9-15 can be read only by the attached system. These bits are set or reset by the Communications Processor.

#### 2.4.1.1 Writing to the Interrupt Register

A direct I/O (DIO) write to the most significant bit of the Interrupt Register will cause an interrupt to the adapter. Bits 1-7 provide an interrupt reason code to the adapter. A write of zero to bit 8 will reset the adapter-to-system interrupt level on the SINTR/SIRO pin. Figure 2-8 shows the bit assignments of the SIF Interrupt Register. Table 2-2 defines the functions of each bit when written by the attached system. Table 2-3 defines the functions of each bit when read by the attached system.

| BIT O | INTERRUPTADAPTER |

|-------|------------------|

| 1     | ADAPTERRESET     |

| 2     | SSB_CLEAR        |

| 3     | EXECUTE          |

| 4     | SCB_REQUEST      |

| 5     | RECEIVECANCEL    |

| 6     | RECEIVE_VALID    |

| 7     | TRANSMITVALID    |

| 8     | SYSTEM_INTERRUPT |

| 9     | INITIALIZE       |

| 10    | TEST             |

| 11    | ERROR            |

| 12    | INTERRUPT_CODE   |

| 13    | INTERRUPTCODE    |

| 14    | INTERRUPT_CODE   |

| 15    | INTERRUPT_CODE   |

|       |                  |

Figure 2-8. SIF Interrupt Register

|           | · ·                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT O     | (INTERRUPTADAPTER) - Bit 0, when set to one, will cause an internal adapter interrupt.<br>This bit has no effect when set to zero. This bit will be cleared by the adapter after the adapter<br>responds to the interrupt. The purpose of the interrupt is defined by the ADAPTER_RESET,<br>SSBCLEAR, EXECUTE, SCB_REQUEST, RECEIVE_CANCEL, RECEIVE_VALID, and<br>TRANSMIT_VALID bits described below.                       |

| BIT 1     | (ADAPTER_RESET) - Setting bit 1 to one forces an adapter reset if bits 2-7 are also set<br>to one. Following an adapter reset, the initialization procedure outlined in Section 2.5 should<br>be followed. This reset function is a software command and certain conditions of hardware<br>failure may prevent its execution.                                                                                                |

| BIT 2     | (SSBCLEAR) - This interrupt request is used by the system to notify the adapter that the System Status Block (SSB) is available for the adapter to post additional status information.                                                                                                                                                                                                                                       |

| віт з     | (EXECUTE) - This interrupt is used to initiate an adapter command contained in the System<br>Command Block (SCB). This block will be DMA read and executed by the adapter.                                                                                                                                                                                                                                                   |

| BIT 4     | (SCBREQUEST) - This interrupt is used to request the adapter to interrupt the attached system when the SCB is available for another command. The adapter will return the SCB.CLEAR interrupt code.                                                                                                                                                                                                                           |

| BIT 5     | (RECEIVE_CANCEL) - This interrupt discards remaining data on the frame currently being transferred to the attached system. This interrupt is accepted only when the receive is in a halted state. If the LLC Interface is not enabled (Bit 9 of the Initializations Options is set to zero), then this bit has the meaning of RECEIVE_CONTINUE as described in Chapter 3 of the <i>TMS380 Adapter Chipset User's Guide</i> . |

| ВІТ 6     | (RECEIVEVALID) - This interrupt request signals the adapter that the condition causing list processing suspension (odd forward pointer or invalid list) during receive has been cleared.                                                                                                                                                                                                                                     |

| BIT 7     | (TRANSMITVALID) - This interrupt request signals the adapter that the condition causing list processing suspension during transmit has been cleared.                                                                                                                                                                                                                                                                         |

| BIT 8     | (SYSTEM_INTERRUPT) - Writing a zero to bit 8 resets the adapter-to-attached-system interrupt (i.e., clears the SINTR/SIRQ line). Writing a one to this bit has no effect. See section 2.5.1 to determine correct use of this bit.                                                                                                                                                                                            |

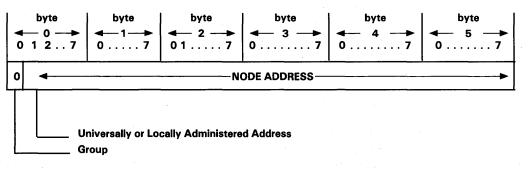

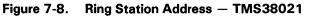

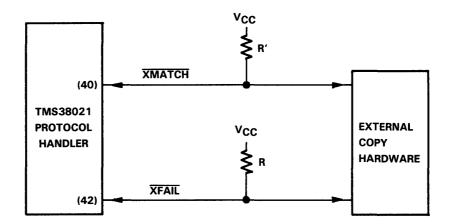

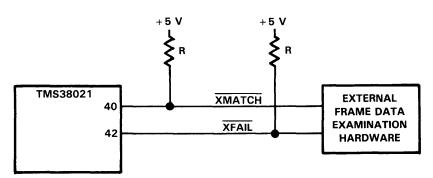

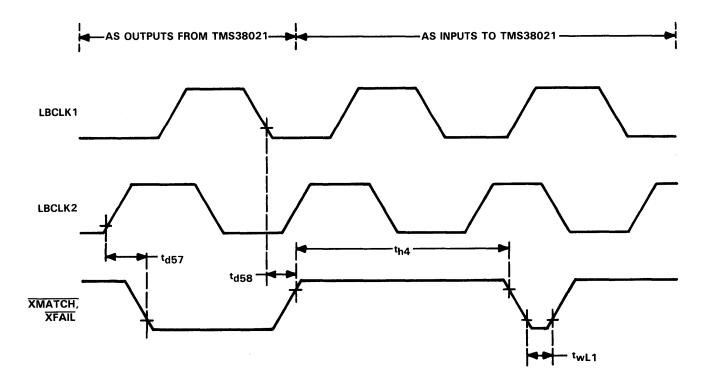

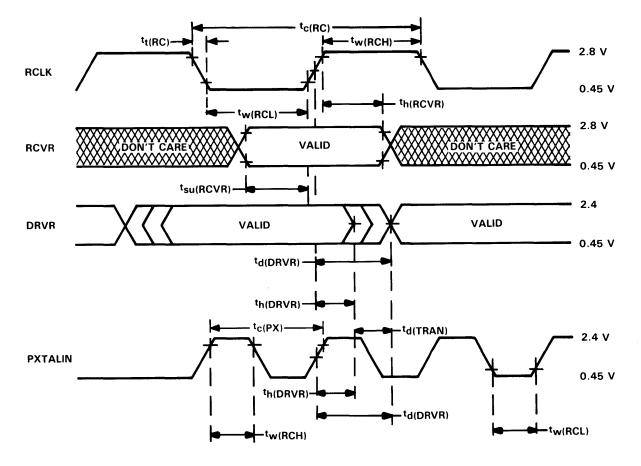

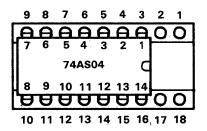

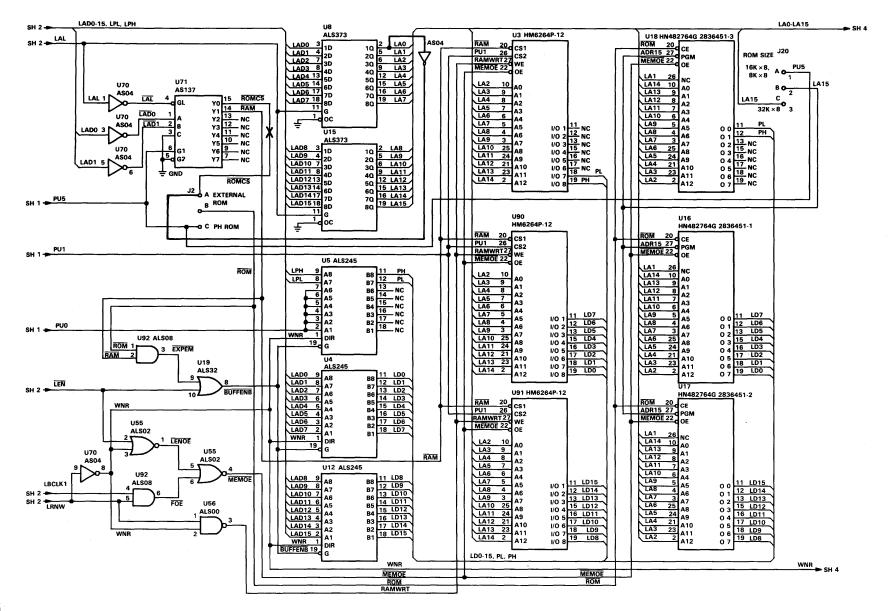

| BITS 9-15 | (RESERVED) - These bits cannot be written by the attached system.                                                                                                                                                                                                                                                                                                                                                            |