# Designer's Handbook

**Datapath VLSI Products**

## TMS34082 Designer's Handbook

2564007-9721 revision A May 1991

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Texas Instruments products are not intended for use in life-support appliances, devices, or systems. Use of a TI product in such applications without the written consent of the appropriate TI officer is prohibited.

Copyright © 1991, Texas Instruments Incorporated

## Preface

## **Read This First**

### How to Use This Manual

The purpose of this user's guide is to provide the TI customer with information on the TMS34082 graphics floating-point processor. This manual can also be used as a reference guide for developing hardware or software applications. The following list summarizes the contents of the chapters and appendices in this user's guide.

#### Chapter 1 Overview of the TMS34082

Introduces the TMS34082, its key features, typical applications, and support tools available.

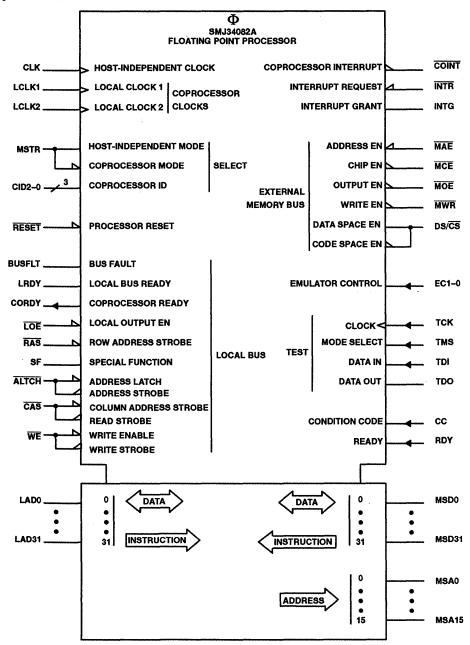

#### Chapter 2 Pinout and Pin Descriptions

Illustrates the TMS34082s package, identifies the interfaces that signals are associated with, and provides an explanation of each signal.

### Chapter 3 Data Formats

Discusses the integer and floating-point operand formats accepted by the TMS34082.

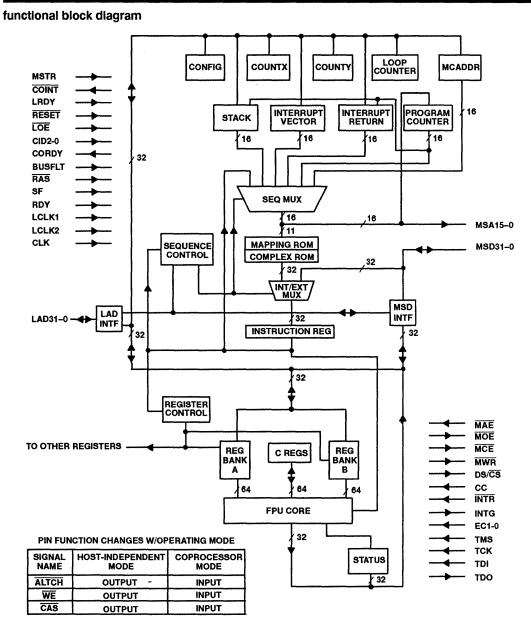

#### Chapter 4 Architecture

Describes the architectural elements of the TMS34082. Includes the bus interfaces, sequence control, registers, internal floating-point unit core, and test logic.

#### Chapter 5 Coprocessor Mode

Describes using the TMS34082 as a coprocessor to the TMS34020, including the hardware interface, recommended configurations, and example programs with timing diagrams.

#### Chapter 6 Host-Independent Mode

Provides information on using the TMS34082 as a stand-alone processor or a coprocessor to another host.

### Chapter 7 Internal Instructions

Shows how to use internal instructions in both coprocessor and host-independent mode. Explains the format and provides an alphabetical reference of the internal instruction set.

#### Chapter 8 External Instructions

Shows how to use external instructions in both coprocessor and host-independent mode. Explains the format and provides an alphabetical reference of the external instruction set.

#### Appendix A System Design Considerations

Provides recommendations on logic design, bypass capacitors, PWB design, and thermal considerations.

#### Appendix B TMS34082 Data Sheet

Contains the commercial data sheet for the TMS34082A.

#### Appendix C SMJ34082 Data Sheet

Contains the advance information military data sheet for the SMJ34082A.

## Appendix D Maximizing Your MFLOPS with the TMS34082 and Motorola MC68030

Contains an application note on interfacing the TMS34082 (in host-independent mode) to the Motorola MC68030.

## Appendix E A High-Performance Floating-Point Image Computing Workstation for Medical Applications

Contains an application note on an imaging system using a TMS34020 with four TMS34082 coprocessors.

### Appendix F Parallel Signal and Matrix Processing with the TMS34082

Contains an application note outlining and analyzing a TMS34082-based parallel architecture design.

## **Related Documentation**

The following documents are available from Texas Instruments. To obtain a copy of any of these TI documents, please call the Customer Response Center (CRC) at (800) 232-3200 unless otherwise noted. When ordering, please identify the book by its title and corresponding literature number.

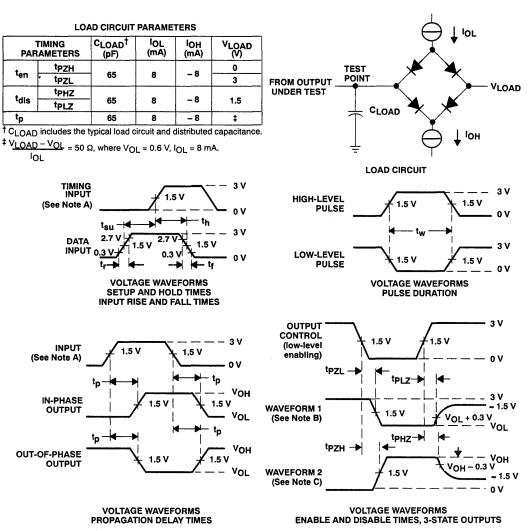

- **TMS34082A Data Sheet** (literature number SCGS001) is included in Appendix B of this book. It contains electrical specifications, timing information, and mechanical data for the TMS34082A.

- SMJ34082A Data Sheet (literature number SGUS012A) is included in Appendix C of this book. It contains electrical specifications, timing information, and mechanical data for the SMJ34082A.

- TMS34020 User's Guide (literature number SPVU019) discusses hardware aspects of the TMS34020, such as pin functions, architecture, stack operations, and interfaces. Contains the TMS34020 instruction set and interface to the TMS34082.

- **TMS34020 Data Sheet** (literature number SPVS004) contains electrical specifications, timing information, and mechanical data for the TMS34020.

- TMS34082 Software Tool Kit User's Guide describes the C compiler, assembler, linker, librarian, and simulator that are available for developing TMS34082 external instruction code. Call your TI sales representative for the demonstration version of the tool kit.

- TMS340 Family Code-Generation Tools User's Guide (literature number SPVU004) describes the C compiler, assembler, linker, archiver, and auxiliary tools that are available for developing TMS34010, TMS34020, or TMS34020/TMS34082 code.

- TMS34082 Assembly Support for Code-Generation Tools User's Guide (literature number SPVU029) summarizes the instruction code used with the TMS34082.

- **TIGA Interface User's Guide** (literature number SPVU015) describes the Texas Instruments Graphics Architecture (TIGA), a software interface that standardizes communication between application software and TMS340-based hardware for IBM-compatible PCs.

- TMS34082 3-D Graphics Library User's Guide describes an extensive array of C-callable functions including polygon clipping, shading, and vector and matrix operations. This library is TIGA-compatible and can also be used in non-TIGA applications. Call your TI sales representative or the DVP System Engineering Hotline for information on purchasing this product.

You may also find the following documentation useful. Many of the complex graphics instructions in the TMS34082 are based on algorithms found in this book:

Foley, James, and Andries van Dam. *Fundamentals of Interactive Computer Graphics*. Reading, Massachusetts: Addison-Wesley, 1982.

### Style and Symbol Conventions

This document uses the following conventions.

Program listings, program examples, filenames, and symbol names are shown in a special typeface similar to a typewriter's. Examples use a bold version of the special typeface for emphasis.

Here is a sample program listing:

| 0011 | 0005 | 0001 | .field 1, | 2 |

|------|------|------|-----------|---|

| 0012 | 0005 | 0003 | .field 3, | 4 |

| 0013 | 0005 | 0006 | .field 6, | 3 |

| 0014 | 0006 |      | .even     |   |

In syntax descriptions, the instruction is in a **bold** typeface font and parameters are in an *italic* typeface. Portions of a syntax that are in **bold** should be entered as shown; portions of a syntax that are in *italics* describe the type of information that should be entered. Here is an example of an instruction syntax:

#### NEGF CRs, CRd

This instruction has two parameters, indicated by *CRs* and *CRd*. When you use NEGF, the parameters must be actual TMS34082 registers, such as RA9 and RB1.

Square brackets ([ and ] ) identify an optional parameter. If you use an optional parameter, you specify the information within the brackets; you don't enter the brackets themselves. Here's an example of an instruction that has an optional parameter:

### MOVD +Rs+, CRd [, count]

The MOVD instruction has three parameters. The first two parameters, *Rs* and *CRd*, are required. The third parameter, *count*, is optional. As this syntax shows, if you use the optional third parameter, you must precede it with a comma.

In the internal instruction set listings, Rs and Rd refer to TMS34020 source and destination registers, respectively. CRs and CRd refer to coprocessor or TMS34082 registers.

## Trademarks

EPIC, SCOPE, and TIGA are trademarks of Texas Instruments Incorporated.

IBM, PC-DOS, and PC/AT are trademarks of International Business Machines, Inc.

MS-DOS is a trademark of Microsoft Corporation.

NeXT is a trademark of NeXT, INC.

PAL is a registered trademark of Monolithic Memories, Inc.

X Windows Systems is a trademark of the Massachusetts Institute of technology.

## If You Need Assistance . . .

| If you want to                                                           | Do this                                                                                                                                                  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive more information<br>about TI floating-point products             | Call the CRC Hot Line:<br>(800) 232-3200                                                                                                                 |

|                                                                          | Or write to:<br>Texas Instruments Incorporated<br>Datapath VLSI Products<br>Marketing Communications<br>P.O. Box 655303, M/S 8316<br>Dallas, Texas 75265 |

| Order TI documentation                                                   | Call the CRC Hot Line:<br>(800) 232-3200                                                                                                                 |

| Ask questions about product<br>operation or report suspected<br>problems | Call DVP Systems Engineering<br>Hot Line:<br>(214) 997-3970                                                                                              |

| Inquiries related to this document:                                      | Write to:<br>Texas Instruments Incorporated<br>Datapath VLSI Products<br>Marketing Communications<br>P.O. Box 655303, M/S 8316<br>Dallas, Texas 75265    |

### **Contents**

0000000

| 1 | Over  | view of the TMS34082 1-1                                                                                            |

|---|-------|---------------------------------------------------------------------------------------------------------------------|

|   | 1.1   | TMS34082 Key Features 1-2                                                                                           |

|   | 1.2   | Performance Benchmarks 1-3                                                                                          |

|   | 1.3   | TMS34082 General Description 1-4                                                                                    |

|   | 1.4   | Typical Applications 1-9                                                                                            |

|   | 1.5   | Development Tools 1-11                                                                                              |

|   |       | 1.5.1 TMS34082 Software Tool Kit 1-11                                                                               |

|   |       | 1.5.2 TMS34082 3-D Graphics Library 1-12                                                                            |

|   |       | 1.5.3 TMS34082 Demonstration Board 1-13                                                                             |

|   | 1.6   | TMS34020 Graphics System Processor 1-14                                                                             |

|   |       | 1.6.1 TMS34020 Key Features 1-14                                                                                    |

|   |       | 1.6.2 TMS34020 Software Tools 1-17                                                                                  |

|   |       | 1.6.3 TIGA Graphics Interface 1-19                                                                                  |

|   |       | 1.6.4 TMS34020 Software Development Board 1-20                                                                      |

|   | 1.7   | TMS34082 Ordering Information 1-21                                                                                  |

|   | 1.8   | Technical Assistance                                                                                                |

| 2 | Pinor | It and Pin Descriptions                                                                                             |

|   | 2.1   | Pinout                                                                                                              |

|   | 2.2   | Pin Functional Descriptions                                                                                         |

| _ |       |                                                                                                                     |

| 3 |       | Formats                                                                                                             |

|   | 3.1   |                                                                                                                     |

|   |       | 3.1.1 Signed Integers                                                                                               |

|   |       | 3.1.2 Unsigned Integer                                                                                              |

|   | 3.2   | Floating-Point Formats3-33.2.1Single-Precision Floating-Point3-3                                                    |

|   |       | 3.2.1       Single-Precision Floating-Point       3-3         3.2.2       Double-Precision Floating-Point       3-3 |

|   |       | 3.2.3 Denormal and Wrapped Numbers                                                                                  |

|   |       | 3.2.4 Special Floating-Point Numbers                                                                                |

|   |       | 3.2.5 Range of Floating-Point Numbers                                                                               |

|   |       | 5.2.5 Range of Floating-Foint Numbers                                                                               |

| 4 | Archi | itecture                                                                                                            |

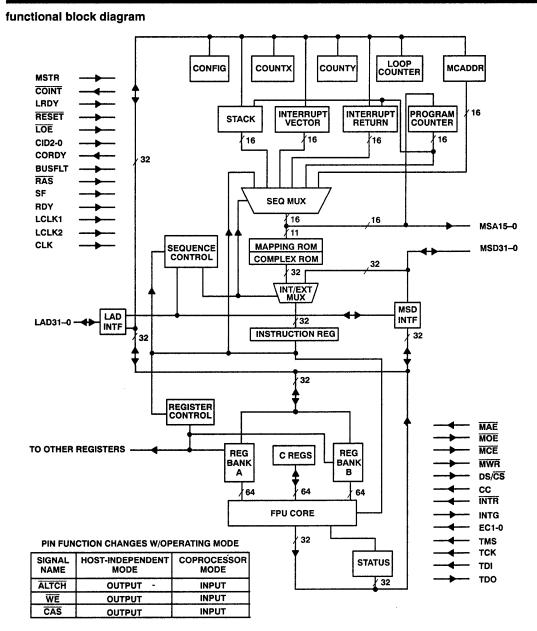

|   | 4.1   | Functional Block Diagram 4-2                                                                                        |

|   | 4.2   | Operating Modes 4-3                                                                                                 |

|   | 4.3   | Bus Interfaces 4-4                                                                                                  |

|   |       |                                                                                                                     |

|   |     | 4.3.1    | LAD Bus                                        | 4-4  |

|---|-----|----------|------------------------------------------------|------|

|   |     | 4.3.2    | MSD Bus                                        | 4-5  |

|   | 4.4 | Sequer   | nce Control                                    | 4-7  |

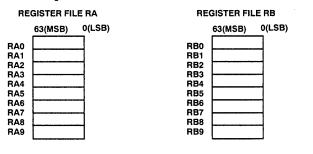

|   | 4.5 | Registe  | ers                                            | 4-8  |

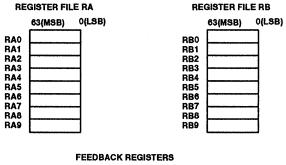

|   |     | 4.5.1    | Register Files RA and RB 4                     | 1-11 |

|   |     | 4.5.2    | Feedback Registers C and CT 4                  | -12  |

|   |     | 4.5.3    | Configuration Register (CONFIG) 4              | -13  |

|   |     | 4.5.4    | Status Register 4                              | -19  |

|   |     | 4.5.5    | Indirect Address Register 4                    | -22  |

|   |     | 4.5.6    | Stack                                          |      |

|   |     | 4.5.7    | Interrupt Vector Register                      | 1-23 |

|   |     | 4.5.8    | Interrupt Return Register 4                    |      |

|   |     | 4.5.9    | COUNTX and COUNTY Registers                    |      |

|   |     | 4.5.10   | MIN-MAX/LOOPCT Register 4                      |      |

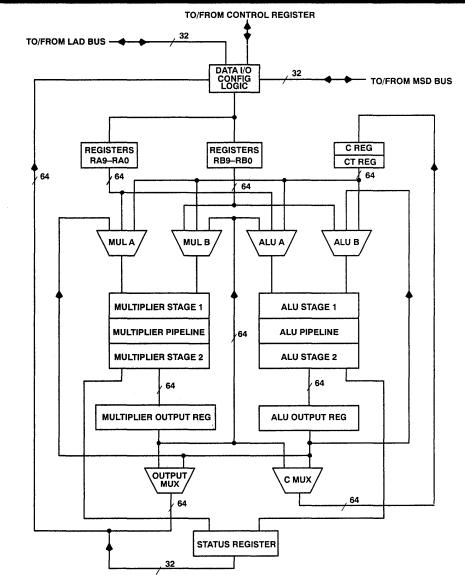

|   | 4.6 |          | ore                                            |      |

|   |     | 4.6.1    | Operand Selection                              |      |

|   |     | 4.6.2    | Pipeline Registers                             |      |

|   |     | 4.6.3    | ALU                                            |      |

|   |     | 4.6.4    | Multiplier                                     |      |

|   |     | 4.6.5    | Output Control                                 |      |

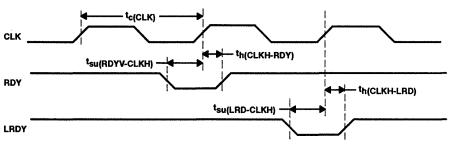

|   | 4.7 |          | and RDY                                        |      |

|   | 4.8 |          | ion Control                                    |      |

|   | 4.9 |          | Fest Port                                      |      |

|   |     | 4.9,1    | Test Instructions                              |      |

|   |     | 4.9.2    | Boundary Scan Register                         |      |

|   |     |          |                                                |      |

| 5 | •   |          | Mode                                           |      |

|   | 5.1 |          | 020/TMS34082 Interface Overview                |      |

|   | 5.2 |          |                                                |      |

|   | 5.3 | TMS34    | 082 Initialization                             | 5-4  |

|   | 5.4 | Configu  | uration Register Settings for Coprocessor Mode | 5-5  |

|   |     | 5.4.1    | Exception Masks                                |      |

|   |     | 5.4.2    | Fast vs IEEE Mode                              | 5-5  |

|   |     | 5.4.3    | Pipeline Mode Settings                         |      |

|   | 5.5 | TMS34    | 020/TMS34082 LAD Bus Operation                 |      |

|   |     | 5.5.1    | LAD Bus Protocol                               | 5-7  |

|   |     | 5.5.2    | Enabling the LAD Bus Drivers 5                 | 5-12 |

|   |     | 5.5.3    | Bus Faults                                     | 5-12 |

|   | 5.6 | Polling  | the Coprocessor 5                              | 5-14 |

|   | 5.7 | Interrup | ot Handling                                    | 5-15 |

|   |     | 5.7.1    | Exception Detect Interrupts 5                  | 5-15 |

|   |     | 5.7.2    | Software Interrupts 5                          | 5-16 |

|   |     | 5.7.3    | Interrupting the TMS34020 5                    | 5-16 |

|   | 5.8 | TMS34    | 020/TMS34082 Code Example 5                    | 5-18 |

|   |     |          |                                                |      |

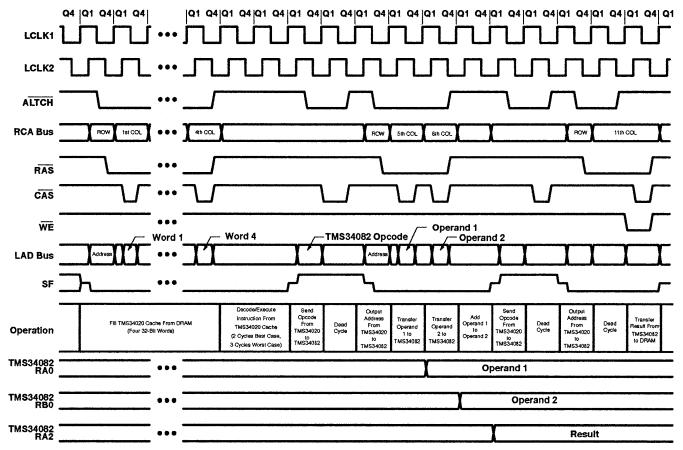

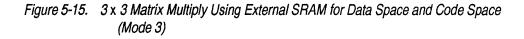

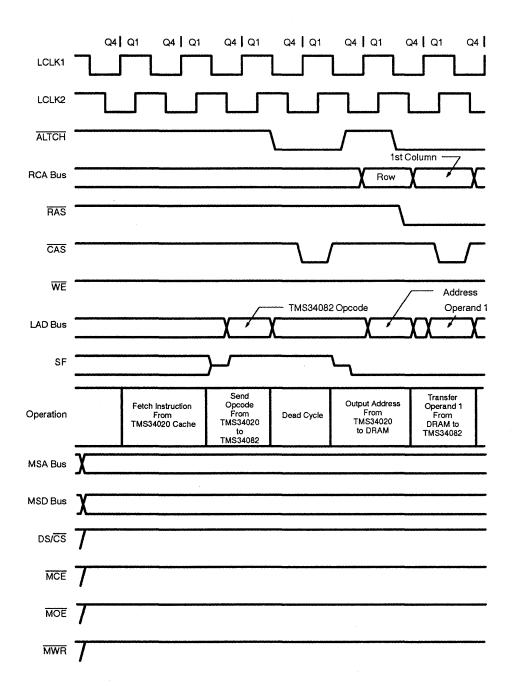

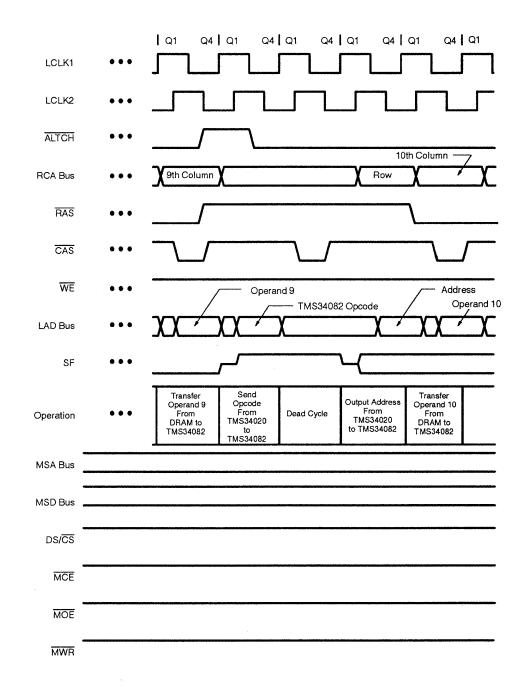

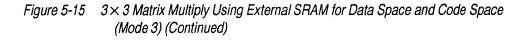

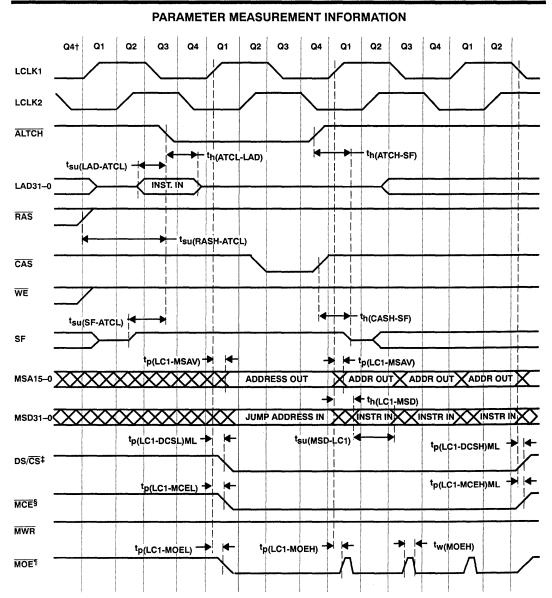

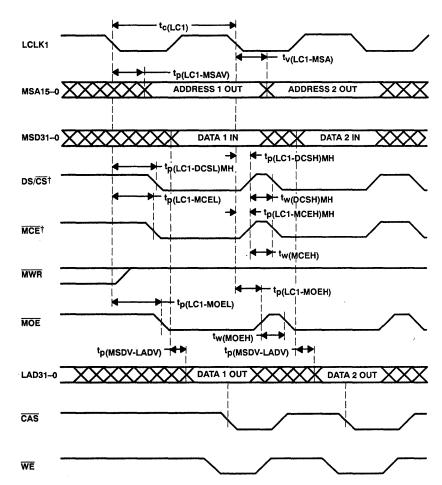

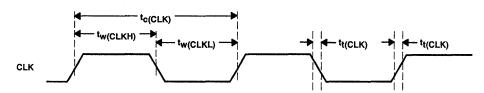

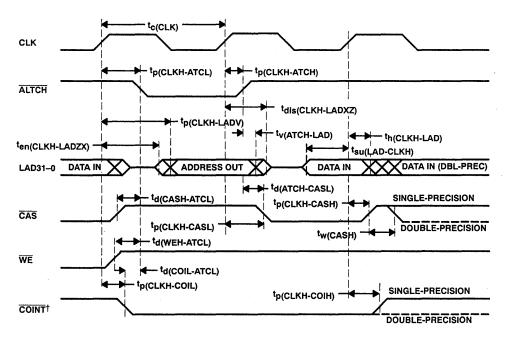

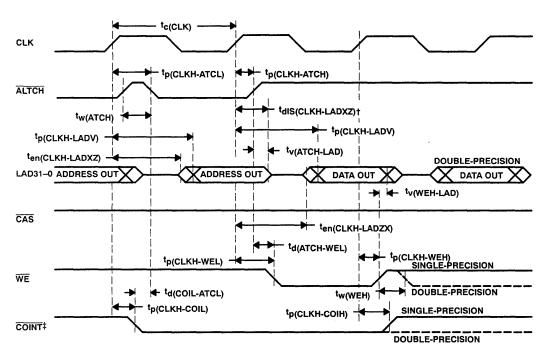

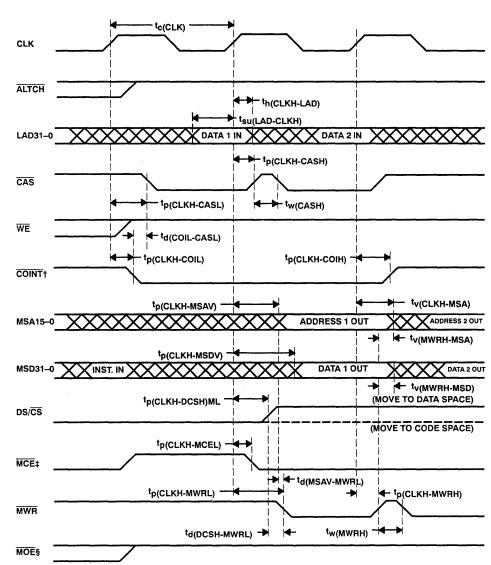

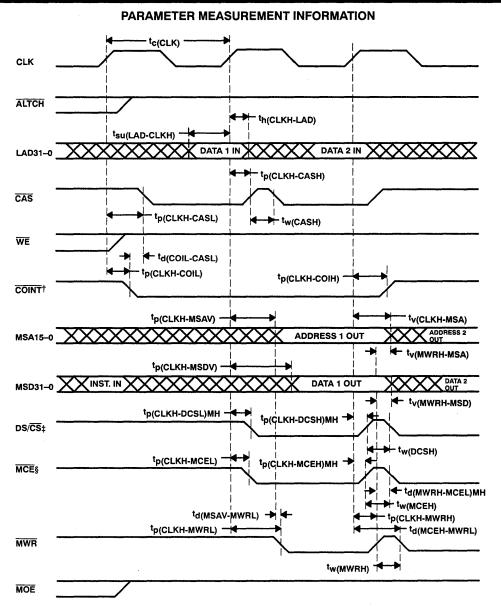

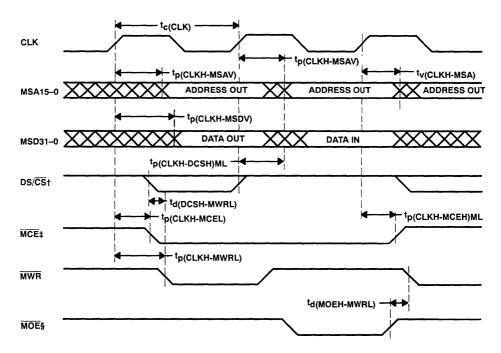

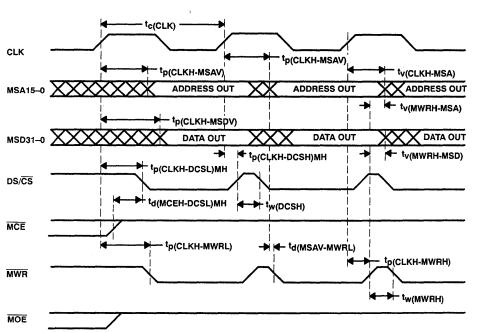

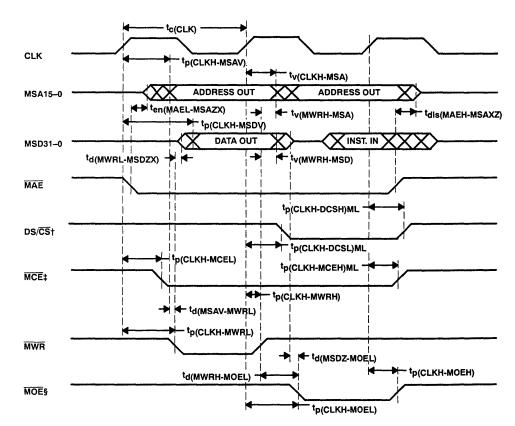

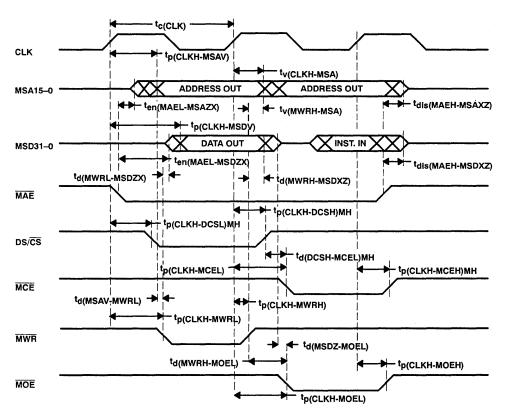

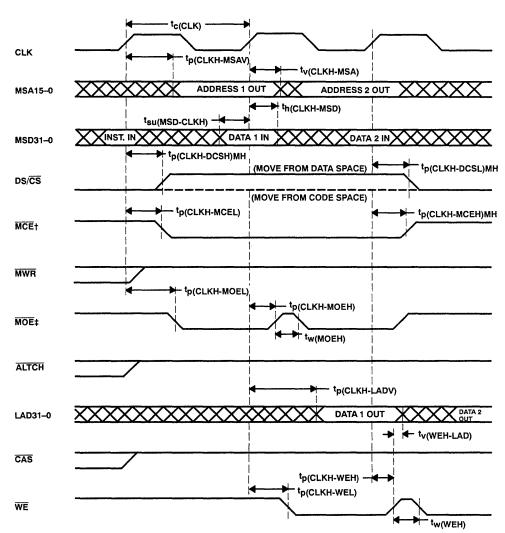

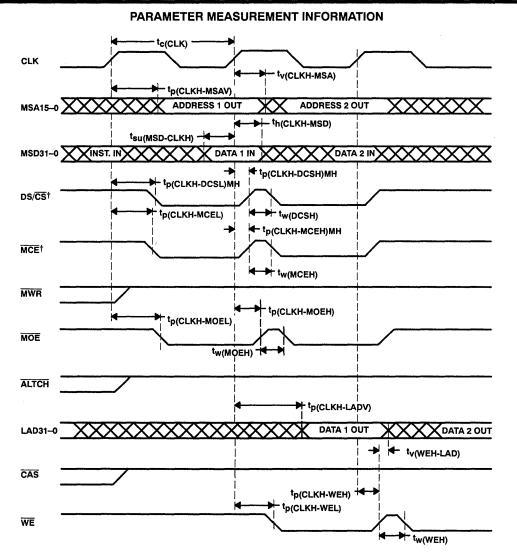

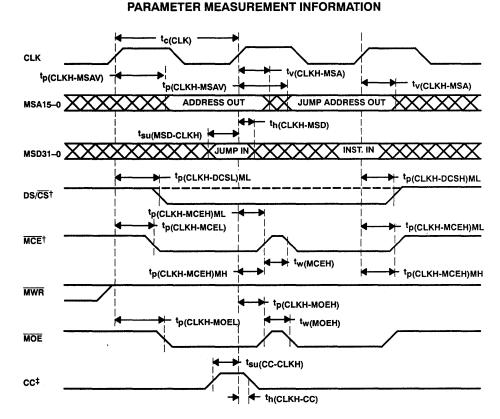

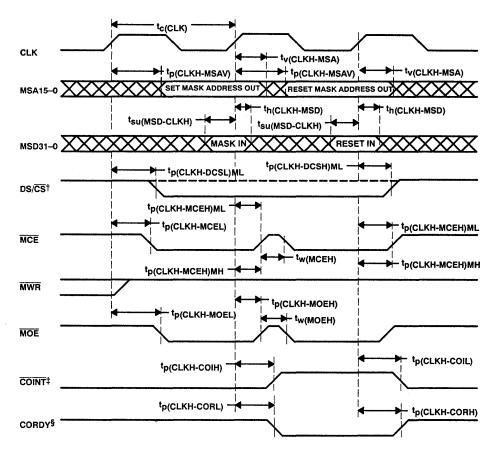

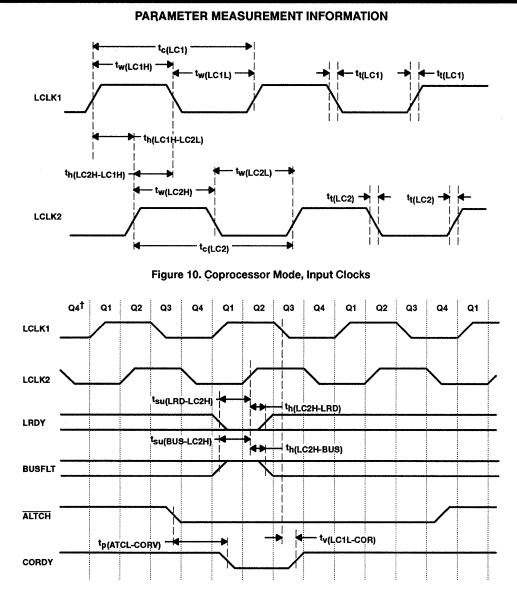

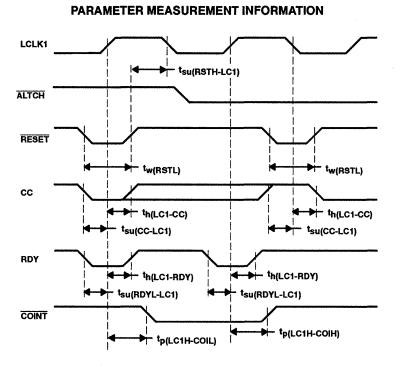

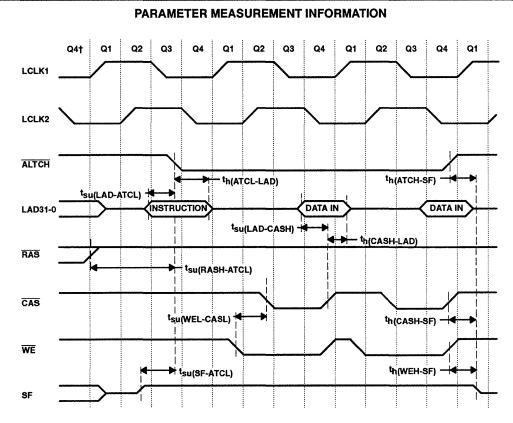

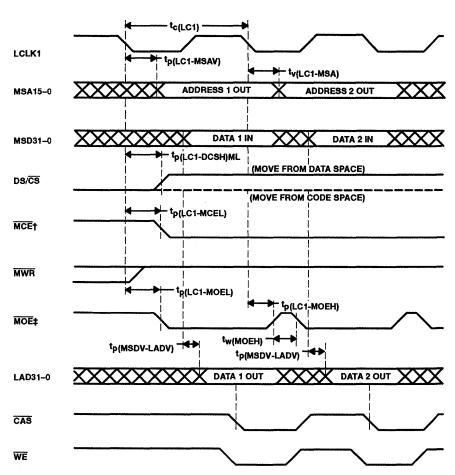

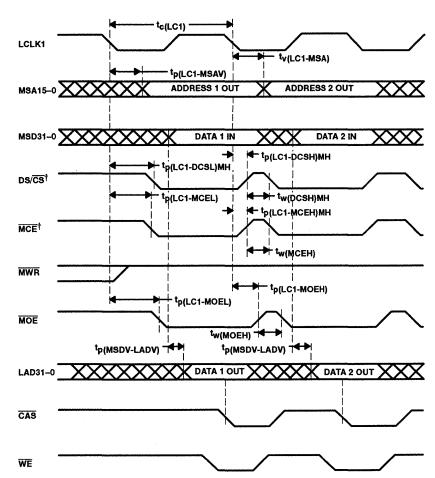

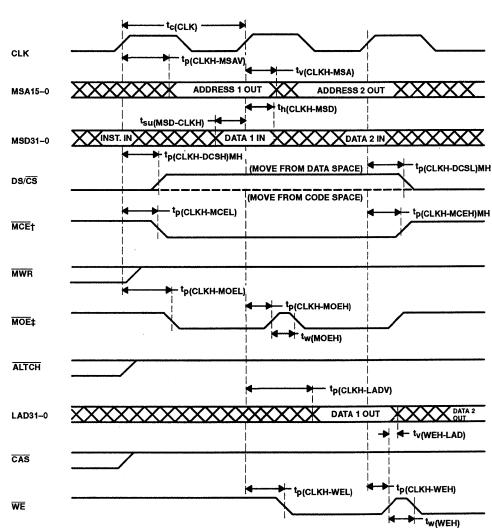

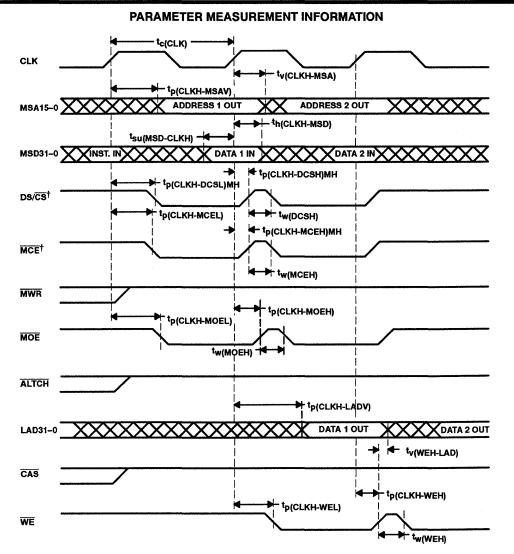

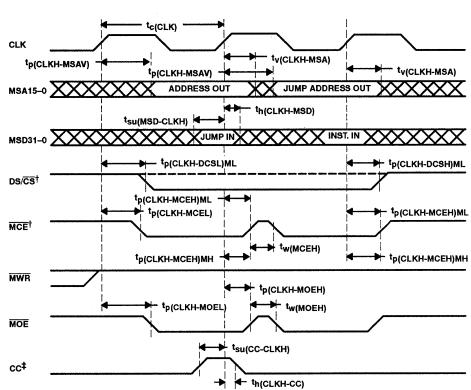

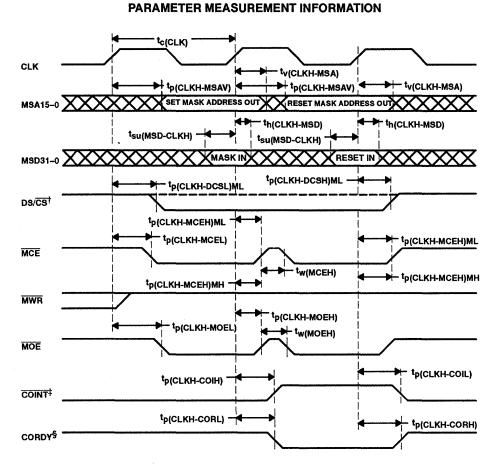

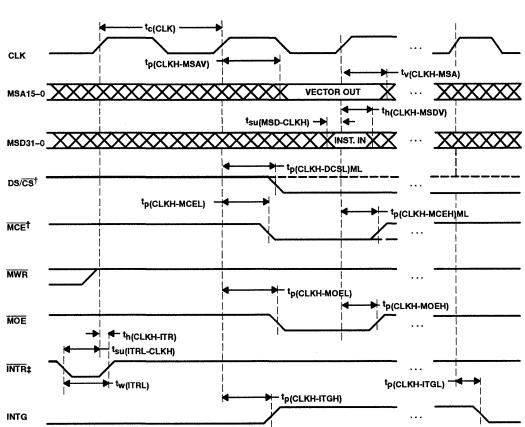

|   | 5.9    | TMS34     | 020/TMS34082 Timing Examples           | 5-20 |

|---|--------|-----------|----------------------------------------|------|

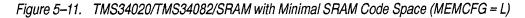

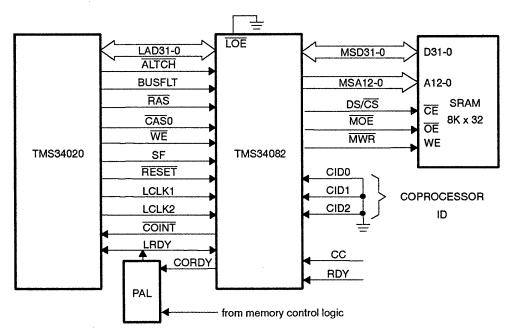

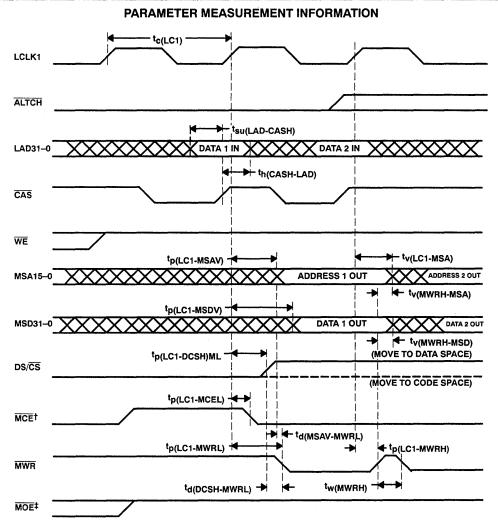

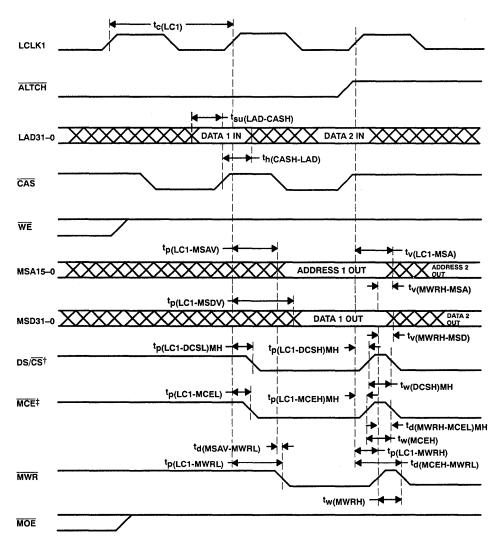

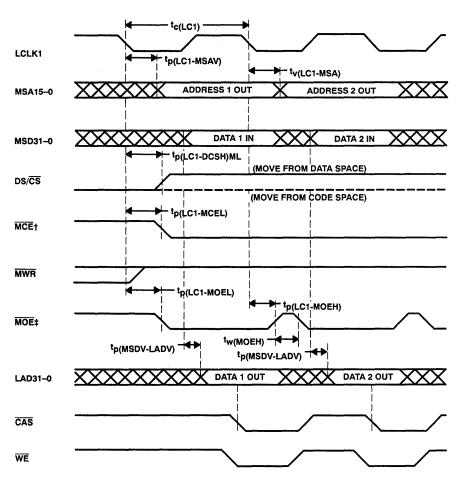

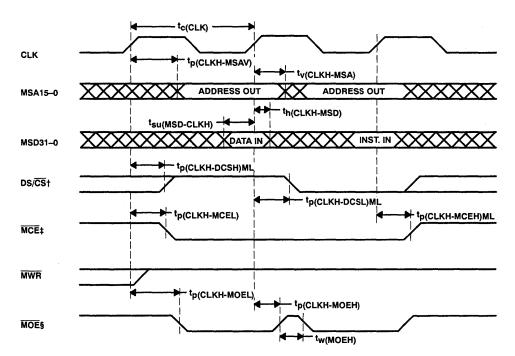

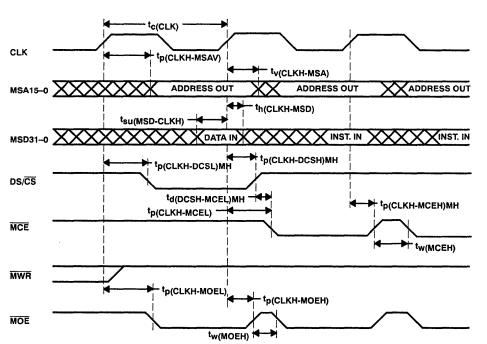

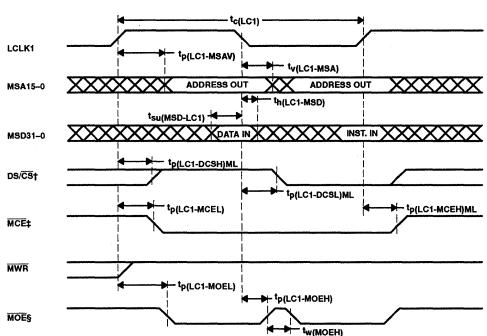

|   | 5.10   | MSD B     | us Operation in Coprocessor Mode       | 5-24 |

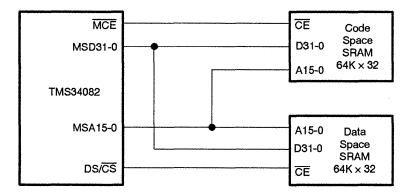

|   |        | 5.10.1    | Connecting External Memory             | 5-24 |

|   |        | 5.10.2    | TMS34082 External SRAM Timing Analysis | 5-25 |

|   |        | 5.10.3    | Using External Code                    | 5-26 |

|   | 5.11   | TMS34     | 020/TMS34082/SRAM Code Example         | 5-28 |

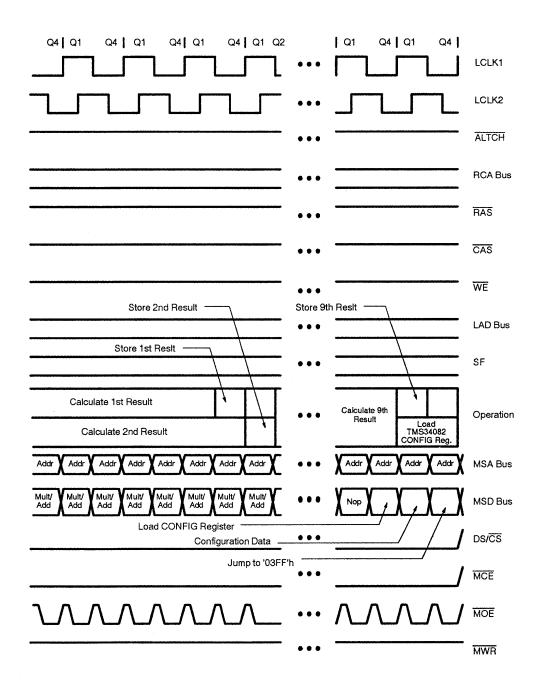

|   | 5.12   |           | e TMS34082s                            |      |

| 6 | Host-  | Indeper   | ndent Mode                             | 6-1  |

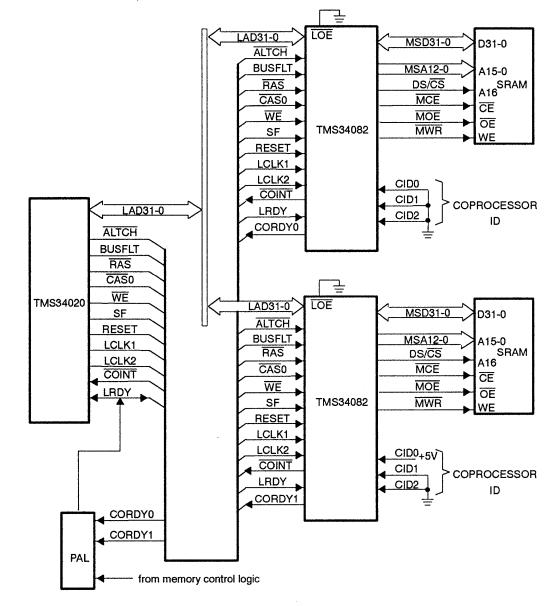

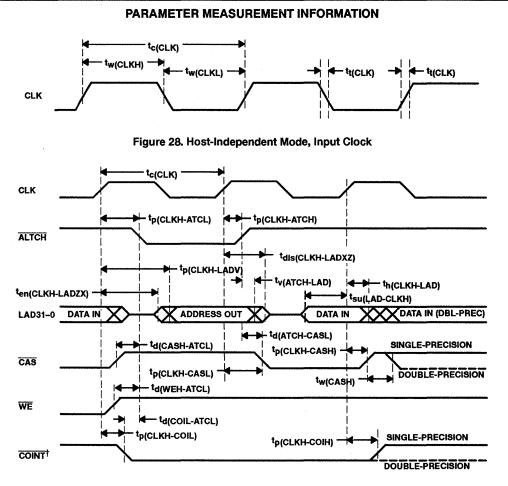

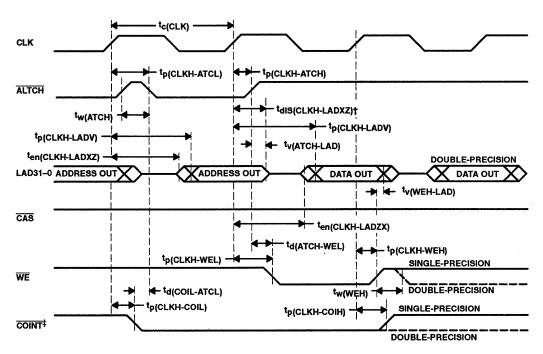

| Ŭ | 6.1    | •         | ation                                  |      |

|   | 0.1    | 6.1.1     | Pin Connections                        |      |

|   |        | 6.1.2     | Bootstrap Loader                       |      |

|   | 6.2    |           | JS                                     |      |

|   | 0.2    | 6.2.1     | Control Signals                        |      |

|   |        | 6.2.2     | Immediate Data Transfers               |      |

|   | 6.3    |           |                                        |      |

|   | 0.0    | 6.3.1     | MSD Bus Control Signals                |      |

|   |        | 6.3.2     | Memory Models                          |      |

|   | 6.4    |           |                                        |      |

|   | 6.5    |           | ates                                   |      |

|   | 6.6    |           | rogrammable Outputs                    |      |

|   | 6.7    |           | onal Code Input                        |      |

|   | 6.8    |           | onal Gode Input                        |      |

|   | 0.0    | 6.8.1     |                                        |      |

|   |        |           | Hardware Interrupts                    |      |

|   |        | 6.8.2     | Software Interrupts                    |      |

|   |        | 6.8.3     | Exception Detect Interrupts            | 0-11 |

| 7 | Intern | nal Instr | uctions                                | 7-1  |

|   | 7.1    |           | I Instructions Overview                |      |

|   | 7.2    | Comple    | ex Graphics Instructions               | 7-4  |

|   | 7.3    |           | I Routine Addresses and Cycle Counts   |      |

|   | 7.4    | Coproc    | essor Mode Internal Instruction Format | 7-14 |

|   |        | 7.4.1     | Coprocessor ID Field                   | 7-14 |

|   |        | 7.4.2     | Register Field                         | 7-14 |

|   |        | 7.4.3     | Addressing Mode Field                  | 7-15 |

|   |        | 7.4.4     | FPU Operation Field                    | 7-15 |

|   | 7.5    | Type, S   | Size, and I Fields                     | 7-16 |

|   | 7.6    | Interna   | Instruction Opcodes                    | 7-17 |

| 8 | Exter  | nal Inst  | ructions                               | 8-1  |

| - | 8.1    |           | ЭШ                                     |      |

|   | 8.2    |           | ocessing Instruction Format            |      |

|   |        | 8.2.1     | FPU Processing Sequencer Opcodes       |      |

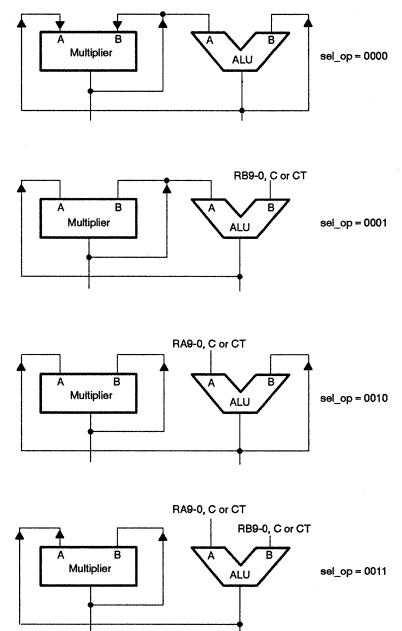

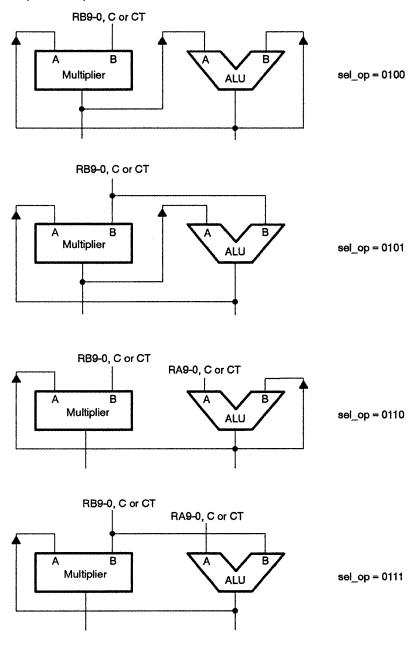

|   |        | 8.2.2     | Operand Selection                      |      |

|   |        |           | · · · · · · · · · · · · · · · · · · ·  |      |

\*\*\*\*\*\*

\*\*\*\*\*

|   | 8.3<br>8.4 | 8.2.3 FPU Processing Instruction Codes                    |      |

|---|------------|-----------------------------------------------------------|------|

|   | 8.5        | External Assembly Instructions                            |      |

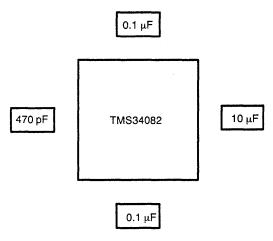

| Α | Syste      | em Design Considerations                                  | A-1  |

|   | A.1        | Logic Design                                              |      |

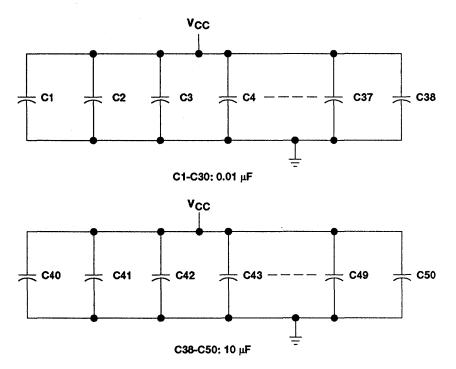

|   | A.2        | Bypass Capacitors                                         |      |

|   | A.3        | PWB Design                                                |      |

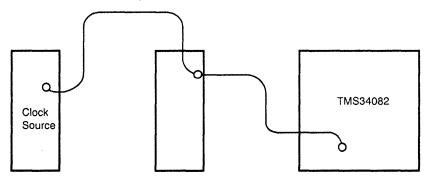

|   | A.4        | Clock Routing                                             |      |

|   | A.5        | Thermal Considerations                                    | A-6  |

| В | TMS        | 34082A Data Sheet                                         | B-1  |

| С | SMJ3       | 34082A Data Sheet                                         | C-1  |

| D | Maxi       | mizing Your MFLOPS with the TMS34082 and Motorola MC68030 | D-1  |

|   | Oven       | view ,                                                    |      |

|   |            | Objectives                                                |      |

|   |            | TMS34082 Overview                                         |      |

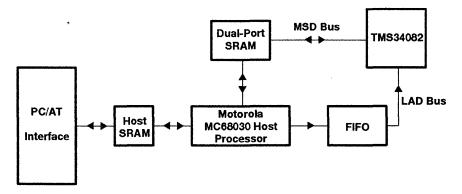

|   | Syste      | m Architecture                                            |      |

|   |            | System Overview                                           |      |

|   |            | Objectives and Trade-Offs                                 |      |

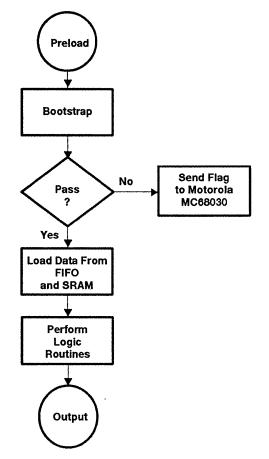

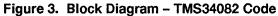

|   | Softw      | vare Description                                          |      |

|   |            | Overview of Code Development                              |      |

|   |            | Big Endian, Little Endian                                 |      |

|   |            | TMS34082 Code Development                                 |      |

|   |            | Motorola MC68030 Code Development                         |      |

|   | Lord       | Intel 80286 Code Development                              |      |

|   | naju       | Overview                                                  |      |

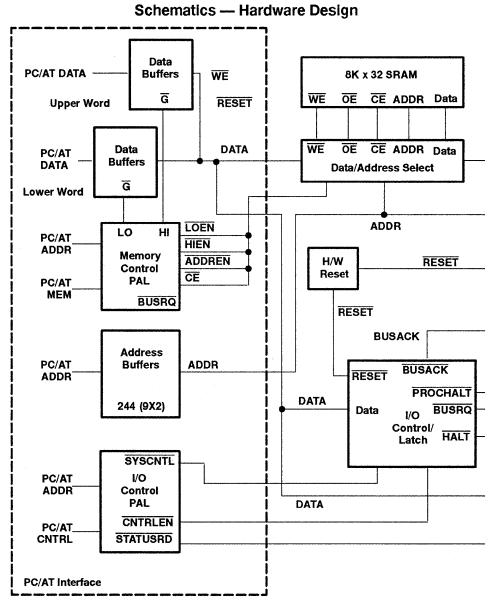

|   |            | PC/AT Interface                                           |      |

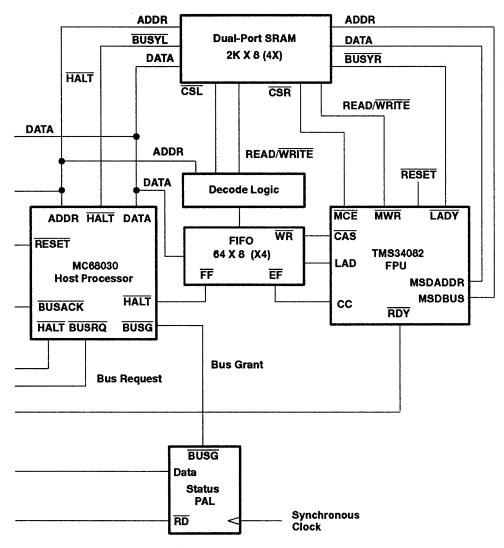

|   |            | Host Processor Interface                                  |      |

|   |            | TMS34082 as a Parallel Processor                          |      |

|   | Perfo      | mance Analysis                                            |      |

|   |            | em Information — Parts List                               |      |

|   |            | matics — Hardware Design                                  |      |

|   |            | Code Listing                                              |      |

|   |            | Memory Decode for TMS34082 Accelerator Board              |      |

|   |            | I/O Decode for TMS34082 Accelerator Board                 |      |

|   |            | Status Control for TMS34082 Accelerator Board             |      |

|   |            | Byte Enable Decode for TMS34082 Accelerator Board         |      |

|   |            | Pattern Decode for TMS34082 Accelerator Board             |      |

|   | Softw      | vare Listings                                             | D-47 |

|   | Refe       | rences                                                    | D-47 |

| Ε | A High Performance Floating-Point Image Computing Workstation for |      |

|---|-------------------------------------------------------------------|------|

|   | Abstract                                                          |      |

|   | Abstract                                                          |      |

|   | Introduction                                                      |      |

|   | Background                                                        |      |

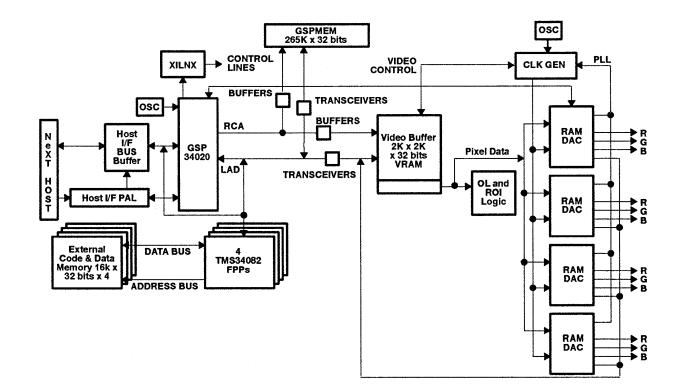

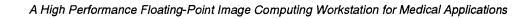

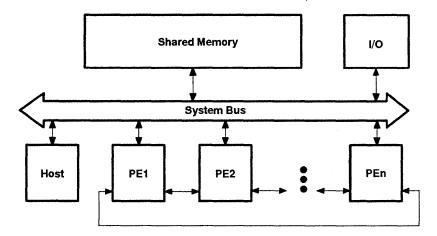

|   | System Architecture                                               |      |

|   | NeXT <sup>™</sup> Host System and Interface Logic                 | E-6  |

|   | Processors                                                        | E-8  |

|   | Memory                                                            | E-9  |

|   | Video Display                                                     | E-9  |

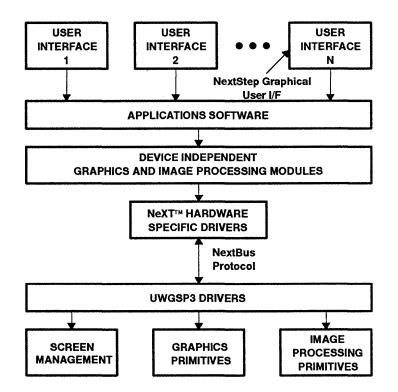

|   | Software Architecture                                             | E-10 |

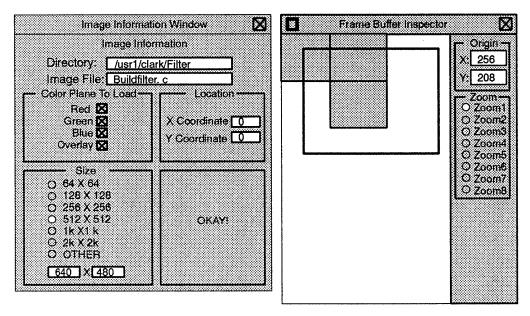

|   | Application Areas                                                 | E-12 |

|   | PACS Workstation                                                  | E-12 |

|   | Electronic Alternator                                             | E-13 |

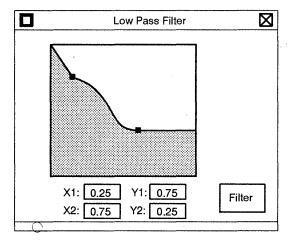

|   | Image Processing and Graphics                                     |      |

|   | Conclusion                                                        |      |

|   | Acknowledgements                                                  |      |

|   | References                                                        |      |

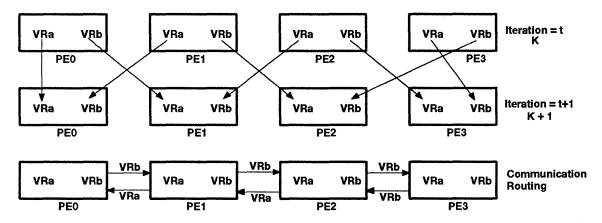

| F | Parallel Signal and Matrix Processing with the TMS34082           | F-1  |

|   | Introduction                                                      | F-3  |

|   | The HARP Architecture                                             |      |

|   | TMS34082 Host-Independent Mode Optimizations                      | F-8  |

|   | Algorithms                                                        |      |

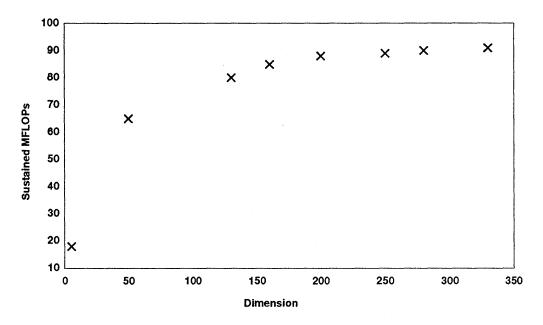

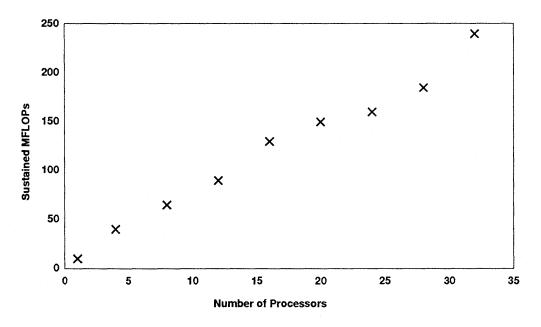

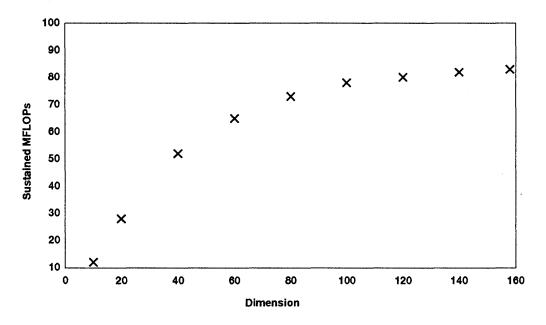

|   | Simulation Results and Performance Analysis                       |      |

|   | Conclusion                                                        |      |

|   | Bibliography                                                      |      |

## Figures

| Figure 1–1.  | TMS34082 High-Level Block Diagram 1-4                              |

|--------------|--------------------------------------------------------------------|

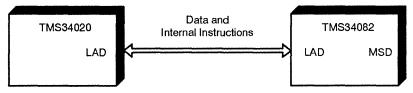

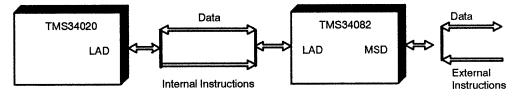

| Figure 1–2.  | Coprocessor Mode Bus Architectures 1-7                             |

| Figure 1-3.  | Host-Independent Mode Bus Architectures 1-8                        |

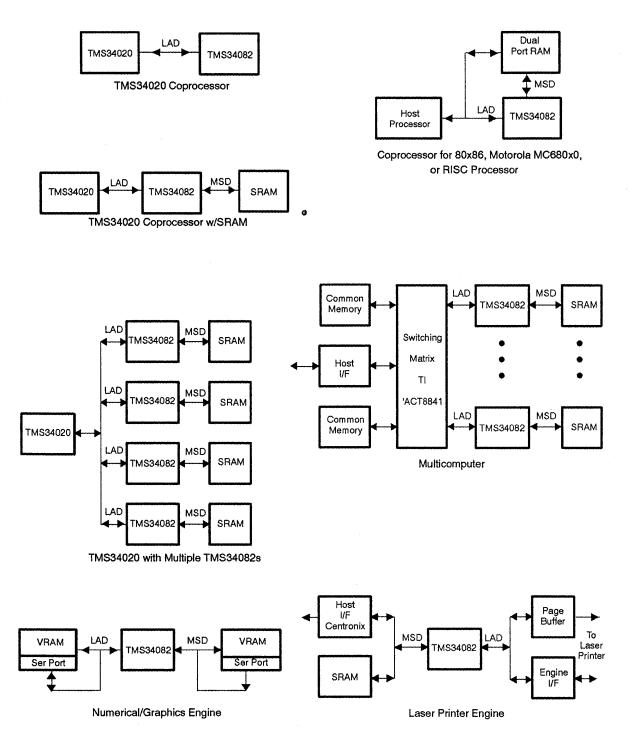

| Figure 1–4.  | Sample TMS34082 Architectures 1-10                                 |

| Figure 1–5.  | Overview of TMS34082 Code-Generation Tools 1-11                    |

| Figure 1–6.  | TMS34082 Demonstration Board Block Diagram 1-13                    |

| Figure 1–7.  | TMS34020 High-Level Block Diagram 1-15                             |

| Figure 1–8.  | TMS34020 and TMS34082 Software Tools 1-18                          |

| Figure 1–9.  | Graphics Processing Shared Between TMS340 and Host Processors 1-19 |

| Figure 1-10. | TMS34020 SDB Block Diagram 1-20                                    |

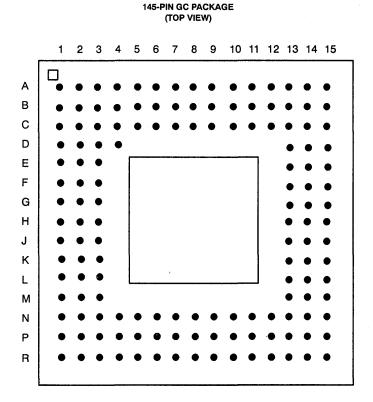

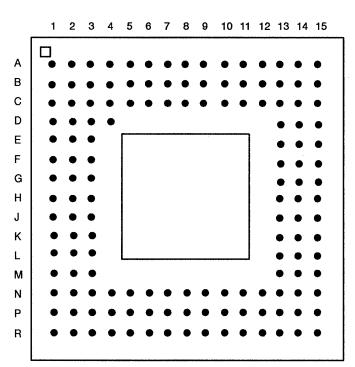

| Figure 2–1.  | TMS34082 Pinout, 145-Pin PGA Package 2-2                           |

| Figure 3–1.  | IEEE Signed Integer Format 3-2                                     |

| Figure 3–2.  | IEEE Unsigned Integer Format 3-2                                   |

| Figure 3–3.  | IEEE Single-Precision Format 3-3                                   |

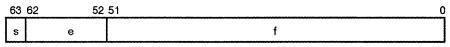

| Figure 3-4.  | IEEE Double-Precision Format                                       |

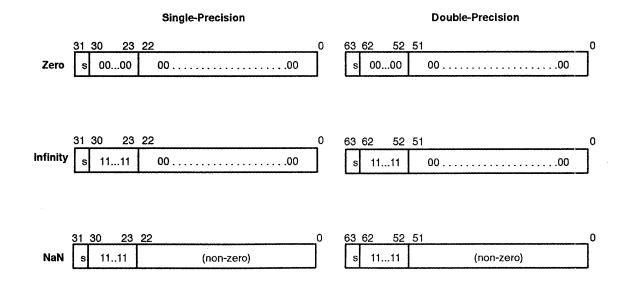

| Figure 3–5.  | Special Floating-Point Formats 3-5                                 |

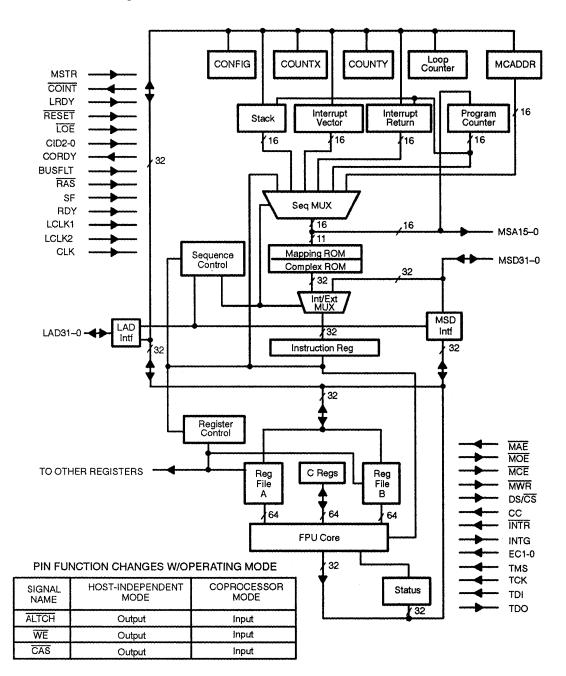

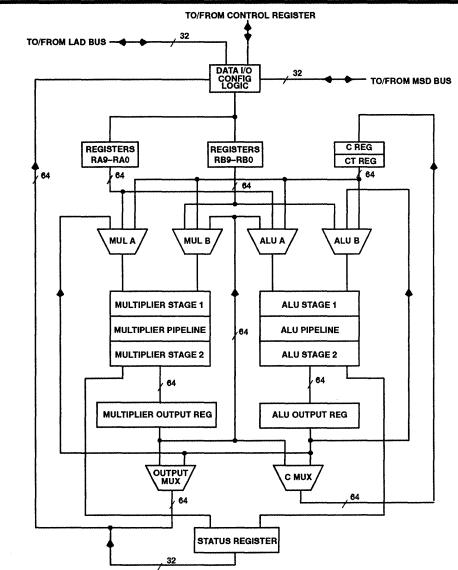

| Figure 4–1.  | Functional Block Diagram 4-2                                       |

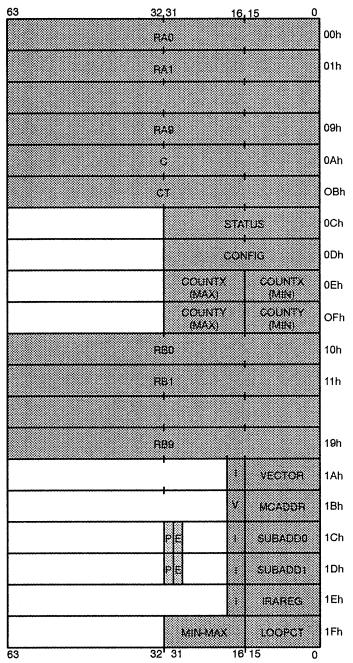

| Figure 4–2.  | Register Usage                                                     |

| Figure 4–3.  | TMS34082 Register Model 4-9                                        |

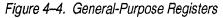

| Figure 4–4.  | General-Purpose Registers 4-11                                     |

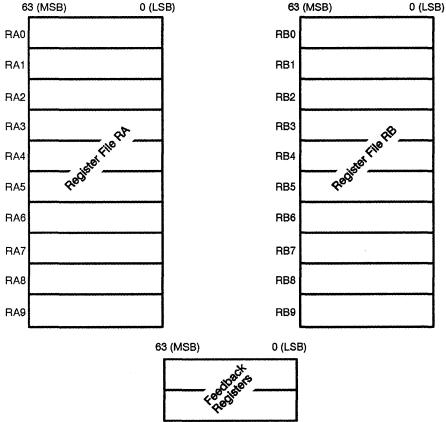

| Figure 4–5.  | Register Files with ONEFILE High 4-12                              |

| Figure 4–6.  | Host-Independent Mode LAD Bus Configuration for LADCFG High 4-15   |

| Figure 4-7.  | MSD Bus Configuration for MEMCFG Low 4-16                          |

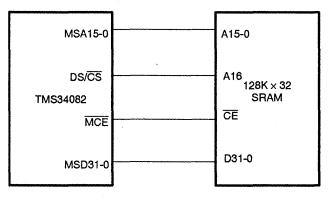

| Figure 4–8.  | MSD Bus Configuration for MEMCFG High 4-16                         |

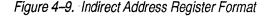

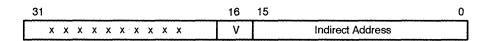

| Figure 4–9.  | Indirect Address Register Format 4-22                              |

| Figure 4-10. | Stack Register Format 4-23                                         |

| Figure 4-11. | Interrupt Vector Register Format 4-23                              |

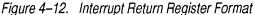

| Figure 4-12. | Interrupt Return Register Format 4-23                              |

| Figure 4–13. | COUNT Registers Format 4-24                                        |

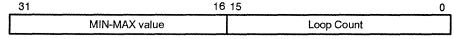

| Figure 4-14. | MIN-MAX/LOOPCT Register Format                                     |

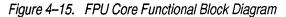

| Figure 4-15. | FPU Core Functional Block Diagram                                                                                   | 4-26 |

|--------------|---------------------------------------------------------------------------------------------------------------------|------|

| Figure 4-16. | Effects of Pipelining                                                                                               | 4-28 |

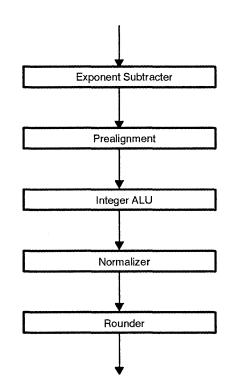

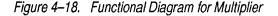

| Figure 4-17. | Functional Diagram for ALU                                                                                          | 4-29 |

| Figure 4-18. | Functional Diagram for Multiplier                                                                                   | 4-30 |

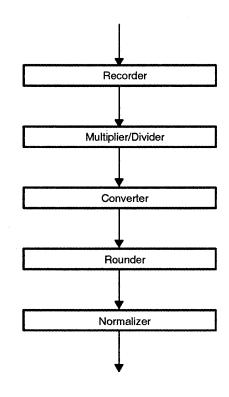

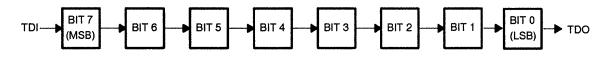

| Figure 4-19. | Instruction Register Order of Scan                                                                                  | 4-34 |

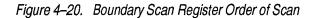

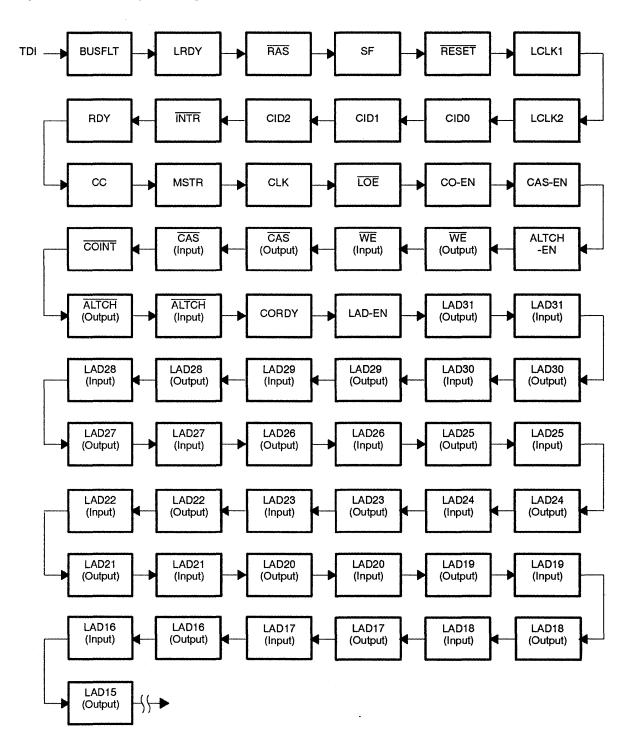

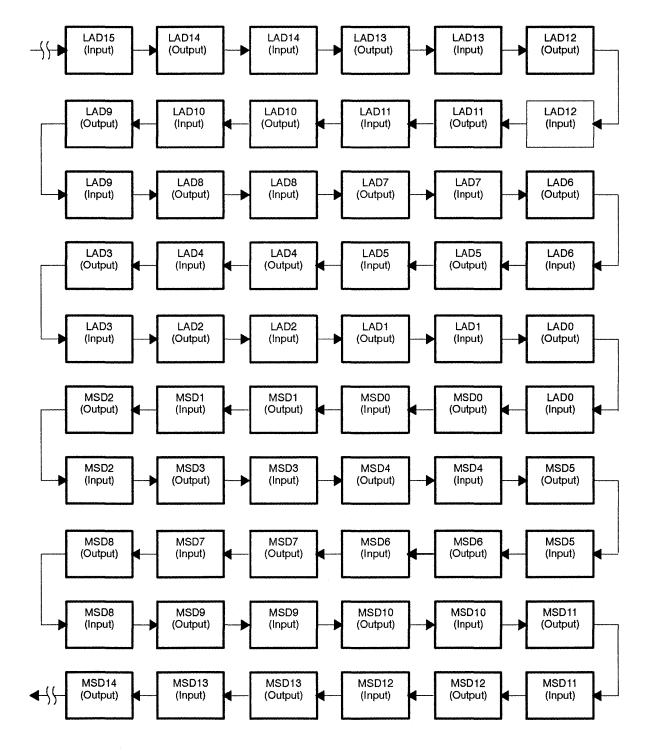

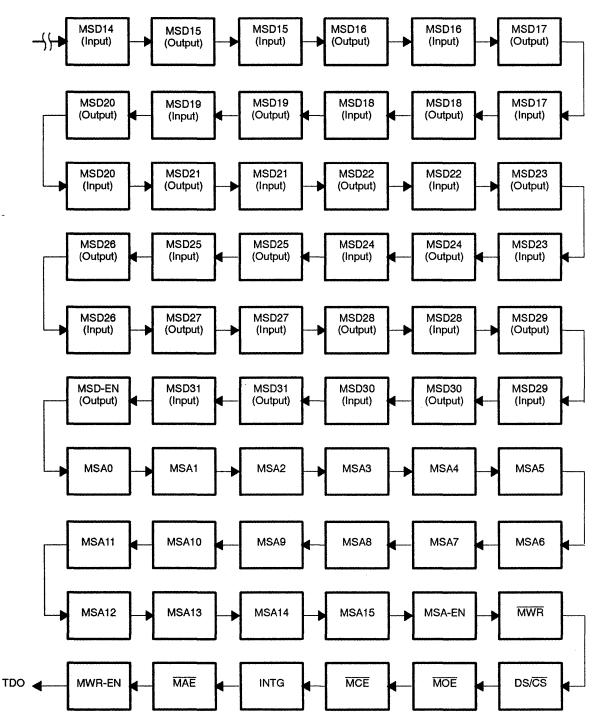

| Figure 4-20. | Boundary Scan Register Order of Scan                                                                                | 4-36 |

| Figure 5-1.  | TMS3402/TMS34082 Register Model                                                                                     | 5-2  |

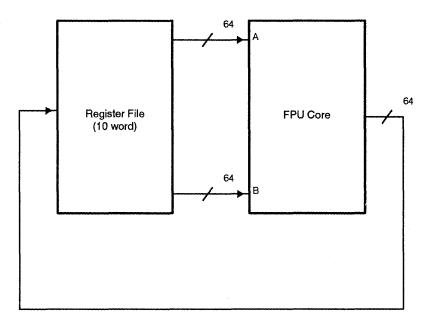

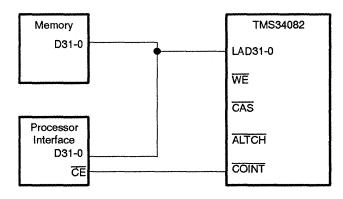

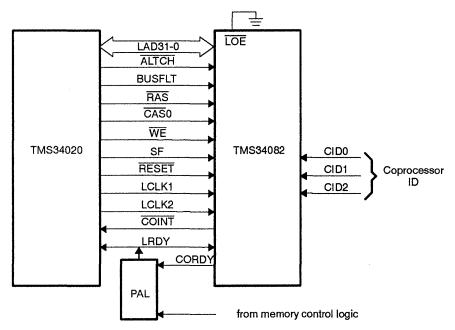

| Figure 5-2.  | TMS34020/TMS34082 Interconnection                                                                                   | 5-3  |

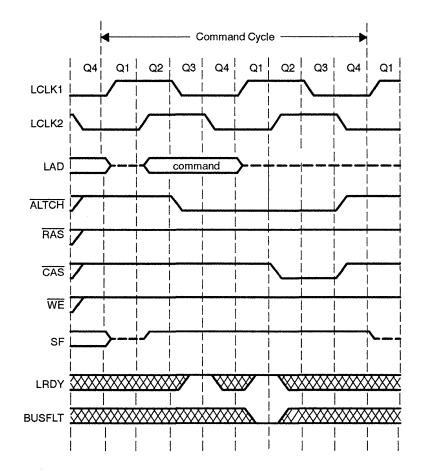

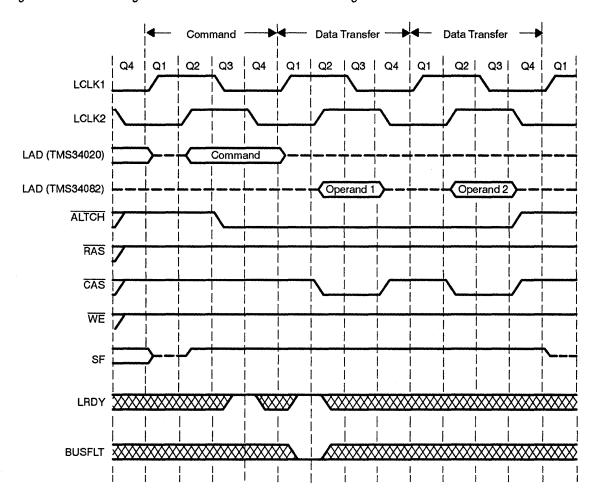

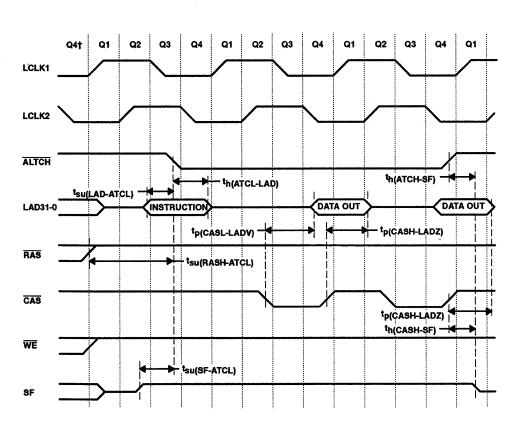

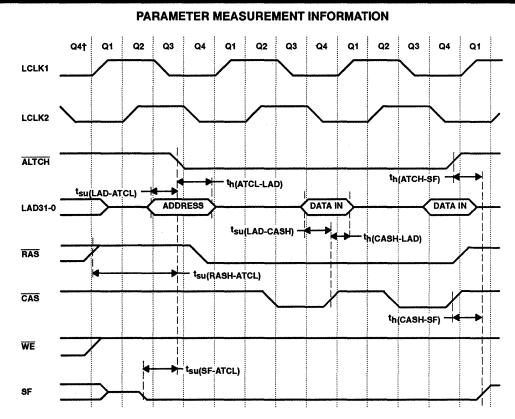

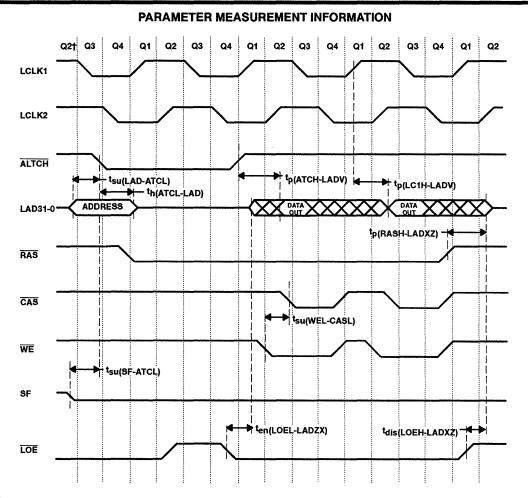

| Figure 5–3.  | Transferring a Command from the TMS34020 to the TMS34082                                                            | 5-8  |

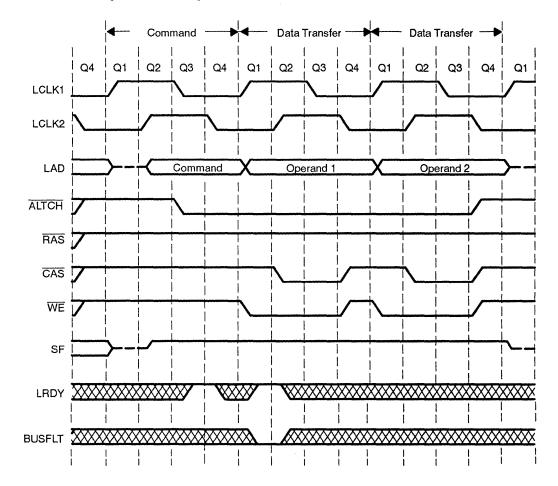

| Figure 5-4.  | Transferring TMS34020 Registers to the TMS34082                                                                     | 5-9  |

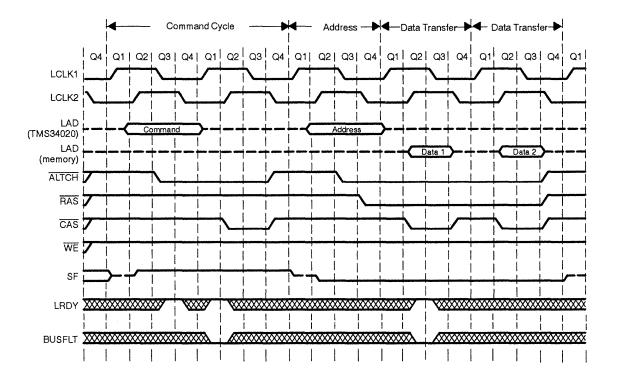

| Figure 5-5.  | Transferring from the TMS34082 to a TMS34020 Register                                                               | 5-10 |

| Figure 5–6.  | Transferring Memory to the TMS34082                                                                                 | 5-11 |

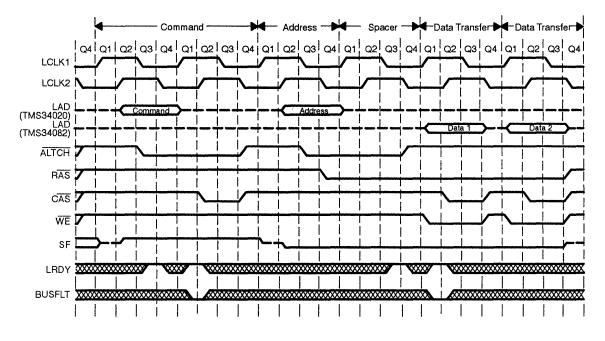

| Figure 5–7.  | Transferring from the TMS34082 to Memory                                                                            | 5-12 |

| Figure 5–8.  | Multiply 2 Double-Precision Numbers in TMS34020 Registers and Store Back to TMS34020 Registers (Mode 1)             | 5-21 |

| Figure 5–9.  | Add 2 Single-Precision Numbers from DRAM and Store Result Back to DRAM (Mode 2)                                     |      |

| Figure 5–10. | Add 2 Single-Precision Numbers from DRAM and Store Result Back to DRAM (Mode 2), Instructions Not in TMS34020 Cache |      |

| Figure 5–11. | TMS34020/TMS34082/SRAM with Minimal SRAM Code Space                                                                 | 5-24 |

| Figure 5-12. | TMS34020/TMS34082/SRAM with Maximum SRAM Code/Data Space<br>(MEMCFG = L)                                            | 5-25 |

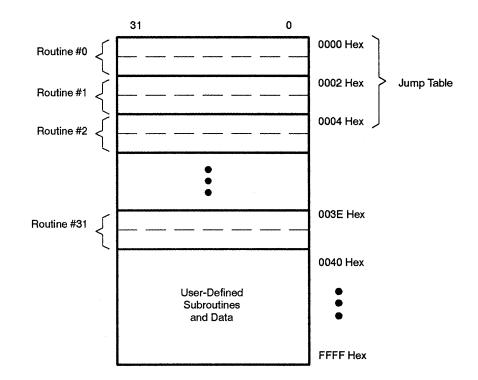

| Figure 5–13. | Memory Map for External Memory                                                                                      |      |

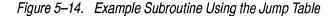

| Figure 5–14. | Example Subroutine Using the Jump Table                                                                             |      |

| Figure 5–15. | TMS34020 with Multiple TMS34082/SRAM Blocks (MEMCFG = L)                                                            |      |

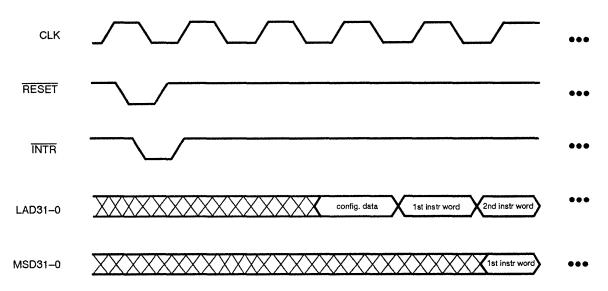

| Figure 6–1.  | Bootstrap Loader                                                                                                    |      |

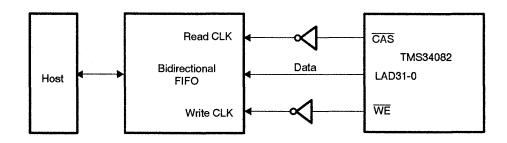

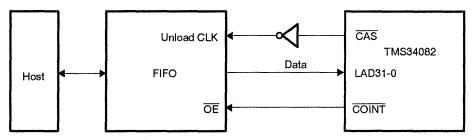

| Figure 6–2.  | Using FIFOs on the LAD Bus                                                                                          |      |

| Figure 6–3.  | Using COINT as a Device Select (LADCFG=H)                                                                           |      |

| Figure 7–1.  | Source for Internal Instructions in Coprocessor Mode                                                                |      |

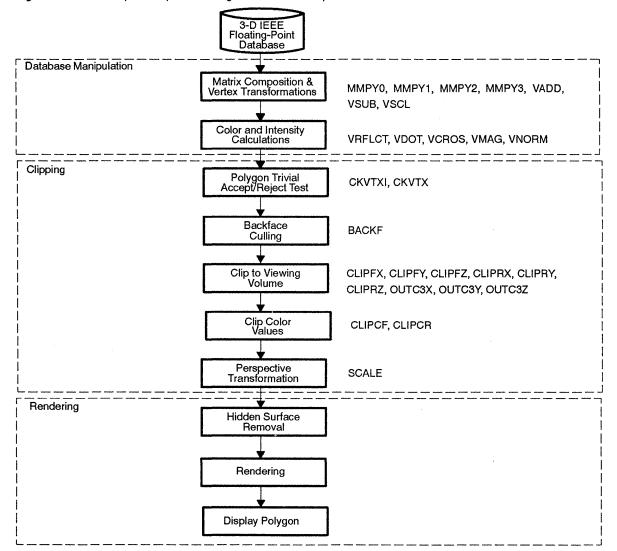

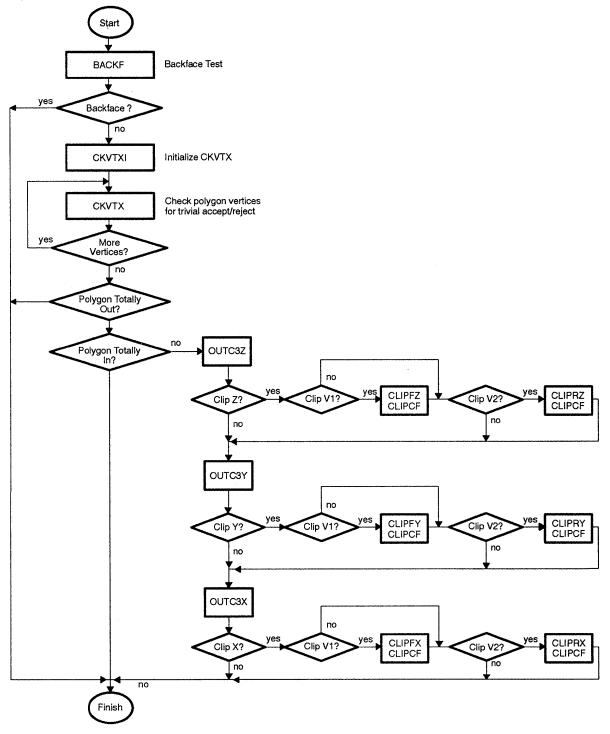

| Figure 7–2.  | 3-D Graphics Pipeline Using TMS34082 Complex Instructions                                                           |      |

| Figure 8–1.  | Source of Instructions for Coprocessor Mode                                                                         |      |

| Figure 8–2.  | Instructions in Host-Independent Mode                                                                               |      |

| Figure 8–3.  | Operand Selection                                                                                                   |      |

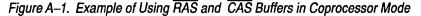

| Figure A-1.  | Example of Using RAS and CAS Buffers in Coprocessor Mode                                                            |      |

| Figure A–2.  | Recommended Bypass Capacitor Placement                                                                              |      |

| Figure A-3.  | Recommended Clock Routing Techniques                                                                                |      |

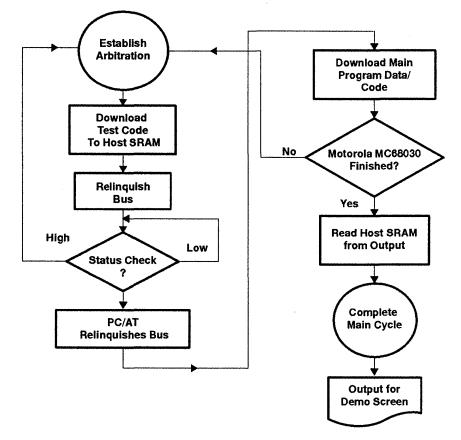

| Figure D-1.  | Motorola MC68030 Interface to the TMS34082 – Block Diagram                                                          |      |

| Figure D-2.  | Data Organization in Memory                                                                                         |      |

| Figure D-3.   | Block Diagram – TMS34082 Code                                       | . D-8 |

|---------------|---------------------------------------------------------------------|-------|

| Figure D-4.   | Block Diagram – Motorola MC68030 Code                               | D-9   |

| Figure D-5.   | Block Diagram – PC/AT Code                                          | D-10  |

| Figure D-6.   | PC/AC Interface: I/O and Memory Addressing                          | D-11  |

| Figure D-7.   | Motorola MC68030 Interface: Memory Addressing                       | D-12  |

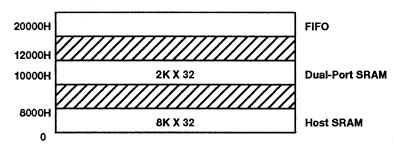

| Figure D-8(a) | Block Diagram                                                       | D-15  |

| Figure D-8(b) | Block Diagram                                                       | D-16  |

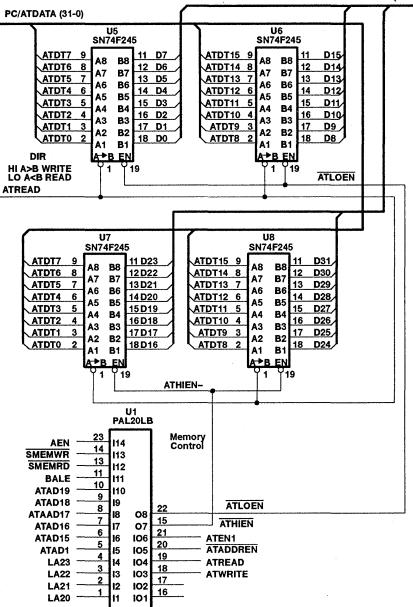

| Figure D–9.   | PC/AT I/F and Control, Details of U1, U5, U6, U7, and U8            | D-17  |

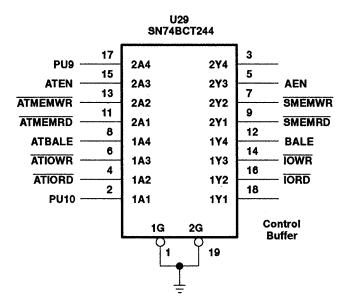

| -             | PC/AT I/F and Control, Details of U29                               |       |

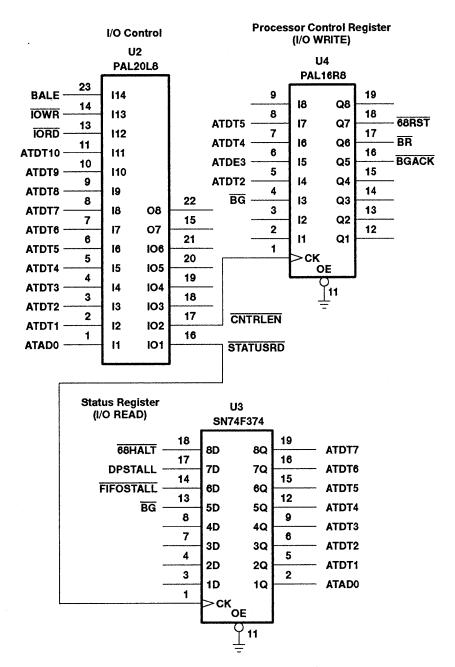

| Figure D-11.  | PC/AT I/F and Control, Details of U2, U3, and U4                    | D-19  |

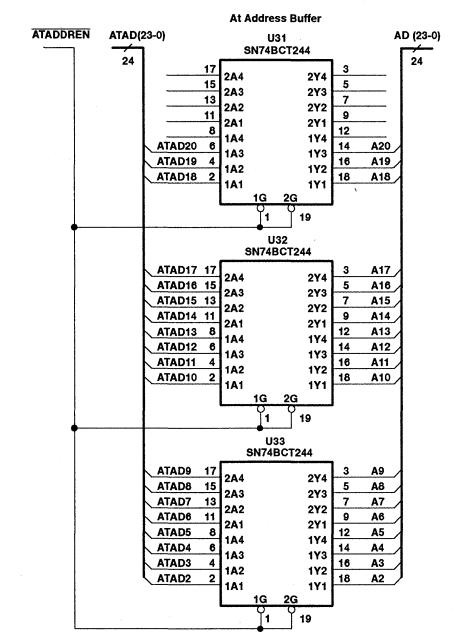

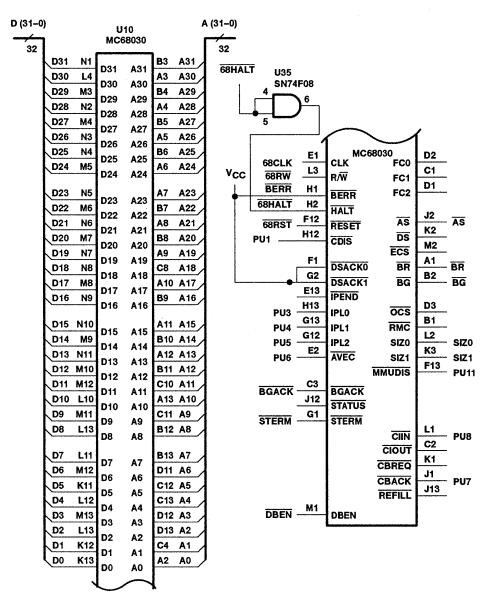

| Figure D-12.  | Motorola MC68030 and Address Buffers, Details of U31, U32, and U33  | D-20  |

| Figure D-13.  | Motorola MC68030 and Address Buffers, Details of U10                | D-21  |

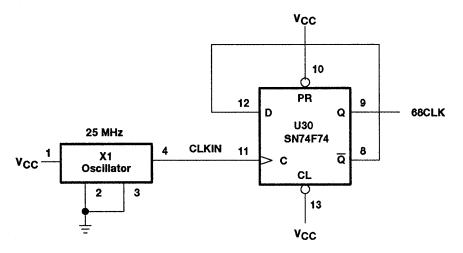

| Figure D-14.  | Motorola MC68030 and Address Buffers, Details of Oscillator and U30 | D-22  |

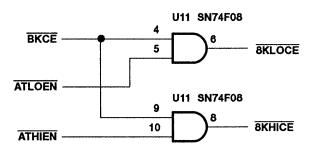

| Figure D-15.  | Motorola MC68030 Decode/Control, Details of U11                     | D-22  |

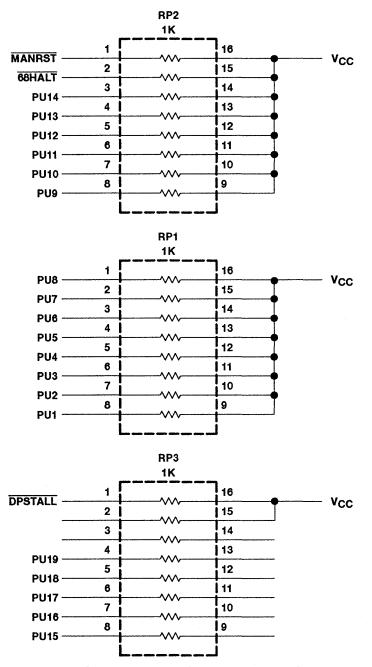

| Figure D-16.  | Motorola MC68030 Decode/Control, Details of RP1, RP2, and RP3       | D-23  |

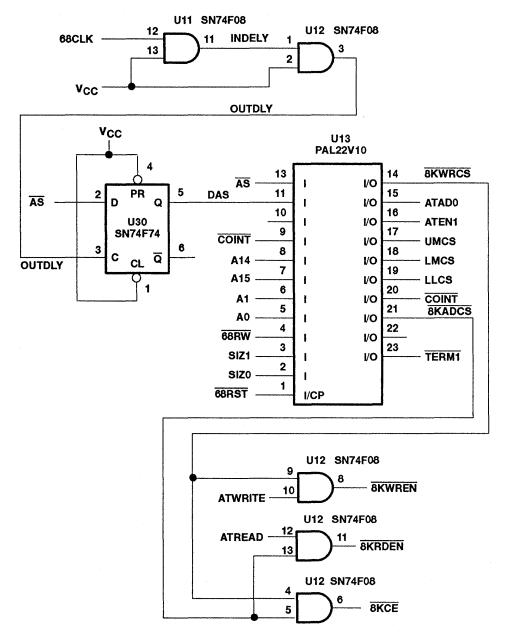

| Figure D-17.  | Motorola MC68030 Decode/Control, Details of U11, U12, U13, and U30  | D-24  |

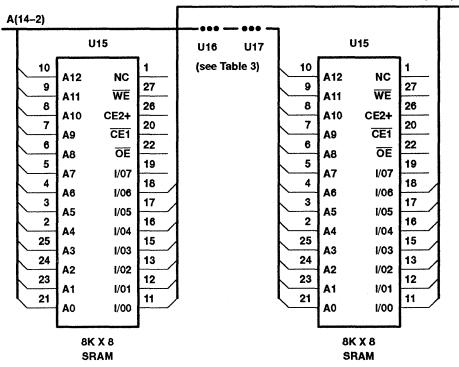

| Figure D-18.  | 8K × 8 SRAM, Details of U15, U16, U17, and U18                      | D-25  |

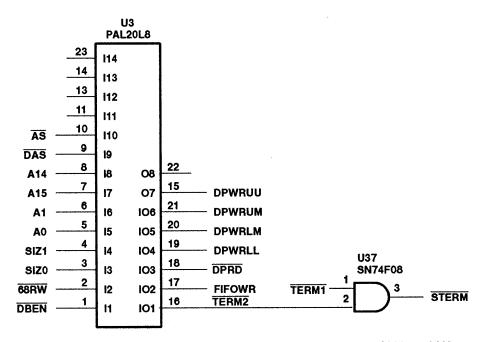

| Figure D-19.  | Motorola MC68030 Decode/Control, Details of U3, and U37             | D-27  |

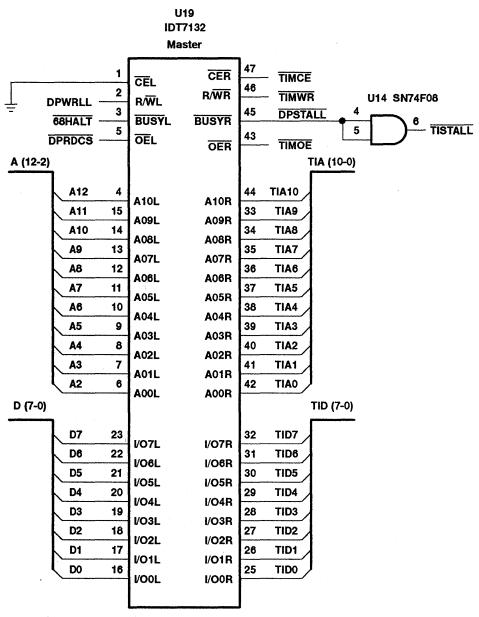

| Figure D-20.  | 8K × 8 DP-SRAM, Details of U14, and U19                             | D-28  |

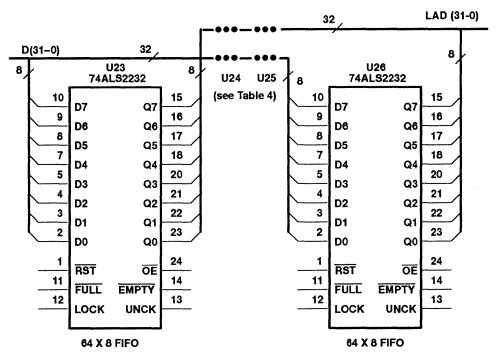

| Figure D-21.  | FIFO Logic, Details of U23, U24, U25, and U26                       | D-29  |

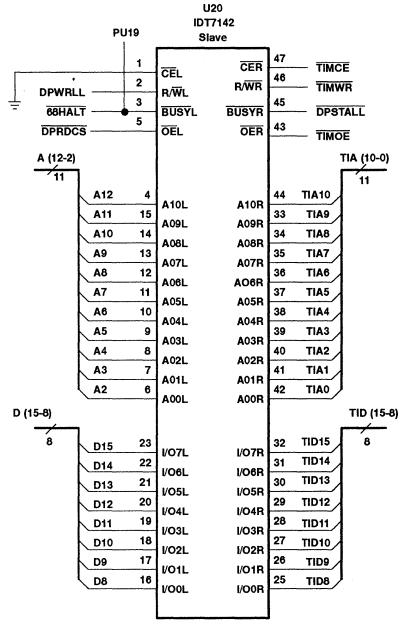

| Figure D-22.  | 8K × 8 DP-SRAM, Details of U20                                      | D-31  |

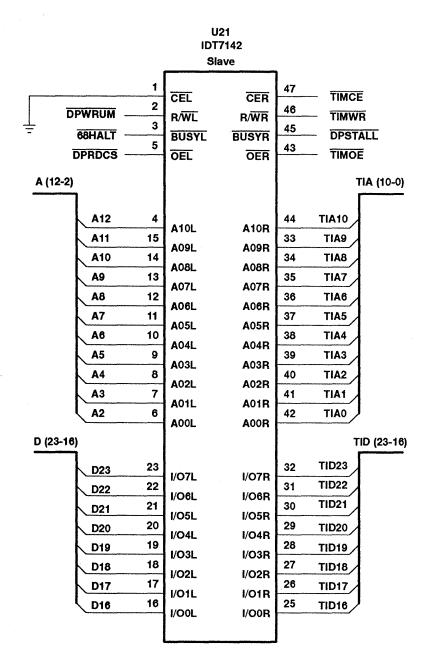

| Figure D-23.  | FIFO Logic, Details of U21                                          | D-32  |

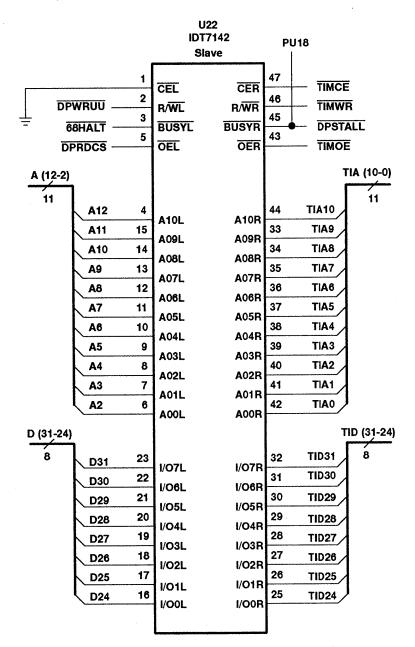

| Figure D-24.  | FIFO Logic DP-SRAM, Details of U22                                  | D-33  |

| Figure D-25.  | FIFO Logic, Details of U14                                          | D-34  |

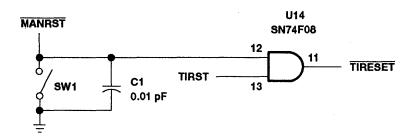

| Figure D-26.  | TMS34082, Details of U38                                            | D34   |

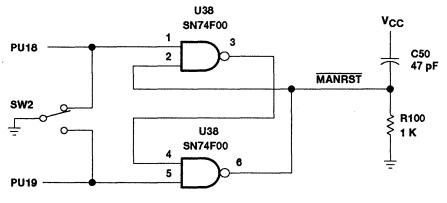

| Figure D-27.  | TMS34082, Details of U28                                            | D-35  |

| Figure D-28.  | TMS34082, Details of U28                                            | D-36  |

| Figure D-29.  | AT-Bus Connector                                                    | D-37  |

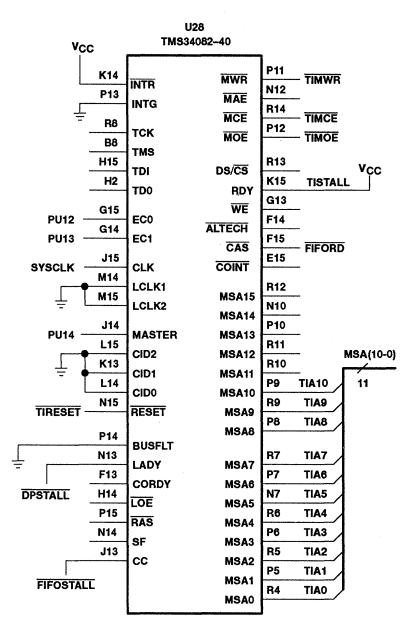

| Figure D-30.  | Capacitors                                                          | D-38  |

| Figure E-1.   | UWGSP3 Software Architecture                                        | . E-6 |

| Figure E-2.   | UWGSP3 Software Architecture                                        | E-10  |

| Figure E-3.   | Lowpass Filter Specification Window                                 | E-11  |

| Figure E-4.   | Image Load (left) and Virtual Frame Buffer (right) Windows          | E-12  |

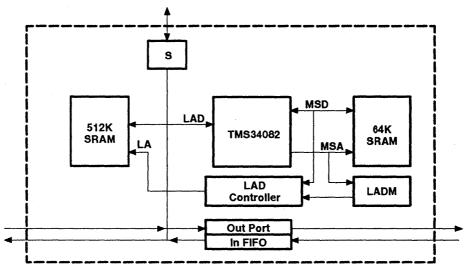

| Figure F-1.   | System Architecture                                                 | . F-5 |

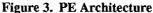

| Figure F-2.   | System Memory Map                                                   | . F-6 |

| Figure F-3.   | PE Architecture                                                     | . F-7 |

| Figure F-4.   | LAD Bus Controller Architecture                                     | . F-7 |

| Figure F-5.   | Parallel Jaccobi Updating on a Systolic Architecture                | F-12  |

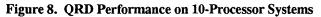

| Figure F-6.  | Matrix Multiplication Performance on 10-Processor Systems | F-14 |

|--------------|-----------------------------------------------------------|------|

| Figure F-7.  | 28 × 128 Matrix Multiplication on P-Processor Systems     | F-14 |

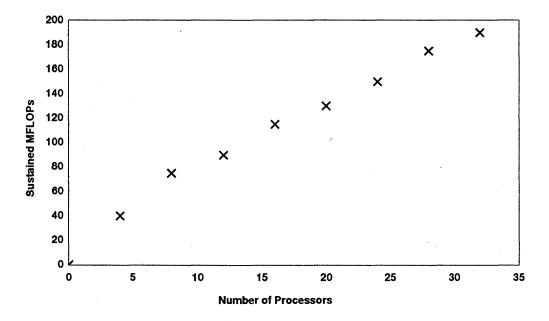

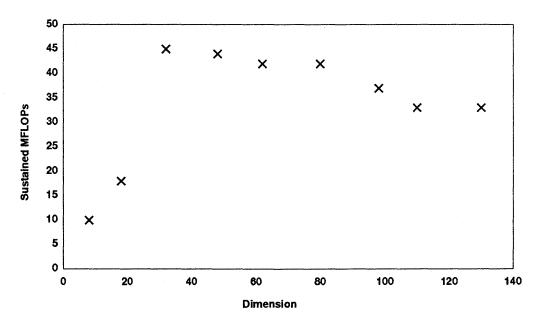

| Figure F-8.  | QRD Performance on 10-Processor Systems                   | F-16 |

| Figure F–9.  | 28 × 128 QRD on P-Processor Systems                       | F-16 |

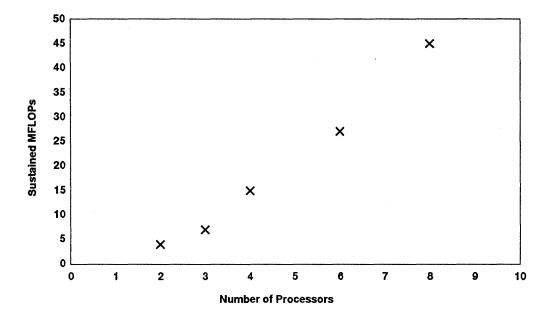

| Figure F-10. | SVD Performance on 8-Processor Systems                    | F-17 |

| Figure F-11. | 48 × 48 SVD on P-Processor Systems                        | F-18 |

## **Tables**

| Table 1-1.  | TMS34082 Integer Benchmark Timings 1-3               |

|-------------|------------------------------------------------------|

| Table 1-2.  | TMS34082 Floating-Point Benchmark Timings1-3         |

| Table 1-3.  | Description of the Benchmarks Used 1-3               |

| Table 1-4.  | Applications for the TMS34082 1-9                    |

| Table 1-5.  | TMS34082 Product Information 1-21                    |

| Table 2-1.  | Pin Assignments (PGA Package) 2-3                    |

| Table 2–2.  | Alphabetical Listing — Pin Assignments (PGA Package) |

| Table 2–3.  | LAD Bus Signals                                      |

| Table 2–4.  | MSD Bus Signals 2-7                                  |

| Table 2–5.  | Clock and Control Signals 2-9                        |

| Table 2–6.  | Emulation Control Signals 2-9                        |

| Table 2–7.  | Power and N/C Signals                                |

| Table 3–1.  | Floating-Point Number Representations 3-6            |

| Table 4-1.  | MSD Bus Control Signals 4-5                          |

| Table 4-2.  | Memory Operations on MSD 4-5                         |

| Table 4–3.  | Internal Registers 4-10                              |

| Table 4-4.  | Configuration Register Definition 4-14               |

| Table 4–5.  | Pipeline Settings 4-17                               |

| Table 4–6.  | Handling Wrapped Multiplier Outputs 4-18             |

| Table 4–7.  | Data Ordering for Loads/Stores 4-18                  |

| Table 4–8.  | Rounding Modes 4-19                                  |

| Table 4–9.  | Status Register Definition 4-20                      |

| Table 4–10. | Signal States During Reset 4-32                      |

| Table 4-11. | Test Modes 4-33                                      |

| Table 4–12. | Test Pins for Normal Operation 4-34                  |

| Table 4–13. | Instruction Register Opcodes 4-35                    |

| Table 4–14. | Boundary Scan Register Enable Bits 4-35              |

| Table 5-1.  | Recommended TMS34082 Pin Connections 5-3             |

| Table 5–2.  | Bus Cycle Completion Conditions 5-13                 |

| Table 5–3.  | Bit Definitions for TMS34020 Status Check Command    |

| Table 5–4. | Parameters Used for Calculating SRAM Speed 5-25                                             |

|------------|---------------------------------------------------------------------------------------------|

| Table 6-1. | Pin Connections 6-2                                                                         |

| Table 7-1. | Internal ROM Routines (for Mode 0 FPU Operations)                                           |

| Table 7–2. | Coprocessor IDs                                                                             |

| Table 7–3. | Addressing Modes                                                                            |

| Table 7-4. | Operand Types                                                                               |

| Table 8–1. | Cycle Counts for External Instructions 8-9                                                  |

| Table 8–2. | Bit Definitions for External Instructions 8-14                                              |

| Table D-1. | Performance Comparison Chart D-13                                                           |

| Table D-2. | System Information — Parts List D-14                                                        |

| Table D-3. | $8\mathrm{K}\times8$ SRAM DP-SRAM, Detail Pin Assignments for U15, U16, U17, and U18 . D-26 |

| Table D-4. | FIFO Logic, Details of Pin Assignments for U23, U24, U25, and U26 D-30                      |

| Table F-1. | Distributed FFT Performance Results F-15                                                    |

| Table F-2. | Pipelined FFT Performance Results for Real-Time Signal and Image Processing F-17            |

## Examples

| Example 5-1. | Using the Status Check Command                                              | 5-14 |

|--------------|-----------------------------------------------------------------------------|------|

| Example 5–2. | Saving and Restoring the TMS34082 Machine State                             | 5-16 |

| Example 5-3. | Multiplying Two 3 × 3 Matrices                                              | 5-18 |

| Example 5-4. | Instructions for a 3 × 3 by 3 × 3 Matrix Multiply                           | 5-19 |

| Example 5-5. | Assembler Source for Double-Precision Multiply                              | 5-20 |

| Example 5-6. | Assembler Source for Single-Precision Add                                   | 5-20 |

| Example 5–7. | TMS34020 Assembler Listing for 3 $\times$ 3 by 3 $\times$ 3 Matrix Multiply | 5-29 |

| Example 58.  | TMS34082 Assembler Listing for 3 × 3 by 3 × 3 Matrix Multiply               | 5-30 |

| Example 5-9. | Assembler Code for Multiple TMS34082s                                       | 5-38 |

## **Chapter 1**

## **Overview of the TMS34082**

The Texas Instruments TMS34082 Graphics Floating-Point Processor is designed for your advanced numeric applications. This high-performance device offers an outstanding price/performance ratio, flexibility, and ease of use with TI's development tools. The TMS34082 acts as either a tightly coupled coprocessor for the TMS34020 Graphics System Processor (GSP), as an independent processor, or as a coprocessor to another host.

By integrating a 64-bit IEEE Floating-Point Unit (FPU) with a modified Harvard architecture microprocessor and multi-port register files onto a single device, the TMS34082 can sustain exceptionally high internal throughput rates. All internal data paths are 64 bits wide. The RISC-like basic instruction set executes at a rate of one instruction per clock cycle. In addition, many popular numeric and graphics routines are contained directly on-chip.

The TMS34082 offers an attractive cost/performance ratio and supports the integration of graphics- and computation-intensive solutions in a single, low-cost device. The cost per MFLOP performance achieved by the TMS34082 makes it an ideal floating-point solution.

Texas Instruments supports the TMS34082 with a complete set of PC-based hardware and software development tools, including an easy-to-use simulator, a TMS34020/TMS34082 software development board, a TMS34082 demonstration board, a 3-D graphics library, an optimizing C compiler, a macro-assembler, and software libraries.

## 1.1 TMS34082 Key Features

High-performance floating-point RISC processor optimized for graphics

Two operating modes:

Floating-point coprocessor for the TMS34020 Graphics System Processor Independent floating-point processor

Direct connection to TMS34020 coprocessor interface

Direct extension to the TMS34020 instruction set Multiple TMS34082 capability

Fast instruction cycle time:

TMS34082-40...50-ns coprocessor mode, 50-ns host-independent mode TMS34082-32...62.5-ns coprocessor mode, 60-ns host-independent mode

Sustained data transfer rates of 160M bytes/second (TMS34082-40)

Sequencer executes internal or user-programmed instructions

Twenty-two 64-bit data registers

Comprehensive floating-point and integer instruction set

Internal programs for vector, matrix, and 3-D graphics operations

Full IEEE Std 754-1985 compatibility:

Addition, subtraction, multiplication, and comparison Division and square root

Selectable data formats:

32-bit integer 32-bit single-precision floating-point 64-bit double-precision floating-point

External memory addressing capability:

Program storage (up to 64K words) Data storage (up to 64K words)

0.8-µm EPIC™ CMOS technology

High-performance Low power (<1.5 W)

## 1.2 Performance Benchmarks

Tables 1–1 and 1–2 show benchmark timings. Table 1–3 describes the benchmarks selected to show TMS34082 performance.

Table 1–1. TMS34082 Integer Benchmark Timings<sup>†</sup>

| Davida           |                   | Integer      |              |

|------------------|-------------------|--------------|--------------|

| Benchmark        | Units of Measure  | TMS34082A-32 | TMS34082A-40 |

| MIPS Equivalents | MIPS              | 32           | 40           |

| Dhrystones       | Dhrystones/second | 10,240       | 12,800       |

Table 1-2. TMS34082 Floating-Point Benchmark Timings<sup>†</sup>

| Benchmark   | Units of Measure   | Single-Precision |              | Double-Precision |              |

|-------------|--------------------|------------------|--------------|------------------|--------------|

|             |                    | TMS34082A-32     | TMS34082A-40 | TMS34082A-32     | TMS34082A-40 |

| Peak MFLOPS | MFLOPS             | 32               | 40           | 16               | 20           |

| Linpack     | MFLOPS             | 11.0             | 13.7         | 6.3              | 7.9          |

| Whetstones  | MWhetstones/second | 7.9              | 9.9          | 4.6              | 5.7          |

<sup>†</sup> Based on actual measured system performance.

Table 1-3. Description of the Benchmarks Used<sup>‡</sup>

| Benchmark  | Operations Tested                                                                                                                   | Where Applicable                                          |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Linpack    | Floating-point and integer array manipulation,<br>including Gaussian elimination, vector dot products,<br>and matrix multiplication | Dense systems of linear equations with array manipulation |

| Whetstones | Mathematical operations: integer, floating-point, and trigonometric operations                                                      | Engineering and scientific computing applications         |

| Dhrystones | Enumeration, record and pointer manipulation, and integer operations                                                                | Systems programming applications                          |

‡ Reference: Hinnant, David F., "What Makes a Good Benchmark?", MIPS, September, 1989, pp. 102-103.

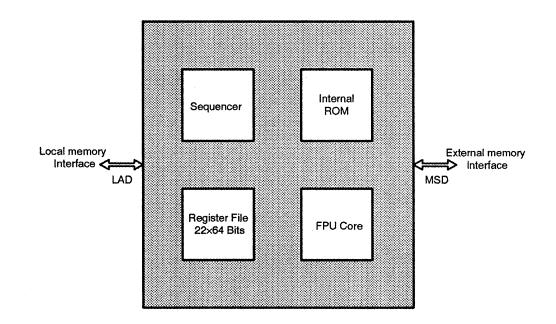

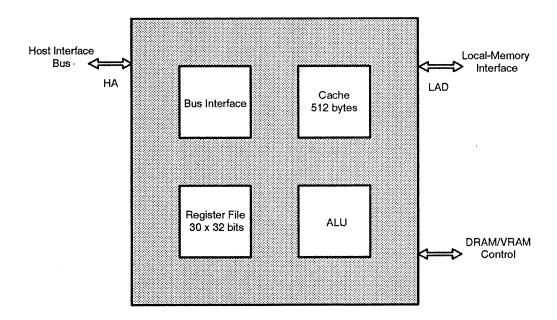

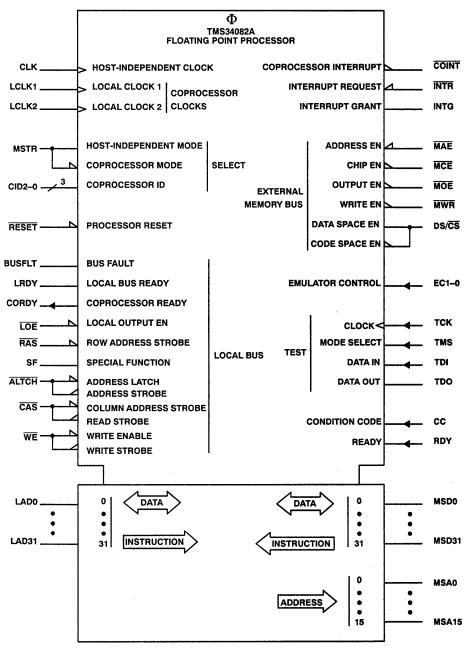

## 1.3 TMS34082 General Description

The TMS34082 is a high-speed floating-point processor implemented in the Texas Instruments advanced 0.8  $\mu$ m CMOS technology. On a single chip, the TMS34082 combines a 16-bit sequencer and a three-operand 64-bit FPU (source A, source B, destination) with twenty-two 64-bit data registers. The data registers are organized into two banks of 10 registers each, with two registers for internal feedback. In addition, an instruction register to control FPU execution, a status register to retain the most recent FPU status results, eight control registers, and a two-register stack are provided. The key architectural elements are shown in Figure 1–1.

The ALU and the multiplier are closely coupled and work in parallel to perform sums of products and products of sums. During multiply/accumulate operations, both the ALU and the multiplier are active, and the registers in the FPU core can be used to feed back products and accumulate sums without tying up locations in register banks A and B.

Data or code may be transferred between the LAD and MSD ports at the rate of one 32-bit word per clock cycle with a one clock latency. That comes out to 1.28 billion bits/second. This provides sufficient bandwidth to quickly transfer vector or scalar arrays into or out of external memories. Up to 512 words may be transferred with a single memory move instruction.

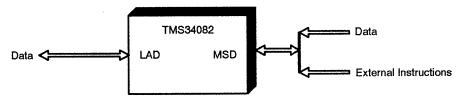

Figure 1-1. TMS34082 High-Level Block Diagram

The TMS34082 complies fully with IEEE Std 754-1985, the industry standard for binary floating-point formats. Floating-point operands can be either singleor double-precision. In addition to floating-point operations, the TMS34082 performs 32-bit integer arithmetic, logical comparisons, and shifts. Integer operations may be performed on 32-bit 2s complement or unsigned operands. Floating-point to integer and integer to floating-point conversions are also available.

The comprehensive RISC-like instruction set eliminates the need for complex CISC-type instructions or wide microcoded instruction words. By programming the TMS34082 at the simplest level, operations are customized for each application and most instructions execute in one clock cycle. Divide and square root instructions are ideal for numeric processing and graphics rendering, such as ray tracing routines. Using dedicated hardware and patented algorithms, the TMS34082 calculates a 64-bit double-precision divide or square root result in only 13 or 16 clock cycles, respectively.

In a single clock cycle, two single-precision or integer operands may:

- 1) Be read from the register file

- 2) Be run through the ALU and/or multiplier

- 3) Have result placed back into the register file

This is accomplished with both the internal pipeline and output registers disabled. Double-precision multiplies take two clock cycles to complete. Such low latencies simplify writing assembly language code, eliminating the problem of data coherency in a long pipeline. Refilling or flushing the instruction pipeline is fast, also.

An internal ROM includes many commonly used matrix, graphics, and vector routines as described below. With the exception of MIN-MAX and compare operations, these routines are constructed directly from the TMS34082's basic instruction set. The internal routines include:

Matrix operations consisting of  $1 \times 3$ ,  $3 \times 3$ ,  $1 \times 4$ , and  $4 \times 4$  matrix multiplies

Graphics routines such as backface testing, clipping, 2-D and 3-D compares, linear interpolation, 1-D and 2-D MIN-MAX, viewport scaling and conversion, cubic splines, and polygon elimination

Vector operations including add, subtract, magnitude, scaling, dot product, cross product, normalization, and reflection

Additional routines for  $3 \times 3$  convolution, multiply/accumulate, and polynomial expansion

When used with the TMS34020, the TMS34082 operates in coprocessor mode. The TMS34020 can control multiple TMS34082 coprocessors without any additional glue logic or buffering. The clock and control signals are generated directly by the TMS34020. You can use external memory to store subroutines as well as data for those subroutines. See Chapter 5 for additional information.

When used alone or with processors other than the TMS34020, the TMS34082 functions in host-independent mode. The TMS34082 is fully programmable and can interface to other processors (such as a RISC, 80x86, or Motorola MC680x0 processor) or floating-point subsystems through its two 32-bit bidirectional buses. Chapter 6 covers this mode in greater detail.

Other features include:

Support of common microprocessor addressing modes (register, direct, indirect, postincrement, immediate)

A fully synchronous, on-chip, direct memory interface to SRAMs/ EPROMs with no glue logic and to DRAMs/VRAMs with minimal glue logic

Fully user-programmable hardware and software realtime interrupts.

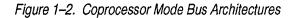

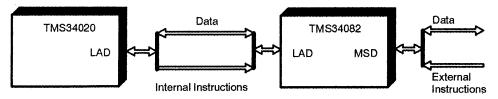

The TMS34082 may implement a von Neumann architecture, a modified Harvard architecture, or a mixture of both. In a von Neumann architecture, data and instruction memories both reside on the same bus. However, a Harvard architecture has separate data and instruction sources so that both may be fetched in parallel. External data may originate from either the LAD or MSD ports. External instructions may only come from the MSD port, but the LAD port can be used to input jump entries into the MSD port memory.

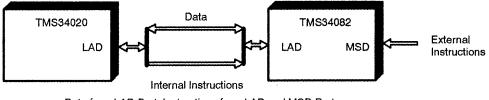

Figure 1–2 shows possible TMS34082 bus architectures for coprocessor mode. In addition, Figure 1–3 shows several example architectures for host-independent mode.

Data from LAD Port, Instructions from LAD and MSD Port

Data from LAD and MSD Ports, Instructions from LAD and MSD Port

Figure 1–3. Host-Independent Mode Bus Architectures

## 1.4 Typical Applications

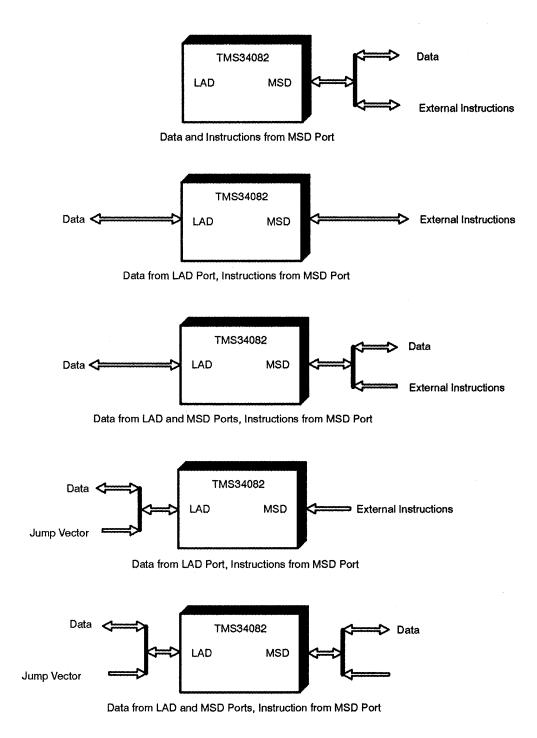

The 64-bit power and exceptional flexibility of the TMS34082 meet system computing requirements across the performance spectrum. These range from workstations to personal computers to embedded controllers. Table 1–4 lists typical end uses for this device. Figure 1–4 shows several examples of systems using the TMS34082.

Numeric Processor **Graphics Processor** CAD/CAE workstations 3-D graphics processing UNIX/DOS accelerator for RISC/CISC machines Graphics workstations/super workstations Scientific computing Image processing Personal computers Laser printers Graphics rendering engines Vector processing Multiprocessing architectures Imaging compression/decompression, JPEG Digital signal processing Flight simulators High-speed protocol engines Electronic publishing Array processing Computer animation

Table 1–4. Applications for the TMS34082

#### Overview of the TMS34082

## 1.5 Development Tools

### 1.5.1 TMS34082 Software Tool Kit

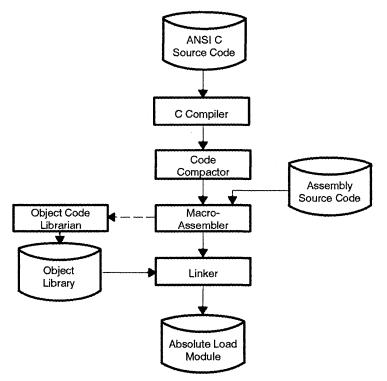

The TMS34082 Software Tool Kit can be used to develop code for host-independent mode applications or for external subroutines in coprocessor mode. The tool kit includes:

An ANSI standard, optimizing C compiler

A macro-assembler

A linker

An object code librarian

A functional simulator

The C compiler supports common subexpression elimination. A peephole optimizer is also provided to further enhance the execution speed and the code size of the source program. Inline assembly code can be incorporated into the C program for time-critical and hardware-dependent code sections. The object librarian allows the storage of frequently used functions in libraries for easy access (see Figure 1–5).

Figure 1–5. Overview of TMS34082 Code-Generation Tools

Included with the TMS34082 tool kit are highly optimized transcendental assembly language routines for sine, cosine, tangent, arc sine, arc cosine, and arc tangent. These are accurate to the least significant bit.

The TMS34082 tool kit will execute on an IBM PC/AT or compatible machine with MS-DOS (or PC-DOS) 2.0 or higher, 640K of memory, one floppy drive, and one hard drive. An 80287/80387 math coprocessor is required for the simulator. A demonstration version of the Software Tool Kit is also available.

The interactive simulator displays the entire machine state of the TMS34082 (such as registers, address counter, stack, status register) and works with the C compiler/assembler/linker object files. The simulator is menu driven. During program execution, breakpoints may be set and the trace memory displayed. The cycle counting feature is useful when evaluating performance of the processor or during code optimization.

The TMS340 Family compiler and assembler, which support both the TMS34020 and TMS34082, are described in subsection 1.6.3 of this document.

### 1.5.2 TMS34082 3-D Graphics Library

The TMS34082 3-D Graphics Library contains an extensive array of C-callable functions including polygon clipping, shading, and vector and matrix operations. The library is TIGA-compatible and can also run as a non-TIGA product, giving the user portability and flexibility. The task of porting graphics standard to the TMS34020/TMS34082 is greatly simplified with the variety of functions in the library. The library also includes a 3-D graphics pipeline that can shorten the development time for application programs.

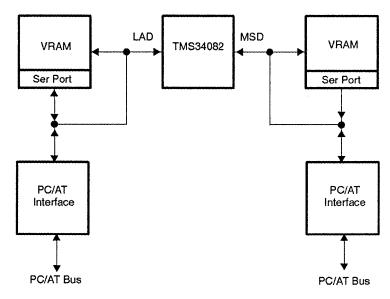

## 1.5.3 TMS34082 Demonstration Board

The TMS34082 Demonstration Board is a 40-MFLOP parallel processor with up to 3M bytes of on-board memory. This powerful board allows you to evaluate performance and write code for the TMS34082 using the software tool kit, develop algorithm implementations, and integrate the software modules with the hardware. In addition, programs are executed directly on the TMS34082, resulting in much faster execution times than a software simulator. The board plugs into a PC/AT<sup>TM</sup> 32-bit card slot. Figure 1–6 is a block diagram of the demonstration board.

## Figure 1–6. TMS34082 Demonstration Board Block Diagram

Built on a PC/AT card occupying a single slot, the TMS34082 Demonstration Board features:

TMS34082-40 Floating-Point Processor (operating in host-independent mode)

20 MHz processor clock speed, 7.9 MFLOPs double-precision Linpack

Fully programmable: von Neumann or modified Harvard architectures or both

2M-bytes VRAM memory on LAD port accessible though PC/AT bus interface

256K-bytes VRAM memory on MSD port accessible through PC/AT bus interface, expandable up to 1M bytes of VRAM memory

## 1.6 TMS34020 Graphics System Processor

The TMS34020 Graphics System Processor (GSP) is an advanced 32-bit microprocessor optimized for graphic display systems. The TMS34020 is a member of the TMS340 family of computer graphics products from Texas Instruments.

The TMS34020 provides high-performance cost-effective solutions for applications that require efficient data manipulations in a graphics environment. The TMS34020 can be configured to serve in a host-based, standalone, or multiprocessing system. It has both host and multiprocessor interfaces to facilitate implementation of multiple TMS34020 systems.

The TMS34020 is supported by a full set of hardware and software development tools, including an optimizing C compiler, assembler, software libraries, a PC-based development board on a PC-based emulator. The TMS340 Family Code Generation Tools may be used to develop code for the TMS34082 in coprocessor mode. In addition, the TMS34020 is fully compatible with and supported by the Texas Instruments Graphics Architecture (TIGA).

## 1.6.1 TMS34020 Key Features

Fully programmable 32-bit general-purpose processor with 512M-byte linear address range (bit addressable)

Second generation graphics system processor:

Object code compatible with the TMS34010

Enhanced instruction set

Optimized graphics instructions

Direct coprocessor interface to TMS34082 Floating-Point Processor

On-chip peripheral features include:

Programmable CRT control

Direct DRAM/VRAM interface

Direct communication with an external (host) processor

Communication with multiple TMS34020s

Functional expansion with the coprocessor interface

Automatic CRT display refresh

Instruction set supports special graphics functions such as pixel processing, XY addressing, and window clip/hit detection

Programmable 1-,2-,4-,8-,16-, or 32-bit pixel size

16 Boolean and 6 arithmetic pixel processing options (raster-ops)

30 general-purpose 32-bit registers

512-byte LRU on-chip instruction cache

**General Description**

The TMS340 family from Texas Instruments combines the best features of general-purpose microprocessors and graphics controllers to create a range of cost-effective, flexible, powerful graphics systems. The key features of the TMS340 family are speed, a high degree of programmability, and efficient manipulation of hardware-supported data types such as pixels and 2-dimensional pixel arrays.

With a built-in instruction cache, the ability to simultaneously access memory and registers, and an instruction set that enhances raster graphics operations, the TMS34020 provides programmable control of the CRT interface as well as the memory interface (both standard DRAM and multiport RAM). The 4G-bit (512M-byte) physical address space is completely bit addressable on bit boundaries using variable width data fields (1 to 32 bits). Figure 1–7 is a TMS34020 high-level block diagram.

Figure 1-7. TMS34020 High-Level Block Diagram

The TMS34020 unique memory interface speeds performance of tasks such as bit alignment and masking while supporting advanced DRAM access modes. The 32-bit architectures supplies the large blocks of contiguously-addressable memory that are necessary in graphics applications.

Systems designed with the TMS34020 can utilize VRAM technology to facilitate applications such as high-bandwidth frame buffers. This circumvents the bottleneck often encountered when using conventional DRAMs in graphics systems.

The TMS34020 instruction set includes a full complement of general-purpose instructions, as well as graphics functions, that can be used to construct efficient high-level instructions. The instructions support arithmetic and Boolean operations, data moves, conditional jumps, and subroutine calls and returns.

The TMS34020 architecture supports a variety of pixel sizes, frame buffer sizes, and screen sizes. On-chip functions have been carefully selected so that no functions tie the TMS34020 to a particular display resolution. This enhances the portability of graphics software and allows the TMS34020 to adapt to graphics standards such as MIT's X-Windows<sup>™</sup>, CGI/CGM, GKS, NAPLPS, PHIGS, and evolving industry standards.

Texas Instruments offers a wide variety of system solutions. The simplest TMS340 graphics system consists of the TMS34020 alone. Floating-point computations are performed in software using IEEE floating-point libraries. Adding a TMS34082 appears merely as an extension to the TMS34020 instruction set. The same calculations run much faster in dedicated hardware rather than software.

Adding external memory to the TMS34082 allows user-programmed subroutines, such as shading or contour fitting, to execute while the TMS34020 is performing other functions. Since the data for the subroutines is also in external memory, the TMS34082 is effectively decoupled from the TMS34020. The TMS34020 can poll the TMS34082 to see if the subroutine has finished. The highest performance TMS340 graphics solutions contain one or more TMS34020 along with multiple TMS34082s in a parallel processing environment. The TMS34020 acts as the display manager and also orchestrates tasks for the floating-point coprocessors. Jobs and/or data may be loaded into external memory of one TMS34082 while other TMS34082s are still executing.

#### 1.6.2 TMS34020 Software Tools

Texas Instruments offers extensive development support for the TMS340 graphics family. Software tools for the TMS34020 also comprehend the TMS34082. The TMS340 Family software tools include:

An optimizing C compiler An assembler An archiver for building object libraries A linker A loader for TMS34020 and TMS34082 absolute load modules A C source debugger

The compiler accepts programs written in C language. It outputs assembly language source code that is then processed by the assembler to convert the mnemonics to object code. The compiler and assembler generate efficient TMS34082 code in the form of internal instructions. The C compiler allows time-critical routines written in assembly language to be called from within the C program. The converse is also available; assembly routines may call C functions.

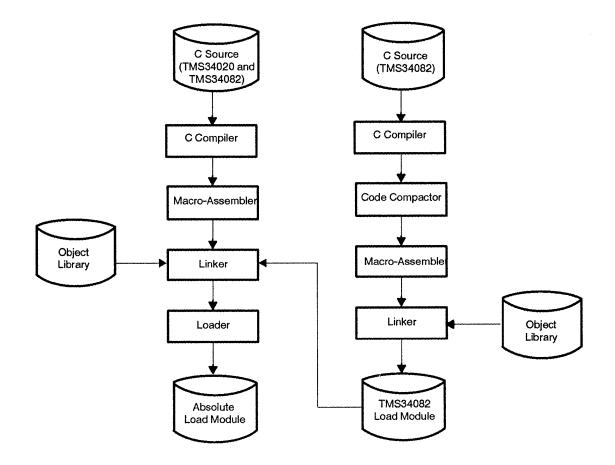

If external TMS34082 memory is present, the TMS34082 Software Tool Kit must be used to generate the subroutine code in the form of external instructions. When the TMS34082 load module has been generated, the TMS34020 loader can download both load modules as shown in Figure 1–8.

The TMS340 Family C Source Debugger supports both the TMS34020 and the TMS34082 in coprocessor mode. Other debugging tools for the TMS34082 in coprocessor and host-independent modes are available from third-party vendors.

Figure 1-8. TMS34020 and TMS34082 Software Tools

TMS340 Family Software Code Generation Tools (used for generating TMS34020 code and TMS34082 internal instructions)

TMS34082 Software Tool Kit (generates TMS34082 code for external memory)

#### **1.6.3 TIGA™ Graphics Interface**

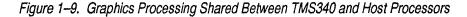

The Texas Instruments Graphics Architecture (TIGA) is a software interface standard for the TMS340 family of graphics system processors. TIGA enhances the performance of MS-DOS-based PCs that contain a TMS34020 or TMS34020 (and an optional TMS34082) and an 8088/86 or 80286/80386 host microprocessor by optimizing communications between the graphics processor and the host processor. The TIGA interface allows the host and graphics processors to share execution of the application, as shown in Figure 1–9.

### 1.6.4 TMS34020 Software Development Board

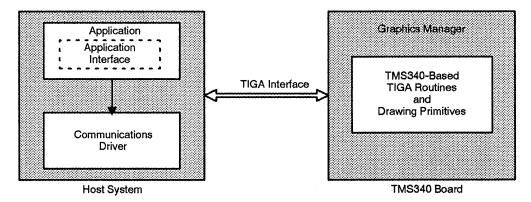

The TMS34020 Software Development Board (SDB20) is a high-performance PC/AT bus graphics card. It allows you to write applications software for the TMS34020 and its companion floating-point processor, the TMS34082. The board also demonstrates the simplicity of hardware design using the TMS34020 and TMS34082 for high-performance bit-mapped graphics displays.

An optional upgrade kit, the TMS34082 SRAM Upgrade Kit, contains a business card sized board with the TMS34082 and 32K bytes of SRAM, plus software and documentation. The board plugs into the TMS34082 socket presently existing on the SDB20.

Figure 1–10. TMS34020 SDB Block Diagram

Key features of the TMS34020 SDB include:

1M-byte VRAM organized as  $256K \times 32$  bits

1M-byte DRAM organized as 256K × 32 bits

TMS34082 Floating-Point Coprocessor (optional)

VGA support for  $640 \times 480$  pixel resolution

Software selectable resolutions:

$1024 \times 768$  by 4 or 8 bits per pixel

$640 \times 480$  by 4 or 8 bits per pixel

$640 \times 480$  VGA mode

Software configurable base address over a full 16M-byte range

TMS34020 emulation support

# 1.7 TMS34082 Ordering Information

For the latest ordering and pricing information, please call your local TI field sales representative or authorized TI distributor. Table 1–5 summarizes the products available for the TMS34082.

Table 1-5. TMS34082 Product Information

| Туре            | Description                                                                                                   | Part Number    |

|-----------------|---------------------------------------------------------------------------------------------------------------|----------------|

| Silicon Devices | TMS34082A device, 32 MHz, 145-pin ceramic PGA package                                                         | TMS34082AGC-32 |

|                 | TMS34082A device, 40 MHz, 145-pin ceramic PGA package                                                         | TMS34082AGC-40 |

| Documentation   | TMS34082A Data Sheet                                                                                          | SCGS001        |

|                 | TMS34082 Designer's Handbook                                                                                  | SCGU004        |

| Software        | TMS34082 Demonstration Software Tool Kit                                                                      | Contact TI     |

|                 | TMS34082 Software Tool Kit                                                                                    | TMDS3440808201 |

|                 | TMS34082 3-D Graphics Library                                                                                 | Contact TI     |

|                 | TIGA Software Developer's Kit<br>(includes the TMS340 Family Code Generation Tools and C Debugger for the PC) | TMS340SDK-PC   |

| Hardware        | TMS34020 Software Development Board (SDB20)                                                                   | TMS3460120000  |

|                 | TMS34082 SRAM Upgrade Kit                                                                                     | TMDS3481800-02 |

# 1.8 Technical Assistance

The Texas Instruments Datapath VLSI Products Systems Engineering group is a resource available to help you in the selection of TI's high-performance FPUs, such as the TMS34082 Graphics Floating-Point Processor. Located in Dallas, the group works directly with designers to provide ready answers to device-related questions and also prepares a variety of applications information. The phone number for the DVP Systems Engineering hotline is (214) 997-3970.

# **Chapter 2**

# **Pinout and Pin Descriptions**

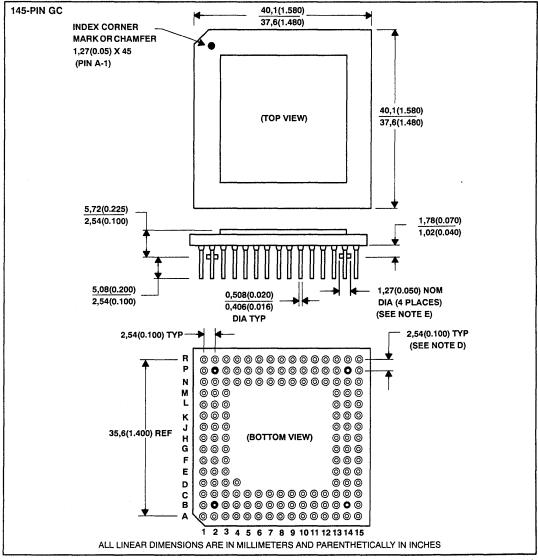

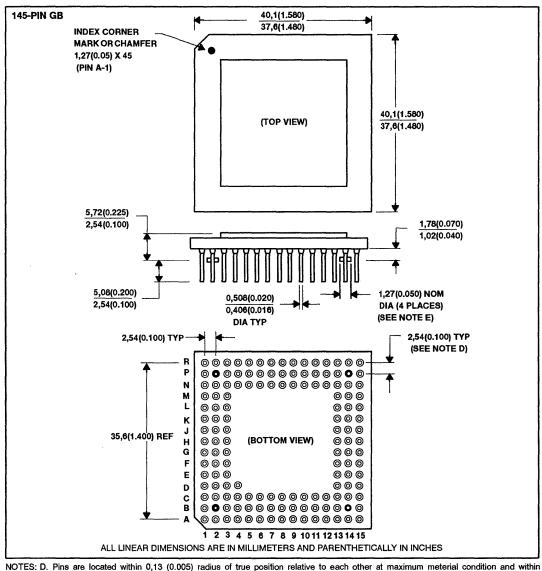

This chapter illustrates the TMS34082 pinouts and provides detailed descriptions of the TMS34082 signals. For mechanical dimensions of the TMS34082A packages, please refer to the data sheet in Appendix B. For mechanical dimensions of the SMJ34082A packages, please refer to the data sheet in Appendix C.

## 2.1 Pinout

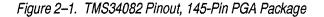

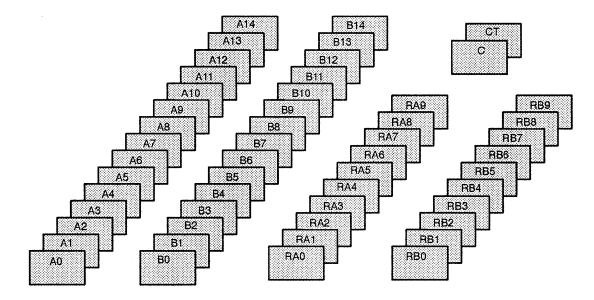

The TMS34082A and the SMJ34082A are offered in a ceramic, 145-pin grid array (PGA) package (GC). Figure 2-1 shows the 145-pin PGA pinout.

(TOP VIEW)

Table 2–1. Pin Assignments (PGA Package)

|     | Pin   |     | Pin   |     | Pin             |     | Pin   |     | Pin    |  |  |

|-----|-------|-----|-------|-----|-----------------|-----|-------|-----|--------|--|--|

| GC# | Name  | GC# | Name  | GC# | Name            | GC# | Name  | GC# | Name   |  |  |

| A1  | NC    | B15 | LAD27 | F1  | MSD10           | K15 | RDY   | P2  | NC     |  |  |

| A2  | LAD1  | C1  | MSD4  | F2  | MSD9            | L1  | MSD18 | P3  | MSD29  |  |  |

| A3  | LAD3  | C2  | MSD3  | F3  | Vcc             | 1.2 | MSD21 | P4  | MSD31  |  |  |

| A4  | LAD5  | C3  | MSD0  | F13 | CORDY           | L3  | MSD23 | P5  | MSA1   |  |  |

| A5  | LAD8  | C4  | VSS   | F14 | ALTCH           | L13 | VSS   | P6  | MSA3   |  |  |

| A6  | LAD9  | C5  | Vcc   | F15 | CAS             | L14 | CIDO  | P7  | MSA6   |  |  |

| A7  | LAD11 | C6  | LAD6  | G1  | MSD13           | L15 | CID2  | P8  | MSA8   |  |  |

| A8  | LAD12 | C7  | VSS   | G2  | MSD12           | M1  | MSD20 | P9  | MSA10  |  |  |

| A9  | LAD13 | C8  | Vcc   | G3  | MSD11           | M2  | MSD24 | P10 | MSA13  |  |  |

| A10 | LAD15 | C9  | VSS   | G13 | WE              | МЗ  | VSS   | P11 | MWR    |  |  |

| A11 | LAD17 | C10 | Vcc   | G14 | EC1             | M13 | Vcc   | P12 | MOE    |  |  |

| A12 | LAD19 | C11 | LAD21 | G15 | EC0             | M14 | LCLK1 | P13 | INTG   |  |  |

| A13 | LAD22 | C12 | VSS   | H1  | MSD14           | M15 | LCLK2 | P14 | BUSFLT |  |  |

| A14 | LAD24 | C13 | LAD25 | H2  | TDO             | N1  | MSD22 | P15 | RAS    |  |  |

| A15 | NC    | C14 | LAD26 | H3  | VSS             | N2  | MSD26 | R1  | NC     |  |  |

| B1  | MSD1  | C15 | LAD29 | H13 | VSS             | N3  | Vcc   | R2  | MSD27  |  |  |

| B2  | NC    | D1  | MSD6  | H14 | LOE             | N4  | MSD28 | R3  | MSD30  |  |  |

| B3  | LAD0  | D2  | MSD5  | H15 | TDI             | N5  | Vss   | R4  | MSA0   |  |  |

| B4  | LAD2  | D3  | MSD2  | J1  | MSD15           | N6  | Vcc   | R5  | MSA2   |  |  |

| B5  | LAD4  | D4  | NC    | J2  | MSD16           | N7  | MSA5  | R6  | MSA4   |  |  |

| B6  | LAD7  | D13 | Vcc   | J3  | Vcc             | N8  | VSS   | R7  | MSA7   |  |  |

| B7  | LAD10 | D14 | LAD28 | J13 | CC              | N9  | Vcc   | R8  | TCK    |  |  |

| B8  | TMS   | D15 | LAD31 | J14 | MASTER          | N10 | MSA14 | R9  | MSA9   |  |  |

| B9  | LAD14 | E1  | MSD8  | J15 | CLK             | N11 | VSS   | R10 | MSA11  |  |  |

| B10 | LAD16 | E2  | MSD7  | K1  | MSD17           | N12 | MAE   | R11 | MSA12  |  |  |

| B11 | LAD18 | E3  | VSS   | K2  | MSD19           | N13 | LRDY  | R12 | MSA15  |  |  |

| B12 | LAD20 | E13 | VSS   | КЗ  | V <sub>SS</sub> | N14 | SF    | R13 | DS/CS  |  |  |

| B13 | LAD23 | E14 | LAD30 | K13 | CID1            | N15 | RESET | R14 | MCE    |  |  |

| B14 | NC    | E15 | COINT | K14 | INTR            | P1  | MSD25 | R15 | NC     |  |  |

| Ρ      | in  | Pin    |     | F     | in  | P     | in  |      | Pin |

|--------|-----|--------|-----|-------|-----|-------|-----|------|-----|

| Name   | GC# | Name   | GC# | Name  | GC# | Name  | GC# | Name | GC# |

| ALTCH  | F14 | LAD14  | B9  | MSA3  | P6  | MSD16 | J2  | тск  | R8  |

| BUSFLT | P14 | LAD15  | A10 | MSA4  | R6  | MSD17 | K1  | TDI  | H15 |

| CAS    | F15 | LAD16  | B10 | MSA5  | N7  | MSD18 | L1  | TDO  | H2  |

| CC     | J13 | LAD17  | A11 | MSA6  | P7  | MSD19 | K2  | TMS  | B8  |

| CIDO   | L14 | LAD18  | B11 | MSA7  | R7  | MSD20 | M1  | Vcc  | C5  |

| CID1   | K13 | LAD19  | A12 | MSA8  | P8  | MSD21 | L2  | Vcc  | C8  |

| CID2   | L15 | LAD20  | B12 | MSA9  | R9  | MSD22 | N1  | Vcc  | C10 |

| CLK    | J15 | LAD21  | C11 | MSA10 | P9  | MSD23 | L3  | Vcc  | D13 |

| COINT  | E15 | LAD22  | A13 | MSA11 | R10 | MSD24 | M2  | VCC  | F3  |

| CORDY  | F13 | LAD23  | B13 | MSA12 | R11 | MSD25 | P1  | Vcc  | J3  |

| DS/CS  | R13 | LAD24  | A14 | MSA13 | P10 | MSD26 | N2  | Vcc  | M13 |

| EC0    | G15 | LAD25  | C13 | MSA14 | N10 | MSD27 | R2  | Vcc  | N3  |

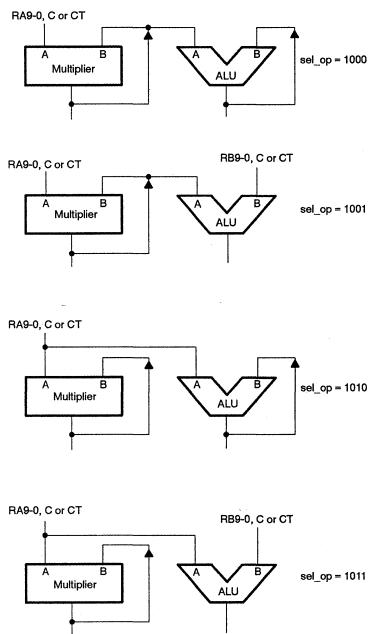

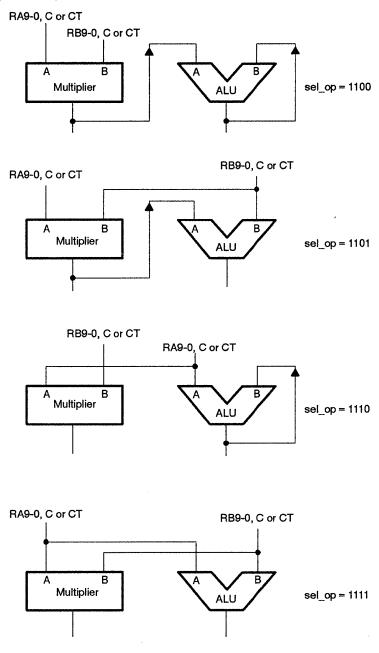

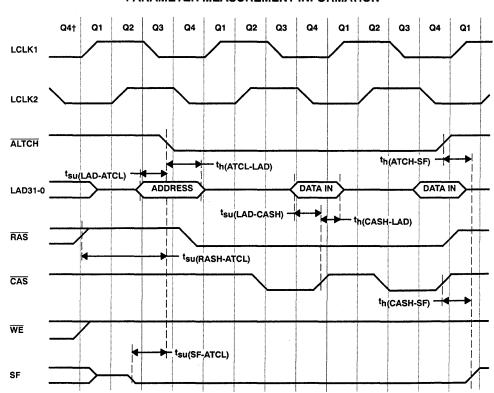

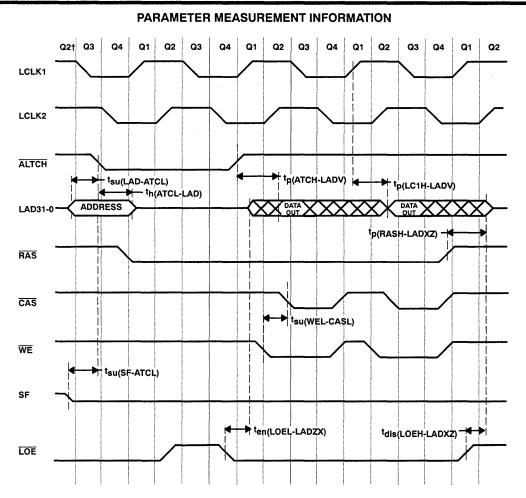

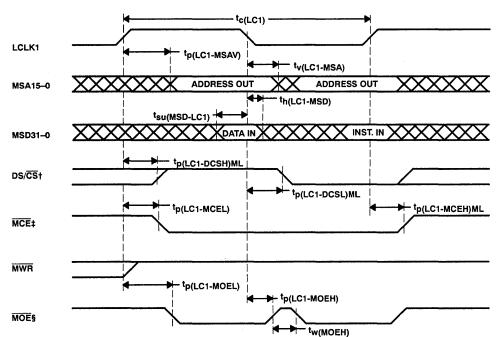

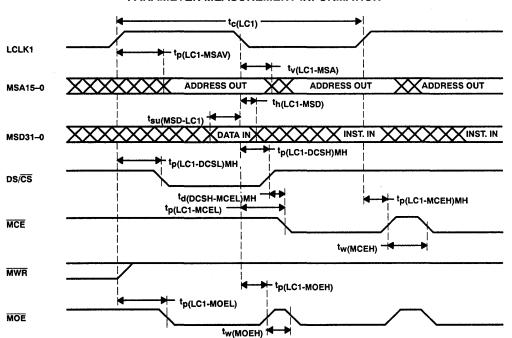

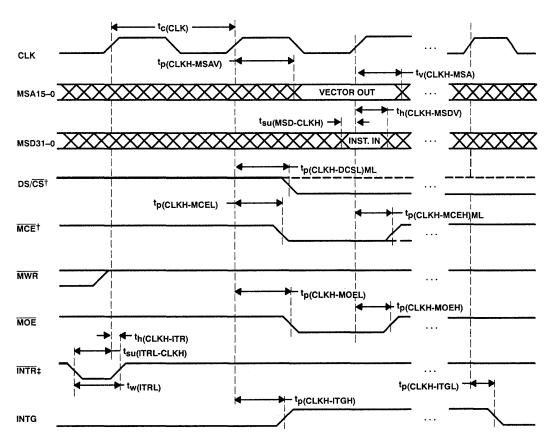

| EC1    | G14 | LAD26  | C14 | MSA15 | R12 | MSD28 | N4  | Vcc  | N6  |