## ELECTRONIC DESIGN AUTOMATION

MK

LAUNG-TERNG WANG . YAO-WEN CHANG **KWANG-TING (TIM) CHENG**

# **Electronic Design Automation**

### The Morgan Kaufmann Series in Systems on Silicon

Series Editor Wayne Wolf Georgia Institute of Technology

The Designer's Guide to VHDL, Second Edition Peter J. Ashenden

The System Designer's Guide to VHDL-AMS Peter J. Ashenden, Gregory D. Peterson, and Darrell A. Teegarden

Modeling Embedded Systems and SoCs Axel Jantsch

ASIC and FPGA Verification: A Guide to Component Modeling Richard Munden

Multiprocessor Systems-on-Chips Edited by Ahmed Amine Jerraya and Wayne Wolf

*Functional Verification* Bruce Wile, John Goss, and Wolfgang Roesner

*Customizable and Configurable Embedded Processors* Edited by Paolo Ienne and Rainer Leupers

Networks-on-Chips: Technology and Tools Edited by Giovanni De Micheli and Luca Benini

VLSI Test Principles & Architectures Edited by Laung-Terng Wang, Cheng-Wen Wu, and Xiaoqing Wen

Designing SoCs with Configured Processors Steve Leibson

ESL Design and Verification Grant Martin, Andrew Piziali, and Brian Bailey

Aspect-Oriented Programming with e David Robinson

Reconfigurable Computing: The Theory and Practice of FPGA-Based Computation Edited by Scott Hauck and André DeHon

System-on-Chip Test Architectures Edited by Laung-Terng Wang, Charles Stroud, and Nur Touba

Verification Techniques for System-Level Design Masahiro Fujita, Indradeep Ghosh, and Mukul Prasad

VHDL-2008: Just the New Stuff Peter J. Ashenden and Jim Lewis

On-Chip Communication Architectures: System on Chip Interconnect Sudeep Pasricha and Nikil Dutt

Embedded DSP Processor Design: Application Specific Instruction Set Processors Dake Liu

Processor Description Languages: Applications and Methodologies Edited by Prabhat Mishra and Nikil Dutt

Three-dimensional Integrated Circuit Design Vasilis F. Pavlidis and Eby G. Friedman

Electronic Design Automation: Synthesis, Verification, and Test Edited by Laung-Terng Wang, Kwang-Ting (Tim) Cheng, Yao-Wen Chang

# Electronic Design Automation: Synthesis, Verification, and Test

**Edited by**

Laung-Terng Wang Yao-Wen Chang Kwang-Ting (Tim) Cheng

AMSTERDAM • BOSTON • HEIDELBERG • LONDON NEW YORK • OXFORD • PARIS • SAN DIEGO SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO

Morgan Kaufmann Publishers is an imprint of Elsevier

Morgan Kaufmann Publishers is an imprint of Elsevier. 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA

This book is printed on acid-free paper.

© 2009 by Elsevier Inc. All rights reserved.

Designations used by companies to distinguish their products are often claimed as trademarks or registered trademarks. In all instances in which Morgan Kaufmann Publishers is aware of a claim, the product names appear in initial capital or all capital letters. Readers, however, should contact the appropriate companies for more information regarding trademarks and registration.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopying, scanning, or otherwise—without prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, E-mail: permissions@elsevier.com. You may also complete your request online via the Elsevier homepage (http://elsevier.com), by selecting "Support & Contact" then "Copyright and Permission" and then "Obtaining Permissions."

### Library of Congress Cataloging-in-Publication Data

Electronic design automation : synthesis, verification, and test/edited by Laung-Terng Wang, Yao-Wen Chang, Kwang-Ting (Tim) Cheng.

p. cm. ISBN: 978-0-12-374364-0 (alk. paper) 1. Electronic circuit design–Data processing. 2. Computer-aided design. I. Wang, Laung-Terng, II. Chang, Yao-Wen. III. Cheng, Kwang-Ting, 1961– TK7867.E4227 2008 621.39'5–dc22

For information on all Morgan Kaufmann publications, visit our Web site at www.mkp.com

Printed in the United States of America

08 09 10 11 12 10 9 8 7 6 5 4 3 2 1

Working together to grow

libraries in developing countries

www.elsevier.com

www.bookaid.org

ELSEVIER

BOOK AID International

Sabre Foundation

2008041788

## Contents

| Preface         |                                                                | xxi    |

|-----------------|----------------------------------------------------------------|--------|

| In the Classroo | m                                                              | XXV    |

| Acknowledgme    | ents                                                           | xxvii  |

| Contributors    |                                                                | xxix   |

| About the Edite | ors                                                            | xxxiii |

|                 |                                                                |        |

| CHAPTER 1       | Introduction                                                   | 1      |

|                 | Charles E. Stroud, Lang-Terng (LT.) Wang, and<br>Yao-Wen Chang |        |

| 1.1             | Overview of electronic design automation                       | 2      |

|                 | 1.1.1 Historical perspective                                   | 2      |

|                 | 1.1.2 VLSI design flow and typical EDA flow                    | 4      |

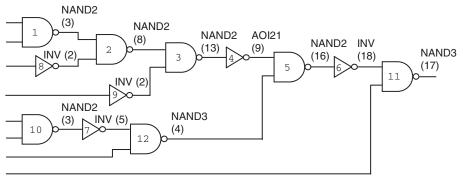

|                 | 1.1.3 Typical EDA implementation examples                      | 9      |

|                 | 1.1.4 Problems and challenges                                  | 12     |

| 1.2             | Logic design automation.                                       | 13     |

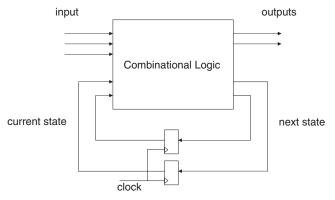

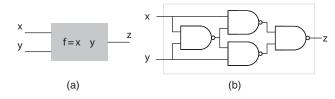

|                 | 1.2.1 Modeling                                                 | 13     |

|                 | 1.2.2 Design verification                                      | 14     |

|                 | 1.2.3 Logic synthesis                                          | 17     |

| 1.3             | Test automation                                                | 18     |

|                 | 1.3.1 Fault models                                             | 19     |

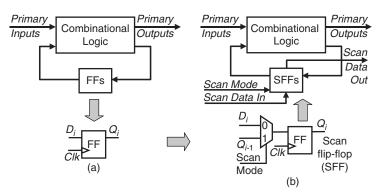

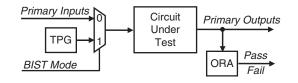

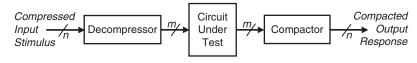

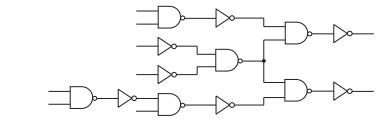

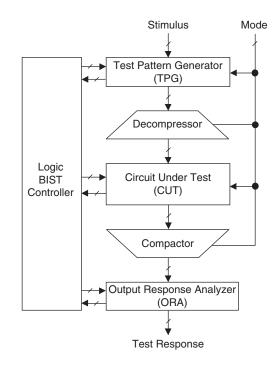

|                 | 1.3.2 Design for testability                                   | 21     |

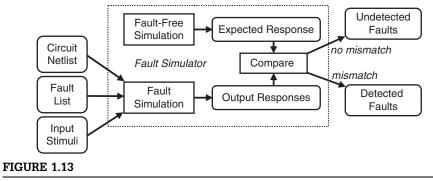

|                 | 1.3.3 Fault simulation and test generation                     | 23     |

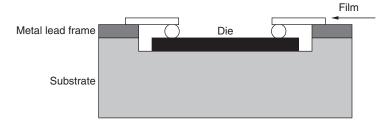

|                 | 1.3.4 Manufacturing test                                       | 24     |

| 1.4             | Physical design automation                                     | 25     |

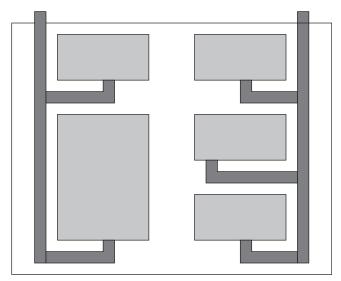

|                 | 1.4.1 Floorplanning                                            | 27     |

|                 | 1.4.2 Placement                                                | 27     |

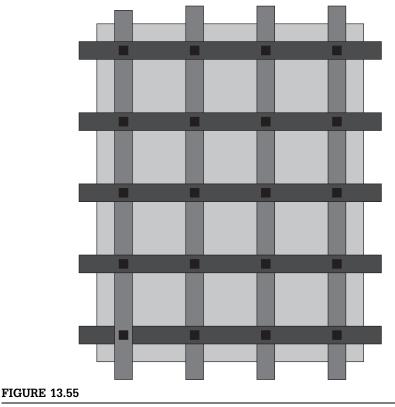

|                 | 1.4.3 Routing                                                  | 28     |

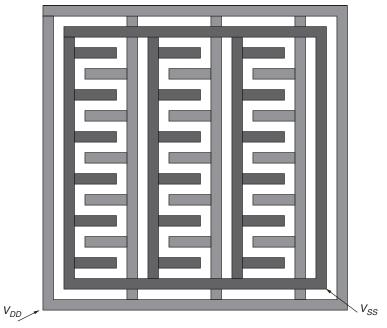

|                 | 1.4.4 Synthesis of clock and power/ground networks .           | 29     |

| 1.5             | Concluding remarks                                             | 32     |

| 1.6             | Exercises                                                      | 33     |

| Α               | cknowledgments                                                 | 35     |

| R               | leferences                                                     | 35     |

| <b>CHAPTER 2</b> | Fundamentals of CMOS design                                                                               | 39   |

|------------------|-----------------------------------------------------------------------------------------------------------|------|

|                  | Xingbao Chen and Nur A. Touba                                                                             |      |

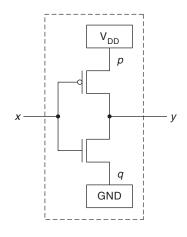

| 2.1              | Introduction                                                                                              | 39   |

| 2.2              | Integrated circuit technology                                                                             | 40   |

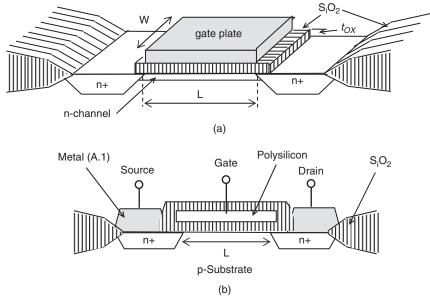

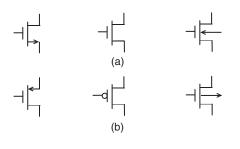

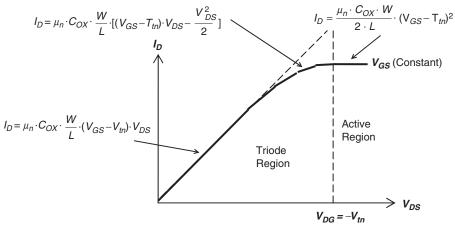

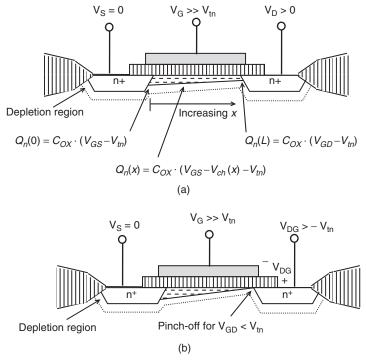

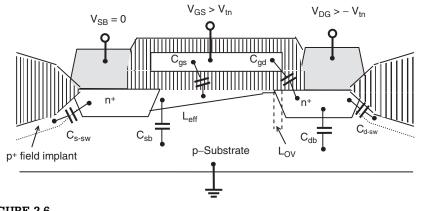

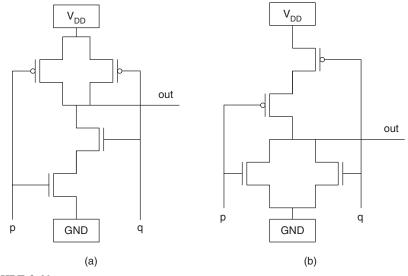

|                  | 2.2.1 MOS transistor                                                                                      | 41   |

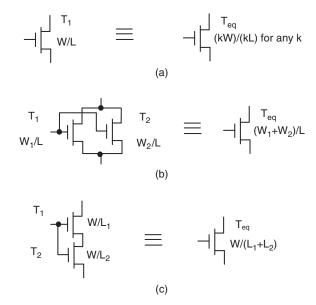

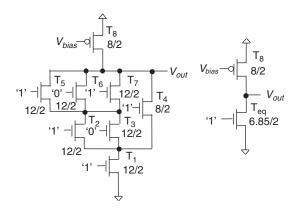

|                  | 2.2.2 Transistor equivalency                                                                              | 44   |

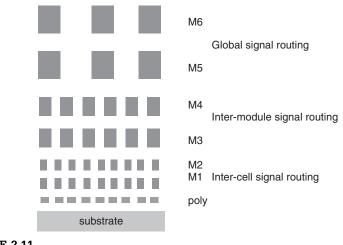

|                  | 2.2.3 Wire and interconnect.                                                                              | 46   |

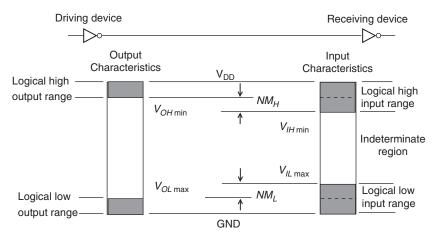

|                  | 2.2.4 Noise margin                                                                                        | 48   |

| 2.3              | CMOS logic                                                                                                | 49   |

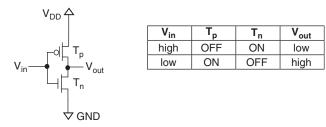

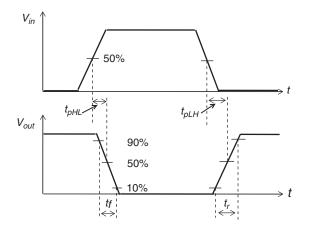

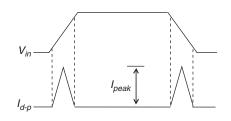

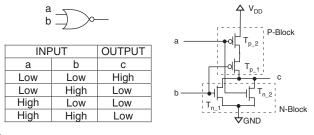

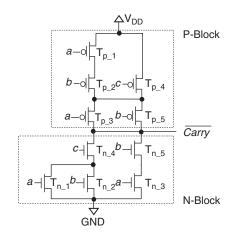

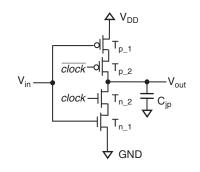

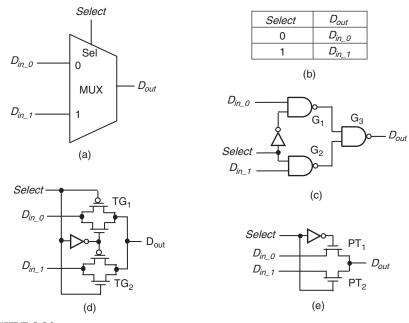

|                  | 2.3.1 CMOS inverter and analysis                                                                          | 49   |

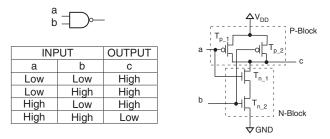

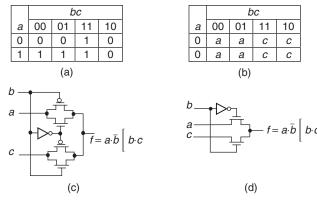

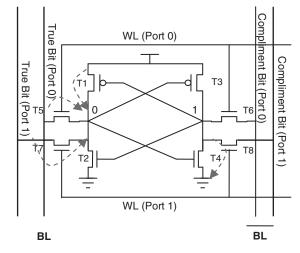

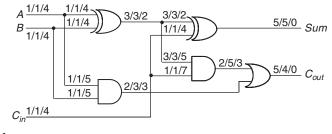

|                  | 2.3.2 Design of CMOS logic gates and circuit blocks                                                       |      |

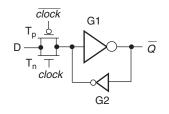

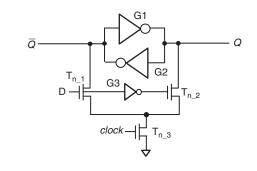

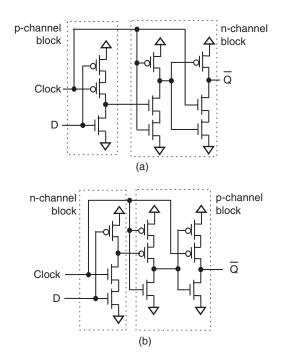

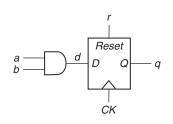

|                  | 2.3.3 Design of latches and flip-flops                                                                    |      |

|                  | 2.3.4 Optimization techniques for high performance                                                        |      |

| 2.4              | Integrated circuit design techniques                                                                      |      |

|                  | 2.4.1 Transmission-gate/pass-transistor logic                                                             |      |

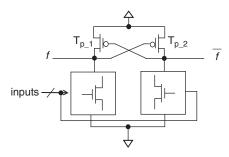

|                  | 2.4.2 Differential CMOS logic                                                                             |      |

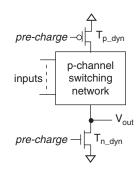

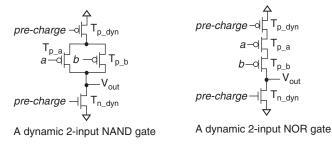

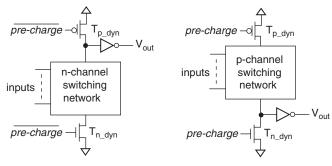

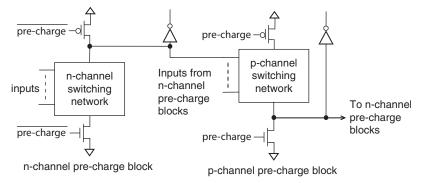

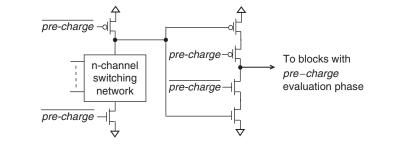

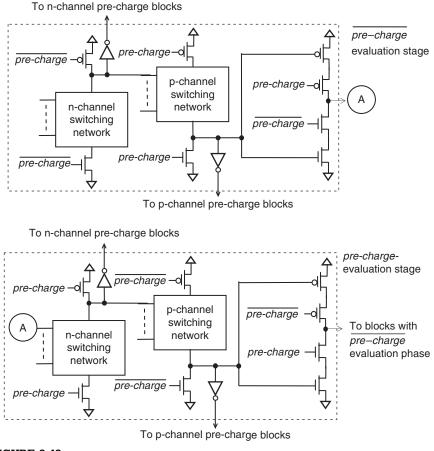

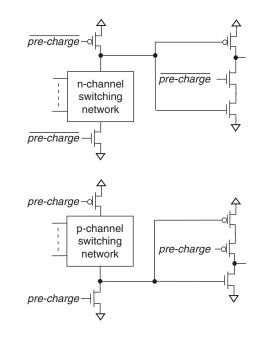

|                  | 2.4.3 Dynamic pre-charge logic                                                                            |      |

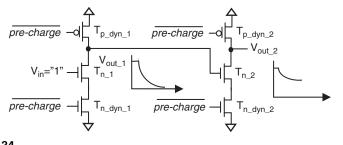

|                  | 2.4.4 Domino logic                                                                                        |      |

|                  | 2.4.5 No-race logic                                                                                       |      |

|                  | 2.4.6 Single-phase logic                                                                                  |      |

| 2.5              | CMOS physical design                                                                                      |      |

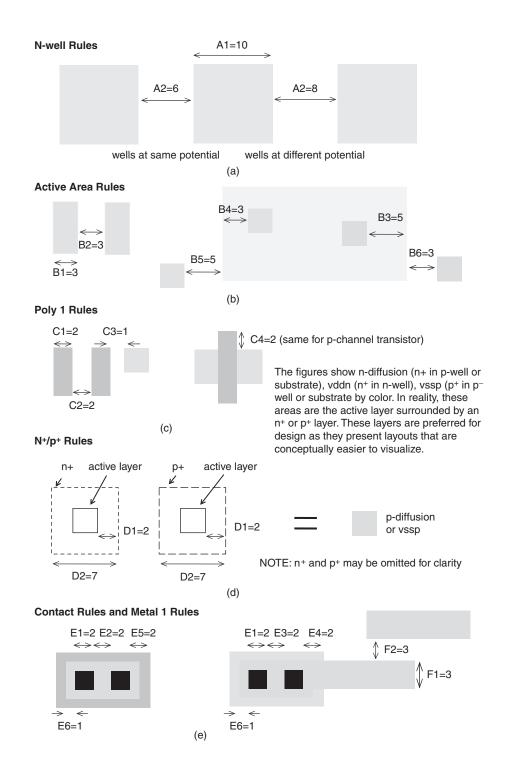

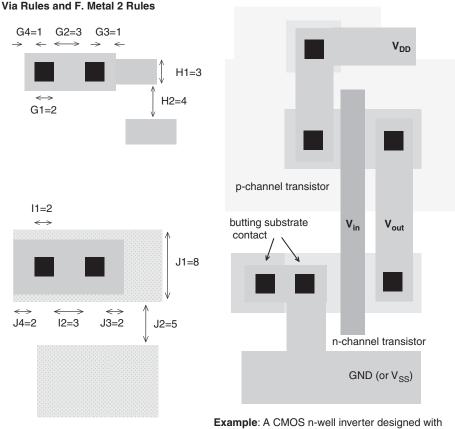

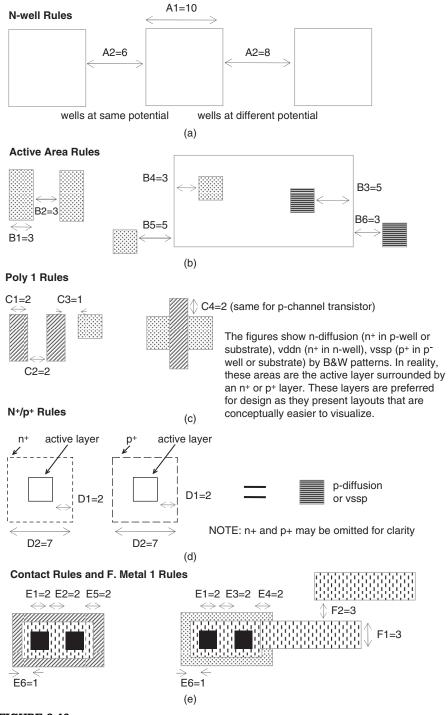

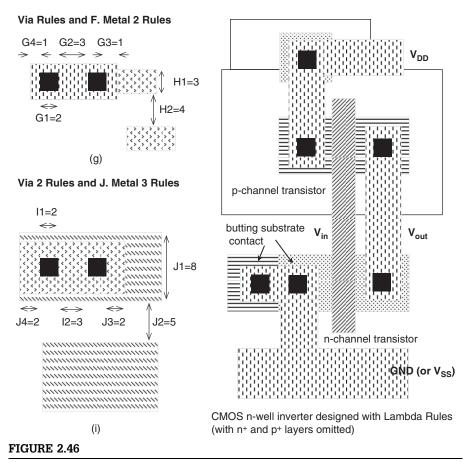

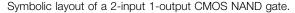

|                  | 2.5.1 Layout design rules                                                                                 |      |

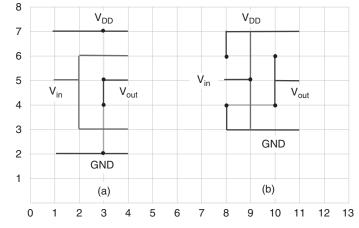

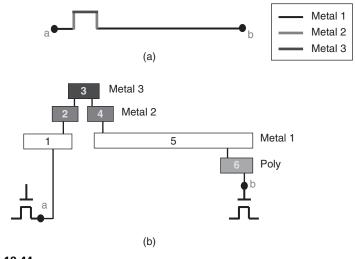

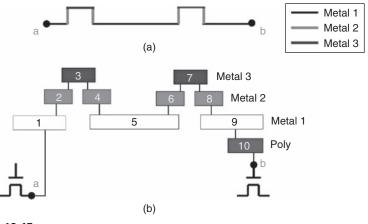

|                  | 2.5.2 Stick diagram                                                                                       |      |

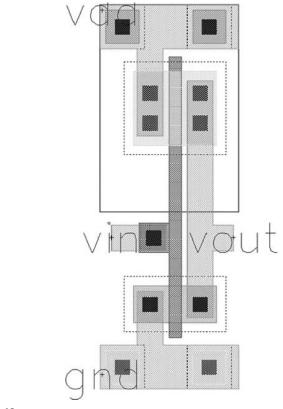

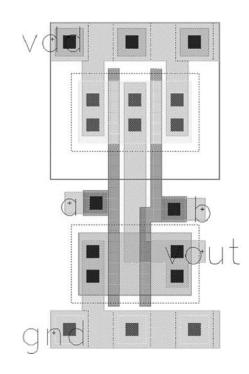

| 0.0              | 2.5.3 Layout design                                                                                       |      |

| 2.6              | Low-power circuit design techniques                                                                       |      |

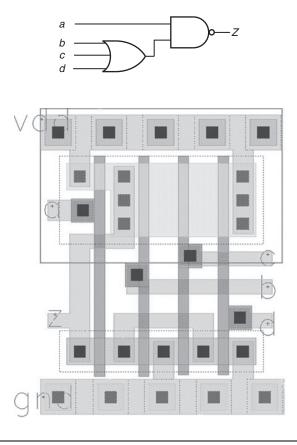

|                  | 2.6.1 Clock-gating                                                                                        |      |

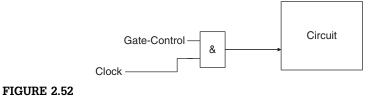

|                  | 2.6.2 Power-gating.                                                                                       |      |

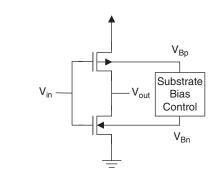

|                  | 2.6.3 Substrate biasing                                                                                   |      |

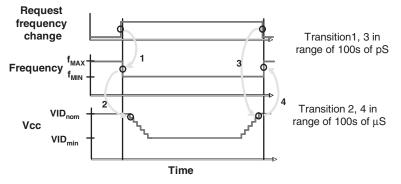

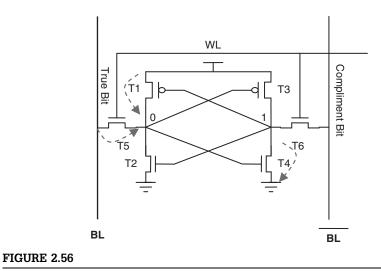

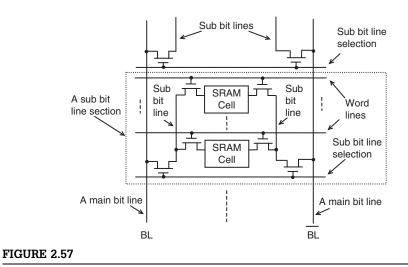

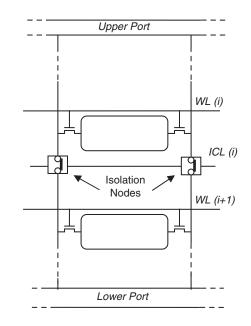

|                  | <ul><li>2.6.4 Dynamic voltage and frequency scaling</li><li>2.6.5 Low-power cache memory design</li></ul> |      |

| 27               | Concluding remarks.                                                                                       |      |

|                  | Exercises                                                                                                 |      |

|                  | cknowledgments.                                                                                           | -    |

|                  | eferences                                                                                                 |      |

|                  |                                                                                                           |      |

| CHAPTER 3        | Design for testability                                                                                    | . 97 |

|                  | Laung-Terng (LT.) Wang                                                                                    |      |

| 3.1              | Introduction                                                                                              | 98   |

| 3.2              | Testability analysis                                                                                      | 100  |

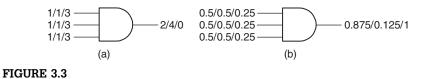

| 3.2.1 SCOAP testability analysis                     |

|------------------------------------------------------|

| 3.2.1.1 Combinational controllability and            |

| observability calculation                            |

| 3.2.1.2 Sequential controllability and observability |

| calculation                                          |

| 3.2.2 Probability-based testability analysis         |

| 3.2.3 Simulation-based testability analysis          |

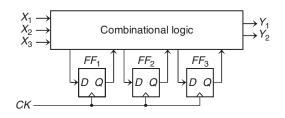

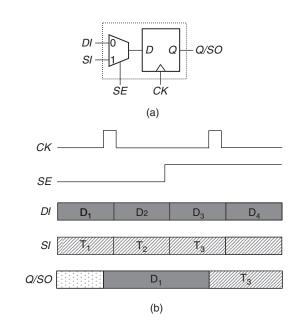

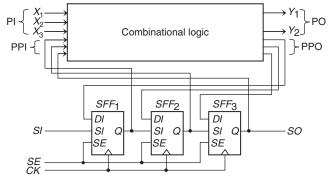

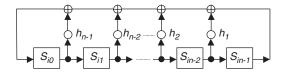

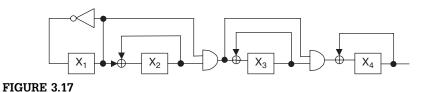

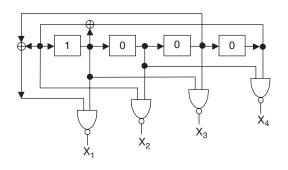

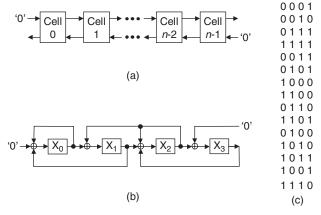

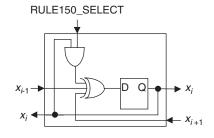

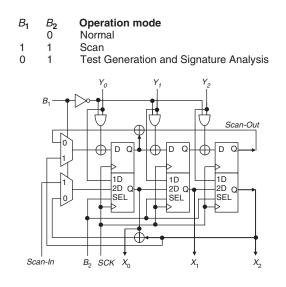

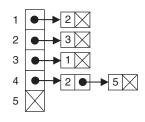

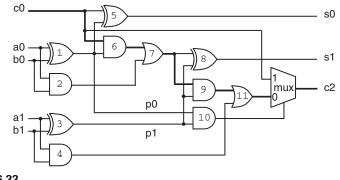

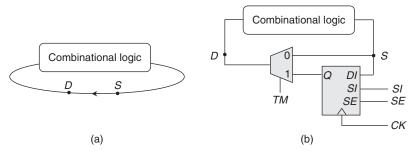

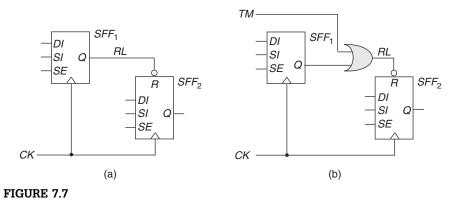

| <b>3.3</b> Scan design                               |

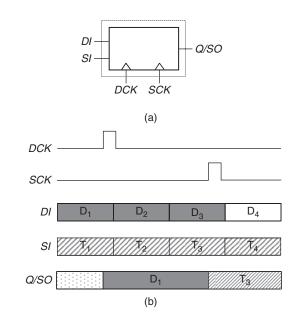

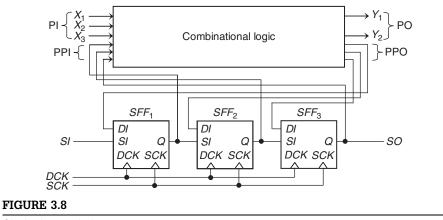

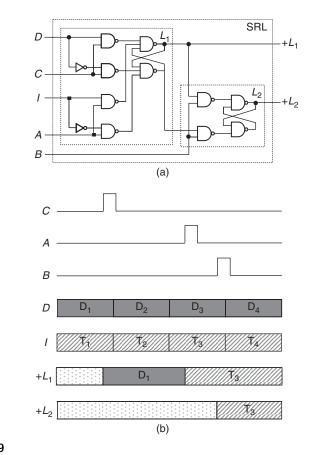

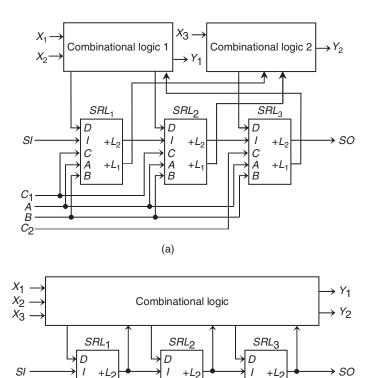

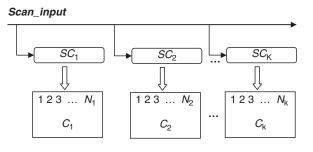

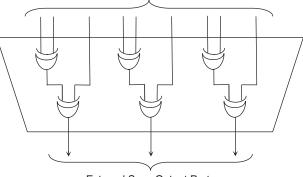

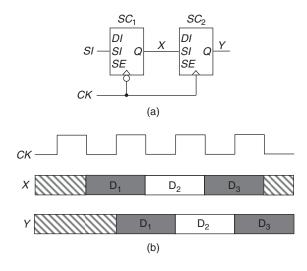

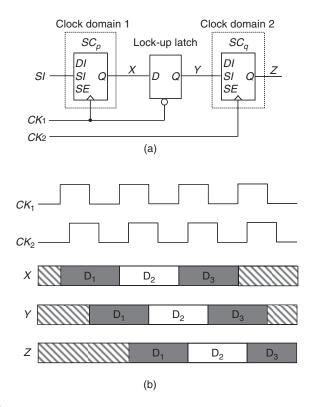

| 3.3.1 Scan architectures                             |

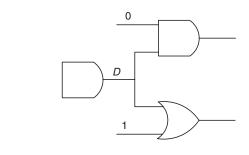

| 3.3.1.1 Muxed-D scan design                          |

| 3.3.1.2 Clocked-scan design                          |

| 3.3.1.3 LSSD scan design                             |

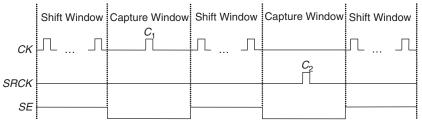

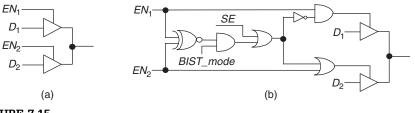

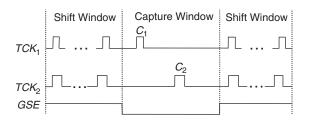

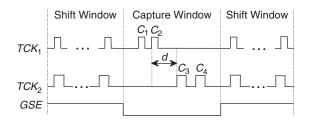

| 3.3.2 At-speed testing                               |

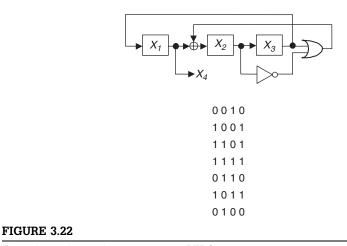

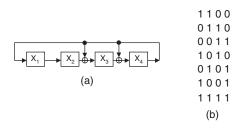

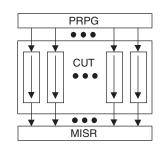

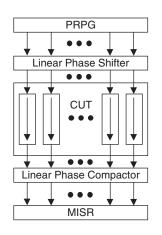

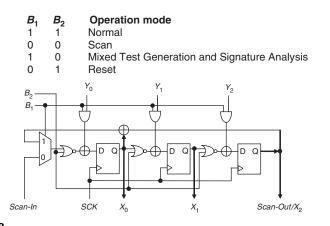

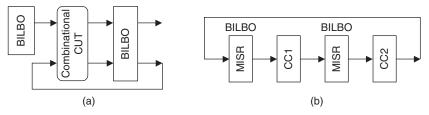

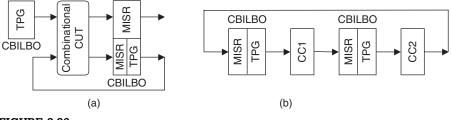

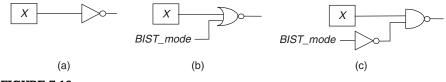

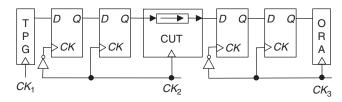

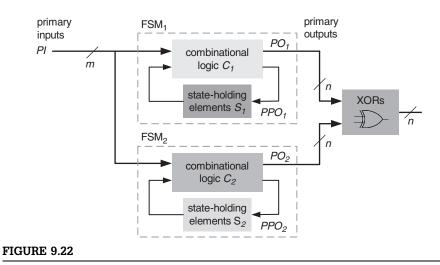

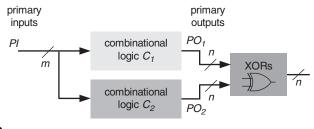

| <b>3.4</b> Logic built-in self-test                  |

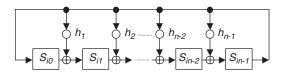

| 3.4.1 Test pattern generation                        |

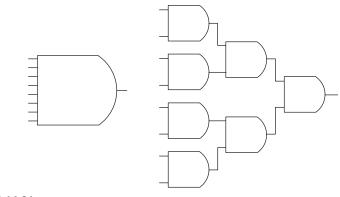

| 3.4.1.1 Exhaustive testing                           |

| 3.4.1.2 Pseudo-random testing                        |

| 3.4.1.3 Pseudo-exhaustive testing                    |

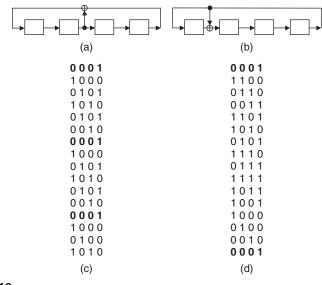

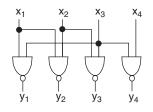

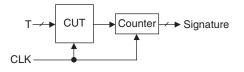

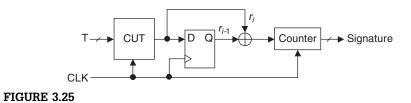

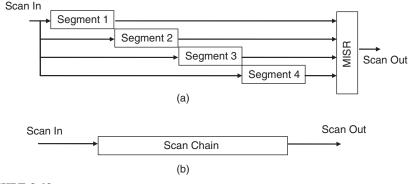

| 3.4.2 Output response analysis                       |

| 3.4.2.1 Ones count testing                           |

| 3.4.2.2 Transition count testing                     |

| 3.4.2.3 Signature analysis                           |

| 3.4.3 Logic BIST architectures                       |

| 3.4.3.1 Self-testing with MISR and parallel          |

| SRSG (STUMPS)                                        |

| 3.4.3.2 Built-in logic block observer (BILBO)136     |

| 3.4.3.3 Concurrent built-in logic block              |

| observer (CBILBO)                                    |

| 3.4.4 Industry practices                             |

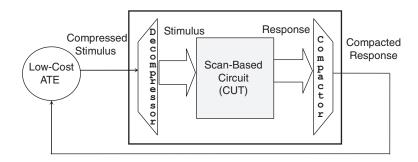

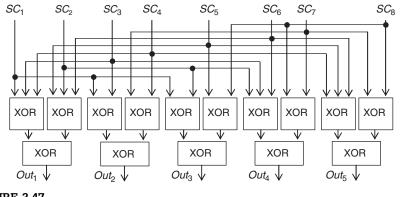

| <b>3.5</b> Test Compression                          |

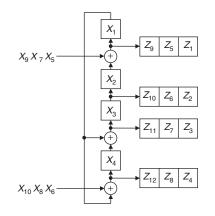

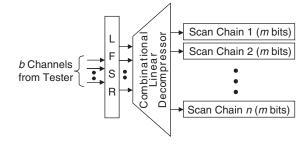

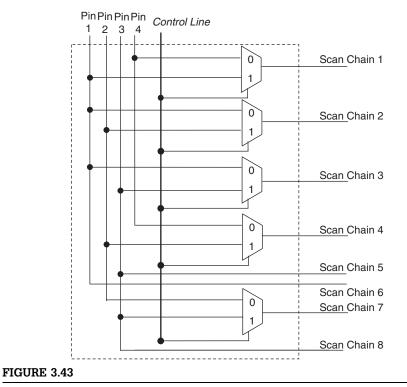

| 3.5.1 Circuits for test stimulus compression         |

| 3.5.1.1 Linear-decompression-based schemes141        |

| 3.5.1.2 Broadcast-scan-based schemes                 |

| 3.5.2 Circuits for test response compaction          |

| 3.5.2.1 Combinational compaction                     |

| 3.5.2.2 Sequential compaction                        |

| 3.5.3 Industry practices                             |

| <b>3.6</b> Concluding remarks                        |

| <b>3.7</b> Exercises                                 |

| Acknowledgments                                      |

| References                                           |

| <b>CHAPTER 4</b> | Fundamentals of algorithms 17                                       | '3 |

|------------------|---------------------------------------------------------------------|----|

|                  | Chung-Yang (Ric) Huang, Chao-Yue Lai, and<br>Kwang-Ting (Tim) Cheng |    |

| 4.1              | Introduction                                                        | 73 |

| 4.2              | Computational complexity                                            | 75 |

|                  | 4.2.1 Asymptotic notations                                          | 77 |

|                  | 4.2.1.1 O-notation                                                  | 78 |

|                  | 4.2.1.2 $\Omega$ -notation and $\Theta$ -notation                   | 79 |

|                  | 4.2.2 Complexity classes                                            | 30 |

|                  | 4.2.2.1 Decision problems versus optimization                       |    |

|                  | problems                                                            | 30 |

|                  | 4.2.2.2 The complexity classes P versus NP 18                       |    |

|                  | 4.2.2.3 The complexity class NP-complete                            |    |

|                  | 4.2.2.4 The complexity class NP-hard                                |    |

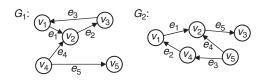

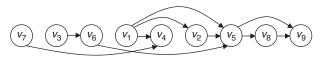

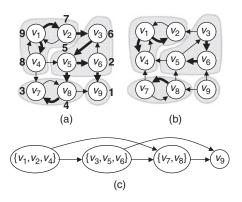

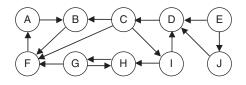

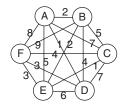

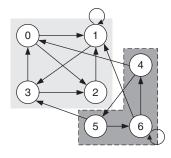

| 4.3              | Graph algorithms                                                    |    |

|                  | 4.3.1 Terminology                                                   |    |

|                  | 4.3.2 Data structures for representations of graphs 18              |    |

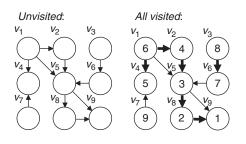

|                  | 4.3.3 Breadth-first search and depth-first search                   |    |

|                  | 4.3.3.1 Breadth-first search                                        |    |

|                  | 4.3.3.2 Depth-first search                                          |    |

|                  | 4.3.4 Topological sort                                              |    |

|                  | 4.3.5 Strongly connected component                                  |    |

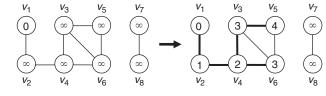

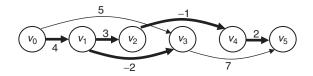

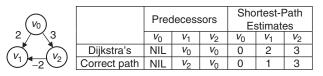

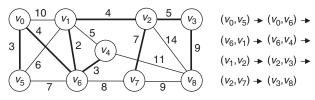

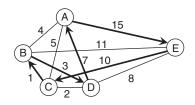

|                  | 4.3.6 Shortest and longest path algorithms                          |    |

|                  | 4.3.6.2 Shortest path algorithms on directed                        | ,  |

|                  | acyclic graphs                                                      | )6 |

|                  | 4.3.6.3 Dijkstra's algorithm                                        |    |

|                  | 4.3.6.4 The Bellman-Ford algorithm                                  |    |

|                  | 4.3.6.5 The longest-path problem                                    |    |

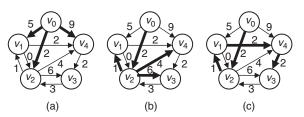

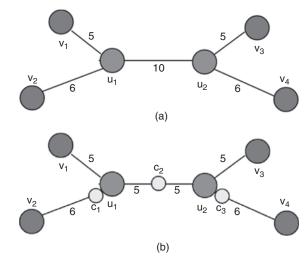

|                  | 4.3.7 Minimum spanning tree                                         |    |

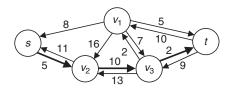

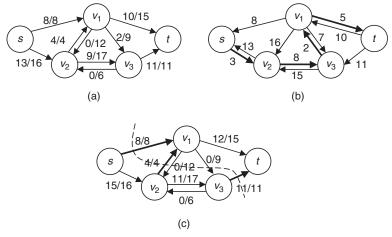

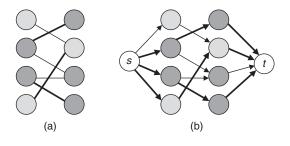

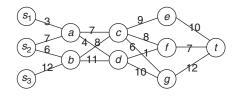

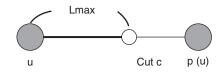

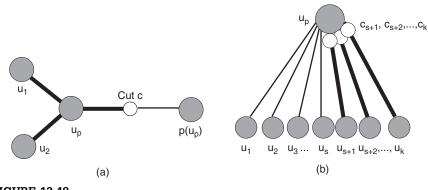

|                  | 4.3.8 Maximum flow and minimum cut                                  |    |

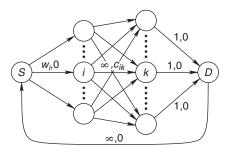

|                  | 4.3.8.1 Flow networks and the maximum-flow                          |    |

|                  | problem                                                             | )2 |

|                  | 4.3.8.2 Augmenting paths and residual                               |    |

|                  | networks                                                            | )3 |

|                  | 4.3.8.3 The Ford-Fulkerson method and the                           |    |

|                  | Edmonds-Karp algorithm                                              | )4 |

|                  | 4.3.8.4 Cuts and the max-flow min-cut                               |    |

|                  | theorem                                                             | )5 |

|                  | 4.3.8.5 Multiple sources and sinks and maximum                      |    |

|                  | bipartite matching                                                  | )7 |

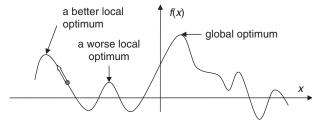

| 4.4       | Heuristic algorithms                                  | .208     |

|-----------|-------------------------------------------------------|----------|

|           | 4.4.1 Greedy algorithm                                |          |

|           | 4.4.1.1 Greedy-choice property                        | 210      |

|           | 4.4.1.2 Optimal substructure                          | .211     |

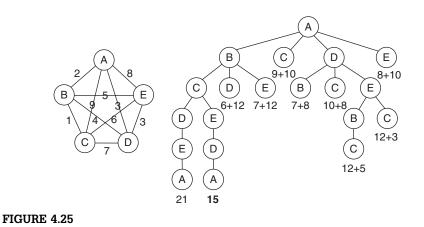

|           | 4.4.2 Dynamic programming                             | .211     |

|           | 4.4.2.1 Overlapping subproblems                       | .213     |

|           | 4.4.2.2 Optimal substructure                          |          |

|           | 4.4.2.3 Memoization                                   | .214     |

|           | 4.4.3 Branch-and-bound                                |          |

|           | 4.4.4 Simulated annealing                             |          |

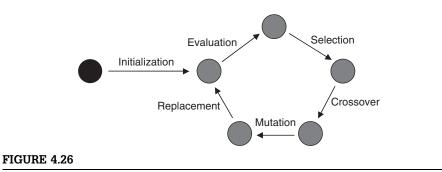

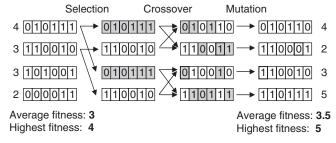

|           | 4.4.5 Genetic algorithms                              |          |

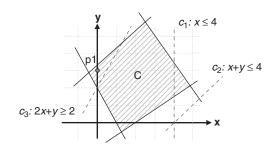

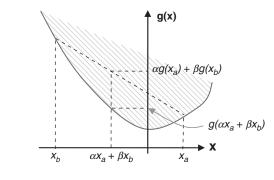

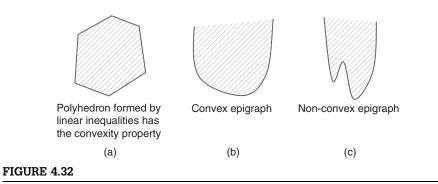

| 4.5       | Mathematical programming.                             | .221     |

|           | 4.5.1 Categories of mathematical programming          |          |

|           | problems                                              |          |

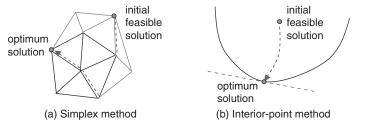

|           | 4.5.2 Linear programming (LP) problem                 |          |

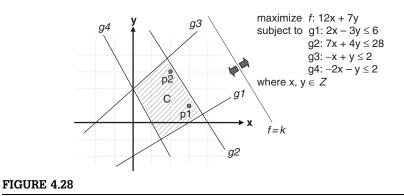

|           | 4.5.3 Integer linear programming (ILP) problem        | .223     |

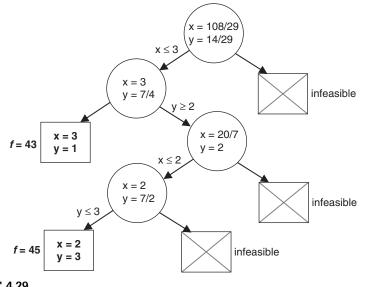

|           | 4.5.3.1 Linear programming relaxation and             | 224      |

|           | branch-and-bound procedure                            |          |

|           | 4.5.3.2 Cutting plane algorithm                       |          |

|           | 4.5.4 Convex optimization problem                     |          |

| 16        | Concluding remarks                                    |          |

|           | Exercises                                             |          |

|           | cknowledgments.                                       |          |

|           | eferences                                             |          |

|           |                                                       | .292     |

| CHAPTER 5 | Electronic system-level design and                    | <b>-</b> |

|           | high-level synthesis.                                 | 235      |

|           | Jianwen Zhu and Nikil Dutt                            |          |

| 5.1       | Introduction                                          | .236     |

|           | 5.1.1 ESL design methodology                          | .236     |

|           | 5.1.2 Function-based ESL methodology                  | .239     |

|           | 5.1.3 Architecture-based ESL methodology              | .241     |

|           | 5.1.4 Function architecture codesign methodology      | .243     |

|           | 5.1.5 High-level synthesis within an ESL              |          |

|           | design methodology                                    |          |

| 5.2       | Fundamentals of High-level synthesis.                 |          |

|           | 5.2.1 TinyC as an example for behavioral descriptions |          |

|           | 5.2.2 Intermediate representation in TinyIR           |          |

|           | 5.2.3 RTL representation in TinyRTL.                  | .253     |

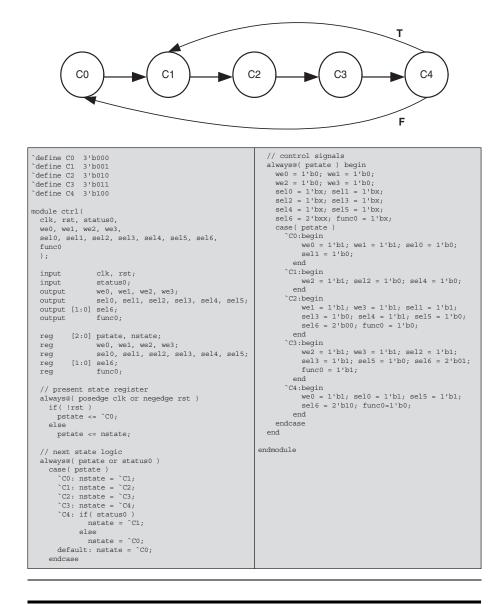

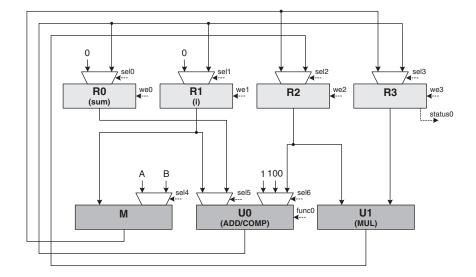

|           | 5.2.4 Structured hardware description in FSMD         | .254 |

|-----------|-------------------------------------------------------|------|

|           | 5.2.5 Quality metrics                                 | .257 |

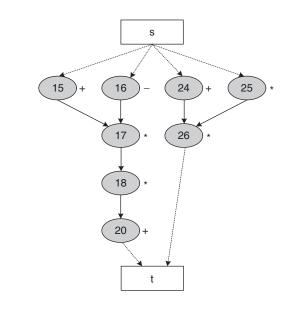

| 5.3       | High-level synthesis algorithm overview               | .261 |

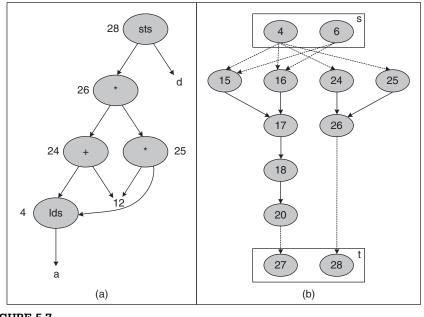

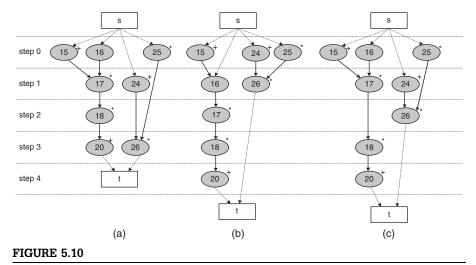

| 5.4       | Scheduling                                            | .263 |

|           | 5.4.1 Dependency test                                 | .263 |

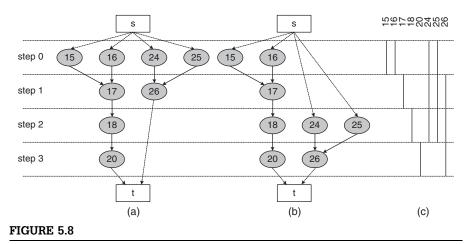

|           | 5.4.2 Unconstrained scheduling                        | .266 |

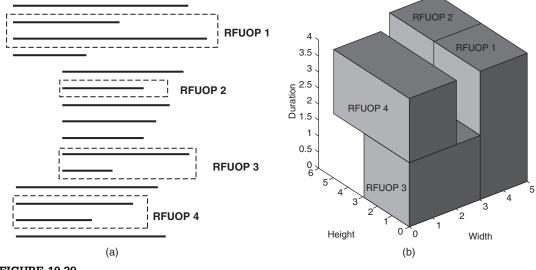

|           | 5.4.3 Resource-constrained scheduling                 | .268 |

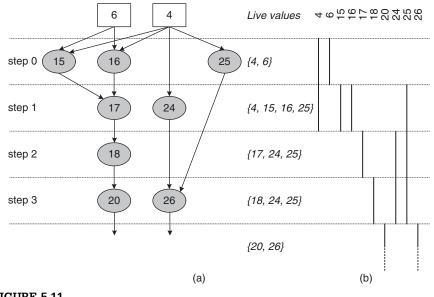

| 5.5       | Register binding                                      | .273 |

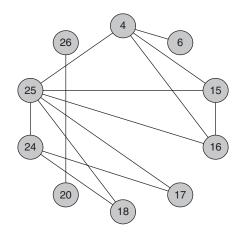

|           | 5.5.1 Liveness analysis                               | .273 |

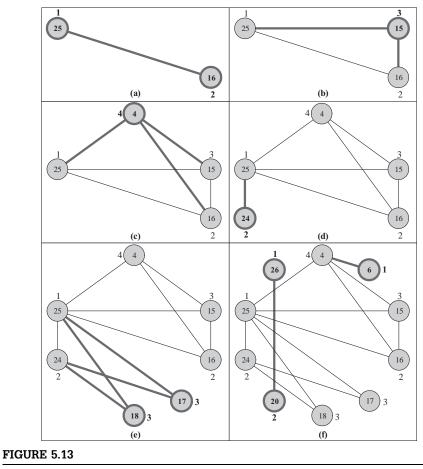

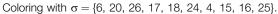

|           | 5.5.2 Register binding by coloring                    | .277 |

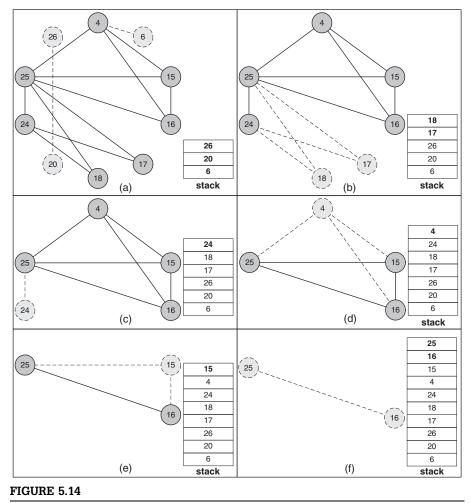

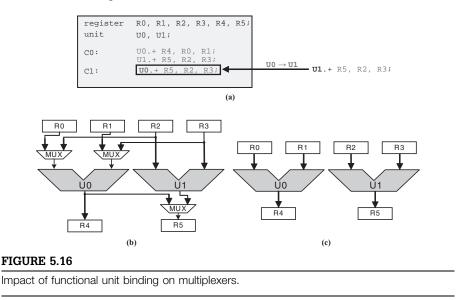

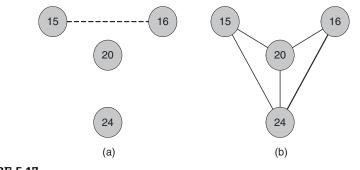

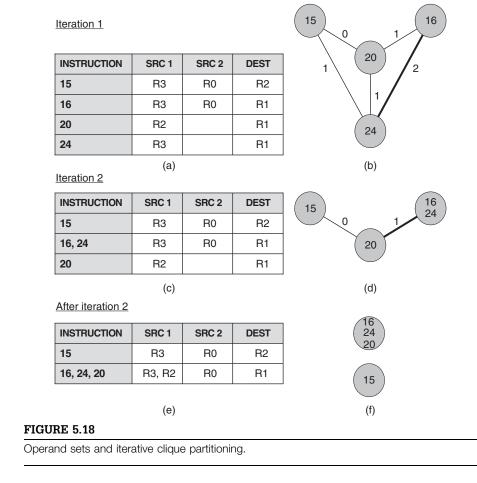

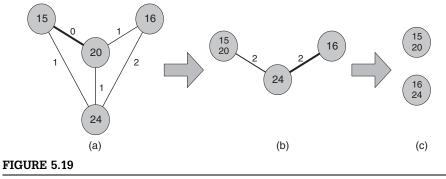

| 5.6       | Functional unit binding                               | .281 |

| 5.7       | Concluding remarks                                    | .289 |

| 5.8       | Exercises                                             | .293 |

| А         | cknowledgments                                        | .294 |

| R         | eferences                                             | .294 |

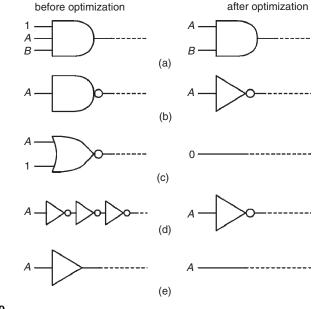

| CHAPTER 6 | Logic synthesis in a nutshell                         | 299  |

|           | Jie-Hong (Roland) Jiang and Srinivas Devadas          |      |

| 6.1       | Introduction                                          | .299 |

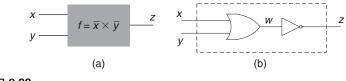

|           | Data Structures for Boolean representation            |      |

|           | and reasoning                                         | .302 |

|           | 6.2.1 Quantifier-free and quantified Boolean formulas | .303 |

|           | 6.2.2 Boolean function manipulation                   | .308 |

|           | 6.2.3 Boolean function representation                 | .309 |

|           | 6.2.3.1 Truth table                                   | .309 |

|           | 6.2.3.2 SOP                                           | .310 |

|           | 6.2.3.3 POS                                           | .311 |

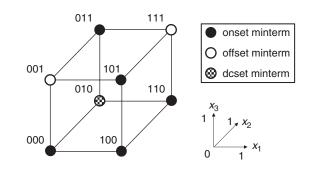

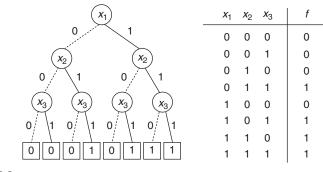

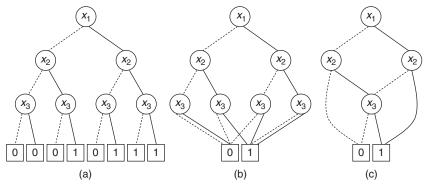

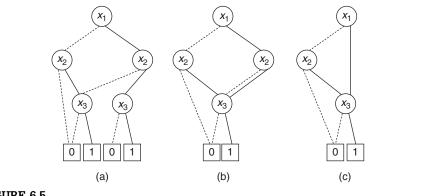

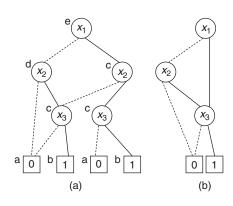

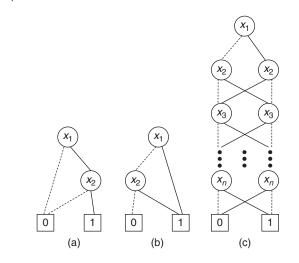

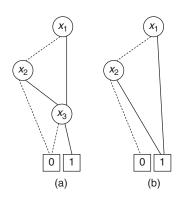

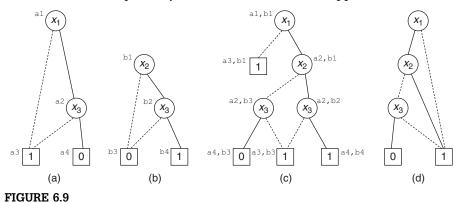

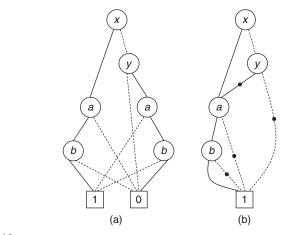

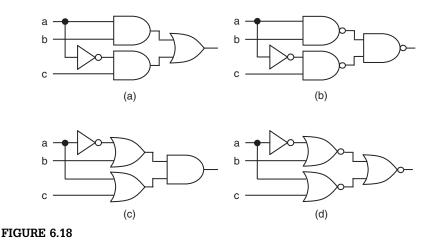

|           | 6.2.3.4 BDD                                           | .312 |

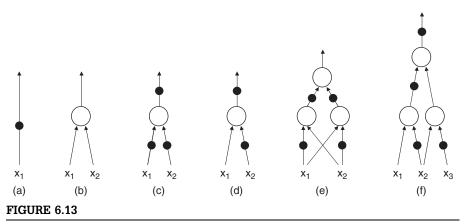

|           | 6.2.3.5 AIG                                           | .321 |

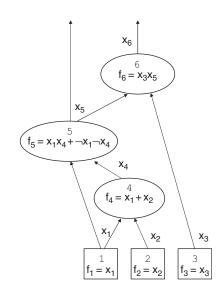

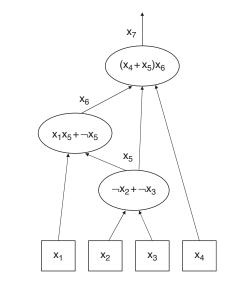

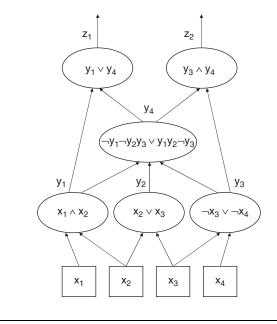

|           | 6.2.3.6 Boolean network                               | .323 |

|           | 6.2.4 Boolean representation conversion               | .324 |

|           | 6.2.4.1 CNF <i>vs</i> . DNF                           | .324 |

|           | 6.2.4.2 Boolean formula vs. circuit                   | .326 |

|           | 6.2.4.3 BDD vs. Boolean network                       | .326 |

|           | 6.2.5 Isomorphism between sets and                    |      |

|           | characteristic functions                              | .328 |

|           | 6.2.6 Boolean reasoning engines                       | .331 |

| 6.3       | Combinational logic minimization                      | .332 |

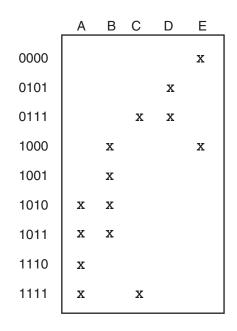

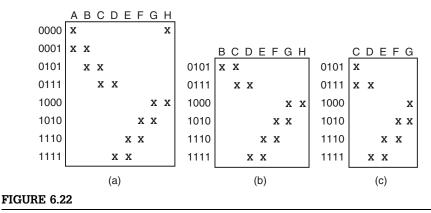

|           | 6.3.1 Two-level logic minimization                    | .332 |

|           |                                                       |      |

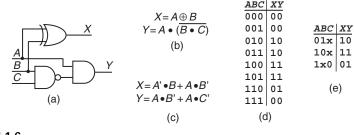

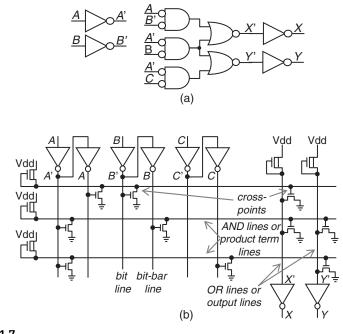

| 6.3.1.1 PLA implementation vs. SOP               |

|--------------------------------------------------|

| minimization                                     |

| 6.3.1.2 Terminology                              |

| 6.3.2 SOP minimization                           |

| 6.3.2.1 The Quine-McCluskey method               |

| 6.3.2.2 Other methods                            |

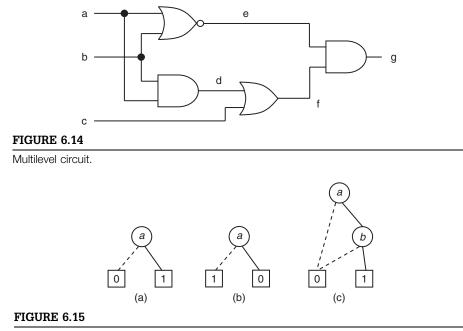

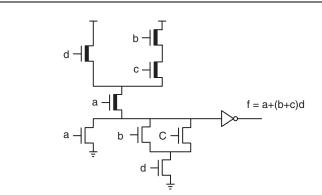

| 6.3.3 Multilevel logic minimization              |

| 6.3.3.1 Logic transformations                    |

| 6.3.3.2 Division and common divisors             |

| 6.3.3.3 Algebraic division                       |

| 6.3.3.4 Common divisors                          |

| 6.3.3.5 Boolean division                         |

| 6.3.4 Combinational complete flexibility         |

| 6.3.5 Advanced subjects                          |

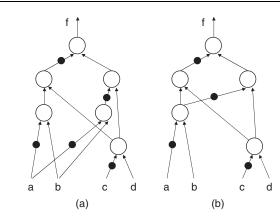

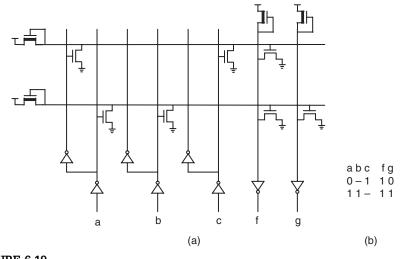

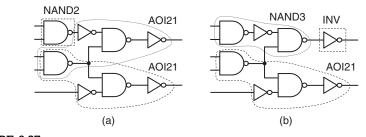

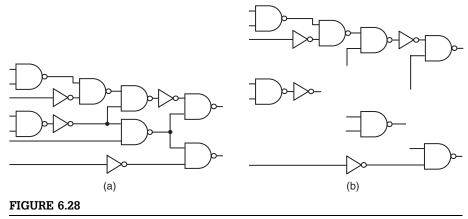

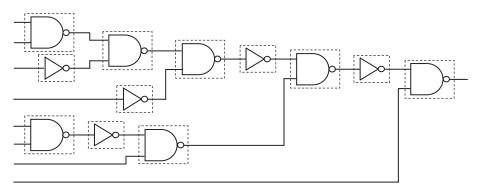

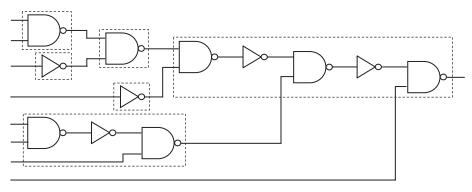

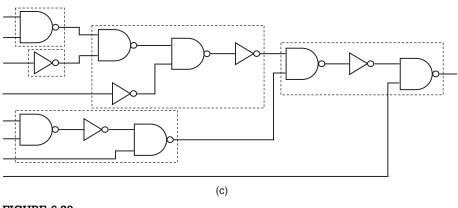

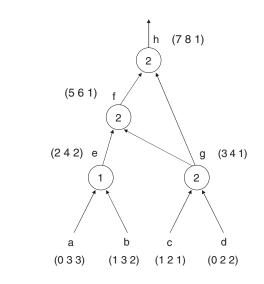

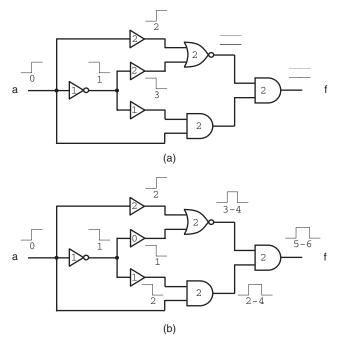

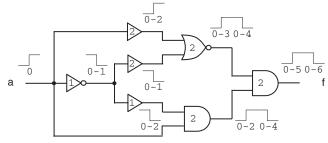

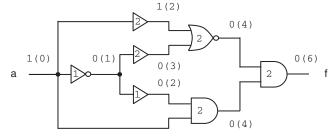

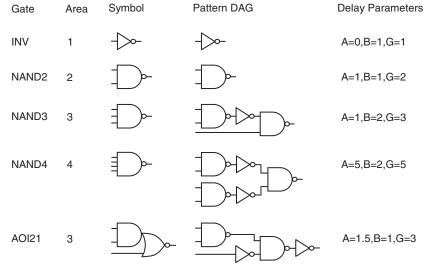

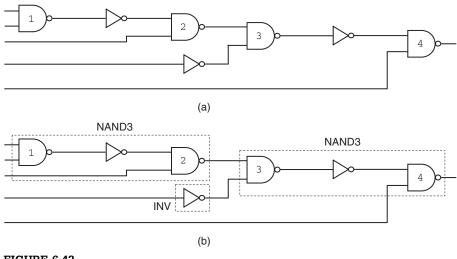

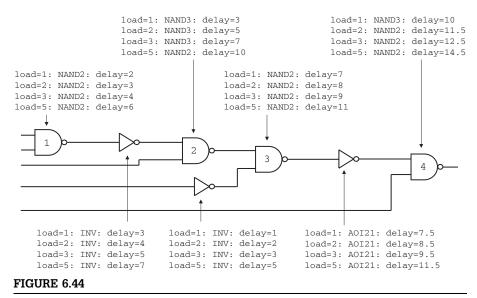

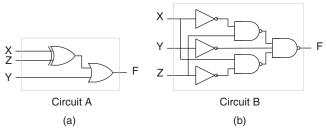

| <b>6.4</b> Technology mapping                    |

| 6.4.1 Technology libraries                       |

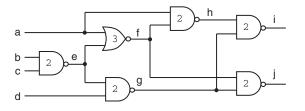

| 6.4.2 Graph covering                             |

| 6.4.3 Choice of atomic pattern set               |

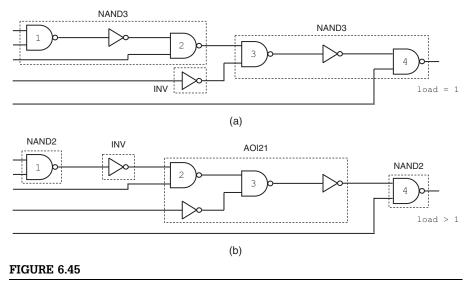

| 6.4.4 Tree covering approximation                |

| 6.4.5 Optimal tree covering                      |

| 6.4.6 Improvement by inverter-pair insertion     |

| 6.4.7 Extension to non-tree patterns             |

| 6.4.8 Advanced subjects                          |

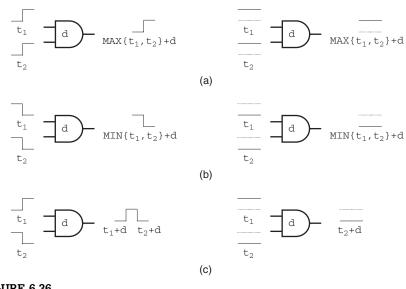

| <b>6.5</b> Timing analysis                       |

| 6.5.1 Topological timing analysis                |

| 6.5.2 Functional timing analysis                 |

| 6.5.2.1 Delay models and modes of operation      |

| 6.5.2.2 True floating mode delay                 |

| 6.5.3 Advanced subjects                          |

| <b>6.6</b> Timing optimization                   |

| 6.6.1 Technology-independent timing optimization |

| 6.6.2 Timing-driven technology mapping           |

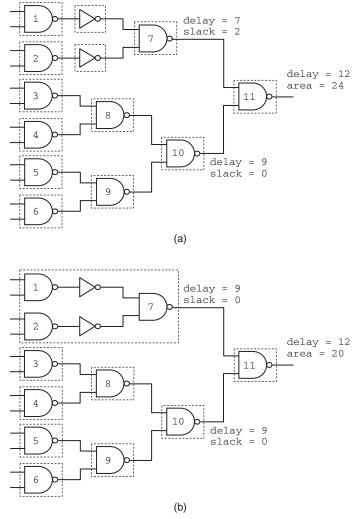

| 6.6.2.1 Delay optimization using tree covering   |

| 6.6.2.2 Area minimization under                  |

| delay constraints                                |

| 6.6.3 Advanced subjects                          |

| <b>6.7</b> Concluding remarks                    |

| <b>6.8</b> Exercises                             |

| Acknowledgments                                  |

| References                                       |

| CHAPTER 7    | Test synthesis                                            | 405  |

|--------------|-----------------------------------------------------------|------|

|              | Laung-Terng (LT.) Wang, Xiaoqing Wen, and<br>Shianling Wu |      |

| 7.1          | Introduction                                              | .406 |

| 7.2          | Scan design                                               | .408 |

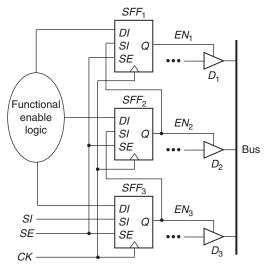

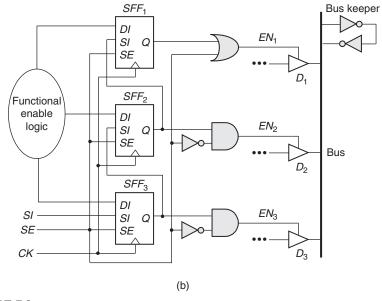

|              | 7.2.1 Scan design rules                                   | .408 |

|              | 7.2.1.1 Tristate buses                                    | .408 |

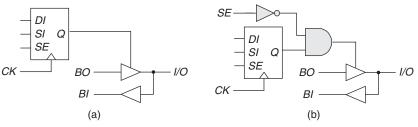

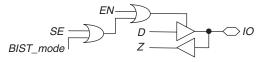

|              | 7.2.1.2 Bidirectional I/O ports                           |      |

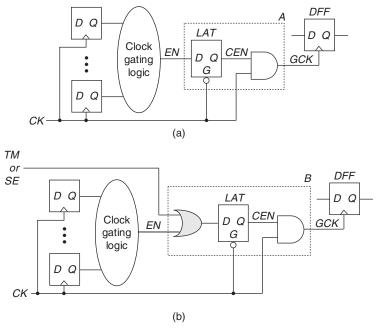

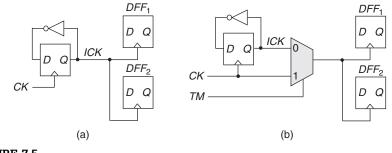

|              | 7.2.1.3 Gated clocks                                      |      |

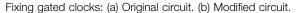

|              | 7.2.1.4 Derived clocks                                    |      |

|              | 7.2.1.5 Combinational feedback loops                      |      |

|              | 7.2.1.6 Asynchronous set/reset signals                    |      |

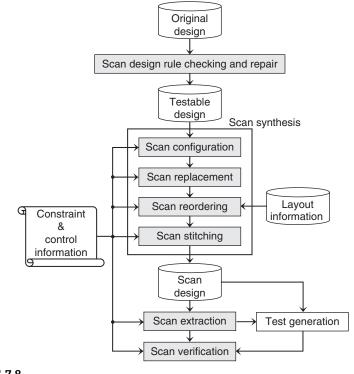

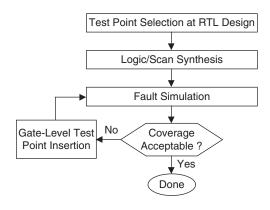

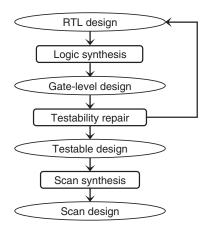

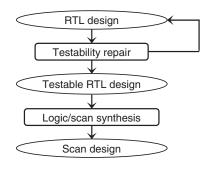

|              | 7.2.2 Scan design flow.                                   |      |

|              | 7.2.2.1 Scan design rule checking and repair              |      |

|              | 7.2.2.2 Scan synthesis                                    |      |

|              | 7.2.2.3 Scan extraction                                   |      |

|              | 7.2.2.4 Scan verification                                 |      |

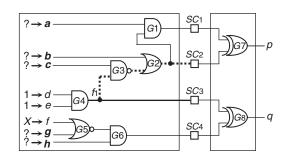

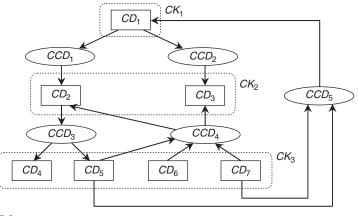

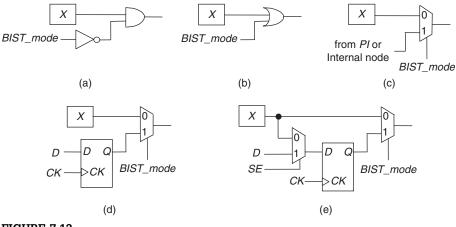

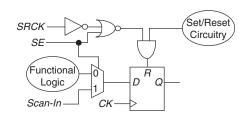

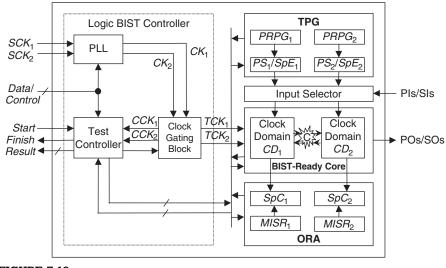

| 7.3          | Logic built-in self-test (BIST) design                    |      |

|              | 7.3.1 BIST design rules                                   |      |

|              | 7.3.1.1 Unknown source blocking                           |      |

|              | 7.3.1.2 Re-timing                                         |      |

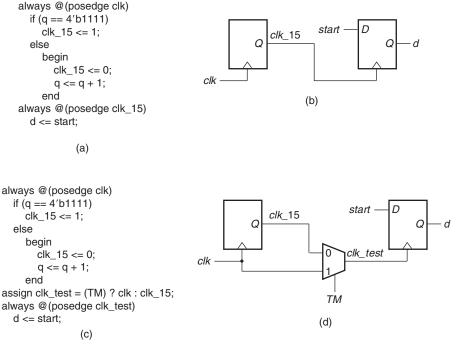

|              | 7.3.2 BIST design example                                 |      |

|              | 7.3.2.2 Logic BIST system design                          |      |

|              | 7.3.2.3 RTL BIST system design                            |      |

|              | 7.3.2.4 Design verification and fault coverage            | .4)/ |

|              | enhancement                                               | 438  |

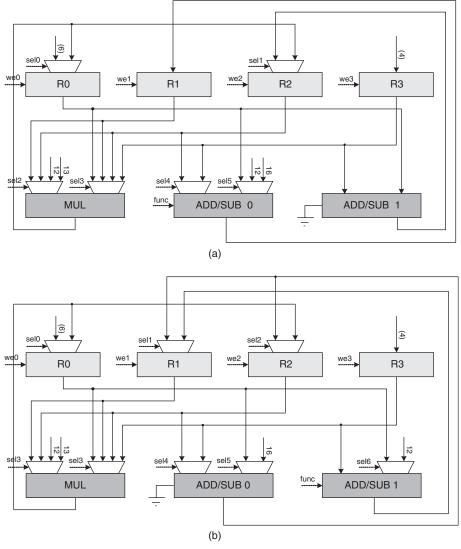

| 7.4          | RTL Design for testability                                |      |

| <i>,</i> ,,_ | 7.4.1 RTL scan design rule checking and repair.           |      |

|              | 7.4.2 RTL scan synthesis                                  |      |

|              | 7.4.3 RTL scan extraction and scan verification           |      |

| 7.5          | Concluding remarks                                        |      |

|              | Exercises                                                 |      |

|              | cknowledgments                                            |      |

|              | eferences                                                 |      |

|              |                                                           |      |

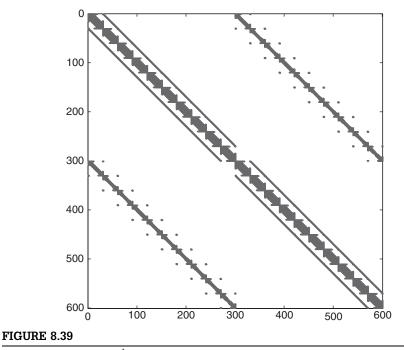

| CHAPTER 8 | Logic and circuit simulation                          | 449     |  |

|-----------|-------------------------------------------------------|---------|--|

|           | Jiun-Lang Huang, Cheng-Kok Koh, and Stephen F. Cauley |         |  |

| 8.1       | Introduction                                          | .450    |  |

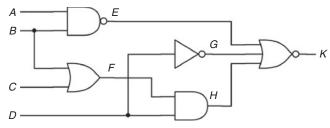

|           | 8.1.1 Logic simulation                                | .451    |  |

|           | 8.1.2 Hardware-accelerated logic simulation           |         |  |

|           | 8.1.3 Circuit simulation                              | .452    |  |

| 8.2       | Logic simulation models                               | .453    |  |

|           | 8.2.1 Logic symbols and operations                    |         |  |

|           | 8.2.1.1 "1" and "0"                                   | .453    |  |

|           | 8.2.1.2 The unknown value $u \ldots \ldots \ldots$    | .453    |  |

|           | 8.2.1.3 The high-impedance state $Z$                  | .453    |  |

|           | 8.2.1.4 Basic logic operations                        | .454    |  |

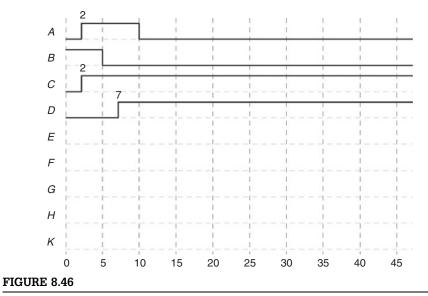

|           | 8.2.2 Timing models                                   | .455    |  |

|           | 8.2.2.1 Transport delay                               |         |  |

|           | 8.2.2.2 Inertial delay                                |         |  |

|           | 8.2.2.3 Functional element delay model                |         |  |

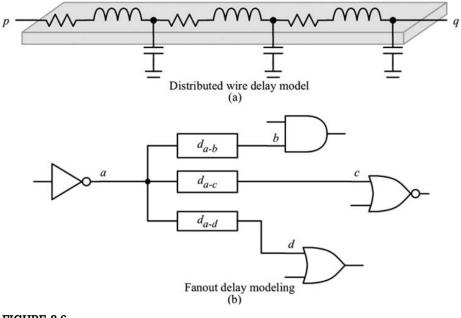

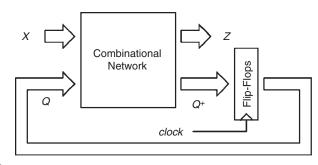

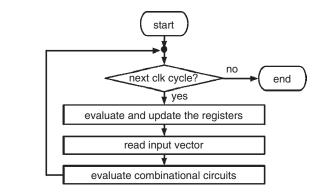

|           | 8.2.2.4 Wire delay                                    |         |  |

| 8.3       | Logic simulation techniques                           |         |  |

|           | 8.3.1 Compiled-code simulation                        |         |  |

|           | 8.3.1.1 Preprocessing                                 |         |  |

|           | 8.3.1.2 Code generation                               |         |  |

|           | 8.3.1.3 Applications                                  |         |  |

|           | 8.3.2 Event-driven simulation                         |         |  |

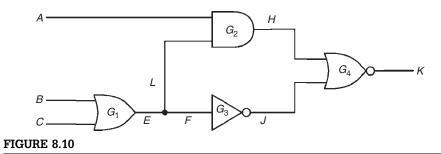

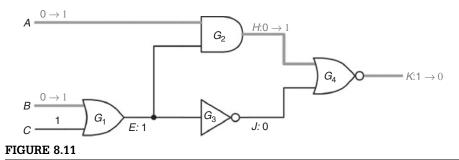

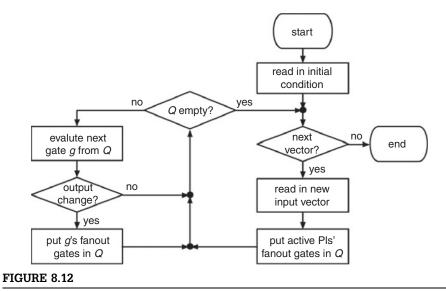

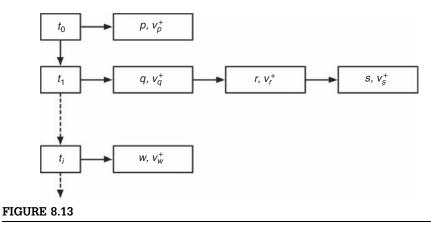

|           | 8.3.2.1 Zero-delay event-driven simulation            |         |  |

| 0.4       | 8.3.2.2 Nominal-delay event-driven simulation         |         |  |

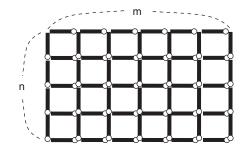

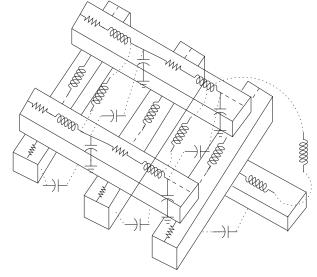

| 8.4       | Hardware-accelerated logic simulation                 |         |  |

|           | 8.4.1 Types of hardware acceleration                  |         |  |

|           | 8.4.2 Reconfigurable computing units.                 |         |  |

|           | 8.4.3 Interconnection architectures                   |         |  |

|           | 8.4.3.2 Indirect interconnect                         |         |  |

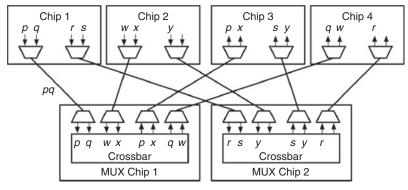

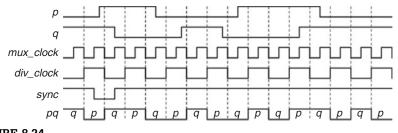

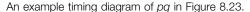

|           | 8.4.3.3 Time-multiplexed interconnect                 |         |  |

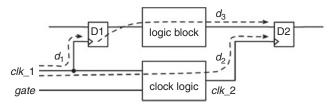

|           | 8.4.4 Timing issues                                   |         |  |

| 85        | Circuit simulation models                             |         |  |

| 0.0       | 8.5.1 Ideal voltage and current sources               |         |  |

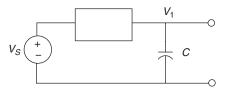

|           | 8.5.2 Resistors, capacitors, and inductors            |         |  |

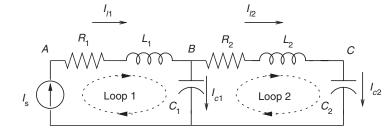

|           | 8.5.3 Kirchhoff's voltage and current laws            |         |  |

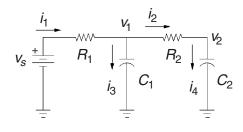

|           | 8.5.4 Modified nodal analysis                         |         |  |

|           |                                                       | • • / / |  |

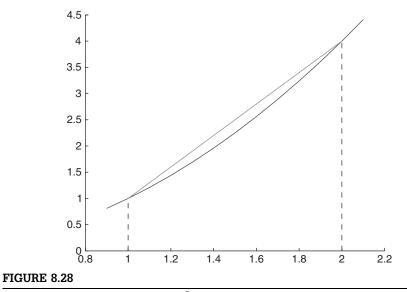

| <b>8.6</b> Numerical methods for transient analysis         | 30         |

|-------------------------------------------------------------|------------|

| 8.6.1 Approximation methods and                             |            |

| numerical integration                                       | 30         |

| 8.6.2 Initial value problems                                | 33         |

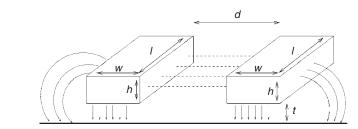

| <b>8.7</b> Simulation of VLSI interconnects                 |            |

| 8.7.1 Wire resistance                                       |            |

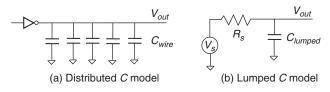

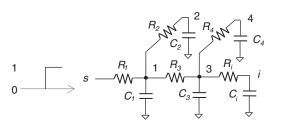

| 8.7.2 Wire capacitance                                      | 37         |

| 8.7.3 Wire inductance                                       | 39         |

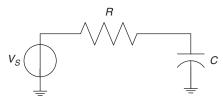

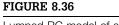

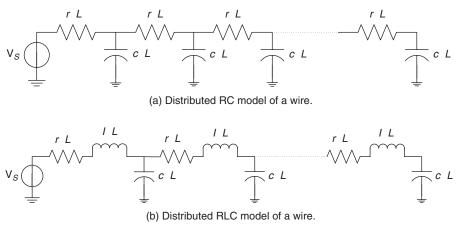

| 8.7.4 Lumped and distributed models                         | )1         |

| 8.7.5 Simulation procedure for interconnects                |            |

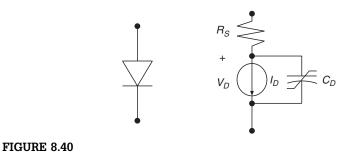

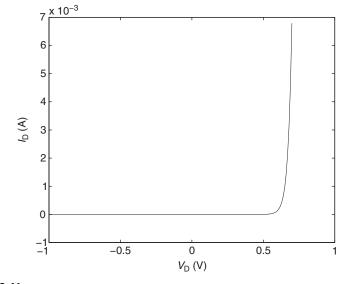

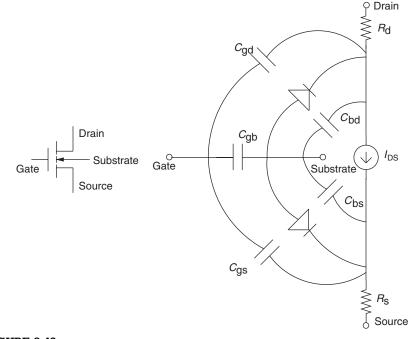

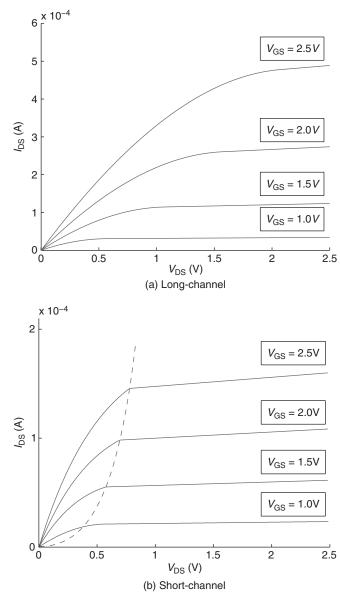

| <b>8.8</b> Simulation of nonlinear devices                  | <b>)</b> 5 |

| 8.8.1 The diode                                             | <b>)</b> 6 |

| 8.8.2 The field-effect transistor                           | )8         |

| 8.8.3 Simulation procedure for nonlinear devices50          | )2         |

| <b>8.9</b> Concluding remarks                               | )4         |

| <b>8.10</b> Exercises                                       | )6         |

| Acknowledgments                                             | )9         |

| References                                                  | 10         |

| CHAPTER 9 Functional verification                           | .3         |

| Hung-Pin (Charles) Wen, Li-C. Wang, and                     |            |

| Kwang-Ting (Tim) Cheng                                      |            |

| <b>9.1</b> Introduction                                     | 4          |

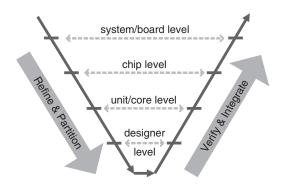

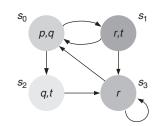

| 9.2 Verification hierarchy                                  |            |

| 9.2.1 Designer-level verification                           |            |

| 9.2.2 Unit-level verification                               |            |

| 9.2.3 Core-level verification                               |            |

| 9.2.4 Chip-level verification                               |            |

| 9.2.5 System-/board-level verification                      |            |

| <b>9.3</b> Measuring verification quality                   |            |

| 9.3.1 Random testing                                        |            |

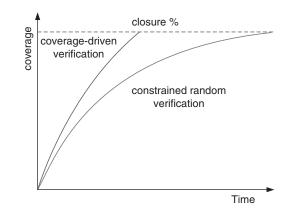

| 9.3.2 Coverage-driven verification                          |            |

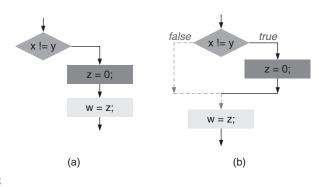

| 9.3.3 Structural coverage metrics                           |            |

| 9.3.3.1 Line coverage ( <i>a.k.a.</i> statement coverage)52 |            |

| 9.3.3.2 Toggle coverage                                     |            |

| 9.3.3.3 Branch/path coverage                                |            |

| 9.3.3.4 Expression coverage                                 |            |

| 9.3.3.5 Trigger coverage ( <i>a.k.a.</i> event coverage)52  |            |

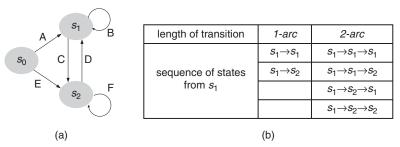

| 9.3.3.6 Finite state machine (FSM) coverage                 |            |

| 9.3.3.7 More on structural coverage                         |            |

| 9.3.4 Functional coverage metrics                           |            |

| 2.5.1 Functional coverage metrico                           | / +        |

| 9.4        | Simulation-based approach                       | .532 |

|------------|-------------------------------------------------|------|

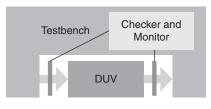

|            | 9.4.1 Testbench and simulation environment      |      |

|            | development                                     | .533 |

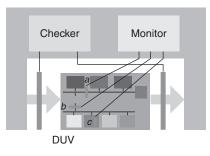

|            | 9.4.2 Methods of observation points             | .535 |

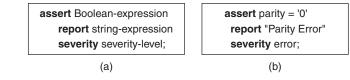

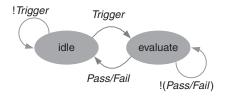

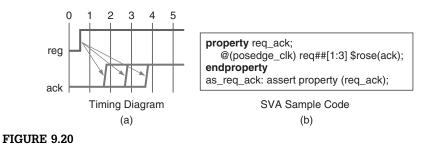

|            | 9.4.3 Assertion-based verification              | .537 |

|            | 9.4.3.1 Assertion coverage and classification   | .538 |

|            | 9.4.3.2 Use of assertions                       | .539 |

|            | 9.4.3.3 Writing assertions                      | .540 |

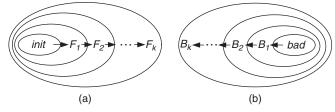

| 9.5        | Formal approaches                               | .540 |

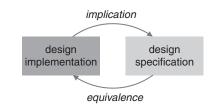

|            | 9.5.1 Equivalence checking                      | .541 |

|            | 9.5.1.1 Checking based on functional            |      |

|            | equivalence                                     | .543 |

|            | 9.5.1.2 Checking based on structural search     | .543 |

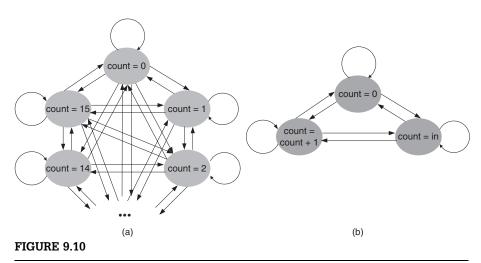

|            | 9.5.2 Model checking (property checking)        | .547 |

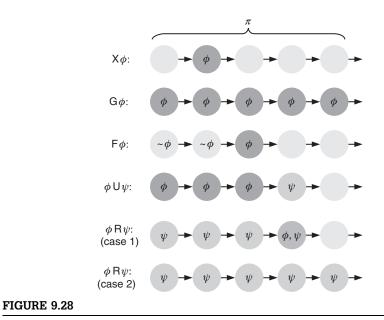

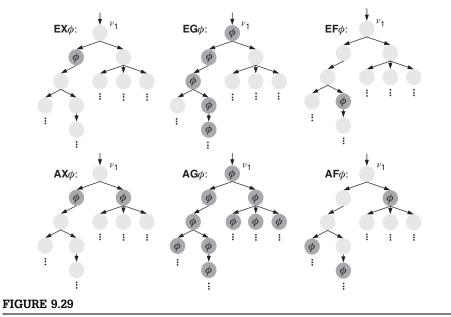

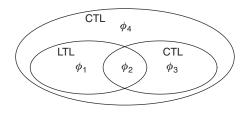

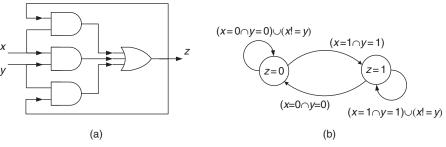

|            | 9.5.2.1 Model checking with temporal logic      | .553 |

|            | 9.5.3 Theorem proving                           |      |

|            | Advanced research                               |      |

|            | Concluding remarks                              |      |

|            | Exercises                                       |      |

| Α          | cknowledgments                                  | .570 |

| R          | References                                      | .570 |

| CHAPTER 10 | Floorplanning                                   | 575  |

|            | Tung-Chieh Chen and Yao-Wen Chang               |      |

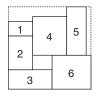

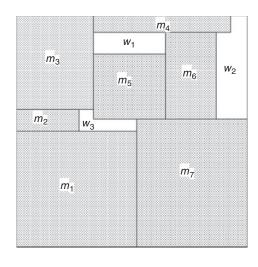

| 10.1       | Introduction                                    | .575 |

|            | 10.1.1 Floorplanning basics                     |      |

|            | 10.1.2 Problem statement.                       |      |

|            | 10.1.3 Floorplanning model                      |      |

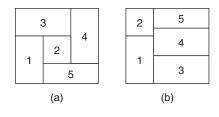

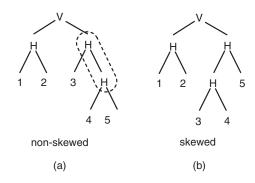

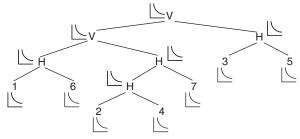

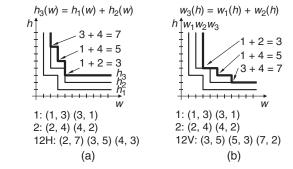

|            | 10.1.3.1 Slicing floorplans                     |      |

|            | 10.1.3.2 Non-slicing floorplans                 |      |

|            | 10.1.4 Floorplanning cost.                      |      |

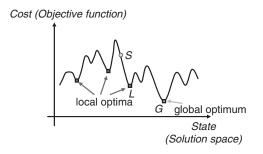

| 10.2       | Simulated annealing approach.                   |      |

|            | 10.2.1 Simulated annealing basics               |      |

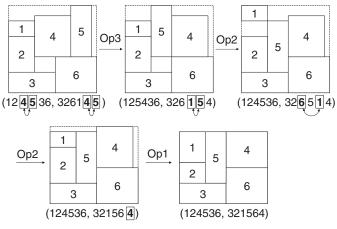

|            | 10.2.2 Normalized Polish expression for slicing |      |

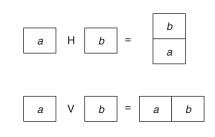

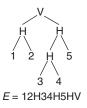

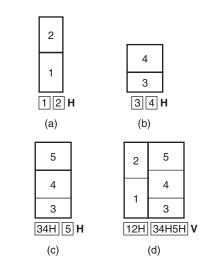

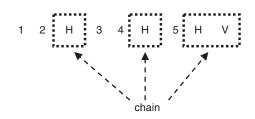

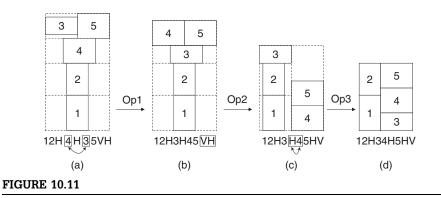

|            | floorplans                                      | .583 |

|            | 10.2.2.1 Solution space                         | .585 |

|            | 10.2.2.2 Neighborhood structure                 |      |

|            | 10.2.2.3 Cost function                          |      |

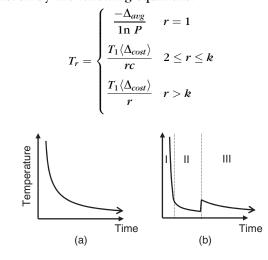

|            | 10.2.2.4 Annealing schedule                     |      |

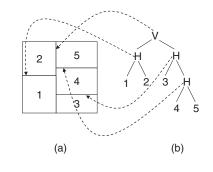

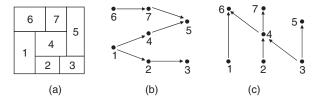

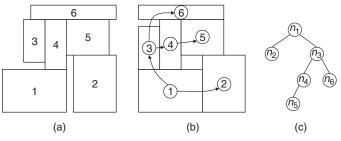

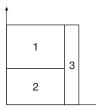

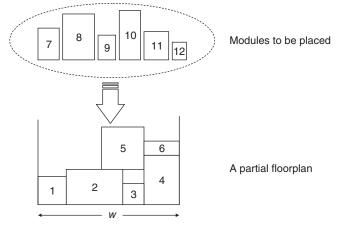

|            | 10.2.3 B*-tree for compacted floorplans         |      |

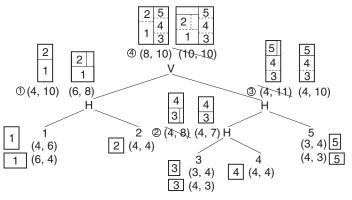

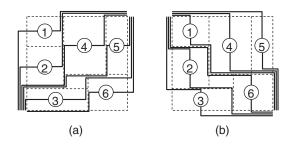

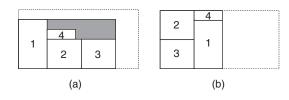

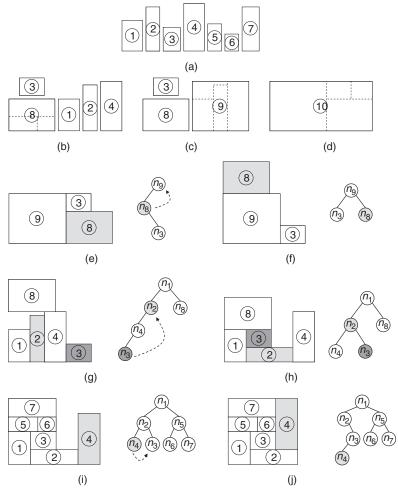

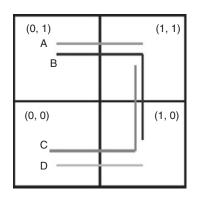

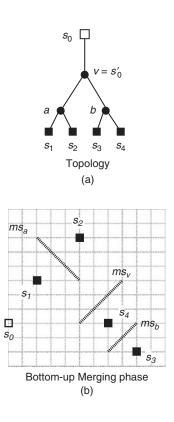

|            | 10.2.3.1 From a floorplan to its B*-tree        |      |

|            |                                                 |      |

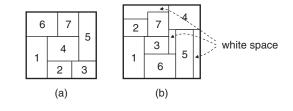

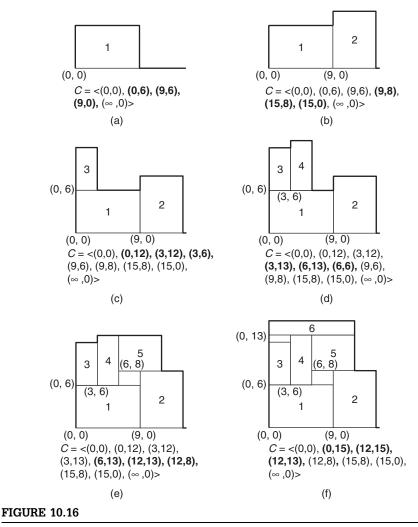

| 10.2.3.2 From a B*-tree to its floorplan        | .594 |

|-------------------------------------------------|------|

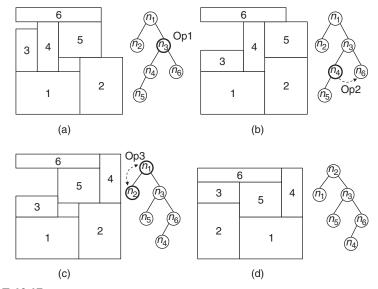

| 10.2.3.3 Solution space                         | .598 |

| 10.2.3.4 Neighborhood structure                 | .598 |

| 10.2.3.5 Cost function                          | .600 |

| 10.2.3.6 Annealing schedule                     | .600 |

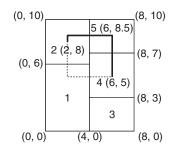

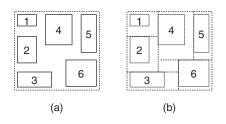

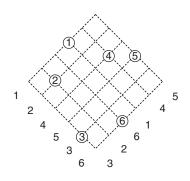

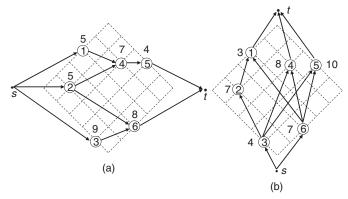

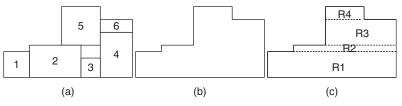

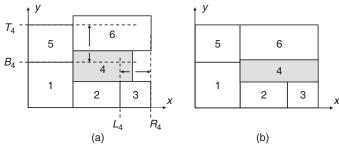

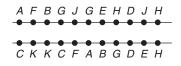

| 10.2.4 Sequence pair for general floorplans     | .600 |

| 10.2.4.1 From a floorplan to its sequence pair  | .600 |

| 10.2.4.2 From a sequence pair to its floorplan  | .601 |

| 10.2.4.3 Solution space                         | .604 |

| 10.2.4.4 Neighborhood structure                 | .604 |

| 10.2.4.5 Cost function                          | .605 |

| 10.2.4.6 Annealing schedule                     | .605 |

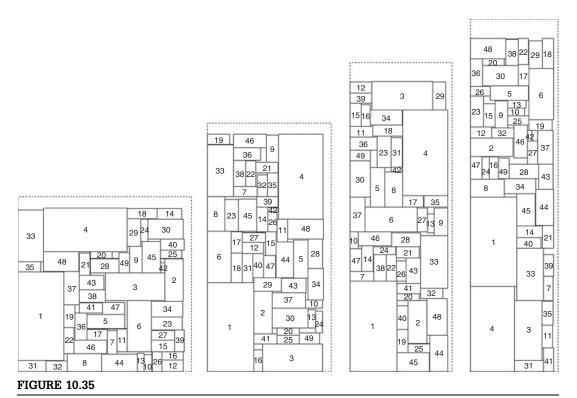

| 10.2.5 Floorplan representation comparison      | .605 |

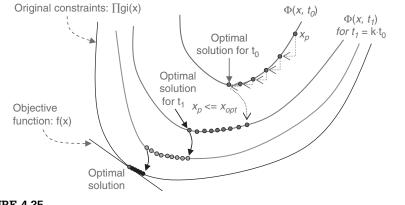

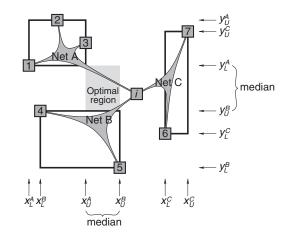

| <b>10.3</b> Analytical approach                 | .607 |

| <b>10.4</b> Modern floorplanning considerations | .612 |

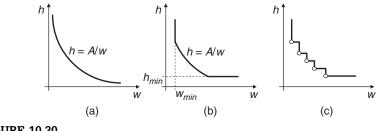

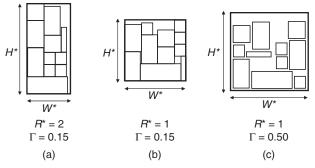

| 10.4.1 Soft modules                             | .612 |

| 10.4.2 Fixed-outline constraint                 | .615 |

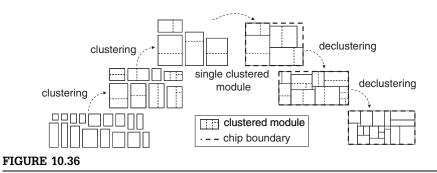

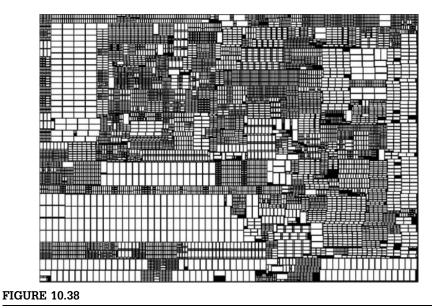

| 10.4.3 Floorplanning for large-scale circuits   |      |

| 10.4.4 Other considerations and topics          |      |

| <b>10.5</b> Concluding remarks                  | .625 |

| <b>10.6</b> Exercises                           |      |

| Acknowledgments                                 |      |

| References                                      | .631 |

| CHAPTER 11 Placement                            | 635  |

| Chris Chu                                       |      |

| <b>11.1</b> Introduction                        | .635 |

| <b>11.2</b> Problem formulations                |      |

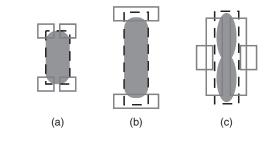

| 11.2.1 Placement for different design styles    |      |

| 11.2.1.1 Standard-cell placement                |      |

| 11.2.1.2 Gate array/FPGA placement              |      |

| 11.2.1.3 Macro block placement                  | .637 |

| 11.2.1.4 Mixed-size placement                   | .638 |

| 11.2.2 Placement objectives                     | .638 |

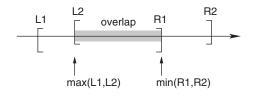

| 11.2.2.1 Total wirelength                       |      |

| 11.2.2.2 Routability                            |      |

| 11.2.2.3 Performance                            | .640 |

| 11.2.2.4 Power                                  | .640 |

| 11.2.2.5 Heat distribution                      | .640 |

| 11.2.3 A common placement formulation           | .641 |

|                                                 |      |

| 11.3 | Global  | placement: partitioning-based approach           |

|------|---------|--------------------------------------------------|

|      | 11.3.1  | Basics for partitioning                          |

|      |         | 11.3.1.1 Problem formulation                     |

|      |         | 11.3.1.2 The Fiduccia-Mattheyses algorithm643    |

|      |         | 11.3.1.3 A multilevel scheme                     |

|      | 11.3.2  | Placement by partitioning                        |

|      |         | 11.3.2.1 The basic idea                          |

|      |         | 11.3.2.2 Terminal propagation technique          |

|      | 11.3.3  | Practical implementations                        |

|      |         | 11.3.3.1 The Capo algorithm                      |

|      |         | 11.3.3.2 The Fengshui algorithm                  |

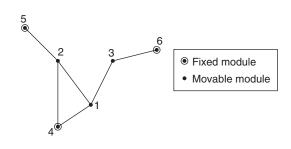

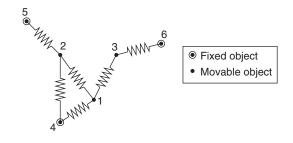

| 11.4 |         | placement: simulated annealing approach          |

|      | 11.4.1  | The placement algorithm in TimberWolf            |

|      |         | 11.4.1.1 Stage 1                                 |

|      |         | 11.4.1.2 Stage 2                                 |

|      |         | 11.4.1.3 Annealing schedule                      |

|      |         | The Dragon placement algorithm                   |

| 11.5 |         | placement: analytical approach                   |

|      |         | An exact formulation                             |

|      | 11.5.2  | Quadratic techniques                             |

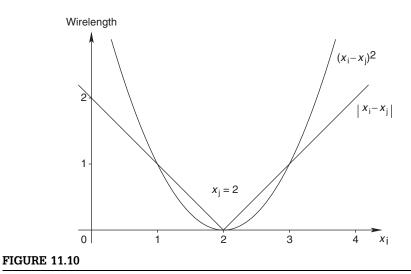

|      |         | 11.5.2.1 Quadratic wirelength                    |

|      |         | 11.5.2.2 Force interpretation of quadratic       |

|      |         | wirelength                                       |

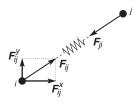

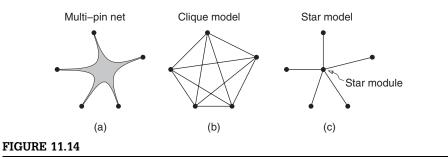

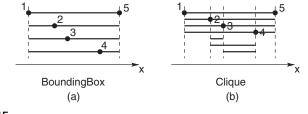

|      |         | 11.5.2.3 Net models for multi-pin nets           |

|      |         | 11.5.2.4 Linearization methods                   |

|      |         | 11.5.2.5 Handling nonoverlapping constraints664  |

|      | 11.5.3  | Nonquadratic techniques                          |

|      |         | 11.5.3.1 Log-sum-exponential wirelength          |

|      |         | function                                         |

|      |         | 11.5.3.2 Density constraint smoothing by         |

|      |         | bell-shaped function                             |

|      |         | 11.5.3.3 Density constraint smoothing by inverse |

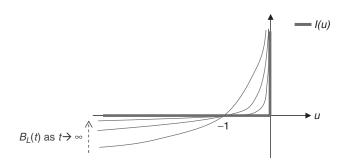

|      |         | laplace transformation                           |

|      | 1154    | 11.5.3.4 Algorithms for nonlinear programs672    |

|      | 11.5.4  | Extension to multilevel                          |

|      |         | 11.5.4.2 Best choice                             |

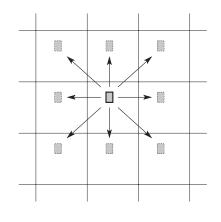

| 11 G | Lecalia | ation                                            |

|      |         |                                                  |

| 11./ |         | d placement                                      |

|      |         | The FastDP algorithm                             |

|      | 11./.2  |                                                  |

| 11.8       | Concluding Remarks                    | 579         |

|------------|---------------------------------------|-------------|

| 11.9       | Exercises                             | 680         |

| Ac         | cknowledgments                        | 682         |

| Re         | eferences                             | 682         |

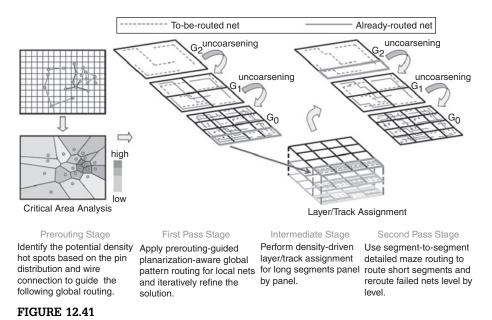

| CHAPTER 12 | Global and detailed routing 6         | 87          |

| i i        | Huang-Yu Chen and Yao-Wen Chang       |             |

| 12.1       | Introduction                          | <i>5</i> 88 |

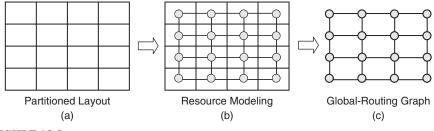

| 12.2       | Problem definition                    | 689         |

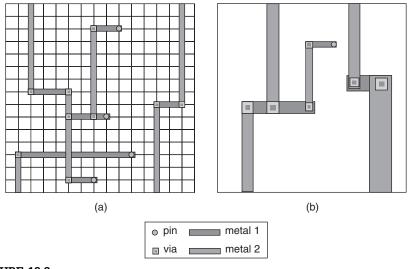

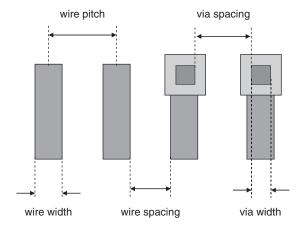

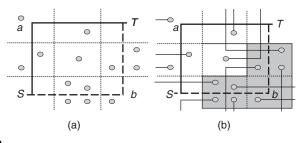

|            | 12.2.1 Routing model                  | 689         |

|            | 12.2.2 Routing constraints            | <b>591</b>  |

| 12.3       | General-purpose routing               | <i>5</i> 92 |

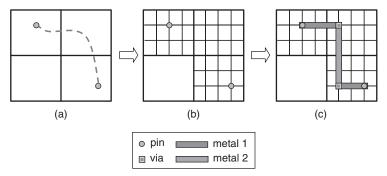

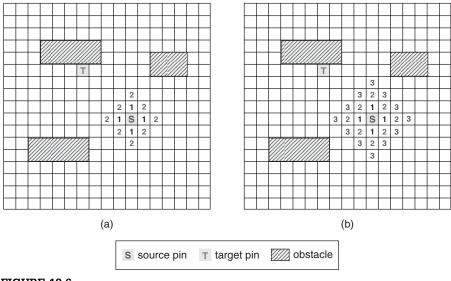

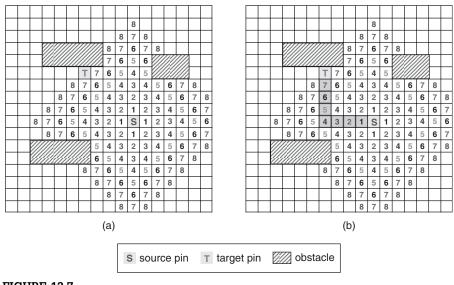

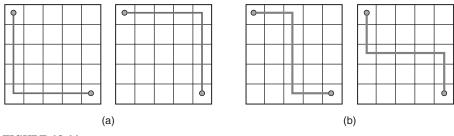

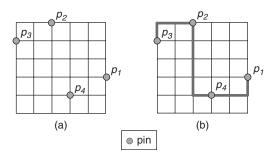

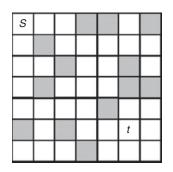

|            | 12.3.1 Maze routing                   | <i>5</i> 93 |

|            | 12.3.1.1 Coding scheme                | <b>594</b>  |

|            | 12.3.1.2 Search algorithm             |             |

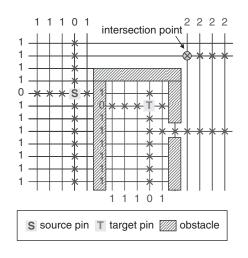

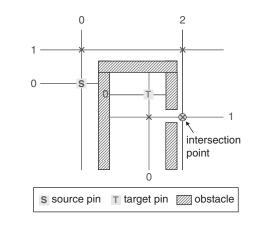

|            | 12.3.1.3 Search space                 |             |

|            | 12.3.2 Line-search routing            |             |

|            | 12.3.3 A*-search routing              |             |

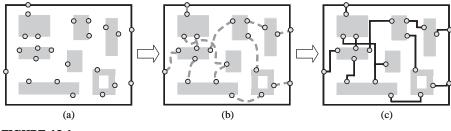

| 12.4       | Global routing                        |             |

|            | 12.4.1 Sequential global routing      |             |

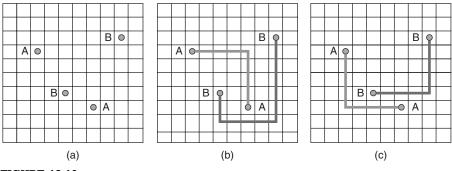

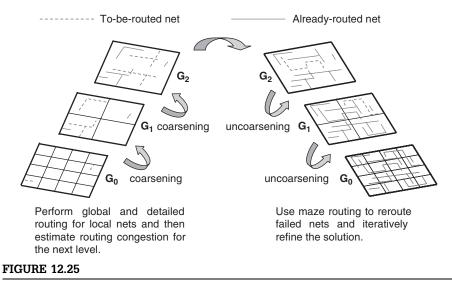

|            | 12.4.2 Concurrent global routing      |             |

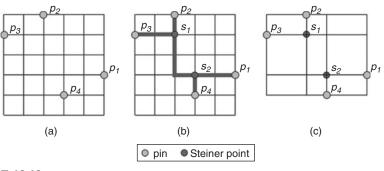

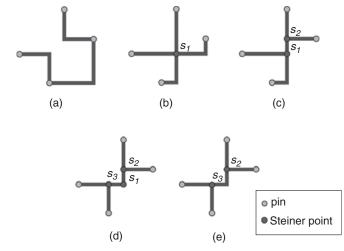

|            | 12.4.3 Steiner trees                  |             |

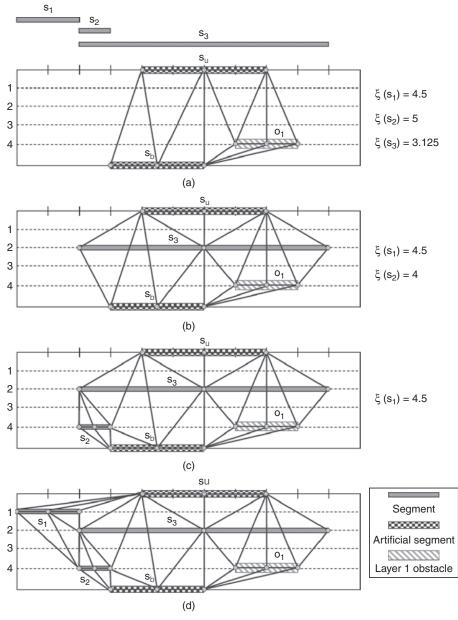

| 12.5       | Detailed Routing                      |             |

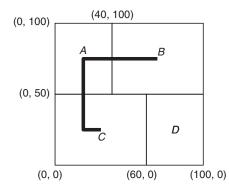

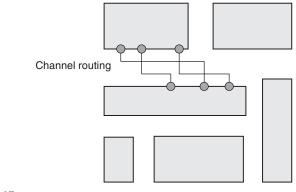

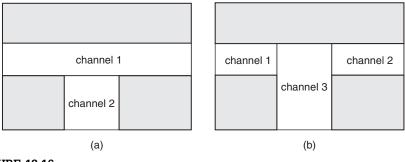

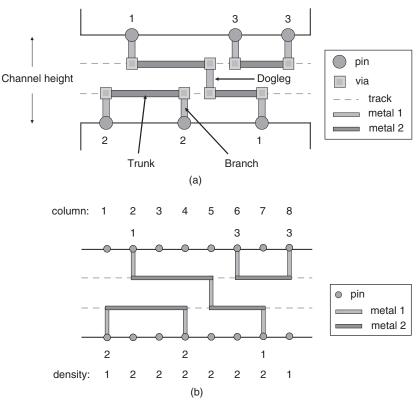

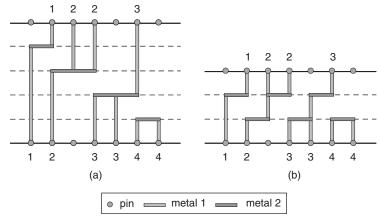

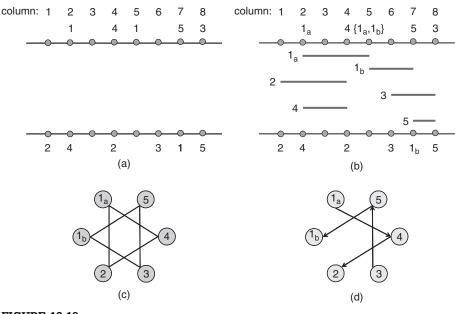

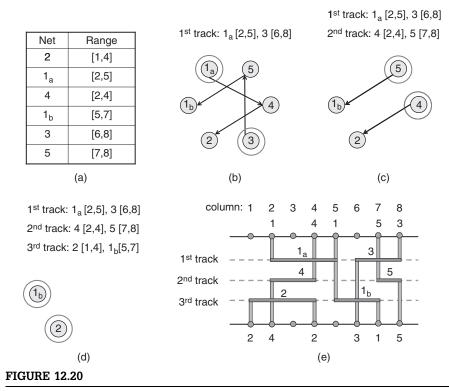

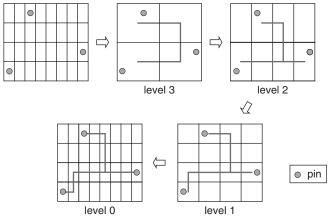

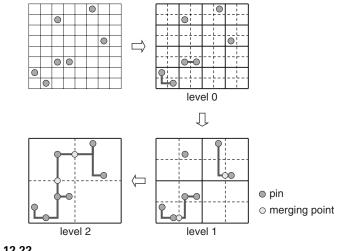

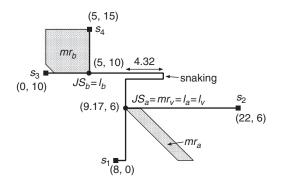

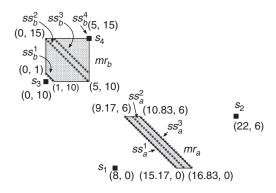

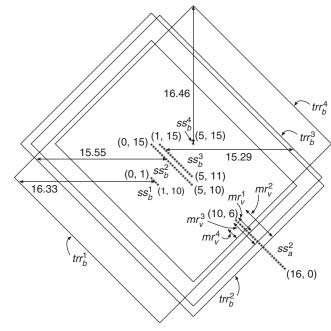

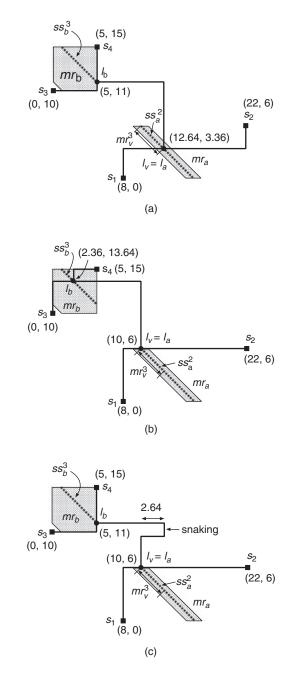

|            | 12.5.1 Channel routing                |             |

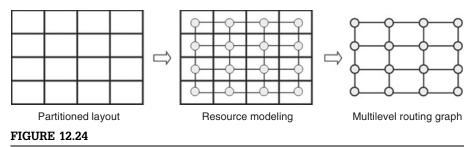

|            | 12.5.2 Full-chip routing              |             |

| 12.6       | Modern routing considerations         |             |

|            | 12.6.1 Routing for signal integrity   |             |

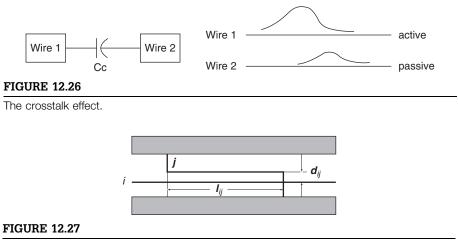

|            | 12.6.1.1 Crosstalk modeling7          |             |

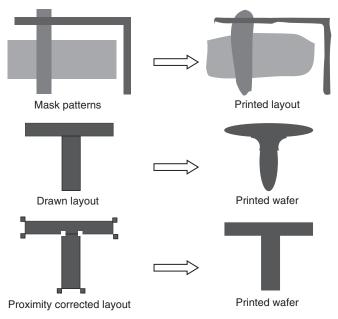

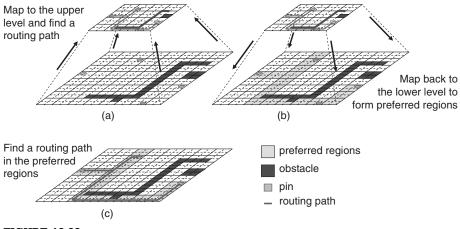

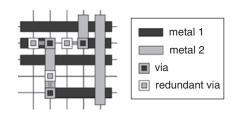

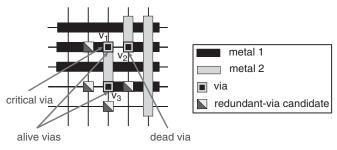

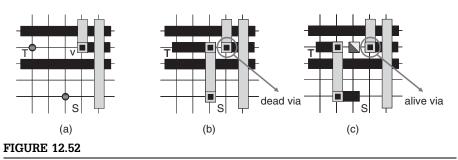

|            | 12.6.1.2 Crosstalk-aware routing      |             |

|            | 12.6.2 Routing for manufacturability  |             |

|            | 12.6.2.1 OPC-aware routing            |             |

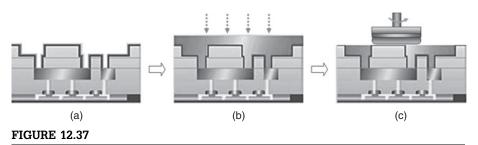

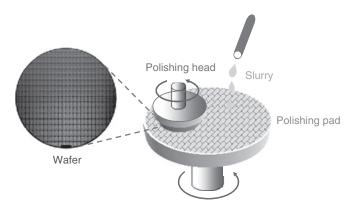

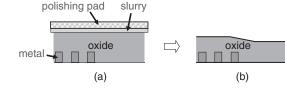

|            | 12.6.2.2 CMP-aware routing            |             |

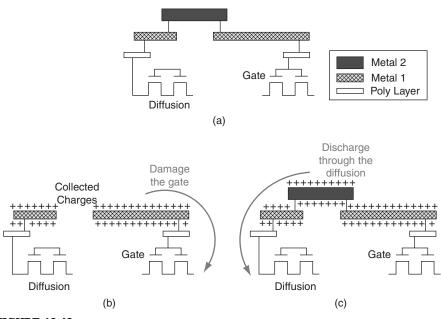

|            | 12.6.3 Routing for reliability        |             |

|            | 12.6.3.1 Antenna-avoidance routing    |             |

|            | 12.6.3.2 Redundant-via aware routing7 |             |

|            | Concluding remarks                    |             |

|            | Exercises                             |             |

|            | cknowledgments7                       |             |

| R          | eferences                             | '45         |

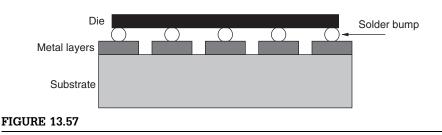

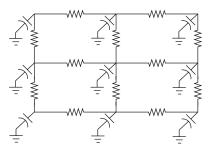

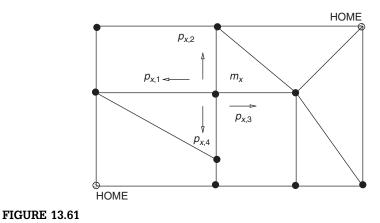

| CHAPTER 13 Synthesis of clock and power/ground    |

|---------------------------------------------------|

| networks                                          |

| Cheng-Kok Koh, Jitesh Jain, and Stephen F. Cauley |

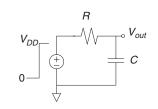

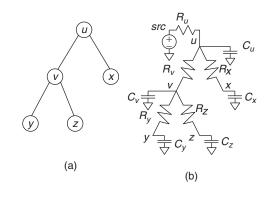

| <b>13.1</b> Introduction                          |

| <b>13.2</b> Design considerations                 |

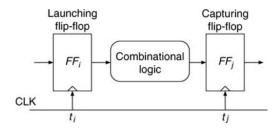

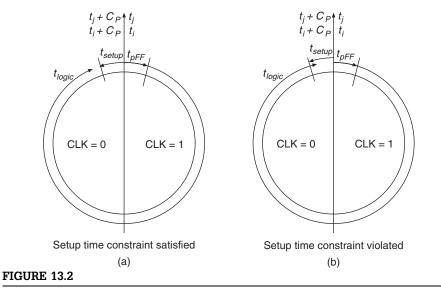

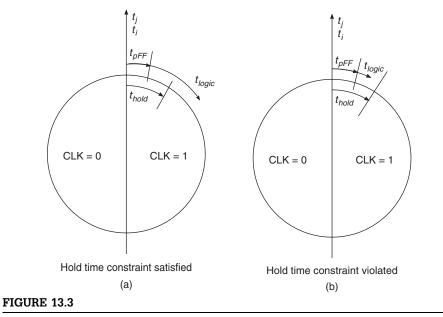

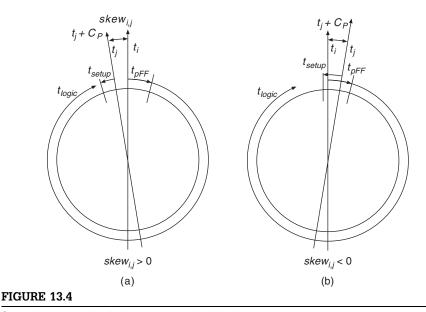

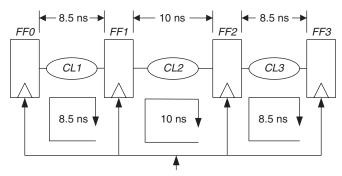

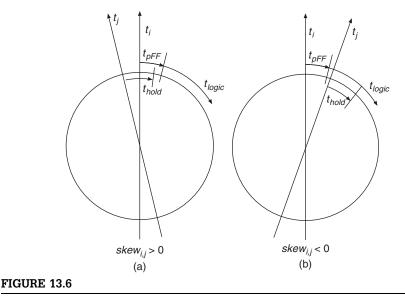

| 13.2.1 Timing constraints                         |

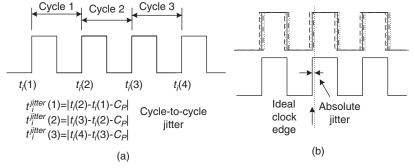

| 13.2.2 Skew and Jitter                            |

| 13.2.3 <i>IR</i> drop and $L \cdot di/dt$ noise   |

| 13.2.4 Power dissipation                          |

| 13.2.5 Electromigration                           |

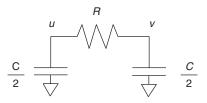

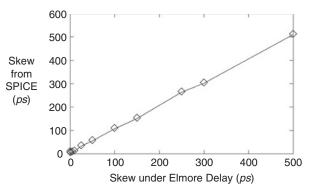

| <b>13.3</b> Clock Network design                  |

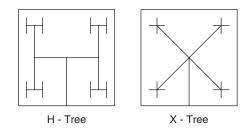

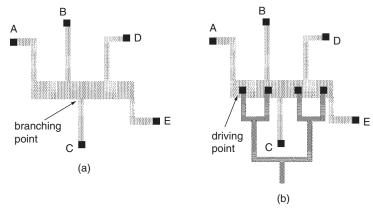

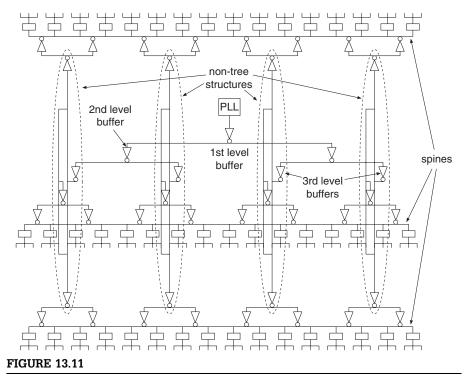

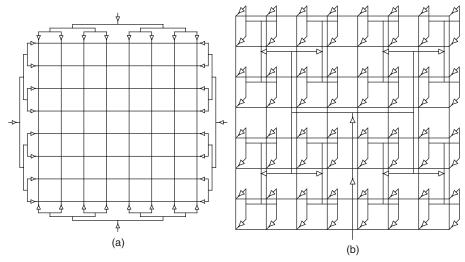

| 13.3.1 Typical clock topologies                   |

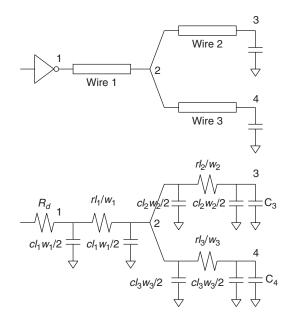

| 13.3.2 Clock network modeling and analysis        |

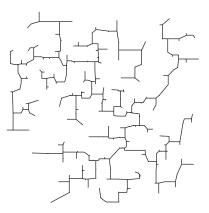

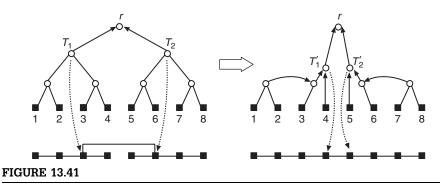

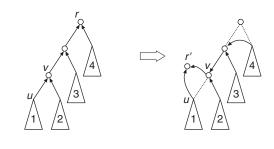

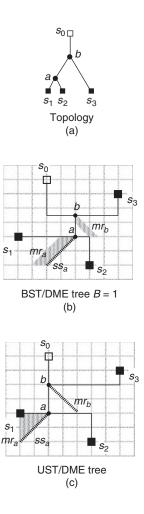

| 13.3.3 Clock tree synthesis                       |

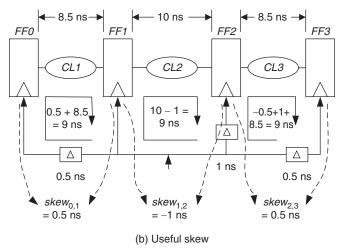

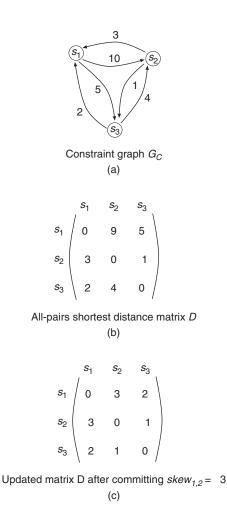

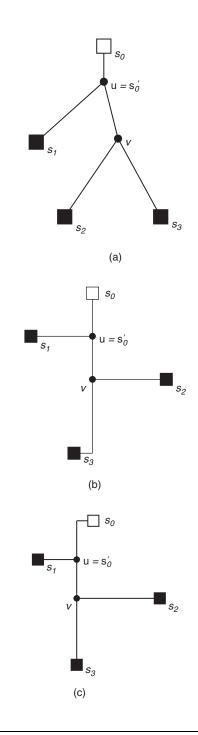

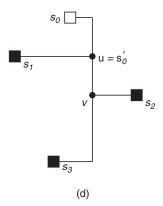

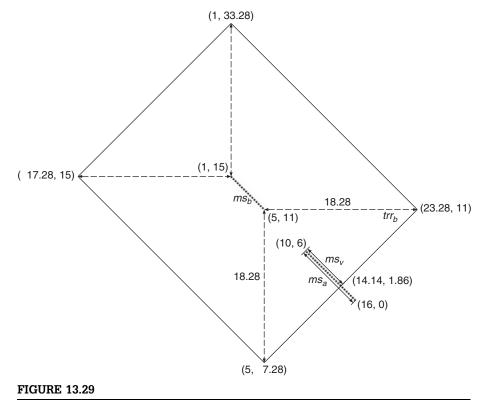

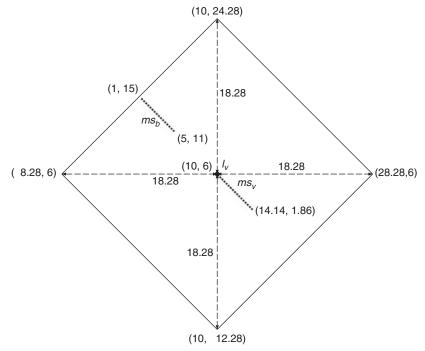

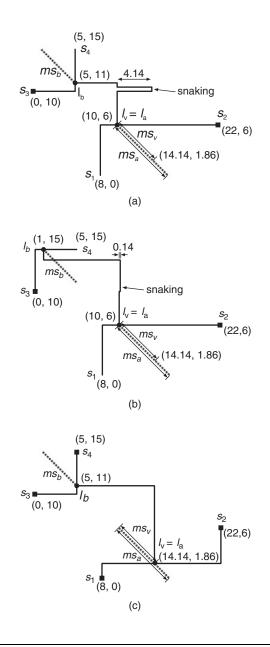

| 13.3.3.1 Clock skew scheduling                    |

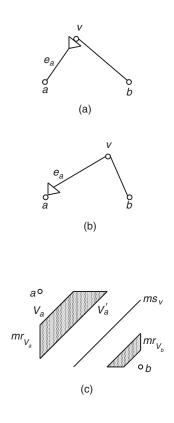

| 13.3.3.2 Clock tree routing                       |

| 13.3.3.3 Zero-skew routing                        |

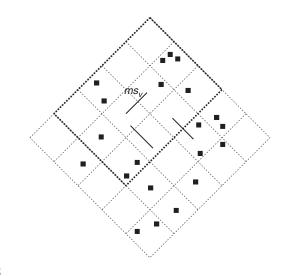

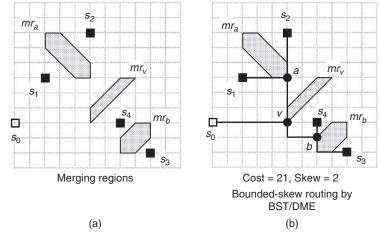

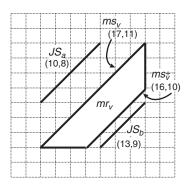

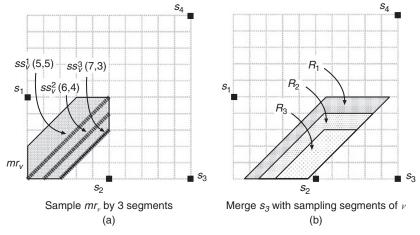

| 13.3.3.4 Bounded-skew routing                     |

| 13.3.3.5 Useful-skew routing                      |

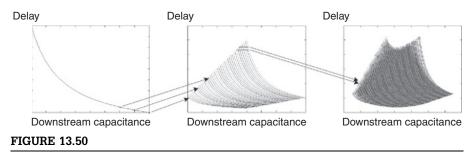

| 13.3.4 Clock tree optimization                    |

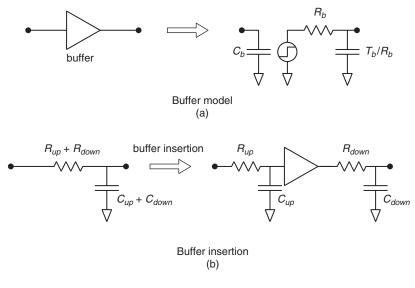

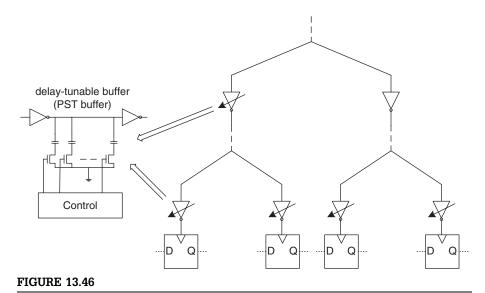

| 13.3.4.1 Buffer insertion in clock routing        |

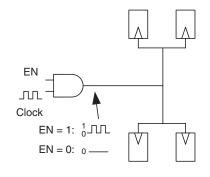

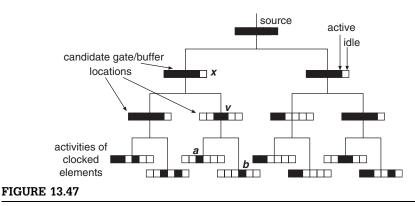

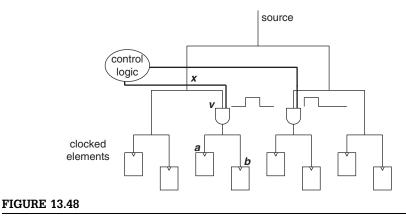

| 13.3.4.2 Clock gating                             |

| 13.3.4.3 Wire sizing for clock nets               |

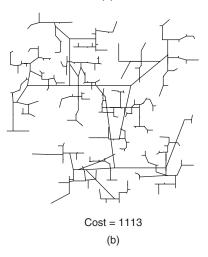

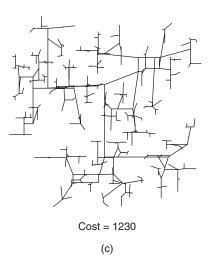

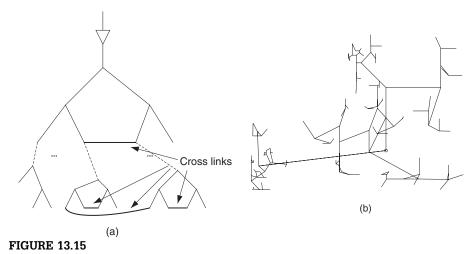

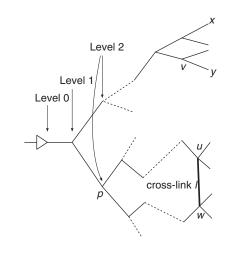

| 13.3.4.4 Cross-link insertion                     |

| <b>13.4</b> Power/ground network design           |

| 13.4.1 Typical power/ground topologies            |

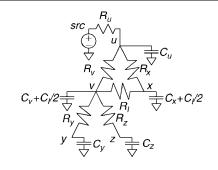

| 13.4.2 Power/ground network analysis              |

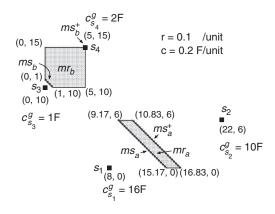

| 13.4.3 Power/ground network synthesis             |

| 13.4.3.1 Topology optimization                    |

| 13.4.3.2 Power pad assignment                     |

| 13.4.3.3 Wire width optimization                  |

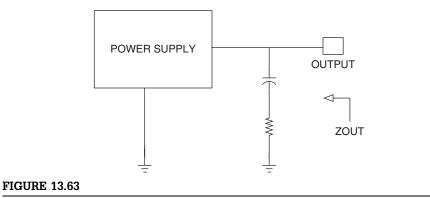

| 13.4.3.4 Decoupling capacitance                   |

| <b>13.5</b> Concluding remarks                    |

| Acknowledgments                                   |

| References                                        |

| References                                        |

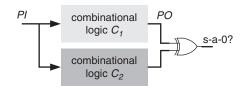

| CHAPTER 14 Fault Simulation and Test Generation 8  | 51  |

|----------------------------------------------------|-----|

| James CM. Li and Michael S. Hsiao                  |     |

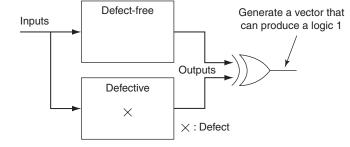

| <b>14.1</b> Introduction                           | 351 |

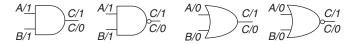

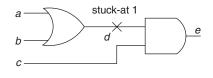

| <b>14.2</b> Fault Collapsing                       | 354 |

| 14.2.1 Equivalence fault collapsing                |     |

| 14.2.2 Dominance fault collapsing                  |     |

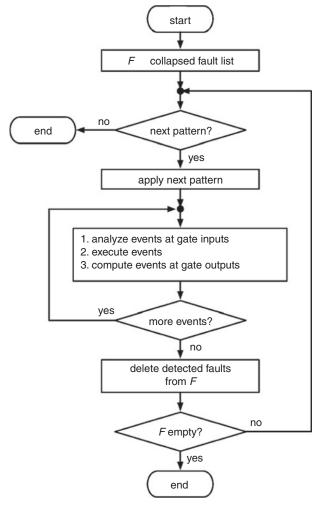

| <b>14.3</b> Fault Simulation                       |     |

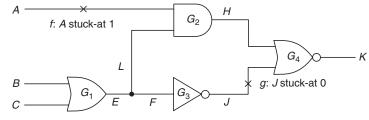

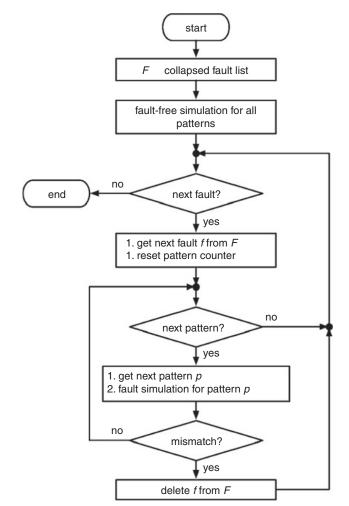

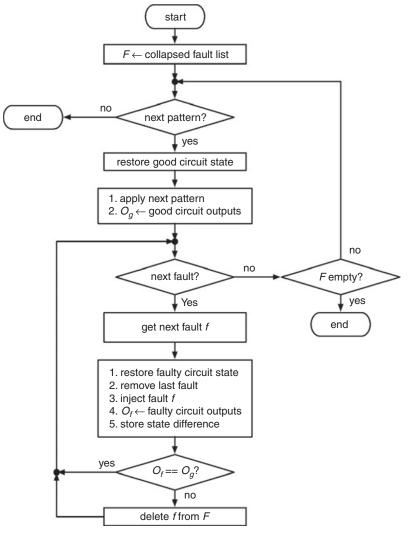

| 14.3.1 Serial fault simulation                     | 361 |

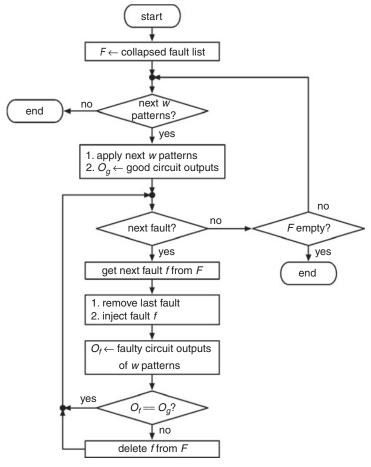

| 14.3.2 Parallel fault simulation                   | 363 |

| 14.3.2.1 Parallel fault simulation                 | 364 |

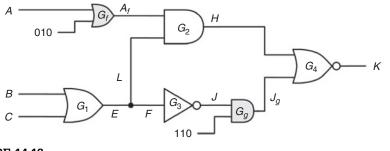

| 14.3.2.2 Parallel pattern fault simulation 8       | 366 |

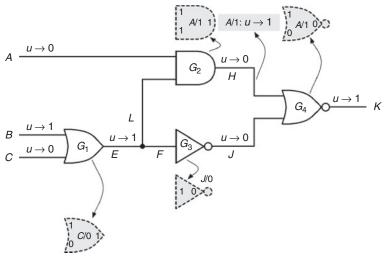

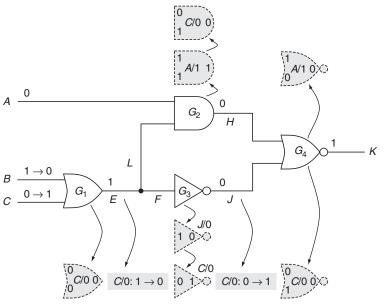

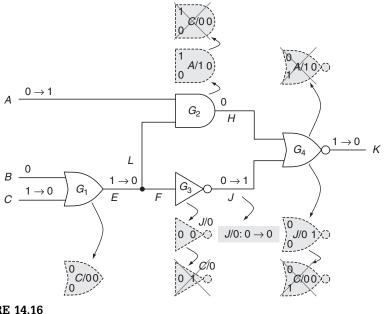

| 14.3.3 Concurrent fault simulation                 | 368 |

| 14.3.4 Differential fault simulation               | 371 |

| 14.3.5 Comparison of fault simulation techniques 8 | 374 |

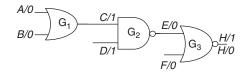

| <b>14.4</b> Test Generation                        | 376 |

| 14.4.1 Random test generation                      | 376 |

| 14.4.1.1 Exhaustive testing                        | 379 |

| 14.4.2 Theoretical Background: Boolean difference8 | 380 |

| 14.4.2.1 Untestable Faults                         | 381 |

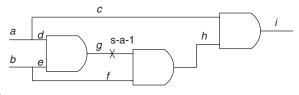

| 14.4.3 Designing a stuck-at ATPG for               |     |

| combinational circuits                             | 382 |

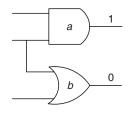

| 14.4.3.1 A naive ATPG algorithm                    | 382 |

| 14.4.3.2 A basic ATPG algorithm                    | 386 |

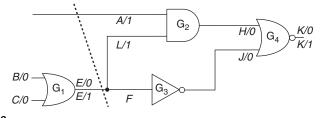

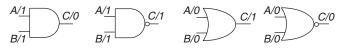

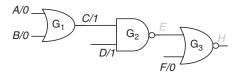

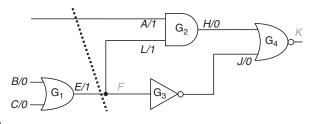

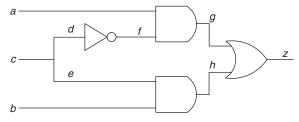

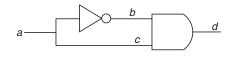

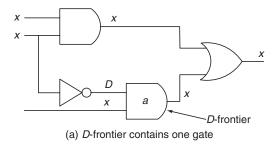

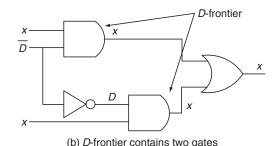

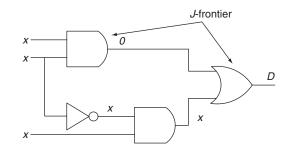

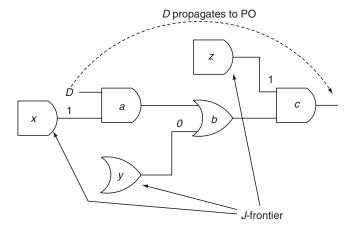

| 14.4.3.3 D algorithm                               | 390 |

| 14.4.4 PODEM                                       | 395 |

| 14.4.5 FAN                                         | )00 |

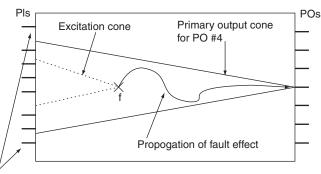

| <b>14.5</b> Advanced Test Generation               | 02  |

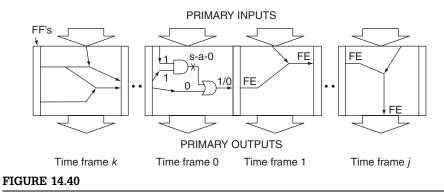

| 14.5.1 Sequential ATPG: Time frame expansion 9     | 02  |

| 14.5.2 Delay fault ATPG                            | )05 |

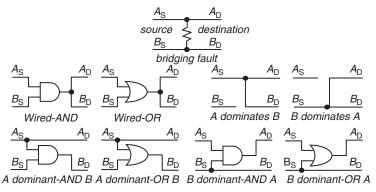

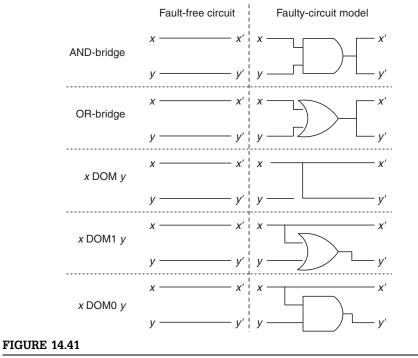

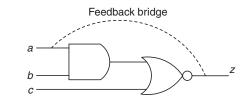

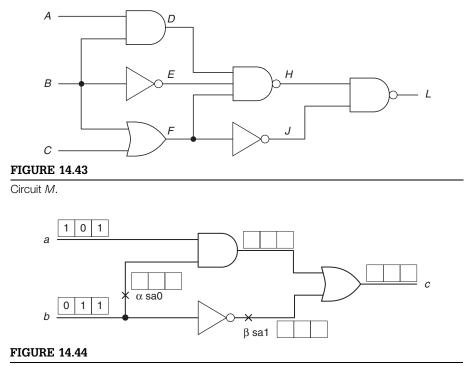

| 14.5.3 Bridging fault ATPG                         |     |

| <b>14.6</b> Concluding Remarks                     | )09 |

| <b>14.7</b> Exercises                              | )10 |

| Acknowledgments                                    | )13 |

| References                                         | )13 |

| Index                                              | )19 |

### Preface

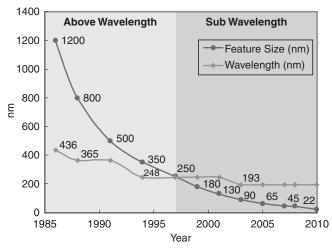

New applications enabled by advances in semiconductor manufacturing technology continue to grow at an amazing rate. A wide spectrum of novel products, ranging from high-performance processors to a broad array of low-power portable devices to micro sense/communicate/actuate chips, facilitates various new applications that have changed, and will continue to change, our daily lives. However, as the semiconductor industry moves to ever-smaller feature sizes and the number of transistors embedded within a *very-large-scale integration* (VLSI) circuit continues to grow, under the relentless pressure of time-to-market for high-quality, reliable products, the semiconductor industry is increasingly dependent on design technology for design closure and for meeting productivity goals. The design technology we refer to here covers all of the core knowledge, software tools, algorithms, methodologies, and infrastructure required to assist in the synthesis, verification, testing, and manufacturing of a functioning and reliable integrated circuit.

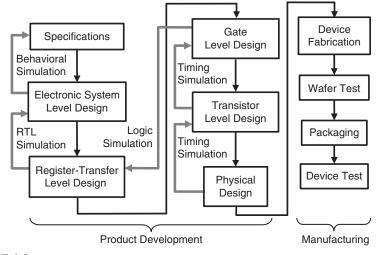

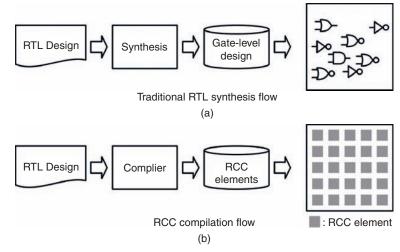

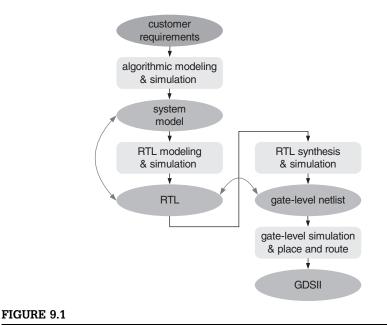

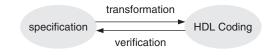

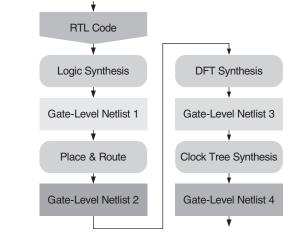

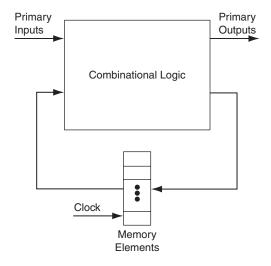

*Electronic design automation* (EDA) has driven advances in design technologies for the past 30 years and will continue to do so. Traditional EDA tools support the design process starting from the register-transfer level (RTL) through to layout. The tasks assisted by these tools can be coarsely classified into RTL/logic synthesis, physical design, design verification, and design for testability (DFT). Since the late 1990s, the landscape of EDA has rapidly expanded such that it now includes an even broader range of tasks. These new tasks cover the support of *electronic-system-level* (ESL) design that includes system specification, transaction-level modeling, and behavioral synthesis as well as tasks related to manufacturing and post-silicon activities such as design for manufacturability and reliability (DFM/DFR), post-layout manipulations for yield optimization, and post-silicon debug. At the same time, the traditional RTL-to-layout tasks are also refined, resulting in a synthesis process which involves many steps of design refinements and employs highly complex optimizations and analysis. The design environment has evolved from a set of point tools to a highly sophisticated and integrated system able to manipulate a huge amount of design data at several different levels of design abstraction.

The fast and continuing evolution of design technology and the enormous growth in the complexity and sophistication of an EDA system has made it such that very few people can master all fronts of this field. New problems, new algorithms, new methodologies and tools, and new start-ups offering new solutions, emerge every year. This trend will continue, perhaps at an even faster pace in the future! As a result, it is becoming difficult even for experts to follow and comprehend the progress on a continuing basis. Training students to prepare them for careers in academia or industry as the next generation of leaders in VLSI design and EDA is a challenging task!

While a comprehensive treatment of all EDA subjects is infeasible for either the undergraduate or entry-level graduate VLSI curriculum, integrating more EDA subjects into existing VLSI and logic design courses is essential for giving the students a balanced, and more accurate, view of modern system-on-chip (SOC) design. To facilitate that goal and to evolve the VLSI design curriculum, this textbook selects a set of core EDA topics which, in our opinion, provides an essential, fundamental understanding of the EDA tasks and the design process. These topics range from the basics of complementary metal oxide semiconductor (CMOS) design to key algorithms used in EDA. Also covered are various modeling and synthesis techniques at the system, register-transfer, and gate levels, as well as physical synthesis, including floorplanning, placement, routing, and synthesis of clock and power/ground networks. We have also chosen key topics on functional verification, including both simulation and formal techniques, and a range of testing topics, such as design for testability, test synthesis, fault simulation, and test generation. The intent is to allow the readers to understand fundamental EDA algorithms as well as VLSI test principles and DFT architectures, preparing them to tackle EDA and test problems caused by advances in semiconductor manufacturing technology and complex SOC designs in today's nanometer era.

Each chapter of this book follows a specific format. The subject matter of the chapter is first introduced. Related methods are explained in detail next. Then, industry practices, if applicable, are described before concluding remarks. Each chapter contains a variety of exercises to allow the use of this book as a textbook for an entry-level EDA course. Every chapter concludes with acknowledgment to contributors and reviewers and a list of references.

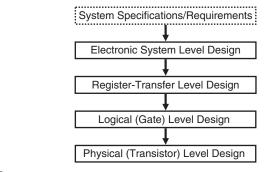

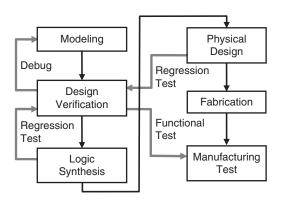

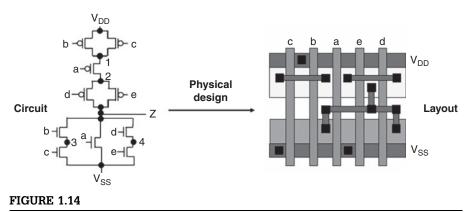

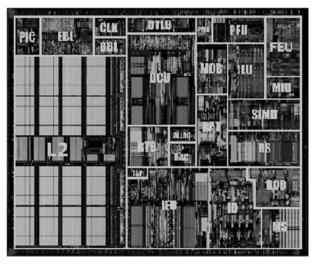

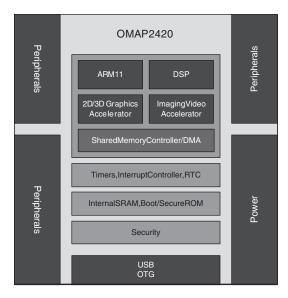

Chapter 1 provides an introduction to *electronic design automation (EDA)*. It begins with an overview of the EDA historic perspective. This is followed by a discussion of the importance of EDA – why EDA plays a central role in meeting time-to-market pressure and manufacturing quality of the nanometer design era. Typical design flows and examples are illustrated at different levels of abstraction – how a system-level design is automated through the modeling, synthesis, verification, and test stages.

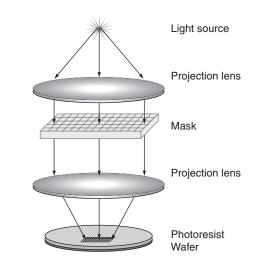

Chapter 2 covers fundamental *complementary metal oxide semiconductor* (CMOS) design principles and techniques that are required knowledge for the understanding of *system-on-chip* (SOC) designs and EDA applications. While the topic is quite broad, we mainly focus on the widely used CMOS design and automation techniques and introduce them in an easy-to-grasp manner with extensive illustrations and examples. Emerging low-power design techniques that can be utilized to lengthen battery life or to reduce system failures due to overheat are also included in the chapter.

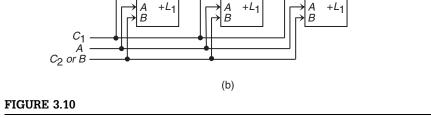

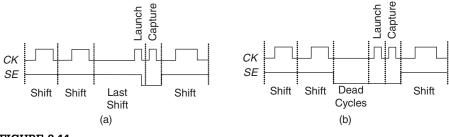

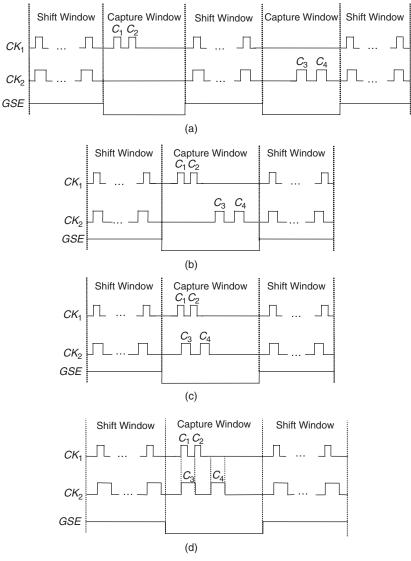

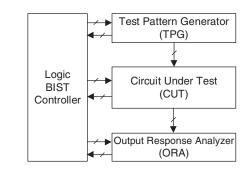

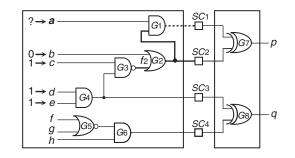

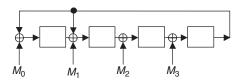

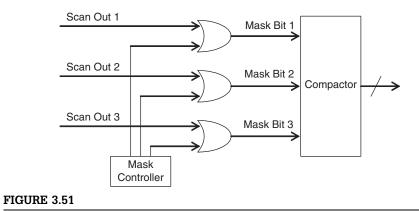

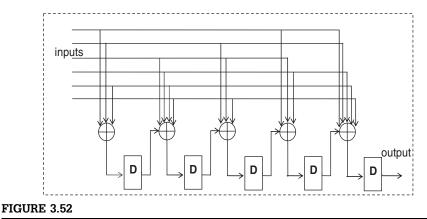

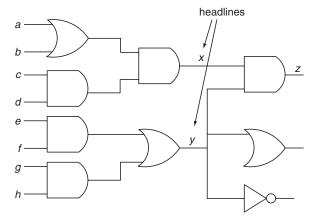

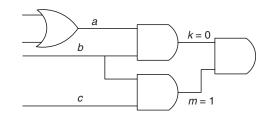

Chapter 3 covers fundamental *design-for-testability* (DFT) architectures to ensure high product quality and low test cost for VLSI or SOC designs. This chapter puts great emphasis on three basic DFT techniques that have been widely used in industry today for digital circuit testing: *scan design, logic built-in self-test* (BIST), and *test compression. Testability analysis* methods to assess the testability of a logic circuit are first described. The three DFT techniques are then explained in detail including schemes for *at-speed testing* and practiced in industry.

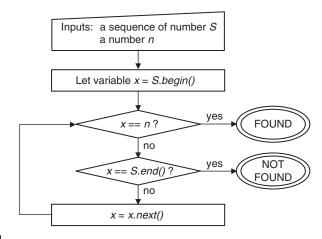

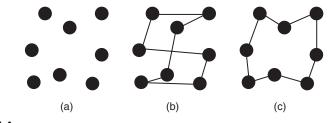

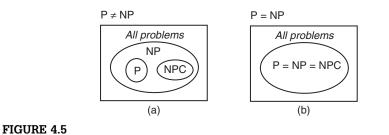

Chapter 4 introduces the fundamentals of algorithms that are essential to EDA tasks including synthesis, verification, and test. This chapter starts with an introduction to *computational complexity*, followed by various *graph* algorithms that are commonly used to model and solve EDA problems. It also covers several heuristic algorithms for practical use on real-life designs. The remainder of the chapter briefly surveys the *mathematical programming* techniques that can provide a theoretical background on the optimization problems.

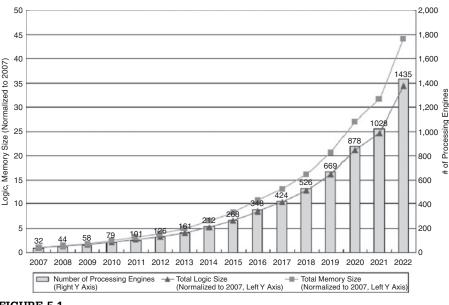

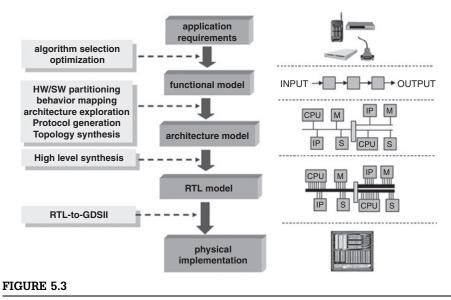

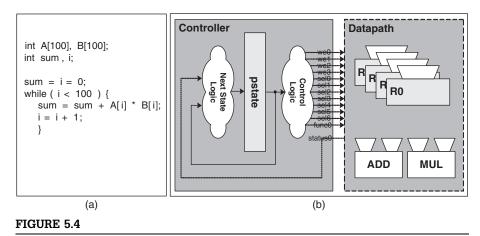

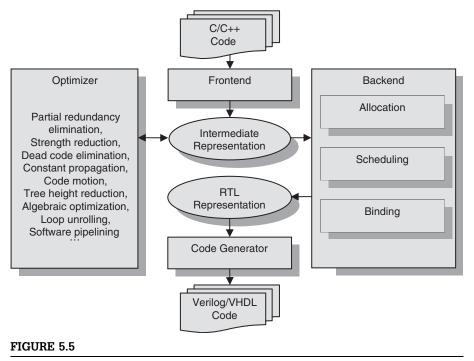

Chapter 5 begins with *electronic-system-level* (ESL) *design modeling and high-level synthesis* – the first step of EDA after a design is specified for implementation. The role of high-level synthesis in the context of ESL design modeling is discussed. An example is given to describe the generic structure required to build a high-level synthesis tool and the tasks involved. This is followed by a detailed description of the key algorithms, including *scheduling* and *binding*. Advanced topics are discussed at the end of the chapter.

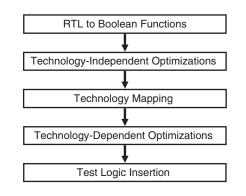

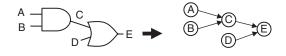

Chapter 6 jumps into *logic synthesis* – the essential step bridging high-level synthesis and physical design. Important data structures for Boolean function representation and reasoning are first introduced, followed by the classical issues of *logic optimization* (which includes two-level and multilevel logic minimization), *technology mapping*, *timing analysis*, and *timing optimization*. Advanced and emerging topics are outlined for further reading.

Chapter 7 discusses the *test synthesis* process that automatically inserts the DFT circuits, discussed in Chapter 3, into a design during or after logic synthesis. Design rules specific to scan design and logic BIST are given to comply with DFT requirements. Test synthesis flows and examples are then described to show how the test automation is performed. The remainder of the chapter is devoted to illustrating the automation of DFT circuit insertion at the *register-transfer level* (RTL).

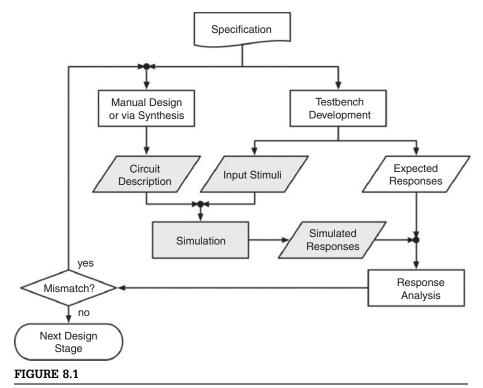

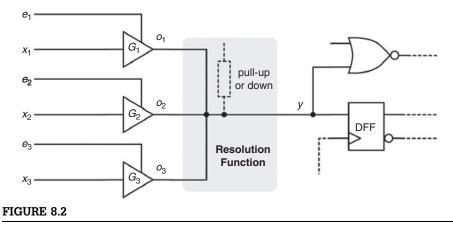

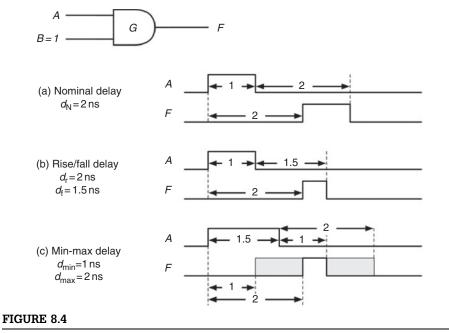

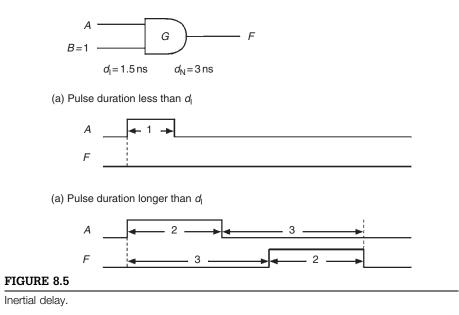

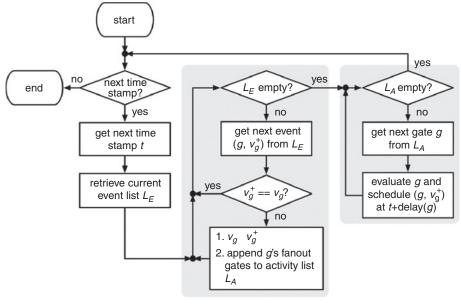

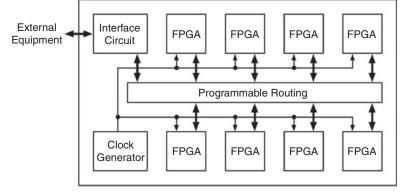

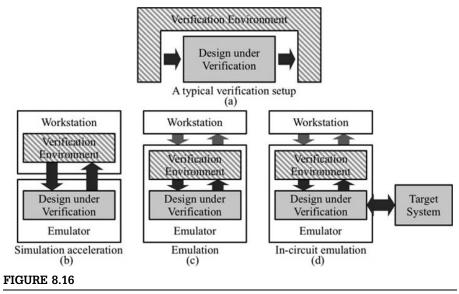

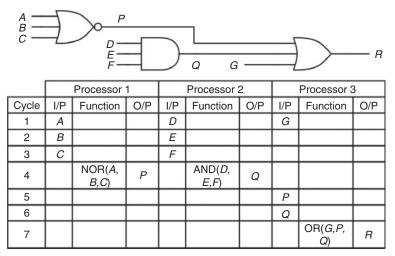

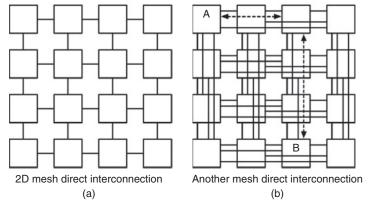

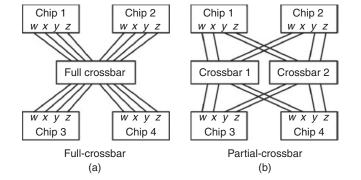

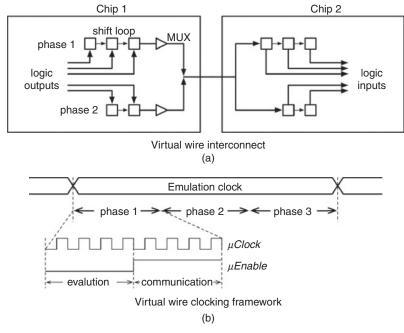

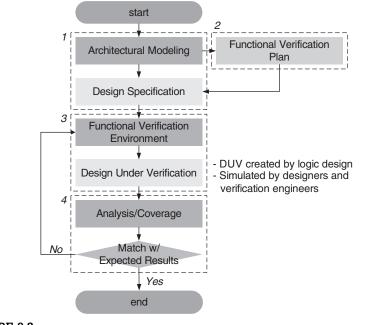

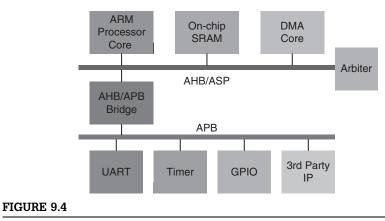

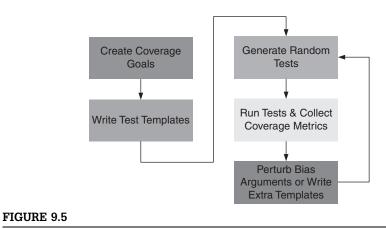

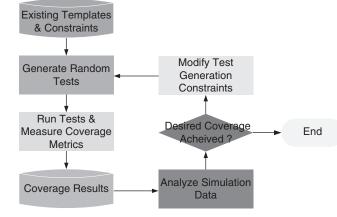

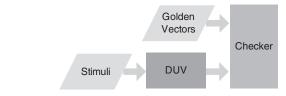

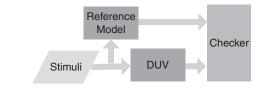

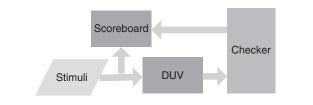

Chapter 8 covers various *logic and circuit simulation* techniques that allow a designer to understand the dynamic behavior of a system at different stages of the design flow. The chapter begins with a discussion of logic simulation techniques that are fundamental to software simulators. Next, hardware-accelerated logic simulation, which is commonly referred to as *emulation*, is introduced. Both logic simulation and emulation of systems are typically performed at a higher level of design abstraction. The last part of the chapter deals with the simulation of the most basic components of a circuit, namely, devices and interconnects. Chapter 9 is devoted to *functional verification*. This chapter first introduces the verification processes at various design stages. Common structural and functional coverage metrics which measure the verification quality are described. This chapter also discusses the key tasks involved in *simulation-based verification*, such as *stimulus generation*, *assertion-based verification*, and *random testing*. The mathematical backgrounds and examples for various formal approaches are also provided. Advanced verification techniques are presented as supplements at the end of the chapter.

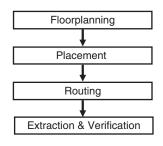

Chapter 10 addresses *floorplanning* of the physical design process. The two most popular approaches to floorplanning, *simulated annealing* and *analytical formulations*, are covered. Based on simulated annealing, three popular floorplan representations, *normalized Polished expression*, *B\*-tree*, and *sequence pair* are further discussed and compared. Some modern floorplanning issues related to soft modules, fixed-outline constraints, and large-scale designs are also addressed.

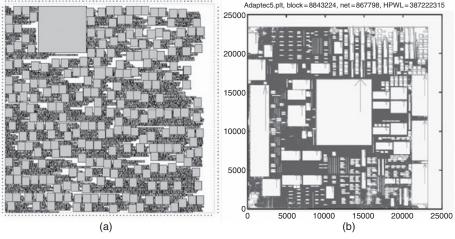

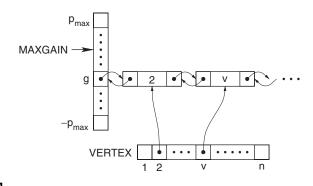

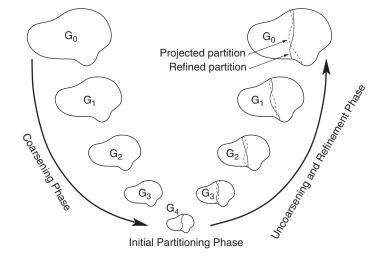

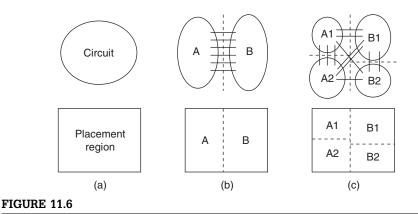

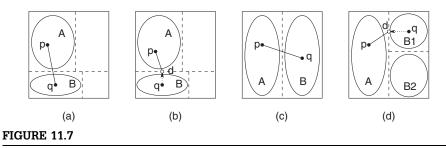

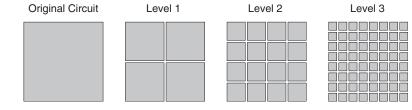

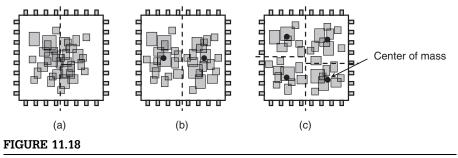

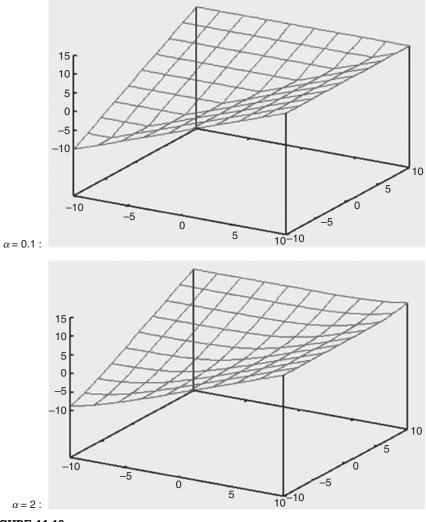

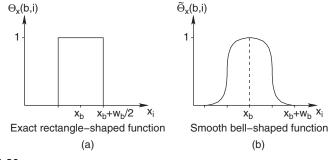

Chapter 11 covers *placement* of the physical design process. This chapter focuses on techniques to solve the *global placement* problem. Algorithms for the most common global placement approaches, namely *partitioning-based approach*, *simulated annealing approach* and *analytical approach*, are presented. The analytical approach is particularly emphasized as the best global placement algorithms are all based on the analytical approach. Techniques for *legalization* and *detailed placement* are also discussed.

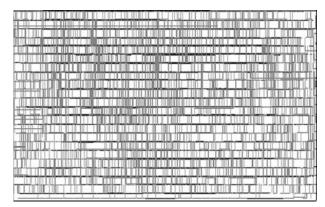

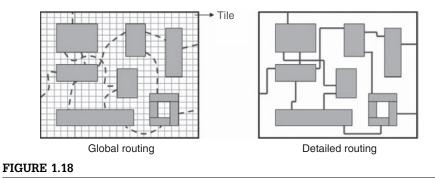

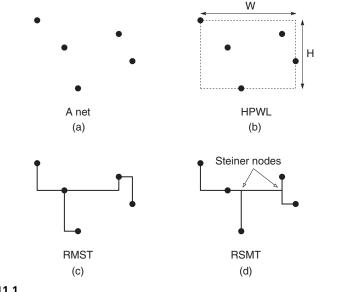

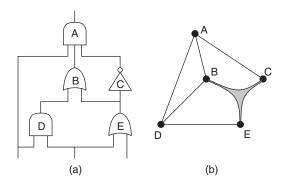

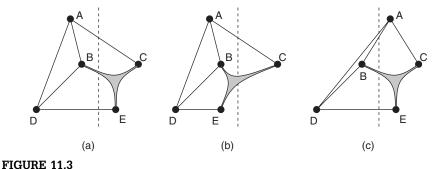

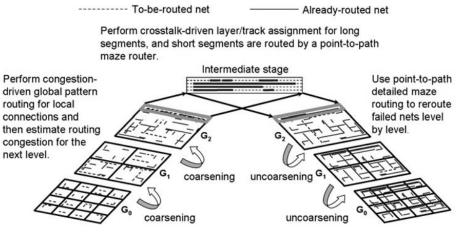

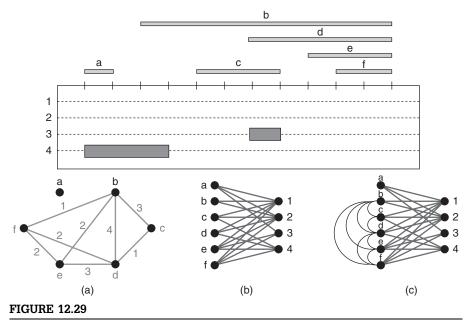

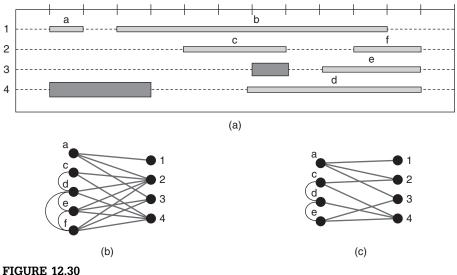

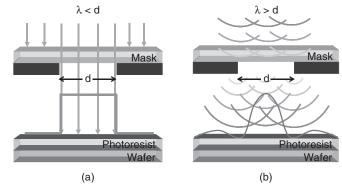

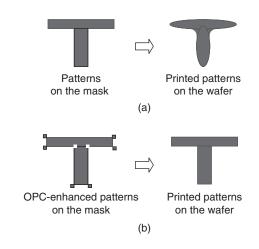

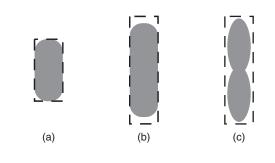

Chapter 12 covers *signal routing*. This chapter classifies the routing algorithms into three major categories: *general-purpose routing*, *global routing*, and *detailed routing*. For general-purpose routing, maze routing, line-search routing, and *A\*-searcb* routing are discussed. For global routing, both sequential and concurrent techniques are covered. Steiner tree construction is also addressed to handle the interconnection of multi-terminal nets. Some modern routing considerations in signal integrity, manufacturability, and reliability such as crosstalk *optical proximity correction* (OPC), *chemical-mechanical polishing* (CMP), antenna effect, and double-via insertion, are also briefly discussed.

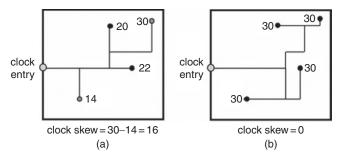

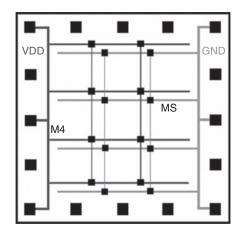

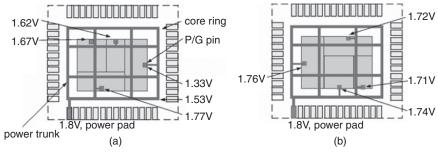

Chapter 13 addresses the *synthesis of clock and power/ground networks*, with a stronger emphasis on clock network synthesis. Following a discussion of the key issues that affect the integrity of clock networks and power/ground networks, the chapter delves into the automated analysis, synthesis, and optimization of both types of large-scale interconnection networks.

Chapter 14 consists of two major VLSI testing topics – *fault simulation* and *automatic test pattern generation* (ATPG) – for producing high-quality test patterns to detect defective chips during manufacturing test. The chapter starts with fault collapsing, which helps speed up fault simulation and ATPG. Several fault simulation techniques, including serial, parallel, concurrent, and differential fault simulation, are introduced and compared. Next, basic ATPG techniques, including Boolean difference, PODEM, and FAN, are described. The chapter concludes with advanced test generation techniques to meet the needs of covering defects that arise in deep-submicron devices, including sequential ATPG, delay fault ATPG, and bridging fault ATPG.

### In the Classroom

This book is designed to be used as an entry-level text for undergraduate seniors and first-year graduate students in computer engineering, computer science, and electrical engineering. Selected chapters can also be used to complement existing logic or system design courses. The book is also intended for use as a reference book for researchers and practitioners. It is self-contained with most topics covered extensively from fundamental concepts to current techniques used in research and industry. However, we assume that students have had basic courses in logic design, computer programming, and probability theory. Attempts are made to present algorithms, wherever possible, in an easy-to-understand manner.

To encourage self-learning, the instructor or reader is advised to check the Elsevier companion Web site (http://www.elsevierdirect.com/companions/9780123743640) to access up-to-date software and lecture slides. Instructors will have additional privileges to assess the Solutions directory for all exercises given in each chapter by visiting www.textbooks.elsevier.com and registering a username and password.

Laung-Terng (L.-T.) Wang Yao-Wen Chang Kwang-Ting (Tim) Chang This page intentionally left blank

### Acknowledgments

The editors would like to acknowledge many of their colleagues who helped create this book. First and foremost are the 25 chapter/section contributors listed in the next two pages. Without their strong commitments to contributing the chapters and sections of their specialty to the book in a timely manner, it would not have been possible to publish this book.

We also would like to thank the external reviewers in providing invaluable feedback to improve the contents of this book. We would like to thank Prof. Robert K. Brayton (University of California, Berkeley), Prof. Hung-Ming Chen (National Chiao Tung University), Prof. Jiang Hu (Texas A&M University), Professors Alan J. Hu and Andre Ivanov (University of British Columbia, Canada), Prof. Jing-Yang Jou (National Chiao Tung University), Prof. Shinji Kimura (Waseda University, Japan), Prof. Chong-Min Kyung (Korea Advanced Institute of Science and Technology, Korea), Prof. Yu-Min Lee (National Chiao Tung University), Prof. Eric MacDonald (University of Texas at El Paso), Prof. Subhasish Mitra (Stanford University), Prof. Preeti Ranjan Panda (India Institute of Technology at Delhi, India), Prof. Kewal K. Saluja (University of Wisconsin -Madison), Prof. Tsutomu Sasao (Kyushu Institute of Technology, Japan), Prof. Sheldon X.-D. Tan (University of California at Riverside), Prof. Ren-Song Tsay (National Tsing Hua University, Taiwan), Prof. Natarajan Viswanathan (Iowa State University), Prof. Ting-Chi Wang (National Tsing Hua University, Taiwan), Prof. Martin D. F. Wong, (University of Illinois at Urbana-Champagne), Prof. Hiroto Yasuura (Kyushu University, Japan), Prof. Evangeline F. Y. Young (Chinese University of Hong Kong, China), Prof. Tian-Li Yu (National Taiwan University), Khader S. Abdel-Hafez (Synopsys, Mountain View, CA), Dr. Aiqun Cao (Synopsys, Mountain View, CA), Wen-Chi Chao and Tzuo-Fan Chien (National Taiwan University), Dr. Tsung-Hao (Howard) Chen (Mentor Graphics, San Jose, CA), William Eklow (Cisco, San Jose, CA), Dr. Farzan Fallah (Fujitsu Laboratories of America, Sunnyvale, CA), Dr. Patrick Girard (LIRMM/CNRS, Montpellier, France), Dr. Sumit Gupta (Nvidia, San Jose, CA), Meng-Kai Hsu and Po-Sen Huang (National Taiwan University), Dr. Rohit Kapur (Synopsys, Mountain View, CA), Dr. Brion Keller (Cadence Design Systems, Endicott, NY), Benjamin Liang (University of California, Berkeley), T. M. Mak (Intel, Santa Clara, CA), Dr. Alan Mishchenko (University of California at Berkeley), Dr. Benoit Nadeau-Dostie (LogicVision, Ottawa, Canada), Linda Paulson (University of California, Santa Barbara), Chin-Khai Tang (National Taiwan University), Jensen Tsai (SpringSoft, Hsinchu, Taiwan), Dr. Chung-Wen Albert Tsao (Cadence Design Systems, San Jose, CA), Natarajan Viswanathan (Iowa State University), Dr. Bow-Yaw Wang (Academia Sinica, Taipei, Taiwan), Dr. Ming-Yang Wang (SpringSoft, Fremont, CA), Ho-Chun Wu (Cadence Design Systems, Hsinchu, Taiwan), Dr. Jin Yang (Intel, Hillsboro, OR), and all chapter/section contributors for cross-reviewing the manuscript. Special thanks also go to Wan-Ping Lee and Guang-Wan Liao of National Taiwan University and many colleagues at SynTest Technologies, Inc., including Dr. Ravi Apte, Boryau Sheu, Dr. Zhigang Jiang, Jianping Yan, Jianghao Guo, Fangfang Li, Lizhen Yu, Ginger Qian, Jiayong Song, Sammer Liu, and Teresa Chang who helped draw symbolic layouts, review the manuscript, solve exercises, develop lecture slides, and draw figures and tables.

Finally, we would like to acknowledge the generosity of SynTest Technologies (Sunnyvale, CA) for allowing Elsevier to put an exclusive version of the company's most recent VLSI Testing and DFT software on the Elsevier companion Web site for readers to use in conjunction with the book to become acquainted with DFT practices.

### Contributors

**Stephen F. Cauley,** Ph.D. Student (Chapters 8 and 13) School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana

**Huang-Yu Chen**, Ph.D. Student (Chapter 12) Graduate Institute of Electronics Engineering, National Taiwan University, Taipei, Taiwan

**Tung-Chieh Chen,** Post-Doctoral Fellow (Chapter 10) Graduate Institute of Electronics Engineering, National Taiwan University, Taipei, Taiwan

Xinghao Chen, Ph.D. (Chapters 2 and 3) CTC Technologies, Endwell, New York

**Chris Chu**, Associate Professor (Chapter 11) Department of Electrical and Computer Engineering, Iowa State University, Ames, Iowa

**Srinivas Devadas,** Professor and Associate Head, EECS, IEEE Fellow (Chapter 6) Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts

**Nikil Dutt**, Chancellor's Professor, IEEE Fellow (Chapter 5) Department of Computer Science, University of California, Irvine, California

**Yinhe Han**, Associate Professor (Chapter 3) Institute of Computing Technology, Chinese Academy of Sciences, Beijing, China

**Michael S. Hsiao**, Professor and Dean's Faculty Fellow (Chapter 14) Bradley Department of Electrical and Computer Engineering, Virginia Tech, Blacksburg, Virginia

**Chung-Yang (Ric) Huang,** Assistant Professor (Chapter 4) Graduate Institute of Electronics Engineering, National Taiwan University, Taipei, Taiwan **Jiun-Lang Huang,** Associate Professor (Chapter 8) Graduate Institute of Electronics Engineering, National Taiwan University, Taipei, Taiwan

**Jitesh Jain,** Post-Doctoral Fellow (Chapters 8 and 13) School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana

**Jie-Hong (Roland) Jiang,** Assistant Professor (Chapter 6) Graduate Institute of Electronics Engineering, National Taiwan University, Taipei, Taiwan

**Cheng-Kok Koh**, Associate Professor (Chapters 8 and 13) School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana

**Chao-Yue Lai,** Research Assistant (Chapter 4) Graduate Institute of Electronics Engineering, National Taiwan University, Taipei, Taiwan

James C.-M. Li, Associate Professor (Chapter 14) Graduate Institute of Electronics Engineering, National Taiwan University, Taipei, Taiwan

Xiaowei Li, Professor (Chapter 3) Institute of Computing Technology, Chinese Academy of Sciences, Beijing, China

**Charles E. Stroud,** Professor, IEEE Fellow (Chapter 1) Department of Electrical and Computer Engineering, Auburn University, Auburn, Alabama

**Nur A. Touba,** Professor, IEEE Fellow (Chapters 2 and 3) Department of Electrical and Computer Engineering, University of Texas, Austin, Texas

**Li-C. Wang,** Associate Professor (Chapter 9) Department of Electrical and Computer Engineering, University of California, Santa Barbara, California

**Ruilin Wang**, Ph.D. Student (Chapter 13) School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana

**Hung-Pin (Charles) Wen,** Assistant Professor (Chapter 9) Department of Communication Engineering, National Chiao Tung University, Hsinchu, Taiwan **Xiaoqing Wen,** Professor (Chapters 3 and 7) Graduate School of Computer Science and Systems Engineering, Kyushu Institute of Technology, Fukuoka, Japan

**Shianling Wu**, Vice President of Engineering (Chapter 7) SynTest Technologies, Inc., Princeton Junction, New Jersey

**Jianwen Zhu,** Associate Professor (Chapter 5) Department of Electrical and Computer Engineering, University of Toronto, Toronto, Ontario, Canada This page intentionally left blank

### About the Editors

Laung-Terng (L.-T.) Wang, Ph.D., is chairman and chief executive officer (CEO) of SynTest Technologies (Sunnyvale, CA). He received his BSEE and MSEE degrees from National Taiwan University in 1975 and 1977, respectively, and his MSEE and EE Ph.D. degrees under the Honors Cooperative Program (HCP) from Stanford University in 1982 and 1987, respectively. He worked at Intel (Santa Clara, CA) and Daisy Systems (Mountain View, CA) from 1980 to 1986 and was with the Department of Electrical Engineering of Stanford University as Research Associate and Lecturer from 1987 to 1991. Encouraged by his advisor, Professor Edward J. McCluskey, a member of the National Academy of Engineering, he founded SynTest Technologies in 1990. Under his leadership, the company has grown to more than 50 employees and 250 customers worldwide. The design for testability (DFT) technologies Dr. Wang has developed have been successfully implemented in thousands of ASIC designs worldwide. He currently holds 18 U.S. Patents and 12 European Patents in the areas of scan synthesis, test generation, at-speed scan testing, test compression, logic built-in self-test (BIST), and design for debug and diagnosis. Dr. Wang's work in at-speed scan testing, test compression, and logic BIST has proved crucial to ensuring the quality and testability of nanometer designs, and his inventions are gaining industry acceptance for use in designs manufactured at the 90-nanometer scale and below. He spearheaded efforts to raise endowed funds in memory of his NTU chair professor, Dr. Irving T. Ho, cofounder of the Hsinchu Science Park and vice chair of the National Science Council, Taiwan. Since 2003, he has helped establish a number of chair professorships, graduate fellowships, and undergraduate scholarships at Stanford University, National Taiwan University and National Tsing Hua University in Taiwan, as well as Xiamen University, Tsinghua University, and Shanghai Jiaotong University in China. Dr. Wang has co-authored and co-edited two internationally used DFT textbooks - VLSI Test Principles and Architectures: Design for Testability (2006) and System-on-Chip Test Architectures: Nanometer Design for Testability (2007). A member of Sigma Xi, he received a Meritorious Service Award from the IEEE Computer Society in 2007 and is a Fellow of the IEEE.