# phyBOARD®-Mira-i.MX 6

# **Application Guide**

Document No.: L-806e\_0

SBC Prod. No..: **PB-01501-xxx**

CB PCB No.: **1434.0** SOM PCB No.: **1429.0**

**Edition:** February 2015

Copyrighted products are not explicitly indicated in this manual. The absence of the trademark (<sup>TM</sup>, or <sup>®</sup>) and copyright (©) symbols does not imply that a product is not protected. Additionally, registered patents and trademarks are similarly not expressly indicated in this manual.

The information in this document has been carefully checked and is considered to be entirely reliable. However, PHYTEC Messtechnik GmbH assumes no responsibility for any inaccuracies. PHYTEC Messtechnik GmbH neither gives any guarantee nor accepts any liability whatsoever for consequential damages resulting from the use of this manual or its associated product. PHYTEC Messtechnik GmbH reserves the right to alter the information contained herein without prior notification and accepts no responsibility for any damages that might result.

Additionally, PHYTEC Messtechnik GmbH offers no guarantee nor accepts any liability for damages arising from the improper usage or improper installation of the hardware or software. PHYTEC Messtechnik GmbH further reserves the right to alter the layout and/or design of the hardware without prior notification and accepts no liability for doing so.

#### © Copyright 2015 PHYTEC Messtechnik GmbH, D-55129 Mainz.

Rights - including those of translation, reprint, broadcast, photomechanical or similar reproduction and storage or processing in computer systems, in whole or in part - are reserved. No reproduction may occur without the express written consent from PHYTEC Messtechnik GmbH.

|           | EUROPE                                       | NORTH AMERICA                  | FRANCE                     |

|-----------|----------------------------------------------|--------------------------------|----------------------------|

| Address:  | PHYTEC Messtechnik GmbH                      | PHYTEC America LLC             | PHYTEC France              |

|           | Robert-Koch-Str. 39                          | 203 Parfitt Way SW, Suite G100 | 17, place Saint-Etienne    |

|           | D-55129 Mainz                                | Bainbridge Island, WA 98110    | F-72140 Sillé-le-Guillaume |

|           | GERMANY                                      | USA                            | FRANCE                     |

| Sales:    | +49 (6131) 9221-32                           | +1 (800) 278-9913              | +33 (0)2 43 29 22 33       |

|           | sales@phytec.de                              | sales@phytec.com               | info@phytec.fr             |

| Technical | +49 (6131) 9221-31                           | +1 (206) 780-9047              | support@phytec.fr          |

| Support:  | support@phytec.de                            | support@phytec.com             |                            |

| Fax:      | +49 (6131) 9221-33                           | +1 (206) 780-9135              | +33 (0)2 43 29 22 34       |

| Web Site: | http://www.phytec.de<br>http://www.phytec.eu | http://www.phytec.com          | http://www.phytec.fr       |

|                       | INDIA                                                                                                                                 | CHINA                                                                                                                                                       |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address:              | PHYTEC Embedded Pvt. Ltd.<br>#16/9C, 3rd Main, 3rd Floor, 8th Block,<br>Opp. Police Station Koramangala,<br>Bangalore-560095<br>INDIA | PHYTEC Information Technology (Shenzhen) Co. Ltd.<br>Suite 2611, Floor 26, Anlian Plaza,<br>4018 Jin Tian Road<br>Futian District, Shenzhen<br>CHINA 518026 |

| Sales:                | +91-80-4086 7046/48 sales@phytec.in                                                                                                   | +86 (755) 3395 5875<br>sales@phytec.cn                                                                                                                      |

| Technical<br>Support: | +91-80-4086 7047<br>support@phytec.in                                                                                                 | support@phytec.cn                                                                                                                                           |

| Fax:                  |                                                                                                                                       | +86 (755) 3395 5999                                                                                                                                         |

| Web Site:             | http://www.phytec.in                                                                                                                  | http://www.phytec.cn                                                                                                                                        |

# Preliminary Edition February 2015

| List o | of Fig | ures           | •••••       | •••••••••••••••••••••••••••••••••••••••                                | iii |

|--------|--------|----------------|-------------|------------------------------------------------------------------------|-----|

| List o | of Tab | oles           | •••••       | ••••••                                                                 | iv  |

| Conv   | entio  | ns, Abb        | reviation   | s and Acronyms                                                         | V   |

|        |        |                |             |                                                                        |     |

|        |        |                |             | ••••••                                                                 |     |

| 1      |        |                |             |                                                                        |     |

|        | 1.1    |                |             | ew                                                                     |     |

|        |        | 1.1.1<br>1.1.2 |             | agramhe phyBOARD-Mira-i.MX 6                                           |     |

|        | 1.2    |                |             | w                                                                      |     |

|        | 1.2    | 1.2.1          |             | vv                                                                     |     |

|        |        | 1.2.2          |             |                                                                        |     |

|        |        | 1.2.3          |             | or                                                                     |     |

|        |        | 1.2.4          | The GNU     | Cross Development Toolchain                                            | 6   |

| 2      | Appl   | ication        | Programn    | ning                                                                   | 7   |

|        | 2.1    | Installi       | ng our mo   | odified Ubuntu Live System                                             | 7   |

|        | 2.2    |                | g with Ecli |                                                                        | 8   |

|        |        | 2.2.1          | Program     | ming in the C/C++ Perspective                                          | 8   |

|        |        |                | 2.2.1.1     | Work with the Demo Project                                             | 8   |

|        |        |                | 2.2.1.2     | Creating a New Project                                                 |     |

|        |        |                | 2.2.1.3     | Modifying the Demo Application                                         |     |

|        |        |                | 2.2.1.4     | Starting a Program out of Eclipse on the Target                        |     |

|        |        | 2.2.2          |             | ng an Example Project                                                  |     |

|        |        |                | 2.2.2.1     | Starting the GDB Server on the Target                                  |     |

|        |        |                | 2.2.2.2     | Configuring and starting the Debugger in Eclipse  Setting a Breakpoint |     |

|        |        |                | 2.2.2.4     | Stepping through and Watching Variable Contents                        |     |

|        |        |                | 2.2.2.5     | Stepping through and Changing Variable Contents                        |     |

|        |        |                | 2.2.2.6     | Using the Memory Monitor                                               |     |

| 3      | Acce   | ssina th       |             | ARD-Mira Features                                                      |     |

|        | 3.1    | •              | . / -       | hyBOARD-Mira Peripherals                                               |     |

|        | J.1    | 3.1.1          |             | ors and Pin Header                                                     |     |

|        |        | 3.1.2          |             |                                                                        |     |

|        |        | 3.1.3          |             |                                                                        |     |

|        | 3.2    | Functio        | nal Comp    | onents on the phyBOARD-Mira SBC                                        | 41  |

|        |        | 3.2.1          |             | ıpply                                                                  |     |

|        |        |                | 3.2.1.1     | Power Connectors (X2)                                                  |     |

|        |        |                |             | 3.2.1.1.1 PHOENIX 2-pole MINI COMBICON Base Strip (X2)                 |     |

|        |        |                |             | 3.2.1.1.2 WAGO 6-pole Male Header (X2)                                 |     |

|        |        |                | 3.2.1.2     | Power LED D2                                                           |     |

|        |        | 2 2 2          | 3.2.1.3     | VBAT, RTC and JP3                                                      |     |

|        |        | 3.2.2          | 3.2.2.1     | nnectivity (X17 and X23)                                               |     |

|        |        | 3.2.3          |             | Software Implementation                                                |     |

|        |        | ٥.٢.٥          | 3.2.3.1     | Software Implementation                                                |     |

|        |        | 3.2.4          |             | nectivity (X5 and X6)                                                  |     |

|        |        | J.=• 1         | 3.2.4.1     | Software Implementation                                                |     |

|        |        |                |             | 3.2.4.1.1 USB Host                                                     |     |

|   |      |         | 3.2.4.1.2 USB OTG                                                        | .48 |

|---|------|---------|--------------------------------------------------------------------------|-----|

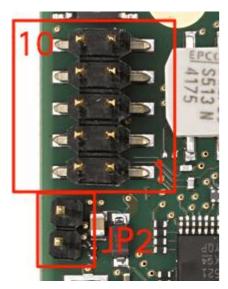

|   |      | 3.2.5   | CAN Connectivity (X3, JP2)                                               | 49  |

|   |      |         | 3.2.5.1 Software Implementation                                          |     |

|   |      | 3.2.6   | Secure Digital Memory Card/MultiMedia Card (X22)                         | 52  |

|   |      |         | 3.2.6.1 Software Implementation                                          |     |

|   |      | 3.2.7   | PCIe Connectivity (X7)                                                   |     |

|   |      |         | 3.2.7.1 Software Implementation                                          | 53  |

|   |      | 3.2.8   | Camera Connectivity (X10)                                                | 54  |

|   |      |         | 3.2.8.1 Software Implementation                                          | 54  |

|   |      | 3.2.9   | HDMI Connectivity (X28)                                                  | 54  |

|   |      |         | 3.2.9.1 Software Implementation                                          |     |

|   |      | 3.2.10  |                                                                          | 56  |

|   |      |         | 3.2.10.1 Software Implementation                                         | 56  |

|   |      |         | Backlight and Control Connector (X8)                                     | 56  |

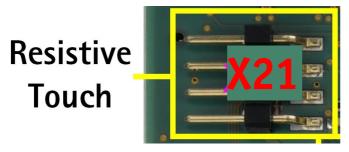

|   |      | 3.2.12  | Touch Screen Connectivity (X13, X21)                                     |     |

|   |      |         | 3.2.12.1 Software Implementation                                         | 57  |

|   |      | 3.2.13  | Multicolor (RGB) LED (D6)                                                | 57  |

|   |      |         | 3.2.13.1 Software Implementation                                         | 57  |

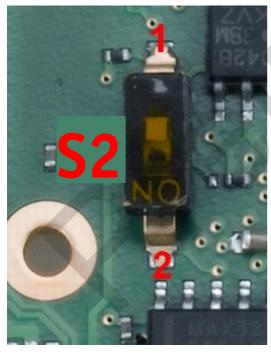

|   |      | 3.2.14  | Boot Mode (S2)                                                           | 58  |

|   |      | 3.2.15  | System Reset Button (S1)                                                 |     |

|   |      | 3.2.16  | Audio/Video connectors (X13 and X14)                                     |     |

|   |      | 3.2.17  | Expansion connector (X17)                                                |     |

|   |      |         | Addressing the RTC                                                       |     |

|   |      | 3.2.19  |                                                                          | 60  |

| , |      | 3.2.20  | Using Qt                                                                 | 61  |

| 4 | Syst | em Leve | l Customizinghis Section                                                 | 62  |

|   |      |         |                                                                          |     |

|   | 4.2  |         | re Overview                                                              |     |

|   | 4.3  | _       | Started with the BSP                                                     |     |

|   |      |         | Working with Yocto                                                       |     |

|   |      | 4.3.2   | Writing the Images into the Target's Flash                               |     |

|   | 4.4  |         | ng the software                                                          | 69  |

|   |      | 4.4.1   | Creating a bootable SD card                                              |     |

|   |      | 4.4.2   | Flashing the Bootloader                                                  |     |

|   |      | 4.4.3   | Writing the Kernel / Root File System into Flash                         |     |

|   | 4.5  | •       | Level Hardware Information                                               |     |

|   |      | 4.5.1   | USB Connectivity (X5, X6, X7 and X17)                                    | 71  |

|   |      |         | 4.5.1.1 Rerouting the USB Interfaces to other Connectors (J5, J6, J9 and | - 4 |

|   |      | ( 5 0   | J10)                                                                     |     |

|   |      | 4.5.2   | HDMI Connector (X28)                                                     |     |

|   |      | 4.5.3   | LVDS connector (X9)                                                      |     |

|   |      | 4.5.4   | CAN Connectivity                                                         |     |

|   |      | 4.5.5   | Mini PCI express connector (X7)                                          | 75  |

|            | 4.5.6 Au                                   | udio/Video connectors (X13 and X14)       | 77 |

|------------|--------------------------------------------|-------------------------------------------|----|

|            | 4.                                         | 5.6.1 Software Implementation             |    |

|            |                                            | 4.5.6.1.1 Framebuffer                     |    |

|            |                                            | 4.5.6.1.2 Touch                           |    |

|            |                                            | 4.5.6.1.3 Audio I <sup>2</sup> S          |    |

|            | / E 7 Ev                                   | 4.5.6.1.4 I <sup>2</sup> C Connectivity   |    |

|            |                                            | spansion connector (X17)                  |    |

|            | 4.                                         | 4.5.7.1.1 UART Connectivity               |    |

|            |                                            | 4.5.7.1.2 SPI Connectivity                |    |

|            |                                            | 4.5.7.1.3 I <sup>2</sup> C Connectivity   |    |

|            |                                            | 4.5.7.1.4 User programmable GPIOs         | 85 |

| 5 Revis    | ion Histor                                 | у                                         | 86 |

| Index      | ••••••                                     |                                           | 87 |

|            |                                            |                                           |    |

| List of Fi | aures                                      |                                           |    |

|            | •                                          |                                           |    |

| Figure 1:  |                                            | gram of the phyBOARD-Mira-i.MX 6          |    |

| Figure 2:  |                                            | ne phyBOARD-Mira-i.MX 6 (top)             |    |

| Figure 3:  |                                            | ne phyBOARD-Mira-i.MX 6 (bottom)          |    |

| Figure 4:  |                                            | pply Connectors(X2)                       |    |

| Figure 5:  | RS-232 o                                   | r RS-485 Interface Connector X23          | 44 |

| Figure 6:  | RS-232/                                    | RS-485 Connector Signal Mapping           | 45 |

| Figure 7:  | Ethernet                                   | Interface at Connectors X4                | 46 |

| Figure 8:  | Components supporting the USB Interfaces47 |                                           |    |

| Figure 9:  | Compone                                    | ents supporting the CAN Interface         | 49 |

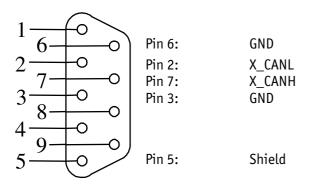

| Figure 10: | CAN Conr                                   | nector Signal Mapping                     | 50 |

| Figure 11: | SD/MM Ca                                   | ard Interface at Connector X22(back side) | 52 |

| Figure 12: | PCIe Inte                                  | erface at Connector X7                    | 53 |

| Figure 13: | Camera I                                   | nterface(phyCAM-S+)at Connector X10       | 54 |

| Figure 14: | HDMI Int                                   | terface Connector X28                     | 55 |

| Figure 15: | Touch Sci                                  | reen Connectors X21                       | 57 |

| Figure 16: | Boot Switch (S2)58                         |                                           |    |

# **List of Tables**

| Table 1:  | Abbreviations and Acronyms used in this Manual                      | vi |

|-----------|---------------------------------------------------------------------|----|

| Table 2:  | phyBOARD-Mira Connectors and Pin Headers                            | 39 |

| Table 3:  | phyBOARD-Mira LEDs Descriptions                                     | 40 |

| Table 4:  | phyBOARD-Mira Switches Description                                  | 40 |

| Table 5:  | Pin Assignment of the 2-pole PHOENIX MINI COMBICON Base Strip at X2 | 42 |

| Table 6:  | Pin Assignment of the 6-pole WAGO Connector at X2                   | 42 |

| Table 7:  | Pinout of the 2-pole pin header JP3                                 | 43 |

| Table 8:  | Pin Assignment of RS-232 /RS-485 Interface Connector X23            |    |

| Table 9:  | Pin Assignment of CAN Connector X3                                  | 49 |

| Table 10: | PHYTEC Camera Connector X10                                         | 54 |

| Table 11: | Display Power Connector X8 Signal Description                       | 56 |

| Table 12: | Touch Screen Connectivity                                           | 57 |

| Table 13: | Multicolor LED Configuration                                        | 57 |

| Table 14: | Boot Switch Configuration (S2)                                      |    |

| Table 15: | USB1 (USB OTG) Routing Configuration                                | 71 |

| Table 16: | USB2 (USB Host) Routing Configuration                               | 71 |

| Table 17: | Pin Assignment HDMI Connector X28                                   | 72 |

| Table 18: | Pin Assignment LVDS Display Connector X9                            | 73 |

| Table 19: | Configuration for LVDS Display Connector X9                         | 74 |

| Table 20: | Configurations for CAN interface                                    | 74 |

| Table 21: | Mini PCI express Connector X7                                       | 76 |

| Table 22: | PHYTEC A/V connector X14                                            | 78 |

| Table 23: | PHYTEC A/V connector X13                                            | 79 |

| Table 24: | A/V Jumper Configuration J1                                         | 79 |

| Table 25: | I <sup>2</sup> C1 Connectivity                                      | 81 |

| Table 26: | I <sup>2</sup> C Addresses in Use                                   | 81 |

| Table 27: | PHYTEC Expansion Connector X17                                      | 84 |

### **Conventions, Abbreviations and Acronyms**

This hardware manual describes the PB-01501-XXX Single Board Computer (SBC) in the following referred to as phyBOARD-Mira-i.MX 6. The manual specifies the phyBOARD-Mira-i.MX 6's design and function. Precise specifications for the Freescale Semiconductor i.MX 6 microcontrollers can be found in the Freescale Semiconductor's i.MX 6 Data Sheet and Technical Reference Manual.

#### **Conventions**

The conventions used in this manual are as follows:

- Signals that are preceded by an "n", "/", or "#"character (e.g.: nRD, /RD, or #RD), or that have a dash on top of the signal name (e.g.: RD) are designated as active low signals. That is, their active state is when they are driven low, or are driving low.

- A "0" indicates a logic zero or low-level signal, while a "1" represents a logic one or high-level signal.

- The hex-numbers given for addresses of I<sup>2</sup>C devices always represent the 7 MSB of the address byte. The correct value of the LSB which depends on the desired command (read (1), or write (0)) must be added to get the complete address byte. E.g. given address in this manual 0x41 => complete address byte = 0x83 to read from the device and 0x82 to write to the device.

- Tables which describe jumper settings show the default position in bold, blue text.

- Text in *blue italic* indicates a hyperlink within, or external to the document. Click these links to quickly jump to the applicable URL, part, chapter, table, or figure.

- Text in bold italic indicates an interaction by the user, which is defined on the screen.

- Text in Consolas indicates an input by the user, without a premade text or button to click on.

- Text in *italic* indicates proper names of development tools and corresponding controls (windows, tabs, commands etc.) used within the development tool, no interaction takes place.

- White Text on black background shows the result of any user interaction (command, program execution, etc.)

# **Abbreviations and Acronyms**

Many acronyms and abbreviations are used throughout this manual. Use the table below to navigate unfamiliar terms used in this document.

| Abbreviation | Definition                                                            |

|--------------|-----------------------------------------------------------------------|

| A/V          | Audio/Video                                                           |

| BSP          | Board Support Package (Software delivered with the Development Kit    |

|              | including an operating system (Windows, or Linux) preinstalled on the |

|              | module and Development Tools).                                        |

| СВ           | Carrier Board; used in reference to the phyBOARD-Mira Development     |

|              | Kit Carrier Board.                                                    |

| DFF          | D flip-flop.                                                          |

| DSC          | Direct Solder Connect                                                 |

| EMB          | External memory bus.                                                  |

| EMI          | Electromagnetic Interference.                                         |

| GPI          | General purpose input.                                                |

| GPI0         | General purpose input and output.                                     |

| GP0          | General purpose output.                                               |

| IRAM         | Internal RAM; the internal static RAM on the Freescale Semiconductor  |

|              | i.MX 6 microcontroller.                                               |

| J            | Solder jumper; these types of jumpers require solder equipment to     |

|              | remove and place.                                                     |

| JP           | Solderless jumper; these types of jumpers can be removed and placed   |

|              | by hand with no special tools.                                        |

| NC           | Not Connected                                                         |

| NM           | Not Mounted                                                           |

| NS           | Not Specified                                                         |

| PCB          | Printed circuit board.                                                |

| PDI          | PHYTEC Display Interface; defined to connect PHYTEC display adapter   |

|              | boards, or custom adapters                                            |

| PEB          | PHYTEC Expansion Board                                                |

| PMIC         | Power management IC                                                   |

| PoE          | Power over Ethernet                                                   |

| PoP          | Package on Package                                                    |

| POR          | Power-on reset                                                        |

| RTC          | Real-time clock.                                                      |

| SBC          | Single Board Computer; used in reference to the PBA-C(D)-06           |

|              | /phyBOARD-Mira-i.MX 6                                                 |

| SMT          | Surface mount technology.                                             |

| SOM          | System on Module; used in reference to the PCM-058 /phyCORE-i.MX 6    |

|              | module                                                                |

| Sx           | User button Sx (e.g. S1, S2) used in reference to the available user  |

|              | buttons, or DIP switches on the CB.                                   |

| Sx_y         | Switch y of DIP switch Sx; used in reference to the DIP switch on the |

|              | carrier board.                                                        |

| VSTBY        | SOM standby voltage input                                             |

Table 1: Abbreviations and Acronyms used in this Manual

**Note:** The BSP delivered with the phyBOARD-Mira-i.MX 6 usually includes drivers and/or software for controlling all components such as interfaces, memory, etc. Therefore programming close to hardware at register level is not necessary in most cases. For this reason, this manual contains no detailed description of the controller's registers. Please refer to the i.MX 6 Technical Reference Manual, if such information is needed to connect customer designed applications.

The BSP is configured according to the hardware configuration including the expansion board delivered with the kit. Thus some functions of the phyBOARD-Mira-i.MX 6 might not be available if the corresponding pins and drivers are needed to support an expansion board. If the expansion board is removed, or exchanged the BSP must be exchanged, too.

From BSP version Am335x-PD14.1-rc1 on it is possible to configure the BSP in regard to the hardware configuration. This allows to easily adapt the BSP if an expansion board is attached, removed, or exchanged.

#### **Preface**

As a member of PHYTEC's new phyBOARD® product family the phyBOARD-Mira-i.MX 6 is one of a series of PHYTEC System on Modules (SBCs) that offer off-the-shelf solutions for a huge variety of industrial applications. The new phyBOARD® product family consists of a series of extremely compact embedded control engines featuring various processing performance classes. All phyBOARDs are rated for industry, cost optimized and offer long-term availability. The phyBOARD-Mira-i.MX 6 is one of currently six industrial-grade carrier boards which are suitable for series production and that have been realized in accordance with PHYTEC's new SBCplus concept. It is an excellent example of this concept.

#### **SBCplus Concept**

The SBCplus concept was developed to meet fine differences in customer requirements with little development effort and thus to greatly reduce the time-to-market.

Core of the SBCplus concept is the SBC design library (a kind of construction set) that consists of a great number of function blocks (so-called "building blocks") which are refined constantly. The recombination of these function blocks allows to develop a customer specific SBC within a short time. Thus, PHYTEC is able to deliver production-ready custom Single Board Computers within a few weeks at very low costs.

The already developed SBCs, such as the phyBOARD-Mira, each represent an intersection of different customer wishes. Because of that all necessary interfaces are already available on the standard versions, thus, allowing to integrate them in a large number of applications without modification. For any necessary detail adjustment extension connectors are available to enable adding of a wide variety of functions.

# Cost-optimized with Direct Solder Connect (DSC) Technology

At the heart of the phyBOARD-Mira is the phyCORE-i.MX 6 System on Module (SOM). As with all SBCs of the phyBOARD family the SOM is directly soldered onto the carrier board PCB for routing of signals from the SOM to applicable I/O interfaces. This "Direct Solder Connect" (DSC) of the SOM eliminates costly PCB to PCB connectors, thereby further reducing overall system costs, and making the phyBOARDs ideally suited for deployment into a wide range of cost-optimized and robust industrial applications.

# **Customized Expandability from PHYTEC**

Common interface signals route to standard connector interfaces on the carrier board such as Ethernet, CAN, RS-232, and audio. Due to the easily modifiable phyBOARD design approach (see "SBCplus concept"), these plug-and-play interfaces can be readily adapted in customer-specific variants according to end system requirements.

Some signals from the processor populating the SOM also extend to the expansion, and A/V connectors of the phyBOARD-Mira. This provides for customized expandability according to end user requirements. Thus expandability is made easy by available plugand-play expansion modules from PHYTEC.

- HDMI and LVDS/Parallel Displays

- Power Supply, with broad voltage range

- Industrial I/O (including WLAN)

- Home-Control Board (WiFi, KNX/EIB, I/O)

- M2M Board (GPS, GSM, I/O's)

- Debug Adapter

The default orientation of the expansion bus connectors is parallel and on the top side of the carrier board PCB. However, in custom configurations the connectors can be mounted on the PCB's underside. Connectors in perpendicular orientation can also populate the top or underside of the PCB. This enables maximum flexibility for orientation of expansion modules on the phyBOARD-Mira, as well as integration of the system into a variety of end application physical envelopes and form factors.

#### Easy Integration of Display und Touch

The phyBOARD and its expansion modules enable easy connection of parallel or LVDS based displays, as well as resistive or capacitive touch screens.

# **OEM Implementation**

Implementation of an OEM-able SBC subassembly as the "core" of your embedded design allows you to focus on hardware peripherals and firmware without expending resources to "re-invent" microcontroller circuitry. Furthermore, much of the value of the phyBOARD SBC lies in its layout and test.

# **Software Support**

Production-ready Board Support Packages (BSPs) and Design Services for our hardware will further reduce your development time and risk and allow you to focus on your product expertise.

### **Ordering Information**

Ordering numbers:

phyBOARD-Mira-i.MX 6 Development Kit: KPB-01501-xxx phyBOARD-Mira-i.MX 6 SBC: PB-01501-xxx

# **Product Specific Information and Technical Support**

In order to receive product specific information on changes and updates in the best way also in the future, we recommend to register at

http://www.phytec.de/de/support/registrierung.html or http://www.phytec.eu/europe/support/registration.html

For technical support and additional information concerning your product, please visit the support section of our web site which provides product specific information, such as errata sheets, application notes, FAQs, etc.

http://www.phytec.de/de/support/faq/faq-phyBOARD-Mira-i.MX6.html or http://www.phytec.eu/europe/support/faq/faq-phyBOARD-Mira-i.MX6.html

# **Other Products and Development Support**

Aside of the new phyBOARD familiy, PHYTEC supports a variety of 8-/16- and 32-bit controllers in two ways:

- (1) as the basis for Rapid Development Kits which serve as a reference and evaluation platform

- (2) as insert-ready, fully functional OEM modules, which can be embedded directly into the user's peripheral hardware design.

Take advantage of PHYTEC products to shorten time-to-market, reduce development costs, and avoid substantial design issues and risks. With this new innovative full system solution you will be able to bring your new ideas to market in the most timely and cost-efficient manner.

# For more information go to:

http://www.phytec.de/de/leistungen/entwicklungsunterstuetzung.html or www.phytec.eu/europe/oem-integration/evaluation-start-up.html

# Declaration of Electro Magnetic Conformity of the PHYTEC phyBOARD-Mira-i.MX 6

PHYTEC Single Board Computers (henceforth products) are designed for installation in electrical appliances, or as part of custom applications, or as dedicated Evaluation Boards (i.e.: for use as a test and prototype platform for hardware/software development) in laboratory environments.

#### Caution!

PHYTEC products lacking protective enclosures are subject to damage by ESD and, hence, may only be unpacked, handled or operated in environments in which sufficient precautionary measures have been taken in respect to ESD-dangers. It is also necessary that only appropriately trained personnel (such as electricians, technicians and engineers) handle and/or operate these products. Moreover, PHYTEC products should not be operated without protection circuitry if connections to the product's pin header rows are longer than 3 m.

PHYTEC products fulfill the norms of the European Union's Directive for Electro Magnetic Conformity only in accordance to the descriptions and rules of usage indicated in this hardware manual (particularly in respect to the pin header row connectors, power connector and serial interface to a host-PC).

Implementation of PHYTEC products into target devices, as well as user modifications and extensions of PHYTEC products, is subject to renewed establishment of conformity to, and certification of, Electro Magnetic Directives. Users should ensure conformance following any modifications to the products as well as implementation of the products into target systems.

# Product Change Management and information in this manual on parts populated on the SOM / SBC

When buying a PHYTEC SOM / SBC, you will, in addition to our HW and SW offerings, receive a free obsolescence maintenance service for the HW we provide.

Our PCM (Product Change Management) Team of developers, is continuously processing, all incoming PCN's (Product Change Notifications) from vendors and distributors concerning parts which are being used in our products.

Possible impacts to the functionality of our products, due to changes of functionality or obsolesce of a certain part, are being evaluated in order to take the right masseurs in purchasing or within our HW/SW design.

Our general philosophy here is: We never discontinue a product as long as there is demand for it.

Therefore we have established a set of methods to fulfill our philosophy:

#### **Avoiding strategies**

- Avoid changes by evaluating long-livety of parts during design in phase.

- Ensure availability of equivalent second source parts.

- Stay in close contact with part vendors to be aware of roadmap strategies.

Change management in case of functional changes

- Avoid impacts on product functionality by choosing equivalent replacement parts.

- Avoid impacts on product functionality by compensating changes through HW redesign or backward compatible SW maintenance.

- Provide early change notifications concerning functional relevant changes of our products.

Change management in rare event of an obsolete and non replaceable part

- Ensure long term availability by stocking parts through last time buy management according to product forecasts.

- Offer long term frame contract to customers.

Therefore we refrain from providing detailed part specific information within this manual, which can be subject to continuous changes, due to part maintenance for our products.

In order to receive reliable, up to date and detailed information concerning parts used for our product, please contact our support team through the contact information given within this manual.

#### 1 Introduction

#### 1.1 Hardware Overview

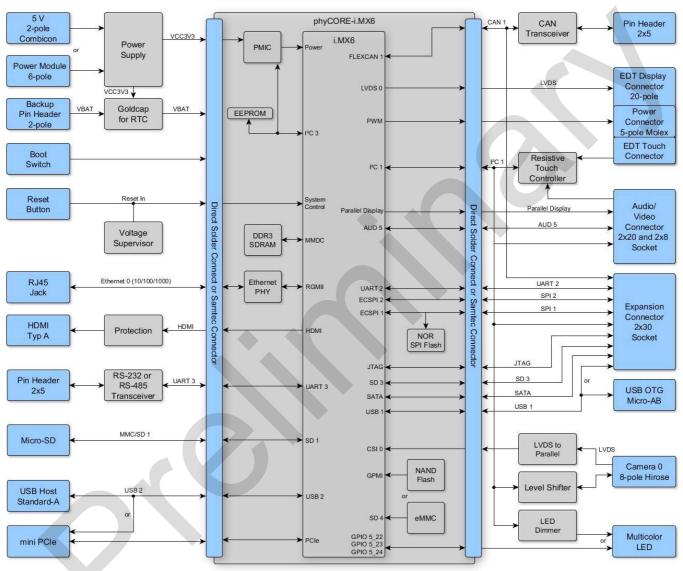

The phyBOARD-Mira for phyCORE-i.MX 6 is a low-cost, feature-rich software development platform supporting the Freescale Semiconductor i.MX 6 microcontroller. Moreover, due to the numerous standard interfaces the phyBOARD-Mira-i.MX 6 can serve as bedrock for your application. At the core of the phyBOARD-Mira is the PCL-058/phyCORE-i.MX 6 System On Module (SOM) in a direct solder form factor, containing the processor, DRAM, NAND Flash, power regulation, supervision, transceivers, and other core functions required to support the i.MX 6 processor. Surrounding the SOM is the PBA-CD-06/phyBOARD-Mira carrier board, adding power input, buttons, connectors, signal breakout, and Ethernet connectivity amongst other things.

- Adding the phyCORE-i.MX 6 SOM into your own design is as simple as orderinDeveloped in accordance with PHYTEC's new SBCplus concept (*Preface*)

- PHYTEC's phyCORE-i.MX 6 SOM

- Pico ITX standard dimensions (100 mm × 72 mm)

- Boot from MMC or NAND Flash

- Max. 1.2 GHz core clock frequency and up to four cores

- Two different power supply options (5 V via 3.5 mm combicon or 12 V 24 V through external power module)

- One RJ45 jacks for 10/100/1000 Mbps Ethernet

- One USB Host interface brought out to an upright USB Standard-A connector, or at the mini PCI express connector

- One USB OTG interface available at an USB Micro-AB connector, or at the expansion connector

- One Secure Digital / Multi Media Memory Card interface brought out to a Micro-SD connector at the back side

- CAN interface at 2×5 pin header 2.54 mm

- One HDMI interface brought out to a standard type A connector

- One LVDS interface brought out to a 20 pin FFC connector at the backside, and separate connector for backlight supply and control

- One touch interface at 1x4 pin header 2.54 mm

- One LVDS camera interfaces compatible to PHYTEC phyCAM-S+ camera standard with I<sup>2</sup>C for camera control

- One PCI interface brought out to a Mini PCI Express connector; SIM-card signals are also available at the expansion connector

- RS-232 or RS-485 transceiver supporting UART3 incl. handshake signals with data rates of up to 1 Mbps (2×5 pin header 2.54 mm)

- Reset-Button

- One multicolor LED

- Audio/Video (A/V) connectors

- Expansion connector with different interfaces

- RTC

- Backup battery supply for RTC with external 2-pole pin-header or with Gold cap (lasts approx. 17 ½ days)

- Industrial temperature range (-40 °C to +85 °C)

#### 1.1.1 Block Diagram

Figure 1: Block Diagram of the phyBOARD-Mira-i.MX 6

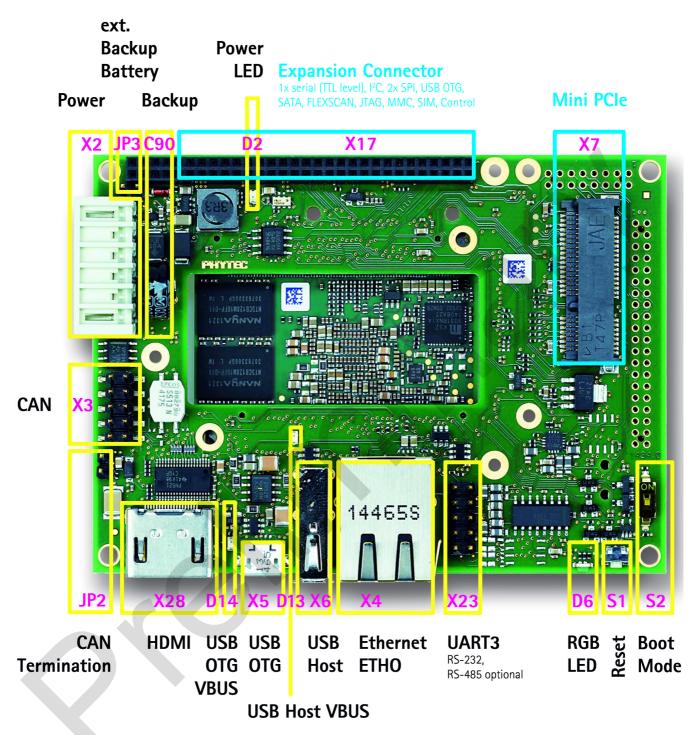

# 1.1.2 View of the phyBOARD-Mira-i.MX 6

Figure 2: View of the phyBOARD-Mira-i.MX 6 (top)

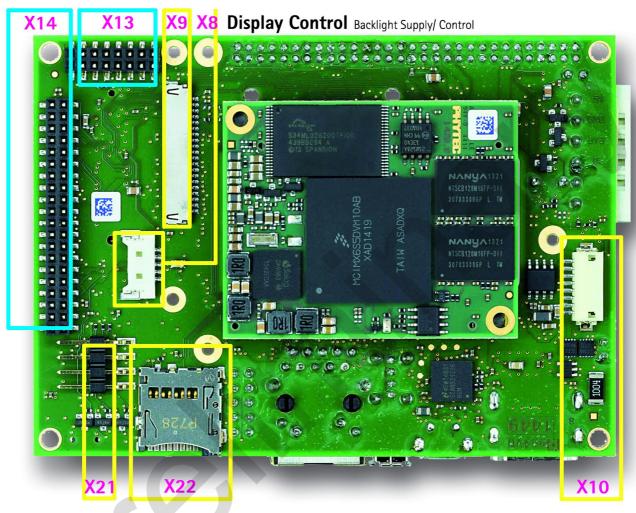

A/V

Connector 1 A/V

(dual entry) Connector 2

RGB Interface (24-bit) I<sup>2</sup>S, Touch, I<sup>2</sup>C, Control Backlight Control LVDS Display Interface

Resitive Touch micro SD SD1

Camera O phyCAM -S+

Figure 3: View of the phyBOARD-Mira-i.MX 6 (bottom)

#### 1.2 Software Overview

#### 1.2.1 Ubuntu

*Ubuntu* - which you is used as operating system for our Live System - is a free and open source operating system based on *Debian Linux*. Basically it is designed for desktop use. Web statistics suggest that *Ubuntu* is one of the most popular operating systems in the Linux desktop environment.

The *Ubuntu* release which we deliver is 14.04.2 and was released on 20. February 2015. *Ubuntu* 14.04 code name "*Trusty Tahr*" is designated as a **Long Term Support (LTS)** release and the first stable release was on 17 April 2014. LTS means that it will be supported and updated for five years.

Our *Ubuntu* version comes with *Unity* as desktop environment, *dpkg* as package management system, the update method is based on *APT* (*Advanced Packaging Tool*) and the user space uses *GNU*.

#### 1.2.2 Eclipse

The *Eclipse* platform provides support for C/C++. Because the *Eclipse* platform is only a framework for developer tools, it does not support C/C++ instead it uses external plug-ins. This Application Guide shows you how to make use of the *CDT*, a set of plug-ins for C/C++ development in conjunction with the GCC C/C++ toolchain.

The *CDT* is an open source project (licensed under the Common Public License) implemented purely in *Java* as a set of plug-ins for the *Eclipse* SDK platform. These plug-ins add a C/C++ perspective to the *Eclipse* Workbench that can now support C/C++ development with a number of views and wizards, along with advanced editing and debugging support.

Due to its complexity, the *CDT* is broken down into several components, which take the form of separate plug-ins. Each component operates as an autonomous project, with its own set of committers, bug categories, and mailing lists. However, all plug-ins are required for the *CDT* to work properly. Here is a list of the plug-ins/components:

- **Primary CDT plug-in** is the "framework" for the *CDT* plug-ins.

- **CDT Feature Eclipse** is the *CDT* Feature Component.

- CDT Core provides Core Model, CDOM, and Core Components.

- **CDT UI** is the Core UI, views, editors, and wizards.

- **CDT Launch** provides the launch mechanism for external tools such as the compiler and debugger.

- **CDT Debug Core** provides debugging functions.

- **CDT Debug UI** provides the user interface for the *CDT* debugging editors, views, and wizards.

- CDT Debug MI is the application connector for MI-compatible debuggers.

#### 1.2.3 Qt Creator

Qt Creator is a cross-platform development environment for the Qt framework. Included are a code editor and a Qt Designer to build graphical user interfaces (GUI). It uses the C++ GNU Compiler.

#### 1.2.4 The GNU Cross Development Toolchain

Cross development in general refers to the overall software development process that produces a single application or a complete system running on a platform that is different from the development platform. This is an important concept when the target system does not have a native set of compilation tools, or when the host system is faster and has greater resources.

The platform where the actual development takes place is called the *host platform*. The platform where the final application is tested and run is called the *target platform*. In this Quick Start we are using an x86-based Linux as the host platform. As the target platform we are using the ARM®Cortex<sup>TM</sup>-A9 architecture on the phyBOARD-Mira-i.MX 6 SBC.

Building a program for a CPU architecture different from the one used on the machine where the compilation is done is accomplished using a cross compiler toolchain and cross-compiled libraries. In this Application Guide we are using the GNU C/C++ cross development toolchain.

# 2 Application Programming

During this chapter you will learn how to build your own C/C++ applications for the target with the help of Eclipse.

We assume that you have first completed our QuickStart Guide successfully.

As all changes on the example projects will be lost if you proceed using the live environment we recommend to now install our modified *Ubuntu* Live System. If you only want to make your own fast experience with our phyBOARD-Mira-i.MX 6-Kit you can continue with section 2.2 "Working with Eclipse".

To ensure successful introduction to the development with the phyBOARD-Mira-i.MX 6 we strongly recommend continuing with the modified *Ubuntu*, either in a live environment, or completely installed on your PC as described in the next section.

Nonetheless; if you want to use your already existing environment we explain how to modify your system to get the same experience as with our Live System in section *O "Flash the device tree* by typing:

erase /dev/nand0.oftree.bb

cp /mnt/tftp/zImage-imx6q-phytec-phyboard-mira.dtb

/dev/nand0.oftree.bb

Write the root file system into flash by typing:

ubiformat /dev/nand0.root

ubiattach /dev/nand0.root

ubimkvol /dev/ubi0 root 0

cp /mnt/tftp/phytec-qt4demo-image-phyboard-mira-imx6-\*.ubifs

/dev/ubi0.root

".

# 2.1 Installing our modified Ubuntu Live System

As described above, this step is not needed to successfully finish this chapter but for more in-depth development it is better to install our Live System on your computer or into a virtual machine. We recommend purchasing our bootable USB flash drive or to create your own USB flash drive as explained in our QuickStart Guide please verify the boot priorities of your system. Plug-in the USB flash drive and restart your PC system. If you have our iso-image you can install the Live System in a virtual machine. If you want to install our Live System native you must create a bootable USB flash drive for example with the help of the UNetbootin Tool under Linux.

We recommend to have at least 70 GB of free disk space available to install the customized Live System.

- There are two methods to install our Live System, but for both the first step is to select

*Install Ubuntu*.

- The Preparing to install Ubuntu... window appears. From Ubuntu it is advised that you select Download updates while installing and Install this third-party software now. Click on Continue.

- The Installation type window appears. You now have different options how to install Ubuntu. Depending on your system you have a number of possibilities that are shown in the dialog. After you have chosen one click on Continue.

- The Install Ubuntu... window appears. After you have checked the settings you can click on Install now.

- While the installation is started *Ubuntu* asks for your location, keyboard layout and login and password details. Please insert this information and wait until the installation is finished.

- Finally you must restart your system after the installation is finished.

- After that the system boots up and you can log into *Ubuntu*. Please configure your network connection now and connect the phyBOARD-Mira-i.XM 6 to your host. How to do that was shown in our QuickStart Guide.

# 2.2 Working with Eclipse

Now we start developing our own applications with the help of *Eclipse*.

# 2.2.1 Programming in the C/C++ Perspective

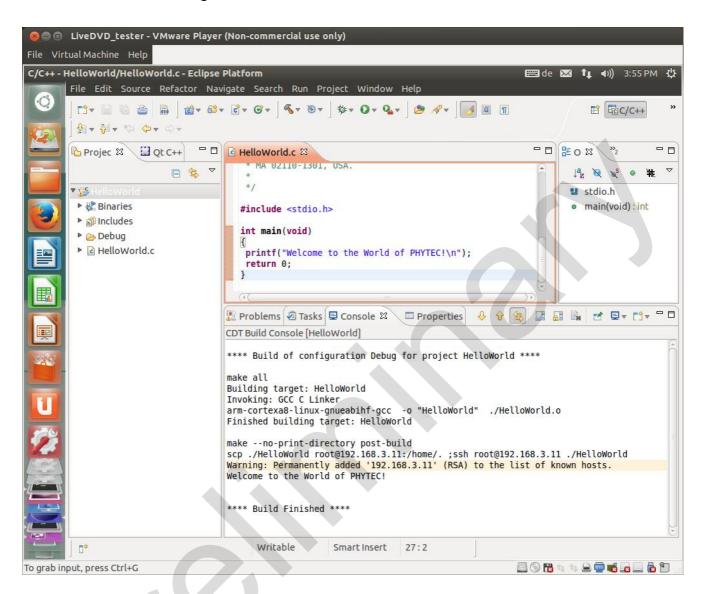

We are starting with the C/C++ workbench. Therefore you will import an existing Eclipse project into your workspace. The imported example project will be compiled with the cross compiler. After that, you will copy and execute the newly created program on the target.

# 2.2.1.1 Work with the Demo Project

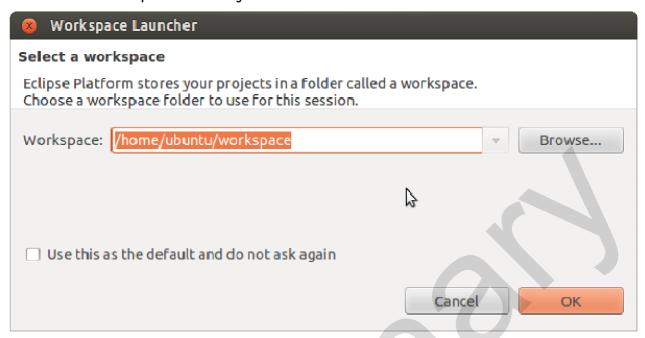

• Click the **Eclipse icon** to start the application. You can find this icon on your desktop.

Confirm the workspace directory with OK

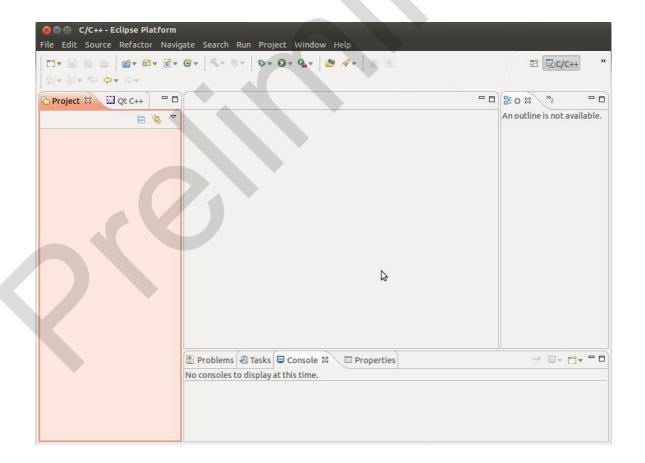

Now you can see the *Eclipse* workbench.

First we will import an existing project.

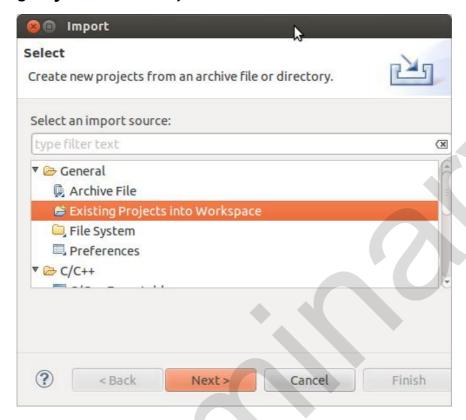

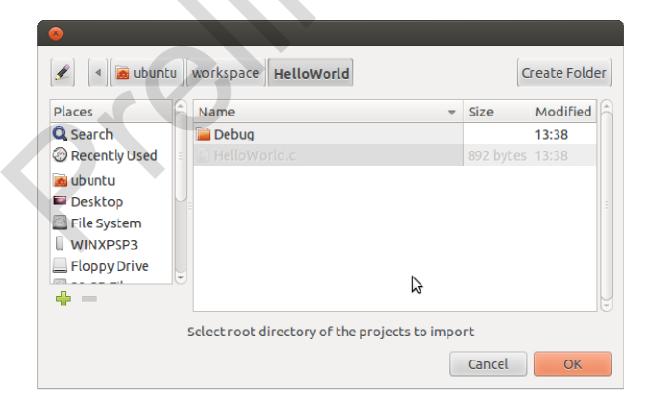

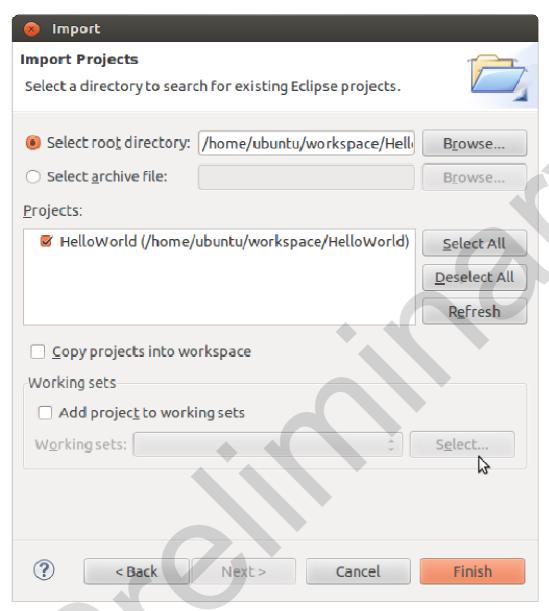

- Select *File* **Import** from the menu bar

- Select Existing Projects into Workspace and click Next

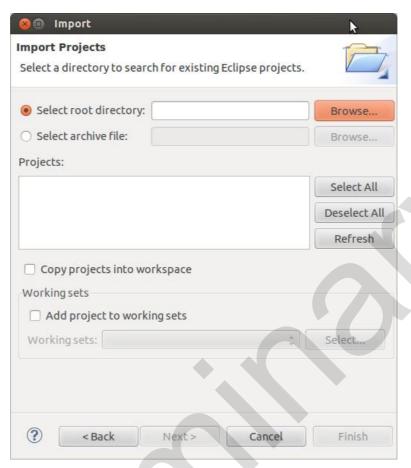

#### Select Browse

- Double-click the HelloWorld directory under /home/ubuntu/workspace/

- Click OK

Select *Finish* to import the project

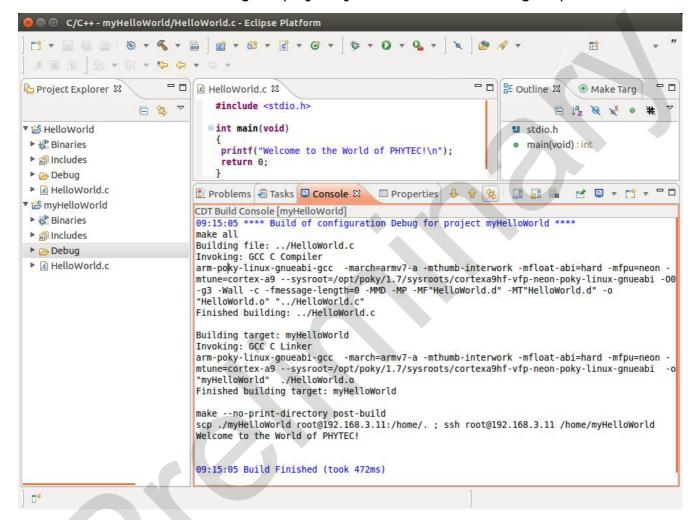

Select Project ➤ Build Project from the menu bar

The *HelloWorld* program will be compiled and the *HelloWorld* executable is built for the target. Then the *HelloWorld* file is copied to the target using *secure copy*. After the file has been copied to the target, the program is executed on the target using *SSH*.

You will see the following content in the Console window:

If you do not get this result verify that you have the target connected to your host, and that the network has been configured as explained in our QuickStart Guide.

You have successfully passed the first steps with the *Eclipse* IDE. You are now able to import existing projects into the *Eclipse* workspace. You can compile an existing project and execute the program on the target.

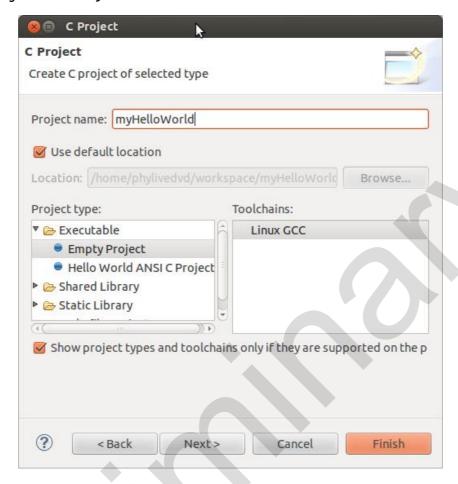

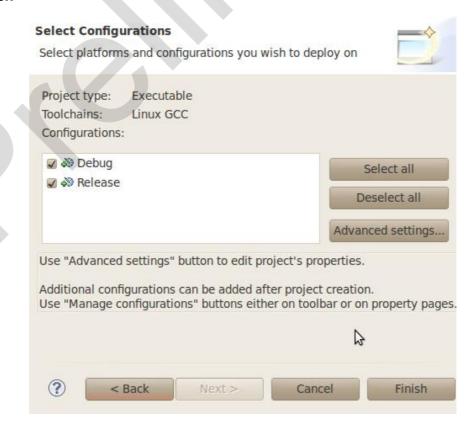

#### 2.2.1.2 Creating a New Project

In this section you will learn how to create a new project with *Eclipse* and how to configure the project for use with the GNU C/C++ cross development toolchain.

- Open *Eclipse* if it is not already opened

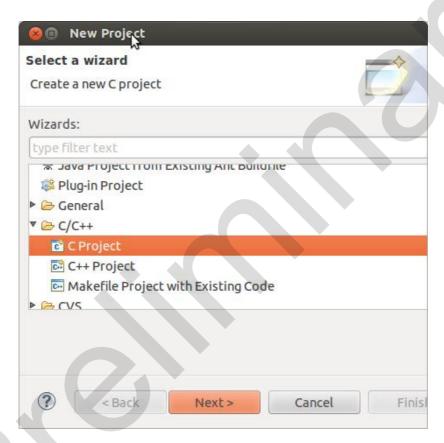

- Select File ➤ New ➤ Project from the menu bar.

A new dialog opens.

Select C Project and click Next

Enter the project name myHelloWorld and click Next

#### • Click Finish

You will see the C/C++ IDE with the myHelloWorld project.

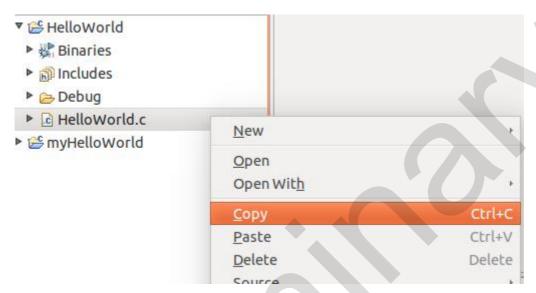

- If the HelloWorld Project is not expand double-click the HelloWorld project which we have worked with previously

- Right-click on HelloWorld.c in the HelloWorld project

- Select Copy

- Select the myHelloWorld project

- Right-click the myHelloWorld project

- Select Paste

- Double-click on HelloWorld.c in the myHelloWorld project

If *Build Automatically* from the *Project* menu is selected, the *HelloWorld* application will now be compiled and created with the standard *GCC C/C*++ compiler suitable for your host machine. You will find the executable file, which can only run on your host system, in the *workspace/myHelloWorld/Debug* directory.

To compile your project for the phyCORE-AM335x instead, you will have to use the GNU C/C++ cross compiler.

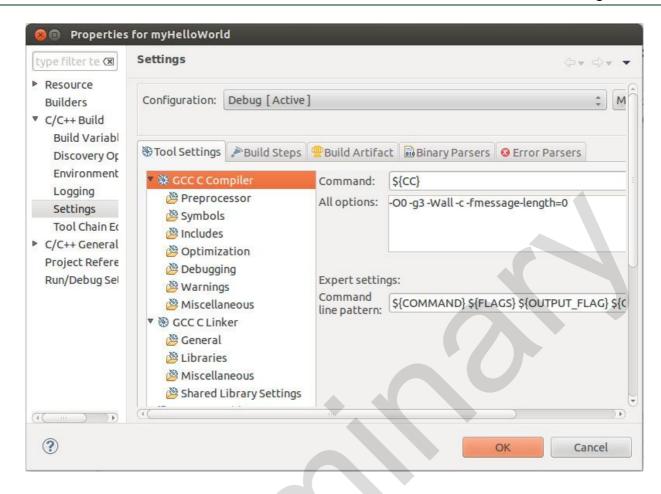

Right-click the myHelloWorld project and choose Properties

The Properties dialog appears.

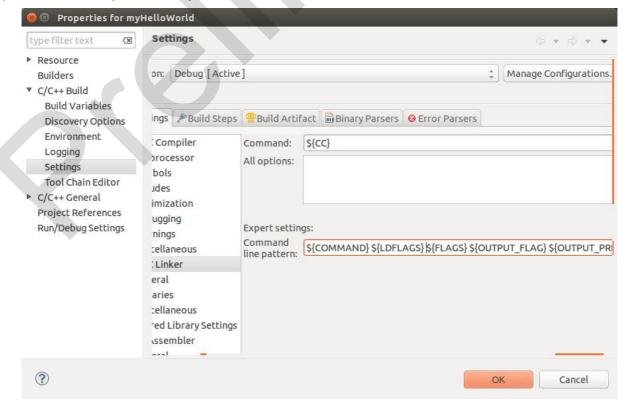

- Select C/C++ Build ➤ Settings

- Enter \${CC} into the Command input field

- Select GCC C Compiler

#### Select GCC C Linker

Enter \${CC} into the Command input field and add \${LDFLAGS} in the Command line pattern after \${COMMAND}

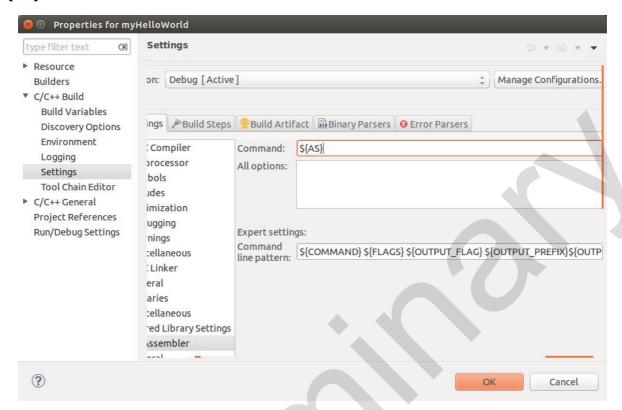

- Select GCC Assembler

- In the Command input field, change the default as to \${AS}

- Click Apply

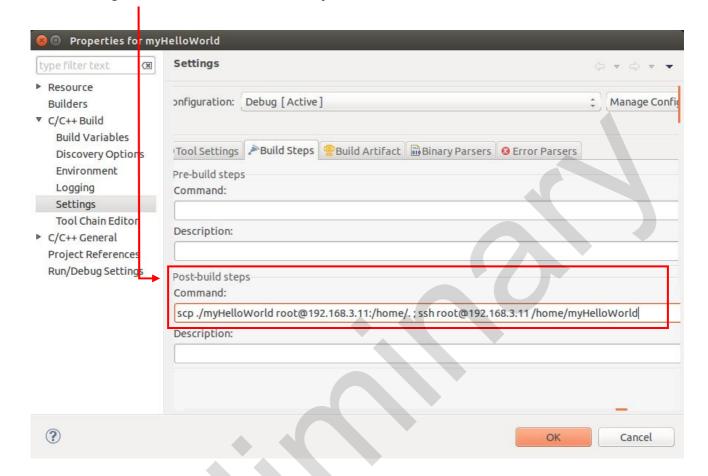

- Select the Build Steps tab

Enter the following command in the Post-build steps Command input field: scp ./myHelloWorld root@192.168.3.11:/home/.;ssh root@192.168.3.11 . /home/myHelloWorld

Be sure to enter the **semicolon** before the ssh command.

Ensure that the file *myHelloWorld* on the target will have execution rights, because otherwise *ssh* will fail.

- Click Apply

- Click OK

- Select **Project** ➤ **Clean** from the menu bar

Confirm with OK

The project will be rebuilt.

Select the Console tab

If no errors occur while building the project, you will see the following output:

You have successfully created your first own project with the *Eclipse* IDE. You have configured the project to create an application for your target platform.

#### 2.2.1.3 Modifying the Demo Application

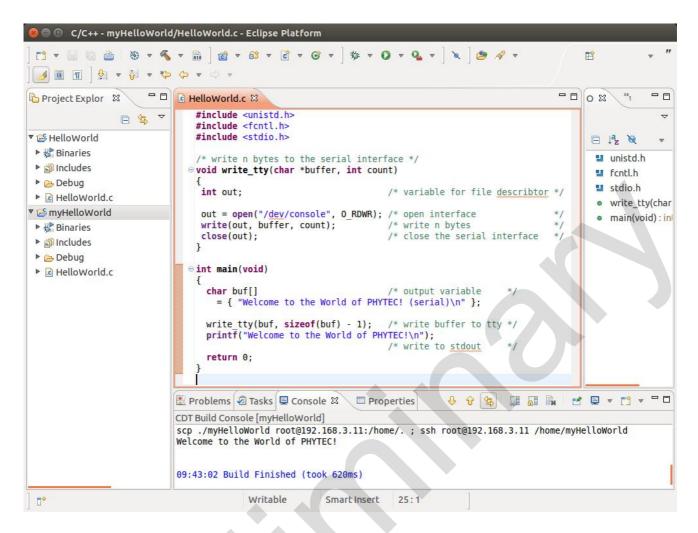

Now we will extend the *myHelloWorld* application. The extended *myHelloWorld* application will write an output to the first serial interface as well as to the standard output.

- Open Eclipse if it is not opened yet

- Double-click HelloWorld.c in the myHelloWorld project

- First include the following two additional header files: #include <unistd.h> #include <fcntl.h>

- Then add the function write\_tty(), which writes n bytes to the first serial interface (which, on the phyBOARD-Mira-i.MX 6, is connected to the system console /dev/console):

```

void write_tty (char *buffer, int count)

{

int out;

out = open ("/dev/console", O_RDWR);

write(out, buffer, count);

close(out);

}

```

Enter the following two lines in the main() function to declare the buffer and call the write\_tty() function:

```

char buf [] = { "Welcome to the World of PHYTEC! (serial)\n" };

write_tty(buf, sizeof (buf) - 1);

```

In the next screenshot you can see the complete program

Save your program after changing the code

The application will be compiled, built, copied to the target and executed.

• Click the *Microcom icon* on the desktop

- If you are not logged in, enter root and press Enter

- Type /home/myHelloWorld to start the application

- You will see the following output: Welcome to the World of PHYTEC! (serial) Welcome to the World of PHYTEC!

- Close Microcom

When you start the application via an SSH session, you only see one output line. When you execute the program with Microcom, you see two output lines.

The first line is a direct output on the serial interface. You can not see this line in an *SSH* session, because you are connected over a TCP/IP connection to the target. With *Microcom*, however, you have direct access to the serial interface, so you can also see the line that is written to the serial console.

In this section you have changed an existing application. You also learned how to access the serial interface. First you called the function open() on the device /dev/console. The return value of this function was a file descriptor. With the file descriptor you called the function write() to send n bytes to the device /dev/console. After that, the file descriptor was closed with the function close().

This procedure is quite typical for Linux, because Linux treats everything like a file.

### 2.2.1.4 Starting a Program out of Eclipse on the Target

In the following you will find another method to start an application out of Eclipse.

After compiling a project in *Eclipse*, the program is copied to the target and directly executed. A program can also be executed on the target without compiling a project. In the following section you will learn how to start a program on the target as an external tool.

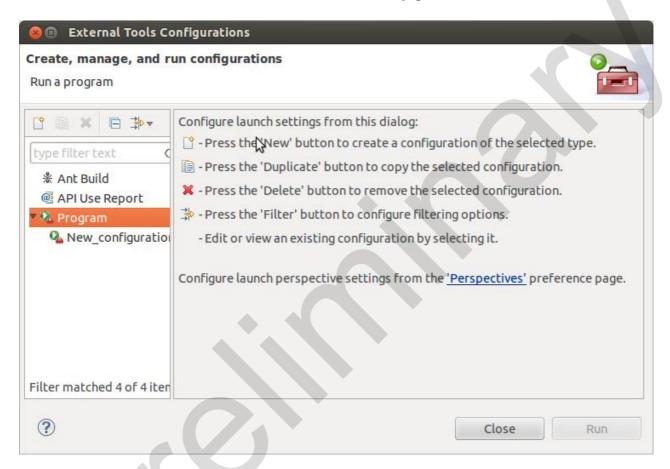

■ Select *Run* ▶ *External Tools* ▶ *External Tools Configurations* from the menu bar

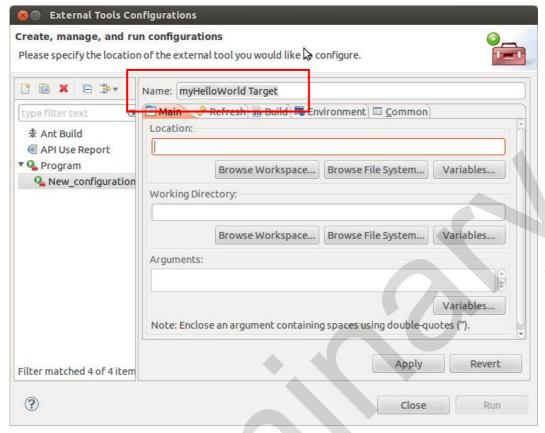

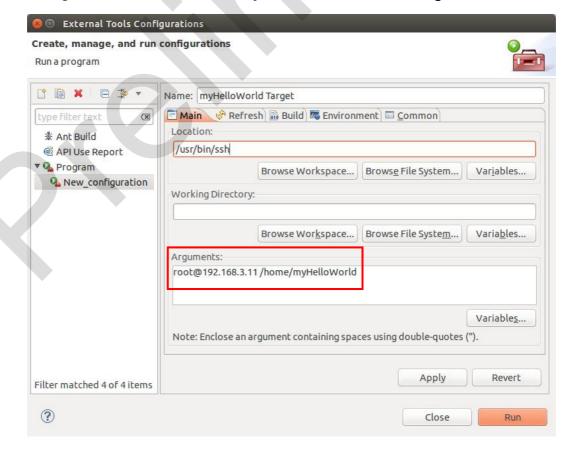

Double-Click Program and select New\_configuration

In the Name input field, enter: myHelloWorld Target

- Enter / usr/bin/ssh in the Location input field

- Enter root@192.168.3.11 /home/myHelloWorldinto the Arguments field

- Select Apply

- Select Run

Now the program is executed on the target and you will see the output Welcome to the World of PHYTEC! (serial) in the *Microcom* window.

If you want to execute the program the next time, you can use the *Run External Programs* button from the menu bar.

You have successfully created your own *Eclipse* project and you learned how to execute a program on the target.

# 2.2.2 Debugging an Example Project

In this chapter you will learn using the *GNU debugger GDB* on the host for remote debugging in conjunction with the *GDB* server on the target. *GDB* is the symbolic debugger of the *GNU* project and is arguably the most important debugging tool for any Linux system.

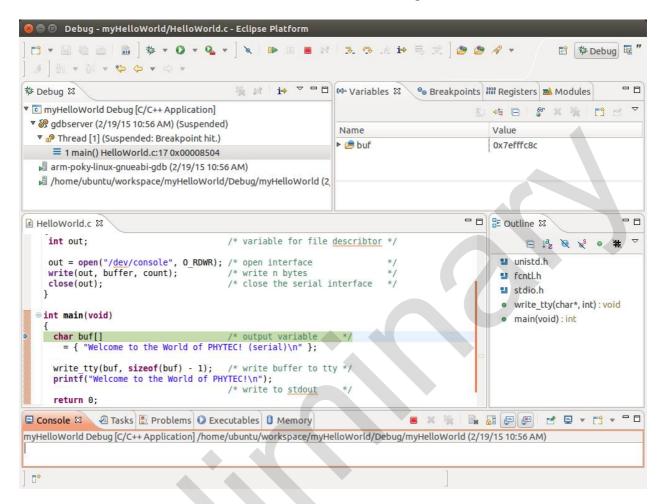

First you will start the *GDB* server on the target. Then you will configure the *Eclipse* platform and start the *GNU* debugger out of *Eclipse* using the *Debug* view.

The *CDT* extends the standard *Eclipse Debug* view with functions for debugging *C/C++* code. The *Debug* view allows you to manage the debugging and running of a program in the workbench. Using the *Debug* view you will be able to set breakpoints/watchpoints in the code and trace variables and registers. The *Debug* view displays the stack frame for the threads of each target you are debugging. Each thread in your program appears as a node in the tree, and the *Debug* view displays the process for each target you are running.

The *GDB* client is running on the host and is used to control the *GDB* server on the target, which in turn controls the application running on the target. *GDB* client and *GDB* server can communicate over a TCP/IP network connection as well as via a serial interface. In this Application Guide we will only describe debugging via TCP/IP.

### 2.2.2.1 Starting the GDB Server on the Target

In this passage you will learn how to start the *GDB* server on the target. The *GDB* server will be used to start and control the *myHelloWorld* program.

To debug a program with *GDB*, the program needs extended debugging symbols. These have already been added while building the program.

- Open Microcom

- Type root and press Enter

- Start the GDB server: gdbserver 192.168.3.11:10000 /home/myHelloWorld

You have started the *GDB* server on the target. The *GDB* server is now waiting for connections on TCP port 10000.

# 2.2.2.2 Configuring and starting the Debugger in Eclipse

In this passage you will learn how to configure your project settings to use *Eclipse* with the *GNU* debugger. After the configuration of your project settings, the *GNU* debugger will start and connect to the *GDB* server on the target.

- Start Eclipse if the application is not started yet

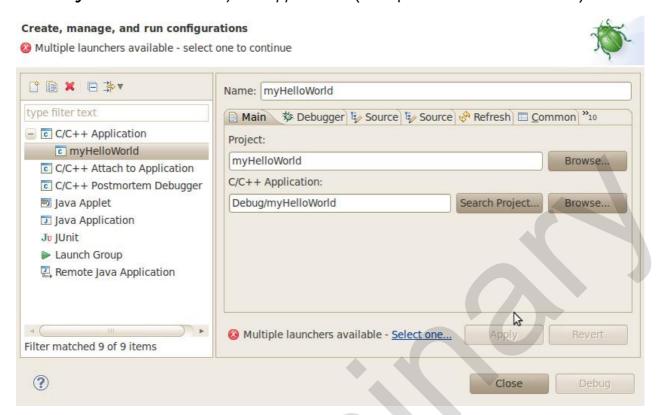

- Right-click on the myHelloWorld project in the Navigator window

- Select **Debug As** ► **Debug Configurations**

A dialog to create, manage and run applications appears.

• Select *myHelloWorld* under *C/C++ Application* (to expand it double click on it)

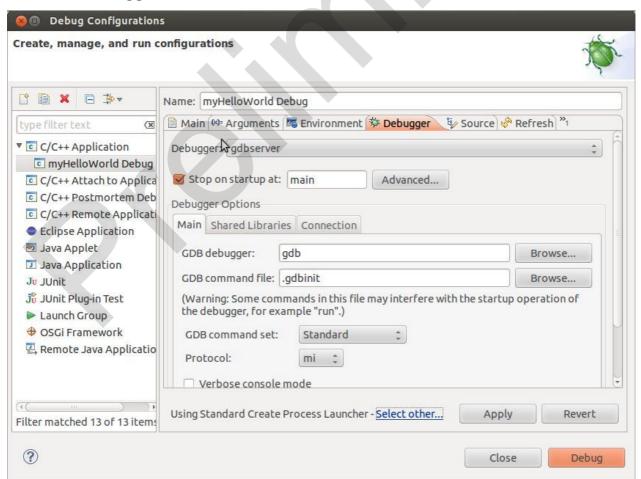

Select the **Debugger** tab

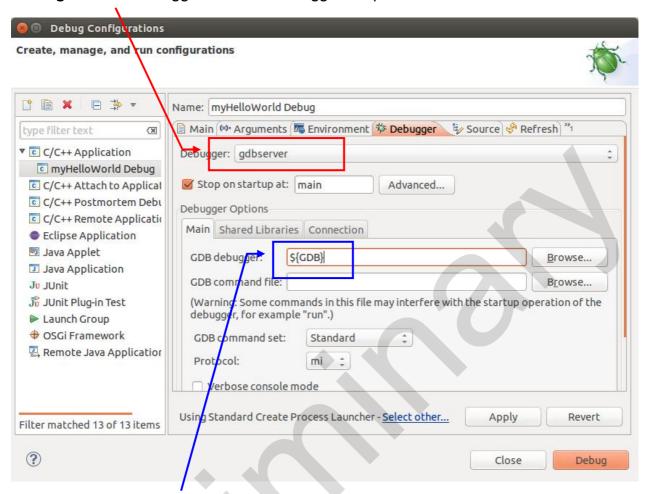

Select gdbserver Debugger from the Debugger drop-down box

- Enter \${GDB} in the GDB Debugger field

- Keep the GDB command file field empty

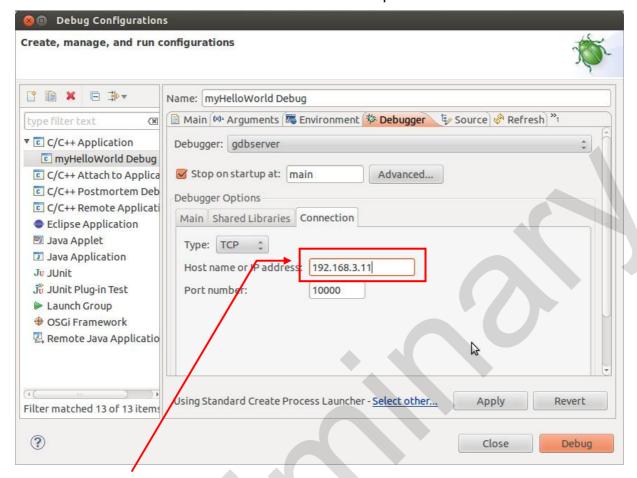

Select the Connection tab and select TCP in the drop-down box

Enter 192.168.3.11 (the target's IP address) in the Host name input field

The host's GDB will connect to this IP address to communicate with the target's GDB server.

- Click Apply

- Click **Debug**

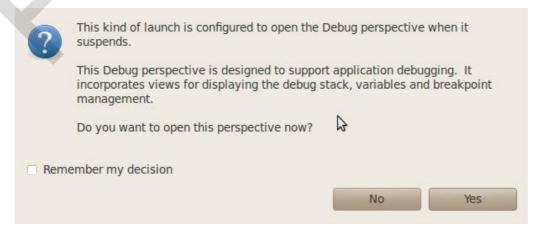

A new dialog appears.

Select Yes to switch to the Debug perspective

The debug perspective opens and the debugger stops automatically at the first line. The host's *GDB* is now connected to the *GDB* server on the target.

You have configured your project for remote debugging. You have started the *GNU* debugger in *Eclipse* and connected the host's *GDB* with the target's *GDB* server. You can now start to debug the project.

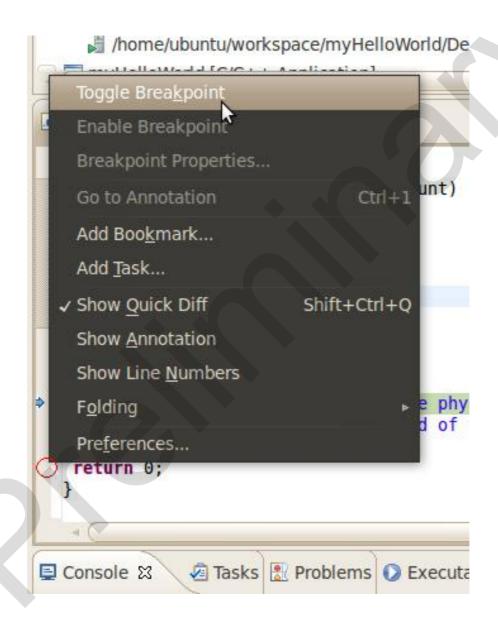

### 2.2.2.3 Setting a Breakpoint

Now you will set a breakpoint in your program. The breakpoint will be set on the last line of the function main(). If you resume the application, the debugger will stop on this line.

- Select the last line in main()

- Right-click into the small grey border on the left-hand side and select

Toggle Breakpoint to set a new breakpoint

## 2.2.2.4 Stepping through and Watching Variable Contents

In this part you will step through the example project with the debugger. You will also learn how to check the content of a variable.

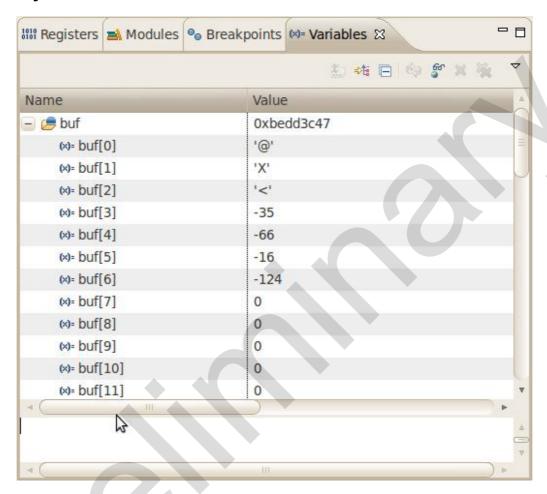

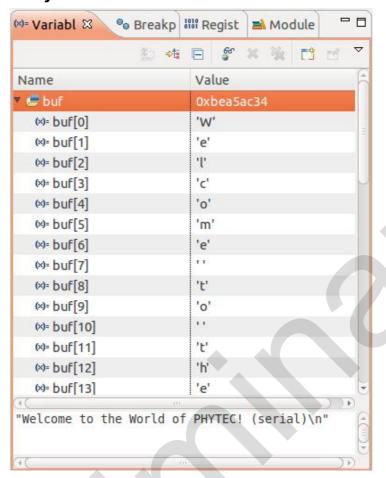

Expand buf in the Variables window

Click the Step Over button in the Debug window to step to the next line. You will see the

content of the buf variable in the Variables window

• Click on the variable **buf**

Then click the button Step into to enter the function write\_tty()

The debugger stops in write\_tty()

You will see the following variable window:

Click on the variable buffer

You will probably see a different address on the buffer pointer. Remember which address is shown in your case; you will need this address later.

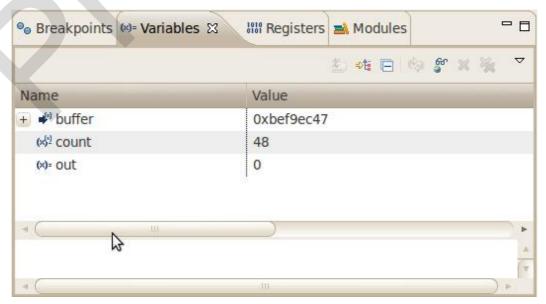

### 2.2.2.5 Stepping through and Changing Variable Contents

In this section you will change the value of a variable. At the end of this part you will see the effect of this change.

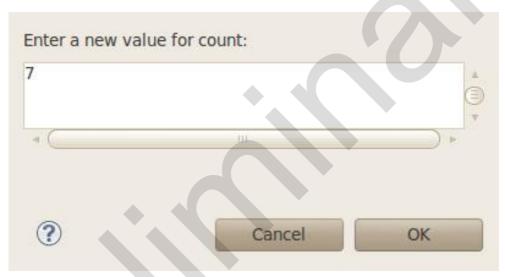

- Select the count variable in the Variables window

- Right-click on count and select Change Value

- Change the value of count to 7 and click OK

- Open Microcom if the application is not already opened

- Go back to Eclipse

- Click the Step Over button twice

Switch to Microcom

```

root@phyBOARD-WEGA-AM335x:~ gdbserver 192.168.3.11:10000 myHelloWorld Process myHelloWorld created; pid = 827

Listening on port 10000

Welcome to the World of PHYTEC! (serial)

Remote debugging from host 192.168.3.10

Welcome

```

Because we changed the *count* variable to 7 only the first seven characters (*Welcome*) are displayed in the *Microcom* console.

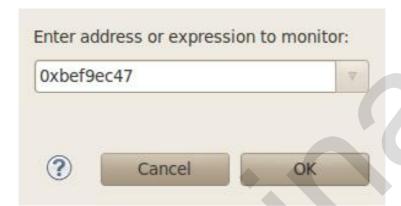

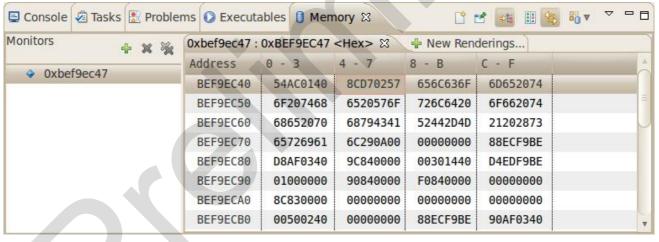

### 2.2.2.6 Using the Memory Monitor

In the last section of this chapter you will use the memory monitor to control the content at a memory address.

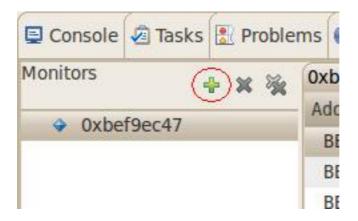

- Select the Memory tab in the frame where you can find the Console

- Click + Add Memory Monitor

- Enter the address of the buffer and click OK. Remember that the variable's address might be different on your system

Change the size of the window

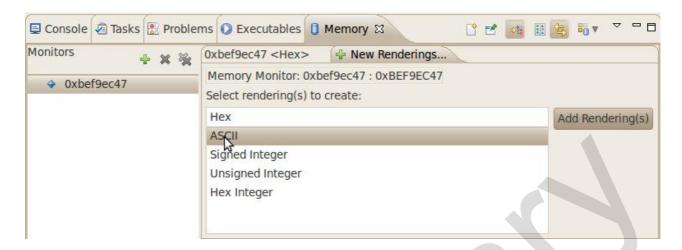

Click Add Rendering

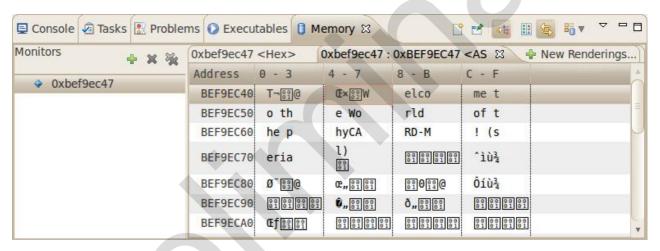

# Select ASCII and click Add Rendering(s)

You can see the contents of the variable *buffer* at address *0xbef9ec47* (or at the specific address used on your system).

Now click the Resume button from the menu bar

The debugger stops at the breakpoint in the last line of main().

```

out = open("/dev/console", 0_RDWR); /* open interface

write(out, buffer, count); /* write n bytes

close(out); /* close the serial interface */

}

int main(void)

{

char buf[] /* output variable */

= { "Welcome to the World of PHYTEC! (serial)\n" };

write_tty(buf, sizeof(buf) - 1); /* write buffer to tty */

printf("Welcome to the World of PHYTEC!\n");

/* write to stdout */

return 0;

}

```

Click the Resume button to end the application

You have successfully passed the debugging chapter. You are now able to configure and use *Eclipse* for remote debugging. You can step through a project, watch and change the content of variables, and you can use the memory monitor to view the content at a memory address.

# 3 Accessing the phyBOARD-Mira Features

PHYTEC phyBOARD-Mira is fully equipped with all mechanical and electrical components necessary for the speedy and secure start-up.

# 3.1 Overview of the phyBOARD-Mira Peripherals

The phyBOARD-Mira is depicted in *Figure 2*. It features many different interfaces and is equipped with the components as listed in *Table 2*, and *Table 3*. For a more detailed description of each peripheral refer to the appropriate chapter listed in the applicable table. *Figure 2* highlights the location of each peripheral for easy identification.

#### 3.1.1 Connectors and Pin Header

Table 2 lists all available connectors on the phyBOARD-Mira. Figure 2 highlights the location of each connector for easy identification.

| Reference<br>Designator | Description                                                                                     | See<br>Section |

|-------------------------|-------------------------------------------------------------------------------------------------|----------------|

| X2                      | Power supply 5 V only (via 6-pole WAGO male header, or 2-pole PHOENIX MINI COMBICON base strip) | 3.2.1.1        |

| Х3                      | CAN connector (2×5 pin header 2.54 mm pitch)                                                    | 3.2.5          |

| X4                      | Ethernet O connector (RJ45 with speed and link LED)                                             | 0              |

| X5                      | USB On-The-Go connector (USB Micro-AB)                                                          | 3.2.4          |

| X6                      | USB Host connector (USB 2.0 Standard-A)                                                         | 3.2.4          |

| X7                      | PCI Express connector (Mini PCI Express)                                                        | 3.2.7          |

| X8                      | Display backlight and control connector (5-pole Molex)                                          | 3.2.11         |

| X9                      | Display LVDS connector(20 pin FCC connector 1 mm pitch)                                         | 0              |

| X10                     | Camera phyCAM-S connector (8-pole Hirose Board-to-Wire Connector 1.25 mm pitch)                 | 0              |

| X13                     | A/V connector #1 (2×8 dual entry connector 2 mm pitch)                                          | 3.2.16         |

| X14                     | A/V connector #2 (2×20 dual entry connector 2 mm pitch)                                         | 3.2.16         |

| X17                     | Expansion connector (2×30 socket connector 2 mm pitch)                                          | 3.2.17         |

| X21                     | Touch connector (1x4 pin header 2.54 mm pitch)                                                  | 3.2.12         |

| X22                     | Secure Digital / Multi Media Card (Micro-slot)                                                  | 3.2.6          |

| X23                     | RS-232 with RTS and CTS, or RS-485 (UART3 2×5 pin header 2.54 mm pitch)                         | 3.2.2          |

| X28                     | HDMI connector (Typ-A)                                                                          | 3.2.9          |

| JP3                     | Backup voltage connector (1x2 pin header 2.54 mm pitch)                                         | 3.2.1.3        |

Table 2: phyBOARD-Mira Connectors and Pin Headers

Ensure that all module connections are not to exceed their expressed maximum voltage or current. Maximum signal input values are indicated in the corresponding controller User's Manual/Data Sheets. As damage from improper connections varies according to use and application, it is the user's responsibility to take appropriate safety measures to ensure that the module connections are protected from overloading through connected peripherals.

#### 3.1.2 LEDs

The phyBOARD-Mira is populated with three LEDs to indicate the status of the USB VBUS voltages, as well as of the power supply voltage. The fourth LED is a user programmable RGB-LED.

Figure 2 shows the location of the LEDs. Their function is listed in the table below:

| LED | Color | Description                                          | See<br>Section |

|-----|-------|------------------------------------------------------|----------------|

| D2  | red   | 3.3 V voltage generation of the phyBOARD-Mira        | 3.2.1.2        |

| D6  | RGB   | User programmable RGB-LED                            | 0              |

| D13 | green | Indicates presence of VBUS at the USB Host interface | 3.2.4          |

| D14 | green | Indicates presence of VBUS at the USB OTG interface  | 3.2.4          |

Table 3: phyBOARD-Mira LEDs Descriptions

#### 3.1.3 Switches

The phyBOARD-Mira is populated with two switches, one to reset the phyBOARD-Mira and another to configure the boot sequence.

Figure 2 shows the location of the switches. Their function is listed in the table below:

| Switch | Description  | See<br>Section |

|--------|--------------|----------------|

| S1     | Reset Button | 3.2.15         |

| S2     | Boot Switch  | 0              |

Table 4: phyBOARD-Mira Switches Description

Detailed descriptions of the assembled connectors, jumpers and switches can be found in the following chapters.

# 3.2 Functional Components on the phyBOARD-Mira SBC

This section describes the functional components of the phyBOARD-Mira. Each subsection details a particular connector/interface and associated jumpers for configuring that interface.

### 3.2.1 Power Supply

Do not change modules or jumper settings while the phyBOARD-Mira is supplied with power!

## 3.2.1.1 Power Connectors (X2)

The phyBOARD-Mira is available with two different power supply connectors. Depending on your order you will find one of the following connectors on your SBC:

- 1. a 2-pole PHOENIX MINI COMBICON base strip 3.5 mm connector (X2) suitable for a single 5 V supply voltage, or

- 2. a 6-pole WAGO male header (X2) to attach the Power Module for phyBOARDs (PEB-POW-01) which provides connectivity for 12 V 24 V

The required current load capacity for all power supply solutions depends on the specific configuration of the phyCORE mounted on the phyBOARD-Mira, the particular interfaces enabled while executing software, as well as whether an optional expansion board is connected to the carrier board. A 5 V adapter with a minimum supply of 1.5 A is recommended.

PHOENIX base strip

JP3

WAGO male header 6-pole

Figure 4: Power Supply Connectors (X2)

### 3.2.1.1.1 PHOENIX 2-pole MINI COMBICON Base Strip (X2)

The permissible input voltage is +5 V DC if your SBC is equipped with a 2-pole PHOENIX MINI COMBICON base strip.

Figure 4 and the following table show the pin assignment.

| Pin | Signal   | Description       |  |  |

|-----|----------|-------------------|--|--|

| 1   | VCC5V_IN | +5 V power supply |  |  |

| 2   | GND      | Ground            |  |  |

Table 5: Pin Assignment of the 2-pole PHOENIX MINI COMBICON Base Strip at X2

## 3.2.1.1.2 WAGO 6-pole Male Header (X2)

If a WAGO 6-pole male header is mounted on your board (*Figure 2* and *Figure 4*) your board is prepared to connect to a phyBOARD Power Module (PEB-POW-01), or a custom power supply circuitry. The ordering number of the mating connector from WAGO is: EAN 4045454120610.

Use of the 6-pole connector has the following advantages:

- Higher and wider operate range of the input voltage

- External scaling potential to optimize the electrical output current, by use of customized Power Modules which match the requirements

- 5 V, 3.3 V and backlight power supply

Pin assignment of the 6 -pole WAGO connector:

| Pin | Signal        | Description                                            |

|-----|---------------|--------------------------------------------------------|

| 1   | VCC5V_IN      | +5 V power supply                                      |

| 2   | GND           | Ground                                                 |

| 3   | VCC3V3_PMOD   | +3.3 V power supply                                    |

| 4   | VCC_BL        | Backlight power supply (input voltage of power module) |

| 5   | PMOD_PWRGOOD  | Power good signal (connected to reset nRESET_IN)       |

| 6   | nPMOD_PWRFAIL | Power fail signal                                      |

Table 6: Pin Assignment of the 6-pole WAGO Connector at X2

A detailed description of the Power Module for phyBOARDs can be found in the Application Guide for phyBOARD Expansion Boards (L-793e).

#### 3.2.1.2 Power LED D2

The red LED D2 next to expansion connector X17 (*Figure 2*) indicates the presence of the 3.3 V supply voltage generated from the 5 V input voltage.

#### 3.2.1.3 **VBAT, RTC and JP3**

The phyBOARD-Mira features an external RTC at U12 (*Figure 2*) in addition to the RTC of the Power Management IC mounted on the phyCORE-i.MX 6 module. It is used for real-time or time-driven applications. To backup the RTC a Gold cap (C90) (*Figure 2*) is placed on the phyBOARD-Mira. Alternatively the 2-pole pin header JP3 can be used to connect an external battery (3.3 V) to VBAT to feed in the backup voltage.

Figure 4 and the following table show the pin assignment of JP3.

| Pin | Signal | Description            |

|-----|--------|------------------------|

| 1   | VBAT   | Backup Battery voltage |

| 2   | GND    | Ground                 |

Table 7: Pinout of the 2-pole pin header JP3

The backup voltage source (either Gold cap at C90, or external battery via JP3) supplies the external RTC at U12 and connects to the backup voltage pin VBAT (A5) of the phyCORE-i.MX 6 supplying some critical registers and the RTC of the Power Management IC when the primary system power, VCC5V, is removed. The backup supply lasts approximately 17 ½ days.

## 3.2.2 UART Connectivity (X17 and X23)

The i.MX 6 SOM supports up to 5 so called UART units. On the phyBOARD-Mira TTL level signals of UART1 and UART2 (the standard console) are routed to expansion connector X17. UART3 is available at pin header connector X23 at RS-232 level, or optionally at RS-485 level.

The Evaluation Board (PEB-EVAL-01) delivered with the kit plugs into the expansion connector and allows easy use of the standard console (UART2) which is required for debugging. Please find additional information on the Evaluation Board in Application Guide for phyBOARD Expansion Boards (L-793e).

Further information on the expansion connector can be found in section 4.5.7.

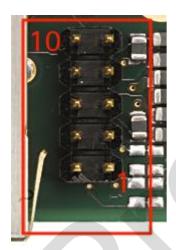

Pin header connector X23 is located next to the Ethernet connector (*Figure 5*) and provides the UART3 signals of the i.MX 6 at RS-232, or RS-485 level. The serial interface is intended to be used as data terminal equipment (DTE) and allows for a 5-wire connection including the signals RTS and CTS for hardware flow control. *Table 8* shows the signal mapping of the RS-232 and RS-485 level signals at connector X23.

Figure 5: RS-232 or RS-485 Interface Connector X23

| Pin | Signal            | Pin | Signal            |

|-----|-------------------|-----|-------------------|

| 10  | NC                | 9   | GND               |

| 8   | X_UART3_RS485_B   | 7   | X_UART3_RS485_A   |

| 6   | X_UART3_CTS_RS232 | 5   | X_UART3_TXD_RS232 |

| 4   | X_UART3_RTS_RS232 | 3   | X_UART3_RXD_RS232 |

| 2   | NC                | 1   | NC                |

Table 8: Pin Assignment of RS-232 / RS-485 Interface Connector X23

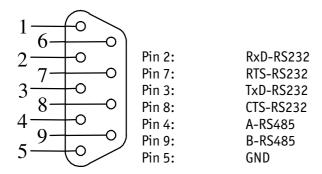

An adapter cable is included in the phyBOARD-Mira-i.MX 6 Kit to facilitate the use of the UART3 interface. The following figure shows the signal mapping of the adapter.

Figure 6: RS-232 / RS-485 Connector Signal Mapping

### 3.2.2.1 Software Implementation

Only /dev/ttymxc1 for UART2 and /dev/ttymxc2 for UART3 have been implemented within the BSP.

The standard console UART2 is accessible as /dev/ttymxc1 and is mainly used for debugging and control of software updates.

UART1 can be accessed as /dev/ttymxc2. It is intended for user applications.

## 3.2.3 Ethernet Connectivity (X4)

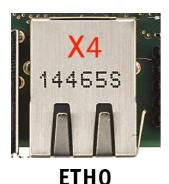

The Ethernet 0 interface of the phyBOARD-Mira is accessible at the RJ45 connector X4.

Figure 7: Ethernet Interface at Connectors X4

The standard phyBOARD-Mira is equipped with an RJ45 connector supporting a 10/100Base-T network connection. Optionally, it can be ordered with the phyCORE-i.MX 6 module configured for also 1000 Mbps Ethernet and a different RJ45 connector allowing to use the phyBOARD-Mira in a 10/100/1000Base-T network<sup>1</sup>. The LEDs for LINK (green) and SPEED (yellow) indication are integrated in the connector. The Ethernet transceiver supports Auto MDI-X, eliminating the need for the consideration of a direct connect LAN cable, or a cross-over path cable. They detect the TX and RX pins of the connected device and automatically configure the PHY TX and RX pins accordingly.

# 3.2.3.1 Software Implementation