# **TRN Module Summary Description**

### 1 Introduction

This document provides the module description for the following module.

- (1) Module Name: TRN module

- (2) Module Number: HNS0531

- (3) Unit and application to be used

LPRM/APRM, LPRM, FLOW, SRNM Units for BWR-2, 3, 4, 5 and 6 Application OPRM, LPRM, APRM, SRNM, DTF-RPS, DTF-MSIV, DTF-MSIV-S, TLF-RPS, TLF-MSIV, SPTM, SPTM-S Units for ABWR Application

(4) Number of FPGA on the module: Six

## 2 Functional Summary

The TRN module has two data processing trains that collect data from other modules mounted in the same unit, generate a data frame in a fixed format by multiplexing the collected data, and transmit the data frame to external over fiber optic links and to other modules in the same unit. When installed in the LPRM/APRM unit, the TRN module receives the data frame from the APRM module in the same unit, and transmits the data frame over fiber optic links instead of the data frame generated in the TRN module.

## 3 Module Description

### 3.1 Module Front Panel

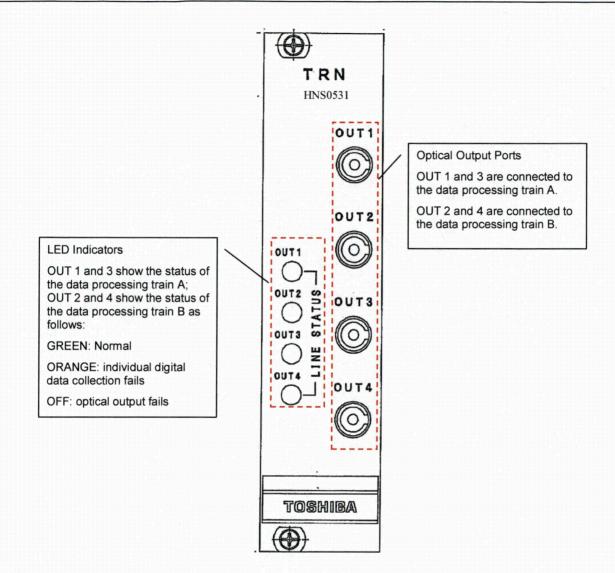

Figure 1 shows the front panel of the TRN module.

### 3.2 Inputs and Outputs

The TRN module has the following inputs and outputs.

#### 3.2.1 Inputs

(1) Input signals via process input and output modules

N/A

(2) Input signals via communication modules

N/A

(3) Others to be noted

The TRN module has two data processing trains A and B receiving the same inputs data through point-to-point serial communication links in the backplane. The TRN module has the following two data collecting functions:

(a) Collect individual digital data from modules. Up to 16 digital data are collected. The digital data typically come from modules equipped with an analog-to-digital converter, such as the LPRM or SQ-ROOT module.

(b) Receive data frames from a module transmitting more than one data, such as the APRM module. The data frame is in a fixed data format, multiplexing 46 data items of 16 bits long.

#### 3.2.2 Outputs

(1) Output signals via process input and output modules

N/A

#### (2) Outputs via communication modules

Each data processing train transmits data frames containing collected data items through two identical optical transmitters. Note that the TRN module installs no hand shaking method with the receiver.

(3)Others to be noted

Each data processing train transmits data frames containing the data collected using function (a) in Section 3.2.1 described above to other modules through the backplane.

Figure 1 The front panel of the TRN module

### 3.3 FPGA functions

Figure 2 shows Functional Block Diagram of the TRN module. Table 1 provides functions of each FPGA.

MEM-JHS-000105 Rev.1

### 3.4 Self Diagnosis

Watchdog timers in each data processing trains monitors operation of FPGAs. The TRN module shows the results of the monitoring on the front panel.

#### MEM-JHS-000105 Rev.1

|                                                                    | r           | 変更記録                                                                                                                                                                            | REVISIONS               | T                        | 1                       | 1                      |

|--------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|-------------------------|------------------------|

| 変更記号<br>REV.MARK<br>変更発行日<br>REV.ISSUED                            | ページ<br>PAGE | 変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS                                                                                                                                         | 承認<br>APPROVED<br>BY    | 調査<br>REVIEWED<br>BY     | 担当<br>PREPARED<br>BY    | 保 管<br>REGISTEREI      |

| 0<br>Feb.13. 2013                                                  |             | First Issue                                                                                                                                                                     | K.Wakita<br>Feb.13,2013 | T.Tarumi<br>Feb.13,2013  | H.Ito<br>Feb.13,2013    | H.Ito<br>Feb.13,2013   |

| (1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | 3           | Descriptions on communication were improved.<br>Figure number was changed from 3-1 to 1.<br>Figure number was changed from 3-2 to 2.<br>Table number was changed from 3-1 to 1. | K.Waluta<br>Robit.2013  | 7.7arumi<br>Feb. 15,2013 | 25. Ito<br>Feb.15. 2013 | X. Sto<br>Feb. 15.2013 |

|                                                                    |             |                                                                                                                                                                                 |                         |                          |                         |                        |

|                                                                    |             |                                                                                                                                                                                 |                         |                          |                         |                        |

|                                                                    |             |                                                                                                                                                                                 |                         |                          |                         |                        |

|                                                                    |             |                                                                                                                                                                                 |                         |                          |                         |                        |

|                                                                    |             |                                                                                                                                                                                 |                         |                          |                         |                        |

|                                                                    |             |                                                                                                                                                                                 |                         |                          |                         |                        |

|                                                                    |             |                                                                                                                                                                                 |                         |                          |                         |                        |

|                                                                    |             |                                                                                                                                                                                 |                         |                          |                         |                        |

# RCV Module Summary Description

### 1 Introduction

This document provides the module description for the following module.

- (1) Module Name: RCV module

- (2) Module Number: HNS0541

- (3) Unit and application to be usedLPRM, LPRM/APRM Unit for BWR-2, 3, 4, 5 and 6 Application

OPRM, LPRM, APRM, DTF-RPS, DTF-MSIV, TLF-RPS, TLF-MSIV, SPTM for ABWR Application

(4) Number of FPGA on the module: Eight

## 2 Functional Summary

The RCV module has four independent data processing trains that receive optical signals containing a fixed format data frame from external, and transmits the data frame to other modules mounted in the same unit through point-to-point serial communication links.

## 3 Module Description

### 3.1 Module Front Panel

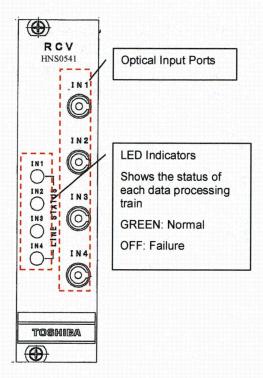

Figure 1 shows the front panel of the RCV module.

### 3.2 Inputs and Outputs

The RCV module has the following inputs and outputs.

#### 3.2.1 Inputs

(1) Input signals via process input and output modules

#### N/A

(2) Input signals via communication modules

Four optical input ports.

#### 3.2.2 Outputs

(1) Output signals via process input and output modules

#### N/A

(2) Outputs via communication modules

N/A

#### (3) Others to be noted

Each data processing train transmits the data frame to other modules mounted in the same unit through point-to-point serial communication links in the backplane.

Figure 1 The front panel of the RCV module

#### 3.3 FPGA functions

Figure 2 shows Functional Block Diagram of the RCV module. Table 1 provides functions of each FPGA.

MEM-JHS-000107 Rev.1

a,c

### Figure 2 Functional Block Diagram of RCV module

#### Table 1 FPGA functions in the RCV module

|             | 変 更 記 録                                                                                                                                                                                                                        | REVISIONS                                                                                                                                                                                                                                                     | 1                                                                                                                                                      |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ページ<br>PAGE | 変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS                                                                                                                                                                                        | 承認<br>APPROVED<br>BY                                                                                                                                                                                                                                          | 調 査<br>REVIEWED<br>BY                                                                                                                                  | 担当<br>PREPARED<br>BY                                                                                                                           | 保 管<br>REGISTEREI                                                                                                                                                                                                                                                                                                                                                                                                       |

| -           | First Issue                                                                                                                                                                                                                    | K.Wakita<br>Feb.13,2013                                                                                                                                                                                                                                       | T.Tarumi<br>Feb.13,2013                                                                                                                                | H.Ito<br>Feb.13,2013                                                                                                                           | H.lto<br>Feb.13,2013                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1<br>2<br>3 | Descriptions on communication were improved.<br>Figure number was changed from 3-1 to 1.<br>Figure number was changed from 3-2 to 2.<br>Table number was changed from 3-1 to 1.<br>Description on self diagnosis was improved. | K. Wakila<br>Feblt. 2013                                                                                                                                                                                                                                      | 7. Tarumi<br>Feb,15,2013                                                                                                                               | 78. Uto<br>Feb. 15. 2013                                                                                                                       | N. Ito<br>Feb. 15. 2-13                                                                                                                                                                                                                                                                                                                                                                                                 |

|             |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             | PAGE<br>                                                                                                                                                                                                                       | ページ<br>PAGE 変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS<br>- First Issue<br>1 Descriptions on communication were improved.<br>Figure number was changed from 3-1 to 1.<br>2 Figure number was changed from 3-1 to 1.<br>2 Table number was changed from 3-1 to 1. | ページ<br>PAGE 変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS APPROVED<br>BY<br>- First Issue<br>- First Issue<br>1 Descriptions on communication were improved. | ページ<br>PAGE 変更箇所・変更內容<br>CHANGED PLACE AND CONTENTS 承認 調査<br>APPROVED REVIEWED<br>BY BY<br>- First Issue<br>- K.Wakita T.Tarumi<br>Feb.13,2013 | ページ<br>PAGE     変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS     承認調査<br>APPROVED<br>BY     担当       -     First Issue     REVIEWED<br>BY     PREPARED<br>BY       -     First Issue     K.Wakita     T.Tarumi       1     Descriptions on communication were improved.<br>Figure number was changed from 3-1 to 1.     K.Wakita     7.Tarumi       2     Figure number was changed from 3-1 to 1.     K.Uokita     7.Tarumi |

## LVPS Module Summary Description

### 1 Introduction

This document provides the module description for the following module.

- (1) Module Name: LVPS module

- (2) Module Number: HNS500

- (3) Unit and application to be used

LPRM/APRM, LPRM, FLOW, OPRM, SRNM Units for BWR-2, 3, 4, 5 and 6 Application LPRM, APRM, OPRM, SRNM, DTF-RPS, DTF-MSIV, DTF-MSIV-S, TLF-RPS, TLF-MSIV, SPTM, SPTM-S Units for ABWR Application

(4) Number of FPGA on the module: None

### 2 Functional Summary

The LVPS module is a plug-in type direct current (DC) power supply mounted in a unit and supplies DC power to other modules in the same unit through the backplane. Toshiba FPGA-based unit mount two redundant LVPSs, and either alone provide sufficient power to operate the unit. The LVPS module monitors the output voltage inside the power supply, and generates an alarm signal in case of failure.

### 3 Module Description

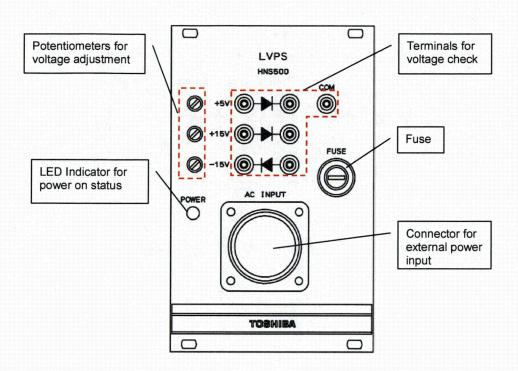

#### 3.1 Module Front Panel

Figure 1 shows the front panel of the LVPS module.

#### 3.2 Inputs and Outputs

The LVPS module has the following inputs and outputs.

#### 3.2.1 Inputs

N/A

#### 3.2.2 Outputs

The LVPS module provides a discrete alarm signal to the module which has a function of status indicator in the same unit through the backplane.

Figure 1 The front panel of the LVPS module

|                                         | r           | 変更記録                                                                               | REVISIONS              | -                      | T                      |                       |

|-----------------------------------------|-------------|------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|-----------------------|

| 変更記号<br>EEV.MARK<br>変更発行日<br>REV.ISSUED | ページ<br>PAGE | 変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS                                            | 承認<br>APPROVED<br>BY   | 調査<br>REVIEWED<br>BY   | 担当<br>PREPARED<br>BY   | 保 管<br>REGISTERE      |

| 0<br>Feb.8. 2013                        | -           | First Issue                                                                        | K.Wakita<br>Feb.8,2013 | T.Tarumi<br>Feb.8,2013 | H.lto<br>Feb.8,2013    | H.Ito<br>Feb.8,2013   |

| (1)<br>14. 15.2013                      | 1           | Improve description in Section 2 and 3.<br>Figure number was changed from 3-1 to 1 | K.Wakita<br>Robić.2013 | 7.7<br>Feb.15,2013     | N eltr<br>Feb 15, 2013 | W.sltv<br>Feb. 15-201 |

|                                         |             |                                                                                    |                        |                        |                        |                       |

|                                         |             |                                                                                    |                        |                        |                        |                       |

|                                         |             |                                                                                    |                        |                        |                        |                       |

|                                         |             |                                                                                    |                        |                        |                        |                       |

|                                         |             |                                                                                    |                        |                        |                        |                       |

|                                         |             |                                                                                    |                        |                        |                        |                       |

|                                         |             |                                                                                    |                        |                        |                        |                       |

# **AO Module Summary Description**

## 1 Introduction

This document provides the module description for the following module.

- (1) Module Name: AO module

- (2) Module Numbers: HNS515, HNS516, HNS517, HNS518

- (3) Unit and application to be used

LPRM/APRM, LPRM, FLOW, SRNM Units for BWR-2, 3, 4, 5 and 6 Application

LPRM, APRM, SRNM, SPTM Units for ABWR Application

(4) Number of FPGA on the module: None

## 2 Functional Summary

The AO module provides sixteen 12-bit analog outputs to external equipment. The AO module receives individual digital values from other modules in the same unit through point-to-point copper serial communication links on the backplane. The AO module converts each output's digital data into an analog output value. The model number specifies the output signal voltage range for all of the digital-to-analog converters.

## 3 Module Description

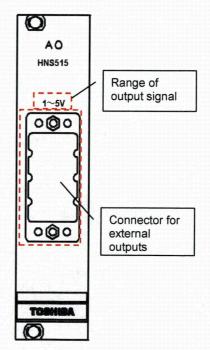

### 3.1 Module Front Panel

Figure 1 shows the front panel of the AO module.

### 3.2 Inputs and Outputs

The AO module has the following inputs and outputs.

#### 3.2.1 Inputs

Sixteen serial digital data values, over sixteen individual copper communication paths.

#### 3.2.2 Outputs

Sixteen single ended analog voltage output ports of the following voltage ranges. An isolated DC/DC converter provides power to the output ports.

HNS515: 1 to 5 V HNS516: 0 to 1 V HNS517: 0 to 5 V HNS518: 0 to 160 mV

Figure 1 The front panel of the AO module (HNS515)

|                                         | r           | 変更記録                                                                                      | REVISIONS                 | }                         | r                      | r                       |

|-----------------------------------------|-------------|-------------------------------------------------------------------------------------------|---------------------------|---------------------------|------------------------|-------------------------|

| 変更記号<br>REV.MARK<br>変更発行目<br>REV.ISSUED | ベージ<br>PAGE | 変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS                                                   | 承認<br>APPROVED<br>BY      | 調 査<br>REVIEWED<br>BY     | 担当<br>PREPARED<br>BY   | 保 管<br>REGISTERE        |

| 0<br>Feb.8, 2013                        | -           | First Issue                                                                               | K.Wakita<br>Feb.8,2013    | T.Tarumi<br>Feb.8,2013    | H.lto<br>Feb.8,2013    | H.Ito<br>Feb.8,2013     |

| (1)<br>12 (5, 2013                      | I           | Descriptions in Section 2 and 3 were improved.<br>Added information on the communication. | K.Walcila<br>Robits. 2013 | 7. Turumi<br>Feb. 15,2013 | H. Sta<br>Feb 15. 2013 | ) f. Ito<br>Feb. 15.201 |

|                                         |             |                                                                                           |                           |                           |                        |                         |

|                                         |             |                                                                                           |                           |                           |                        |                         |

|                                         |             |                                                                                           |                           |                           |                        |                         |

|                                         |             |                                                                                           |                           |                           |                        |                         |

|                                         |             |                                                                                           |                           |                           |                        |                         |

|                                         |             |                                                                                           |                           |                           |                        |                         |

|                                         |             |                                                                                           |                           |                           |                        |                         |

2E

# **DIO Module Summary Description**

## 1 Introduction

This document provides the module description for the following module.

- (1) Module Name: DIO module

- (2) Module Number: HNS520

- (3) Unit and application to be used LPRM/APRM, LPRM, FLOW, SRNM Units for BWR-2, 3, 4, 5 and 6 Application LPRM, APRM, OPRM, SRNM Units for ABWR Application

- (4) Number of FPGA on the module: None

# 2 Functional Summary

The DIO module provides for sampling four discrete inputs from external equipment, and 16 discrete outputs to external equipment. The received signals are sent to other modules in the same unit. The output signals are provided from other modules in the same unit. The inputs and outputs are provided to the DIO module through the backplane (which Toshiba refers to as a middle plane) on copper point-to-point discrete wiring.

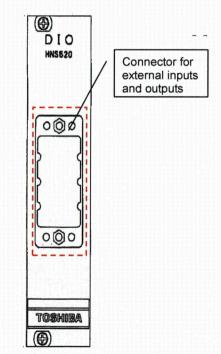

# 3 Module Description

### 3.1 Module Front Panel

Figure 1 shows the front panel of the DIO module.

### 3.2 Inputs and Outputs

The DIO module has the following inputs and outputs.

#### 3.2.1 Inputs

Four discrete 24 VDC input points. All signals share a common ground. The external voltage source is isolated from the backplane through photo couplers.

### 3.2.2 Outputs

Sixteen discrete contact output points. The sixteen points are grouped in four. Output points in each group share a common ground. Each output point is isolated from the backplane through a photo coupler.

Figure 1 The front panel of the DIO module

|                                         |             | 変更記録                                                                                      | REVISIONS              |                           |                        |                        |

|-----------------------------------------|-------------|-------------------------------------------------------------------------------------------|------------------------|---------------------------|------------------------|------------------------|

| 変更記号<br>REV.MARK<br>変更発行日<br>REV.ISSUED | ベージ<br>PAGE | 変更箇所 · 変更内容<br>CHANGED PLACE AND CONTENTS                                                 | 承認<br>APPROVED<br>BY   | 調査<br>REVIEWED<br>BY      | 担当<br>PREPARED<br>BY   | 保管<br>REGISTEREE       |

| 0<br>Feb.5. 2013                        | -           | First Issue                                                                               | K.Wakita<br>Feb.5,2013 | T.Tarumi<br>Feb.5,2013    | H.Jto<br>Feb.5,2013    | H.Ito<br>Feb.5,2013    |

| (1)<br>28, 15,243                       | I           | Descriptions in Section 2 and 3 were improved<br>Figure number was changed from 3-1 to 1. | K.Wakta<br>Feb 15.20B  | 7. Гагиті<br>Feb. 15.2013 | N. elto<br>Feb. 15.20B | 20. Ita<br>Feb. 15. 20 |

|                                         |             |                                                                                           |                        |                           | •                      |                        |

|                                         |             |                                                                                           |                        |                           |                        |                        |

|                                         |             |                                                                                           |                        |                           |                        |                        |

|                                         |             |                                                                                           |                        |                           |                        |                        |

|                                         |             |                                                                                           |                        |                           |                        |                        |

|                                         |             |                                                                                           |                        |                           |                        |                        |

|                                         |             |                                                                                           |                        |                           |                        |                        |

|                                         |             |                                                                                           |                        |                           |                        |                        |

# **BLANK Module Summary Description**

## 1 Introduction

This document provides the module description for the following module.

- (1) Module Name: BLANK module

- (2) Module Number: HNS490

- (3) Unit and application to be usedLPRM/APRM, LPRM Units for BWR-2, 3, 4, 5 and 6 Application

- (4) Number of FPGA on the module: None

# 2 Functional Summary

The BLANK module fills a unit slot instead of an LPRM module. The BLANK module bypasses alarm signal lines that take OR (logical disjunction) of each LPRM module alarm.

## 3 Module Description

### 3.1 Module Front Panel

Figure 1 shows the front panel of the BLANK module.

### 3.2 Inputs and Outputs

The BLANK module has the following inputs and outputs through the backplane.

### 3.2.1 Inputs

Three types of daisy chain signals (LPRM High, LPRM Downscale, LPRM inoperable) for alarm detection from one neighboring LPRM module.

### 3.2.2 Outputs

The BLANK module provides the three types of daisy chain signals to the other neighboring LPRM module. A DIO module accepts the signals at the end.

One dummy LPRM inoperable signal to the TRN module.

Figure 1 The front panel of the BLANK module

| 変更記号                |             | 変更記録                                    | REVISIONS                   | T                        |                           | 1                      |

|---------------------|-------------|-----------------------------------------|-----------------------------|--------------------------|---------------------------|------------------------|

| 変更発行日<br>REV.ISSUED | ページ<br>PAGE | 変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS | 承認<br>APPROVED<br>BY        | 調査<br>REVIEWED<br>BY     | 担当<br>PREPARED<br>BY      | 保管<br>REGISTERED       |

| 0<br>Feb.8. 2013    | ł           | First Issue                             | K.Wakita<br>Feb.8,2013      | T.Tarumi<br>Feb.8,2013   | H.lto<br>Feb.8,2013       | H.lto<br>Feb.8,2013    |

| 1)<br>Feb. 15-2413  | 1           | Figure number 3-1 was changed to 1.     | K. Walkitu<br>Fab. UT. 2013 | 7. Tarumi<br>Feb 15,2013 | N° el to<br>F2b. 15. 2013 | 24 dts<br>Fab 15. 2013 |

|                     |             |                                         |                             |                          |                           |                        |

|                     |             |                                         |                             |                          |                           |                        |

|                     |             |                                         |                             |                          |                           |                        |

|                     |             |                                         |                             |                          |                           |                        |

|                     | •           |                                         |                             |                          |                           |                        |

|                     |             |                                         |                             |                          |                           |                        |

|                     |             |                                         |                             |                          |                           |                        |

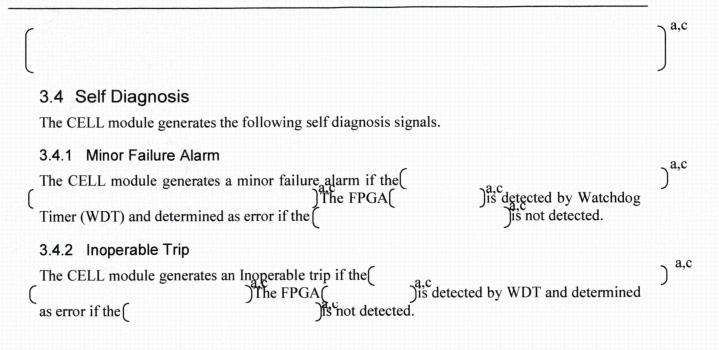

# CELL Module Summary Description

## 1 Introduction

This document provides the module description for the following module.

- (1) Module Name: CELL module

- (2) Module Number: HNS0400

- (3) Unit and application to be used OPRM Unit for ABWR Application

- (4) Number of FPGA on the module: Eleven

## 2 Functional Summary

The CELL module converts LPRM levels to normalized oscillation levels, and provides the data to AGRD and PBD module for trip determinations.

## 3 Module Description

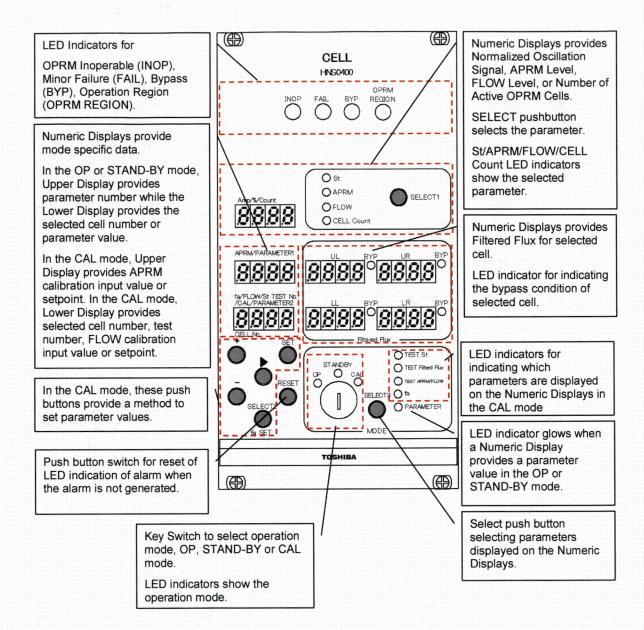

### 3.1 User Interfaces

Figure 1 shows the front panel of the CELL module.

### 3.2 Inputs and Outputs

The CELL module has the following inputs and outputs.

#### 3.2.1 Inputs

(1) Input signals via process input and output modules

N/A

(2) Input signals via communication modules

The CELL module uses the LPRM levels and status from individual LPRM modules. The TRN module in the LPRM unit that is not shown in the Figure 2 transmits the LPRM data to OPRM unit. The RCV module in the OPRM unit receives the LPRM data. The CELL module is responsible for receiving the LPRM data from the RCV module.

#### MEM-JHS-000121 Rev.1

Figure 1 The front panel of the CELL module

#### 3.2.2 Outputs

(1) Output signals via process input and output modules

N/A

(2) Output signals via communication modules

The CELL module provides the data including the discrete alarm signal to the DAT/ST module and DAT/ST module provides the data to external equipment via TRN module.

a,c

### 3.3 FPGA functions

Figure 2 shows Functional Block Diagram of the CELL module where each block is an FPGA. Table 1 provides functions of each FPGA.

Figure 2 Functional Block Diagram of CELL module

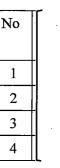

Table 1 FPGA functions in the CELL module

| FPGA               | Description |     |

|--------------------|-------------|-----|

|                    |             | ר ' |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

|                    |             |     |

| OSHIBA CORPORATION | 3/5         |     |

MEM-JHS-000121 Rev.1

|                                         |             | 変 更 記 錄                                 | REVISIONS                 | k                        |                          |                          |

|-----------------------------------------|-------------|-----------------------------------------|---------------------------|--------------------------|--------------------------|--------------------------|

| 変更記号<br>REV.MARK<br>変更発行日<br>REV.ISSUED | ページ<br>PAGE | 変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS | 承認<br>APPROVED<br>BY      | 調査<br>REVIEWED<br>BY     | 担当<br>PREPARED<br>BY     | 保管<br>REGISTERED         |

| 0<br>Feb 25,2013                        | -           | First Issue                             | K. Wakita<br>Feb 25,2013  | T. Tarumi<br>Feb 25,2013 | H. Ito<br>Feb 25,2013    | H. Ito<br>Feb 25,2013    |

| 1)<br>Har-11-2013                       | I           | Editorial error correction.             | K. Wakita<br>Mar 11, 2013 | 7. Tarami<br>Mar.11,2013 | 24. Itu<br>Har. 11. 2013 | N. Ito<br>Mos. 11 . 2013 |

|                                         |             |                                         |                           | 1744<br>1744 - 174       |                          |                          |

|                                         |             |                                         |                           |                          |                          |                          |

|                                         |             |                                         |                           |                          |                          |                          |

|                                         |             |                                         |                           |                          |                          |                          |

|                                         |             |                                         |                           |                          |                          |                          |

|                                         |             |                                         |                           |                          |                          |                          |

|                                         |             |                                         |                           |                          |                          |                          |

|                                         |             |                                         |                           |                          |                          |                          |

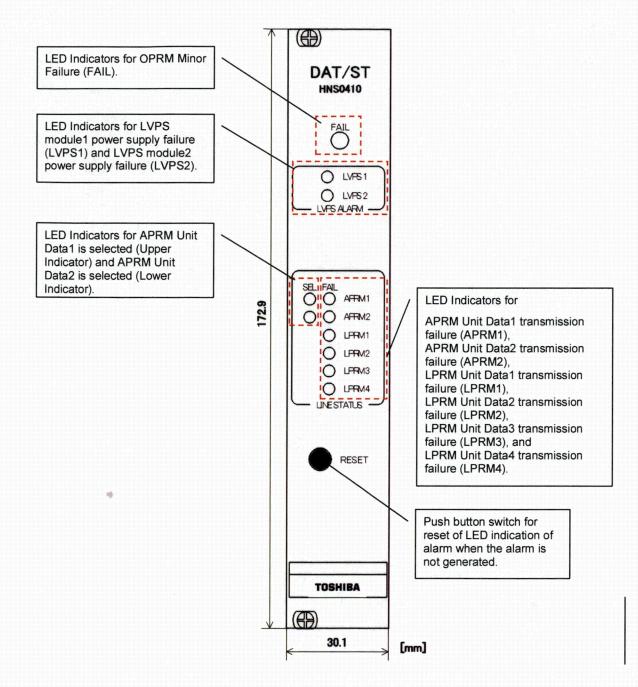

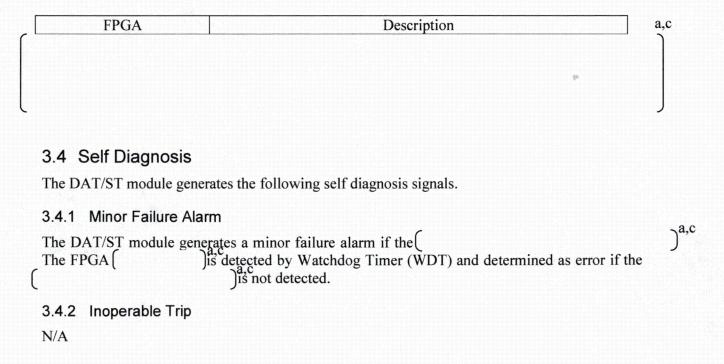

# DAT/ST Module Summary Description

### 1 Introduction

This document provides the module description for the following module.

- (1) Module Name: DAT/ST module

- (2) Module Number: HNS0410

- (3) Unit and application to be usedOPRM Unit for ABWR Application

- (4) Number of FPGA on the module: Two

## 2 Functional Summary

The DAT/ST module receives data from CELL module, AGRD module, PBD module and LVPS module, multiplexes these data, and outputs them to the TRN module.

The DAT/ST module also displays input and power status on the front panel.

## 3 Module Description

### 3.1 User Interfaces

Figure 1 shows the front panel of the DAT/ST module.

### 3.2 Inputs and Outputs

The DAT/ST module has the following inputs and outputs.

3.2.1 Inputs

(1) Input signals via process input and output modules

N/A

(2) Input signals via communication modules

N/A

(3) Others to be noted

The DAT/ST module receives data from CELL module, AGRD module, PBD module, and LVPS module on the same chassis.

MEM-JHS-000122 Rev.1

Figure 1 The front panel of the DAT/ST module

#### 3.2.2 Outputs

(1) Output signals via process input and output modules

N/A

(2) Output signals via communication modules

a,c

The DAT/ST module provides received data from CELL module, AGRD module, PBD module and LVPS module to external via TRN module.

#### 3.3 FPGA functions

Figure 2 shows Functional Block Diagram of the DAT/ST module where each block is an FPGA. Table 1 provides functions of each FPGA.

#### Figure 2 Functional Block Diagram of DAT/ST module

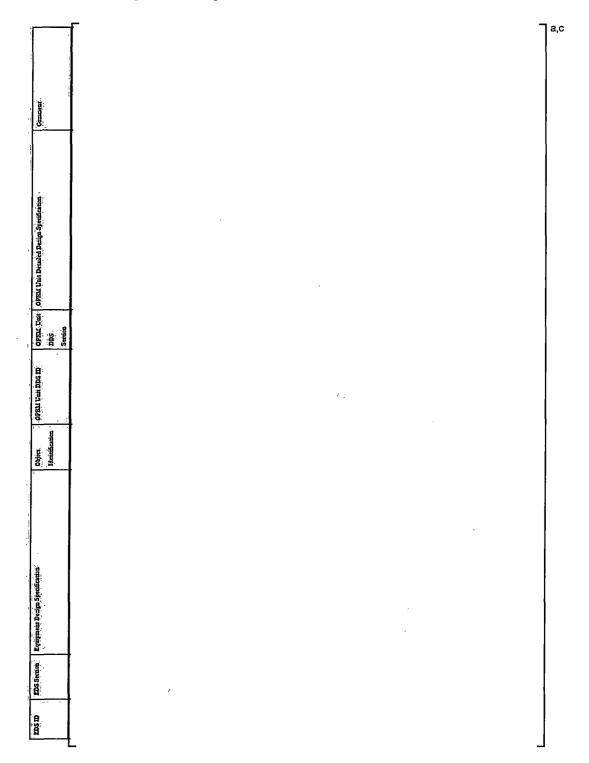

#### Table 1 FPGA functions in the DAT/ST module

| 変更配号<br>REV.MARK<br>変更発行日<br>REV.ISSUED | ページ<br>PAGE | 変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS | 承認<br>APPROVED<br>BY      | 調査<br>REVIEWED<br>BY      | 担当<br>PREPARED<br>BY      | 保管<br>REGISTERED      |

|-----------------------------------------|-------------|-----------------------------------------|---------------------------|---------------------------|---------------------------|-----------------------|

| 0<br>Feb 25,2013                        |             | First Issue                             | K. Wakita<br>Feb 25,2013  | T. Tarumi<br>Feb 25,2013  | H. Ito<br>Feb 25,2013     | H. Ito<br>Feb 25,2013 |

| 1)<br>ar. 11. 2013                      | 1,2         | Editorial error correction              | K. Wakila<br>Har 11. 2013 | 7. Tarumi<br>Mar. 11,2013 | 94. olto<br>Mar. 11. 2013 | N. Ito<br>Nav. 11. 20 |

|                                         |             |                                         |                           |                           |                           |                       |

|                                         |             |                                         |                           |                           |                           |                       |

|                                         |             |                                         |                           |                           |                           |                       |

|                                         |             |                                         |                           |                           |                           |                       |

|                                         |             |                                         |                           |                           |                           |                       |

|                                         |             |                                         |                           |                           |                           |                       |

|                                         |             |                                         |                           |                           |                           |                       |

|                                         |             |                                         |                           |                           |                           |                       |

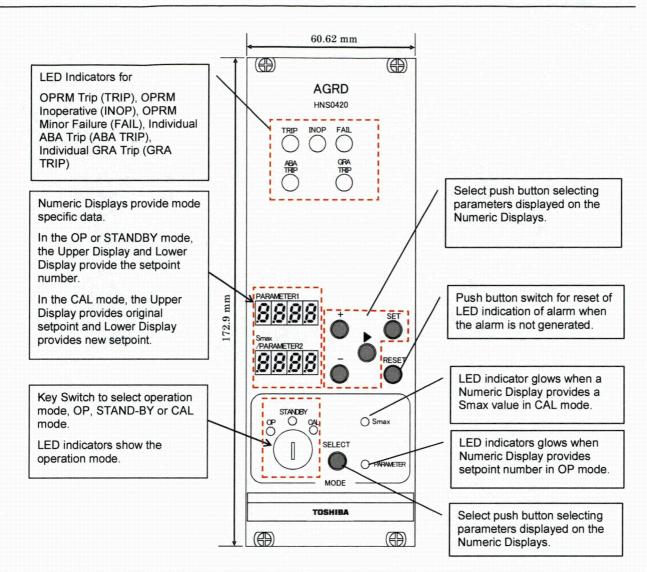

# AGRD Module Summary Description

### 1 Introduction

This document provides the module description for the following module.

- (1) Module Name: AGRD module

- (2) Module Number: HNS0420

- (3) Unit and application to be used OPRM Unit for ABWR Application

(4) Number of FPGA on the module: Eight

## 2 Functional Summary

The AGRD module receives OPRM cell data from the CELL module, monitors power oscillation for each cell using the Amplitude-Based Algorithm (ABA) and Growth Rate-based detection Algorithm (GRA). When the power oscillation is detected by ABA or GRA, the AGRD module generates a trip signal to DIO module. The AGRD module transmits AGRD calculation data to the DAT/ST module.

## 3 Module Description

### 3.1 User Interfaces

Figure 1 shows the front panel of the AGRD module.

### 3.2 Inputs and Outputs

The AGRD module has the following inputs and outputs.

3.2.1 Inputs

(1) Input signals via process input and output modules

N/A

(2) Input signals via communication modules

N/A

(3) Others to be noted

The AGRD module receives OPRM cell data from the CELL module.

Figure 1 The front panel of the AGRD module

#### 3.2.2 Outputs

(1) Output signals via process input and output modules

When the power oscillation is detected by ABA or GRA, the AGRD module generates a trip signal to DIO module.

(2) Output signals via communication modules

The AGRD module transmits AGRD calculation data to the DAT/ST module.

a,c

### 3.3 FPGA functions

Figure 2 shows Functional Block Diagram of the AGRD module where each block is an FPGA. Table 1 provides functions of each FPGA.

#### Figure2 Functional Block Diagram of AGRD module

#### Table1 FPGA functions in the AGRD module

| FPGA               | Description |   |

|--------------------|-------------|---|

|                    |             | ) |

|                    |             |   |

|                    |             |   |

|                    |             |   |

|                    |             |   |

|                    |             |   |

|                    |             |   |

|                    |             |   |

|                    |             |   |

|                    |             |   |

|                    |             | J |

| OSHIBA CORPORATION | 3/5         |   |

MEM-JHS-000123 Rev.1

a,c

a,c

a.c

a,c

)<sup>a,c</sup>

### 3.4 Self Diagnosis

The AGRD module generates the following self diagnosis signals.

#### 3.4.1 Minor Failure Alarm

The AGRD module generates a minor failure alarm if the EEPROM data error or the ) is detected. The ( ) is detected by Watchdog Timer (WDT) and determined as error if the ) is not detected.

#### 3.4.2 Inoperable Trip

Ę

ſ

The AGRD module generates an inoperable trip if ( )is detected. The ( detected by WDT and determined as error if the (

)<sup>a,c</sup> ) is not detected.

|           |             | 変 更 記 録                                 | REVISIONS                   | 3                          |                          |                        |

|-----------|-------------|-----------------------------------------|-----------------------------|----------------------------|--------------------------|------------------------|

| AKK       | ページ<br>PAGE | 変更箇所・変更内容<br>CHANGED PLACE AND CONTENTS | 承認<br>APPROVED<br>BY        | 調査<br>REVIEWED<br>BY       | 担当<br>PREPARED<br>BY     | 保管<br>REGISTEREI       |

| 2013      | <b>B</b> a  | First Issue                             | K. Wakita<br>Feb 25,2013    | T. Tarumi<br>Feb 25,2013   |                          | H. Ito<br>Feb 25,2013  |

| )<br>2015 | 1,3         | Editorial error correction.             | K., Lookita.<br>Mar 11.7013 | 7. Tarumi<br>Mar. 11, 2013 | 95. Ito<br>Mar. 11. 2013 | N. Sto<br>Mar. 11. 20] |

|           |             |                                         |                             |                            |                          |                        |

|           |             |                                         |                             |                            |                          |                        |

|           |             |                                         |                             |                            |                          |                        |

|           |             |                                         |                             |                            | 2                        |                        |

|           |             |                                         |                             |                            |                          |                        |

|           |             |                                         |                             |                            |                          |                        |

|           |             |                                         |                             |                            |                          |                        |

|           |             |                                         |                             |                            |                          |                        |

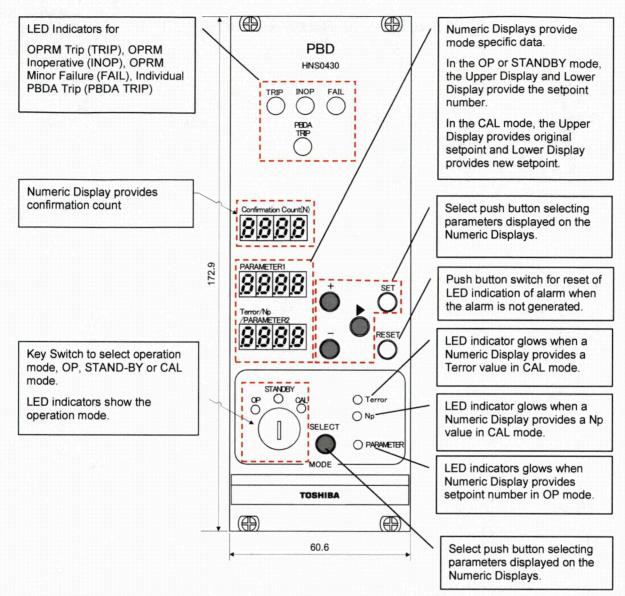

# PBD Module Summary Description

### 1 Introduction

This document provides the module description for the following module.

- (1) Module Name: PBD module

- (2) Module Number: HNS0430

- (3) Unit and application to be used OPRM Unit for ABWR Application

- (4) Number of FPGA on the module: Seven

# 2 Functional Summary

The PBD module receives OPRM cell data from the CELL module, monitors power oscillation for each cell using the Period-Based Detection Algorithm (PBDA). When the power oscillation is detected by PBDA, the PBD module generates a trip signal to DIO module. The PBD module transmits PBDA calculation data to the DAT/ST module.

## 3 Module Description

### 3.1 User Interfaces

Figure 1 shows the front panel of the PBD module.

### 3.2 Inputs and Outputs

The PBD module has the following inputs and outputs.

#### 3.2.1 Inputs

(1) Input signals via process input and output modules

N/A

(2) Input signals via communication modules

#### N/A

(3) Others to be noted

The PBD module receives OPRM cell data from the CELL module.

Figure 1 The front panel of the AGRD module

#### 3.2.2 Outputs

(1) Output signals via process input and output modules

When the power oscillation is detected by PBDA, the PBD module generates a trip signal to DIO module.

(2) Output signals via communication modules

The PBD module transmits PBD calculation data to the DAT/ST module.

### 3.3 FPGA functions

Figure 2 Functional Block Diagram of PBD module

#### 3.4 Self Diagnosis

The PBD module generates the following self diagnosis signals.

1

#### 3.4.1 Minor Failure Alarm

The PBD module generates a minor failure alarm if the EEPROM data error or the jis detected. The detected by Watchdog Timer (WDT) and determined as error if the jis not detected.

#### 3.4.2 Inoperable Trip

l

[

The PBD module generates an inoperable trip if stop is detected. The detected by WDT and determined as error if the

)<sup>a,c</sup> Jis ) is not detected.

a,c

a,cک

)<sup>a,c</sup>

|                                        |             | 変 更 記 録                                        | REVISIONS                    |                           |                        |                        |

|----------------------------------------|-------------|------------------------------------------------|------------------------------|---------------------------|------------------------|------------------------|

| 交更記号<br>REV.MARK<br>変更発行日<br>REV.ISWED | ページ<br>Page | 変更 箇 所 ・ 変 更 内 容<br>CHANGED PLACE AND CONTENTS | 承認<br>APPROVED<br>BY         | 調査<br>REVIEWED<br>BY      | 担当<br>PREPARED<br>BY   | 保管<br>REGISTERED       |

| 0<br>Feb 25,2013                       | _           | First Issue                                    | K. Wakita<br>Feb 25,2013     | T. Tarumi<br>Feb 25,2013  | H. Ito<br>Feb 25,2013  | H. Ito<br>Feb 25,2013  |

| 1)<br>Flor. 11. 2013                   | 1           | Editorial error correction.                    | K , Luskata<br>Mar-11 , 2013 | 7. Torumi<br>Mar.11, 2013 | H. Sto<br>Har. 11-2013 | H. Ito<br>Mar 11. 2013 |

|                                        |             | ,                                              |                              |                           |                        |                        |

|                                        |             |                                                |                              |                           |                        |                        |

|                                        |             |                                                |                              |                           |                        |                        |

|                                        |             |                                                |                              |                           |                        |                        |

|                                        |             | <b>、</b>                                       |                              |                           |                        |                        |

|                                        |             |                                                |                              |                           |                        | ·                      |

|                                        |             |                                                |                              |                           |                        |                        |

|                                        |             |                                                |                              |                           |                        |                        |

5E

# TOSHIBA Leading Innovation >>>

UTLR-0020NP Part III Rev.2 August 2015

# **Topical Report**

Licensing Topical Report for Toshiba NRW-FPGA-based Instrumentation and Control System for Safety-Related Application

### Part III

Qualification Results of the BWR-5 PRM and the ABWR OPRM

Approved by Electrical System Design & Engineering Dept.

# Masahiko Hamada

Toshiba Corporation Nuclear Energy Systems & Services Division

©2012 - 2015 Toshiba Corporation All Rights Reserved

Licensing Topical Report for Toshiba NRW-FPGA-based Instrumentation and Control System for Safety-Related Application UTLR-0020NP Part III Rev.2 Part III Qualification Results of the Power Range Monitor (PRM)

The use of the information contained in this document by anyone for any purpose other than that for which it is intended is not authorized. In the event the information is used without authorization from TOSHIBA CORPORATION, TOSHIBA CORPORATION makes no representation or warranty and assumes no liability as to the completeness, accuracy, or usefulness of the information contained in this document.

TOSHIBA CORPORATION NUCLEAR ENERGY SYSTEMS & SERVICES DIV. Licensing Topical Report for Toshiba NRW-FPGA-based Instrumentation and Control System for Safety-Related Application UTLR-0020NP Part III Rev.2 Part III Qualification Results of the Power Range Monitor (PRM)

# Table of Contents

| Table of Contents                                          |    |

|------------------------------------------------------------|----|

| List of Figures                                            |    |

| List of Tables                                             |    |

| Note for Acronyms and References                           | 5  |

| III-1 Introduction                                         |    |

| III-1.1 Background                                         | 6  |

| III-1.2 Purpose                                            | 7  |

| III-1.3 Scope                                              |    |

| III-2 Qualification Test of PRM                            |    |

| III-2.1 General Description                                |    |

| III-2.1.1 Pre-Qualification Tests                          | 9  |

| III-2.1.2 Qualification Tests                              |    |

| III-2.1.3 Performance Proof Tests                          |    |

| III-2.2 Qualification Tests for PRM System                 |    |

| III-2.2.1 Environmental Test                               | 14 |

| III-2.2.2 Seismic Test                                     | 17 |

| III-2.2.3 Electromagnetic Compatibility (EMC) Test         | 20 |

| III-2.2.4 Performance Proof Test for PRM System            | 27 |

| III-2.2.5 Conclusion of Qualification Tests for PRM System | 27 |

| III-3 Qualification Analysis of PRM                        | 29 |

| III-3.1 General Description                                |    |

| III-3.2 Qualification Analysis of PRM System               |    |

| III-3.2.1 Availability/Reliability Analysis of PRM System  | 30 |

| III-3.2.2 FMEA for PRM System                              | 30 |

| III-3.2.3 Setpoint Support Analysis for PRM System         | 31 |

| III-4 Verification and Validation of PRM                   | 32 |

| III-4.1 Power Range Neutron Monitor                        |    |

| III-4.1.1 V&V Organization and Process                     | 32 |

| III-4.1.2 Design Verification                              | 33 |

| III-4.1.3 Hazard Analyses                                  | 36 |

| III-4.1.4 V&V Iteration                                    |    |

| TOSHIBA CORPORATION                                        |    |

· -

Licensing Topical Report for Toshiba NRW-FPGA-based Instrumentation and Control System for Safety-Related Application UTLR-0020NP Part III Rev.2 Part III Qualification Results of the Power Range Monitor (PRM)

| III-4.1.: | 5 V&V Conclusions                                  | 37 |

|-----------|----------------------------------------------------|----|

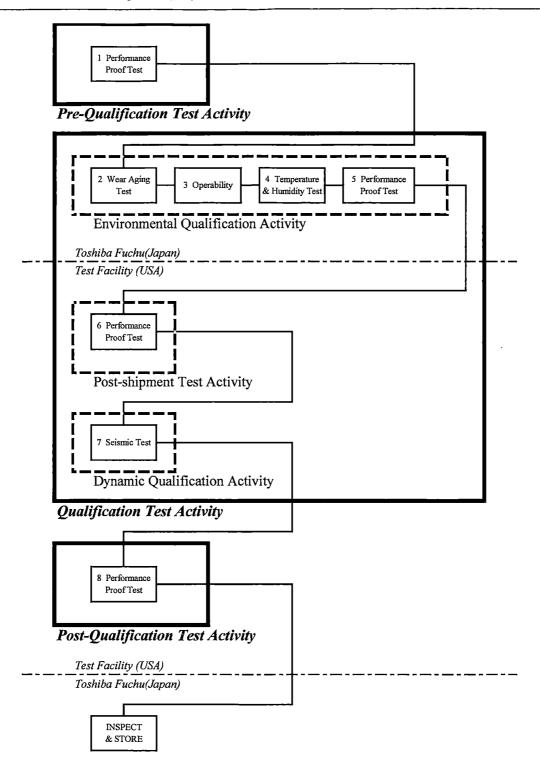

| III-5 Qua | alification Test of OPRM                           | 38 |

| III-5.1   | General Description                                | 38 |

| III-5.1.  | 1 Performance Proof Test                           | 39 |

| III-5.2   | Qualification Tests for OPRM System                | 39 |

| III-5.2.  | 1 Environmental Test                               | 44 |

| III-5.2.2 | 2 Seismic Test                                     | 45 |

| Ш-5.2.    | 3 Electromagnetic Compatibility (EMC) Test         | 48 |

| III-5.3   | Similarity Evaluation for New Module Design        | 53 |

| III-5.4   | Conclusion of Qualification Tests for OPRM System  | 54 |

| III-6 Qua | alification Analysis of OPRM                       | 56 |

| III-6.1   | General Description                                | 56 |

| III-6.2   | Qualification Analysis of OPRM System              | 56 |

| III-6.2.  | 1 Availability/Reliability Analysis of OPRM System | 56 |

| III-6.2.2 | 2 FMEA for OPRM System                             | 57 |

| `III-6.2  | 3 Setpoint Support Analysis for OPRM System        | 57 |

| III-7 Ver | ification and Validation of OPRM                   | 59 |

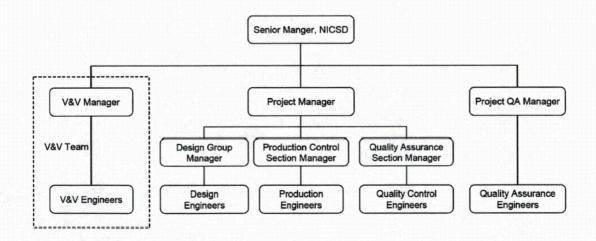

| III-7.1   | Oscillation Power Range Neutron Monitor            | 59 |

| III-7.1.  | 1 V&V Organization and Process                     | 59 |

| III-7.1.2 | 2 Design Verification                              | 60 |

| III-7.1.  | 3 Safety Analyses                                  | 62 |

| III-7.1.4 | 4 V&V Iteration                                    | 63 |

| III-7.1.: | 5 V&V Conclusions                                  | 63 |

ļ

ļ

2

# List of Figures

| Figure III-2-1 Test Sequence (PRM Qualification Project)                                  | 14 |

|-------------------------------------------------------------------------------------------|----|

| Figure III-3-1 Availability/Reliability Analysis Results (Test Specimen)                  | 30 |

| Figure III-3-2 Availability/Reliability Analysis Results (Full PRM System)                | 30 |

| Figure III-5-1 Environmental and Seismic Qualification Test Sequence (OPRM Qualification) | 42 |

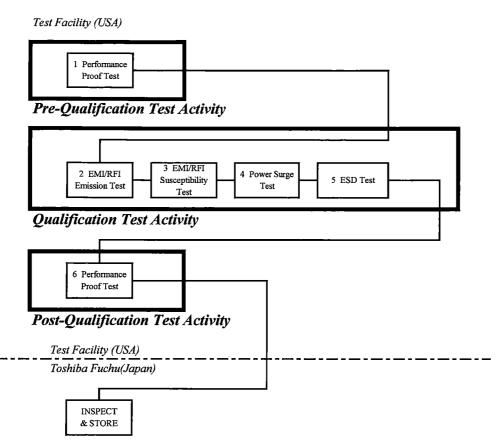

| Figure III-5-2 EMC Qualification Test Sequence (OPRM Qualification)                       | 43 |

# List of Tables

| Table III-2-1 Qualification Test Overview (PRM Qualification Project)                      | .13  |

|--------------------------------------------------------------------------------------------|------|

| Table III-2-2 Seismic Levels                                                               | 19   |

| Table III-2-3 EMC Test Results                                                             | 21   |

| Table III-2-4 [Deleted]                                                                    | 22   |

| Table III-2-5 [Deleted]                                                                    | .22  |

| Table III-5-1 Test Specimen Configuration during Environmental, Seismic, and EMC test of C |      |

| Table III-5-2 Qualification Test Overview (OPRM Qualification)                             | 41   |

| Table III-5-3 Seismic Levels                                                               | .46  |

| Table III-5-4 EMC Test Results                                                             | .49  |

| Table III-5-5 Applicable Module Type and FPGA Code Name for TRN Modules                    | 53   |

| Table III-5-6 Applicable Module Type and FPGA Code Name for RCV Modules                    | . 54 |

| Table III-6-1 Availability/Reliability Analysis Results (OPRM equipment)                   | . 56 |

\_ - -----

4

١

# Note for Acronyms and References

All acronyms and references are listed in the separate Acronym and Reference Part, which is part of this LTR.

# III-1 Introduction

This Part III of the Licensing Topical Report (LTR) for the Toshiba Non-Rewritable Field Programmable Gate Array-based (NRW-FPGA-based) Instrumentation and Control (I&C) Systems for Safety-Related Applications. This part addresses qualification results of the Power Range neutron Monitor (PRM) for Boiling Water Reactor (BWR)-5 and Oscillation Power Range Monitor (OPRM) for Advanced Boiling Water Reactor (ABWR).

# III-1.1 Background

Toshiba has extensive experience in supplying nuclear safety-grade Instrumentation and Control (I&C) systems in Japan. This experience ranges from supplying digital I&C systems, such as power range neutron monitors for individual plants, up to designing and manufacturing the world's first fully integrated digital CPU-based I&C systems for ABWRs. These systems were first installed at Kashiwazaki-Kariwa Unit 6, and are in use at Kashiwazaki-Kariwa Unit 6 and Hamaoka Unit 5.

Following the installation of the CPU-based BWR digital system, Toshiba started development of I&C technology based on Non-Rewritable (NRW) Field Programmable Gate Arrays (FPGAs) and supplied the NRW-FPGA-based I&C products to Japanese Nuclear Power Plants under Toshiba's ISO 9001 program. NRW-FPGA-based products have been installed in 11 nuclear power plants including 254 NRW-FPGA-based units for non-safety-related systems, 91 units for safety-related process radiation monitors, and 60 units for safety-related neutron monitoring systems.

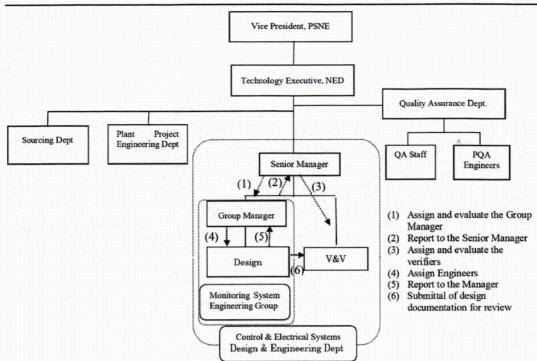

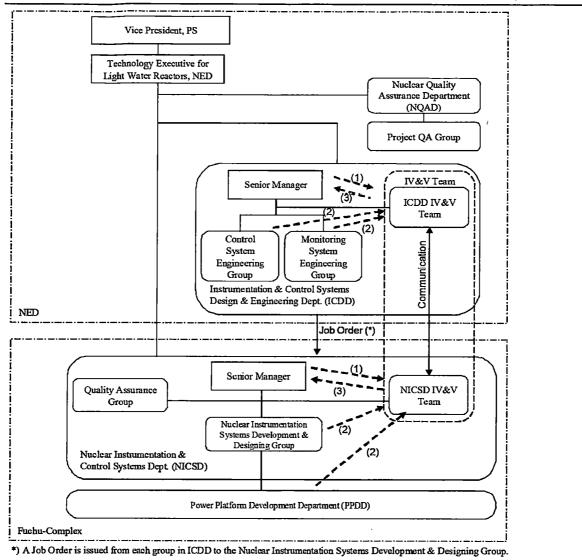

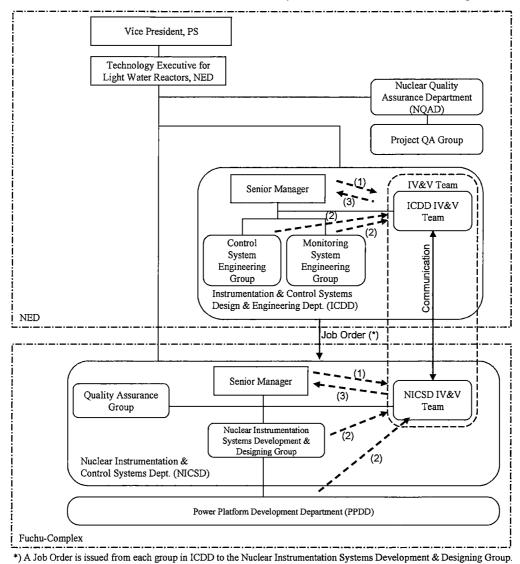

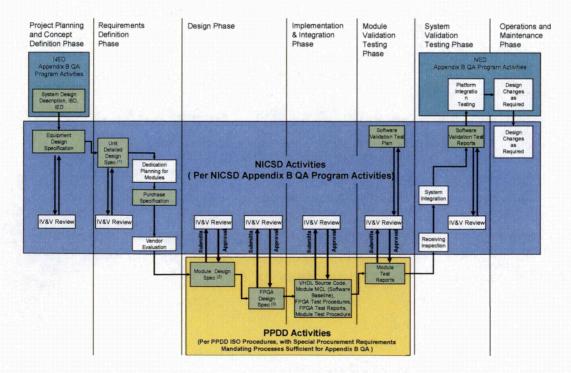

Toshiba also established a 10 CFR 50 Appendix B (Reference (a2)) Quality Assurance (QA) process to permit the use of Toshiba FPGA-based system in the US for safety-related applications in nuclear power plants. Toshiba implemented Appendix B QA processes in a phased approach as follows to ensure a smooth transition of the processes at the affected organizations.

• Original Process:

Initial establishment of the Appendix B QA process in the system engineering organization. This process was applied to the development and the qualification of the Power Range Monitor (PRM) for a Boiling Water Reactor (BWR)-5. This process is referred to as the "Original Process" in this topical report.

• Current Process:

Toshiba improved the Original Process by extending the Appendix B QA process into the

design organization and closer to the manufacturing organization where other Toshiba NRW-FPGA-based I&C products are developed. This process is referred to as the "Current Process" in this LTR. All future work will be under this process, including a modifications to equipment produced under the original process.

Toshiba has used the Original Process to develop and qualify a NRW-FPGA-based PRM for a BWR-5. Toshiba used the Current Process to develop and qualify the OPRM for ABWR.

This LTR uses the term "PRM," to means PRM for BWR-5 and uses the term "OPRM," to means OPRM for ABWR.

This LTR consists of the following six parts.

Part I describes software lifecycle and development processes.

Part II provides the design descriptions for the PRM and the OPRM and includes an application guide.

Part III describes the qualification results for the PRM and the OPRM.

Part IV provides the compliance tables for Toshiba processes to important Codes and Standards.

Part V provides the BWR-5 PRM V&V report.

Par VI provides the ABWR OPRM V&V report.

The Acronym and Reference Part lists all the acronyms and references used in the all Parts except Part V and VI of the LTR. Part V and Part VI have their own acronym and reference lists because they are the existing actual V&V reports for the PRM and the OPRM.

This is Part III of the LTR.

## III-1.2 Purpose

The purpose of Part III of the LTR is to describe the qualification of Toshiba NRW-FPGA-based PRM and OPRM.

The PRM was developed by the Original process, and the qualification activities of the PRM, including EQ and EMC testing were completed using this process. Comparison between the Current process and the Original process is provided in Appendix I-A. One exception was a V&V iteration performed to resolve a problem found in the FPGA dynamic testing of PRM.

The relating activities including V&V were performed using the Current process.

The OPRM was developed by the Current process, and the qualification activities of the OPRM including EQ and EMC testing were completed using current process.

# III-1.3 Scope

This Part III of the report includes the following information:

- Section III-1 provides introductory material like the report purpose and scope,

- Section III-2 introduces the qualification testing and describes how Toshiba implements this qualification testing for qualification of PRM.

- Section III-3 introduces the qualification analysis and describes how Toshiba implements this qualification analysis for qualification of PRM.

- Section III-4 introduces the system V&V process and results of the PRM.

- Section III-5 introduces the qualification testing and describes how Toshiba implements this qualification testing for qualification of OPRM.

- Section III-6 introduces the qualification analysis and describes how Toshiba implements this qualification analysis for qualification of OPRM.

- Section III-7 introduces the system V&V process and results of the OPRM.

The model numbers of the qualified modules for PRM are listed in Table 4-1 of the Requirements Definition Phase V&V Report for the PRM, which is included in Part V.

The model numbers of the qualified modules for OPRM are listed in Table 9-1, 9-5, and 10-1 of the NICSD V&V Report for OPRM, which is included in Part VI.

Licensing Topical Report for Toshiba NRW-FPGA-based Instrumentation and Control System for Safety-Related Application UTLR-0020NP Part III Rev.2 Part III Qualification Results of the Power Range Monitor (PRM)

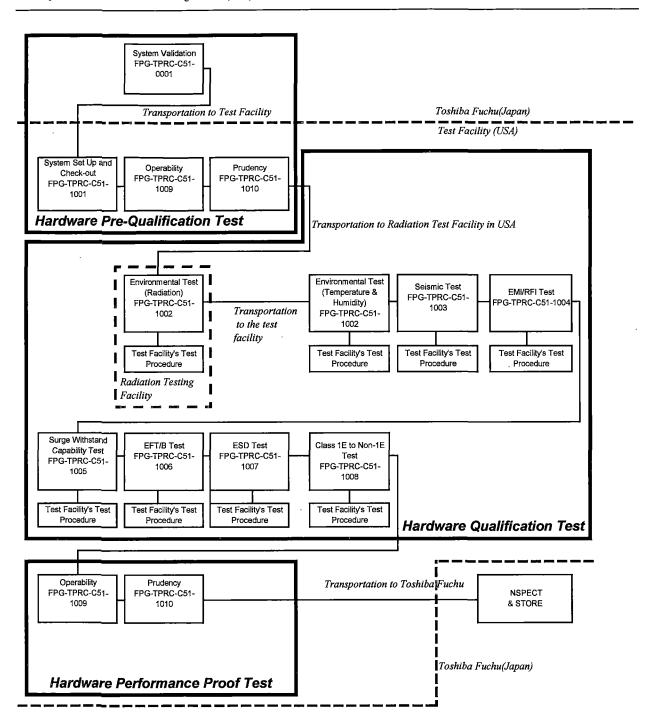

# III-2 Qualification Test of PRM

# III-2.1 General Description

This section describes the qualification of the Toshiba FPGA-based PRM. Toshiba performed qualification test activities as required by EPRI TR-107330, (Reference (a46)), which describes the hardware qualification tests to demonstrate hardware acceptability for safety-related applications. The tests specified in EPRI TR-107330 are required in order to comply with the applicable regulatory requirements and industry standards. The qualification tests were performed using an assembled test system that is comprised of a test specimen and test equipment with validated final FPGA logic.

For equipment qualification, test plans were prepared that define the test activities and test sequence. The test plans specify the set of qualification tests to be performed on the test specimen, including defining a set of operability tests to be performed during qualification test. The tests include a pre-qualification test, qualification test, and performance proof test. The following describes the hardware testing required by EPRI TR-107330 as it relates to the FPGA-based systems. Test limits have been adjusted by more current NRC guidance, including USNRC RG 1.180, Revision 1.

## III-2.1.1 Pre-Qualification Tests

The Pre-Qualification Test was performed prior to the Qualification Test. This test was performed to demonstrate that the Test Specimen operates as intended and to provide a performance baseline for the Qualification Tests. The Pre-Qualification test includes:

- System Set-up and Check-out Test. The purpose of this test is to verify proper assembly, integration, and operation of the assembled Test System for Pre-Qualification Test. This test confirms proper connection and operation of the Test System including monitoring instruments, variable power supplies, and signal simulators.

- Burn-in Test. The purpose of this test is to perform a minimum 352 hour burn-in of the assembled Test System. The objective of the test is to detect any failures in early life that might otherwise impact the subsequent Qualification Test activities. System Set-up and Check-out Test described above is repeated after the Burn-in Test.

- Operability Test. The purpose of this test is to verify the Test System functions correctly prior to the performance of Qualification Tests. This initial performance during Pre-Qualification Testing also established the baseline performance of the Test

System, which are used for comparison to performance measured during Qualification Tests.

• Prudency Test. The purpose of this test is to verify the Test System functions correctly while being exercised in various ways to simulate potential in-service stresses prior to the performance of Qualification Test. This initial performance of the prudency test also establishes baseline performance of the Test System for comparison to performance measured during Qualification Tests.

These tests were performed in accordance with Section 5 of EPRI TR-107330.

## III-2.1.2 Qualification Tests