# ST-8000 HF MODEM

# TECHNICAL MANUAL

**VOLUME I**

ST-8000

HF MODEM

# TECHNICAL MANUAL

VOLUME I

Copyright © 1986 by HAL Communications Corp., Urbana, Illinois. Printed in the United States of America. All rights reserved. Contents of this publication may not be reproduced in any form without written permission of the copyright owner.

870-08001

June, 1986 Printing

| VO | LU | ME | Ι |

|----|----|----|---|

|----|----|----|---|

|         |    | $INTRODUCTION \dots 2$                                                 |

|---------|----|------------------------------------------------------------------------|

| CHAPTER | 1. | SPECIFICATIONS                                                         |

| CHAPTER | 2. | TECHNICAL DESCRIPTION                                                  |

|         |    | 2.1ST8000 Organization62.2Modem Assembly6                              |

|         |    | • · · · · · · · · · · · · · · · · · · ·                                |

|         |    |                                                                        |

|         |    |                                                                        |

|         |    |                                                                        |

|         |    |                                                                        |

|         |    | 2.2.5 Pulse Detectors                                                  |

|         |    |                                                                        |

|         |    |                                                                        |

|         |    | 2.2.5.3 Print Squelch Detc 17<br>2.2.5.4 DMPC Circuit 18               |

|         |    | 2.2.5.5 Detector Mode Select . 19                                      |

|         |    | 2.2.6 RX Data Control                                                  |

|         |    | 2.2.6.1 Polarity, REGEN, A/S . 19                                      |

|         |    | 2.2.6.2 Print SQ, Diversity 20                                         |

|         |    | 2.2.6.3 RXD I/O Interface 21                                           |

|         |    | 2.2.6.4 Motor Control 21                                               |

|         |    | 2.2.6.5 CRT Trace Control 22                                           |

|         |    | 2.2.6.6 Indicators                                                     |

|         |    | 2.2.7 Diversity & AGC Squelch 23                                       |

|         |    | 2.2.7.1 Non-diversity Squelch . 23                                     |

|         |    | 2.2.7.2 Diversity Mode 24                                              |

|         |    | 2.2.8 TXD Control, KOS, & ECHO 25                                      |

|         |    | 2.2.8.1 TXD I/O Interface 25                                           |

|         |    | 2.2.8.2 TX/RX PTT Circuit 25                                           |

|         |    | 2.2.8.3 Echo Control 26                                                |

|         |    | 2.2.8.4 AFSK, FSK TXD Output . 26                                      |

|         |    | 2.2.9 AFSK Oscillator 27                                               |

|         |    | 2.2.10 Power Supply                                                    |

|         |    | 2.2.11 Modem Assembly Interconnections 27                              |

|         |    | 2.3 Control Assembly                                                   |

|         |    | 2.3.1 Microprocessor Controller 28                                     |

|         |    | 2.3.2 System Clocks                                                    |

|         |    | 2.3.3 RESET and Sanity Timer 30                                        |

|         |    | 2.3.4 Memory and I/O Map                                               |

|         |    | 2.3.5 EPROM and RAM Memory 33                                          |

|         |    | 2.3.6 Modem Board Latched Interface . 33                               |

|         |    | 2.3.6.1 M/S Filter Q Select 34                                         |

|         |    | 2.3.6.2 CRT Control                                                    |

|         |    | 2.3.6.3 Regeneration Control . 35<br>2.3.6.4 Normal/Reverse Control 36 |

|         |    |                                                                        |

|         |    | 2.3.6.5 Input Filter Bandwidth 36<br>2.3.6.6 Selective Call Control 36 |

|         |    | 2.3.6.7 Detector Mode Control . 37                                     |

|         |    | 2.3.6.8 Antispace Control 37                                           |

|         |    | 2.3.6.9 Push to Talk Control . 38                                      |

|         |    | 2.3.6.10 CTS Control Bit 38                                            |

|         |    |                                                                        |

-

|            |      | 2.3.7 Regeneration and Control Port . | 39       |

|------------|------|---------------------------------------|----------|

|            |      |                                       | 40       |

|            |      | •                                     | 41       |

|            |      |                                       | 43       |

|            |      | 2.3.11 SPACE Filter Synthesizer       | 44       |

|            |      | 2.3.12 BAND PASS Filter Synthesizer 4 | 44       |

|            |      | 2.3.13 LOW PASS Filter Synthesizer    | 45       |

|            | 2.4  |                                       | 46       |

|            |      | 2.4.1 Front Panel Switches            | 46       |

|            |      | 2.4.2 Front Panel Displays 4          | 46       |

|            | 2.5  |                                       | 47       |

|            |      | 2.5.1 CRT Power Supplies              |          |

|            |      | 2.5.2 CRT Controls                    |          |

|            |      | 2.5.3 Deflection Amplifiers 4         |          |

|            |      | 2.5.4 Trace Switching                 |          |

|            |      | 2.5.5 Spectra-Tune                    |          |

|            |      | 2.5.6 Trace Rotation                  |          |

|            | 26   |                                       | 50       |

|            | 2.0  | -                                     |          |

|            |      |                                       | 50       |

|            |      | 2.6.2 Cabinet Finish Protection       | 51       |

|            |      | 2.6.3 Cabinet Ventilation             | 51       |

|            |      |                                       |          |

|            | mpcm |                                       | 5 2      |

| CHAPTER 3. |      | AND ALIGNMENT                         |          |

|            | 3.1  |                                       | 52       |

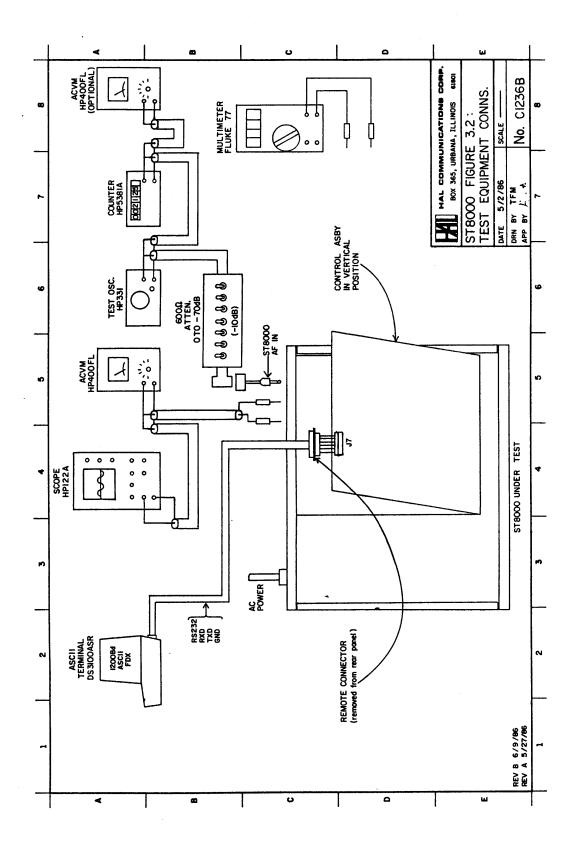

|            |      | 3.1.1 Test Equipment                  | 52       |

|            |      |                                       |          |

|            | ~ ~  |                                       | 53       |

|            |      |                                       | 53       |

|            | 3.3  |                                       | 55       |

|            |      | 3.3.1 Initial Set-up                  | 55       |

|            |      |                                       | 59       |

|            |      | 3.3.3 Limiter and AGC Alginment 6     | 61       |

|            |      |                                       | 62       |

|            |      | 3.3.4.1 Mark Filter 6                 | 63       |

|            |      | 3.3.4.2 Space Filter 6                | 66       |

|            |      | 3.3.5 AFSK Generator Tests 6          | 69       |

|            |      | 3.3.6 Transmit Data Input Circuitry . | 71       |

|            |      |                                       | 72       |

|            |      |                                       | 73       |

|            |      |                                       | 74       |

|            |      |                                       | 78       |

|            |      |                                       | 78       |

|            |      |                                       | 79       |

|            |      |                                       | 80       |

|            |      |                                       | 82       |

|            | 3.4  |                                       | o∠<br>83 |

|            | 5.4  |                                       |          |

|            |      | <b>▲</b>                              | 83       |

|            |      |                                       | 84       |

|            |      |                                       | 85       |

|            |      |                                       | 86       |

|            | 3.5  | -                                     | 87       |

|            |      | <b>L 1</b>                            | 87       |

|            |      | 3.5.2 Front Panel Switches 8          | 88       |

¢.

|            | 3.6  | CRT Alignment and Test 89                                |

|------------|------|----------------------------------------------------------|

|            |      | 3.6.1 Initial Set-up 89                                  |

|            |      | 3.6.2 CRT Trace Control Adjustments . 89                 |

|            |      | 3.6.3 CRT Spectra-Tune Adjustments 90                    |

|            | 3.7  | Other ST8000 Tests 91<br>3.7.1 Data Processing Delays 91 |

|            |      | 3.7.1 Data Processing Delays 91                          |

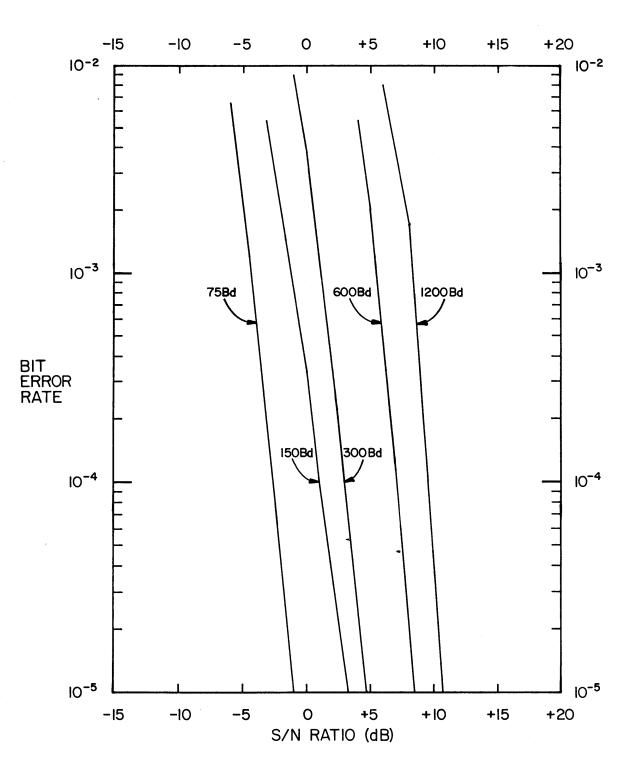

|            |      | 3.7.2 Bit Error Rate Tests 92                            |

|            |      |                                                          |

| CHAPTER 4. | MAIN | TENANCE AND REPAIR                                       |

|            | 4.1  |                                                          |

|            |      | Factory Return Procedures 98                             |

|            | 4.3  |                                                          |

|            | 4.4  | Modem Assembly Maintenance 100                           |

|            |      | 4.4.1 Power Supply 100                                   |

|            |      | 4.4.2 Receive Data Filters 101                           |

|            |      | 4.4.3 Receive Data Processing 102                        |

|            |      | 4.4.4 Diversity Circuitry 103                            |

|            |      | 4.4.5 TXD Control 103                                    |

|            |      | 4.4.6 AFSK Generator 104                                 |

|            |      | 4.4.7 Transmitter PTT Control 104                        |

|            | 4.5  | Control Assembly Maintenance 104                         |

|            |      | 4.5.1 Component Failure 105                              |

|            |      | 4.5.1.1 Clock/Reset Failure 105                          |

|            |      | 4.5.1.2 Synthesizer Failure 106                          |

|            |      | 4.5.1.3 Other Components 106                             |

|            |      | 4.5.2 Interconnection Problems 107                       |

|            | 4.6  | Front Panel Assembly Maintenance 107                     |

|            |      | 4.6.1 Display Failure 107                                |

|            |      | 4.6.2 Front Panel Switches 108                           |

|            |      | 4.6.3 Front Panel Integrated Circuits 108                |

|            |      | 4.6.4 Mechanical Failure 109                             |

|            | 4.7  | CRT Assembly Maintenance 109                             |

|            |      | 4.7.1 CRT Replacement 109                                |

|            |      | 4.7.2 Other CRT Problems                                 |

|            |      |                                                          |

| CHAPTER 5. | PART | S LISTS                                                  |

|            | 5.1  | S LISTS                                                  |

|            | 5.2  | Demodulator Assembly                                     |

|            | 5.3  | Control Assembly                                         |

|            | 5.4  | Front Panel Assembly 129                                 |

|            | 5.5  | CRT Assembly                                             |

|            | 5.6  | CRT Assembly                                             |

|            | 5.7  | ST8000 Accessories                                       |

|            | 5.8  |                                                          |

|            | 5.9  |                                                          |

# VOLUME II

| CHAPTER | 6. | TECHNICAL | DIAGRAMS | • | • | • | • | • | • | • | • | ٠ | • | • | • | • | 14 | 15 | , |

|---------|----|-----------|----------|---|---|---|---|---|---|---|---|---|---|---|---|---|----|----|---|

|---------|----|-----------|----------|---|---|---|---|---|---|---|---|---|---|---|---|---|----|----|---|

-

# VOLUME I

| FIGURE | 1.1  | ST8000 HF MODEM                      | 2 |

|--------|------|--------------------------------------|---|

| FIGURE | 2.1  | INPUT BANDPASS FILTERS               | 8 |

| FIGURE | 2.2  | LIMITER OUTPUT CHARACTERISTICS (TP8) | 9 |

| FIGURE | 2.3  | AGC CHARACTERISTICS (TP4) 10         | 0 |

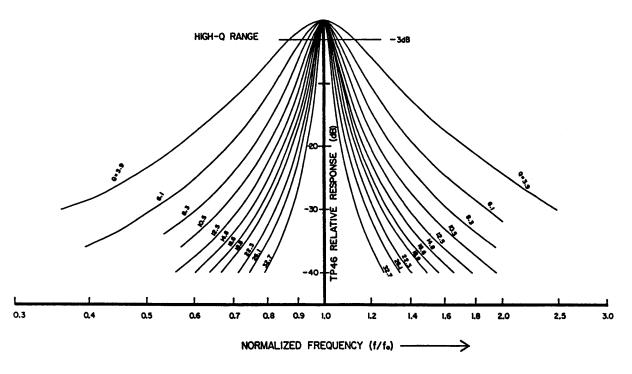

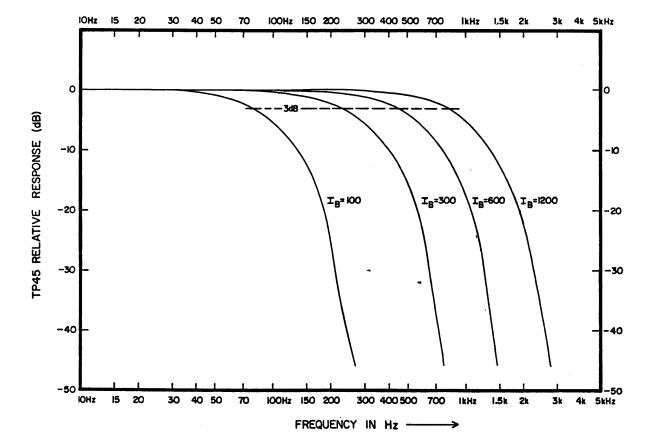

| FIGURE | 2.4  | MARK/SPACE FILTER - HIGH Q RANGE 1   | 2 |

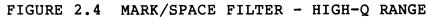

| FIGURE | 2.5  | MARK/SPACE FILTER - LOW Q RANGE 1    | 2 |

| FIGURE | 2.6  | LOW PASS FILTER RESPONSE 14          | 4 |

| FIGURE | 2.7  | SPACE ONLY DETECTOR WAVEFORMS 1      | 5 |

| FIGURE | 2.8  | DMPC WAVEFORMS 18                    | 8 |

| FIGURE | 2.9  | CLOCK DISTRIBUTION                   | 9 |

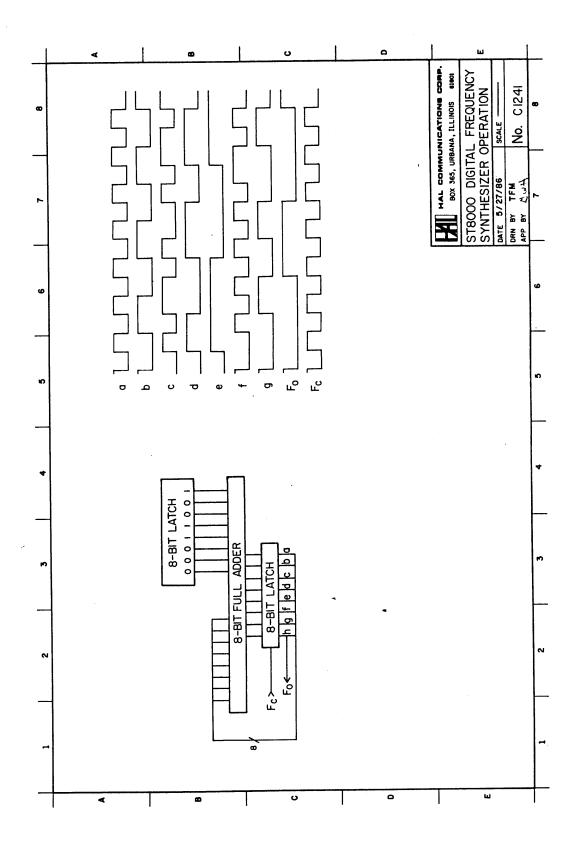

| FIGURE | 2.10 | SYNTHESIZER OPERATION 42             | 2 |

| FIGURE | 3.1  | ST8000 VOLTAGE TEST POINTS 53        | 3 |

| FIGURE | 3.2  | TEST EQUIPMENT CONNECTIONS           | 6 |

| FIGURE | 3.3  | TYPICAL ST8000 MODEM MEASUREMENTS 5  | 7 |

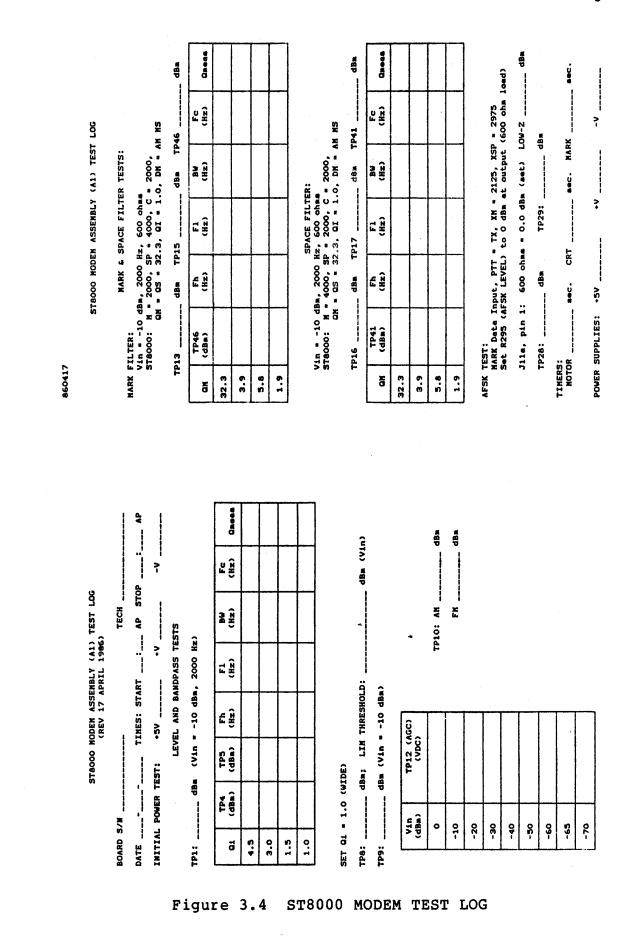

| FIGURE | 3.4  | ST8000 TEST LOG                      | 3 |

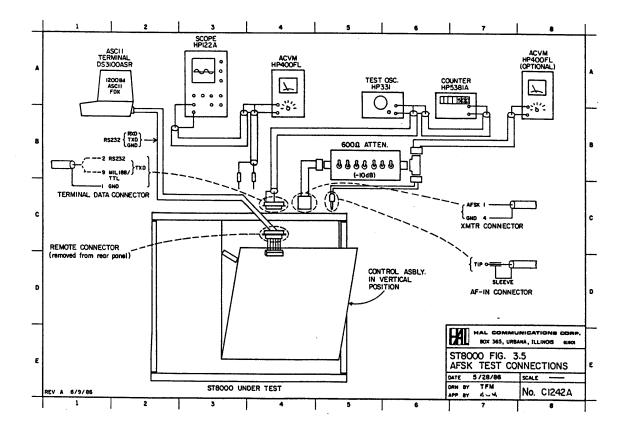

| FIGURE | 3.5  | AFSK TEST GENERATOR CONNECTIONS      | 3 |

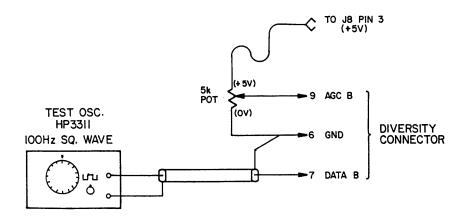

| FIGURE | 3.6  | DIVERSITY TEST CONNECTIONS           | 9 |

| FIGURE | 3.7  | BER TESTS                            | 4 |

# VOLUME II

| FIGURE 6.1  | ST8000 DRAWING CONVENTIONS 147                                                        |

|-------------|---------------------------------------------------------------------------------------|

| FIGURE 6.2  | BLOCK DIAGRAM                                                                         |

| FIGURE 6.3  |                                                                                       |

| FIGURE 6.4  | MODEM ASBLY - INPUT FILTER SCHEMATIC 150<br>MODEM ASBLY - LIMITER & AGC PICTORIAL 151 |

| FIGURE 6.5  | MODEM ASBLY - LIMITER & AGC PICTORIAL 151                                             |

| FIGURE 6.6  | MODEM ASBLY - LIMITER & AGC SCHEMATIC 152                                             |

|             | MODEM ASBLY - MARK FILTER PICTORIAL 153                                               |

|             | MODEM ASBLY - MARK FILTER SCHEMATIC 154                                               |

|             | MODEM ASBLY - SPACE FILTER PICTORIAL 155                                              |

| FIGURE 6.10 | MODEM ASBLY - SPACE FILTER SCHEMATIC 156                                              |

| FIGURE 6.11 |                                                                                       |

| FIGURE 6.12 |                                                                                       |

|             | MODEM ASBLY - DETC. & PR SQUELCH PICTORIAL . 159                                      |

| FIGURE 6.14 | MODEM ASBLY - DETC. & PR SQUELCH SCHEMATIC . 160                                      |

| FIGURE 6.15 |                                                                                       |

| FIGURE 6.16 | MODEM ASBLY - RX DATA CONTROL SCHEMATIC 162                                           |

| FIGURE 6.17 |                                                                                       |

| FIGURE 6.18 | MODEM ASBLY - DIVERSITY SCHEMATIC 164                                                 |

| FIGURE 6.19 | MODEM ASBLY - TXD CONTROL, KOS PICTORIAL 165                                          |

| FIGURE 6.20 |                                                                                       |

| FIGURE 6.21 |                                                                                       |

| FIGURE 6.22 |                                                                                       |

| FIGURE 6.23 |                                                                                       |

| FIGURE 6.24 | MODEM ASBLY - POWER SUPPLY SCHEMATIC 170                                              |

| FIGURE 6.25 |                                                                                       |

| FIGURE 6.26 |                                                                                       |

| FIGURE 6.27 |                                                                                       |

| FIGURE 6.28 | CONTROL ASBLY - PROCESSOR RAM/ROM SCHEMATIC 174                                       |

|             |                                                                                       |

| FIGURE 6.30 | CONTROL ASBLY - MODEM CONTROL SCHEMATIC 176                                           |

•

| FIGURE 6.31 | CONTROL ASBLY - SERIAL, DSPLY I/O PICTORIAL 177  |

|-------------|--------------------------------------------------|

|             |                                                  |

| FIGURE 6.32 | CONTROL ASBLY - SERIAL, DSPLY I/O SCHEMATIC 178  |

| FIGURE 6.33 | CONTROL ASBLY - SYNTH. CLOCK PICTORIAL 179       |

| FIGURE 6.34 | CONTROL ASBLY - SYNTH. CLOCK SCHEMATIC 180       |

| FIGURE 6.35 | CONTROL ASBLY - AFSK SYNTHESIZER PICTORIAL . 181 |

| FIGURE 6.36 | CONTROL ASBLY - AFSK SYNTHESIZER SCHEMATIC . 182 |

| FIGURE 6.37 | CONTROL ASBLY - MARK SYNTHESIZER PICTORIAL . 183 |

| FIGURE 6.38 | CONTROL ASBLY - MARK SYNTHESIZER SCHEMATIC . 184 |

| FIGURE 6.39 | CONTROL ASBLY - SPACE SYNTHESIZER PICTORIAL 185  |

| FIGURE 6.40 | CONTROL ASBLY - SPACE SYNTHESIZER SCHEMATIC 186  |

| FIGURE 6.41 | CONTROL ASBLY - BAND-PASS SYNTH. PICTORIAL . 187 |

| FIGURE 6.42 | CONTROL ASBLY - BAND-PASS SYNTH. SCHEMATIC . 188 |

| FIGURE 6.43 | CONTROL ASBLY - LOW-PASS SYNTH. PICTORIAL . 189  |

|             |                                                  |

| FIGURE 6.44 | CONTROL ASBLY - LOW-PASS SYNTH. SCHEMATIC . 190  |

| FIGURE 6.45 | CONTROL ASBLY - PARTS PLACEMENT 191              |

| FIGURE 6.46 | CONTROL ASBLY - I/O CONNECTOR SCHEMATIC 192      |

| FIGURE 6.47 | FRONT PANEL ASBLY - PICTORIAL                    |

| FIGURE 6.48 | FRONT PANEL ASBLY - SCHEMATIC                    |

| FIGURE 6.49 | CRT ASBLY - PICTORIAL                            |

| FIGURE 6.50 | CRT ASBLY - SCHEMATIC                            |

| FIGURE 6.51 | CABINET ASBLY - PICTORIAL 1                      |

|             |                                                  |

| FIGURE 6.52 | CABINET ASBLY - PICTORIAL 2                      |

| FIGURE 6.53 | INTER-MODULE CONNECTIONS - PICTORIAL 199         |

| FIGURE 6.54 | INTER-MODULE CONNECTIONS - SCHEMATIC 200         |

|             |                                                  |

# TABLES

| TABLE | 3.1 | ST8000  | VOLTAGE  | MEASU | JREME | NTS  | •   | • | • | • | • | • | • | • | 54 |

|-------|-----|---------|----------|-------|-------|------|-----|---|---|---|---|---|---|---|----|

| TABLE | 3.2 | TYPICAL | ST8000   | TIME  | DELA  | YS . | •   | • | • | • | • | • | • | • | 92 |

| TABLE | 4.1 | ELECTRO | STATIC : | SENSI | TIVE  | DEVI | CES | 5 | • | • | • | • | • | • | 97 |

V

# (THIS PAGE IS INTENTIONALLY BLANK)

۰

#### INTRODUCTION

This manual is the technical and maintenance companion to the "ST8000 OPERATOR'S MANUAL" and "ST8000 OPERATOR'S GUIDE". Operation and installation of the ST8000 are fully described in these documents. Technical, test, and maintenance information are contained in this ST8000 TECHNICAL MANUAL.

Because of the size and quantity of technical drawings for the ST8000, this TECHNICAL MANUAL is published in two volumes. VOLUME I contains Chapters 1 through 5 (Specifications, Technical Description, Test and Alignment, Maintenance, and Parts Lists). VOLUME II contains the pictorial and schematic diagrams of the ST8000. The diagrams in VOLUME II are arranged with the schematic diagram for a given circuit section on the right-hand page and the corresponding pictorial for parts location on the left-hand facing page. The texts of Chapter 2, 3, and 4 are keyed to this page arrangement.

It is assumed that the reader has an electronic equipment servicing background and has access to the required test equipment. Please use EXTREME CAUTION when testing to avoid damaging the ST8000 circuitry. In particular, CMOS microcircuits are used in sections of the ST8000 and the technician should use all accepted grounding and static electrical discharge prevention techniques available to him.

In some cases, particularly when testing the CRT Assembly, DANGEROUS HIGH VOLTAGES will be exposed. Use EXTREME CAUTION when performing these tests to avoid POTENTIALLY LETHAL HIGH VOLTAGE shocks.

All of the described tests may be performed with standard test equipment. However, the accuracy of the measurements is determined by the accuracy of the test instruments themselves. Assure yourself of your test equipment's accuracy and reliability before assuming "incorrect measurements" are due to an ST8000 circuit failure.

FIGURE 1.1 ST8000 HF MODEM

J

CHAPTER 1. SPECIFICATIONS

| INPUT DATA:<br>Data Rate: | 10 to 1200 baud                                                                                                                                                                                                              |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency:                | 400 - 4000  Hz                                                                                                                                                                                                               |

| Impedance:                | 8 or 600 ohms, bal. or unbal.<br>5K ohms, unbalanced                                                                                                                                                                         |

| Dynamic Range:            | -65 to +10 dBm (580 uV to 2.5 V)                                                                                                                                                                                             |

| RECEIVE PROCESSING        | :                                                                                                                                                                                                                            |

| Mode:                     | Hard-limiting FM (-54 dBm threshold)<br>AGC controlled AM (-65 dBm threshold)                                                                                                                                                |

| Input Filters:            | 4 filters: 6-pole 1/3, 1/2, 1 Octave<br>bandwidth - tunable and tracked to<br>center frequency of selected Mark and<br>Space tones; 400 - 4000 Hz fixed tuned.                                                               |

| Tone Filters:             | Matched 4-pole tunable filters, set to<br>selected Mark and Space frequencies<br>from 400 to 4000 Hz in 1 Hz increments.<br>M/S filter bandwidths set in 32 steps,<br>automatically tracked with Baud and<br>Shift selected. |

| DATA PROCESSING:          |                                                                                                                                                                                                                              |

| Detectors:                | Matched full-wave active detectors.<br>Outputs for Mark Only, Space Only,<br>M/S differential, or Digital Multi-Path<br>Correction.                                                                                          |

| LP Filters:               | Matched separate Mark and Space 7-pole<br>linear phase tunable low-pass filters.<br>Cut-off frequencies set by Input Baud<br>rate control.                                                                                   |

| Antispace:                | Prevents "open loop" on interference.                                                                                                                                                                                        |

| Print Squelch:            | Adjustable Print Squelch threshold;<br>returns to Mark-hold with no signal (LOS).                                                                                                                                            |

| Diversity:                | Infinite Resolution Diversity Control for two<br>receiver selection diversity system.                                                                                                                                        |

| Regeneration:             | Dual digital UART regenerator for ASCII or<br>Baudot data; also provides code and speed<br>conversion (45 - 1200 bd).                                                                                                        |

| Clock Recovery:           | Recovered receive data clock output.                                                                                                                                                                                         |

TUNING FEATURES: Frequencies derived from quartz crystal Control: synthesizers. Set Mark, Space, Shift, and Center frequencies, Input or Output Baud in 1 Hz or 1 Baud increments. Modes: BAUD - set Input or Output Baud rate - set Space or Shift frequency SP/SH MARK/Fo - set Mark or Center frequency - Maintain Shift and set Mark, TRACK Space, and Fo frequencies. Memories: Eight - non-volatile and programmable. Each memory stores Mark, Space, Fo, Shift, Input Filter, M/S Bandwidth, LP Filter Frequency, Input Baud, Output Baud, and M/S AFSK transmit frequencies. TX/RX variable, RX variable, TX memory, Memory Modes: TX/RX memory. Remote Control: Separate terminal port for control of all demodulator parameters. (Serial ASCII; 300-9600 Baud). TRANSMIT FEATURES: 400 to 4000 Hz in 1 Hz increments. AFSK Tones: Track receiver tones or fixed by memory selection. AFSK Level: -40 to +10 dBm (rear panel control) (7.8 mV to 2.5 V rms at 600 ohms). 8 or 600 ohms, balanced or unbalanced, Impedance: transformer coupled or DC isolated output. Relay closure to ground; internal KOS, PTT Control: terminal KOS, RS232C RTS, or manual front panel switch control; +/- 50V, 0.5A max. Logic voltage to drive direct FSK input FSK Output: on transmitter. Polarity and voltage level selectable (open collector, +5V, or +8V for Mark or Space). **DISPLAYS:** 1.50 x 2.00 inch rectangular CRT; Tuning: crossed-ellipse Mark/Space and 500-3500 Hz spectral Spectra Tune display of received signals; CRT beam turned off on LOS (Loss Of Signal).

turned off on LOS (Loss Of Signal).Frequency:Three 4-digit displays show Mark or Fo,<br/>Space or Shift, and Input or Output Baud.LED:Mark, Space, LOS, Print On, A or B<br/>Diversity, TX on, and Power on.

INPUT/OUTPUT CONNECTIONS:

| TERMINAL DATA: | Shielded 1 | DB-25S socket-type connector. |

|----------------|------------|-------------------------------|

|                | RS232C:    | TXD, RXD, RTS, CTS,           |

|                |            | CD, DSR, recovered RXC        |

|                | MIL-188C:  | TXD, RXD                      |

|                |            | TXD, RXD                      |

|                | Misc:      | Terminal KOS, Motor Control,  |

|                |            | FSK output.                   |

- DIVERSITY: Shielded DE-9S socket to connect second ST8000 in two-channel diversity system.

- REMOTE CONTROL: Shielded DB-25S socket for serial remote control of all front panel parameters.

- RECEIVE AUDIO: Stereo 1/4" phone jack for audio input.

- TRANSMITTER: 4-pin shielded mic. connector; transmit audio and PTT or transmit FSK and PTT.

- POWER: IEC AC power connector; shielded and filtered.

#### PHYSICAL DATA:

- Cabinet Finish: Natural aluminum with irridite finish; black vinyl front panel. Cabinet Style: 19" rack mounting or table-top with tilt-bail and feet. Size: 3.50 H x 14 D x 19 W (rack mtg) (8,9 x 35.6 x 48.3 cm) 4.125 H x 14 D x 17 W (table case) (10.5 x 35.6 x 43.2 cm)

- Weight: 13 lbs (5.9 kg) net, 19 lbs (8.6 kg) shipping.

- Power: 100-120 or 200-240 VAC, 44-440 Hz; 36 Watts; IEC style AC Connector.

- Power Line Fused with type 3AG, 1.0A SB Fuse; Protection: Type 1EF2 RFI/EMI Filter (22dB at 0.15 mHz, 49 dB at 30 mHz).

#### CHAPTER 2. TECHNICAL DESCRIPTION

This chapter presents a detailed explanation of the circuitry of the ST8000. Frequent references will be made to the schematic and pictorial diagrams in Chapter 6 (VOLUME II). These references will be given at the head of each subsection of the discussion in the form [6.x] where "6.x" is the figure number. Additional illustrations will be included in this Chapter as necessary. Drawing conventions used in this manual are shown in Figure 6.1.

2.1 ST8000 ORGANIZATION [6.2]

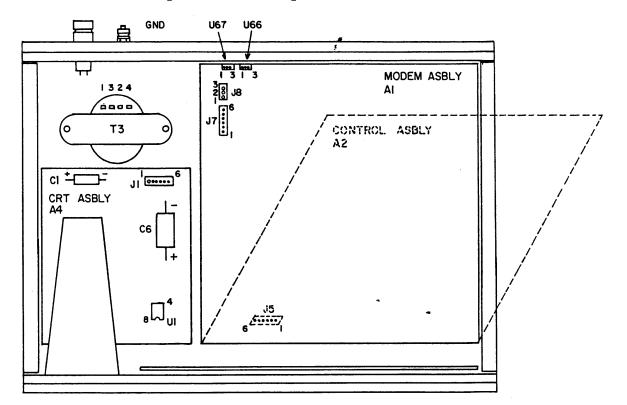

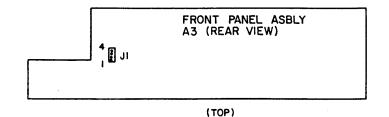

The ST8000 is constructed of 5 subassemblies: MODEM (Al), CONTROL (A2), FRONT PANEL (A3), CRT (A4), and CABINET (A5). Each assembly is connected to the other with the cables shown in Figures 6.53 and 6.54. All of the audio and data processing detection circuitry for receive and transmit operation are contained on the MODEM (Al) assembly. Master control and frequency generating synthesizer circuits are on the CONTROL (A2) assembly. Cathode Ray Tube (CRT) control and amplifier circuits are on the CRT assembly (A4). Front panel switches, controls, and decoding circuits are on the FRONT PANEL assembly (A3). Low voltage power for the MODEM, CONTROL, FRONT PANEL, and CRT assemblies is obtained from regulators on the MODEM assembly (Al). High voltages and filament voltage for the CRT are obtained from the CRT assembly (A4). The CABINET assembly (A5) contains only the AC power input components, the power transformer, and the +5 volt regulator. With the exception of the CRT itself, all ST8000 circuits operate from supply voltages of +8 VDC (+V), -8 VDC (-V), (all analog circuits) and +5 VDC (all digital circuits).

2.2 MODEM ASSEMBLY A1 [6.3 through 6.26]:

The MODEM assembly is the lower of two large circuit boards in the right center section of the cabinet. It may accessed by removing the ST8000 top cover, three thumb-screws from the upper CONTROL assembly, and swinging the CONTROL assembly to a vertical position. Steps to obtain access to the MODEM assembly are described in detail in Section 2.1 of the ST8000 OPERATOR'S MANUAL.

2.2.1 INPUT FILTER [6.3, 6.4]:

Audio signals from the radio receiver are connected to the rear panel RCVR AUDIO connector (J12). The input characteristics may be set with option DIP switch S1-1 through S1-5 for 600 ohm or 8 ohm impedance, balanced or unbalanced or 5,000 ohms, unbalanced. The setting procedure is explained in Section 2.2 of the ST8000 OPERATOR'S MANUAL. Transformer T1 provides impedance matching and balanced-to-unbalanced transformation of the input signal. Input levels marked on the schematic diagrams assume a 2000 Hz, -10.0 dBm input signal.

860610

Input signals with levels greater than +12 dBm are clipped by diodes D69 through D71, providing input overload protection for the demodulator. Amplifier U50a provides input isolation and approximately 5 dB gain. Stage U50b is a two-pole active lowpass filter to prevent aliasing problems in following Switched Capacitor Filters (SCF's). TPl provides a test point for the input amplifier and low-pass filter performance.

Switches U51 and U44 provide electronic selection of one of four bandpass filters (U41, U42, U43, and U52). Switching of U51 and U44 is controlled by the microprocessor on the CONTROL assembly through J2-19 and J2-20.

Stages U41, U42, and U43 are monolithic integrated circuit Switched Capacitor Filters (SCF). Each contains a 6-pole Chebyshev Class II bandpass filter. The filters have the following fixed Q's:

| STAGE | BANDWIDTH  | Q   | IC TYPE      |

|-------|------------|-----|--------------|

| U41   | 1/3 OCTAVE | 4.5 | R5614/RF5614 |

| U42   | 1/2 OCTAVE | 3.0 | R5615/RF5615 |

| U43   | 1.0 OCTAVE | 1.5 | R5616/RF5616 |

The center frequency of each filter is controlled by the synthesized Input Filter Clock, supplied on J2-1 from the CONTROL assembly (A2). This clock frequency is nominally 54 times the desired Input Bandpass Filter center frequency. The selection of the filter and choice of the clock frequency is controlled by the microprocessor on the CONTROL assembly.

A fourth filter, U52, is much wider to allow processing of wide shift and high data rate RTTY signals. Section U52a is a twopole active low-pass filter with a cut-off frequency of 4200 Hz. Section U52b is a two-pole high-pass filter with an 380 Hz cutoff frequency. The two sections form a wide bandpass filter for signals between 380 and 4200 Hz.

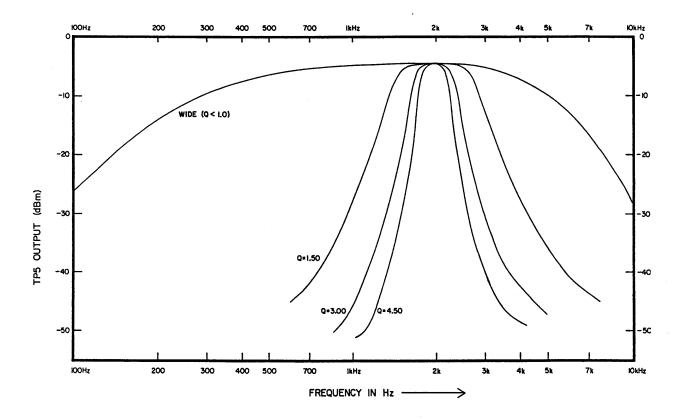

Stage U32 is a low-pass filter to remove all clock noise from the outputs of filter stages U41, U42, and U43. U32 also provides two additional poles of low-pass filtering for stage U52, increasing the skirt selectivity of the wide filter. Test points TP4 and TP5 allow monitoring of the signal output of the Input Bandpass Filter stages. Typical frequency response curves for the four input filters are shown in Figure 2.1.

FIGURE 2.1 INPUT BANDPASS FILTERS

# 2.2.2 LIMITER & AGC [6.5, 6.6]:

The signal from TP5 of the Input Bandpass Filter drives both a hard Limiter stage (U31) and an AM Automatic Gain Control (AGC) stage (U30, U21, U22, U13, and U3). The input levels to both stages are set for optimum dynamic range with dividers R187/R177 (Limiter) and R190/R184 (AGC).

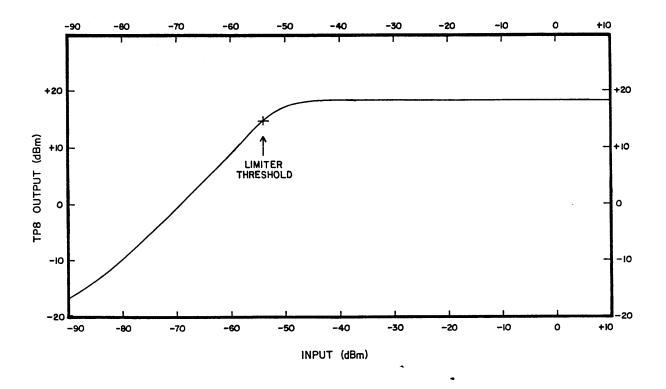

Limiter stage U31 is operated as a very high gain (>70 dB) compensated amplifier. The limiter threshold of U31 is typically -53 dBm, referred to the receiver input (J12). Control R182 is adjusted for symmetrical limiting on weak signals at TP6 or TP8. U23 is a two-pole anti-aliasing low-pass filter to prevent harmonics generated in the limiter from reaching the MARK and SPACE channel filters. Resistive divider R116/R96 sets the limited signal amplitude to be compatible with the output of the AGC amplifier. Typical limiter output vs receiver input level is shown in Figure 2.2.

FIGURE 2.2 LIMITER OUTPUT CHARACTERISTICS (TP8)

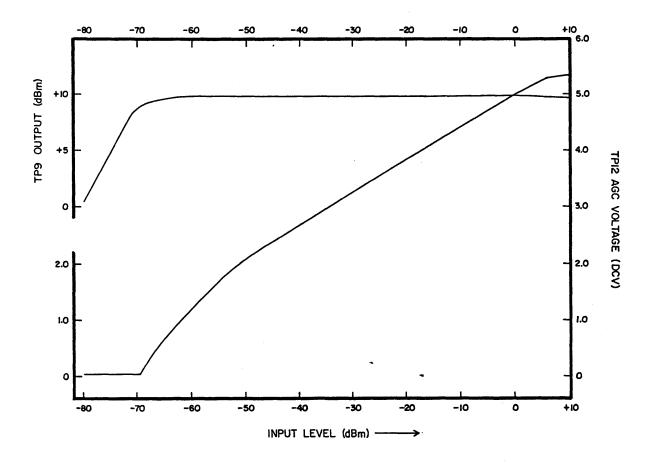

An AGC dynamic range of  $\pm 10$  to -65 dBm is obtained in stages U30, U21, U22, and U13. The total gain of amplifiers U30 and U22 is controlled by a DC voltage from the output of U21 (TPll). Stages and U13b provide gain and high-pass/low-pass U13a, U21a, filtering in the AGC loop. The output audio signal is detected in diodes D2 through D5. The approximate 3.0 volt drop in the diode chain sets the regulation voltage level output of the AGC system at +10.0 dBm. Amplifier U21b provides the amplifier feedback gain controlling voltage to U30 and U22 with time constant set by R104 and C46.

860610

#### TECHNICAL DESCRIPTION

Amplifier stages U3a and U3b condition the AGC voltage to be within the range of 0 to +5 VDC. The resulting output (TPl2) is used to drive the DIVERSITY selection circuits of two ST8000's in a two-channel diversity system. Control Rl02 is set for a reference voltage of 0.56 VDC at R3 and control Rl03 is set for +5.0 VDC at TPl2 with a 0 dBm receiver input signal on Jl2 [6.4]. Typical AGC voltage at TPl2 vs input signal level is shown in Figure 2.3.

FIGURE 2.3 AGC CHARACTERISTIC (TP4)

The output of the Limiter (from Rll6/R96) and AGC (TP9) stages are selected electronically by switch Ul4. This switch is controlled via J2-7 by the microprocessor on the CONTROL assembly (A2). The front panel DETECTOR MODE switch or REMOTE CONTROL commands select AM or FM mode.

860610

# 2.2.3 MARK AND SPACE FILTERS [6.7 - 6.10]

The MARK and SPACE discriminator filter stages are identical. Only the MARK circuit will be discussed with SPACE filter references in parenthesis ().

Stages U17a (U26a) and U17b (U26b) are cascaded two-pole SCF The center frequency of the filters is set by a filters. synthesized clock, whose frequency is nominally 50 times the desired center frequency. The clock signal is supplied via J1-20 from the MARK (SPACE) synthesizer on the CONTROL assembly (J2-5)(R124) allow (A2). Controls R85 (R123) and R86 precise adjustment of the center frequency of the filters, compensating for any variations in the clock-to-center frequency ratio of the SCF microcircuits. Stage U9 (U18) is a 2-pole low-pass filter to remove any residual clock noise from the filter output. Control R132 (R131) provides DC offset compensation of the output at TP46 (TP41).

The bandwidth of the MARK (SPACE) filter is controlled by (U24) and U7 (U33) in conjunction with resistor networks U15 resistors R94 (R95), R13 (R165), R81-R83 (R125-R128), R18 (R30), The shunt resistance to ground of U15 (U24) and and R19 (R31). U7 (U33) is controlled by switches U5 (U16) and U6 (U25). Α total of 16 different shunt resistances and therefore filter Q's may be selected with the 4-bit data input on J1-13,15,17, and 20 (J2-12, 14, 16, and 18). In addition, switches U2c (U2b) and U2d (U2a) provide selection between a HIGH and LOW range of Q-values with control input on J1-20 (J1-6). The effectively 5-bit line sets MARK (SPACE) Q values between 32.7 and 1.9 control as shown in the Table on Figure 6.8 (6.10). When used in the HIGH-Q range, stages Ul7a (U26a) and Ul7b (U26b) are both used as variable-Q, 2-pole filters. In the LOW-Q range, stage Ul7a (U26a) is used as a variable Q filter, but the Q of stage U17b (U26b) is fixed at Q = 1.00. Precision resistances are used for all Q-determining circuits and no Q adjustments are required. Typical HIGH-Q curves are shown in Figure 2.4 and LOW-Q curves in Figure 2.5.

FIGURE 2.5 MARK/SPACE FILTER - LOW-Q RANGE

860610

#### 2.2.4 MARK/SPACE DETECTORS & LP FILTERS [6.11, 6.12]:

The outputs of the MARK (TP46) and SPACE (TP41) filters drive identical but opposite polarity full-wave ideal-diode detectors (U10 and U37). These detector circuits have a dynamic range of greater than 40 dB, adding to the wide-dynamic range performance of the ST8000. Stages U10b and U37b serve the dual function of summing ports for the full-wave rectifier and low-pass filters to remove residual audio components from the rectified MARK and SPACE pulses.

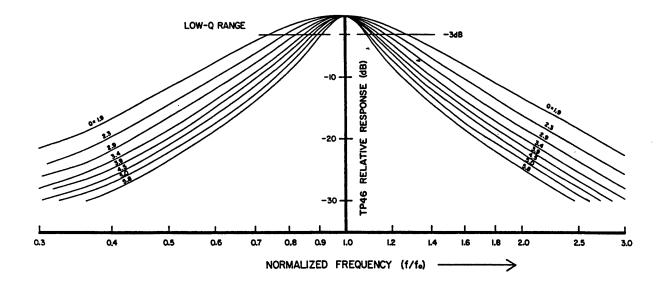

Stages Ull and U27 are identical 7-pole linear-phase SCF low-pass filters. The cut-off frequency of these filters is controlled by a synthesized clock whose frequency is 128 times the desired cut-The clock is obtained via J2-17 from а off frequency. synthesizer on the CONTROL assembly (A2). Stages Ul2 and U28 are 2-pole low-pass filters to remove any residual clock noise from low-pass filter output. Controls R65 and R68 are used to the compensate for DC offset at TP45 and TP37. Control R63 allows adjustment of the SPACE detected signal level so that MARK and The variable SPACE detected signal voltages may be balanced. low-pass cut-off frequency is normally set to 0.75 times the INPUT BAUD rate, but may be set to other values using the REMOTE CONTROL feature. The frequency response of the low-pass filter is shown in Figure 2.6.

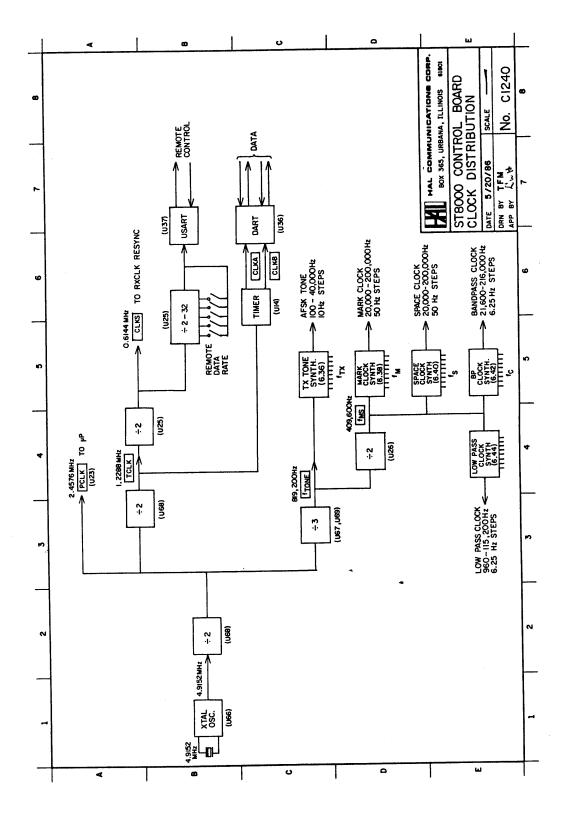

# 2.2.5 PULSE DETECTORS, PRINT SQUELCH, DMPC [6.13, 6.14]:

The outputs of the low-pass filters (TP45 and TP41) drive four different pulse detectors to provide MARK ONLY (MO), SPACE ONLY (SO), MARK/SPACE (M/S) and PRINT SQUELCH (+/+) outputs. In addition, the MO and SO outputs are combined to provide a Digital Multi-Path Correction (DMPC) output.

Figure 2.6 Low-Pass Filter Response

#### 2.2.5.1 MO/SO DETECTORS [6.13, 6.14]:

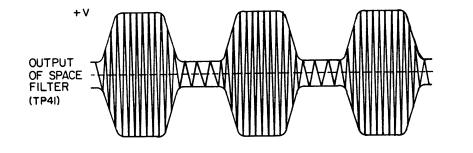

The MARK ONLY and SPACE ONLY detectors are identical except for diode and output pulse polarity. To simplify the explanation, the positive voltage pulse output of the SPACE detector will be described. Corresponding references to the MARK ONLY detector will be shown in parenthesis (#). Refer to Figure 2.7 for waveforms used in the following discussion.

FIGURE 2.7 SPACE ONLY DETECTOR WAVEFORMS

Circuit U28 (U12) forms the SPACE ONLY detector. Diode D53 (D12) peak detects the positive (negative) SPACE (MARK) pulse output, presenting a DC voltage proportional to the peak signal level at Diode D52 (D10) peak detects the (Ul2b). pin 5 of U28b between the data pulse and +V (-V), producing а difference voltage proportional to the amplitude of the "valley" between This voltage is applied to pin 10 of U28c SPACE (MARK) pulses. Stages U28b (U12b) and U28c (U12c) are isolation (Ul2c). used to prevent loading of the peak detected amplifiers, Resistors RI40 (R45) and RI39 (R46) present the midvoltages. voltage difference between the "peak" and "valley" values of the The pulse to the positive input of comparator U28d (U12d). detected SPACE (MARK) signal from TP37 is connected to original the negative input of U28d (U12d). The "sliced" and thresholdcorrected SPACE ONLY (MARK ONLY) signal is the output of U28d (U12d) at TP40 (TP44).

In this manner, a sliced +/- output is obtained from comparator U28d (U12d) using a reference that is proportional to the average mid-voltage between pulse maxima and minima. This technique prevents loss of data due to rapid signal fades and for high data conditions when MARK and SPACE filter bandwidths are so rate large that there is considerable filter output from the opposite channel signal. Diodes D28, D30, and D31 (D14, D18, D19) provide clamp on the magnitude of the "valley" voltage to prevent it а from rising to meet the peak value during extended periods of constant SPACE (MARK) condition. Time constants of the peak detectors are set to 200 ms, corresponding to typical HF RTTY signal fades. The time constant of the "valley" detector is set to 1 second to minimize biasing effects of "spike" noise.

The sliced SPACE ONLY output of U28d has a polarity of +V = SPACE signal present and -V = SPACE not present. The MARK ONLY output of Ul2d is +V = MARK signal present and -V = MARK not present. +/- voltages are converted to +5V logic levels These bv transistors in microcircuit U19. The SPACE ONLY (SO) output is further inverted in stage U49a. The resulting logic level outputs (U19, pin 2 and U49 pin 2) both have the polarity of +5V SPACE and OV = MARK. The MARK ONLY and SPACE ONLY detectors = should always be used with AM signal processing and are best used for OOK (ON-OFF KEYED) signals such as CW or when heavy interference blocks one data signal.

#### 2.2.5.2 M/S DETECTOR [6.13, 6.14]:

The outputs from the MARK (TP45) and SPACE (TP37) low-pass filters are of opposite polarity. These two signals are summed the input to U20a, a unity-gain inverting amplifier. The at resulting bipolar signal is coupled through the ATC (Automatic Threshold Correction) circuit (D20-23, C19-20, R48-49) to the input of the high gain comparator, U20b. The ATC circuit provides DC level restoration and balance, even when either the MARK or SPACE signal strength fades with respect to the other. The +/- output of U20b is converted to logic levels in transistor Ul9a, resulting in a signal polarity of MARK = 0V, SPACE = +5V. The MARK/SPACE detector gives consistent low-distortion data output for most signal conditions using either AM or FM The detector with AM processing is particularly processing. effective for recovery of weak signals with heavy differential MARK/SPACE fading.

#### 2.2.5.3 PRINT SQUELCH DETECTOR [6.13, 6.14]:

The opposite polarity MARK (TP45) and SPACE (TP37) signals are differentially summed in stage U29a, producing a voltage at TP38 that is positive if a signal is present at EITHER the MARK or If either MARK or SPACE is weaker or SPACE frequency. not present, the signal at TP38 will show variations at the data This +/+ signal is detected and filtered by D26, C21, rate. and R146 to give a slowly varying DC voltage, applied to pin 5 of When a valid MARK/SPACE RTTY signal is received, the U29b. voltage at pin 5 will be positive and at a maximum, non-varying If BOTH MARK and SPACE pulses are not presented in level. alternate fashion, the voltage at pin 5 will be lower than maximum and vary. Therefore, noise or signals in just one of the two MARK/SPACE channels will not produce a steady high-amplitude Also, if the RTTY signal is mistuned so that the tones voltage. do NOT match those of the MARK and SPACE filters, this voltage will also be low and vary.

The pin 6 input to comparator U29b is a voltage that is set by the front panel PRINT SQUELCH control. When the smoothed "+/+" voltage at pin 5 is greater than that on pin 6 from the PRINT SQUELCH control, TP39 (output of U29b) is positive, indicating PRINT ON condition. When the "+/+" voltage falls BELOW the PRINT SQUELCH value, TP39 swings rapidly negative to the NON-PRINT condition. Adjustment of the PRINT SQUELCH control adjusts the this threshold value. Since the absolute outputs of the MARK and SPACE filters do vary with selected filter Q, the optimum PRINT squelch setting will vary with data rate selected. The bipolar squelch signal at TP39 is converted to logic levels in transistor U19, producing the logic signal "SQA" (SQUELCH - CHANNEL A).

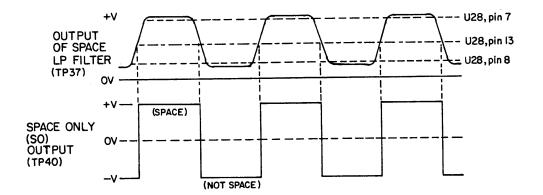

# 2.2.5.4 DMPC CIRCUIT [6.13, 6.14]:

logic-level outputs of the MARK ONLY and SPACE ONLY signals The are combined in stages U39a and U40 to provide correction for multi-path distortion of the RTTY signal. Multi-path propagation of an RTTY signal may cause differential fading or severe pulse In the case of differential fading, distortion of the signal. In use of AM and the M/S detector is usually adequate. the second case, the propagation path-lengths may be sufficiently different that the received composite signal has a noticeable time-overlap between MARK and SPACE pulse conditions. This pulse-overlap condition is corrected by the DMPC circuit. Refer to Figure 2.8 for the following explanation.

The MARK and SPACE ONLY signals are applied to XOR gate U39a, producing an output ONLY when the two signals are different. The two signals are then gated by U39a output (U40a,b) and applied to a set-reset flip-flop (U40c,d). The resulting output at TP49 will ONLY change states when there is no time-overlap between MARK and SPACE data. As shown in Figure 2.8, the resulting data signal is shifted in time by the amount of the overlap, but is NOT otherwise distorted with MARK or SPACE bias.

FIGURE 2.8 DMPC WAVEFORMS

# 2.2.5.5 DETECTOR MODE SELECT [6.13, 6.14]:

The outputs of the 4 data detectors - MARK ONLY (MO), SPACE ONLY (SO), MARK/SPACE ATC (M/S), and DIGITAL MULTI-PATH CORRECTION (DMPC) - are selected under processor control by switch stage U38. A two-bit control line from the control board (J2-9 and J2-10) sets the detector selection. Either the front panel DETECTOR MODE switch or a REMOTE CONTROL command are used to select the desired detector output and AM or FM processing. The two controls are normally inter-locked so that MO and SO modes are only available in AM mode. However, if DIRECT CONTROL (DC) mode is used with REMOTE CONTROL commands, each switch may be without inter-locking (see Chapter 3 of ST8000 OPERATO set OPERATOR'S MANUAL). The output polarity at TP34 is MARK = TTL logic high (>3.5 VDC) and SPACE = TTL logic low (< 0.45 VDC).

# 2.2.6 RX DATA CONTROL [6.15, 6.16]:

The outputs of several data and data control circuits are combined in the circuitry of Figure 6.16 to produce the data outputs to the TERMINAL DATA connector (J9). This circuitry includes selection of data polarity, Antispace, Print Squelch, Diversity data source, CRT trace ON/OFF, Printer Motor ON/OFF, and signals to drive various front panel indicators.

# 2.2.6.1 POLARITY, REGEN, ANTISPACE [6.15, 6.16]:

Stage U39b is used to provide front panel selection of data polarity. The front panel POLARITY switch controls BOTH receive and transmit data polarity to assure true transceive operation. If opposite receive/transmit polarities are required, this can be achieved by either programming different transmit and receive Mark/Space tones or by using RS232 for receive and MIL-188 or TTL I/O for transmit.

The receive data output of U39b is passed through the data Regeneration circuit on the CONTROL board (A2) via J2-4 and J2-2. NOTE: Jumper JP4 is used ONLY for test situations when the CONTROL board is NOT connected. This jumper should not be in place when the MODEM and CONTROL assemblies are connected together. The jumper pins do serve, however, as convenient test pins for REGEN data input/output.

The ANTISPACE circuit is enabled by the front panel ANTISPACE switch via J2-11. When enabled, the circuit tests for a long period of Space pulse condition (logic low at pin 7 of U49c). When the SPACE data condition persists for more than approximately 200 ms, the data output of U48a is forced to a continuous MARK condition (MARK-Hold). The ANTISPACE circuit has no effect when the front panel switch is OFF. 2.2.6.2 PRINT SQUELCH and DIVERSITY CONTROL [6.15, 6.16]:

Receive data from the control board REGEN circuit is passed through inverter U48c and gate U48a. As discussed above, the output of U48a is controlled by the Antispace circuit. In addition, a PRINT/NOT-PRINT signal is derived from Squelch and Diversity signals to also force the output of U48a to MARK-Hold whenever a valid signal is not detected.

The outputs of the Print Squelch circuit (SQA and NOT-SQA) [6.13, 6.14] are combined with outputs from the Diversity and AGC Squelch circuit (to be described in section 2.2.7). The combinational logic of stages U49b, U49d, U49e, U59, and U60 produce outputs to drive PRINT/NOT-PRINT gate U48a and Diversity selection gate U58.

When a single ST8000 is used in a non-diversity system, the diversity circuit serves as a signal-strength squelch, driven by the ST8000 AGC voltage. In this case, BOTH the Print Squelch (NOT-SQA) and Local Signal (SIGA) must be asserted for a PRINT condition to be passed to gate U48a. This condition also sets diversity gate U58c to pass receive data from the internal ST8000 to the data I/O interface amplifiers. If EITHER Print or AGC Squelch conditions are not positive, a NOT-PRINT condition is passed to U48a and the data output of the ST8000 is placed in MARK-Hold.

When two ST8000's are connected for diversity and both are turned ON, the Print Squelch Signals from both demodulators are compared with the DIVERSITY/NOT-DIVERSITY and A/B signals to produce the desired PRINT/NOT-PRINT and A/B control signals. In this case, if A channel (this ST8000) is selected AND NOT-SQA is low, data is passed through U48a and "A" channel is selected in U58. If NOT-SQA is high, U48a is placed in MARK-Hold. If B channel (other ST8000) is selected and NOT-SQB is low, data from the other ST8000 is selected and passed to the data output.

Automatic PRINT SQUELCH control of data flow may be over-ridden by SEL-CAL control (J1-7) from the CONTROL board (A2). The SEL-CAL feature is programmed using the REMOTE CONTROL feature of the ST8000. Note that SEL-CAL control will force the ST8000 print data circuits ON, but that OFF control is logically OR'ed with the internal sensing circuits.

#### 2.2.6.3 RXD I/O INTERFACE [6.15, 6.16]:

and U39 are I/O amplifiers used to convert the +5V Stages U57 logic data signals to the required I/O levels. The output of U57a produces RS232-C compatible bipolar signals (J9-3). This signal is -7 VDC for MARK and +7 VDC for SPACE. **U39d and U57b** provide MIL-188C compatible data output at J9-10, with levels of +7 VDC (MARK) and -7 VDC (SPACE). Stage U39c provides a TTLcompatible output signal at J9-16. Since both MARK/SPACE polarities are commonly used in various TTL-based data systems, either polarity may be selected with jumper JP2. The normal (N) polarity of the TTL output is for MARK = CMOS high logic level (>3.5 V) and SPACE = CMOS low logic level (<1.5 V). The input to all three data output amplifiers is obtained from the RXD ECHO circuit [6.19, 6.20]. Normally, this is simply the output of diversity gate U58a.

Stage U57c also provides an RS232-C Carrier-Detect (CD) output to J9-8. This output is high (+7 VDC) when EITHER Print Squelch or AGC Squelch conditions are active. It is low (-7 VDC) when BOTH conditions are not met. A TTL NOT-CD signal is also available on J9-21. This signal is low whenever Print Squelch is affirmative and is NOT controlled by AGC squelch. This output gives a rapidly switched ON/OFF Carrier Detect signal, useful for ARQ, Packet, and other burst-transmission modes.

# 2.2.6.4 MOTOR CONTROL [6.15, 6.16]:

The ST8000 does not include a high-voltage loop or provision for direct control of the AC power to a printer motor. However, these features are provided by the LP1200 Loop Power Supply option. An output is provided on J9-12 that may be used to drive a relay to switch printer motor power. Stage U35d and Q3 provide a delayed open-collector switch for relay control. The collector Q3 is in an ON state (low impedance to ground) when EITHER of Print Squelch or AGC Squelch are affirmative. Approximately 18 seconds after BOTH Print Squelch and AGC Squelch fail, the output of Q3 turns OFF (high impedance to ground). Q3 may be used to switch a positive voltage (<+50 VDC) to ground (current <+100 If two ST8000's are used in a diversity connection, the ma). printer motor output will remain ON whenever a valid signal is present from the selected demodulator output (A or B).

#### 2.2.6.5 CRT TRACE CONTROL [6.15, 6.16]:

The trace of the CRT Tuning Indicator is automatically controlled to prevent "burning" of the phosphor when no signals or a continuous MARK signal is received. In addition, the trace is automatically restored for approximately 10 seconds whenever any front panel switch or tuning adjustment is changed. Stage U60c the receive data output and turns the CRT trace OFF senses (through gate U59b) whenever a MARK condition longer than approximately 10 seconds occurs. Since the input to U60c is derived after the Antispace circuit, a long SPACE condition will also turn-off the CRT if ANTISPACE is turned ON. The CRT trace is also turned OFF whenever PRINT SQUELCH is OFF (output of An output from the CONTROL board (J1-5) forces the CRT U60d). trace ON whenever ST8000 tuning controls or switches are changed or when commanded by the REMOTE CONTROL CRT-ON command. External grounding of J9-25 turns the CRT trace OFF, over-riding ALL internal CRT trace control states. Similarly, grounding of J9-18 forces the CRT trace ON, regardless of internal control states.

2.2.6.6 INDICATORS [6.15, 6.16]:

Four front panel indicators are driven by this circuitry (MARK, SPACE, LOS, and PRINT). The MARK lamp signal indicates the data state of the output of U48a and therefore shows the effect on the signal of the ANTISPACE and PRINT SQUELCH circuits. The SPACE lamp indicates the data status of the I/O amplifiers. The SPACE lamp condition therefore reflects the data state of the selected diversity channel (A or B) as well as the data obtained from the RX ECHO circuit.

The PRINT lamp is ON whenever valid signals are to be printed. The PRINT lamp is used to set the threshold level of the PRINT SQUELCH control. The LOS lamp will be ON only when both Print Squelch and AGC Squelch fail. The LOS lamp indication is the complement of the RS232-C CD output (J9-8). 2.2.7 DIVERSITY AND AGC SQUELCH [6.17, 6.18]:

The AGC voltage output from U3b [6.4, 6.5] is used in both single-channel, non-diversity systems (one ST8000) and in twochannel diversity systems (two ST-8000's with Diversity cable). In a non-diversity system, the AGC voltage drives a signalstrength squelch circuit. When diversity is used, the AGC voltages of each demodulator are compared to determine channel selection.

NOTE: JP1 MUST be installed for a single-channel ST8000 to operate properly.

The AGC voltage from U3b [6.6] is connected through JPl to isolation amplifier U36a. The output of U36a drives one end of the front panel DIVERSITY potentiometer. When a second ST8000 is connected for diversity combination, its AGC voltage is buffered and inverted by stage U36b and applied to the other end of the DIVERSITY potentiometer. The wiper of the potentiometer then drives comparator stages U46a and U45a (diversity) or U46b and U45b (non-diversity).

2.2.7.1 NON-DIVERSITY SQUELCH [6.17, 6.18]:

a second ST8000 is not connected to J10, the DIVERSITY rear If panel connector, or is connected AND turned OFF, the zero voltage from J10-9 is sensed by U47a, setting the output high (NOT-DIV at Q2 then turns ON and biases U36b to produce a constant TP33). negative voltage at TP35. The DIVERSITY potentiometer therefore becomes a level control for only the AGC voltage of the local ST8000 (AGC-A). Stages U46b and U45b then serve as an integrating threshold detector for the non-diversity condition. The switch threshold at TP23 is at approximately zero volts and is proportional to the difference between the AGC-A voltage and the negative bias at TP35. Therefore, adjustment of the DIVERSITY control changes the amount of AGC-A voltage required to produce a negative-to-positive transition at TP23. The switch time constant for signal/no-signal non-diversity operation is approximately 0.1 second for signal acquisition and 1.0 second signal loss. U45b is a high-gain threshold detector for and transistor U53b performs the required bipolar to TTL level conversion.

# 2.2.7.2 DIVERSITY MODE [6.17, 6.18]:

When two ST8000's are connected for diversity AND both units are turned ON, the presence of a positive voltage at AGC-B (J10-9)sets U47a to the DIV state (TP33 to negative level). This turns Q2 OFF and allows U36b to act as an inverting buffer for the Since the two AGC voltages are applied with AGC-B voltage. inverse polarities to either end of the DIVERSITY control, the wiper setting is proportional to the voltage difference. As in the non-diversity case, the threshold point occurs when the voltage at TP23 passes through zero volts. A negative voltage at TP23 causes selection of channel B (other ST8000) and a positive Changing the voltage corresponds to selection of the A channel. DIVERSITY control therefore sets the ratio of the two voltages required to produce the zero-voltage switch condition.

Stages U46a and U45a are the integrating threshold detector for diversity operation. U46a and its diode bridge (D42-D45) form a dual-gain amplifier. For input voltages less than +/- 0.2 volts, the gain is low (approximately 1/3). When the input voltage these limits, the voltage gain is increased to exceeds The output of U46a drives the bipolar approximately 5. integrator R206/C72/C73 with a time constant of approximately 1 If the difference between the A and B channel AGC second. TP23 is high, the gain of U46a is also high and voltages at C72/C73 are rapidly charged. As the capacitor voltage passes through zero volts, threshold detector U45a provides a rapid channel switch. If the difference between AGC voltages at TP23 low, U46a gain is low and change in the C72/C73 capacitor is voltage is much slower. This dual time-constant effect thus prevents "chatter" or "hunting" effects of rapid back-and-forth channel switching which might otherwise occur on two slowly varying signals. However, if one signal undergoes a rapid change (such as in a deep prolonged fade), the higher gain condition of U46a takes over and the data is rapidly switched to the other Stage U53a provides level conversion from bipolar to channel. TTL levels. Gate U34 is driven by the two threshold detectors the DIV/NON-DIV output of U47a to provide the required A/B and channel switch signal for U58 [6.15, 6.16].

Front panel indicator A is ON whenever the local signal is present and selected. Indicator B will be ON only when DIV mode is selected AND B channel is selected. The B indicator will not turn ON when a single channel (non-diversity) system is used. This section of the ST8000 includes I/O interface drivers for RS232-C, MIL188C, or TTL data input, transmit-receive PTT control, receive and transmit data ECHO control, transmit data to the AFSK oscillator, and FSK output signals.

## 2.2.8.1 TXD I/O INTERFACE [6.19, 6.20]:

Transistors Q5 and Q6 and gates U54a and U54b provide I/Ointerface for three different data I/O electrical interfaces. RS232C TXD signals from J9-2 are sensed and converted to +5 volt logic levels by Q6. The required input signal levels are: SPACE >1.2 VDC, MARK < 0.6 VDC. The input signal may be either bipolar or positive within these limits. The MIL188C (J2-9) and TTL (J2-14) inputs have the same voltage limitations, but include an additional inversion. Note that ONLY one of the three possible inputs may be used at a time. The output of the TXD I/O circuits drives the REGEN circuit on the CONTROL circuit board (A2) test through J1-1 and J1-2. Jumper JP3 is provided ONLY for conditions when the MODEM and CONTROL boards are not connected. JP3 should be OMITTED whenever the two boards are connected.

# 2.2.8.2 TX/RX PTT CIRCUIT [6.19, 6.20]:

The ST8000 includes a relay that is used to switch the radio system from receive to transmit condition. This is normally accomplished by switching the transmitter push-to-talk (PTT) circuit to ground to transmit. The PTT relay may be controlled from several sources: (1) Front Panel PTT switch, (2) internal Keyboard Operated Switch (KOS) automatic circuit, (3) by an external switch to ground (TERMINAL KOS), and (4) by the RS232C RTS (Request To Send) signal.

The ST8000 Keyboard Operated Switch (KOS) circuit is made up of stages U63, U56a, and U64a. Automatic send-receive control is achieved by sensing the state of the input transmit data (TXD). U63b, U56a, When a Mark-to-Space transition is detected, U63a, The ON condition and U64a produce a transmit ON condition. continues until after an adjustable delay following the last data This delay is controlled by timer stages U63e and transition. U64a and is adjustable from 1-10 seconds with control R226 The time delay may be increased to (factory set at minimum). compensate for extended periods between TXD pulses, particularly when hand-typing data. A rapid return to receive, over-riding the delay, is available if the transmit data source is held in SPACE condition for longer than 0.5 second (U63c and U63d).

The front panel PTT switch and stages U56b and U64b allow selection of either receive only (RX), Keyboard Operated Switch (KOS), or continuous transmit (TX) conditions. The automatic KOS circuit may only be used when this switch is in KOS position.

#### TECHNICAL DESCRIPTION

Two external control signals may also be used to set transmit mode, Terminal KOS and RS232C RTS. If the Terminal KOS (J9-19) input is grounded, the PTT relay is switched to TX-ON condition. When RTS input (J9-4) is driven to greater than +3 VDC, TX-ON condition is set. Both TERMINAL KOS and RTS inputs over-ride the RX or KOS positions of the PTT front panel switch. The TERMINAL KOS input is commonly used with the KOS and KY outputs of the DS3100 terminal to provide compatible transmit/receive switching.

The front panel TX lamp is ON whenever the ST8000 PTT relay is in TX condition. Option switch S4-5 also allows ON/OFF control of the AFSK tones by the PTT circuit. When this switch is ON (factory setting), AFSK tone output is produced only when the ST8000 is in TX state. If S4-5 is set OFF, the AFSK tone output is always ON, regardless of ST8000 PTT state.

# 2.2.8.3 ECHO CONTROL [6.19, 6.20]

Gates U54c, U54d and U55 allow selection of data sources to drive both the AFSK tone generator, FSK Output, and RXD output to the data terminal. Option switch S3-1 through S3-5 allows choice of normal full- and half-duplex options. The S3 Factory setting is: S3-1 and S3-5 ON, S3-2, S3-3, and S3-4 OFF. This is the recommended setting for a full-duplex (FDX) system such as the DS3100 terminal. Note that BOTH S3-1 and S3-2 should NOT be set ON at the same time. Similarly, only one of the S3-3, S3-4, and S3-5 switch sections may be set ON at a given time.

# 2.2.8.4 AFSK AND FSK DATA OUTPUT [6.19, 6.20]:

Transmit data output from the echo circuit is set to either polarity by the front panel switch and stage U62a. This polarity is matched to that of the receive data as discussed in section 2.2.6. The output signal is used to drive the AFSK Mark/Space switch on the control board through J1-11.

The transmit data output also drives the FSK output circuit of stages U62b and Q7. Option switch S4-1 through S4-4 allows choice of the level and polarity of the FSK output signal. The S4 Factory setting is S4-2 and S4-3 ON, producing a +5 VDC output on MARK and 0 volts on SPACE transmit data conditions.

# 2.2.9 AFSK OSCILLATOR [6.21, 6.22]:

The setting of MARK and SPACE transmit tone frequencies is controlled by the synthesizer on the CONTROL board (J2-6). The synthesized signal at 10 times the output frequency drives U61, a ten-step sine-wave synthesizer. The resulting stepped-waveform is filtered and smoothed in amplifier/low-pass filter stages U65a Rear panel control R295 sets the output level of the and U65b. Transformer T2 and option switch S2 allow AFSK tone signal. setting of two AFSK levels and choice of balanced or unbalanced Switch S2-5 also allows connection of the FSK rather output. than AFSK signal to the rear panel XMTR connector (Jlla). The PTT relay is also connected to Jlla. The factory setting for S4 is for 600 ohms, unbalanced with the level set for 0 dBm (S4-1, S4-2, and S4-4 ON; S4-3 and S4-5 OFF). If FSK output is desired, set S4-1, S4-4, and S4-5 ON and S4-2 and S4-3 OFF.

# 2.2.10 POWER SUPPLY [6.23, 6.24]:

With the exception of the high voltages and filament voltage for the CRT, all other operating voltages for the ST8000 are obtained from the modem board power supplies. The ST8000 uses +8 VDC (+V) and -8 VDC (-V) for all analog circuitry and +5 VDC for all digital and display circuits. Standard three-terminal integrated circuit regulators are used for all three supply voltages. The +8 and -8 volt regulators (U67 and U66) are mounted on the MODEM board and bolted to the rear panel for heat conduction. The +5 volt regulator (LM323) is part of assembly A5-REG (960-08309), mounted directly to its heat sink on the rear panel.

All operating voltages, including those for the CRT are obtained from the power transformer mounted in the left rear section of the cabinet. The transformer primary may be connected for either 100-130 VAC or 200-260 VAC power line input. Power line frequencies between 44 and 440 Hz may be used. Both sides of the AC power input are filtered to prevent RFI to or from the ST8000. Both power wires are switched by the AC POWER switch on the ST8000 front panel.

# 2.2.11 MODEM ASSEMBLY INTERCONNECTIONS [6.25, 6.26]:

interconnections between the MODEM assembly (Al) and other A11 assemblies or external connectors are shown in Figure 6.26. The connector numbers correspond to those on the schematic diagrams and on the screened markings on the circuit board itself. In corresponding addition, page references are given to the schematic diagram title-block page for each signal. Arrows on the signal lines indicate the predominate direction of signal flow with respect to the connector on the MODEM board.

#### 2.3 CONTROL ASSEMBLY (A2) [6.27 - 6.46]:

The ST-8000 Control Board is a Z80A (or equivalent) based microprocessor system with 16K bytes of firmware EPROM memory and 2K bytes of battery backed up RAM memory. This processor controller polls the front panel switches and tuner and tests for changes, refreshes the front panel seven segment LED displays, generates the Modem Board filter oscillators, and sets various internal operational latch bits. In addition, all serial control port communication and terminal serial transmit and receive data regeneration is controlled by the Control Board microprocessor system.

In the following sections detailed descriptions of the Control Board circuitry are presented. References are made to the schematic diagrams located in Volume II of this Technical Manual; having that volume handy will aid understanding.

#### 2.3.1 Microprocessor Controller [6.27, 6.28]:

The ST-8000 Control Board uses a conventional dedicated single microprocessor design architecture with 16K bytes EPROM and 2K bytes of RAM memory (see Figure 6.28). The Z80A microprocessor uses a 2.4576 MHz clock (PCLK) derived from the 4.9152 MHz common system clock illustrated in Figure 6.34 for a cycle time of 407 ns. The Control Board uses both memory mapped and IO port mapped buffers and latches as shall be discussed in subsequent sections. The microprocessor operates with no wait states.

The Z80A has two interrupt sources: the serial channel controller (INT) and the refresh timer (NMI) illustrated in Figure 6.32. The RESET signal is generated by a "deadman" timer and power on circuit illustrated in Figure 6.30.

Note the 10K pullup resistors on U23-16, -21, and -22, in Figure 6.28. These resistors hold the -WR (NOT-WR signal) and -RD (NOT-RD) lines high when the processor is in the RESET or power on condition where these lines may be in the high impedance tristate condition. Without the pullup resistors, a -WR signal might cause a false memory write signal into the battery backup RAM parameters corrupting stored data.

Two pullup resistors are included on the -BUSREQ and -WAIT inputs to hold these inputs high. Since all components on the processor board operate full speed, there is no need for a processor wait signal. -BUSREQ is used only in DMA or multi-processor application, thus that input is held high in the ST-8000.

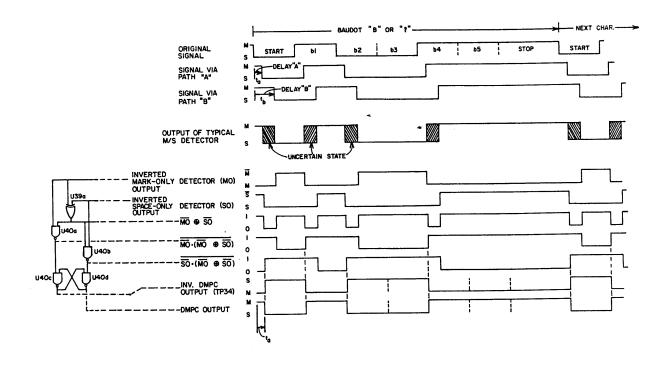

Figure 2.9 Clock Distribution

## 2.3.2 System Clocks [6.33, 6.34]:

The entire Control Board operates with a single crystal clock as shown in Figure 2.9, a block diagram of the clock distribution in the ST-8000. Since all timing signals are based on the same crystal oscillator, all clocks remain as stable as the crystal reference.

As illustrated Figure 6.34, two sections of U66 form a 4.9152 MHz crystal oscillator with a buffered output on U66-8. A D-type flip-flop, U68, divides this clock output by 2 to produce PCLK, a 50% duty cycle square wave 2.4576 MHz (406.9 ns) processor clock and synthesizer reference clock.

The processor clock, PCLK, is buffered once again by U49 in Figure 6.28 since the clock input to the Z80A requires a 330 ohm pullup resistor to +5 volts. This same clock output from U49-2 provides the system timing clock for the regeneration dual serial receiver/transmitter (DART) chip, U36-20, in Figure 6.32.

The frequency synthesizers require two reference timing clocks; FTONE at 819,200 Hz (1.22 us) and FMS at 409,600 Hz (2.44 us). PCLK is divided by 3 with the dual D flip-flop U67 and one gate from U69. U67-5 and U67-9 form a 2 bit ripple counter triggered by the rising edge of PCLK on U67-3. When the count reaches 3, both U67-5 and U67-9 are high, U69-11 goes low resetting the count to 0. Thus, U67-9 has a period of three cycles of PCLK and a frequency of 819,200 Hz. FTONE is not a 50% duty cycle waveform; it is low for two cycles (813.8 ns) and high for one cycle (406.9 ns) of PCLK.

The FMS timing signal is generated by dividing FTONE by 2. U26, a D flip-flop, uses FTONE as an input on U26-11 and generates the 409,600 Hz (2.44 us) timing signal on U26-9. FMS is a 50% duty cycle waveform.

2.3.3 RESET and Sanity Timer [6.29, 6.30]:

The RESET and Sanity Timer circuit is found in Figure 6.30. The sanity timer is used to reset the ST-8000 processor when an operational glitch has occurred.

When the power is first turned ON, capacitor C26 is fully discharged so the voltage across the capacitor is close to 0 volts. With U71-11,12 low, the output of the invertor on U71-13 will be high which holds the four bit decade counter U70 output set to 9. The high level inputs on U71-5,6 drive U71-4 low which holds the -RESET (U71-4) line low, and RESET (U71-1) high. As long as the -RESET line is low, the Z80A microprocessor is held in the reset state. As soon as C26 charges to about 2.4 volts through R7, U71-13 will go low releasing the set to 9 input on U70. U69, an astable multivibrator oscillator, generates a timing clock input for the decade counter on U70-10. Once U71-13 goes low, the counter will begin to count up on the next falling edge of U69-3. This next clock edge will increment the counter to a count of 0 so that both U71-5 and U71-6 are low resulting in U71-4 going high and Thus, -RESET goes high and RESET goes low allowing U71-1 low. the microprocessor to start.

During operation, the firmware periodically writes the memory address E007H to reset the decade counter to zero. A write to that location pulses U2-7 low and U71-10 high, resetting the U70 counter (DEADT). Since the U69 timer continues to run, U70 will keep trying to count up. If the DEADT signal does not pulse low before counter U70 reaches a count of 8, U70-8 will go high which causes U71-4 to go low resulting in a processor reset signal.

The frequency of U69-3 is not critical; the components shown yield a frequency of about 60 Hz (17 ms). When the ST-8000 is idle and no front panel switches are changed, the DEADT counter reset signal has a frequency of about 2240 Hz (446 us). Note, however, that the period of this waveform is dependent on what specific tasks the processor is performing at the time and it will vary greatly. In no case should the U70 counter cause a system reset unless a glitch has occurred.

#### 2.3.4 Memory and I/O Map [6.27 - 6.30]:

The control board uses both memory and I/O port mapping for the system memory, control bits, and peripheral interface devices. Listed below are the board addresses and the specific function associated with each address.

Memory addresses are decoded by U3, U4, and U24. I/O port addresses are decoded by U9. All addresses below are in HEX.

MEMORY ADDRESS MAP

\_\_\_\_\_\_

#### ADDRESS DESCRIPTION

0000H - 1FFFH U10; 2764 firmware EPROM 0, read only 2000H - 3FFFH Ull; 2764 firmware EPROM 1, read only 4000H - 5FFFH Ul2; (not installed) U13; 2K x 8 battery RAM, read/write 6000H - 6800H U3; Synthesizer control (see below) 8000H - 8007H U4; Synthesizer control (see below) A000H - A007H E000H - E007H U2; Sanity Timer and Modem Latch (see below) ¥

#### MEMORY MAPPED CONTROL REGISTERS

\_\_\_\_\_

| ADDRESS | DESCRIPTION                                     |  |  |

|---------|-------------------------------------------------|--|--|

| 8000H   | U3-15; MARK transmit tone, low byte             |  |  |

| 8002H   | U3-13; SPACE transmit tone, low byte            |  |  |

| 8003H   | U3-12; MARK/SPACE transmit tone, high nibbles   |  |  |

| 8004H   | U3-11; MARK filter synthesizer, low byte        |  |  |

| 8006H   | U3-9; SPACE filter synthesizer, low byte        |  |  |

| 8006H   | U3-7; MARK/SPACE filter synth., high nibbles    |  |  |

| A000H   | U4-15; Band pass filter synthesizer, low byte   |  |  |

| A001H   | U4-14; Band pass filter synthesizer, high byte  |  |  |

| A002H   | U4-13; Low pass filter synthesizer, low byte    |  |  |

| A003H   | U4-12; Low pass filter synthesizer, high byte   |  |  |

| A004H   | U4-11; Front panel, Baud Rate digits (DS2)      |  |  |

| A044H   | U4-11; Front panel, MARK digits (DS0)           |  |  |

| A005H   | U4-10; Front panel, Common Cathode select (DS3) |  |  |

| A045H   | U4-10; Front panel, SPACE digits (DS1)          |  |  |

| A006H   | U4-9; MARK/SPACE filter Q select low nibbles    |  |  |

| A007H   | U4-7; Modem control register                    |  |  |

| E000H   | U2-15; Modem board options                      |  |  |

| E007H   | U2-7; Sanity timer                              |  |  |

I/O PORT ADDRESS MAP

\_\_\_\_\_\_

| ADDRESS | DESCRIPTION                          |  |  |

|---------|--------------------------------------|--|--|

|         |                                      |  |  |

| 00H     | U9-12; Front panel switch input 0    |  |  |

| 04H     | U9-13; Front panel switch input l    |  |  |

| 08н     | U9-14; Front panel switch input 2    |  |  |

| ОСН     | U9-15; Front panel switch input 3    |  |  |

| 10H     | U9-11; Refresh timer enable latch    |  |  |

| 14H-17H | U9-10; Baud rate and refresh timer   |  |  |

| 18H-1BH | U9-9; Regeneration serial controller |  |  |

| 1CH-1DH | U9-7; Command port serial controller |  |  |

#### 2.3.5 EPROM and RAM Memory [6.27, 6.28]

The ST-8000 memory address map is presented below:

MEMORY ADDRESS MAP