# 8-Bit MCU with 1Kx16 (ECC) SRAM and 16Kx16 (ECC) E-Flash

## **GENERAL DESCRIPTION**

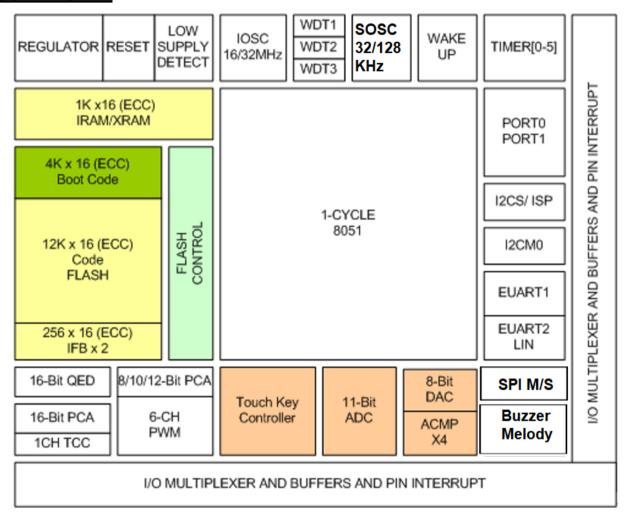

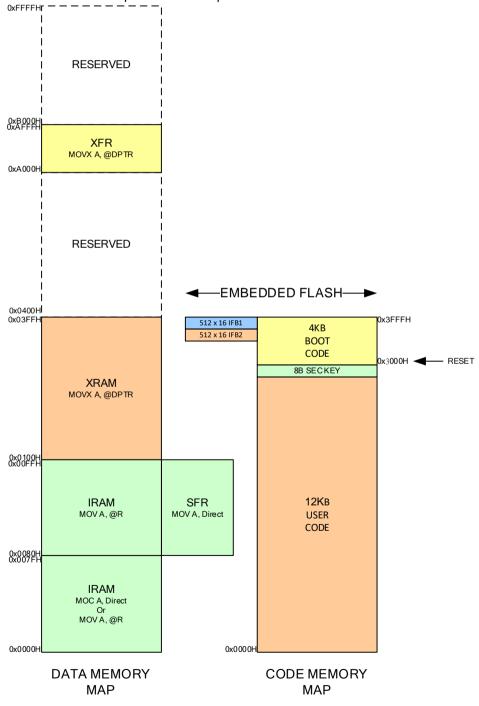

CS8975 is a general-purpose MCU with 16KB Code e-Flash memory with ECC and 1K SRAM with ECC. The embedded flash for code storage has built-in ECC that corrects 1-bit error and detects two-bit errors. CPU accesses the e-Flash through address read and through Flash Controller which can perform software read/write operations of e-Flash.

CPU in CS8975 is a 1-T 8051 with enhanced multiplication and division accelerator. There are three

clock sources for the system, one is a 16MHz/32MHz IOSC (manufacturer calibration +/- 2%), another is XCLK, and the other one is SOSC32KHz (typical 32KHz) which is divided from an internal slow oscillator. ALL clock sources have a clock programmable divider for scaling down the frequency to save power dissipations. The clock selections are combined with flexible power management schemes, including NORMAL, IDLE, STOP, and SLEEP modes to balance speed and power consumption.

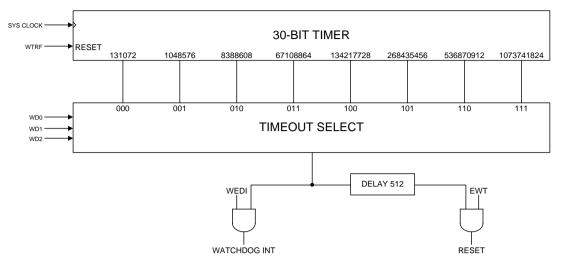

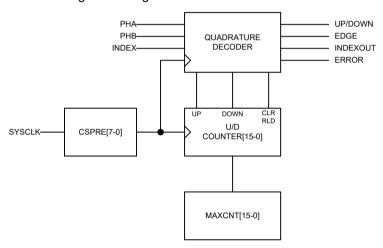

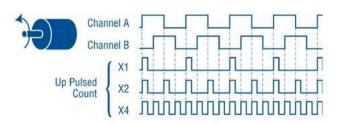

There are T0/T1/T2/T3/T4/T5 timers coupled with CPU and three WDT where WDT1 is clocked by SYSCLK, and WDT2/WDT3 are clocked by a non-stop SOSC32KHz. An 8-bit/16-bit checksum and 16-bit CRC accelerator is included. There are EUART/LIN controller, I<sup>2</sup>C master/Slave controller and SPI master/slave controller. The interfaces of these controllers are multiplexed with GPIO pins. Other useful peripherals include a buzzer control, 6 channels of 12-bit PWM, one channel of 16-bit timer/capture and quadrature decoder.

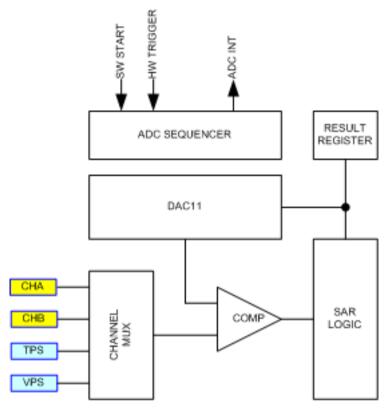

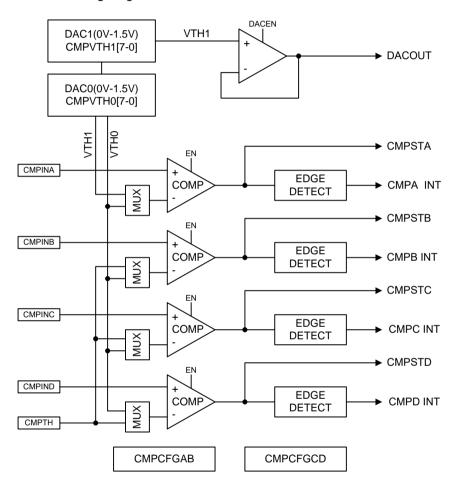

Analog peripherals include an 11-bit ADC with an internal temperature sensor, an 8-bit voltage output DAC, and four analog comparators with a programmable threshold. A touch key controller with up to 20-bit resolutions is also included. The touch key controller also has shield output capability for moisture immunity. The touch key controller allows sleep mode (under 10uA) and uses auto-detection for wakeup. The maximum number of sensor keys is 11. CS8975 can support passive proximity sensing.

CS8975 also provides a flexible method of flash programming that supports ISP and IAP. The protection of data loss is implemented in hardware by access restriction of critical storage segments. The code security is reinforced with sophisticated writer commands and ISP commands. The on-chip breakpoint processor also allows easy debugging which can be integrated with ISP. Reliable power-on-reset circuit and low supply voltage detection allow reliable operations under harsh environments.

#### **APPLICATION**

- Touch key applications with high robustness and reliability requirements

- Automotive, Industry and Appliance

### **FEATURE**

## **CPU and Memory**

- 1-Cycle 8051 CPU core up to 32MHz

- 16-bit Timers T0/T1/T2/T3/T4 and 24-bit T5

- Checksum and CRC accelerator

- WDT1 by SYSCLK, WDT2/WDT3 by SOSC32KHz

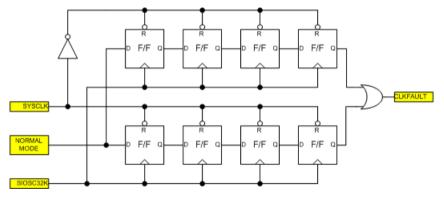

- Clock fault monitor

- All GPIO pins can be assigned to two external interrupts

- Power-saving modes IDLE, STOP, and SLEEP

- 256B IRAM and 768B XRAM with ECC check

- 16KB Code e-Flash with ECC and two 512x16 Information Block

- Program read with hardware ECC

- 16-bit software read/write direct access

- Code security and data loss protection

- 100K endurance and 10 years retention

## **Clock Source**

- Internal oscillator at 16MHz/32MHz +/- 2%

- Spread Spectrum option

- Internal low power oscillator 128KHz

- External clock option

#### **Digital Peripheral**

■ 6 CH 8/10/12-bit center-aligned PWM controller

- Trigger interrupt and ADC conversion

- Output polarity control

- One 16-bit Timer/Capture and One 16-bit quadrature decoder

- Buzzer/Melody generator

- One I<sup>2</sup>C Master

- One I<sup>2</sup>C Slave also for ISP and debug

- One SPI Master/Slave Controller

- One EUART1 and one EUART2/LIN

#### **Analog Peripheral**

- Capacitance sense touch-key controller with scan up to 11 key inputs

- Shield output for moisture immunity

- Low power sleep mode wakeup (<5uA).

- 11-Bit SAR ADC with GPIO analog input

- Temperature sensor and voltage supply measurement

- 8-Bit DAC and four analog comparators

- Power-on reset and Low voltage detect (2.3V-4.5V)

#### **Miscellaneous**

- Up to 12 GPIO pins with multi-function options

- 2.3V to 5.5V single supply

- Active current < 150uA/MHz in Normal mode

- Low power standby (< 1uA) in SLEEP mode

- Operating temperature -40°C to 125°C

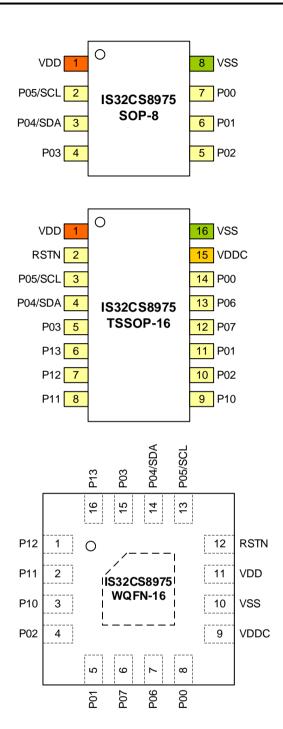

- SOP-8, TSSOP-16 and wettable flank QFN-16 (WQFN-16) package

- RoHS & Halogen-Free compliant

- TSCA compliance

- AEC-Q100 qualification

## **BLOCK DIAGRAM**

# **PINOUT**

# **Table of Contents**

| 1.  | PIN Description and Multifunction Table         |                                                                      |          |  |  |  |  |

|-----|-------------------------------------------------|----------------------------------------------------------------------|----------|--|--|--|--|

| 2.  | Memo                                            | ry Map                                                               | 3        |  |  |  |  |

| 3.  | 8. REGISTER MAP SFR (0x80 – 0xFF)               |                                                                      |          |  |  |  |  |

| 4.  | TA protected REGISTER MAP XFR (0xA000 – 0xAFFF) |                                                                      |          |  |  |  |  |

| 5.  | 8051 CPU                                        |                                                                      |          |  |  |  |  |

|     | 5.1                                             | CPU Register                                                         |          |  |  |  |  |

|     | 5.2                                             | Addressing Timing and Memory Modes                                   |          |  |  |  |  |

|     | 5.3<br>5.4                                      | MOVX A, @Ri Instructions                                             |          |  |  |  |  |

|     | 5. <del>4</del><br>5.5                          | Interrupt System                                                     |          |  |  |  |  |

|     | 5.6                                             | Register Access Control                                              |          |  |  |  |  |

|     | 5.7                                             | Clock Control and Power Management Modes                             | 15       |  |  |  |  |

|     |                                                 | 5.7.1 IDLE Mode                                                      |          |  |  |  |  |

|     |                                                 | 5.7.2 STOP Mode                                                      |          |  |  |  |  |

|     |                                                 | 5.7.4 Clock Control                                                  |          |  |  |  |  |

|     | 5.8                                             | Watchdog Timer                                                       | 17       |  |  |  |  |

|     | 5.9                                             | System Timers – T0 and T1                                            |          |  |  |  |  |

|     |                                                 | 5.9.1 Mode 0                                                         |          |  |  |  |  |

|     |                                                 | 5.9.3 Mode 2                                                         |          |  |  |  |  |

|     |                                                 | 5.9.4 Mode 3                                                         |          |  |  |  |  |

|     | 5.10                                            | System Timer – T2                                                    |          |  |  |  |  |

|     | 5.11<br>5.12                                    | System Timer – T3 and T4                                             |          |  |  |  |  |

|     | 5.12                                            | System Timer – T5                                                    | 20<br>27 |  |  |  |  |

|     | 0.10                                            | 5.13.1 Division – 32-bit divide by 16-bit or 16-bit divide by 16-bit | 29       |  |  |  |  |

|     |                                                 | 5.13.2 Multiplication – 16-bit multiply by 16-bit                    | 29       |  |  |  |  |

|     |                                                 | 5.13.3 Normalization – 32-bit                                        |          |  |  |  |  |

|     |                                                 | 5.13.4 Shift – 32-bit                                                |          |  |  |  |  |

|     | 5.14                                            | I <sup>2</sup> C Master                                              |          |  |  |  |  |

|     | 5.15                                            | Checksum/CRC Accelerator                                             |          |  |  |  |  |

|     | 5.16                                            | Break Point and Debug Controller                                     |          |  |  |  |  |

|     | 5.17                                            | Debug I <sup>2</sup> C Port                                          | 37       |  |  |  |  |

|     | 5.18<br>5.19                                    | Data SRAM ECC Handling                                               |          |  |  |  |  |

|     | 5.20                                            | Memory and Logic BIST Test.                                          |          |  |  |  |  |

|     | 5.21                                            | System Clock Monitoring                                              |          |  |  |  |  |

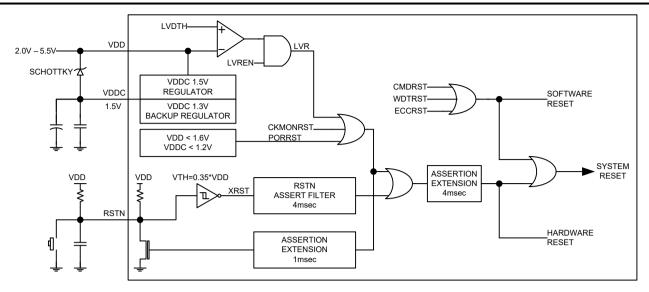

|     | 5.22                                            | Reset                                                                |          |  |  |  |  |

| 6.  | Flash                                           | Controller                                                           | 42       |  |  |  |  |

| 7.  | I <sup>2</sup> C SI                             | ave Controller 2 (I2CS2)                                             | 46       |  |  |  |  |

| 8.  | EUAR                                            | T1 Enhanced Function UART1                                           | 49       |  |  |  |  |

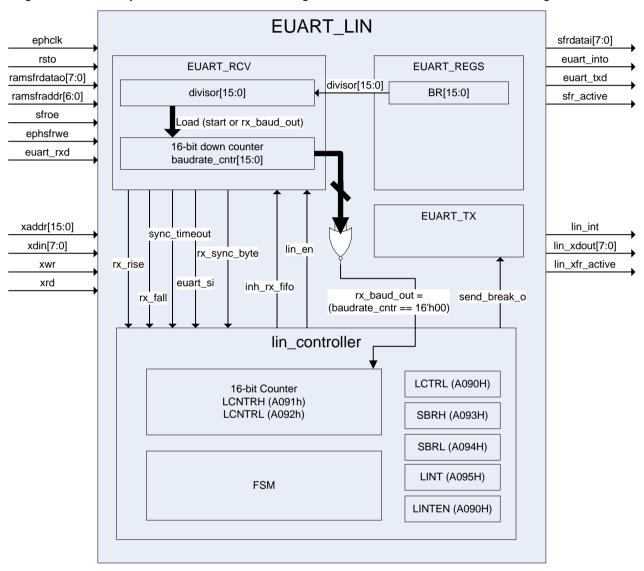

| 9.  | EUAR                                            | T2 with LIN Controller                                               | 53       |  |  |  |  |

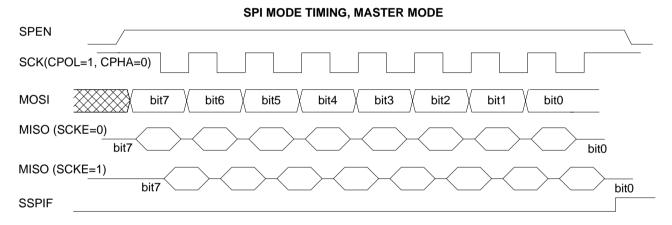

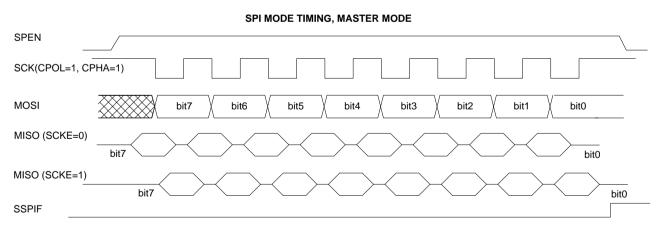

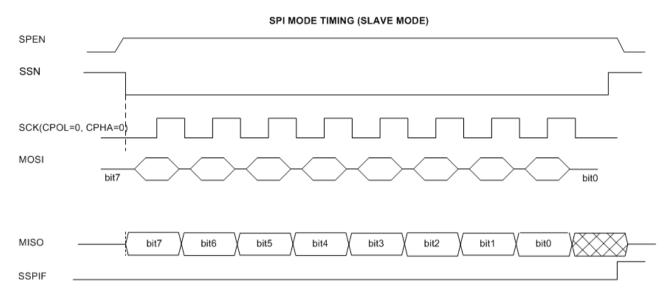

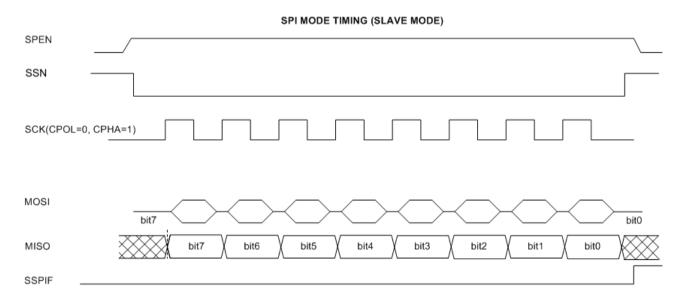

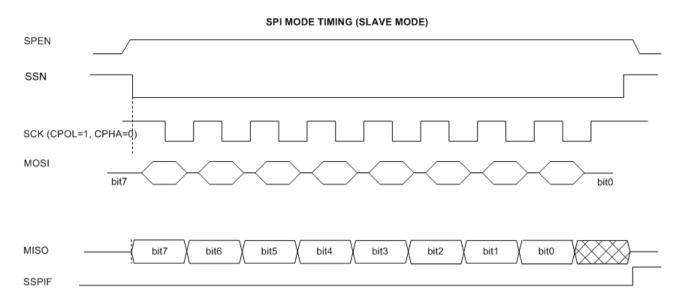

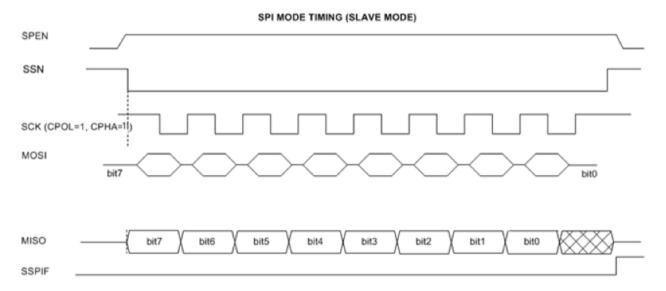

| 10. | Serial                                          | Peripheral Interface (SPI)                                           | 62       |  |  |  |  |

|     |                                                 | SPI Master Timing Illustration                                       |          |  |  |  |  |

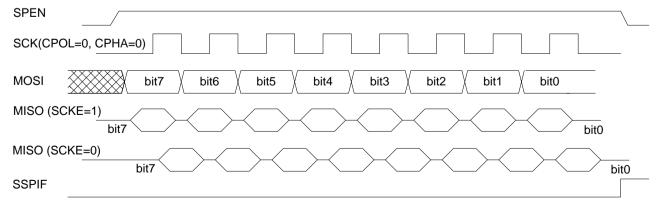

|     |                                                 | 10.1.1 CPOL=0 CPHA=0                                                 |          |  |  |  |  |

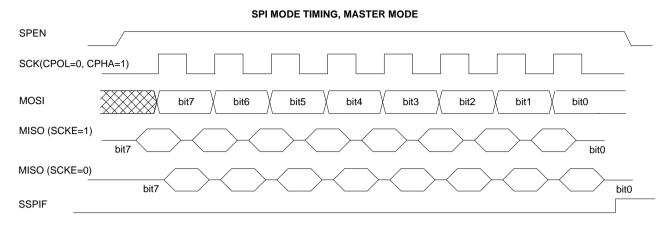

|     |                                                 | 10.1.2 CPOL=0 CPHA=1                                                 | _        |  |  |  |  |

|     |                                                 | 10.1.4 CPOL=1 CPHA=1                                                 |          |  |  |  |  |

|     | 10.2                                            | SPI Slave Timing Illustration                                        |          |  |  |  |  |

|     |                                                 | 10.2.1 CPOL=0 CPHA=0                                                 |          |  |  |  |  |

|     |                                                 | 10.2.2 CPOL=0 CPHA=1                                                 |          |  |  |  |  |

|     |                                                 | 10.2.4 CPOL=1 CPHA=1                                                 |          |  |  |  |  |

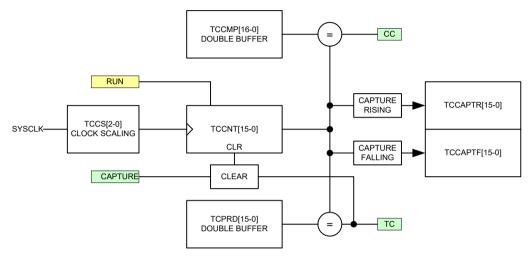

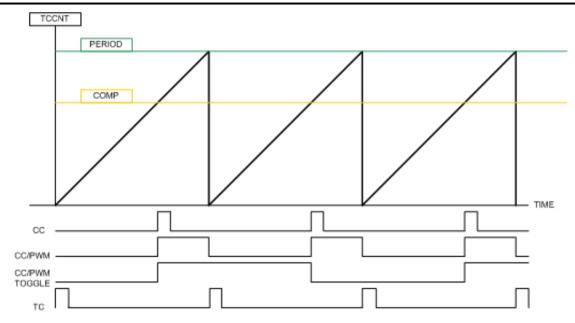

| 11. | Timer                                           | with Compare/Capture and Quadrature Encoder                          | 67       |  |  |  |  |

| 12. | PWM                                             | Controller                                                           | 73       |  |  |  |  |

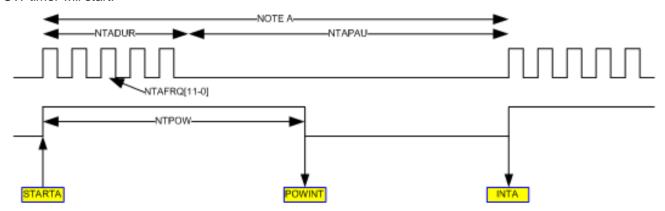

| 13. | Buzze                                           | r and Melody Controller                                              | 76       |  |  |  |  |

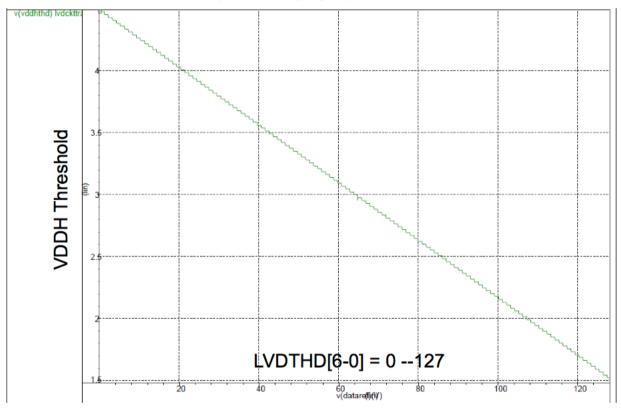

| 14. | Core Regulator and Low Voltage Detection                                   | 79  |

|-----|----------------------------------------------------------------------------|-----|

|     | 14.1 Supply Low Voltage Detection (LVD)                                    |     |

| 15. | IOSC and SOSC                                                              | 81  |

|     | 15.1 IOSC 16MHz/32MHz                                                      |     |

|     | 15.2 SOSC 128KHz                                                           |     |

| 16. | 11-Bit SAR ADC (ADC)                                                       | 83  |

| 17. | Analog Comparators (ACMP) and 8-bit DAC                                    | 86  |

| 18. | Touch Key Control III                                                      | 89  |

| 19. | GPIO Multi-Function Select and Pin Interrupt                               | 94  |

| 20. | Information Block IFB                                                      | 96  |

| 21. | Writer Mode                                                                | 98  |

| 22. | Boot Code and In-System Programming                                        | 100 |

| 23. | Electrical Specifications                                                  | 101 |

|     | 23.1 Absolute Maximum Ratings                                              | 101 |

|     | 23.2 Recommended Operating Condition                                       |     |

|     | 23.3 DC Electrical Characteristics (VDD = 2.35V to 5.5V TA=-40°C to 125°C) |     |

|     | 23.4 AC Electrical Characteristics (VDD =2.3V to 5.5V TA=-40°C to 125°C)   |     |

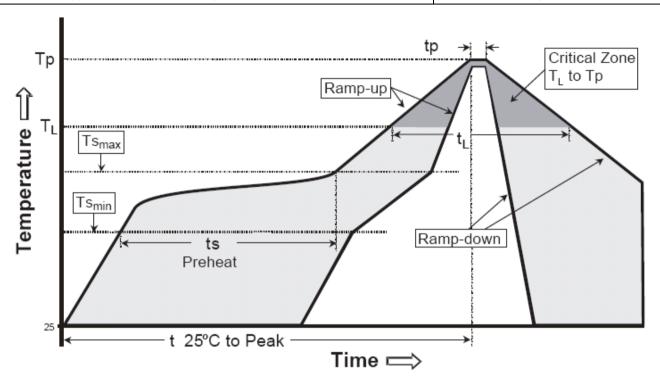

|     | 23.5 Classification Reflow Profiles                                        | 103 |

| 24. | Packaging Outline                                                          |     |

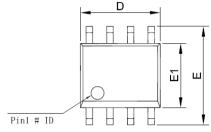

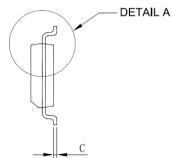

|     | 24.1 8-pin SOP                                                             |     |

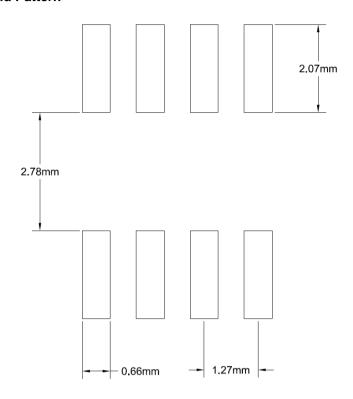

|     | 24.1.2 POD                                                                 |     |

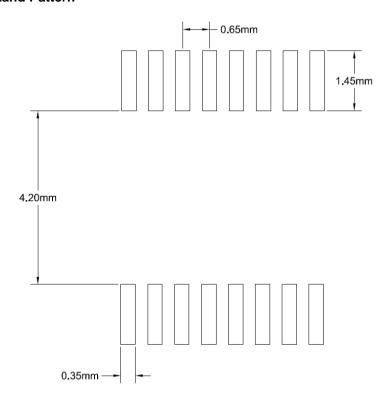

|     | 24.2 16-pin TSSOP                                                          |     |

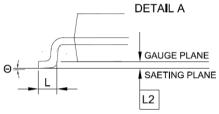

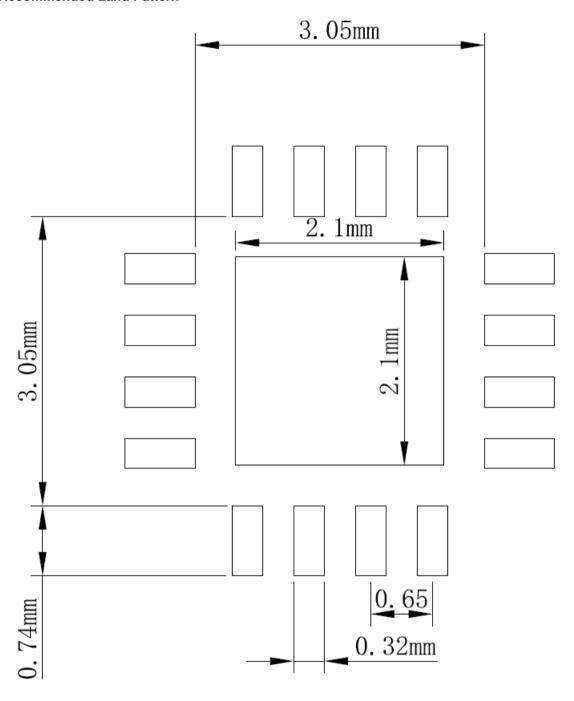

|     | 24.2.1 Recommended Land Pattern                                            | -   |

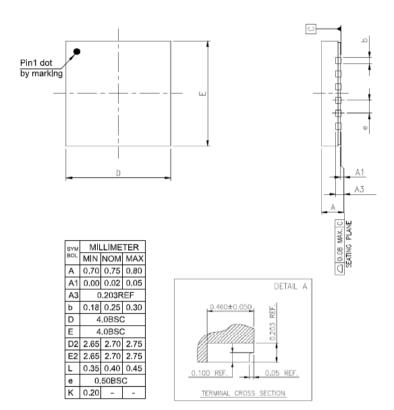

|     | 24.2.2 POD                                                                 |     |

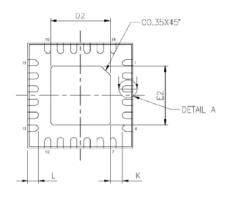

|     | 24.3 16-pin WQFN                                                           |     |

|     | 24.3.2 POD                                                                 |     |

| 25. | Ordering Information                                                       | 111 |

| 26. | Errata                                                                     | 112 |

| 27  | Revisions                                                                  | 113 |

# **List of Tables**

| 1.          | PIN Description and Multifunction Table                                                                     | 1  |

|-------------|-------------------------------------------------------------------------------------------------------------|----|

|             | Table 1-1 PIN Description Table                                                                             |    |

|             | PIN Description and Multifunction Table  Table 1-1 PIN Description Table  Table 1-2 PIN Multifunction Table | 2  |

|             |                                                                                                             |    |

| 3.          | REGISTER MAP SFR (0x80 – 0xFF)                                                                              | 4  |

|             | REGISTER MAP SFR (0x80 – 0xFF)  Table 3-1 SFR Register map                                                  |    |

|             |                                                                                                             |    |

| 4.          | TA protected REGISTER MAP XFR (0xA000 – 0xAFFF)  Table 4-1 TA protected REGISTER MAP                        | 5  |

|             | Table 4-1 TA protected REGISTER MAP                                                                         | 6  |

| _           |                                                                                                             | _  |

| 5.          | 8051 CPU  Table 5-1 Interrupt sources and interrupt vectors                                                 | 7  |

|             | Table 5-1 Interrupt sources and interrupt vectors                                                           | 11 |

| 20          | Information Block IFB                                                                                       | 00 |

| <b>2</b> 0. |                                                                                                             |    |

|             | Table 20-1 Information Block (IFB)                                                                          | 97 |

| 21.         | Writer Mode                                                                                                 | 98 |

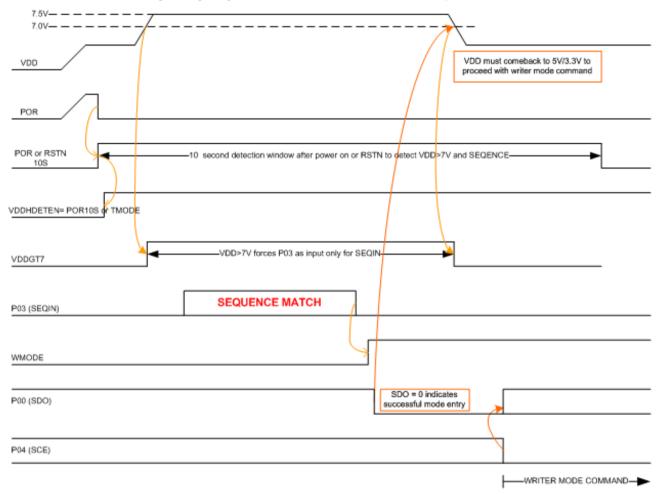

|             | Table 21-1 Timing diagram for Writer Mode access                                                            | 98 |

|             |                                                                                                             |    |

# **List of Figures**

| 2.    | Memory Map                                                   |    |

|-------|--------------------------------------------------------------|----|

|       | Figure 2-1 Memory Map                                        | 3  |

| 5.    | 8051 CPU                                                     | 7  |

|       | Figure 5-1 Watchdog Timer block diagram                      | 18 |

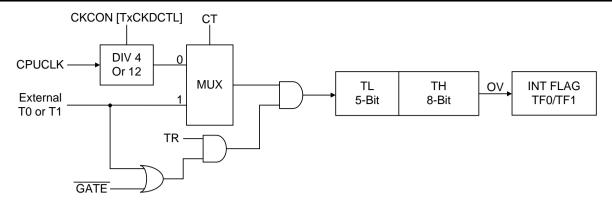

|       | Figure 5-2 Timer/Counter Mode 0: 13-bit counter              | 22 |

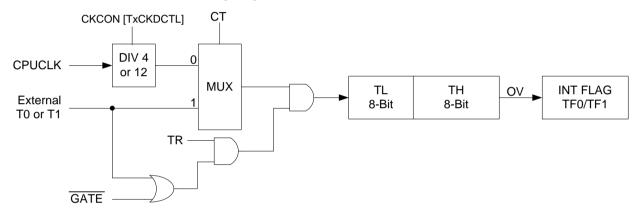

|       | Figure 5-3 Timer/Counter Mode 1: 16-bit counter              |    |

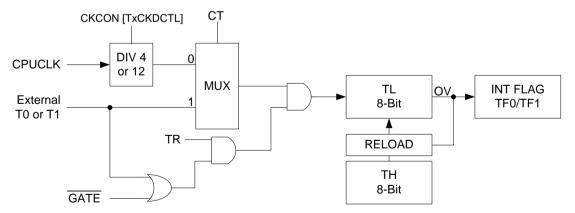

|       | Figure 5-4 Timer/Counter Mode 2: 8-bit re-load               |    |

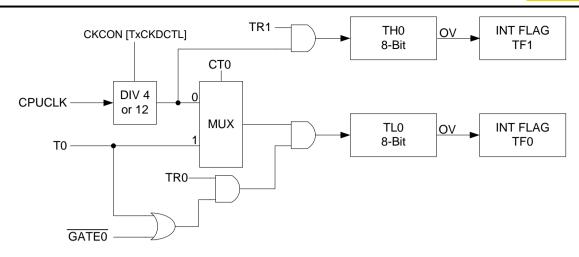

|       | Figure 5-5 Timer/Counter Mode 3: Two 8-bit counters          |    |

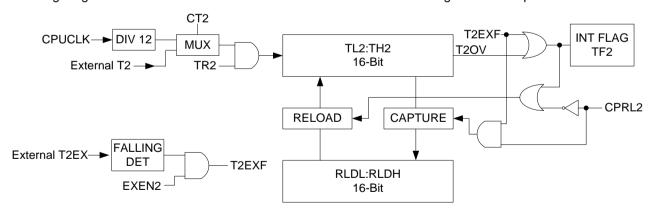

|       | Figure 5-6 Timer 2 block diagram of Auto-reload and Capture  |    |

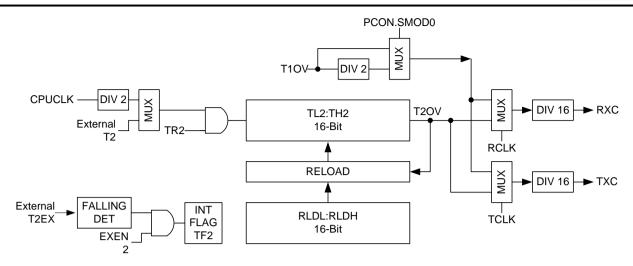

|       | Figure 5-7 Timer 2 block diagram of Baud Rate Generator      |    |

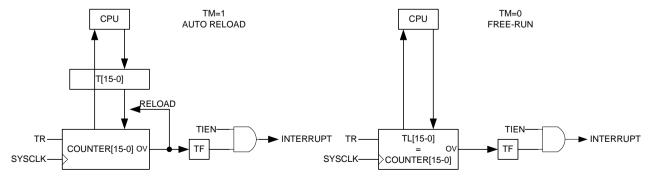

|       | Figure 5-8 Timer 3 and Timer 4 block diagram                 |    |

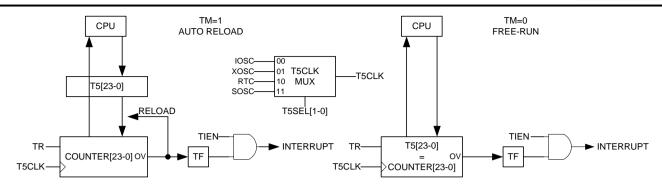

|       | Figure 5-9 Timer 5 block diagram                             |    |

|       | Figure 5-10 System Clock Monitor diagram                     |    |

|       | Figure 5-11 Reset block diagram                              | 41 |

| 9.    | EUART2 with LIN Controller                                   | 53 |

|       | Figure 9-1 EUART2 with LIN Controller block diagram          |    |

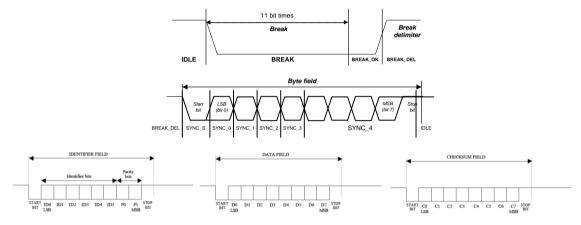

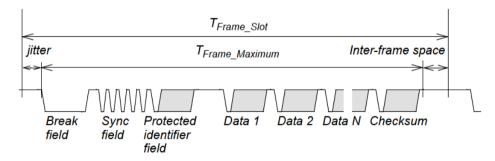

|       | Figure 9-2 LIN frame structure                               | 56 |

|       | Figure 9-3 LIN frame timing                                  |    |

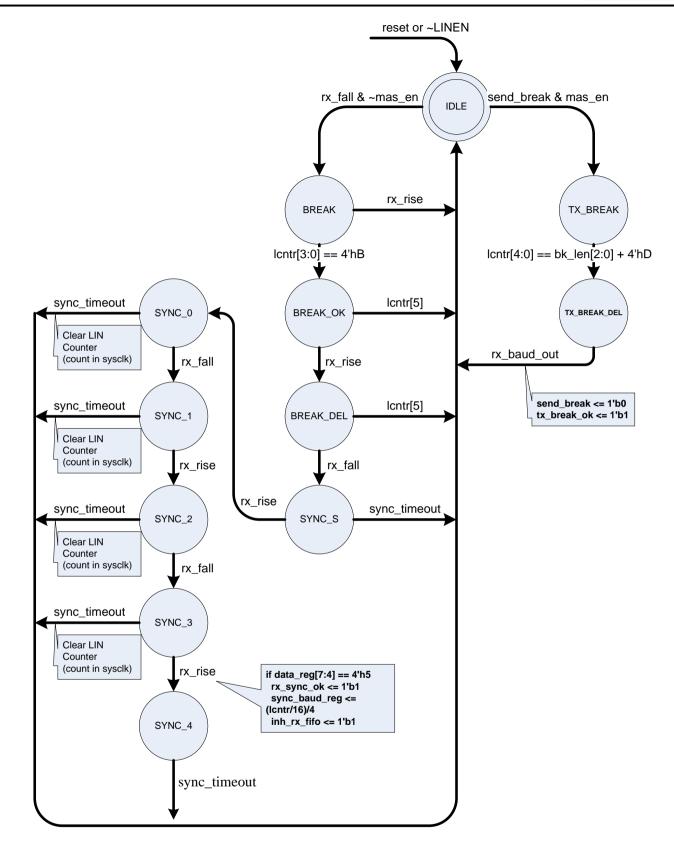

|       | Figure 9-4 Finite State Machine of the LIN extension         | 57 |

| 10    | Serial Peripheral Interface (SPI)                            | 62 |

|       | Figure 10-1 SPI Master Timing with CPOL=0, CPHA=0            |    |

|       | Figure 10-2 SPI Master Timing with CPOL=0, CPHA=1            |    |

|       | Figure 10-3 SPI Master Timing with CPOL=1, CPHA=0            |    |

|       | Figure 10-4 SPI Master Timing with CPOL=1. CPHA=1            |    |

|       | Figure 10-5 SPI Slave Timing with CPOL=0, CPHA=0             |    |

|       | Figure 10-6 SPI Slave Timing with CPOL=0, CPHA=1             |    |

|       | Figure 10-7 SPI Slave Timing with CPOL=1. CPHA=0             | 66 |

|       | Figure 10-8 SPI Slave Timing with CPOK=1, CPHA=1             |    |

| 11    | Timer with Compare/Capture and Quadrature Encoder            | 67 |

| • • • | Figure 11-1 TCC implementations diagram                      | 67 |

|       | Figure 11-2 TCC timing diagram                               |    |

|       | Figure 11-3 QE implementation diagram                        |    |

|       | Figure 11-4 Timing diagram of CHA/CHB with X1/X2/X4 modes    | 71 |

|       |                                                              |    |

| 13.   | Buzzer and Melody Controller                                 |    |

|       | Figure 13-1 Buzzer and Melody output timing diagram          | 76 |

| 14.   | Core Regulator and Low Voltage Detection                     |    |

|       | Figure 14-1 LVD Threshold VX LVDTHD[6-0]                     | 79 |

| 15.   | IOSC and SOSC                                                | 81 |

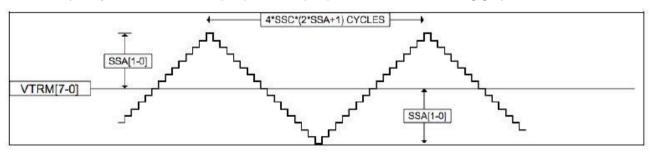

|       | Figure 15-1 IOSC sweep rate and amplitude of Spread Spectrum | 81 |

|       |                                                              |    |

| 16.   | 11-Bit SAR ADC (ADC)                                         | 83 |

|       | Figure 16-1 11-bit SAR ADC block diagram                     | 83 |

| 17.   | Analog Comparators (ACMP) and 8-bit DAC                      | 86 |

|       | Figure 17-1 ACMP and 8-bit DAC block diagram                 |    |

| 18.   | Touch Key Control III                                        | 89 |

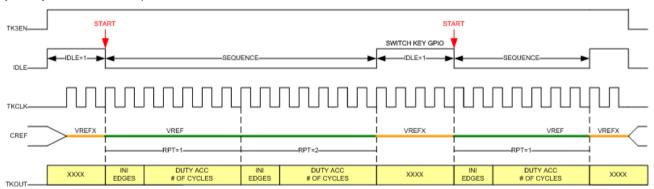

|       | Figure 18-1 TK3 signals timing diagram                       |    |

|       | Figure 18-2 Timing diagram of Auto Detection in Sleep mode   |    |

|       |                                                              |    |

| 21.   | Writer Mode                                                  |    |

|       | Figure 21-1 Timing diagram for Writer Mode access            | 98 |

# **List of Registers**

| 5. | 8051 CPU                                                                               | 7          |

|----|----------------------------------------------------------------------------------------|------------|

|    | ACC (0xE0) Accumulator R/W (0x00)                                                      | 7          |

|    | B (0xF0) B Register R/W (0x00)                                                         | 7          |

|    | PSW (0xD0) Program Status Word R/W (0x00)                                              |            |

|    | SP (0x81) Stack Pointer R/W (0x00)                                                     | 7          |

|    | ESP (0x9B) Extended Stack Pointer R/W (0x00)                                           |            |

|    | STATUS (0xC5) Program Status Word RO(0x00)                                             |            |

|    | WTST (0x92) R/W (0x07)                                                                 |            |

|    | MCON (0xC6) XRAM Relocation Register R/W (0x00) TA Protected                           |            |

|    | ACON (0x9D) R/W (0x00) TA Protected                                                    |            |

|    | DPXR (0xDA) R/W (0x00)                                                                 |            |

|    |                                                                                        |            |

|    | DPS (0x86) Data Pointer Select R/W (0x00)                                              |            |

|    | DPH (0x83) Data Pointer High R/W (0x00)                                                |            |

|    | DPL1 (0x84) Extended Data Pointer Low R/W (0x00)                                       |            |

|    | DPH1 (0x85) Extended Data Pointer High R/W (0x00)                                      |            |

|    | DPX (0x93) Data Pointer Top R/W (0x00)                                                 |            |

|    | DPX1 (0x95) Extended Data Pointer Top R/W (0x00)                                       |            |

|    | IE (0xA8) Interrupt Enable Register R/W (0x00)                                         | 12         |

|    | EXIE (0xE8) Extended Interrupt Enable Register R/W (0x00)                              | 12         |

|    | IP (0xB8) Interrupt Priority Register R/W (0x00)                                       |            |

|    | EXIP (0xF8) Extended Interrupt Priority Register R/W (0x00)                            |            |

|    | EXIF (0x91) Extended Interrupt Flag R/W (0x00)                                         | 12         |

|    | WKMASK (0x9F) R/W (0xFF) Wake Up Mask Register TB Protected                            |            |

|    | TCON (0x88) R/W (0x00)                                                                 | 13         |

|    | TA (0xC7) Time Access A Control Register2 WO xxxxxxxx0                                 |            |

|    | TB (0xC9) Time Access B Control Register2 RW (0x00)                                    |            |

|    | PCON (0x87) R/W (0x00)<br>PMR (0xC4) R/W (010xxxxx)                                    |            |

|    | CKSEL (0x8F) System Clock Selection Register R/W (0x0C) TB Protected                   |            |

|    | WKMASK (0x9F) R/W (0xFF) Wake-Up Mask Register TB Protected                            |            |

|    | WDCON (0xD8) WDT1 Interrupt Flag Register R/W (0x02) TA Protected for WDT1CLR bit only |            |

|    | CKCON (0x8E) Clock Control and WDT1 R/W (0xC7)                                         |            |

|    | WDT2CF (0xA0D8h) Watchdog Timer 2 Configure Registers R/W (0xA7) TB Protected          |            |

|    | WDT2L (0xA0D9h) Watchdog Timer 2 Time Out Value Low Byte RW (0xFF) TB Protected        |            |

|    | WDT2H (0xA0DAh) Watchdog Timer 2 Time Out Value High Byte RW (0x0F) TB Protected       |            |

|    | WDT3CF (0xA0DBh) Watchdog Timer 3 Configure Registers R/W (0xD1) TB Protected          | 20         |

|    | WDT3L (0xA0DCh) Watchdog Timer 3 Time Out Value Low Byte RO R/W (0xFF) TB Protected    | 20         |

|    | WDT3H (0xA0DDh) Watchdog Timer 3 Time Out Value High Byte RO R/W (0x0F) TB Protected   |            |

|    | TCON (0x88) R/W (0x00)                                                                 |            |

|    | TMOD (0x89h) Timer 0 and 1 Mode Control Register R/W (0x00)                            |            |

|    | TL0 (0x8Ah) Timer 0 Low Byte Register R/W (0x00)                                       |            |

|    | TH0 (0x8Ch) Timer 0 High Byte Register 0 R/W (x00)                                     |            |

|    | TL1 (0x8Bh) Timer 1 Low Byte Register 0 R/W (0x00)                                     |            |

|    | TH1 (0x8Dh) Timer 1 High Byte Register 0 R/W (0x00)                                    |            |

|    | T2CON (0xC8h) Timer 2 Control and Configuration Register R/W (0x00)                    |            |

|    | TH2 (0xCCh) Timer 2 High Byte Register 0 R/W (0x00)                                    |            |

|    | RLDL (0xCAh) Timer 2 reload Low Byte Register 0 R/W (0x00)                             |            |

|    | RLDH (0xCBh) Timer 2 reload High Byte Register 0 RW (0x00)                             |            |

|    | T34CON (0xCFh) Timer 3 and Timer 4 Control and Status Register R/W (00000000)          | <u>2</u> 6 |

|    | TL3 (0xAEh) Timer 3 Low Byte Register 0 R/W 00000000                                   |            |

|    | TH3 (0xAFh) Timer 3 High Byte Register 0 R/W 00000000                                  |            |

|    | TL4 (0xACh) Timer 4 Low Byte Register 0 R/W 00000000                                   |            |

|    | TH4 (0xADh) Timer 4 High Byte Register 0 R/W 00000000                                  | 26         |

|    | T5CON (0xA068h) Timer 5 Control and Status Register R/W (00000000)                     |            |

|    | TL5 (0xA069) Timer5 Low Byte Register 0 R/W (0x00)                                     |            |

|    | TH5 (0xA06A) Timer5 Medium Byte Register 0 R/W (0x00)                                  |            |

|    | TT5 (0xA06B) Timer5 High Byte Register 0 R/W (0x00)                                    |            |

|    | ARCON (0xFF) MDU Control R/W (0x00)                                                    |            |

|    | MD0 (0xF9) MDU Data Register 0 R/W (0x00)                                              |            |

|    | MD1 (0xFA) MDU Data Register 1 R/W (0x00)                                              |            |

|    | MD2 (0xFB) MDU Data Register 2 R/W (0x00)                                              |            |

|    | MD3 (0xFC) MDU Data Register 3 R/W (0x00)                                              |            |

|    | MD5 (0xFE) MDU Data Register 5 R/W (0x00)                                              |            |

|    |                                                                                        | ∠೨         |

6.

7.

8.

| I2CMTP (0xF7h) I <sup>2</sup> C Master Time Period R/W (x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| I2CMSA (0xF4) I <sup>2</sup> C Master Slave Address R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

| I2CMBUF (0xF6) I <sup>2</sup> C Master Data Buffer Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

| I2CMCR (0xF5) I <sup>2</sup> C Master Control and Status Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

| I2CMTO (0xC3) I2C Time Out Control Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

| CCCFG (0xA078h) Checksum/CRC Accelerator Configuration Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |

| CCDATA0 (0xA07Ch) Checksum/CRC Data Register 0 R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34                                                                                                           |

| CCDATA1 (0xA07Dh) Checksum/CRC Data Register 1 R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |

| CCDATA2 (0xA07Eh) Checksum/CRC Data Register 2 R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |

| CCDATA3 (0xA07Fh) Checksum/CRC Data Register 2 R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |

| BPINTF (A0E0h) Break Point Interrupt Flag Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35                                                                                                           |

| BPINTE (A0E1h) Break Point Interrupt Enable Register R/W (0x00) TB Protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35                                                                                                           |

| BPINTC (A0E2h) Break Point Interrupt Control Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 35                                                                                                         |

| BPCTRL (A0E3h) DBG and BKP ISR Control and Status Register R/W (0xFC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |

| PC1AL (A0F0h) Program Counter Break Point 1 Low Address Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

| PC1AH (A0F1h) Program Counter Break Point 1 High Address Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

| PC1AT (A0F2h) Program Counter Break Point 1 Top Address Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

| PC2AL (A0F4h) Program Counter Break Point 2 Low Address Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

| PC2AH (A0F5h) Program Counter Break Point 2 High Address Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

| PC2AT (A0F6h) Program Counter Break Point 2 Top Address Register R/W (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36                                                                                                           |

| DBPCIDL (A098h) Debug Program Counter Address Low Register RO (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                              |