**MAX22212**

Click here to ask an associate for production status of specific part numbers.

## 36V, 7.6A High Current Single H-Bridge with Integrated Current Sense

#### **General Description**

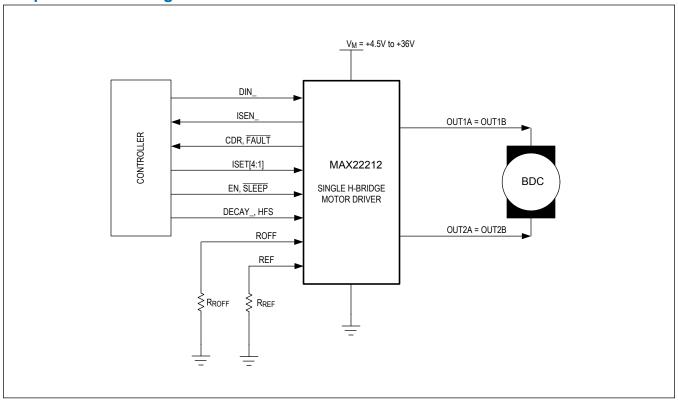

The MAX22212 integrates a high current 36V, 7.6A<sub>MAX</sub> H-Bridge to drive one Brushed DC motor or one half of a stepper motor. The H-Bridge FETs feature very low impedance, resulting in high driving efficiency and low heat generation. The typical total  $R_{ON}$  (high-side + low-side) is 0.125 $\Omega$ . The H-Bridge can be PWM controlled by using three logic inputs (DIN1, DIN2, and EN).

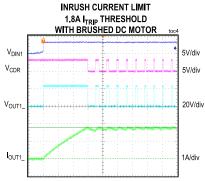

The MAX22212 features an accurate current drive regulation (CDR), which can be used to limit the start up current of a brushed DC motor or to control the phase current for stepper operation. The bridge output current is sensed by a non-dissipative integrated current sensing (ICS) and it is then compared with a user configurable setpoint (I<sub>TRIP</sub>). When the bridge current exceeds the setpoint, the device enforces the decay for a fixed OFF-time (t<sub>OFF</sub>). Four different decay methods are supported (Slow Decay, Fast Decay, and two Mixed Decay modes). The non-dissipative ICS eliminates the bulky external power resistors normally required for this function resulting in a dramatic space and power saving compared with mainstream applications based on the external sense resistor.

A current proportional to the internally-sensed motor current is output to the external pins (ISENA, ISENB). By connecting an external resistor from these pins to GND, a voltage proportional to the motor current is generated. The voltage across this resistor can be used as inputs to ADCs of an external motor controller if motion control algorithm requires the current/torque information.

In addition, one open-drain output (CDR pin) is asserted every time the internal current regulation takes control of the driver so that the activity of the internal current loop can be monitored.

The maximum user configurable full-scale current ( $I_{FS\_MAX}$ ) can be set up to 7.6A limited by the overcurrent protection (OCP). An external resistor connected from REF to GND sets the full-scale current ( $I_{FS}$ ) threshold. An integrated sinusoidal 4-bit DAC allows the user to dynamically modify the current regulation set-point ( $I_{TRIP}$ ) from zero to IFS. Because of thermal considerations, the recommended maximum RMS current on a standard 4-layers PCB is  $4A_{RMS}$ .

In applications in which the requirement of maximum full-scale current is less than 3.8A and high current control accuracy is desired, the half full scale (HFS) logic input pin can be set high to halve the current rating and double the low-side FET  $R_{\mbox{\scriptsize ON}}$ . This results in better current control loop accuracy in the bottom end of the current range.

The MAX22212 features overcurrent protection (OCP), thermal shutdown (TSD), and undervoltage lockout (UV-LO) protection. An open-drain active low FAULT pin is activated every time a fault condition is detected. During thermal shutdown and undervoltage lockout events, the driver is disabled until normal operations are restored.

The MAX22212 is available into a small TQFN32 5mm x 5mm package or in a TSSOP28 4.4mm x 9.7mm package.

#### **Applications**

- Stepper-Motor Driver

- Brushed DC Motor Driver

- Solenoid Driver

- Latched Valves

#### **Benefits and Features**

- One H-Bridge with +36V Voltage Rating

- Total R<sub>DS(ON)</sub> (High-Side + Low-Side): 125mΩ Typical (T<sub>A</sub> = 25°C)

- Current Ratings per H-Bridge (Typical at T<sub>A</sub> = 25°C):

- I<sub>FS\_MAX</sub> = 7.6A (Max Full-Scale Current Setting for Internal Current Drive Regulation)

- I<sub>RMS</sub> = 4A<sub>RMS</sub> Recommended Maximum RMS Current

- Integrated Current Control

- Full-Scale DAC Current Programmable with External Resistor

- Internal Current Sensing (ICS) Eliminates External Bulky Resistors and Improves Efficiency

- Current Drive Regulation Monitor Output Pin (CDR Pin).

- Integrated DAC Sets the Output Current from 16 Levels

- Four Decay Modes Supported (Slow, Fast, and Two Mixed Modes)

- Fixed OFF Time Configurable with External Resistor

- Current Sense Output (Current Monitor)

- Fault Indicator Pin (FAULT)

- Low Power Mode (Sleep Mode)

- Protections

- Overcurrent Protection for each Channel (OCP)

- Undervoltage Lockout (UVLO)

- Thermal Shutdown T<sub>J</sub> = 165°C (TSD)

- TQFN32 5mm x 5mm Package or in a TSSOP28 4.4mm x 9.7mm Package

Ordering Information appears at end of data sheet.

19-101538; Rev 1; 1/24

## **Simplified Block Diagram**

## **TABLE OF CONTENTS**

| General Description                            | 1    |

|------------------------------------------------|------|

| Applications                                   | 1    |

| Benefits and Features                          | 1    |

| Simplified Block Diagram                       | 2    |

| Absolute Maximum Ratings                       | 6    |

| Package Information                            | 6    |

| 32-Pin TQFN—5mm x 5mm                          | 6    |

| 28-Pin TSSOP—4.4mm x 9.7mm                     | 6    |

| Electrical Characteristics                     | 7    |

| Typical Operating Characteristics              | . 10 |

| Pin Configurations                             | . 11 |

| TQFN Pin Configuration                         | . 11 |

| TSSOP Pin Configuration                        | . 12 |

| Pin Description                                | . 12 |

| Functional Diagrams                            | . 14 |

| Diagram                                        | . 14 |

| Detailed Description                           | . 15 |

| Sleep Mode (SLEEP Pin)                         | . 15 |

| PWM Control                                    | . 15 |

| Current-Sense Output (ISEN) - Current Monitor  | . 16 |

| Current Drive Regulation                       | . 18 |

| Setting the Full-Scale Current – IFS           | . 18 |

| Bridge Current Control                         |      |

| Setting the Fixed OFF Time (t <sub>OFF</sub> ) | . 19 |

| CDR Open-Drain Output                          | . 19 |

| Setting the Decay Mode                         | . 20 |

| Fault Protection                               | . 21 |

| Overcurrent Protection – (OCP)                 |      |

| Undervoltage-Lockout Protection                | . 21 |

| Ordering Information                           | . 22 |

| Revision History                               | . 23 |

## MAX22212

# 36V, 7.6A High Current Single H-Bridge with Integrated Current Sense

| LIST OF F                            | IGURES |

|--------------------------------------|--------|

| Figure 1. ISEN Current               |        |

| Figure 2. CDR Monitor Timing Diagram |        |

## MAX22212

# 36V, 7.6A High Current Single H-Bridge with Integrated Current Sense

| LIST OF TABLES                          |    |  |  |  |  |

|-----------------------------------------|----|--|--|--|--|

| Table 1. MAX22212 Truth Table           | 15 |  |  |  |  |

| Table 2. HFS Truth Table                | 18 |  |  |  |  |

| Table 3. H-Bridge ISET Pins Truth Table | 18 |  |  |  |  |

| Table 4. Decay Mode Truth Table         | 20 |  |  |  |  |

## **Absolute Maximum Ratings**

| V <sub>M</sub> to GND   | 0.3V to +42V                                              | ROFF to GND0.3V to mi          | n (+2.2V, V <sub>DD</sub> + 0.3V) |

|-------------------------|-----------------------------------------------------------|--------------------------------|-----------------------------------|

|                         | 0.3V to min (+2.2V, V <sub>M</sub> + 0.3V)                | ISEN_ to GND0.3V to mi         | n (+2.2V, V <sub>DD</sub> + 0.3V) |

| PGND to GND             | 0.3V to +0.3V                                             | DIN_to GND                     | 0.3V to +6V                       |

| OUT                     | 0.3V to (V <sub>M</sub> + 0.3)V                           | EN to GND                      | 0.3V to +6V                       |

| V <sub>CP</sub> to GND( | V <sub>M</sub> - 0.3V) to min (+42V, V <sub>M</sub> + 6V) | HFS to GND                     | 0.3V to +6V                       |

| C <sub>P2</sub> to GND  | 0.3V to min (+42V, V <sub>M</sub> + 0.3V)                 | DECAY_ to GND                  | 0.3V to +6V                       |

| C <sub>P1</sub> to GND( | V <sub>M</sub> - 0.3V) to min (+42V, V <sub>M</sub> + 6V) | SLEEP to GND0.3V to r          | nin (+42V, V <sub>M</sub> + 0.3V) |

| FAULT to GND            | 0.3V to +6V                                               | Operating Temperature Range    | 40°C to +125°C                    |

| CDR to GND              | 0.3V to +6V                                               | Junction Temperature           | +160°C                            |

| ISET_ to GND            | 0.3V to +6V                                               | Storage Temperature Range      |                                   |

| REF to GND              | 0.3V to min (+2.2V, V <sub>DD</sub> + 0.3V)               | Soldering Temperature (reflow) | +260°C                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 32-Pin TQFN—5mm x 5mm

| Package Code                            | T3255-8C       |  |  |

|-----------------------------------------|----------------|--|--|

| Outline Number                          | <u>21-0140</u> |  |  |

| Land Pattern Number                     | 90-0013        |  |  |

| Thermal Resistance, Single-Layer Board: |                |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 47°C/W         |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 1.7°C/W        |  |  |

| Thermal Resistance, Four-Layer Board:   |                |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 29°C/W         |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 1.7°C/W        |  |  |

#### 28-Pin TSSOP—4.4mm x 9.7mm

| Package Code                           | U28E+5C        |  |  |  |

|----------------------------------------|----------------|--|--|--|

| Outline Number                         | <u>21-0108</u> |  |  |  |

| Land Pattern Number                    | <u>90-0147</u> |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 24.65°C/W      |  |  |  |

| Junction to Case $(\theta_{JC})$       | 1.52°C/W       |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.analog.com/en/design-center/packaging-quality-symbols-footprints/package\_index.html">https://www.analog.com/en/design-center/packaging-quality-symbols-footprints/package\_index.html</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.analog.com/en/technical-articles/thermal-characterization-of-ic-packages.html">https://www.analog.com/en/technical-articles/thermal-characterization-of-ic-packages.html</a>.

#### **Electrical Characteristics**

$(V_M$  = +4.5V to +36V,  $R_{ROFF}$  = from 15k $\Omega$  to 120k $\Omega$ ,  $R_{REF}$  = from 12k $\Omega$  to 72k $\Omega$ , typical values are  $T_A$  = +25°C and  $V_M$  = +24V, limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply-voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Note 1.)

| PARAMETER                                          | SYMBOL                  | CONDITIONS                                                       | MIN   | TYP                  | MAX   | UNITS |

|----------------------------------------------------|-------------------------|------------------------------------------------------------------|-------|----------------------|-------|-------|

| POWER SUPPLY                                       | 1                       |                                                                  |       |                      |       | •     |

| Supply-Voltage Range                               | V <sub>M</sub>          |                                                                  | 4.5   |                      | 36    | V     |

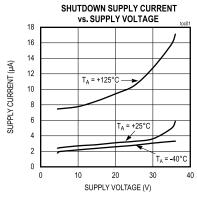

| Sleep-Mode Current<br>Consumption                  | I <sub>VM</sub>         | SLEEP = logic low                                                |       | 4                    | 11    | μΑ    |

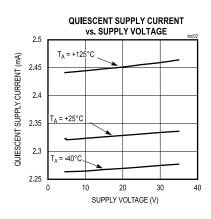

| Quiescent Current<br>Consumption                   | I <sub>VM</sub>         | SLEEP = logic high                                               |       | 2                    | 4     | mA    |

| 1.8V Regulator Output<br>Voltage                   | V <sub>VDD</sub>        | V <sub>M</sub> = +4.5V, I <sub>LOAD</sub> = internal consumption | 1.74  | 1.8                  | 1.86  | V     |

| V <sub>DD</sub> Current Limit                      | I <sub>V18(LIM)</sub>   |                                                                  | 20    |                      |       | mA    |

| V <sub>DD</sub> UVLO Rising                        | UVLOV18 <sub>R</sub>    | V <sub>DD</sub> rising                                           | 1.59  | 1.65                 | 1.69  | V     |

| V <sub>DD</sub> UVLO Falling                       | UVLOV18 <sub>F</sub>    | V <sub>DD</sub> falling                                          | 1.535 | 1.58                 | 1.635 | V     |

| Charge-Pump Voltage                                | V <sub>CP</sub>         |                                                                  |       | V <sub>M</sub> + 2.7 |       | V     |

| LOGIC LEVEL INPUTS/C                               | UTPUTS                  |                                                                  |       |                      |       |       |

| Input Voltage<br>Level—High                        | V <sub>IH</sub>         |                                                                  | 1.2   |                      |       | V     |

| Input Voltage<br>Level—Low                         | V <sub>IL</sub>         |                                                                  |       |                      | 0.65  | V     |

| Input Hysteresis                                   | V <sub>HYS</sub>        |                                                                  |       | 110                  |       | mV    |

| Pull-Down Current                                  | I <sub>PD</sub>         | To GND                                                           | 16    | 34                   | 50    | μA    |

| Open-Drain Output<br>Logic-Low Voltage             | V <sub>OL</sub>         | I <sub>LOAD</sub> = 5mA                                          |       |                      | 0.2   | V     |

| Open-Drain Output<br>Logic-High Leakage<br>Current | ІОН                     | V <sub>PIN</sub> = 3.3V                                          | -1    |                      | +1    | μΑ    |

| SLEEP Voltage Level<br>High                        | V <sub>IH</sub> (SLEEP) |                                                                  | 0.9   |                      |       | V     |

| SLEEP Voltage Level<br>Low                         | V <sub>IL(SLEEP)</sub>  |                                                                  |       |                      | 0.6   | V     |

| SLEEP Pull-Down Input<br>Resistance                | R <sub>PD(SLEEP)</sub>  |                                                                  | 0.8   | 1.5                  |       | ΜΩ    |

| OUTPUT SPECIFICATIO                                | NS                      |                                                                  | •     |                      |       | •     |

| Output ON-Resistance<br>Low-Side                   | Б                       | HFS = logic low, OUT1A = OUT1B,<br>OUT2A = OUT2B                 |       | 0.0625               | 0.11  | 0     |

|                                                    | R <sub>ON(LS)</sub>     | HFS = logic high, OUT1A = OUT1B,<br>OUT2A = OUT2B                |       | 0.11                 | 0.21  | Ω     |

| Output On-Resistance<br>High-Side                  | R <sub>ON(HS)</sub>     | OUT1A = OUT1B, OUT2A = OUT2B 0.0625 0.11                         |       |                      | 0.11  | Ω     |

| Output Leakage                                     | I <sub>LEAK</sub>       | Driver OFF                                                       | -10   |                      | 10    | μA    |

| Dead Time                                          | t <sub>DEAD</sub>       |                                                                  |       | 100                  |       | ns    |

| Output Slew Rate                                   | SR                      |                                                                  |       | 200                  |       | V/µs  |

## **Electrical Characteristics (continued)**

$(V_M$  = +4.5V to +36V,  $R_{ROFF}$  = from 15k $\Omega$  to 120k $\Omega$ ,  $R_{REF}$  = from 12k $\Omega$  to 72k $\Omega$ , typical values are  $T_A$  = +25°C and  $V_M$  = +24V, limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply-voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Note 1.)

| PARAMETER                                              | SYMBOL              | CONDITIONS                                                                                                                              | MIN   | TYP   | MAX   | UNITS    |  |

|--------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|----------|--|

| PROTECTION CIRCUITS                                    |                     |                                                                                                                                         |       |       |       |          |  |

| Overcurrent Protection Threshold                       | OCP                 |                                                                                                                                         | 7.6   |       |       | А        |  |

| Overcurrent Protection Blanking Time                   | t <sub>OCP</sub>    |                                                                                                                                         | 1     | 2.2   | 3.2   | μs       |  |

| Autoretry OCP Time                                     | t <sub>RETRY</sub>  |                                                                                                                                         |       | 3     |       | ms       |  |

| UVLO Threshold on V <sub>M</sub>                       | V <sub>UVLO</sub>   | V <sub>M</sub> rising                                                                                                                   | 3.85  | 4     | 4.15  | V        |  |

| UVLO Threshold on V <sub>M</sub><br>Hysteresis         | UVLO <sub>HYS</sub> |                                                                                                                                         |       | 0.12  |       | V        |  |

| Thermal Protection Threshold Temperature               | TSD                 |                                                                                                                                         |       | +165  |       | °C       |  |

| Thermal Protection Temperature Hysteresis              | TSD <sub>HYS</sub>  |                                                                                                                                         |       | 20    |       | °C       |  |

| <b>CURRENT REGULATION</b>                              | I                   |                                                                                                                                         |       |       |       |          |  |

| REF Output Voltage                                     | $V_{REF}$           |                                                                                                                                         | 0.882 | 0.9   | 0.918 | V        |  |

| I <sub>TRIP</sub> Current Regulation                   | K.=0                | HFS = logic low                                                                                                                         |       | 72    |       | KV       |  |

| Constant                                               | K <sub>IFS</sub>    | HFS = logic high                                                                                                                        |       | 36.8  |       | kV       |  |

|                                                        | DITRIP1             | HFS = logic low, I <sub>OUT</sub> = 2.2A to 6A                                                                                          | -5    |       | 5     |          |  |

| Current Trip Regulation                                |                     | HFS = logic high, I <sub>OUT</sub> = 1.1A to 3A                                                                                         | -5    |       | 5     | %        |  |

| Accuracy                                               |                     | HFS = logic low, I <sub>OUT</sub> = 1A to 2.2A                                                                                          | -10   |       | 10    |          |  |

|                                                        |                     | HFS = logic high, I <sub>OUT</sub> = 0.5A to 1.1A                                                                                       | -10   |       | 10    | <u> </u> |  |

| Fixed OFF – Time<br>Internal                           | toff                | ROFF shorted to V <sub>DD</sub>                                                                                                         | 16    | 20    | 24    | μs       |  |

| Fixed OFF – Time<br>Constant                           | K <sub>TOFF</sub>   | $R_{ROFF}$ from 15kΩ to 120kΩ                                                                                                           |       | 0.667 |       | μs/kΩ    |  |

| PWM Blanking Time                                      | t <sub>BLK</sub>    |                                                                                                                                         | 1.4   | 2.8   | 4     | μs       |  |

| <b>CURRENT-SENSE MONI</b>                              | TOR                 |                                                                                                                                         |       |       |       |          |  |

| ISEN_ Voltage Range                                    | ISEN                | Voltage range at ISEN_ pins                                                                                                             | 0     |       | 1.1   | V        |  |

| Current-Monitor Scaling Factor                         | Y   NICENI          | HFS = logic low. See the I <sub>SEN</sub> output-<br>current equation in the Current Sense<br>Output (ISEN) - Current monitor section.  |       | 7500  |       | ۸/۸      |  |

|                                                        |                     | HFS = logic high. See the I <sub>SEN</sub> output-<br>current equation in the Current Sense<br>Output (ISEN) - Current monitor section. |       | 3840  |       | A/A      |  |

| Current Monitor<br>Accuracy                            | DIVICEN             | HFS = logic low, I <sub>OUT</sub> = 1.4A to 6A                                                                                          | -5    |       | +5    |          |  |

|                                                        | DKISEN <sub>1</sub> | HFS = logic high, I <sub>OUT</sub> = 0.7A to 3A                                                                                         | -5    |       | +5    | ] ,,     |  |

|                                                        | DICEN               | HFS = logic low, I <sub>OUT</sub> = 0.8A to 1.4A                                                                                        | -10   |       | +10   | - %      |  |

|                                                        | DKISEN <sub>2</sub> | HFS = logic high, I <sub>OUT</sub> = 0.4A to 0.7A                                                                                       | -10   |       | +10   | 1        |  |

| Current-Sense Output<br>-3dB Small-Signal<br>Bandwidth | BW                  |                                                                                                                                         |       | 400   |       | KHz      |  |

## **Electrical Characteristics (continued)**

$(V_M$  = +4.5V to +36V,  $R_{ROFF}$  = from 15k $\Omega$  to 120k $\Omega$ ,  $R_{REF}$  = from 12k $\Omega$  to 72k $\Omega$ , typical values are  $T_A$  = +25°C and  $V_M$  = +24V, limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply-voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Note 1.)

| PARAMETER                  | SYMBOL           | CONDITIONS                                                | MIN | TYP | MAX | UNITS |

|----------------------------|------------------|-----------------------------------------------------------|-----|-----|-----|-------|

| FUNCTIONAL TIMING          |                  |                                                           |     |     |     |       |

| Sleep Time                 | tSLEEP           | SLEEP = logic 1 to logic 0 for OUT_ to become three-state |     |     | 150 | μs    |

| Wake-Up Time from<br>Sleep | twake            | SLEEP = logic 0 to logic 1 to resume normal operation     |     |     | 3   | ms    |

| Enable Time                | t <sub>EN</sub>  | Time from EN_ pin rising edge to driver on                |     |     | 0.4 | μs    |

| Disable Time               | t <sub>DIS</sub> | Time from EN_ pin falling edge to driver off              |     |     | 0.6 | μs    |

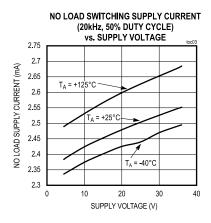

## **Typical Operating Characteristics**

$(V_M = +4.5V \text{ to } +36V; T_A = 25^{\circ}C \text{ unless otherwise noted.})$

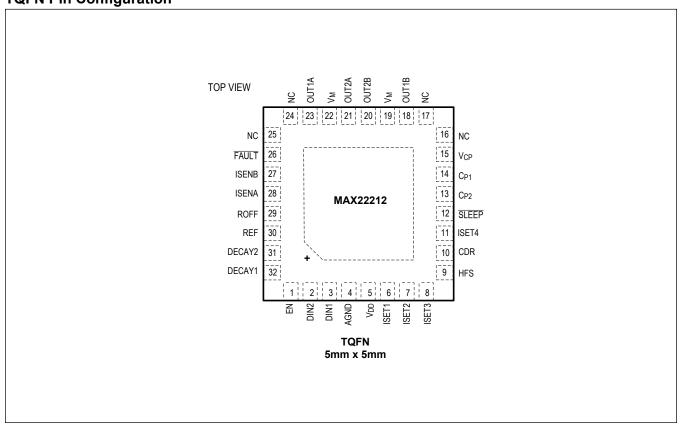

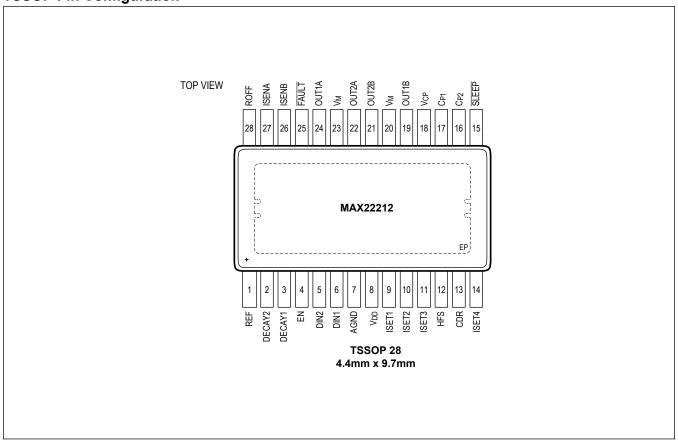

## **Pin Configurations**

## **TQFN Pin Configuration**

## **TSSOP Pin Configuration**

## **Pin Description**

| P      | PIN    | NAME           | E FUNCTION                                                                                                                                                                                                                       |                      |  |

|--------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| TQFN   | TSSOP  | NAME           | FUNCTION                                                                                                                                                                                                                         | TYPE                 |  |

| 30     | 1      | REF            | REF Programmable Current Analog Input. Connect a resistor from REF to GND to set the full scale current.                                                                                                                         |                      |  |

| 29     | 28     | ROFF           | ROFF Time (t <sub>OFF</sub> ) Programmable Resistor Pin. Connect ROFF to V <sub>DD</sub> to use the internal fixed t <sub>OFF</sub> time. Connect a resistor from ROFF to GND to set the fixed OFF time to a desired value.      |                      |  |

| 26     | 25     | FAULT          | FAULT  Active-Low, Open-Drain, Output Fault Indicator. FAULT goes low to indicate that one or more of the protection mechanisms has been activated. Connect a pull-up resistor from FAULT to the microcontroller supply voltage. |                      |  |

| 10     | 13     | CDR            | Open-Drain Output. Current Drive Regulator monitor output                                                                                                                                                                        | Open Drain<br>Output |  |

| 4      | 7      | AGND           | Analog Ground. Connect to ground plane.                                                                                                                                                                                          | GND                  |  |

| 19, 22 | 20, 23 | V <sub>M</sub> | Supply Voltage Input. Connect a $V_M$ -rated $1\mu F$ (minimum) surface-mounted device capacitor from $V_M$ to GND close to the                                                                                                  |                      |  |

## **Pin Description (continued)**

| P              | PIN           |                 | FUNCTION                                                                                                                                     | T)/DE       |

|----------------|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| TQFN           | TSSOP         | NAME            | FUNCTION                                                                                                                                     | TYPE        |

| 5              | 8             | V <sub>DD</sub> | 1.8V Linear Regulator Output. Bypass $V_{DD}$ with a 2.2 $\mu F$ capacitor connected close to the device.                                    | Output      |

| 18, 23         | 19, 24        | OUT1_           | Driver Output Pin. OUT1A and OUT1B are not internally connected and must be externally connected.                                            | Output      |

| 20, 21         | 21, 22        | OUT2_           | Driver Output Pin. OUT2A and OUT2B are not internally connected and must be externally connected.                                            | Output      |

| 27, 28         | 26, 27        | ISEN_           | Current-Sense Output Monitor. ISENA and ISENB are not internally connected and must be connected externally.                                 | Output      |

| 2, 3           | 5, 6          | DIN_            | CMOS PWM Input                                                                                                                               | Logic Input |

| 1              | 4             | EN              | Logic Input Pin. Enable Pin.                                                                                                                 | Logic Input |

| 15             | 18            | V <sub>CP</sub> | Charge-Pump Output. Connect a 1 $\mu$ F capacitor between V <sub>CP</sub> and V <sub>M</sub> as close as possible to the device.             | Output      |

| 14             | 17            | C <sub>P1</sub> | Charge-Pump Flying Capacitor Pin 1. Connect a 22nF capacitor between CP1 and CP2, as close as possible to the device.                        | Output      |

| 13             | 16            | C <sub>P2</sub> | Charge-Pump Flying Capacitor Pin 2. Connect a 22nF capacitor between CP1 and CP2, as close as possible to the device.                        | Output      |

| 12             | 15            | SLEEP           | Active-Low Sleep Pin                                                                                                                         | Logic Input |

| 31, 32         | 2, 3          | DECAY_          | Logic Input. Set the Decay Mode.                                                                                                             | Logic Input |

| 9              | 12            | HFS             | Set Output Current Full Scale. HFS = 0 coefficient is 100%. HFS = 1 coefficient is 50%.                                                      | Logic Input |

| 6, 7, 8, 11    | 9, 10, 11, 14 | ISET_           | Programmable Current Logic Input.                                                                                                            | Logic Input |

| 16, 17, 24, 25 | _             | NC              | No Connection. Not internally connected.                                                                                                     |             |

| EP             | EP            | PGND            | Power GND. Connect to ground plane. The thermal exposed pad (EP) is also the electrical power GND pin and must be properly connected to GND. | GND         |

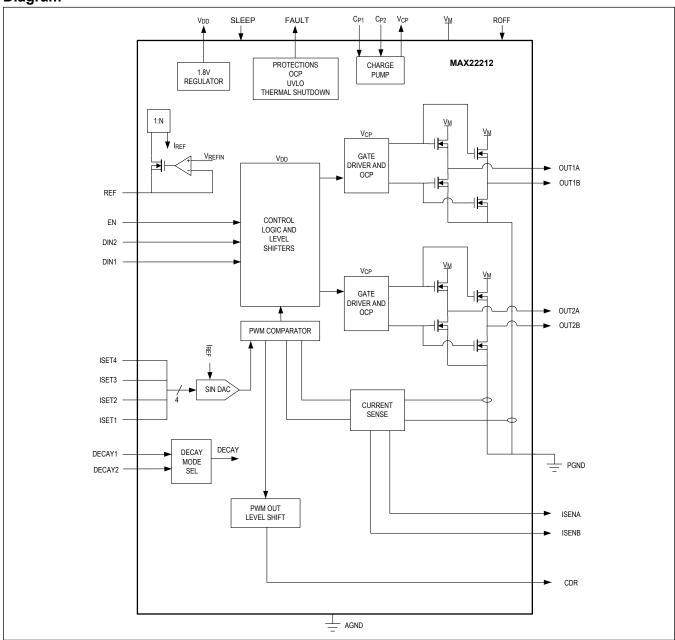

## **Functional Diagrams**

#### **Diagram**

#### **Detailed Description**

The MAX22212 integrates an high current 36V,  $7.6A_{MAX}$  H-Bridge. It can be used to drive one Brushed DC motor or one half of a stepper motor. The H-Bridge FETs feature very low impedance, resulting in high driving efficiency and low heat generation. The typical total  $R_{ON}$  (high-side + low-side) is  $0.125\Omega$ . The H-Bridge can be individually PWM controlled by using three logic inputs (DIN1, DIN2, and EN).

The MAX22212 features an accurate current drive regulation (CDR), which can be used to limit the start-up current of a Brushed DC motor or to control the phase current for stepper operation. The bridge output current is sensed by a non-dissipative Integrated Current Sensing (ICS) and it is then compared with a user configurable setpoint (I<sub>TRIP</sub>). When the bridge current exceeds the setpoint, the device enforces the decay for a fixed OFF-time (t<sub>OFF</sub>). Four different decay methods are supported (Slow Decay, Fast Decay, two Mixed Decay modes). The non-dissipative Integrated Current Sensing eliminates the bulky external power resistors, which are normally required for this function, resulting in dramatic space and power savings compared with mainstream applications using an external sense resistor.

A current proportional to the internally-sensed motor current is output to external pins (ISENA, ISENB). By connecting an external resistor from these pins to GND, a voltage proportional to the motor current is generated. The voltage across this resistor can be used as inputs to ADCs of an external motor controller if the motion control algorithm requires the current/torque information.

In addition, one open-drain output (CDR pin) is asserted every time the internal current regulation takes control of the driver so that the activity of the internal current loop can be monitored.

The maximum user configurable full-scale current ( $I_{FS\_MAX}$ ) can be set up to 7.6A limited by the overcurrent protection. An external resistor connected from REF to GND sets the full-scale current ( $I_{FS}$ ) threshold. An integrated sinusoidal 4-bit DAC allows the user to dynamically modify the current regulation set-point ( $I_{TRIP}$ ) from zero to IFS. Because of thermal considerations, the recommended maximum RMS current on a standard 4-layer PCB is  $4A_{RMS}$ .

In applications in which the requirement of maximum full-scale current is less than 3.8A and high current control accuracy is desired, the half-full-scale (HFS) logic input pin can be set high to halve the current rating and double the low-side FET RON. This results in better current control loop accuracy in the bottom end of the current range.

The MAX22212 features over current protection (OCP), thermal shutdown (TSD), and undervoltage lockout (UVLO) protection. An open-drain active low FAULT pin is activated every time a fault condition is detected. During thermal shutdown and undervoltage lockout events, the driver is disabled until normal operations are restored.

The MAX22212 is available into a small TQFN32 5mm x 5mm package or in a TSSOP28 4.4mm x 9.7mm package.

### Sleep Mode (SLEEP Pin)

The SLEEP pin can be driven low to place the device into the lowest power-consumption mode possible, with all outputs three-stated, the internal circuits biased off, and the charge pump disabled. A pull-down resistor should be connected between SLEEP and GND to ensure the part is disabled whenever this pin is not actively driven. Driving the SLEEP pin high wakes up the device and returns it to normal mode. twake is 3ms (max).

#### **PWM Control**

When the bridge current is below the programmed threshold (i.e.,  $I_{BRIDGE} < I_{TRIP}$ ), the H-Bridge is controlled by three logic inputs (DIN1, DIN2, and EN).

<u>Table 1</u> shows the control Truth Table.

Table 1. MAX22212 Truth Table

| EN | DIN1 | DIN2 | OUT1   | OUT2   | DESCRIPTION                             |

|----|------|------|--------|--------|-----------------------------------------|

| 0  | Х    | Х    | High-Z | High-Z | H-Bridge disabled. High impedance (HiZ) |

| 1  | 0    | 0    | L      | L      | Brake Low; Slow decay                   |

| 1  | 1    | 0    | Н      | L      | Reverse (current from OUT1 to OUT2)     |

| 1  | 0    | 1    | L      | Н      | Forward (current from OUT2 to OUT1)     |

| 1  | 1    | 1    | Н      | Н      | Brake High; Slow decay                  |

## 36V, 7.6A High Current Single H-Bridge with Integrated Current Sense

PWM techniques can be used to vary the output duty cycle and hence to implement motor control.

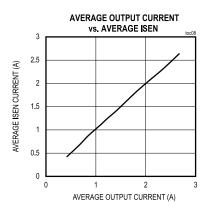

#### **Current-Sense Output (ISEN) - Current Monitor**

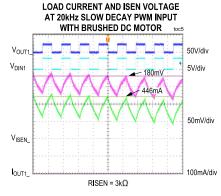

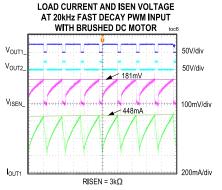

Currents proportional to the internally-sensed motor currents are output to pins ISENA and ISENB. The current is sensed only when the low side FET is ON and sinks current. ISENA must be externally tied to ISENB to sum up the currents and monitor the full-bridge current. When used in this configuration, the ISEN = ISENA + ISENB current reflects the motor current during the Forward, Reverse, and Brake Low (Slow Decay) statuses while it is zeroed during Fast Decay or Coast Status.

The following equation shows the relationship between the current sourced at ISEN = ISENA + ISENB and the motor current.

$$I_{\text{ISEN}}(A) = \frac{I_{\text{OUT}}(A)}{K_{\text{ISEN}}}$$

Equation - ISEN Output Current

in which  $K_{ISEN}$  represents the current mirror factor between the output current and its replica at pin ISEN.  $K_{ISEN}$  is typically 7500 KA/A (when HFS = 0). For instance, if the instantaneous output current is 2A, the current sourced at ISEN is  $266\mu$ A.

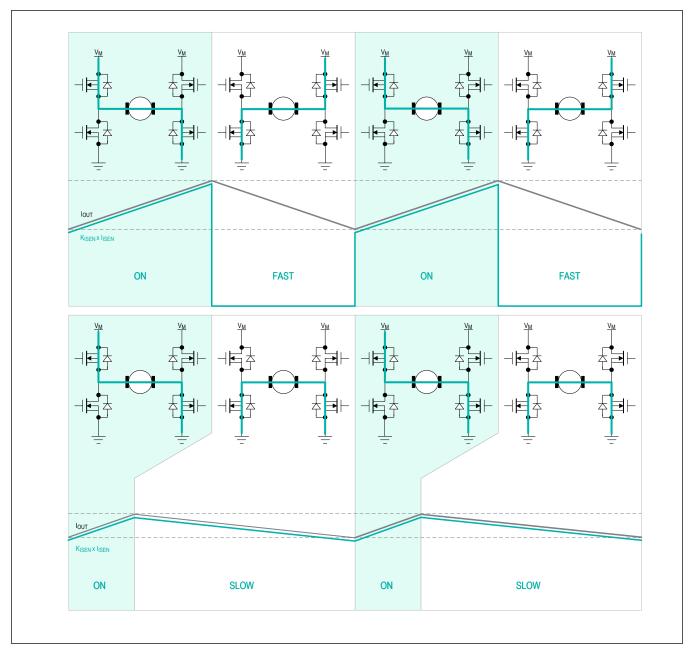

Figure 1 shows an idealized behavior of the ISEN = ISENA + ISENB current when Slow or Fast Decay are used. Blanking Times, delays, and rise/fall edges are ignored.

Figure 1. ISEN Current

By connecting an external signal resistor,  $R_{ISEN}$ , between ISENA = ISENB and GND, a voltage proportional to the motor current is generated. The voltage across the  $R_{ISEN}$  can be input into the ADC of an external controller in applications in which the motor control algorithm requires the current/torque information. The system designer can choose an  $R_{ISEN}$  value so that the peak voltage meets the ADC input full-scale requirement. The following equation shows the formula to calculate  $R_{ISEN}$  once the ADC full-scale voltage ( $V_{FS}$ ) and the maximum operating current ( $I_{MAX}$ ) are known.

$$R_{\text{ISEN}}(\Omega) = K_{\text{ISEN}} \times \frac{V_{\text{FS}}(V)}{I_{\text{MAX}}(A)}$$

The R<sub>ISEN</sub> value also sets the output impedance of the Current-Sense Output circuit (ISEN\_ output impedance). Normally, the input impedance of the ADC is much higher than R<sub>ISEN</sub> enabling a direct connection to the ISEN pin without attenuation. If a low input impedance ADC was used, a preamplifier (buffer) would be required.

The Current-Sense Output circuit bandwidth and step response performances (see Specifications) ensure the current monitor tracks the driver current in PWM motor drive application.

#### **Current Drive Regulation**

The MAX22212 features embedded current drive regulation (CDR). The embedded CDR provides an accurate control of the current flowing into the motor windings. The bridge current is sensed by a non-dissipative Integrated Current Sensing (ICS) circuit and it is then compared with the threshold current ( $I_{TRIP}$ ). As soon as the bridge current exceeds the threshold, the device enforces the decay for a fixed OFF-time ( $t_{OFF}$ ). The device supports different decay modes as described in the following paragraphs. Once  $t_{OFF}$  has elapses, the driver is re-enabled for the next PWM cycle. During current regulation, the PWM duty cycle and frequency depend on the supply voltage, on the motor inductance, and on motor speed and load conditions. The  $t_{OFF}$  duration can be configured with an external resistor connected to the ROFF pin.

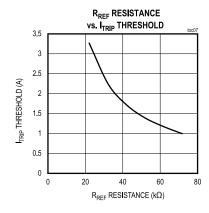

#### Setting the Full-Scale Current - IFS

Connect a resistor from REF to GND to set the full-scale chopping current IFS.

The following equation shows the typical I<sub>FS</sub> current as a function of the R<sub>REF</sub> shunt resistor connected to pin REF. The proportionality constant K<sub>IFS</sub> is typically 72KV if HFS = 0 and 36.8KV if HFS = 1. The external resistor recommended range is from  $9.5K\Omega$  to  $100K\Omega$ .

$$I_{FS} = \frac{K_{IFS}(KV)}{R_{REF}(K\Omega)}$$

When HFS logic input pin is driven logic low, the power FETs  $R_{DS(ON)}$  is set to a minimum of  $0.125\Omega$  (high-side + low-side). When HFS logic input pin is set logic high, the power FETs have higher  $R_{DS(ON)}$  of  $0.18\Omega$  (high-side + low-side). This operating mode is recommended for applications in which the maximum current does not exceed 3.8A and high accuracy at the bottom end of the current range is desirable. Table 2 summarizes the HFS settings.

**Table 2. HFS Truth Table**

| HFS | MAXIMUM FS<br>SETTING | TYPICAL R <sub>DS(ON)</sub><br>(HIGH-SIDE +<br>LOW-SIDE) | NOTES                                                                                                                       |  |

|-----|-----------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| 0   | 7.6A                  | 0.125Ω                                                   | Optimized efficiency and extended operating range up to 7.6AFS                                                              |  |

| 1   | 3.8A                  | 0.18Ω                                                    | Reduced operating range up to 3.8A <sub>FS</sub> . Improved current accuracy control at the bottom end of the current range |  |

#### **Bridge Current Control**

Four input pins, ISET[4:1], are used to program the output current. <u>Table 3</u> shows the bridge current levels for each input combination.

Table 3. H-Bridge ISET Pins Truth Table

| ISET4 | ISET3 | ISET2 | ISET1 | CURRENT<br>(% OF IFS) |

|-------|-------|-------|-------|-----------------------|

| 0     | 0     | 0     | 0     | 100                   |

| 0     | 0     | 0     | 1     | 99.2                  |

| 0     | 0     | 1     | 0     | 97.7                  |

| 0     | 0     | 1     | 1     | 95.3                  |

| Table of the Bridge to Elit mo tradit rable (continuou) |   |   |   |      |  |

|---------------------------------------------------------|---|---|---|------|--|

| 0                                                       | 1 | 0 | 0 | 91.4 |  |

| 0                                                       | 1 | 0 | 1 | 86.7 |  |

| 0                                                       | 1 | 1 | 0 | 81.3 |  |

| 0                                                       | 1 | 1 | 1 | 74.2 |  |

| 1                                                       | 0 | 0 | 0 | 67.2 |  |

| 1                                                       | 0 | 0 | 1 | 58.6 |  |

| 1                                                       | 0 | 1 | 0 | 50   |  |

| 1                                                       | 0 | 1 | 1 | 40.6 |  |

| 1                                                       | 1 | 0 | 0 | 31.3 |  |

| 1                                                       | 1 | 0 | 1 | 21.1 |  |

| 1                                                       | 1 | 1 | 0 | 10.2 |  |

| 1                                                       | 1 | 1 | 1 | 0    |  |

**Table 3. H-Bridge ISET Pins Truth Table (continued)**

#### Setting the Fixed OFF Time (t<sub>OFF</sub>)

The current regulation circuit is based on a constant  $t_{OFF}$  PWM control. If during the ON phase, the bridge current exceeds the target  $l_{TRIP}$  threshold, the OFF phase begins and the current decays. The OFF phase has a fixed time duration  $t_{OFF}$ .

The  $t_{OFF}$  can be configured to a desired value by connecting an external resistor to pin ROFF. When the ROFF pin is shorted to  $V_{DD}$ , the  $t_{OFF}$  time is internally set at a fixed value (20µs typical). By connecting an external resistor to the pin ROFF, the user can configure  $t_{OFF}$  as shown in the following equation in which  $t_{ROFF}$  is an external resistor (in  $t_{ROFF}$ ) connected from the ROFF pin to GND and  $t_{ROFF}$  is an internal constant equal to 0.667µs/ $t_{ROFF}$ ).

$$t_{OFF}(\mu s) = R_{ROFF} \times K_{TOFF}$$

The tope can be programmed from a range of 10µs to 80µs.

#### **CDR Open-Drain Output**

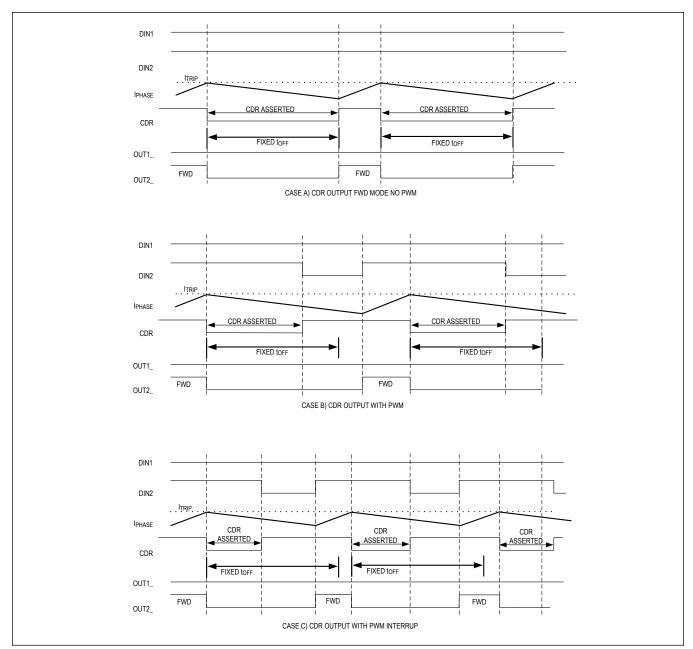

This pin is an active-low open-drain output, which is asserted during the fixed decay time interval (t<sub>OFF</sub>) enforced by the current drive regulation loop. This way, an external controller can monitor if the integrated current loop has taken control of the driver overwriting the status of the PWM logic inputs (DIN1, DIN2). The CDR signal can be used by the external controller for several reasons and provides information about the actual load during current regulation.

In the use case in which the PWM logic inputs are permanently held in Forward or Reverse mode and motor control is entirely entrusted to the internal Current Drive Regulation loop, the CDR pin outputs a PWM logic signal which is a replica of the PWM voltage applied to the load. By processing this signal and comparing its duty cycle with the expected one, a stall detection algorithm can be implemented. The CDR output can also be used as a trigger signal for an external ADC when sampling the ISEN current.

A pullup resistor must be connected from the CDR pins to the controller voltage supply.

The timing diagram in Figure 2 shows the behavior of this function when the motor spins in forward direction with DIN2 held firmly high (Case A) or when DIN2 is toggling (Cases B and C), respectively. The CDR output is asserted only when the decay mode is forced by the internal Current Regulation loop. Note that any PWM transition by the current drive regulation loop resets the fixed off time of the CDR circuit. In Case B, the actual Decay Interval is longer than toff, whereas in Case C, the actual Decay Off interval is shorter.

Figure 2. CDR Monitor Timing Diagram

#### **Setting the Decay Mode**

Two logic input pins allow to set the Decay Mode during  $t_{OFF}$ . The MAX22212 supports slow, fast, and two different mixed decay modes.

<u>Table 4</u> shows the Truth Table for the Decay Mode selection.

#### **Table 4. Decay Mode Truth Table**

| DECAY2 | DECAY1 | DECAY MODE |

|--------|--------|------------|

| 0      | 0      | Slow       |

#### **Table 4. Decay Mode Truth Table (continued)**

| 0 | 1 | Mixed 30% Fast/70% Slow |  |  |

|---|---|-------------------------|--|--|

| 1 | 0 | Mixed 60% Fast/40% Slow |  |  |

| 1 | 1 | Fast                    |  |  |

#### **Fault Protection**

#### Overcurrent Protection – (OCP)

An overcurrent protection (OCP) protects the device against short circuits to the rails (supply voltage and ground) and across the outputs (OUTA and OUTB). The OCP threshold is set at 7.6A minimum. If the output current is larger than the OCP threshold for longer than the Over Current Protection blanking time (t<sub>OCP</sub>), an OCP event is detected.

When an OCP event is detected, the H-Bridge is immediately disabled, and a fault indication is output on pin FAULT. The H-Bridge is kept in a high impedance mode for 3ms (see t<sub>RETRY</sub> specification). The H-Bridge is then re-enabled according to the current state. If the short circuit is still present, this cycle repeats. Otherwise, normal operation resumes. Avoid prolonged operation under the short-circuit failure mode as a prolonged OCP event affects the device reliability.

#### **Undervoltage-Lockout Protection**

When the  $V_M$  supply voltage is below the UVLO threshold, all OUT\_ outputs are three-stated and the  $\overline{FAULT}$  pin is driven low. The OUT\_ outputs automatically return to their current state (defined by EN\_ and DIN\_) when the  $V_M$  supply voltage exceeds the OVLO threshold (max) and  $\overline{FAULT}$  is driven high.

## **Ordering Information**

| PART NUMBER   | TEMPERATURE RANGE | PIN-PACKAGE              |

|---------------|-------------------|--------------------------|

| MAX22212ATJ+T | -40°C to +125°C   | 32 TQFN - 5mm x 5mm      |

| MAX22212AUI+T | -40°C to +125°C   | 28 TSSOP - 4.4mm x 9.7mm |

<sup>+</sup> Denotes a lead(Pb)-free/RoHS-compliant package.

T Denotes tape-and-reel.

## 36V, 7.6A High Current Single H-Bridge with **Integrated Current Sense**

## **Revision History**

| REVISION NUMBER | REVISION DATE | DESCRIPTION                                                                                                                                                 | PAGES<br>CHANGED            |

|-----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 0               | 3/23          | Release for Market Intro                                                                                                                                    | _                           |

| 1               | 1/24          | Updated Absolute Maximum Ratings, Package Information, Electrical Characteristics, Pin Description, Detailed Description, and Ordering Information sections | 6 –9, 12, 13, 15,<br>21, 22 |