### **Adaptive Digital Compensation of Analog Circuit Imperfections for Cascaded Delta-Sigma Analog-to-Digital Converters**

Technical Report

Oregon State University

August 20, 1999 Revised Dec. 31, 1999 Péter Kiss kpeter@ece.orst.edu

### Abstract

Cascaded delta-sigma (MASH) analog-to-digital converters offer a good compromise between high accuracy, robust stability and speed. However, they are very sensitive to analog circuit imperfections.

In this thesis, a cascaded 2-0 delta-sigma ADC architecture with 1–1.5-bit first stage and 10–12-bit second stage was investigated. It uses an adaptive digital FIR filter to reduce the noise leakage due to the imperfect error cancellation. For online adaptation, a pseudo-random test signal was injected into the first stage and a simplified block-LMS algorithm, the sign-sign-block-least-mean-square algorithm, was used to update the coefficients of the adaptation filter.

The basic theory and some design considerations were developed under a previous work. However, the reported effective results (signal-to-noise+distortion ratio SNDR=75 dB @  $f_B=62.5$ -kHz signal bandwidth) validated only the principle of adaptive noise-leakage compensation, leaving open the question of how to improve this initial performance.

The current thesis deals with the improvements to this technique, and its application to a very fast (sampling frequency  $f_S=100$  MHz, oversampling ratio OSR=8-16, signal bandwidth  $f_B=3-6$  MHz) and high-accuracy (signal-to-noise ratio SNR=13-15-bit) implementation. Such converters have wide applications in high-speed instrumentation, high-definition video, imaging, radar and digital communications. Available behavioral and circuit-level simulation results have confirmed an achievable 13-bit @ 6-MHz ADC, which is a useful performance for a state-of-the-art data converter.

### Acknowledgements

I feel privileged to complete my Ph.D. degree under the guidance and expertise of Professor Eugen Pop. I appreciate his deep understanding and passion to measurements. I wish to thank for his help, ideas, feedback, and advice.

This thesis was finalized during my one-year stay at Oregon State University. I have been fortunate enough to work under the supervision of Professor Gabor C. Temes. I have benefited from his intuition in analog circuits design, and from his emphasis on clarity in presentation. I wish to thank for his help, ideas, feedback, support, and friendship.

At Oregon State University I have been working with many wonderful people with whom I have had fruitful discussions. They have included Professor Un-Ku Moon, Professor Jesper Steensgaard, Professor John Stonick, Tetsuya Kajita, Mustafa Keskin, Emad Bidari, Lei Wu, and Zhiliang Zheng. In particular, I would like to thank José Silva for his help in circuit-design issues, and for reviewing my thesis. Also, I wish to thank Andreas Wiesbauer for sharing some of his Matlab codes, and Tao Sun for his advice based on his experience in adaptive MASH ADCs. I would like to thank Professor Ion Boldea and Jánosi Lóránd for their warm recommendation, which made my visit to OSU possible. Finally, I wish to thank Adrian and Dorina Avram, Aristotel Popescu, Ibolya Temes, James and Cindy Cauthorn, Michael Giles, Sarah O'Leary, and Patrick Voltz for their help in my accommodation to Corvallis.

This research has been supported by CDADIC (National Science Foundation Center for Design of Analog-Digital Integrated Circuits), and partly by Lucent Technologies. I would like to thank for their financial support.

The first three years of my Ph.D. program I have spent at "Politehnica" University of Timişoara, being member of a dynamic faculty. I believe that during these years I have gained a lot of theoretical and practical knowledge. I wish to thank Professor Liviu Toma, Professor Dan Stoiciu, Professor Traian Jurca, Professor Virgiliu Tiponuţ, Ion-Alexandru Neag, Virgiliu Ivăşchescu, Mischie Septimiu, Robert Pazsitka, and Corneliu Cristea. In particular, I have benefited from the technical and non-technical discussions, and friendship of Andrei Cimponeriu.

Special thanks to my parents, Elemér and Juliánna-Ágnes, for their constant love and encouragement. Finally, I would like to thank my lovely wife, Erika, for her patience and understanding, and for filling my life with color and happiness.

## Contents

| 1 | Intr | oductio  | 'n                                           | 1  |

|---|------|----------|----------------------------------------------|----|

|   | 1.1  | State-o  | of-the-Art Nyquist-Rate and Delta-Sigma ADCs | 1  |

|   | 1.2  | The Pr   | roposed ADC                                  | 6  |

|   | 1.3  | Thesis   | Structure                                    | 7  |

| 2 | Sing | gle-Looj | p Delta-Sigma ADCs                           | 9  |

|   | 2.1  | -        | ization                                      | 9  |

|   |      | 2.1.1    | Quantization Error                           | 11 |

|   |      | 2.1.2    | Performance Modeling                         | 13 |

|   | 2.2  | Oversa   | ampling Converters                           | 15 |

|   | 2.3  |          | -Shaping Converters                          | 16 |

|   |      | 2.3.1    | Basic Operation                              | 18 |

|   |      | 2.3.2    | Circuit-Level Considerations                 | 19 |

|   |      | 2.3.3    | Single-Bit Quantizer                         | 20 |

|   | 2.4  | First-C  | Order Delta-Sigma ADCs                       | 20 |

|   |      | 2.4.1    | Performance Modeling                         | 21 |

|   |      | 2.4.2    | Circuit-Level Implementation                 | 22 |

|   |      | 2.4.3    | Time-Domain Analysis                         | 23 |

|   |      | 2.4.4    | Performance Limitations                      | 23 |

|   | 2.5  | Secon    | d-Order Delta-Sigma ADCs                     | 25 |

|   |      | 2.5.1    | Performance Modeling                         | 25 |

|   |      | 2.5.2    | Performance Criteria                         | 29 |

|   |      | 2.5.3    | Circuit-Level Implementation                 | 29 |

|   |      | 2.5.4    | Time-Domain Analysis                         | 30 |

|   |      | 2.5.5    | Linearized Model Limitations                 | 31 |

|   |      | 2.5.6    | Non-Unity-Gain Signal Transfer Function      | 34 |

|   |      | 2.5.7    | Tri-Level Quantizer                          | 34 |

|   |      | 2.5.8    | Performance Limitations                      | 38 |

|   |      | 2.5.9    | Adding a Forward Path                        | 39 |

|   | 2.6  | Highe    | r-Order Delta-Sigma ADCs                     | 42 |

|   | 2.7  | -        | usions                                       | 44 |

| 3 | Cas  | caded I  | Delta-Sigma ADCs                             | 45 |

|   | 3.1  |          | ded 2-0 Delta-Sigma ADC Structures           | 46 |

|   |      | 3.1.1    | Performance Modeling                         | 47 |

|   |                                                                                                                    | 3.1.2 Interstage Coefficients                                                                                                                                                                                                              | 48                                                                                      |

|---|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|   |                                                                                                                    | 3.1.3 Tri-Level Quantizer                                                                                                                                                                                                                  | 50                                                                                      |

|   |                                                                                                                    | 3.1.4 Performance Specifications and Limitations                                                                                                                                                                                           | 52                                                                                      |

|   | 3.2                                                                                                                | Analog Circuit Imperfections in SC Cascaded $\Delta\Sigma$ ADCs                                                                                                                                                                            | 54                                                                                      |

|   |                                                                                                                    | 3.2.1 Nonidealities in Switched-Capacitor Integrators                                                                                                                                                                                      | 55                                                                                      |

|   |                                                                                                                    | 3.2.2 Noise Leakage in Cascaded Delta-Sigma ADCs                                                                                                                                                                                           | 56                                                                                      |

|   | 3.3                                                                                                                | Conclusions                                                                                                                                                                                                                                | 58                                                                                      |

| 4 | Ada                                                                                                                | ptive Digital Compensation for Cascaded 2-0 $\Delta\Sigma$ ADCs                                                                                                                                                                            | 59                                                                                      |

|   | 4.1                                                                                                                | Adaptive Digital Compensation of the Noise Leakage                                                                                                                                                                                         | 60                                                                                      |

|   |                                                                                                                    | 4.1.1 Adaptive Digital Compensation Algorithms                                                                                                                                                                                             | 61                                                                                      |

|   |                                                                                                                    | 4.1.2 Test-Signal Approach                                                                                                                                                                                                                 | 63                                                                                      |

|   |                                                                                                                    | 4.1.3 Hardware Implementation of the Adaptive Filter                                                                                                                                                                                       | 65                                                                                      |

|   | 4.2                                                                                                                | Adaptive Digital Compensation Process                                                                                                                                                                                                      | 66                                                                                      |

|   |                                                                                                                    | 4.2.1 Parameters for the Adaptive Compensation Process                                                                                                                                                                                     | 67                                                                                      |

|   |                                                                                                                    | 4.2.2 Adaptation Process Optimization                                                                                                                                                                                                      | 71                                                                                      |

|   |                                                                                                                    | 4.2.3 Shaped or Unshaped Test Signal                                                                                                                                                                                                       | 76                                                                                      |

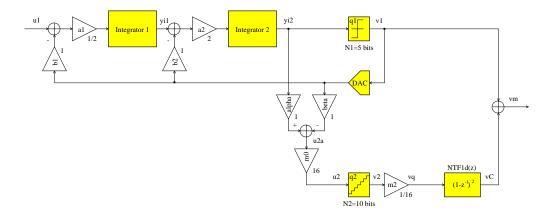

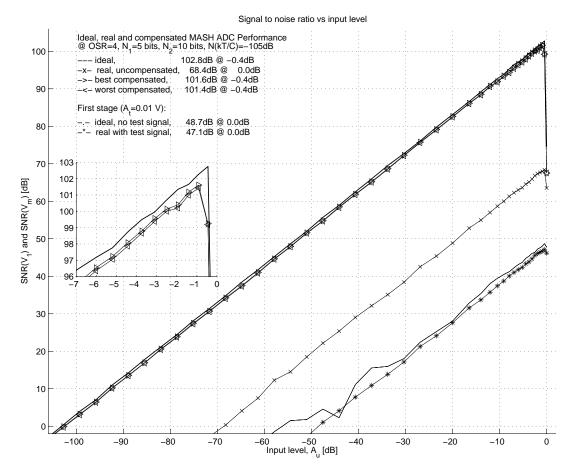

|   | 4.3                                                                                                                | 2-0 MASH ADC with 5-Bit First-Stage Quantization                                                                                                                                                                                           | 78                                                                                      |

|   | 4.4                                                                                                                | Conclusions                                                                                                                                                                                                                                | 80                                                                                      |

|   |                                                                                                                    |                                                                                                                                                                                                                                            |                                                                                         |

| 5 | Prot                                                                                                               | totype Chip Design                                                                                                                                                                                                                         | 81                                                                                      |

| 5 | <b>Pro</b><br>5.1                                                                                                  | First Stage of the MASH ADC                                                                                                                                                                                                                | 81                                                                                      |

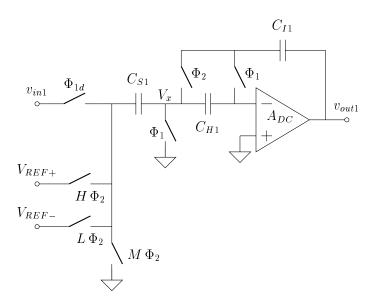

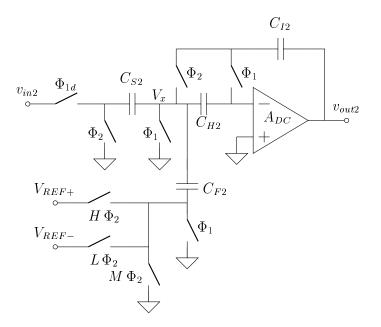

| 5 |                                                                                                                    | First Stage of the MASH ADC      5.1.1      Integrators                                                                                                                                                                                    | 81<br>82                                                                                |

| 5 |                                                                                                                    | First Stage of the MASH ADC5.1.1Integrators5.1.2Operational Amplifiers                                                                                                                                                                     | 81<br>82<br>84                                                                          |

| 5 |                                                                                                                    | First Stage of the MASH ADC5.1.1Integrators5.1.2Operational Amplifiers5.1.3Tri-Level Quantizer                                                                                                                                             | 81<br>82<br>84<br>87                                                                    |

| 5 |                                                                                                                    | First Stage of the MASH ADC5.1.1Integrators5.1.2Operational Amplifiers5.1.3Tri-Level QuantizerSecond Stage of the MASH ADC                                                                                                                 | 81<br>82<br>84<br>87<br>90                                                              |

| 5 | 5.1                                                                                                                | First Stage of the MASH ADC5.1.1Integrators5.1.2Operational Amplifiers5.1.3Tri-Level QuantizerSecond Stage of the MASH ADC5.2.1Analog Subtraction                                                                                          | 81<br>82<br>84<br>87<br>90<br>90                                                        |

| 5 | 5.1                                                                                                                | First Stage of the MASH ADC5.1.1Integrators5.1.2Operational Amplifiers5.1.3Tri-Level QuantizerSecond Stage of the MASH ADC                                                                                                                 | 81<br>82<br>84<br>87<br>90<br>90<br>90                                                  |

| 5 | 5.1                                                                                                                | First Stage of the MASH ADC5.1.1Integrators5.1.2Operational Amplifiers5.1.3Tri-Level QuantizerSecond Stage of the MASH ADC5.2.1Analog Subtraction5.2.2Multibit QuantizerNoise Leakage Compensation Logic                                   | 81<br>82<br>84<br>87<br>90<br>90<br>90<br>93                                            |

| 5 | 5.1<br>5.2                                                                                                         | First Stage of the MASH ADC5.1.1Integrators5.1.2Operational Amplifiers5.1.3Tri-Level QuantizerSecond Stage of the MASH ADC5.2.1Analog Subtraction5.2.2Multibit QuantizerNoise Leakage Compensation Logic5.3.1Test-Signal Generator         | 81<br>82<br>84<br>87<br>90<br>90<br>90<br>93<br>93                                      |

| 5 | 5.1<br>5.2                                                                                                         | First Stage of the MASH ADC5.1.1Integrators5.1.2Operational Amplifiers5.1.3Tri-Level QuantizerSecond Stage of the MASH ADC5.2.1Analog Subtraction5.2.2Multibit QuantizerNoise Leakage Compensation Logic                                   | 81<br>82<br>84<br>87<br>90<br>90<br>90<br>93                                            |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                                                      | First Stage of the MASH ADC5.1.1Integrators5.1.2Operational Amplifiers5.1.3Tri-Level QuantizerSecond Stage of the MASH ADC5.2.1Analog Subtraction5.2.2Multibit QuantizerSolution5.3.1Test-Signal GeneratorCircuit-Level Simulation Results | 81<br>82<br>84<br>87<br>90<br>90<br>90<br>93<br>93                                      |

| 5 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                                        | First Stage of the MASH ADC5.1.1Integrators5.1.2Operational Amplifiers5.1.3Tri-Level QuantizerSecond Stage of the MASH ADC5.2.1Analog Subtraction5.2.2Multibit QuantizerSolution5.3.1Test-Signal GeneratorCircuit-Level Simulation Results | 81<br>82<br>84<br>87<br>90<br>90<br>90<br>93<br>93<br>93<br>94                          |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Con</li> <li>6.1</li> </ul>              | First Stage of the MASH ADC         5.1.1       Integrators         5.1.2       Operational Amplifiers         5.1.3       Tri-Level Quantizer         Second Stage of the MASH ADC                                                        | 81<br>82<br>84<br>87<br>90<br>90<br>90<br>93<br>93<br>93<br>94<br>97<br><b>99</b>       |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Con</li> <li>6.1</li> <li>6.2</li> </ul> | First Stage of the MASH ADC         5.1.1       Integrators         5.1.2       Operational Amplifiers         5.1.3       Tri-Level Quantizer         Second Stage of the MASH ADC                                                        | 81<br>82<br>84<br>87<br>90<br>90<br>90<br>93<br>93<br>93<br>94<br>97<br><b>99</b><br>99 |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>Con</li> <li>6.1</li> </ul>              | First Stage of the MASH ADC         5.1.1       Integrators         5.1.2       Operational Amplifiers         5.1.3       Tri-Level Quantizer         Second Stage of the MASH ADC                                                        | 81<br>82<br>84<br>87<br>90<br>90<br>90<br>93<br>93<br>93<br>94<br>97<br><b>99</b><br>99 |

## **List of Figures**

| 1.1  | State-of-the-art ADCs                                                  | 2  |

|------|------------------------------------------------------------------------|----|

| 1.2  | Figure of merit for state-of-the-art ADCs                              | 4  |

| 2.1  | General analog-to-digital converter                                    | 10 |

| 2.2  | Ideal N-bit quantizer                                                  | 11 |

| 2.3  | Transfer function of an ideal N-bit quantizer                          | 11 |

| 2.4  | Statistical properties of the quantization error                       | 13 |

| 2.5  | The spectrum of a quantized sinewave                                   | 14 |

| 2.6  | General oversampling analog-to-digital converter                       | 16 |

| 2.7  | The power spectral density of the quantization noise                   | 17 |

| 2.8  | General structure of a noise-shaping ADC                               | 17 |

| 2.9  | The spectrum of a single-bit quantized sinewave                        | 21 |

| 2.10 | First-order delta-sigma ADC                                            | 22 |

| 2.11 | Switched-capacitor first-order delta-sigma ADC                         | 23 |

| 2.12 | Time-domain model of the first-order delta-sigma ADC                   | 24 |

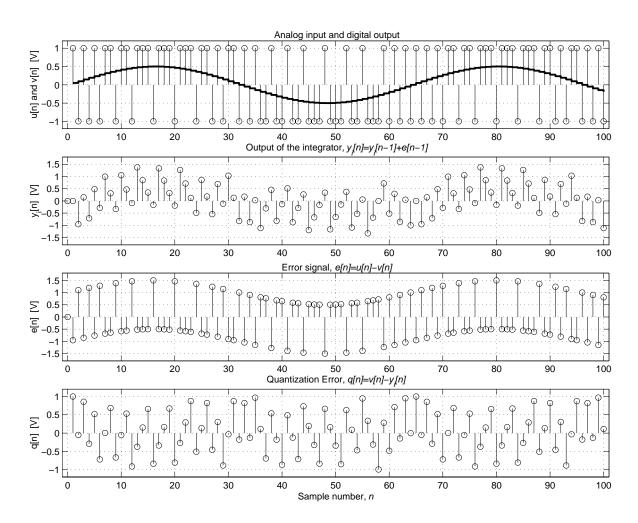

| 2.13 | First-order $\Delta \Sigma$ ADC response in time to a sinewave input   | 24 |

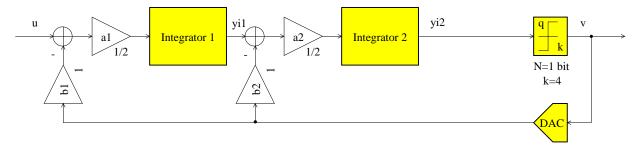

|      | Second-order single-bit delta-sigma ADC                                | 25 |

| 2.15 | Linearized model of the second-order delta-sigma ADC                   | 26 |

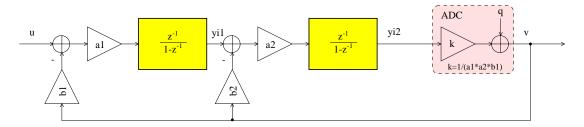

|      | Noise transfer function of the second-order delta-sigma ADC            | 28 |

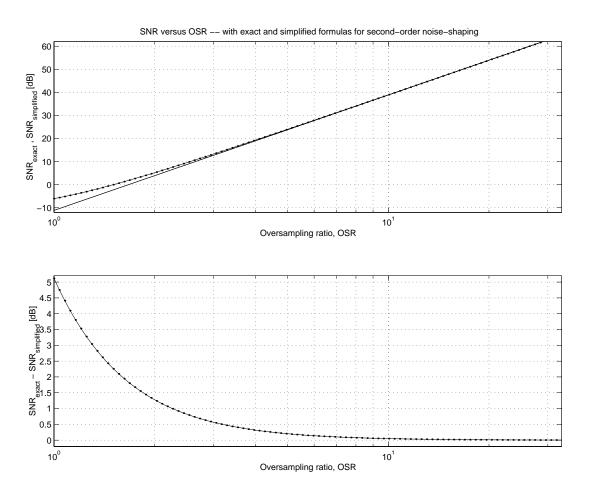

| 2.17 | Signal-to-noise ratio versus oversampling ratio                        | 28 |

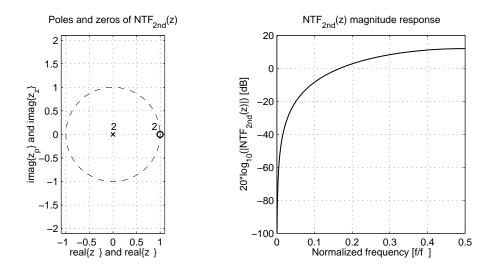

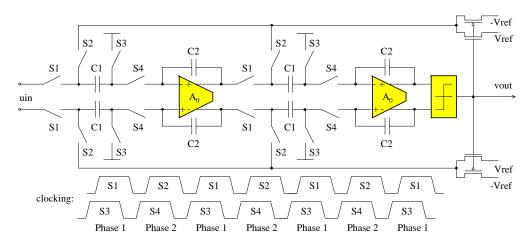

| 2.18 | Switched-capacitor second-order delta-sigma ADC                        | 30 |

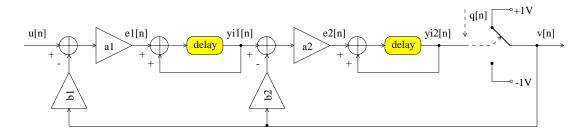

| 2.19 | Time-domain model of the second-order delta-sigma ADC                  | 32 |

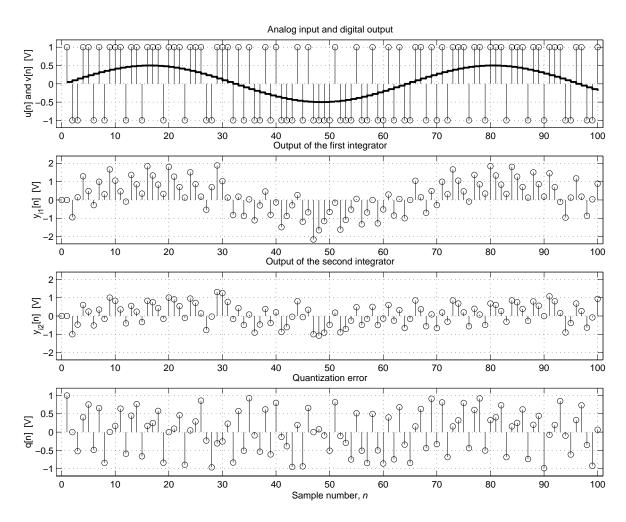

| 2.20 | Second-order $\Delta\Sigma$ ADC response in time to a sinewave input   | 32 |

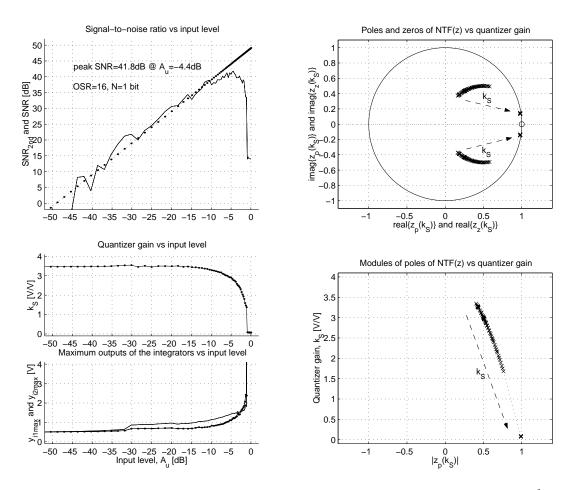

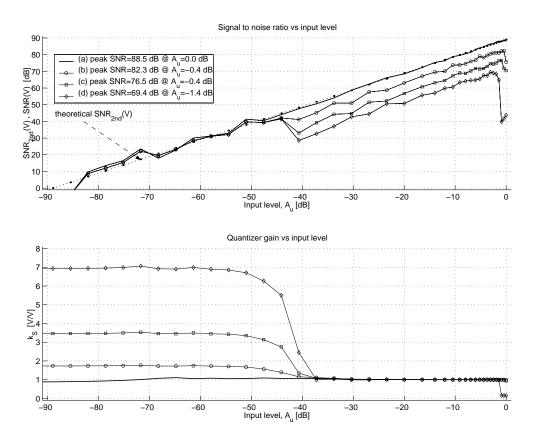

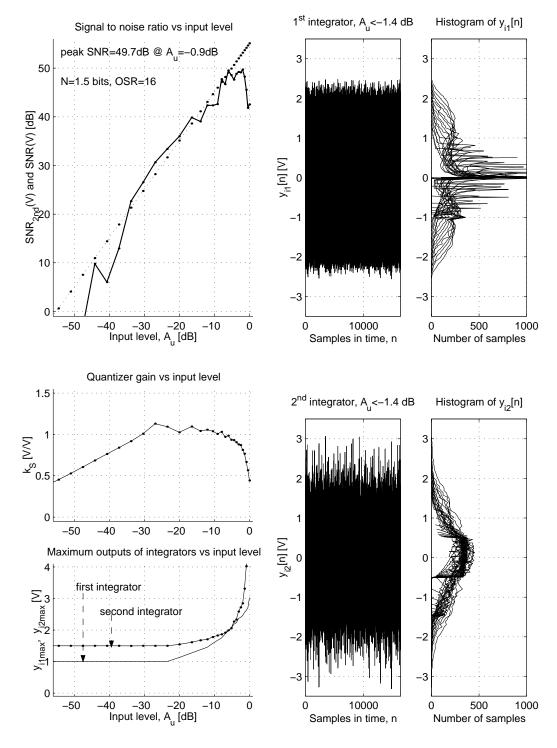

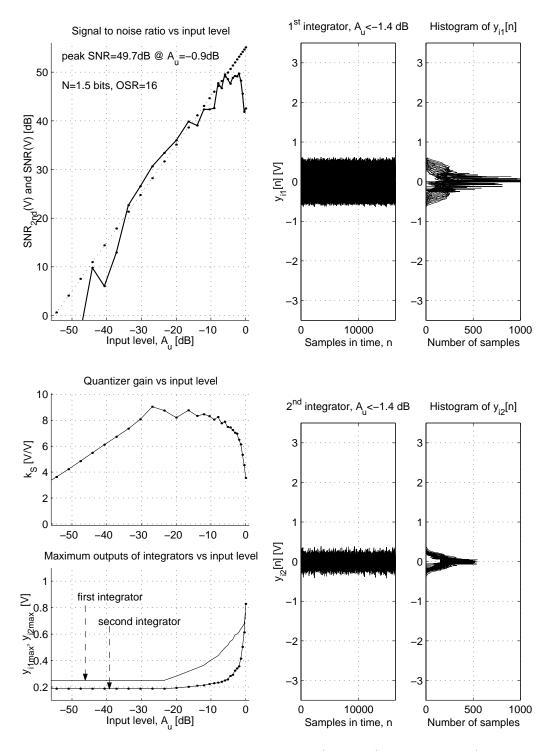

| 2.21 | Performance of the second-order single-bit delta-sigma ADC             | 33 |

| 2.22 | Stability analysis of the second-order delta-sigma ADC                 | 35 |

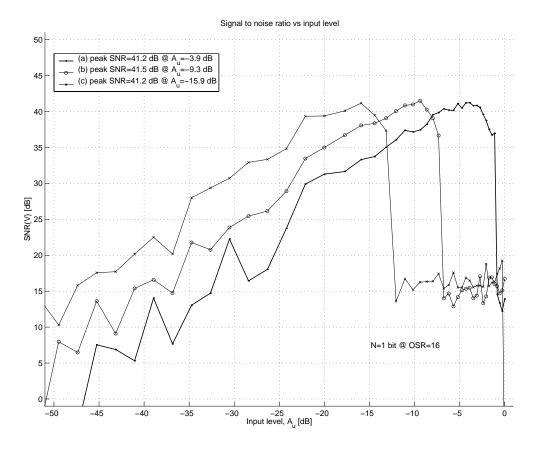

| 2.23 | SNR performance of second-order single-bit delta-sigma ADCs .          | 36 |

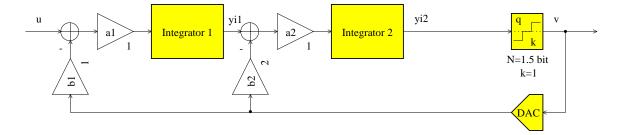

| 2.24 | Second-order tri-level delta-sigma ADC                                 | 37 |

| 2.25 | Comparative performance of bi- and tri-level modulators                | 38 |

| 2.26 | Second-order multibit delta-sigma ADC's SNR curve                      | 39 |

| 2.27 | Internal voltage swing analysis (1)                                    | 40 |

| 2.28 | Internal voltage swing analysis (2)                                    | 41 |

| 2.29 | General delta-sigma modulator with a forward path                      | 42 |

| 3.1  | General structure of a cascaded delta-sigma modulator                  | 46 |

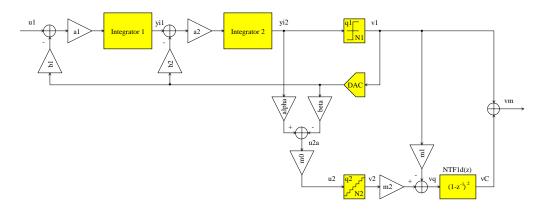

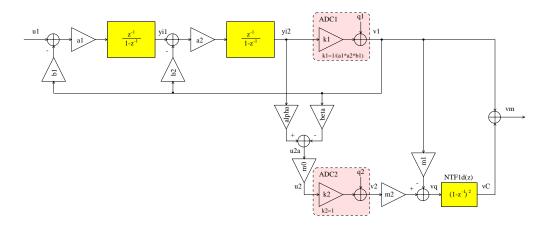

| 3.2  | Standard structure of the cascaded 2-0 delta-sigma ADC                 | 47 |

| 3.3  | Improved standard structure of the cascaded 2-0 $\Delta\Sigma$ ADC $~$ | 47 |

| 3.4  | Simplified structure of the cascaded 2-0 delta-sigma ADC             | 47 |

|------|----------------------------------------------------------------------|----|

| 3.5  | General structure of the cascaded 2-0 delta-sigma ADC                | 48 |

| 3.6  | Linearized model of the general cascaded 2-0 delta-sigma ADC .       | 49 |

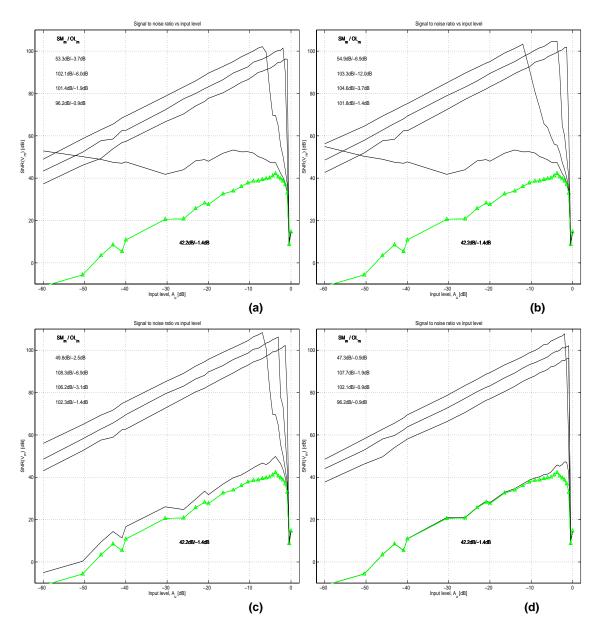

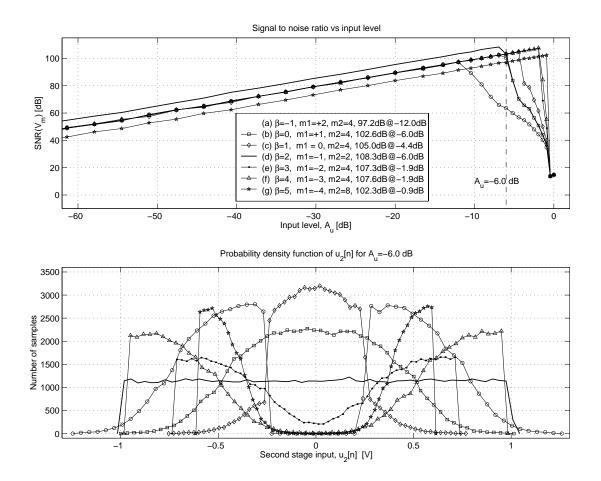

| 3.7  | Comparative SNR analysis between 2-0 MASH structures                 | 51 |

| 3.8  | $SNR(V_m)$ versus $PDF(u_2)$                                         | 52 |

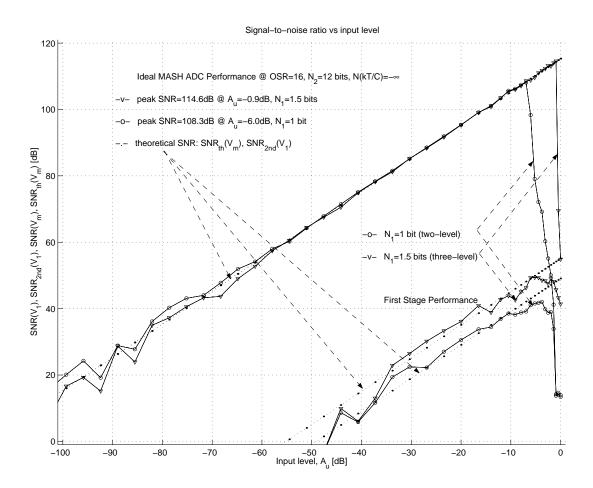

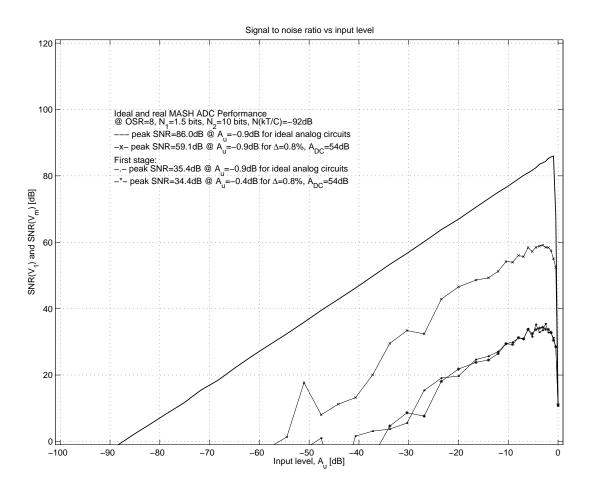

| 3.9  | Comparative performance of the general MASH                          | 53 |

| 3.10 | Ideal and real cascaded 2-0 delta-sigma ADC SNR performance .        | 54 |

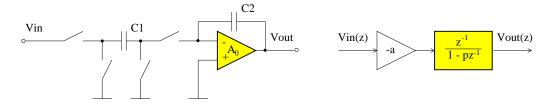

| 3.11 | Switched-capacitor integrator and its linear model                   | 55 |

| 3.12 | Noise leakage in the general cascaded 2-0 delta-sigma ADC            | 57 |

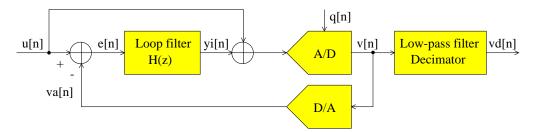

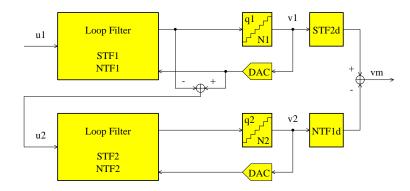

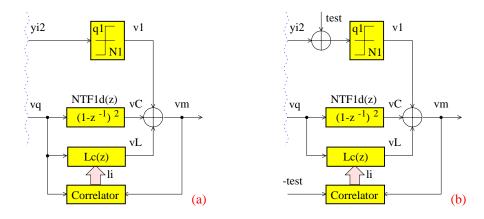

| 4.1  | Adaptive digital noise-leakage compensation (block)                  | 61 |

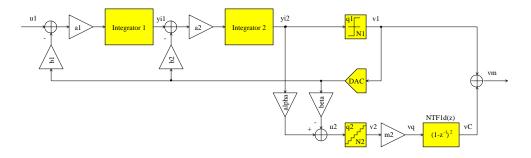

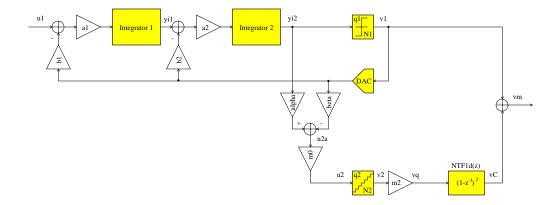

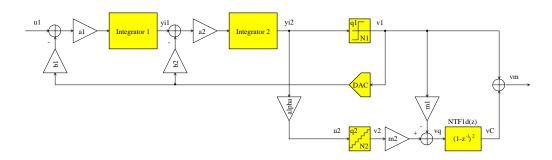

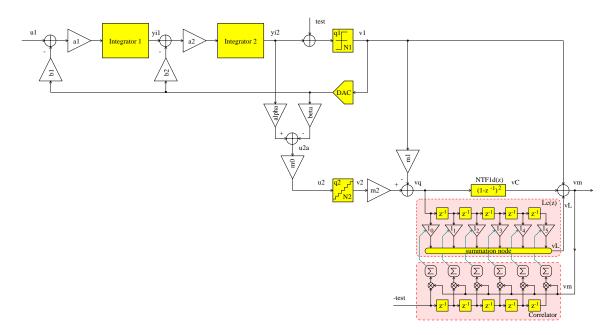

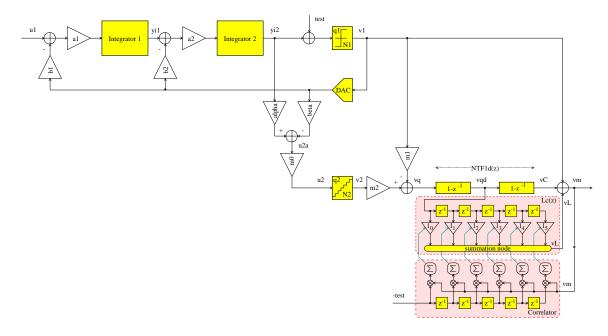

| 4.2  | Adaptive digital noise-leakage compensation (detailed)               | 65 |

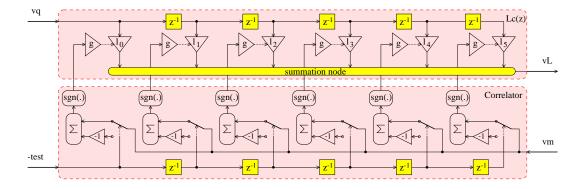

| 4.3  | Simplified hardware implementation of the correlator                 | 67 |

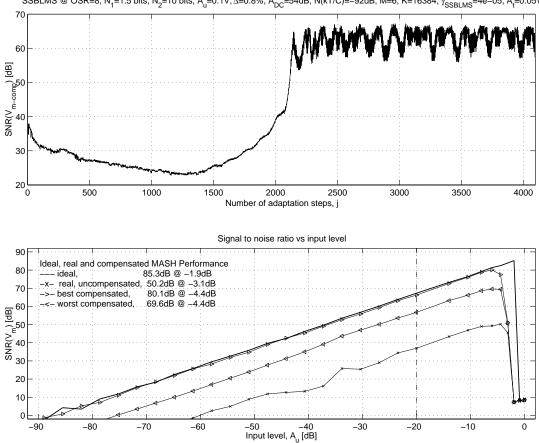

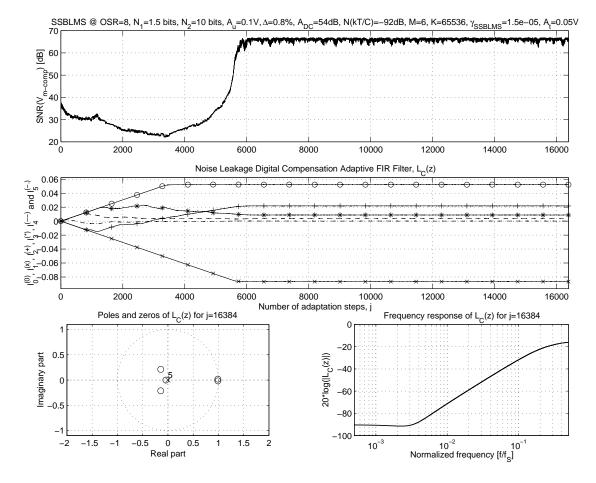

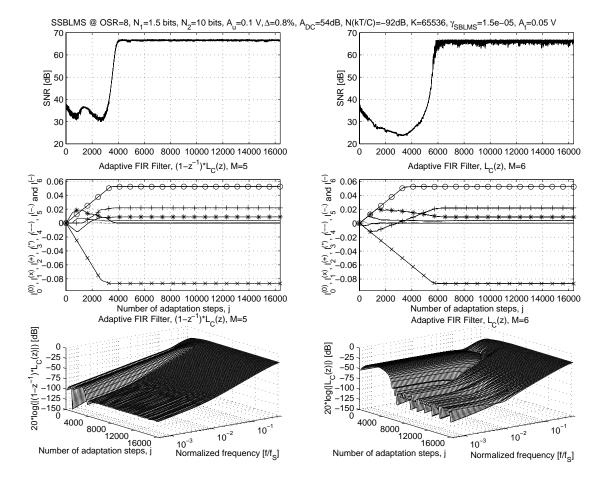

| 4.4  | Adaptive compensation process and achieved SNR (1) $\ldots$ .        | 68 |

| 4.5  | Adaptive compensation process (2)                                    | 69 |

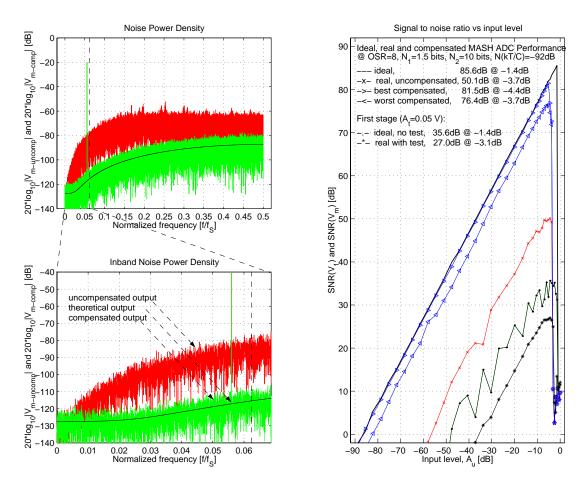

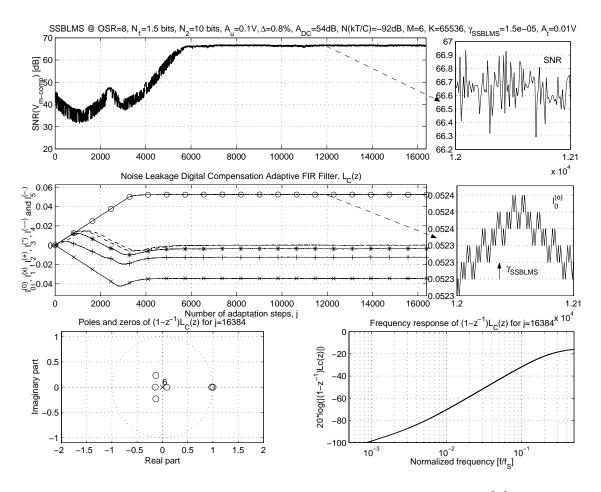

| 4.6  | Achieved SNR performance (2)                                         | 70 |

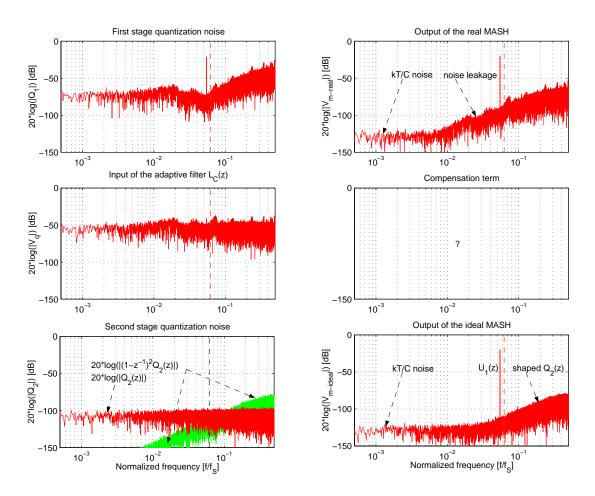

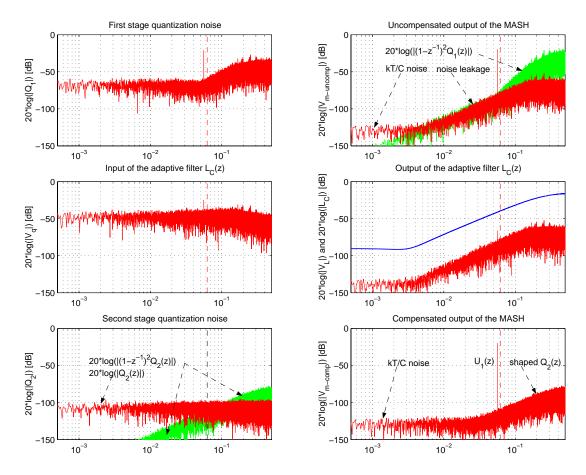

| 4.7  | Spectral analysis of some internal/external signals of the MASH .    | 71 |

| 4.8  | Improved adaptive digital noise-leakage compensation scheme          | 72 |

| 4.9  | Reducing the ripple of the adaptation noise using a differentiator . | 74 |

| 4.10 | Adaptive compensation process (3)                                    | 75 |

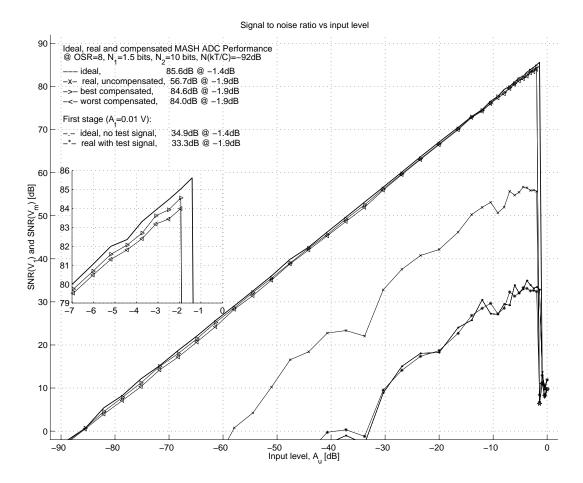

| 4.11 | Achieved SNR performance (3)                                         | 76 |

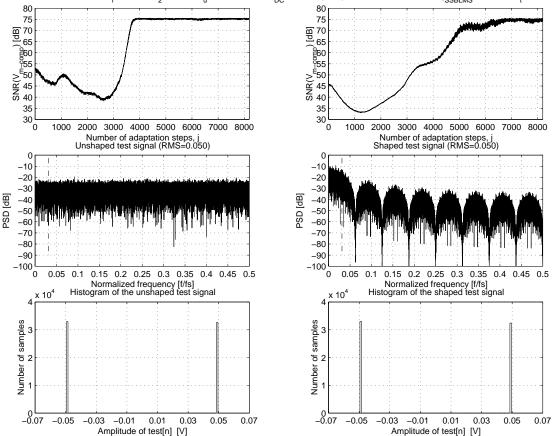

|      | Convergence using unshaped or shaped test signal                     | 78 |

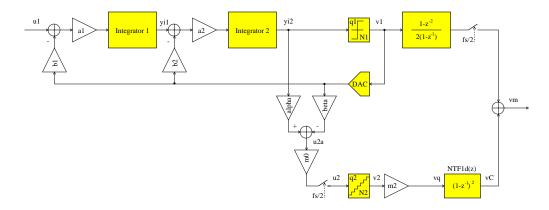

|      | High-performance 2-0 MASH ADC                                        | 79 |

| 4.14 | Simulated $SNR$ performance of the high-performance ADC $\ldots$     | 80 |

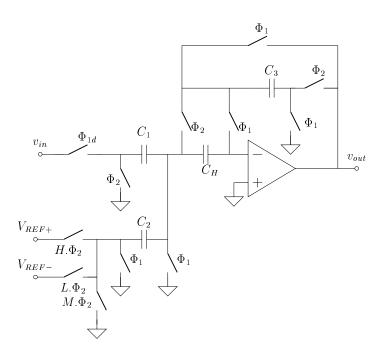

| 5.1  | First integrator from the first stage of the MASH ADC                | 82 |

| 5.2  | Second integrator from the first stage of the MASH ADC               | 83 |

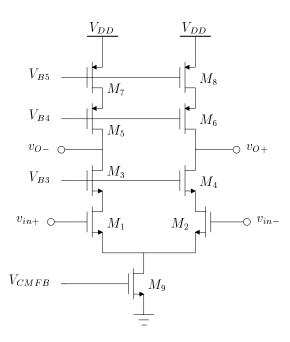

| 5.3  | Telescopic opamp schematic used in the integrators                   | 86 |

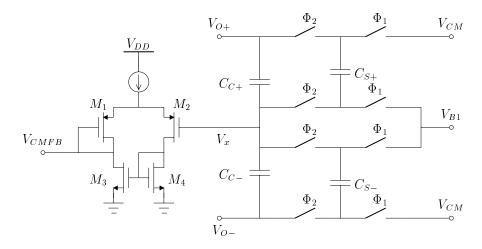

| 5.4  | Common-mode feedback circuit for the opamps                          | 87 |

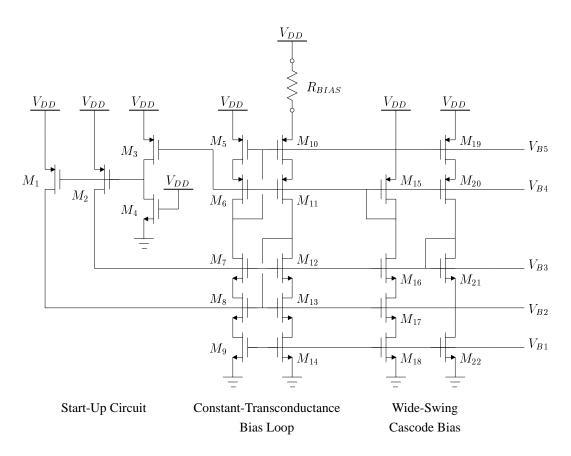

| 5.5  | Generation of the bias voltages for the opamps                       | 88 |

| 5.6  | Tri-level quantizer for the first stage of the MASH ADC              | 89 |

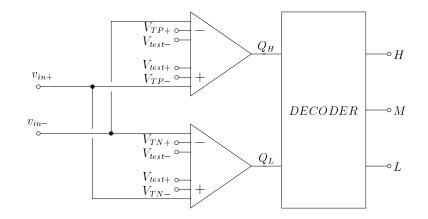

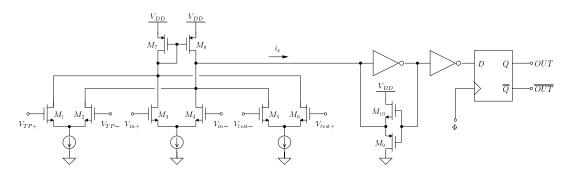

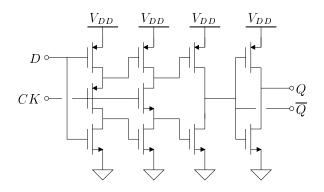

| 5.7  | Comparator used in the tri-level quantizer                           | 89 |

| 5.8  | TSPC flip-flop used in the comparator                                | 89 |

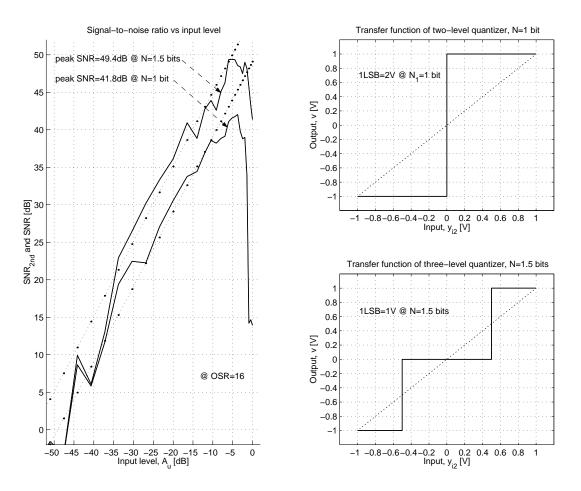

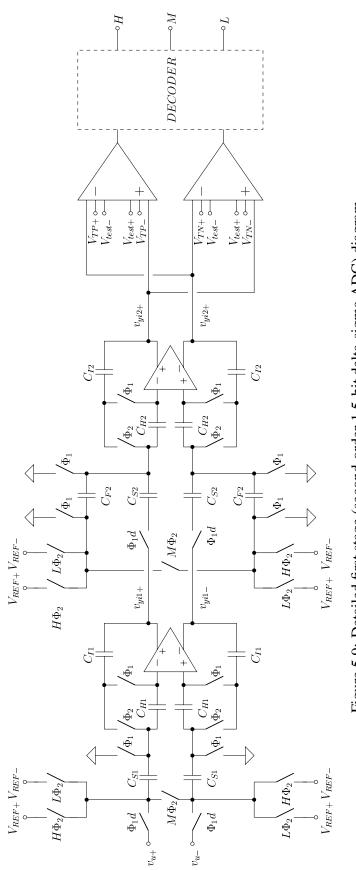

| 5.9  | Detailed SC second-order 1.5-bit delta-sigma ADC                     | 91 |

| 5.10 | Analog subtraction circuit providing the second-stage input          | 92 |

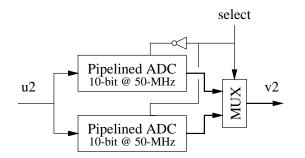

| 5.11 | Time-interleaved pipelined ADC for the second stage                  | 92 |

|      | Reduced sample-rate requirement for the second stage                 | 93 |

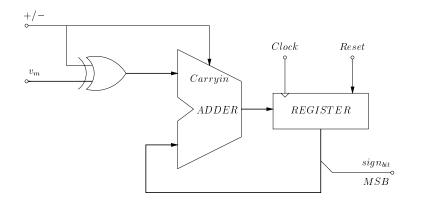

|      | Accumulator for the adaptive filter                                  | 94 |

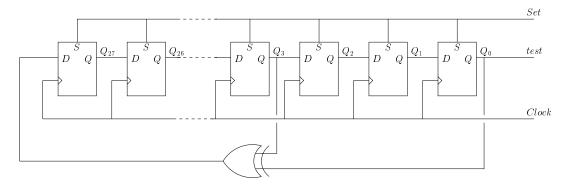

|      | 28-bit maximum-length sequence generator                             | 94 |

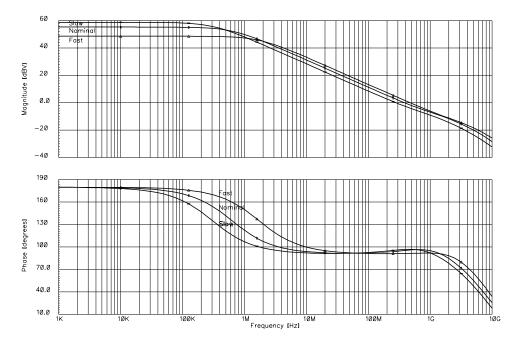

|      | Operational amplifier frequency response                             | 96 |

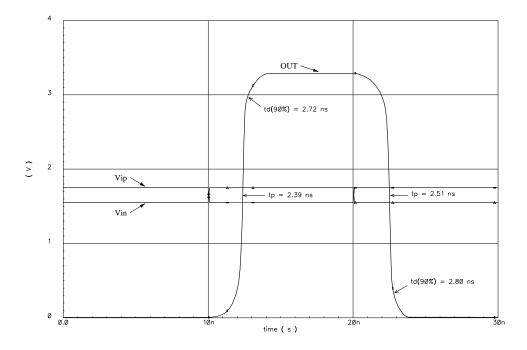

|      | Response of the comparator to a step                                 | 96 |

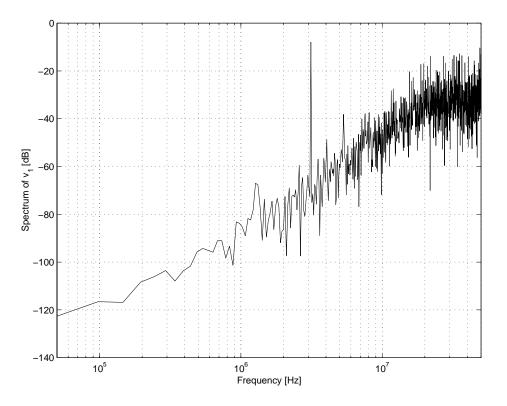

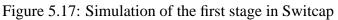

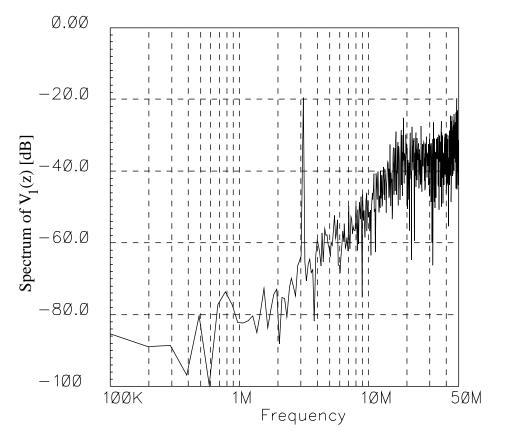

|      | Simulation of the first stage in Switcap                             | 98 |

| 5.18 | Simulation of the first stage at transistor level                    | 98 |

## **List of Tables**

| 1.1 | State-of-the-art ADCs                                                                                                      | 3   |

|-----|----------------------------------------------------------------------------------------------------------------------------|-----|

|     | Coefficients of the adaptive digital compensation filter block<br>Coefficients of the adaptive digital compensation filter |     |

| 5.2 | Parameters for the prototype chip design                                                                                   | 86  |

| 6.1 | Improvements to the previous design                                                                                        | 100 |

\_\_\_\_\_

# Chapter 1 Introduction

The title of the thesis is explained first.

This thesis presents an efficient method to design high-resolution and largebandwidth *analog-to-digital converters*. In order to achieve this goal, the popular *delta-sigma* architecture was used, which provides a high accuracy (>13 bits) even in the basic digital CMOS technology implementation, because it features lower sensitivity to the nonidealities of the analog circuitry than "classical" (Nyquistrate) converters do — a consequence of the time averaging and filtering inherent to the oversampled converter operation. Achieving high resolution and large bandwidth can be accomplished by using higher-order delta-sigma modulators. In addition, to guarantee stable operation even for a higher-order architecture for any input signal and/or initial conditions, the higher-order noise-shaping function was realized using cascaded topology. However, cascaded delta-sigma modulators are sensitive to *analog circuit imperfections*, because they rely on the perfect matching between an analog filter (affected by analog circuit imperfections) and its digital counterpart (which can be built with very high accuracy). Even small mismatch causes significant performance degradation. However, this mismatch, which has a random nature, can be estimated by an *adaptive* algorithm, and it can be corrected by a *digital compensation* adaptive filter. In this thesis it is shown that the adaptive digital compensation of analog circuit imperfections is an effective method by which the performance of a practical cascaded delta-sigma analog-to*digital converter* closely approaches its ideal value.

# 1.1 State-of-the-Art Nyquist-Rate and Delta-Sigma ADCs

Nowadays, the trend in designing analog-to-digital data converters is to obtain high-resolution and large-bandwidth quantization with low-cost fabrication process, which requires low power consumption from a low-voltage supply. For example, a sub-, or deep sub-micron  $(0.25 \dots 0.5 \ \mu m)$  standard CMOS technology with a single  $3.0 \dots 3.3$  V power supply is widely used in designing ADCs for the above mentioned reasons. However, it is a great challenge to maintain, and

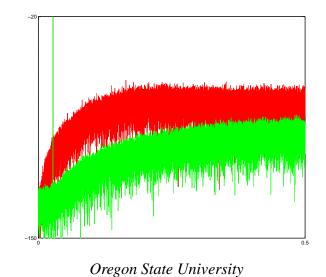

Figure 1.1: State-of-the-art ADCs (August, 1999)

even to improve, the performance level in this low-voltage environment. Due to the trade-off between resolution and signal bandwidth in (mainly) standard CMOS technology there is a large variety of ADCs available, as is illustrated by a selected sample of reported circuits in Tab. 1.1 and Fig.  $1.1^1$ .

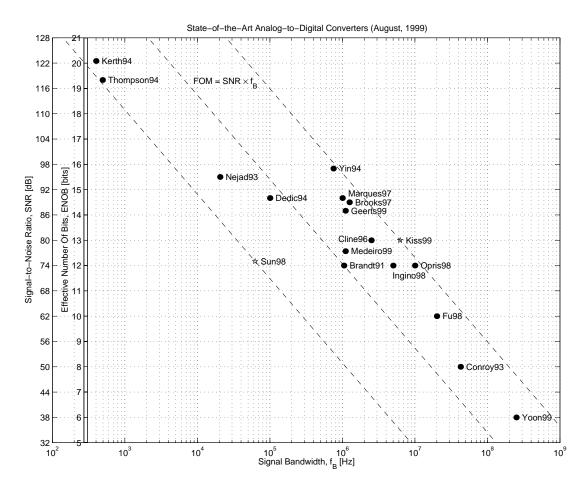

Although the power consumption and the chip area of integrated circuits are important characteristics, if these do not have values beyond reasonable limits (e.g.  $\sim$ 500 mW and  $\sim$ 50 mm<sup>2</sup>), than one can define a figure of merit *FOM* as the exclusive product of the signal-to-noise ratio *SNR* and the signal bandwidth  $f_B$  of the ADC:

$$FOM = SNR \times f_B \quad [V/V \times Hz].$$

(1.1)

Therefore, Fig. 1.2 provides a one-dimensional, so a more simple-to-read but a more subjective (given by the definition of the FOM by (1.1)) comparison between the selected ADCs.

The medium (>1-MHz) and high (>100-MHz) frequencies are populated by "classical", Nyquist-rate high-speed converters. The achievable accuracy of these converters is limited by the analog circuit imperfections as offset, gain, capacitor-ratio and apperture mismatches. To overcome these nonidealities, especially at

<sup>&</sup>lt;sup>1</sup>The definition of the effective number of bits ENOB is given by (2.14) on page 15.

| ly Power              |                   | 330  mW          | $1100 \mathrm{mW}$ | 565 mW             | 250  mW                      | 338 mW                      | 166 mW                       |                                 | 50  mW                         | $45 \mathrm{mW}$               |                              | $40\mathrm{mW}$             | 180  mW                  | V 550 mW               | 55 mW                    | 230  mW                      | 200  mW                                    | 41 mW                        |                        | $\approx 300  \mathrm{mW}$ |                        |                          |                                 |

|-----------------------|-------------------|------------------|--------------------|--------------------|------------------------------|-----------------------------|------------------------------|---------------------------------|--------------------------------|--------------------------------|------------------------------|-----------------------------|--------------------------|------------------------|--------------------------|------------------------------|--------------------------------------------|------------------------------|------------------------|----------------------------|------------------------|--------------------------|---------------------------------|

| Process / Supply      |                   |                  |                    |                    | $0.6 \ \mu m CMOS / 3 V$     | $1 \ \mu m$ CMOS / 5 V      | $1 \ \mu m CMOS / 5 V$       | $0.7~\mu \mathrm{m}$ CMOS / 5 V | $0.5 \ \mu m \ CMOS / 3.3 \ V$ | 1.2 $\mu$ m CMOS / 5 V         |                              | $3 \ \mu m CMOS / \pm 5 V$  | $2 \mu m CMOS / \pm 5 V$ | $2 \ \mu m CMOS / 5 V$ | $1.2 \ \mu m CMOS / 5 V$ | $2 \ \mu m BiCMOS / \pm 2 V$ | $0.6 \mu\mathrm{m}\mathrm{CMOS}$ / 5a-3d V | $0.7 \ \mu m CMOS / \pm 2 V$ | $1 \ \mu m CMOS / 5 V$ | $0.5 \ \mu m$ CMOS / 3.3 V | $1 \ \mu m$ CMOS / 5 V | $1.2 \ \mu m CMOS / 5 V$ | $0.25 \ \mu m \ CMOS / 3.3 \ V$ |

| Architecture          | Nyquist-Rate ADCs | flash            | parallel pipelined | parallel pipelined | digital-calibrated pipelined | analog-calibrated pipelined | digital-calibrated pipelined | Delta-Sigma ADCs                | 4th-order, 1b $\Delta\Sigma$   | 5th-order, 1.5b $\Delta\Sigma$ | 2nd-order, 4b $\Delta\Sigma$ | 2-2-2 MASH, 1.5-1.5-1.5b ΔΣ | 2-1-1 MASH, 1-1-1b ΔΣ    | 2-0 MASH, 5-12b ΔΣ     | 2-1-1 MASH, 1-1-3b ΔΣ    | 2-1-1 MASH, 1-1-1b ΔΣ        | 2-1-1 MASH, 1-1-1b ΔΣ                      | 2-1 MASH, 1-3b ΔΣ            | 2-0 MASH, 1-12b ∆∑     | 2-0 MASH, 1.5-10b ∆∑       |                        |                          |                                 |

| $f_S / OSR$           | Nyqu              | 500 MS/s / 1     | 85 MS/s / 1        | 40 MS/s / 1        | 20 MS/s / 1                  | 10 MS/s / 1                 | 5 MS/s / 1                   | Delta                           | 256 kHz / 256                  | 126 kHz / 128                  | 5.25 MHz / 128               | 3.25 MHz / 16               | 48 MHz / 32              | 20 MHz / 8             | 35.2 MHz / 16            | 48 MHz / 24                  | 52.8 MHz / 24                              | 50 MHz / 24                  | 1 MHz / 8              | 100 MHz / 8                |                        |                          |                                 |

| ${ m SNR} @ { m f_B}$ |                   | 6 bits @ 250 MHz | 8 bits @ 42.5 MHz  | 10 bits @ 20 MHz   | 12 bits @ 10 MHz             | 12 bits @ 5 MHz             | 13 bits @ 2.5 MHz            |                                 | 122.5 dB @ 400 Hz              | 118 dB @ 492 Hz                | 95 dB @ 20.5 kHz             | 90 dB @ 100 kHz             | 97 dB @ 750 kHz          | 89 dB @ 1.25 MHz       | 77.4 dB @ 1.1 MHz        | 90 dB @ 1 MHz                | 87 dB @ 1.1 MHz                            | 74 dB @ 1.05 MHz             | 75 dB @ 62.5 kHz       | $\approx$ 80 dB @ 6.25 MHz |                        |                          |                                 |

| Author                |                   | Yoon99, [1]      | Conroy93, [2]      | Fu98, [3]          | Opris98, [4]                 | Ingino98, [5]               | Cline96, [6]                 |                                 | Kerth94, [7]                   | Thompson94, [8]                | Nejad93, [9]                 | Dedic94, [10]               | Yin94, [11]              | Brooks97, [12]         | Medeiro99, [13]          | Marques97, [14]              | Geerts99, [15]                             | Brandt91, [16]               | Sun98, [17]            | Kiss99, [18]               |                        |                          |                                 |

Table 1.1: State-of-the-Art ADCs (August, 1999)

Figure 1.2: Figure of merit for state-of-the-art ADCs

higher resolution than 10 bits, calibrating circuits are often used. Recently, a 6-bit 500-MSamples/s full-flash ADC was reported, which was implemented in 0.4- $\mu$ m CMOS technology and dissipated 400-mW from a 3.3-V supply [1]. For better resolution but less bandwidth (8-b @ 85-MS/s), a time-interleaved (or parallel) pipelined ADC was built [2]. A digital background calibration was used in another time-interleaved pipelined ADC to trade higher resolution for lower bandwidth (10-b @ 40-MS/s) [3]. Also, a 5-V, 12-b @ 20-MS/s, digital background calibrated [4], and a 3-V, 12-b @ 10-MS/s, analog continuously calibrated [5] pipelined ADCs were reported.

The 12-bit resolution seems to be the upper limit for Nyquist-rate converters implemented in low-cost process even if analog or digital correction circuitry is used. However, a number of high-speed pipelined converter implementations have been reported with resolutions in excess of 12 bits, e.g. [6], [19], [20]. A low-power digital-calibrated pipelined ADC with 13-bits @ 2.5-MHz performance is presented in [6]. In order to achieve a resolution of 16 bits at 500-kHz signal bandwidth a 32-bits on-chip microcontroller was used for self calibrating a pipelined ADC [19]. Laser-trimming techniques can also adjust the accuracy of the pipelined ADCs, e.g. for a 13-bit @ 1.25-MHz performance [20].

Unfortunately, on-chip calibration tends to significantly increase the complexity of pipelined converters. Moreover, one-time calibration schemes (usually at power-up) cannot compensate for the effects of supply and temperature variations. Especially the last two cited circuits [19], [20] require large chip area (e.g.  $150 \times 240 \text{ mm}^2$  in [19]) and expensive fabrication costs, so they could not be included into the list of selected ADC samples from Tab. 1.1 and Fig. 1.1.

Above 13-bit linearity essentially different converters, the so-called delta-sigma data converters can satisfy the high-accuracy and low-cost need in many applications, by using oversampling and noise-shaping techniques to suppress the out-of-band quantization noise. The first and most obvious applications of delta-sigma converters are in instrumentation, e.g. 122.5 dB @ 400 Hz [7] and 118 dB @ 492 Hz [8], and in digital audio, e.g. 96 dB @ 20.5 kHz [9]. In the last few years, successful attempts have been made to use the delta-sigma architecture for medium frequencies (>1-MHz) as well, and recently published papers (Tab.1.1 and Fig. 1.1) sustain the trend of extending the signal bandwidth while preserving the high accuracy (>13 bits).

For such a large signal bandwidth it seems that the cascaded delta-sigma (MASH<sup>2</sup>) topology is suitable, and, therefore is preferred by the researchers. However, it is well-known that this architecture, as in general every cancellationbased architecture, is sensitive to analog circuit imperfections, because they rely on the perfect matching of the transfer functions of the two internal signal paths, one predominantly analog, and the other predominantly digital. This causes quantization noise leakage, and in turn performance degradation. To prevent this, in [12] a multibit (5-bit) quantizer was used in the first stage, which reduces the power of the noise leakage, but which needs a mismatch-shaping digital-toanalog converter in the feedback path. In addition, the second stage was built from a multibit (12-bit) pipelined ADC. Therefore, this high-performance converter (89 dB @ 1.25 MHz !) ended up with a relatively high power consumption (550 mW). Another approach was analyzed and implemented, but which did not necessitate digital correction by using (claimed) optimized architecture and coefficients for a fourth-order cascaded (2-1-1 topology) modulator instead [13]. Therefore, very low power consumption (55-mW) was achieved. Two similar 2-1-1 cascaded but single-bit topologies with (claimed) optimized coefficients were successfully implemented with 5-V [14] and 3-V [15] power supplies. A remarkable design and implementation of 2-1 cascaded delta-sigma ADC was published in 1991 [16] which achieved an impressive (considering the year of publication also) 74-dB @ 10.5-MHz performance.

In the previous cascaded delta-sigma ADC designs [10], [11], [12], [13], [14], [15], [16], the quantization noise leakage was considered as an intrinsic drawback of the topology. Indeed, the noise leakage can be reduced in the analog domain by careful analog circuit design [13], [14], [15], [16] or by the use of multibit

<sup>&</sup>lt;sup>2</sup>The notation  $n_1$ - $n_2$ - $n_3$ -... used in Tab. 1.1 indicates the number of cascaded stages,  $n_i$  is the order of the *i*th delta-sigma loop, and  $n_1 + n_2 + n_3$  is the effective order of the MASH. For example, 2-1-1 [14] was built from 3 stages, a second-order modulator is followed by 2 first-order loops, so the effective order of the MASH ADC is 4.

first stage [12], but only to a limited degree, especially if low-cost fabrication must be used. However, if the noise leakage was handled somehow, the performance would be further increased. On the other hand, several digital domain solutions have been developed including off-line calibration [21] and on-line correction [22], [23], [24], [25].

A robust cascaded delta-sigma structure to analog circuit imperfections was proposed in [26]. The so-called indirectly residue-compensated delta-sigma quantizers estimate differently the quantization error of the first stage, which is quantized by a multibit second stage. If the residue quantizer (second stage) has 10-bit resolution and linearity, and the first stage has also a 5-bit quantizer, than an oversampling ratio of OSR = 10 provides an SNR performance of 105 dB. However, this modulator also requires mismatch-shaping digital-to-analog converter in the first stage, which means larger chip-area and bigger power consumption.

#### **1.2 The Proposed ADC**

An on-line digital-correction method is presented in this thesis. Based on the present work, one can use simple structure and avoid mismatch-shaping digital-to-analog converter in the first stage, and one can allow noise leakage in the output using more relaxed requirements for the integrators, because a simple and effective method can digitally compensate for the analog circuit imperfections in cascaded delta-sigma ADCs.

In this thesis a cascaded 2-0 delta-sigma ADC architecture with 1–1.5-bit first stage and 10–12-bit second stage was investigated, which uses an adaptive digital FIR filter to reduce the noise leakage due to the imperfect error cancellation. For adaptation, a pseudo-random test signal was injected into the first stage and a simplified block-LMS algorithm, the sign-sign-BLMS, was used to update the coefficients of the adaptation filter. The basic theory and some design considerations were developed under a previous work [27], [28], [29], [30]; also, a working prototype of the integrated ADC was successfully fabricated and tested [17], [31]. However, the reported effective results (signal-to-noise+distortion ratio SNDR=75 dB @  $f_B=62.5$ -kHz signal bandwidth [17]) validated only the principle of adaptive noise-leakage compensation, leaving a considerably large room to improve this initial performance.

The current thesis deals with the optimization to this technique, and its application in a very fast (sampling frequency  $f_S=100$  MHz, oversampling ratio OSR=8-16, signal bandwidth  $f_B=3-6$  MHz) and high-accuracy (signal-to-noise ratio SNR=13-15-bit) implementation [18], [32], [33], [34]. Such converters may have wide applications in high-speed instrumentation, high-definition video, imaging, radar and digital communications. Available behavioral and circuit-level simulation results has confirmed an achievable 13-bit @ 6-MHz ADC, which is a useful performance for a state-of-the-art data converter (Tab. 1.1 and Fig. 1.1). Moreover, Fig. 1.2 shows that the proposed ADC has the highest figure of merit FOM, (1.1), among these high-performance data converters.

#### **1.3 Thesis Structure**

This thesis tries to guide the reader gradually through the main issues of the adaptive cascaded delta-sigma modulators. Many figures and selected simulation results show, explain and illustrate the presented topic.

Following this Introduction, Chapter 2 begins by presenting the basics of quantization, and two key features of delta-sigma modulators: oversampling and quantization noise shaping. To keep a logical and progressive order, the first-order delta-sigma ADCs are briefly described next. Because the first stage of our cascaded delta-sigma ADC was chosen to be a second-order delta-sigma modulator, this subject is detailed in the next section. The possibility of using a tri-level quantizer is also investigated, which is a key element in optimizing the cascaded delta-sigma ADC, supported by simulation results, which are only briefly marked in the available bibliography (e.g. coefficient calculus, internal voltage swing, the gain of a single-bit/multibit quantizer). Higher-order delta-sigma modulators are briefly described next. A short selection guide of single-loop delta-sigma modulators concludes this chapter.

Chapter 3 first presents a comparative analysis between cascaded 2-0 deltasigma ADC structures. In order to achieve maximum peak-SNR performance, the use of bi-level and tri-level first-stage quantizer, and different interstage coefficients are investigated. The high sensitivity of the cascaded structure to analog circuit imperfections is studied next. Simulation results are coherent with the theoretical assumptions about the quantization noise leakage.

Chapter 4 deals with the adaptive digital correction of the noise leakage. The possibility of using a test signal for on-line compensation is investigated first. The hardware complexity of the adaptive digital compensation filter is studied in order to being reduced. Next, the optimization of the adaptation process is presented. In order to improve the performance of the adaptive MASH, the parameters of the adaptive compensation process, and the properties of the test signal are analyzed.

Chapter 5 presents a high-frequency (sampling frequency  $f_S = 100$  -MHz) switched-capacitor implementation<sup>3</sup> of the cascaded 2-0 delta-sigma modulator designed at system level in the previous chapters.

Finally, Chapter 6 summarizes the original achievements and conclusions, and gives a few suggestion for future work.

<sup>&</sup>lt;sup>3</sup>The prototype chip design, as well Chapter 5, were contributed by my colleague at Oregon State University, José Silva (silva@ece.orst.edu).

# Chapter 2 Single-Loop Delta-Sigma ADCs

Delta-sigma data converters have been known for nearly fifty years, since 1954 [35, Introduction], but only in the last two decades has the technology, namely the high-density digital VLSI, matured sufficiently to manufacture them as inexpensive monolithic integrated circuits. They are now used in many applications where a low-cost, low to medium signal bandwidth, low-power and high-resolution data converters are required.

The heart of any analog-to-digital converter (ADC) is a quantizer. Therefore, we begin our discussion by describing some basic principles of the quantization. Next, two key features of delta-sigma data modulators: oversampling and noise shaping are presented, which are followed by a detailed system-level analysis of first-order and second-order delta-sigma analog-to-digital converters. Also, some properties of higher-order modulators are presented in the end of this chapter.

#### 2.1 Quantization

Analog-to-digital conversion of a signal is traditionally described in terms of two separate operations: uniform sampling (or quantization, discretization) in time, and quantization (or discretization) in amplitude [36, Section 3.0], [37].

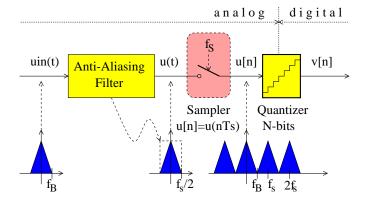

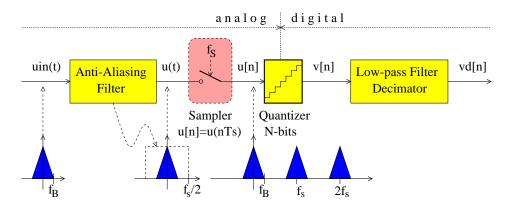

Ideal periodic sampling of a continuous-time signal u(t) at rates  $f_S$  more than twice the signal bandwidth  $f_B$  need not introduce distortion. In other words, the discretization or quantization in time, as a result of sampling, is completely invertible operation, because according to the Nyquist sampling theorem for  $f_S \ge 2 f_B$ , the original continuous-time signal u(t) can be perfectly reconstructed from its discrete-time samples  $u[n] = u(nT_S)$ , without any loss of signal information. In practice, to assure that the Nyquist sampling theorem is indeed satisfied, and to avoid aliasing, the continuous-time input signal  $u_{in}(t)$  is filtered by an antialiasing filter before sampling, and, therefore, its bandwidth  $f_B$  is surely limited to  $\frac{f_S}{2}$  (Fig. 2.1). If  $f_S \ge 2 f_B$ , than the spectrum U(f) of the sampled discrete-time sequence u[n] is a periodic replica of the initial, continuous-time input signal's  $u_{in}(t)$  spectrum  $U_{in}(f)$  with a period of  $T_S = \frac{1}{f_S}$  (Fig. 2.1).

On the other hand, quantization is non-invertible process, since an infinite number of input amplitude values of the discrete-time analog signal u[n] are

mapped into a finite number of output amplitude values of the (discrete-time) digital signal v[n] (Fig. 2.1) [36, Section 3.2.0], [37]. In other words, even an ideal quantization process inherently introduces distortion, and our primary objective in designing analog-to-digital converters is to limit this distortion [38, Section 1.2.1].

Figure 2.1: General analog-to-digital converter

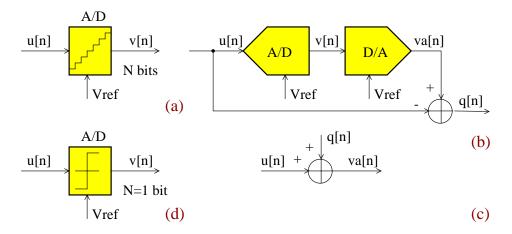

A *N*-bit ideal quantizer is presented in Fig. 2.2.a, where v[n] is the digital output word stream while u[n] and  $V_{ref}$  are the sampled analog input signal and the reference voltage, respectively. If the digital output v[n] is converted back into an analog discrete-time signal  $v_a[n]$  from which the sampled analog input signal u[n] is subtracted, the result will be the quantization error sequence q[n] (Fig. 2.2.b):

$$q[n] = v_a[n] - u[n].$$

(2.1)

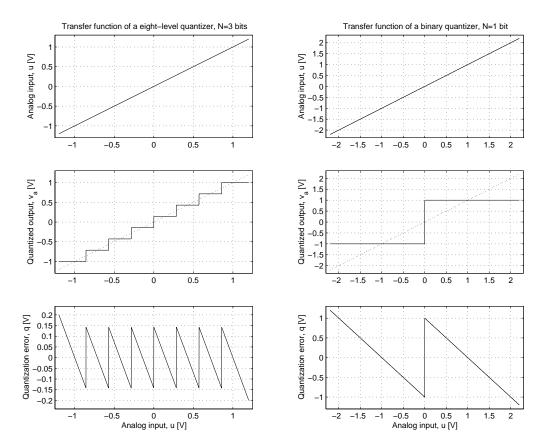

In addition, if the sampled analog input u[n] is a ramp signal, than the quantized output  $v_a[n]$  appears as a staircase, and the quantization error sequence q[n] has a sawtooth form (Fig. 2.3.a). In Fig. 2.3.a the resolution of the quantizer is N =3 bits, the full-scale range of the input is  $FSR = 2A_{max}$ , and, therefore, its step size  $\Delta$ , or its 1 *LSB* (least significant bit), is given by

$$\Delta = 1LSB = \frac{2A_{max}}{2^N - 1} = \frac{2}{7} = 0.28 \text{ V}.$$

(2.2)

Note that the amplitude of the quantization error q[n] is limited to  $\pm \frac{\Delta}{2}$  as far as the analog input signal satisfies the condition:

$$|u[n]| \le A_{max} + \frac{\Delta}{2} \implies |q[n]| \le \frac{\Delta}{2}$$

(2.3)

Under these circumstances the quantizer is said to be not overloaded or saturated. On the other hand, for  $|u[n_0]| > A_{max} + \frac{\Delta}{2}$ , and hence  $|q[n_0]| > \frac{\Delta}{2}$ , the quantizer is said to be overloaded [37]. Note that this statement is true for all input signals, not just for ramps.

Figure 2.2: (a) Ideal *N*-bit quantizer; (b) quantization error generation:  $q[n] = v_a[n] - u[n]$ ; (c) discrete-time domain modeling of the quantization process:  $v_a[n] = u[n] + q[n]$ ; (d) ideal single-bit quantizer

Figure 2.3: Transfer function of an ideal N-bit quantizer for (a) N = 3 bits and (b) N = 1 bit

#### 2.1.1 Quantization Error

According to (2.1), the quantization error q[n] is completely defined by the input signal u[n]. However, if the input signal u[n] changes rapidly from sample to

sample by amounts comparable with or greater than  $\Delta$  without causing saturation, then the quantization error q[n] is largely uncorrelated from sample to sample and has equal probability of lying anywhere in the range  $\left[-\frac{\Delta}{2};+\frac{\Delta}{2}\right]$ . Therefore, it seems to be plausible to assume that the quantization error q[n] has statistical properties that are independent of the input signal u[n], so it can be represented by a random variable, which behaves as a noise, namely, as a "quantization noise"<sup>1</sup> [38, Section 1.2.1].

The equation (2.1) can be rearranged [39] as

$$v_a[n] = u[n] + q[n].$$

(2.4)

Although the equation (2.4) is exact for every time instance, it can express also an intuitive link between the statistical properties of the sampled analog input u[n], the quantized output  $v_a[n]$  and the quantization error q[n].

A rigorous analysis of a nonlinear system, such a quantizer, is a difficult and complicated task. To further simplify the analysis of the quantization noise, the following assumptions about the noise process and its statistics are traditionally made, which are called the "input-independent additive white-noise approximation" (weak version) [38, Section 2.3], [37]:

- **Property 1.** The quantization error sequence q[n] is a sample sequence of a stationary random process.

- **Property 2.** The quantization error sequence q[n] is uncorrelated with the input sequence u[n].

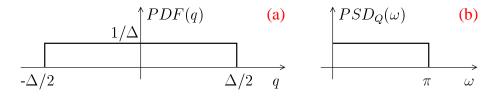

- **Property 3.** The probability density function of the quantization error process PDF(q[n]) is uniform over the range  $\left[-\frac{\Delta}{2}; +\frac{\Delta}{2}\right]$  (Fig. 2.4.a).

- **Property 4.** The power spectral density of the quantization error process  $PSD_Q(\omega)$  is flat (Fig. 2.4.b). (The quantization error is a white noise process.)

These approximations simplify the system analysis because they replace a deterministic nonlinearity by a stochastic linear system, thereby permitting the use of linear system methods to analyze a nonlinear system containing a quantizer [38, Section 2.3]. Also, under certain conditions, namely the Bennett's conditions:

**Condition 1.** The input signal u[n] is not in the overloaded region.

**Condition 2.** The resolution N of the quantizer is asymptotically large.

- **Condition 3.** The step size  $\Delta$  of the quantizer is asymptotically small.

- **Condition 4.** The joint probability density function of the input signal u[n] at different sample times is smooth.

<sup>&</sup>lt;sup>1</sup>In this thesis the concepts of "quantization error" and "quantization noise" will be used interchangeably. However, "quantization error" is a more descriptive and precise term, and it specifically refers to the time-domain signal  $q[n] = v_a[n] - u[n]$ , and "quantization noise" will emphasize its assumed white noise properties — detailed later in this section [38, Section 3.1.0].

these assumptions (Properties 1–4) are reasonable [38, Section 2.3], [37].

In conclusion, under these certain conditions (Conditions 1–4) the quantizer can be modeled as an input-independent additive white-noise source, so the equation (2.4) is valid in the frequency domain also, that is, the digital output V(z) (or the quantized output  $V_a(z)$  — if the gain of the DAC is assumed to be equal to unity) can be calculated as the sum of the analog input U(z) and the quantization noise Q(z):

$$V(z) = V_a(z) = U(z) + Q(z).$$

(2.5)

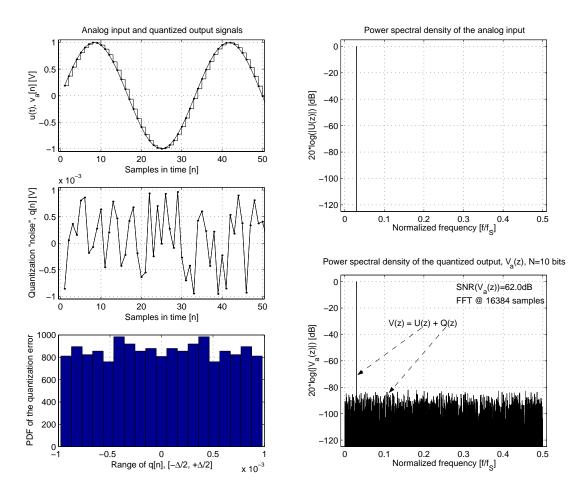

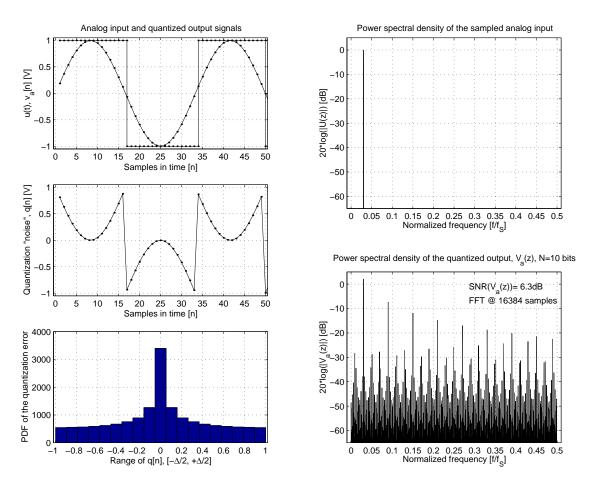

The relation (2.5) can be intuitively verified on Fig. 2.5, where the spectrum of the quantization error seems to be flat (white noise) and completely uncorrelated with the input signal. In this example a full-scale analog input sinewave  $A_u = A_{max}$  with a frequency of  $f = 0.03 f_S$  was applied to a N = 10-bit quantizer, so the Bennett's conditions were satisfied with a good approximation. Note, however, that the probability density function of the quantization error is not quite uniformly distributed over the range  $\left[-\frac{\Delta}{2}; +\frac{\Delta}{2}\right]$ . If the input was a more "busy" signal, for example a sum of sinewaves, than PDF(q) would be more uniform.

A mathematical analysis of the quantization process is given in [36, Section 3.2]. It has been demonstrated that as the step size  $\Delta$  of the quantizer decreases, the quantization error sequence q[n] can be considered less correlated (the autocorrelation of q[n] is low) even if the input sequence u[n] is highly correlated (the autocorrelation of u[n] is high) [36, Section 3.2.3]. In addition, it was shown that for small values of the step size  $\Delta$ , the quantization error sequence q[n] is in fact uncorrelated with the input sequence u[n], although the quantization error q[n] is completely determined by the input sequence u[n], shown by (2.1) [36, Section 3.2.4].

Figure 2.4: Statistical properties of the quantization error as input-independent additive white noise: (a) probability density function PDF(q) and (b) power spectral density  $PSD_Q(\omega)$

#### 2.1.2 Performance Modeling

Next, based on the input-independent additive white-noise approximation for the quantization error, one can derive the signal-to-noise ratio SNR performance of a N-bit ideal analog-to-digital converter or quantizer. According to this approximation (Properties 1 and 3), the quantization error q[n] is a uniformly distributed random variable (PDF(q[n]) = constant) over the range  $\left[-\frac{\Delta}{2}; +\frac{\Delta}{2}\right]$  (Fig. 2.4.a).

Figure 2.5: The spectrum of a quantized sinewave for N=10 bits

Therefore,

$$\int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} PDF(q[n]) \,\mathrm{d}q = 1 \Longrightarrow PDF(q[n]) = \frac{1}{\Delta}, \forall q[n] \in \left[-\frac{\Delta}{2}; +\frac{\Delta}{2}\right]$$

(2.6)

For a zero mean q[n]

$$\bar{q} = \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} PDF(q[n]) \, q \, \mathrm{d}q = \frac{1}{\Delta} \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} \, q \, \mathrm{d}q = 0, \tag{2.7}$$

its variance or power is [40, Section 4.4]

$$\sigma_q^2 = P_q = \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} PDF(q[n]) q^2 \, \mathrm{d}q = \frac{1}{\Delta} \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} q^2 \, \mathrm{d}q = \frac{\Delta^2}{12}.$$

(2.8)

According to Property 4, the spectrum of the quantization error is uniformly distributed ( $PSD_Q(\omega) = \text{constant}$ ) over the digital frequency domain  $[0; \pi]$  (Fig. 2.4.b), so its power spectral density can be calculated by

$$P_q = \int_0^{\pi} PSD_Q(\omega) \,\mathrm{d}\omega = \sigma_q^2 \quad \Longrightarrow \quad PSD_Q(\omega) = \frac{\sigma_q^2}{\pi}.$$

(2.9)

In conclusion, the signal-to-noise ratio  $SNR_{Nyquist}$  of a Nyquist-rate converter for a sinewave input with amplitude  $A_u$  is given by

$$SNR_{Nyquist} = 10 \log_{10} \frac{P_u}{P_q} = 10 \log_{10} \left( \frac{A_u^2}{2} \frac{12}{\Delta^2} \right)$$

(2.10)

$$= 10 \log_{10} \left( 6 A_u^2 \left( \frac{2^N - 1}{2 A_{max}} \right)^2 \right)$$

(2.11)

$$= 20 \log_{10} \frac{A_u}{A_{max}} + 6.02 N + 1.76 \quad [dB], \qquad (2.12)$$

and for a full-scale sinewave input

$$SNR_{Nyquist_{max}} = 6.02 N + 1.76 [dB].$$

(2.13)

Note that for each extra bit of resolution in the ADC, i.e. for every increment in N, there is about a 6 dB improvement in the SNR. Thus, there is a direct relationship between the resolution of an ADC in bits and its SNR performance in dB-s, and it is common to equate differences in SNR in dB to bits, by dividing the dB value by 6 [37]. More precisely, one can define the effective number of bits ENOB of a converter from its SNR performance by [41, Section 6.2], [42]:

$$ENOB = \frac{SNR \,[dB] - 1.76 \,dB}{6.02 \,dB} \,[bits].$$

(2.14)

For example, a N = 10-bit converter has an SNR = 61.86 dB based on (2.13). This theoretical value matches well with the SNR = 62.0 dB obtained by simulations (Fig. 2.5).

#### 2.2 Oversampling Converters

Consider first a band-limited signal with a spectrum which lies in the frequencyband  $[0; f_B]$ , or equivalently in  $[0; \omega_B]$ . Oversampling is a technique that improves the resolution obtained from a conventional Nyquist-rate converter by sampling the signal at a rate considerably faster ( $f_{S_{OS}} = 2OSR f_B$ ,  $OSR \gg 1$ ) than the required Nyquist rate ( $f_{S_{Nyquist}} = 2 f_B$ ) (Fig. 2.6). Typical values for the oversampling ratio (for normalized sampling frequency  $f_S = \frac{\omega_S}{2\pi} = 1$ )

$$OSR = \frac{f_S}{2 f_B} \Big|_{f_S = 1} = \frac{\pi}{\omega_B}$$

(2.15)

are between 8 and 512, and usually it can be represented as a power of 2, i.e.  $OSR = 2^r$ , to facilitate the digital decimating filter.

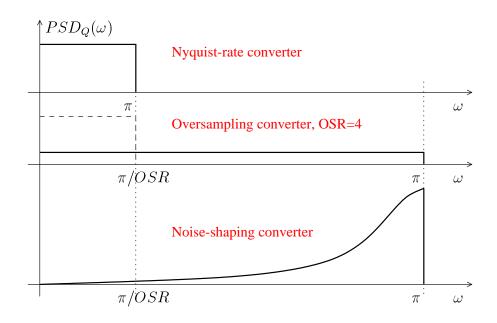

Because the maximum available sampling frequency is limited by the stateof-the art VLSI technology (e.g. for CMOS switched-capacitor circuits is around  $f_S = 100$  MHz), the oversampling technique reduces the available signal bandwidth  $f_B$ . In other words, oversampling converters trade signal bandwidth for higher resolution. By using oversampling, the power spectral density of the quantization error is stretched over the whole band  $[0; \pi]$ , so its power in the signal band of interest  $[0; \omega_B]$  will be reduced proportionally with OSR (Fig. 2.7) [36, Section 3.2.7], [39, Section 14.1]. Therefore, the so-called in-band quantization noise power  $P_0$ is given by:

$$P_{0_{OS}} = \int_0^{\omega_B} PSD_Q(\omega) \,\mathrm{d}\omega = \frac{\sigma_q^2}{\pi} \int_0^{\frac{\pi}{OSR}} \mathrm{d}\omega = \frac{\sigma_q^2}{OSR} \tag{2.16}$$

The power of the out-of-band ( $\omega > \omega_B$ ) quantization noise will be reduced significantly, in ideal case: it will be eliminated, by a digital low-pass filter, and the oversampled digital sequence will be processed by a decimator, which downsamples it to the Nyquist rate  $\omega_B$  (Fig. 2.6). It turns out that the signal-to-noise ratio  $SNR_{OS}$  for an oversampling converter is given by

$$SNR_{OS} = 10 \log_{10} \frac{P_u}{P_{0_{OS}}}$$

$$= 20 \log_{10} \frac{A_u}{A_{max}} + 6.02 N + 10 \log_{10} OSR + 1.76 \quad [dB].$$

(2.17)

If we consider the oversampling ratio being  $OSR = 2^r$ , than  $10 \log_{10} OSR = 3.01 r$  [dB], so every doubling of the oversampling ratio, i.e. for every increment in r, the  $SNR_{OS}$  improves by about 3 dB, or the resolution improves by  $\frac{1}{2}$  bit. In other words, the oversampling converter has a 3-dB/octave or 0.5-bit/octave SNR improvement [39, Section 14.1], [37].

Figure 2.6: General oversampling analog-to-digital converter (OSR = 2)

#### 2.3 Noise-Shaping Converters

The in-band quantization noise power can be further suppressed by using quantization noise shaping in addition to oversampling. Nowadays, the most popular noise-shaping converters are the so-called delta-sigma converters or delta-sigma modulators. The general block-structure of a delta-sigma ADC is presented in

Figure 2.7: The power spectral density of the quantization noise  $PSD_Q(\omega)$  for different converters

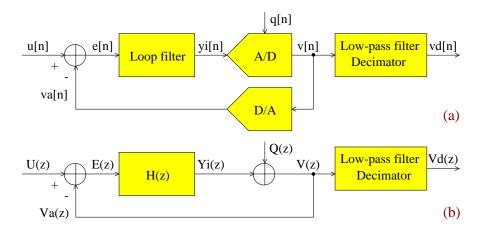

Fig. 2.8.a, which consists of an analog loop filter H(z) and a coarse N-bit quantizer enclosed in a feedback loop.

Since this system usually contains one integrator or cascade of integrators as the analog loop filter, its name is "delta-sigma" modulator, where the "delta" ( $\Delta$ ) denotes the difference operation ( $e[n] = u[n] - v_a[n]$ ) made in the input node, and where the "sigma" ( $\Sigma$ ) denotes the summation (accumulation) performed by the integrators [38, Introduction].

Figure 2.8: (a) General structure of a noise-shaping ADC and (b) its linearized model (for the DAC a unity gain was assumed)

#### **2.3.1 Basic Operation**

To rigorously analyze this delta-sigma converter in the frequency domain is a difficult task due to the presence of the nonlinear quantizer. To simplify this analysis, under certain conditions (Conditions 1–4, Section 2.1.1) one can use the input-independent additive white-noise approximation for the quantization error and analyze the delta-sigma modulator as a linear system. The linearized model is presented in Fig. 2.8.b. Therefore, the calculations became trivial:

$$V(z) = (U(z) - V(z)) H(z) + Q(z)$$

(2.18)

$$\implies V(z) = \frac{H(z)}{1 + H(z)}U(z) + \frac{1}{1 + H(z)}Q(z)$$

(2.19)

From (2.19) it turns out that the delta-sigma converter processes independently the signal and the noise components. Therefore, it can be defined its signal transfer function STF(z) and noise transfer function NTF(z):

$$STF(z) = \frac{V(z)}{U(z)}\Big|_{Q(z)=0} = \frac{H(z)}{1+H(z)}$$

(2.20)

$$NTF(z) = \frac{V(z)}{Q(z)}\Big|_{U(z)=0} = \frac{1}{1+H(z)}$$

(2.21)

and one can also write the output signal V(z) as the combination of the input signal U(z) and the quantization noise signal Q(z), with each being filtered by the corresponding transfer function:

$$V(z) = STF(z) U(z) + NTF(z) Q(z).$$

(2.22)

If one chooses a low-pass loop filter H(z), which have large magnitude over low frequencies, i.e. over the frequency-band of interest  $[0; \omega_B]$ , and small magnitude over high frequencies, than the magnitude of the signal transfer function |STF(z)|will approximate unity over the frequency-band of interest  $[0; \omega_B]$ , hence it will not distort the signal, but the magnitude of the noise transfer function |NTF(z)|will approximate zero over the same band, hence the quantization noise power will be reduced accordingly. The power spectral density of a shaped quantization noise is presented in Fig. 2.7. By doing so, the signal-band spectral composition of the analog input u[n] and digital output v[n] signals will be linearly related, but outside the signal band the spectral composition will differ substantially [26]. Therefore, a digital low-pass filter is used to suppress the out-of-band quantization noise, and a decimator to downsample the filtered but oversampled digital sequence to the Nyquist rate  $\omega_B$  (Fig. 2.8).

In other words, due to the large loop gain given by H(z) over low frequencies, the output sequence v[n] will track with high accuracy the low-frequency input sequence u[n], and the delta-sigma loop keeps the error e[n] very low over low frequencies. However, in order to compare the digital output v[n] with the analog input u[n] and to preserve the high performance of the modulator, it has to be converted back into an analog signal  $v_a[n]$  by a highly linear digital-to-analog converter.

The linearity of the DAC in the feedback loop has to be as good as the overall linearity of the modulator. Because it is difficult to achieve this high linearity in actually available DACs due to analog circuit imperfections (e.g. limited capacitor-ratio accuracy, typical value: 0.1%), inherently linear single-bit DACs are widely used in delta-sigma converters. However, multibit delta-sigma modulators were successfully implemented by using a so-called mismatch-shaping multibit DAC in the feedback path which provides the required high linearity [26], [38, Section 8.3.3]. Moreover, analog [43], [44] and digital [45], [9], [38, Section 8.4] correction techniques are available for multibit delta-sigma ADCs. Unfortunately, multibit delta-sigma ADCs require more complex circuitry, larger chip area and bigger power consumption.

Note that this thesis focuses exclusively on *low-pass* delta-sigma modulators, but the delta-sigma technique is widely applied for *band-pass* signals also. Band-pass delta-sigma modulation allows high-resolution conversion of band-pass signals, if  $f_S$  is much greater than the signal bandwidth  $f_B$ , rather than the highest signal frequency. Band-pass sigma-delta modulators can be used in AM digital radios or receivers for digital cellular mobile radios [37], [38, Chapter 9].

In conclusion, the key-words in delta-sigma converters are: oversampling, noise shaping and single-bit<sup>2</sup> quantization.

#### 2.3.2 Circuit-Level Considerations

According to what was presented so far, a delta-sigma modulator usually contains one or several integrators, a simple comparator and a single-bit DAC included in a feedback loop. The key points in its functioning are to oversample the input analog signal and to high-pass shape the quantization noise using a large loop gain at low frequencies provided by the integrators, and to filter out digitally the out-of-band noise.

Because of oversampling, both the analog and digital circuits should work at high speeds, usually near to the state-of-the-art clock frequency. On the other hand, the requirements for analog continuous-time anti-aliasing filter are relaxed, which is a great advantage of oversampling converters over Nyquist-rate converters.

The analog loop filter should provide a large gain at low frequencies, but this gain can have large fluctuations once it exceeded the required minimum value. Generally speaking, the requirements for the analog circuits are reasonably relaxed due to this large gain in the signal band and using a feedback architecture. On the other hand, the digital signal processing, which includes the low-pass filtering and decimation, raises the digital circuit complexity. However, as the layout

<sup>&</sup>lt;sup>2</sup>The key-word *single-bit* emphasizes on the high-linearity requirement for the feedback DAC, but it does not exclude the possibility of implementing highly-linear *multibit* delta-sigma converters.

density has increased and the power consumption of digital circuits has been reduced over time, this requirement is acceptable nowadays.

In conclusion, delta-sigma converters trade signal bandwidth and very fast circuit operations for higher resolution, and trade analog circuit accuracy for digital circuit complexity. Using standard CMOS technology, the achievable performance is mainly limited by device noise, clock jitter, and other unavoidable effects [26]. Hence, these data converters are the state-of-the art.

#### 2.3.3 Single-Bit Quantizer

One should note that if the delta-sigma modulator uses a single-bit quantizer, that is, a simple comparator, in its internal structure, than Bennett's second and third conditions are not fulfilled (Section 2.1.1), namely the resolution of the quantizer is not asymptotically large, but it is only N = 1 bit, and, in addition, the step size  $\Delta$  is not asymptotically small, but it is as large as  $\Delta = FSR$ . It turns out that the quantization error of a single-bit quantizer cannot be considered mathematically, based on the Bennett's conditions, as an input-independent white noise. Simulation results are presented on Fig. 2.9 for the same full-scale sinewave with a frequency  $0.03 f_S$  as it was considered in Fig. 2.5. It is clear that the quantization error can be hardly considered as an input-independent white noise.

In addition, the gain of a single-bit quantizer is not equal to one, as it was considered correctly for a multibit quantizer. Actually, the gain of a comparator is input-signal dependent, so it is no longer a constant. This can also be intuitively verified in Fig. 2.3.b: for every input  $u[n] \ge 0$ V, the quantized output  $v_a[n] = 1$ V, and for every u[n] < 0V, the quantized output  $v_a[n] = -1$ V, so the instantaneous gain  $\frac{v_a[n]}{u[n]}$  depends on the input signal u[n] values.

However, we can still define a linearized model for the single-bit delta-sigma converter, assuming a white and uniformly distributed additive noise source model, preceded by a gain stage with a gain factor of k, even for the comparator. Surprisingly, the simulation results generally match well with those predicted by the linearized model. The desire for an analytical model to supplement simulations is, of course, motivated by the design insight such a model provides.

In practice, delta-sigma modulators use one or more cascaded integrators for building the low-pass loop filter H(z). Depending on the order of the loop filter one can find first-, second- or higher-order delta-sigma modulators. In the next sections single-loop low-order delta-sigma ADCs will be analyzed.

#### 2.4 First-Order Delta-Sigma ADCs

The simplest delta-sigma analog-to-digital converter is the first-order one, whose block diagram is presented in Fig. 2.10.a. The loop filter is built from a single integrator, which is usually implemented by a simple delayed switched-capacitor

Figure 2.9: The spectrum of a quantized sinewave for N=1 bit

integrator, so

$$H(z) = \frac{z^{-1}}{1 - z^{-1}}.$$

(2.23)

#### 2.4.1 Performance Modeling

Based on the linearized model of the first-order delta-sigma modulator presented in Fig. 2.10.b, (2.22) becomes

$$V(z) = z^{-1} U(z) + (1 - z^{-1}) Q(z).$$

(2.24)

Hence, the signal transfer function  $STF_{1st}(z)$  and its magnitude are given by

$$STF_{1st}(z) = z^{-1}$$

(2.25)

$$|STF_{1st}(z)|^2 = |z^{-1}|^2 = 1$$

(2.26)

Also, the noise transfer function  $NTF_{1st}(z)$  and its magnitude are given by

$$NTF_{1st}(z) = 1 - z^{-1}$$

(2.27)

$$|NTF_{1st}(z)|^2 = |1 - z^{-1}|^2 = \frac{|z - 1|^2}{|z|^2} = |z - 1|^2$$

(2.28)

$$= \left\| \cos \omega T_{S} - 1 + j \sin \omega T_{S} \right\|_{f_{S}=1}^{2}$$

(2.29)

$$= 4\sin^2\frac{\omega}{2}\Big|_{OSR\gg1} \cong 4\left(\frac{\omega}{2}\right)^2 = \omega^2$$

(2.30)

So, the magnitude of the noise transfer function for normalized frequency  $f_S = \frac{\omega_S}{2\pi} = 1$  and for high oversampling ratios, e.g. OSR > 8, which are usual, is simply given by  $|NTF_{1st}(z)| \cong \omega$ . Therefore, the in-band quantization noise power is given by

$$P_{0_{1st}} = \int_0^{\omega_B} |NTF_{1st}(z)|^2 PSD_Q(\omega) \,\mathrm{d}\omega \cong \frac{\sigma_q^2}{\pi} \int_0^{\frac{\pi}{OSR}} \omega^2 \,\mathrm{d}\omega = \frac{\pi^2 \,\sigma_q^2}{3 \, OSR^3} \quad (2.31)$$

Hence, the signal-to-noise ratio  $SNR_{1st}$  can be calculated as

$$SNR_{1\text{st}} = 10 \log_{10} \frac{P_u}{P_{0_{1\text{st}}}}$$

$$\cong 20 \log_{10} \frac{A_u}{A_{max}} + 6.02 N + 30 \log_{10} OSR + 1.76 - 5.17 \quad [\text{dB}].$$

(2.32)

If we consider the oversampling ratio being  $OSR = 2^r$ , than  $30 \log_{10} OSR = 9.03 r$  [dB], so every doubling of the oversampling ratio, i.e. for every increment in r, the  $SNR_{1\text{st}}$  improves by about 9 dB, or the resolution improves by  $1\frac{1}{2}$  bits. In other words, the first-order delta-sigma converter has a 9-dB/octave or 1.5-bit/octave SNR improvement [39, Section 14.2], [37].

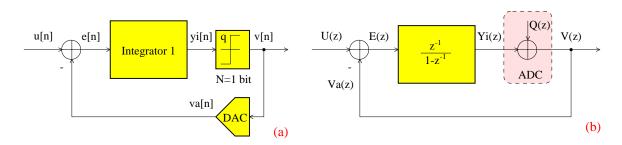

Figure 2.10: (a) First-order delta-sigma ADC and (b) its linearized model

#### 2.4.2 Circuit-Level Implementation

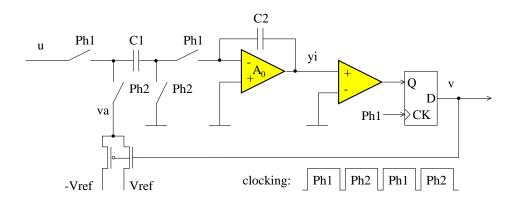

A possible switched-capacitor implementation of the modulator is shown in Fig. 2.11. The analog circuit complexity is clearly quite trivial: it uses 1 switched-capacitor integrator, a single-bit quantizer built from a simple comparator and a D flip-flop, and a single-bit digital-to-analog converter built from 2 reference voltages and 2 switches [17].

Figure 2.11: Switched-capacitor first-order delta-sigma ADC

#### 2.4.3 Time-Domain Analysis

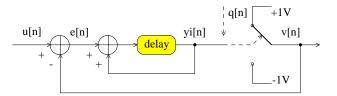

In order to get a deeper insight into the operation of the delta-sigma modulator, a time-domain analysis is required. The time-domain model of a first-order delta-sigma analog-to-digital converter is presented in Fig. 2.12. Note that this is an exact model and there are no underlying assumptions about the statistical properties of the quantization error. In Fig. 2.12 the single-bit quantizer (comparator) is modeled as a true nonlinear element. Hence, one can write the following difference equations: