# POLITEHNICA UNIVERSITY OF BUCHAREST PhD department of Electrical Engineering

# PHD THESIS SUMMARY

# 802.11g STANDARD WIRELESS RADIO COMMUNICATIONS FREQUENCY SYNTHESIZER

PhD: Scientific leader: Msc. Eng. Ursac Iulian Prof.PhD.Eng. Florin Constantinescu

BUCHAREST 2021

# **KEYWORDS**

- -Dual loop PLL frequency synthesizer

- -Digital-controlled oscillator

- -All digital Phase locked loop (ADPLL)

- -Fix-N division factor PLL & Adjustable frequency reference

- -AlN-CMOS oscillator

- BAW AlN resonator

# PHD THESIS CONTENT

Chapter 1: Introduction

Capitolul 2: PLL frequency synthesizer

Capitolul 3: Dual loop WLAN frequency synthesizer having adjustable frequency reference

Capitolul 4: Adjustable frequency reference

Capitolul 5: Conclusions and original contributions

# PHD THESIS SUMARRY CONTENT

| Keywords                                                                      | 2  |

|-------------------------------------------------------------------------------|----|

| PhD Thesis Content                                                            | 2  |

| PhD Thesis Sumarry Content                                                    | 2  |

| 1. Dual loop WLAN frequency synthesizer having adjustable frequency reference | 4  |

| 1.1.CIRCUIT description                                                       | 4  |

| 1.2.Digital Loop                                                              | 5  |

| 1.3.Simulation results of dual loop frequency synthesizer                     | 7  |

| 2. FREQUENCY REFERENCE                                                        | 11 |

| 2.1.Circuit description                                                       | 11 |

| 2.2.Calibration circuit                                                       | 12 |

| 2.3. Simulation results of FREQUENCY REFERENCE                                | 13 |

| 2.3.1.Spectral analysis                                                       | 13 |

| 2.3.2 Phase noise                                                             | 14 |

| 2.3.3 Frequency stability                                     | 14 |

|---------------------------------------------------------------|----|

| 2.3.4 Settling time                                           | 15 |

| 3. Conclusions and original contributions                     | 17 |

| 3.1. General conclusions                                      | 17 |

| 3.2 Original contributions                                    | 19 |

| 3.2.1 Dual loop and fix division factor frequency synthesizer | 19 |

| 3.2.1.1 Fix frequency division factor                         | 19 |

| 3.2.1.2 Dual loop frequency synthesizer: DPLL and ADPLL       | 20 |

| 3.2.1.4 Improving the process of aided capture                | 20 |

| 3.2.1.2 The design way of ADPLL circuit                       | 21 |

| 3.2.1.2 Phase noise improvement                               | 21 |

| 3.2.1.5 Pulse forming network PFN                             | 21 |

| 3.2.2 High speed phase frequency detector                     | 22 |

| 3.2.3 Frequency reference                                     | 22 |

| 3.2.3.1 Fourteen frequencies variable frequency reference     | 22 |

| 3.2.3.2 BAW(AlN)-LC(CMOS) resonator design method             | 23 |

| 3.2.3.3 Frequency compensation method                         | 23 |

| 3.2.3.4 Single chip integration of reference and synthesizer  | 23 |

| List of papers elaborated by thesis author                    | 24 |

| Bibliography                                                  | 25 |

# 1. DUAL LOOP WLAN FREQUENCY SYNTHESIZER HAVING ADJUSTABLE FREQUENCY REFERENCE

#### 1.1.CIRCUIT DESCRIPTION

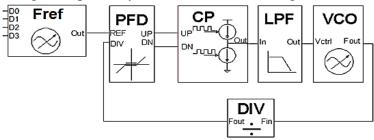

Many high frequency applications as local oscillators for various communication links or network analyzers require the synthesis of a signal having tight error margins for parameters as frequency, settling time and phase noise. A solution to this problem is the phase locked loop (PLL) synthesizer, whose block diagram is given in Fig. 1

The desired signal is provided by the voltage-controlled oscillator (VCO) at its terminal Fout. Usually the frequency reference (FREF) is a quartz oscillator, known for its stability of the oscillation frequency.

The phase and frequency detector (PFD) compares the reference signal REF with the divided oscillator signal available at Fout of the frequency divider (DIV). PFD gives the UP command if Fref > (Fout of DIV) or the DN (down) command if FREF<(Fout of DIV).

The charge pump (CP) can give at its terminal OUT a positive or a negative current. After being filtered by a low pass filter (LPF), this signal is applied to the VCTRL terminal of the voltage-controlled oscillator (VCO). The positive current increases the oscillation frequency of VCO, while the negative current diminishes its value. PFD has a "dead zone" corresponding to no UP or DOWN output signal (see Fig. 1).

Usually, FREF is an oscillator providing a constant oscillation frequency. In the classical solution the desired VCO frequencies are those imposed for the transmission channels of wireless standard 802.11g, which are obtained with different division ratios of DIV, while the FREF has a constant frequency.

A new approach to a frequency synthesizer is proposed: instead of a fixed frequency reference oscillator and a variable ratio frequency divider we use a variable frequency reference oscillator and a fixed ratio frequency divider.

Moreover, the classical passive quartz resonator is replaced by an active AlN bulk acoustic wave (BAW) resonator which can be built in the same system on a chip (SoC) with the electronic CMOS circuit, due to the high compatibility between these technologies [3].

Fig. 1 Block diagram of a PLL synthesizer

In top of that a dual loop architecture is used. This solution has the advantage of a reduced phase noise and settling time with respect to the single loop synthesizer.

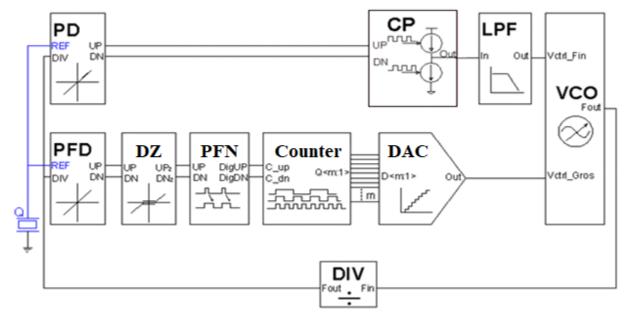

The block diagram for this approach is that in Fig. 2. The differences with respect to the classical solution are: the frequency reference gives an output with variable frequency, and the division factor of DIV is constant.

Fig. 2 Dual loop frequency synthesizer

The voltage controlled oscillator has two control inputs, one for a fine frequency adjustment (Vctrl\_Fin) and the other for a coarse frequency adjustment (Vctrl\_Gros).

The way in which the contributions of the two loops are summed on the oscillator using two different control elements is clearly superior to the way the summation on the filter goes down mainly for two reasons: a) the oscillator would have had a single variable capacitor of very high value involving a high phase noise, at the same time fails to achieve a sufficiently small frequency variation step, b) the low pass filter with high value capacitors, the contribution of the fine-tuning loop does not get to be used at maximum performance.

The first loop presents a predominantly analog topology and controls the low gain input (fine control) of the Vctrl\_fin oscillator. The working mode of this loop is on the signal level, so the pulse width from the output of the PD phase detector circuit dictates the size of the frequency jump from the synthesizer output. As we saw in subchapter 2.1, the control on the signal level generates phase noise problems if the gain of the charge pump is high. In our case we minimized the phase noise of the system by achieving a small gain of the charge pump.

#### 1.2.DIGITAL LOOP

The second loop presents a predominantly digital topology and controls the high gain input (coarse control) of the oscillator (Vctrl\_Gros). The mode of operation of this loop is on the front of the signal. This way of working has a huge advantage for our application, because we will be able to use it efficiently in the control of the VCO oscillator using extremely narrow pulses from the PFD output. Since we replaced the charge pump we have the advantage that no matter how big

the pulse width from the phase detector output and the PFD frequency, the switching noise will be the same, becuse the synthesizer changes its output frequency with a well determined step with the clock signal transition of the counter (active on the rising front). As we saw in subchapter 2.3, fully digital systems have a limitation of the output frequency range due to the finite states of the counter, this being the main reason why we chose to design a system with two PLL loops.

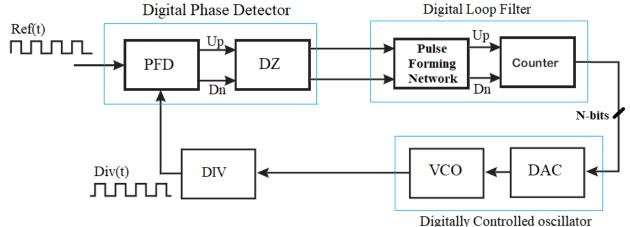

Fig. 3 Digital loop schematic

The digital adjustment loop consists of the following blocks:

- -Digital phase and frequency detector (Digital Phase Detector). This block consists of a sequential phase and frequency detector (PFD) to which is added a block that introduces a dead zone in the detection characteristic (DZ). The phase and frequency detector (PFD) provides a digital voltage whose pulse width is proportional to the phase difference of the two input signals. Dead Zone (DZ) circuit that has the role of setting the detection sensitivity of the coarse adjustment loop. In this way, the operation of the digital loop can be limited only in the acquisition mode.

- -Digital Loop Filter. It consists of a pulse forming circuit (Pulse Forming Network = PFN) which has the role of controlling the reversible counter on N bits (Counter). The PFN circuit increases the width of the narrow pulses from the DZ output up to 50% of the reference clock period, in order to be able to control the counting direction. The reversible counter (Counter / NR), increments or decrements the output of the digital-to-analog converter DAC depending on the control signal received at the input.

- -Digitally controlled oscillator. It consists of an analog-to-digital converter (DAC) and a voltage controlled oscillator of type LC (VCO). Digital to analog converter (DAC) controls the voltage of the VCO oscillator. The variation of the output frequency of the synthesizer is made with the help of the input voltage of the VCO oscillator.

- The frequency from the output of the VCO oscillator is divided by the frequency divider DIV with a fixed division factor N =fixed. The frequency divider is common to the two phase-mounted loops in the frequency synthesizer component.

The phase frequency detector compare the phase of the reference signal  $\Phi$ ref(t) with the digital controlled oscillator divided phase  $\Phi$ div(t): vd(t)=f( $\Phi$ div(t)- $\Phi$ i(t)). If  $\Phi$ div(t)> $\Phi$ i(t), on the PFD output, is active UP output, otherwise, will be active DN output. The PFD output signals

(UP1 or DN1) are tiny pulse width. Pulse width modulator (PWM) increase the pulse width of phase frequency detector output signals (UP1 or DN1). The up/down counter, change state in either direction, under the control of an up/down selector input, that cams from the pulse width modulator output. When the selector is in the up state, the counter increments its value. In this case, the digilat controlled oscillator receives at the input commanda to increase the output frequency. When the selector is in the down state, the counter decrements the count. In this case, the digilat controlled oscillator receives at the input commanda to decrease the output frequency. A change in frequency, is proportional with a phase shift. In this way we controll the output frequency to stay fix at the wanted frequency, upon the reference frequency.

# 1.3.SIMULATION RESULTS OF DUAL LOOP FREQUENCY SYNTHESIZER

The design and transistor-level simulation of each block in the DPLL circuit was done using the SPECTRE simulator in the CADENCE environment, using the 0.18um technological process from TSMC. The frequency synthesizer simulation is partially performed using the models described in the verilog language due to the limited processing resources of the computer used in running the simulations.

The parameters of the frequency synthesizer used in the simulation are presented in the table below:

Fine-tuning analog loop and coarse-tuning digital loop Reference frequency Fref 100MHz VCO output frequency 4.8GHz <del>25\*2=50</del> Division factor CP current 50uA Low gain VCO input 10MHz Hight gain VCO input 200MHz Analog Low pass filter param. Rz 62Kohm Cz 6.33pF Cs 101pF

Table 1 Block parameters used in simulation

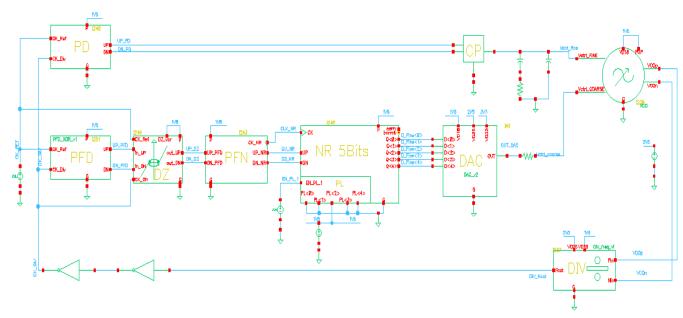

In the following figure we have the test schematic of the dual loop frequency synthesizer.

Fig. 4 Test schematic of dual loop frequency synthesizer

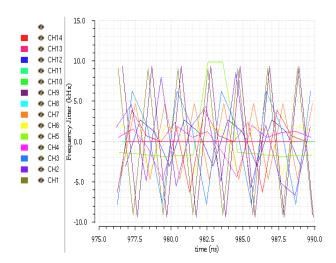

The result of the simulation in the transient domain of the two-loop frequency synthesizer are presented below:

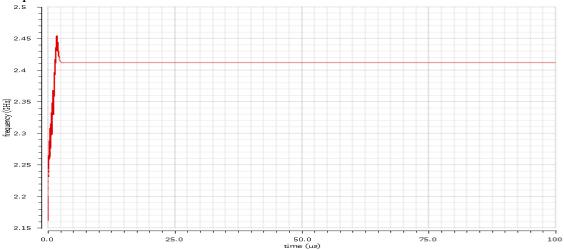

Fig. 5 Start up synthesizer frequency response

The figure above shows the output frequency of the two-loop frequency synthesizer, simulating the most unfavorable case for setting the frequency, namely at startup. It can be seen from the figure that we have a fast setting time, after up to 100us the output frequency of the

# synthesizer remains stable.

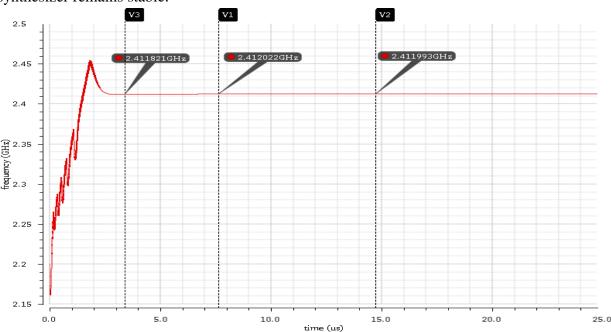

Fig. 6 Zoom of Start up synthesizer frequency response

The figure above shows only the beginning, the first 25us of the simulation to be able to see in detail how the frequency stabilizes. A very fast acquisition regime of up to 3us is observed, following a stabilization of the frequency up to 6.7us near the desired frequency. After 6.7us we can say that the loop has stalled and is working in tracking mode because it reaches the set frequency with a tolerance that falls within the accuracy of  $\pm$  25ppm calculated to be 60KHz. It is also observed that the transient regime shows some fluctuations with increases and decreases, behavior that can be caused by the so-called "cycle sleep" phenomenon, the main cause being the phase and frequency comparator that has a detection limitation.

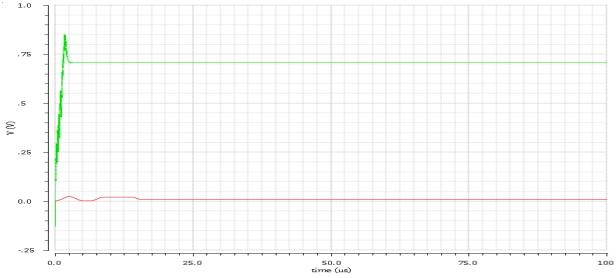

Fig. 7 Voltage control oscillator red=fine tunning and gren= coarse tunning

The figure above shows the oscillator control voltages for the fine reflection (red) and coarse frequency adjustment (green) inputs.

It is observed that the voltage for the coarse control (green) has the same look as the evolution of the output frequency because it is the predominant contributor. It is also observed that we have fast jumps that denote the broadband of the digital filter and the predisposition towards a fast response of the system necessary to obtain a fast frequency time.

It is observed that after 3us a stabilization of the coarse adjustment voltage (green) following that the fine adjustment voltage (red) to determine the final oscillation frequency. We have a slow variation of the control voltage of the fine frequency adjustment (red) which highlights the fact that it filters the high frequency signals to improve the phase noise of the system.

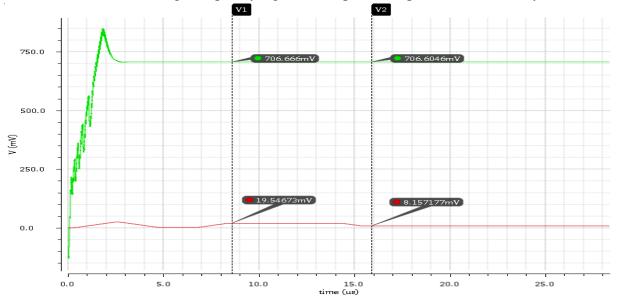

Fig. 8 Voltage control oscillator startup zoom

The figure above is focused on the beginning, the first 25us to observe in detail the voltage variation described above.

The signal from the input of the frequency oscillator faithfully mirrors the variation of the signal from the output of the frequency synthesizer. Thus, based on the control voltage at the input of the oscillator, we can determine the moment when the frequency synthesizer reached the tracking mode where the output frequency of the synthesizer is equal to the input frequency multiplied by the loop splitting factor.

# 2. FREQUENCY REFERENCE

## 2.1.CIRCUIT DESCRIPTION

A new approach with respect of the above one is proposed in this paper, namely a PLL frequency synthesizer using a frequency reference, which provides a signal having a set of frequencies, so that the desired set of VCO frequencies can be obtained with a divider whose division ratio remains unchanged.

The frequency reference scheme is presented in the figure below:

Fig. 9 Variable frequency reference schematic

In above figure, the implementation and characterization of a low phase-noise compensated oscillator (VCO) used as frequency reference for a WLAN wireless transceiver is described.

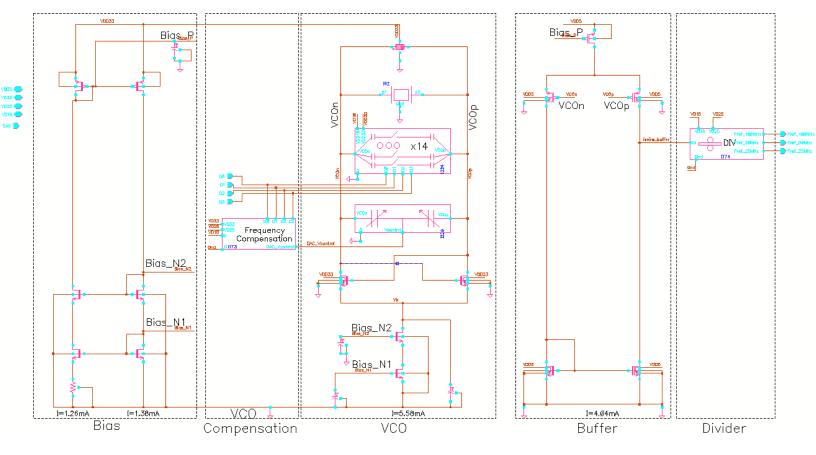

In this case the frequency reference block Fref contains the blocks in Fig. 2: BIAS (the circuitry for DC supply), VCO (reference oscillator), Compensation (calibration circuit), BUFFER(output buffer), and Divider (frequency divider).

This circuit employs a high Q piezoelectric resonator together with a CMOS cross coupled pair amplifier. A calibration circuit for compensation of frequency errors with respect to process variation is proposed (Compensation).

The DC polarization (BIAS) of the active circuit is made using a Widlar cascoded voltage reference, a 3.3V voltage supply and has a total current consumption of 2.64mA.

The buffer circuit (BUFFER) it is a PMOS differential pair amplifier with a NMOS current mirror active load and a PMOS current source, having a 5V supply voltage and 4.04mA current consumption.

The divider by 10 (DIVIDER) is made with two classical dividers, a divider by 2 followed by a divider by 5.

# 2.2.CALIBRATION CIRCUIT

The AlN BAW resonance frequencies are influenced by temperature and changes of the technological process. Two types of methods are applied for the frequency drift compensation with temperature of a BAW AlN oscillator working in a certain frequency band. The first one uses a passive compensation, which can lead to a minimum relative error of  $\pm 40$ ppm frequency shift over the entire temperature range [10]. The second one employs an active way of compensation and can lead to a minimum error of  $\pm 10$ ppm over the entire frequency range [11].

The CMOS process changes can lead to variations up to 30% of capacity or resistance values. In the AlN BAW technology, the piezoelectric layer thickness can vary from sample to sample leading to deviations of fs and fp, also.

Some methods based on trimming using passive circuit elements, which compensate OSC frequency errors are described in [12] and [13]. These methods are suitable just for one output frequency; for multiple frequencies their associate testing cost being increased by the trimming process.

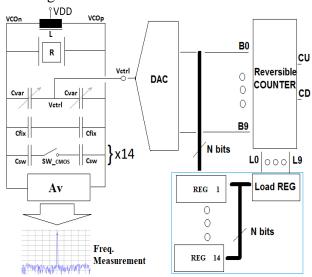

Taking into account that a wireless transceiver is placed usually inside a building, this location having no significant temperature variations, a new approach to compensate frequency errors with respect to process variation is proposed. The block schematic of the oscillator calibration circuit is given in Fig. 10.

Fig. 10. Block schematic of the calibration circuit

The upper left part of Fig. 10 shows the capacitors in Fig. 6, which are used to obtain the desired oscillation frequencies. The frequency reference calibration is performed for each of the 14 output communication channels when the wireless transceiver is tested. The channel is selected using the appropriate Csw fixed capacitor pair by closing the appropriate set of SW-CMOS switches. At each frequency we drive the Reversible COUNTER to count up (CU) or to count down (CD) in order to sweep the full range of Vctrl values from the output of the digital to analog converter (DAC). The DAC output voltage controls the variable capacitors Cvar till the desired frequency is obtained. When the Spectrum Analyzer measures this value in the reference output, the reversible counter digital output is recorded in the appropriate nonvolatile register (REG1, ..., REG14). After the calibration process, the result is a 10 bits digital code for each channel frequency generated by this circuit.

In the normal operation of the frequency reference, when a communication channel is selected with a 4 bits digital word, the same word is used to select its 10 bits code for frequency calibration recorded in the nonvolatile memory. This code is loaded into a 10 bits load register (Load Reg) which controls the reversible counter, in order to command the DAC output voltage to drive variable capacitors Cvar to the values corresponding to the prescribed channel frequency.

# 2.3. SIMULATION RESULTS OF FREQUENCY REFERENCE

# 2.3.1. Spectral analysis

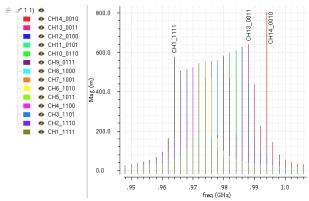

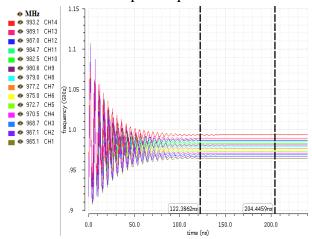

Spectral analysis results of the reference frequency circuit for the unbuffered OSC, containing all 14 output frequencies is given in Fig. 11. This picture gives a measure of spectral purity of the unbuffered OSC.

Fig. 11. Spectral analysis of unbuffered OSC

We observe the ascendant trend of the oscillation amplitude for the last 13 frequencies. This effect can be explained by the lowering of the total Q factor determined by adding a new CMOS capacitor in parallel to a BAW resonator, due to the low Q of CMOS capacitors and to the capacitor switch resistance.

As BUF is an amplifier whose output signal is limited by its DC supply, its output signals have the same amplitude for all frequencies.

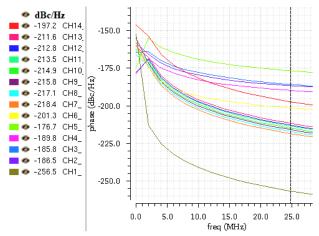

# 2.3.2 Phase noise

The 802.11g standard specification regarding the phase noise requirement is described by Interference=+35 dB (measured at 25 MHz offset from the carrier). The phase noise analysis for all 14 channel frequencies, performed at the OSC output (Fig. 2) is presented in Fig. 12. These results are computed with PN analysis of CADENCE. The maximum value of the phase noise is -176.7 dBc/Hz obtained for the channel 5 (Fig. 12). This value complies with the specifications of the 802.11g standard [14].

Fig. 12. Unbuffered OSC phase noise analysis

# 2.3.3 Frequency stability

In order to improve the frequency reference stability, the VCO is designed at high frequency, around 970 MHz. Using the frequency division by 10 the frequency deviation against median value is decreased 10 times. Starting from 802.11g standard specification with  $\pm 25$  ppm an allowed frequency deviation of  $\pm 600$  KHz results in the range of 2.4 GHz. At the OSC output, where the simulation result in Fig. 13 is given, this allowed frequency deviation is  $\pm 24$ KHz (between 24.84 KHz for CH1 and 24 KHz for CH14). The simulation results computed with the freq\_jitter analysis of CADENCE are given in Fig. 13 and comply with these limits.

Fig. 13. Unbuffered VCO Jitter analysis

# 2.3.4 Settling time

The settling time according 802.11g standard specification need to be  $224\mu s$  for the whole 2.4GHz frequency synthesizer. For the unbuffered frequency reference settling time we impose a limit below 1% ( $2.24\mu s$ ) of the total settling time of the wireless transceiver. The maximum settling time is the time to change between communication channel frequencies; The start-up time represents the worst case. Next picture presents the simulation results for the worst case (start-up settling time) for all 14 VCO unbuffered output frequencies.

Fig. 14. Unbuffered OSC settling time analysis

We observe that settling time is different across output frequencies. The values are between 122.3ns and 205ns worst case, representing a value smaller than 10-3 from 224µs (the total settling time of a frequency synthesizer given in the 802.11g standard specification) [14].

#### 4. CONCLUSIONS

The approach proposed in this paper has several advantages:

- The possibility to include the MOS circuitry together with the AlN BAW resonator in a system in a package (SiP).

- Using a frequency reference providing a variable frequency signal, the FDIV has a fixed division ratio for all channels of the wireless transceiver. This approach eliminates a main source of noise in the classical solution the FDIV with variable division factor.

- A compensation circuit for the process variation has been proposed, in order to satisfy the specifications of the wireless standard 802.11g regarding the parameters of the carrier signals for all 14 communication channels.

In order to prove these advantages, some simulations using several CADENCE analyses have been performed, using the design kit of the TSMC 180nm technology.

#### 3.CONCLUSIONS AND ORIGINAL CONTRIBUTIONS

## 3.1. GENERAL CONCLUSIONS

This doctoral thesis presents two frequency generation solutions within WLAN wireless radio communications systems. The first solution is a variable frequency reference that has fourteen output frequencies for a phase-locked loop. The second solution is a dual-loop frequency synthesizer PLL, which uses the frequency reference block mentioned above. Both circuits are compatible with the 802.11g WLAN communication standard which serves fourteen communication channels in the frequency range 2.412 GHz - 2.484 GHz.

The results of the electrical simulations are obtained using the Specter simulator from the CADENCE design environment. The 0.18um technological process used in the simulations comes from the manufacturer Taiwan Semiconductor Manufacturing Company (TSMC).

In the first chapter is presented the WLAN wireless communication standard as an operating application for the dual loop PLL frequency synthesizer. It begins with a brief introduction to the field of wireless WLAN communication systems, and will address the most important parameters in the design of a frequency synthesizer for the WLAN communication standard 802.11g. There are a number of problems in wireless communication systems due to deviations of the block parameters in the PLL frequency synthesizer.

The second chapter introduces the field of frequency synthesizer circuits. The frequency synthesis methods are presented and we will focus on the principle of indirect frequency synthesis, based on a phase locke loop (PLL). This technique was imposed, both due to the performances related to the broadband of the generated frequencies, the small step of variation and the stability of the output frequency. The main types of PLL are highlighted, and we will focus on two types of phase-locked loops (DPLL and ADPLL).

The frequency synthesizer proposed in this paper is a dual loop architecture, one PLL loop presents the characteristics of digital PLL circuits (DPLL) and the other the characteristics of all digital PLL circuits (ADPLL). For both DPLL and ADPLL, the advantages and disadvantages are presented in order to easily highlight the performance and weaknesses of entire dual-loop frequency synthesizer presented in Chapter 3.

DPLL loop can have several ways of implementation in terms of component blocks used [with or without charge pump, active or passive LPF filter, oscillator type (LC; ring oscillator, etc ...)] . It was considered the presentation of a DPLL that contains the charge pump and LC type oscillator also called CP-PLL because it is the most common topology used in radio communications due his performance. The component blocks, their operation mode and the problems encountered in the CP-PLL are presented.

The ADPLL can also have several ways of implementation in terms of the component blocks used. A review of the component blocks and the implementation modalities is made, following to briefly describe the blocks that are used in the synthesizer proposed in chapter 3.

The circuit proposed in Chapter 3 is designed to meet the design specifications for the WLAN 802.11g communication standard. In the first part of chapter 3 is presented the operation

and design method of the proposed dual loop frequency synthesizer. The simulations performed in the third part ensure that the proposed frequency synthesizer system complies with the requirements imposed by the 802.11g WLAN standard.

In the last part of chapter 3 we have a description of the blocks in the component of the proposed frequency synthesizer and how they work. The current trend is towards the digitization of analog architectures for reasons of area, power, portability of the project to other production technologies. In order to meet the problems of the CP-PLL loop and those of the ADPLL loop reported in Chapter 2, the diagram of a new dual loop frequency synthesizer is presented. At the same time, in order to optimize the compromise achieved in the design of a PLL circuit related to two parameters: noise and frequency settling time, two feedback loops are proposed. The first fine tuning loop of the oscillator is of DPLL type, it has a small gain (gain) on the loop and determines a fine adjustment of the frequency at the system output. Because only the DPLL loop will work in the tracking mode, we will have excellent phase noise performance due to the small gain on the loop that helps us to avoid fast frequency jumps. The filter of this loop is dimensioned with a low cutting frequency to limit the rapid variations of the oscillator control voltage.

The DPLL loop is predominantly analog, consisting of a single digital block: the PD phase detector and the following analog blocks: the CP load pump and the LPF low-pass filter. The second coarse adjustment loop of the oscillator is of ADPLL type, it has a high gain (gain) on the loop and the step of varying the output frequency of the system is approximately equal to the frequency range of the DPLL loop. We say approximately because it is necessary to have a 20% overlap of the DPLL bands between two consecutive steps of the ADPLL frequency. Because in the acquisition (capture) mode, the ADPLL loop will have a majority behavior, it determines a fast settling time with the help of the large gain on the loop. The low pass filter must have a high cutoff frequency to respond quickly to the loop, but at the same time a higher noise component will pass to the oscillator.

The ADPLL loop is mainly made of digital blocks: phase and frequency detector (PFD), Dead\_zone circuit (DZ), pulse forming circuit (PFN), reversible counter (Counter) and a single mixed block (digital-to-analog converter). The frequency divider that closes both loops (DPLL and ADPLL) has a fixed division factor, the variation of the output frequency of the synthesizer is made using the frequency reference presented in Chapter 4. Achieving the performance of using a frequency divider very simple a The major advantage of the proposed phase and frequency synthesizer is that it avoids the noise introduced by a high complexity frequency divider such as the whole or fractional type.

Another major advantage of the proposed new dual loop frequency synthesizer is the combination of the phase noise performance of the DPLL loop with the advantages of a fast ride time of the ADPLL loop. Combining the two types of loops, we obtain a system clearly superior to the one with two DPLL loops or two ADPLL loops.

The fourth chapter deals with the design of a variable frequency reference intended to operate together with the frequency synthesizer with fixed division factor proposed in Chapter 3. Thus the frequency at the output of the frequency synthesizer is changed by varying the reference

frequency. You can select fourteen output frequencies that serve the fourteen communication channels within the 802.11g wi-fi standard.

The design and simulation of the electrical circuits of the frequency reference were made in CMOS 0.18um TSMC technology. Not having a BAW resonator design technology produced in AlN technology, an equivalent BDV model with ideal elements was used in the simulations. In order to have an accurate measurement of the resonator model, we used a parameters of BAW resonator produced in AlN technology [107].

Frequency stability and phase noise are the main characteristics of a frequency reference. Each block in the frequency reference component has been designed to minimize noise sources so that the total frequency reference noise is minimal.

This frequency reference is made of a high precision variable oscillator that combines the advantages of achieving a Q quality factor of over 1000 of a resonator produced in AlN technology and the versatility of the circuits produced in CMOS technology.

The oscillator amplifier A consists of a differential pair of NMOS transistors. The resonant circuit is a combination of a BAW piezoelectric resonator and an LC CMOS resonator. MEMS BAW micromechanical resonators have a high Q quality factor and facilitate the trade-off between power consumption and selectivity (Q), having a high potential for versatility with multiple frequency bands [143]. The BAW type piezoelectric resonator made in AlN technology can be easily integrated with the CMOS production process so the variation of the output frequency is made with a series of switched CMOS capacitors.

In order to compensate the variations of the output frequency due to the variation of the technological production process CMOS, the present paper proposes a calibration circuit of the frequency variation with the variation of the technological process. The calibration method involves measuring the fourteen obtainable output frequencies after encapsulation and storing the calibration code for each frequency that compensates for the deviation from the nominal value in a non-volatile memory area (eg fuses or EPROM memory). Thus, in the normal operation of the synthesizer circuit, with the same four bits that select the fourteen output frequencies, the unique calibration code corresponding to the selected frequency will be activated.

# 3.2 ORIGINAL CONTRIBUTIONS

In this doctoral thesis the following original solutions can be highlighted:

# 3.2.1 Dual loop and fix division factor frequency synthesizer

Chapter 3 presents original contributions of Dual loop and fix division factor frequency synthesizer:

# 3.2.1.1 Fix frequency division factor

The whole or fractional frequency divider are noise generating circuits due to the additional logic needed to be able to change the division factor. By changing the output frequency of the

synthesizer using the variable frequency reference [see chapter 4], it gives us the chance to use a divider with a fixed division factor. Thus, the structure and complexity of the frequency divider circuit are substantially simplified, implicitly decreasing the related noise. In the literature we did not find a frequency synthesizer with a phase-locked loop that works at high frequency (2.4GHz, WiFi communications) and has a divider with a fixed division factor.

# 3.2.1.2 Dual loop frequency synthesizer: DPLL and ADPLL

The literature presents many examples of synthesizer circuits with dual digital phase lock loops (DPLL) or more recently with dual all digital phase locked loops (ADPLL) [see subchapter 2.4]. A novelty in the proposed frequency synthesizer is the fact that the dual loops are different (ADPLL and DPLL), in this way managing to improve the operation of two loops with the help of the particular advantages of each type of loop.

Within the proposed dual-loop synthesizer circuit, we combine the advantage of the low frequency resolution characteristic of DPLL circuits, with the advantage of a fast output frequency setting time offered by an ADPLL loop. Therefore, in comparison with the proposed dual-loop PLL circuit with the DPLL or ADPLL circuit, it has a better phase acquisition speed than DPLL circuit and a better frequency resolution than in the case of the ADPLL circuit [27]

### 3.2.1.4 Improving the process of aided capture

To reduce the settling time of the PLL circuit, the frequency acquisition is aided by a circuit called in the literature aid circuit. The digital logic used in the aid circuit greatly complicates the electrical schematisc of the PLL loops, but makes the user's work much easier and increases the performance of the final circuit. However, there is the advantage that the aid circuit occurs in the same capsule as the frequency synthesizer [8].

We have a great advantage in the proposed synthesizer, because we use as aid circuit parts already existing in the synthesizer, so there is no additional logic.

In order to reduce the settling time of the proposed frequency synthesizer, the frequency acquisition is aided by two procedures:

- -We use two adjustment loops, of which the high gain ADPLL loop ensures a high frequency capture band.

- -We start with the control voltage of the oscillator from a value very close to the one at which its output frequency is set

The aid circuit is implemented with the ADPLL loop, which presents the possibility to predefine the oscillation frequency with the help of the parallel charging of the counter. On the parallel charging of the counter, we can put the digital combination that sets the output of the digital analog to DAC converter at the value of control voltage required for the oscillator to oscillate on the desired frequency. In this way we can establish for a certain period a value of the initial oscillation frequency which is very close to the value of the wanted frequency.

### 3.2.1.2 The design way of ADPLL circuit

The ADPLL loop part of dual loop frequency synthesizer represents an original concept, inspired by the way of performing the direct frequency synthesis. The ADPLL have all the component blocks made digitally and works on the signal front, replacing the working mode on the signal level used in the control of the charge pump block in the DPLL loop.

A unique element is the way in which the ADPLL coarse adjustment loop in the synthesizer circuit is activated automatically depending on the need to use it only for the case of large phase shifts between the input signals. Thus, the ADPLL loop will work at the start of the synthesizer circuit and at the time of high frequency jumps, ensuring a very fast phase acquisition. When the frequency at the output of the oscillator approaches the value of permanent mode, the fully digital loop ADPLL, will cease its activity automatically. Only the analog loop will be used for fine frequency adjustments. This mode of operation has the advantage of obtaining a short frequency settling time as well as a low phase noise.

The ADPLL presented in the chapter is an original concept, which offers a series of advantages due to the replacement of the charge pump with a series of digital blocks that have the possibility to more precisely control the control voltages of the oscillator.

The great advantage of this type of circuit operation is the fact that the system is autonomous, and can decide for itself when to suppress the operation of the ADPLL coarse adjustment loop, by using the dead zone block DZ.

# 3.2.1.2 Phase noise improvement

The main method of decreasing the phase noise of the synthesizer is achieved by decreasing the gain of the blocks in the analog loop component that is used in the tracking mode. Thus we manage to reduce the implicit load pump currents and the noise determined by them.

Another method of reducing noise is to use two loops. We can transfer most of the gain to the second loop. For a fast settling time of the second loop we need IUP currents, high IDNs at the output of the load pump. A high current in the load pump implies the increase of the dimensions of the CMOS transistors from the component of the current sources and the CMOS switches. A larger transistor has a higher input equivalent capacity. The frequency detector must control a higher output capacity so that the disadvantage of the dead zone from the transfer characteristic that leads implicitly to noise problems appears. By replacing the second loop that has a high gain of the component blocks with a digital loop, all the noise problems mentioned before disappear.

#### 3.2.1.5 Pulse forming network PFN

PFN pulse forming circuit connecting the phase and frequency detector block PFD and the NR counter block is an original concept designed especially for this particular case of digital signal conversion with variable filling factor from the phase and frequency detector, in digital signal with 50% fill factor. We need this block because the control of the counting direction cannot be done with a signal that has a narrow pulse width coming from the output of the phase and frequency detector circuit.

The design of the PFN circuit is not inspired but rather designed specifically for the functionality required for the entire synthesizer system. The basic idea to ensure at the input of the counter a control signal with sufficient pulse width to maintain the counting direction is to make a division by four of the signal from the output of the frequency detector to which is added a simple control logic to have only one active output at a time.

# 3.2.2 High speed phase frequency detector

The design of the detector proposed in subchapter 3.4.1.2 is better than high-speed PFD presents at point 2.1.1 because of reducing of propagation time throught detector. In the proposed design we manage to eliminate the delay element from the signal path of the high-speed PFD presented at 2.1.1.

The design proposed in 3.4.1.2 is made with digital blocks as opposed to the High speed low power PFD design from point 2.1.1. This gives it the advantage of having better portability when changing the production process.

# 3.2.3 Frequency reference

In chapter four we have the following original contributions:

# 3.2.3.1 Fourteen frequencies variable frequency reference

Frequency reference with fourteen switchable values in the range 96.48MHz-99.36 MHz is designed to meet the constraints of the 802.11g wireless communication standard. The frequency reference offers the possibility to select the output frequency of the frequency synthesizer circuit (PLL type) by changing the value of the reference frequency and not the PLL loop division factor as usual. Thus we can facilitate the change of the frequencies related to the fourteen communication channels of the 802.11g wireless communication standard, with the help of the reference frequency.

Achieving a frequency reference with fourteen selectable output frequencies is quite difficult having multiple constraints on the maximum value of the achievable frequency and the quality factor. The frequency reference proposed by us which has the frequency of the undivided internal oscillator approx. 1GHz is better unlike other works where we meet a maximum number of 4 generated frequencies (176MHz, 222MHz, 307MHz and 482MHz) with a maximum frequency of 482MHz [133]. In the case of [133] the frequency variation is made with the help of four BAW resonant circuits unlike in our case where the frequency variation is made with the help of an additional LC CMOS resonator. We get a degradation of the quality factor, but we gain a wide range of values that can be switched.

### 3.2.3.2 BAW(AlN)-LC(CMOS) resonator design method

The frequency reference circuit design is an iterative process because we have two resonators that are connected in parallel, with different frequency characteristics that must be tuned to operate on the same frequency. The method of designing the selection of the fourteen frequencies is innovative because the LC\_CMOS and BAW elements have an interdependence relationship that requires the redesign of one of the resonators when modifying the other. The L\_CMOS coil has the role of increasing the fp parallel resonance frequency of the BAW resonator compared to the fs series resonance, in order to offer the possibility for Csw\_CMOS switched capacitors to select the fourteen wi-fi communication channels by decreasing the fp frequency to fs. The main idea is to size the ends of the frequency range so that we have an idea of the total capacity needed to sweep this frequency range. By successive simulation iterations, the total capacity is distributed on the fourteen switched capacitors Csw.

# 3.2.3.3 Frequency compensation method

The method of compensating the variation of the output frequency of the frequency reference block together with the variation of the CMOS / AlN production process is designed in order to minimize the interaction of the human operator in the usual mode of operation of the circuit. In mass production we can find a passive method to compensate the oscillation frequency with the variation of the technological process based on the trimming process [114] [115]. This trimming method is suitable for the case when the oscillator is focused only on a nominal oscillation frequency. In the case of an oscillator with several nominal output frequencies, a new approach is needed. The paper focuses on the realization of a method of frequency compensation with the process, suitable for oscillators with multiple output frequencies. The new compensation method is a dynamic one, offering multiple control ways due to the possibility of software contrhol. The frequency compensation method itself presents a collection of innovative elements that are listed below:

- Dual possibility of storing the fourteen calibration codes using non-volatile solutions: EPROM memories

- How to load the calibration codes and generate the voltage that controls the variable capacitor to compensate the frequency.

#### 3.2.3.4 Single chip integration of reference and synthesizer

The proposed frequency reference uses as main element a BAW type resonator made in AlN technology that has a very good compatibility with the CMOS production process. Due to the very good compatibility between AlN and CMOS technology, it is possible to make an entire 2.4GHz wireless transmitter working in the same capsule that works according to the 802.11g standard.

### LIST OF PAPERS ELABORATED BY THESIS AUTHOR

- [1] Iulian Ursac, Florin Constantinescu "Calibration of a Frequency Reference for the Communications Standard 802.11g", International Symposium on Fundamentals of Electrical Engineering, University Politehnica of Bucharest, November 5-7, **2020**.

- [2] Iulian Ursac, Florin Constantinescu "A New Dual Loop Frequency Synthesizer for the Wireless Standard 802.11g", International Symposium on Fundamentals of Electrical Engineering, University Politehnica of Bucharest, November 5-7, **2020**.

- [3] Iulian Ursac, Florin Constantinescu, Mihai Marin, "A frequecy reference for carrier synthesis in wireless standard 802.11g", The Scientific Bulletin of the Electrical Engineering Faculty Volume 20 (2020): Issue 1 (April 2020), pp. 56-61, ISSN 2286-2455,

#### DOI: 10.2478/SBEEF-2020-0112

[4] Mihai-Eugen Marin , Catalin Brinzei, Florin Constantinescu, Alexandru Gheorghe, Iulian Ursac, "Design of a 8 bit current steering DAC for a GSM transmitter", International Symposium on Fundamentals of Electrical Engineering, November 28-29 2014, University Politehnica of Bucharest, Romania. INSPEC: 14949280, WOS 000380570500033.

https://ieeexplore.ieee.org/abstract/document/7050565?section=abstract

[5] Iulian Ursac, Catalin Brinzei "Dual Loop PLL for a Radio Frequency Transceiver", Universitatea "Politehnica" din București, Inginerie Electrică, 14 Decembrie SNET 2012. Google Scholar

# https://pdfs.semanticscholar.org/3d1f/b1d656e9de52d94007cac32074f55a3161fb.pdf

[6] Catalin Brinzei, Iulian Ursac "Frequency mixer based on a resistor string Digital-to-Analog converter", Universitatea "Politehnica" din București, Inginerie Electrică, 14 Decembrie SNET 2012. Google Scholar

# http://snet.elth.pub.ro/snet2012/volume/P1.18.pdf

[7] Catalin Brinzei, Florin Constantinescu, Iulian Ursac "Digital mixer with current steering DAC", Universitatea "Politehnica" din București, Inginerie Electrică, 14 Decembrie SNET 2012. **Google Scholar**

# http://snet.elth.pub.ro/snet2012/volume/P1.10.pdf

[8] Ursac Iulian, Ivu Ciprian, "Sistem of Surview using Accelerometer Sensor", Third European Conference on Intelligent Systems and Technologies, 21 - 23 July ECIT'2004

## http://www.etc.tuiasi.ro/sibm/ECIT'2004/program.htm

[9] Iulian Ursac, Catalin Brinzei, "Sintetizor de Frecvență PLL cu Arhitectura Digitala", Universitatea "Politehnica" din București, Inginerie Electrică, 3-4 Decembrie SNET 2010.

# http://snet.elth.pub.ro/snet2010/index.php?action=program

[10] Catalin Brinzei, Iulian Ursac "Low Noise Amplifier in combination with the differentialdown-conversion mixer utilizing the current-reuse technique", Universitatea "Politehnica" din București, Inginerie Electrică, 3-4 Decembrie SNET 2010.

http://snet.elth.pub.ro/snet2010/index.php?action=program

[11] Iulian Ursac, Catalin Brinzei "Sintetizor de frecventa cu oscilator comandat digital", Universitatea "Politehnica" din București, Inginerie Electrică, SNET 2009.

http://snet.elth.pub.ro/snet2009/index.php?action=program

[12] Catalin Brinzei, Iulian Ursac "Power mixer for conversion from low to high frequency CMOS", Universitatea "Politehnica" din București, Inginerie Electrică, SNET 2009.

http://snet.elth.pub.ro/snet2009/index.php?action=program

[13] Catalin Brinzei, Iulian URSAC "Ring Oscillator design", Tutorial, Universitatea "Politehnica" București, Inginerie Electrică, 14 Iulie 2010.

## **BIBLIOGRAPHY**

- [1] R. Jacob Baker "CMOS CIRCUIT DESIGN, LAYOUT, AND SIMULATION THIRD EDITION", Copyright © 2010 by the Institute of Electrical and Electronics Engineers, ©John Wiley & Sons, Inc

- [2] Floyd M. Gardner "PHASE LOCK TECHNIQUES" third edition, Palo Alto-California, ©John-Wiley & Sons, Inc., New York, 2005

- [3] Roland E. Best, "PHASE LOCKED-LOOPS: THEORY, DESIGN, AND APPLICATIONS, Fourth Edition", ©Mc-Graw Hill, 1999

- [4] Paul R. Gray, Paul J. Hurst, Stephen H. Lewis, Robert G. Meyer "ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITS, Fourth Edition, ©John Wiley & Sons, 2001

- [5] C. D. Montchenbacher, J. A. Connelly "LOW NOISE ELECTRONIC SYSTEM DESIGN", © 1993, Published by John Wiley & Sons

- [6] Dean Banerjee "PLL PERFORMANCE, SIMULATION, AND DESIGN, fourth edition", © 2006, National Semiconductor

- [7] Behzad Razavi, "RF MICROELECTRONICS", © 1998, Prentice Hall PTR

- [8] Behzad Razavi, "DESIGN OF ANALOG CMOS INTEGRATED CIRCUITS", ©2001, McGraw-Hill Book Co

- [9] *Michael H. Perrott*, "SHORT COURSE ON PHASE-LOCKED LOOPS. ANALOG FREQUENCY SYNTHESIZERS", ©September 16, 2009, IEEE Circuit and System Society, San Diego, CA

- [10] Keliu Shu, Edgar Sánchez-Sinencio, "CMOS PLL SYNTHESIZERS: ANALYSIS AND DESIGN", ©2005 Springer Science + Business Media, Inc.

- [11] Randall W. Rhea, "OSCILLATOR DESIGN AND COMPUTER SIMULATION" Second Edition, © 1995 by Noble Publishing Corporation

- [12] Dean Benarjee, "PLL BUILDING BLOCKS", @National Semiconductor

- [13] Danny Abramovitch, "Phase-Locked Loops: A Control Centric Tutorial", Agilent Labs, May 8, 2002

- [14] Bortecene Terlemez, "OSCILLATION CONTROL IN CMOS PHASE-LOCKED LOOPS", Georgia Institute of Technology, PhD Thesis, November 2004

- [15] *Prof. dr. ing. Andrei Câmpeanu*, "CIRCUITE DE TELECOMUNICAȚII, Sintetizoare de frecvență PLL"

- [16] Shen-Iuan Liu, "ANALYSIS AND DESIGN OF PHASE-LOCKED LOOPS", Depart. of Electrical Engineering National Taiwan University, Email: <a href="mailto:lsi@cc.ee.ntu.edu.tw">lsi@cc.ee.ntu.edu.tw</a>

- [17] Deepika Ghai, Neelu Jain "ALL-DIGITAL PHASE LOCKED LOOP (ADPLL) -A REVIEW" International Journal of Electronics and Computer Science Engineering, ISSN- 2277-1956, pp. 94-101

- [18] P.E. Allen, "LECTURE 050 LINEAR PHASE LOCK LOOPS I- INTRODUCTION TO PHASE LOCK TECHNIQUES", 2003

- [19] Mark A. Wickert, "PHASE-LOCKED LOOPS WITH APPLICATIONS", ECE 5675/4675 Lecture Notes, Spring 2011

- [20] *Kaushik Mazumdar*, "PHASE DETECTOR/PHASE FREQUENCY DETECTOR" http://venividiwiki.ee.virginia.edu/mediawiki/images/2/2b/PFD\_PRESENTATION.ppt

- [21] *Vello MÄNNAMA, Toivo PAAVLE*, "LINEARITY RESTRICTIONS FOR A CLASS OF PHASE FREQUENCY DETECTORS", Proc. Estonian Acad. Sci. Eng., 2001, 7, 4, 331–346

- [22] *Howard Luong*, "DESIGN OF PHASE-FREQUENCY DETECTORS (PFD), CHARGE PUMPS, AND LOOP FILTERS", URL: http://www.ee.ust.hk/~eeluong

- [23] Woogeun Rhee, "DESIGN OF HIGH-PERFORMANCE CMOS CHARGE PUMPS IN PHASE-LOCKED LOOPS", 0-7803-5474-5/99/\$10.00(C)1999 IEEE, pp 545-548

- [24] Z. Yang, Y. Chen, S. Yang, PUI-IN Mak, RUI P. Martins, "A 10.6-MW 26.4-GHZ DUAL-LOOP TYPE-II PHASE-LOCKED LOOP USING DYNAMIC FREQUENCY DETECTOR AND PHASE DETECTOR" IEEE Access, VOLUME 8, 2020, pp 2222-2232, Digital Object Identifier 10.1109/ACCESS.2019.2962060

- [25] Jakob Vovnoboy, Run Levinger, Nadav Mazor, Danny Elad, "A Dual-Loop Synthesizer With Fast Frequency Modulation Ability for 77/79 GHz FMCW Automotive Radar Applications" IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 53, NO. 5, MAY 2018, pp. 1328-1337

- [26] P.E. Allen, "LECTURE 080 ALL DIGITAL PHASE LOCK LOOPS (ADPLL) (Reference [2])", ECE 6440 Frequency Synthesizers, 2003

- [27] G. Carpenter, A. Vize, "ADPLL: All Digital Phase-Locked Loop Circuits", EE295 Spring 2008

- [28] Wissam ALTABBAN, "CONCEPTION PORTABLE D'UNE ADPLL POUR DES APPLICATIONS TV", École Doctorale d'Informatique, Télécommunications et Électronique de Paris, PhD, Dec. 2009

- [29] Stefan Mendel, "SIGNAL PROCESSING IN PHASE-DOMAIN ALL-DIGITAL PHASE-LOCKED LOOPS", Signal Processing and Speech Communication Laboratory Graz University of Technology, Austria, PhD, Oct. 2009

- [30] Chun-Ming Hsu, "TECHNIQUES FOR HIGH-PERFORMANCE DIGITAL FREQUENCY SYNTHESIS AND PHASE CONTROL", © Massachusetts Institute of Technology, Msc., 2008

- [31] Scott Edward Meninger, "LOW PHASE NOISE, HIGH BANDWIDTH FREQUENCY SYNTHESIS TECHNIQUES", © Massachusetts Institute of Technology, PhD, 2005.

- [32] *Han-Woong Son*, "A FULLY INTEGRATED FRACTIONAL-N FREQUENCY SYNTHESIZER FOR WIRELESS COMMUNICATIONS", © Georgia Institute of Technology, PhD, April 2004

- [33] Matthew A. Z. Straayer, "Noise Shaping Techniques for Analog and Time to Digital Converters Using Voltage Controlled Oscillators", © MASSACHUSETTS INSTITUTE OF TECHNOLOGY, PhD, June 2008

- [34] *Dennis Fischette*, "FIRST TIME, EVERY TIME PRACTICAL TIPS FOR PHASE-LOCKED LOOP DESIGN", Website: http://www.delroy.com

- [35] *Michael H. Perrott*, "SHORT COURSE ON PHASE-LOCKED LOOPS. DIGITAL FREQUENCY SYNTHESIZERS", IEEE Circuit and System Society, San Diego, CA, September 16, 2009

- [36] Liangge Xu, Jukka-Pekka Pöyhtäri, Saska Lindfors, "ALL DIGITAL PLL FOR RF TRANSMITTER", CROPS Workshop, Trondheim 19.-20. 9. 2006

- [37] *Danny Abramovitch*, "PHASE-LOCKED LOOPS: A CONTROL CENTRIC TUTORIAL", © Agilent Labs, May 2002, http://www.labs.agilent.com/personal/Danny Abramovitch/pubs/

- [38] Stephan Henzler, "A TUTORIAL ON ROBUST HIGH-RESOLUTION TIME-TO-DIGITAL CONVERTERS" Technische Universität München, 2011

- [39] Chen Yao, "TIME TO DIGITAL CONVERTER USED IN ALL DIGITAL PLL", Master of Science Thesis, Stockholm, 08, 2011

- [40] Stephan Henzler, "TIME TO DIGITAL CONVERTERS", ©Springer Science+Business Media B.V. 2010

- [41] *Jussi Ryynänen, Saska Lindfors, Kari Stadius, and Kari A.I. Halonen,* Integrated Circuits for Multi-Band Multi-Mode Receivers, IEEE Circuits and Systems Magazine, Second quarter 2006

- [42] *David Su* (Qualcomm Atheros, San Jose, California), Designing CMOS Wireless System-on-a-chip-analog/RF perspective, Japan, Nov 2011

- [43] *Jeffrey M. Gilbert, Chinh H. Doan, Sohrab Emami, C. Bernard Shung, A* 4 Gbps Wireless True Uncompressed 1080p-Capable HD A/V Transceiver Using 60 GHz, SiBEAM, Inc.2007

- [44] Yi-Hung Weiy, Quan Lengy, Song Hany, Aloysius K. Moky, Wenlong Zhangz, Masayoshi Tomizukaz, "RT-WiFi: Real-Time High-Speed Communication Protocol for Wireless Cyber-Physical Control Applications", Department of Computer Science, The University of Texas at Austin, Department of Mechanical Engineering, University of California, Berkeley

- [45] *Ştefan Gabriel Şoriga*," ITS-G5 and Mobile WIMAX Performance in vehicle-to-infrastructure communications", University POLITEHNICA of Bucharest, U.P.B. Sci. Bull., Series C, Vol. 74, Iss. 2, 2012

- [46] Muhibbul Muktadir Tanim, "WiMAX & Wi-Fi", IT Infrastructure & Operations QUBEE, April 2012

- [47] J. Song, S. Han, A. K. Mok, D. Chen, M. Lucas, M. Nixon, and W. Pratt, "WirelessHART: Applying wireless technology in real-time industrial process control," in IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS), 2008, pp. 377–386.

- [48] W. Zhang, X. Zhu, S. Han, N. Byl, A. K. Mok, and M. Tomizuka, "Design of a network-based mobile gait rehabilitation system," in IEEE International Conference on Robotics and Biomimetics (ROBIO), 2012, pp. 1773–1778.

- [49] B. Li, Z. Sunk. Mechitov, G. Hackmann, C. Lu, S. J. Dyke, G. Agha, and B. F. Spencer, "Realistic case studies of wireless structural control," in International Conference on Cyber-Physical Systems (ICCPS), 2013.

- [50] S. Han, A. K. Mok, J. Meng, Y.-H. Wei, P.-C. Huang, Q. Leng, X. Zhu, L. Sentis, K. S. Kim, and R. Miikkulainen, "Architecture of a cyberphysical avatar," in International Conference on Cyber-Physical Systems (ICCPS), 2013.

- [51] *Bo Li*, "Wireless Cyber-Physical Simulator and Case Studies on Structural Control", Master thesis, Washington University, Saint Louis, Missouri, August 2013

- [52] IEEE P802.11pTM/D7.0, IEEE Draft Standard for Information Technology Telecommunications and Information exchange between systems, Local and metropolitan area networks, Specific requirements, Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) specifications, Amendment 7: Wireless Access in Vehicular Environments, May 2009

- [53] IEEE Std. 802.16e 2005, IEEE Standards for Local and metropolitan area networks, Part 16: Air Interface for Fixed and Mobile BWA Systems, Amendment 2: Physical and Medium Access Control Layers for Combined Fixed and Mobile Operation in Licensed Bands and Corrigendum 1, 2005

- [54] SaiShankar N, Debashis Dash, Hassan El Madi, and Guru Gopalakrishnan, "WiGig and IEEE 802.11ad For Multi-Gigabyte-Per-Second WPAN and WLAN", Tensorcom Inc., 5900 Pasteur Court, Carlsbad, CA 92008

- [55] LitePoint, A Teradyne Company "IEEE 802.11ac: What Does it Mean for Test?" 2013

- [56] Sung Tae Moon, Ari Yakov Valero-Lopez, Edgar Sanchez-Sinencio, FULLY INTEGRATED FREQUENCY SYNTHESIZERS: A TUTORIAL, International Journal of High Speed Electronics and Systems, World Scientific Publishing Company

- [57] https://commons.wikimedia.org/wiki/File:2.4\_GHz\_Wi-Fi\_channels\_(802.11b,g\_WLAN).svg

- [58] Robert Bogdan Staszewski "State-of-the-Art and Future Directions of High-Performance All-Digital Frequency Synthesis in Nanometer CMOS", Fellow, IEEE, IEEE Transaction om circuits and systems, VOL. 58, NO. 7, July 2011, Pages: 1497-1510

- [59] *Robert Bogdan Staszewski and Poras T. Balsara*, "All-Digital PLL With Ultra Fast Settling ",IEEE Transaction om circuits and systems, VOL. 54, NO. 2, February 2007, Pages181-185

- [60] Kurt M. Ware, Hae-Seung Lee and Charles G. Sodini, "A 200-MHz CMOS Phase-Locked Loop with Dual Phase Detectors A 200-MHz CMOS Phase-Locked Loop with Dual Phase Detectors", IEEE Journal of solid-state circuirs, Vol. 24, No. 6, December 1989

- [61] *Tae Hun Kim and Beomsup Kim*, "Dual-loop Digital PLL Design for Adaptive Clock Recovery", IEEE pp. 347-352, 1998

- [62] Shigeki OBOTE, Yasuaki SUMl, Kouichi SYOUBUT, Yutaka FUKUI and Yoshio ITOH, "DUAL LOOP DSP-PLL WITH WIDE FREQUENCY ACQUISITION RANGE AND FAST FREQUENCY ACQUISITION", IEEE, pp. IV-393÷ IV-396, 1998

- [63] Yi-Cheng Chang and Edwin W. Greeneich, "MONOLITHIC PHASE-LOCKED LOOP CIRCUITS WITH COARSE-STEERING ACQUISITION AID", IEEE, pp. 283 -286, 1999

- [64] Frank Herzel1, Sabbir A. Osmany, Klaus Schmalz, Wolfgang Winkler, J. Christoph Scheytt, Thomas Podrebersek, Rüdiger Follmann, and Heinz-Volker Heyer, "AN INTEGRATED 18 GHZ FRACTIONAL-N PLL IN SIGE BICMOS TECHNOLOGY FOR SATELLITE COMMUNICATIONS", IEEE Radio Frequency Integrated Circuits Symposium, pp. 329-332, 2009

- [65] *Michael H. Perrott*, Digital Frequency Synthesizers, Short Course On Phase-Locked Loops, IEEE Circuit and System Society, San Diego, CA, September 16, 2009

- [66] *Ioannis L. Syllaios, Robert Bogdan Staszewski, and Poras T. Balsara,* "Time-Domain Modeling of an RF All-Digital PLL", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 55, NO. 6, pp. 601-605, JUNE 2008

- [67] Congyin Shi, Chuan Wang, Le Ye, Huailin Liao, "-99DBC/HZ@10KHZ 1MHZ-STEP DUAL-LOOP INTEGER-N PLL WITH ANTI-MISLOCKING FREQUENCY CALIBRATION FOR GLOBAL NAVIGATION SATELLITE SYSTEM RECEIVER", IEEE, pp. 1876-1879, 2011

- [68] Bodhisatwa Sadhu, Mark A. Ferriss, Jean-Olivier Plouchart, Arun S. Natarajan, Alexander V. Rylyakov, Alberto Valdes-Garcia, Benjamin D. Parker, Scott Reynolds, Aydin Babakhani, Soner Yaldiz, Larry Pileggi, Ramesh Harjani, Jose Tierno and Daniel Friedman," A 21.8–27.5GHz PLL in 32nm SOI Using Gm Linearization to Achieve –130dBc/Hz Phase Noise at 10MHz Offset from a 22GHz Carrier", IEEE Radio Frequency Integrated Circuits Symposium, pp.75-78, 2012

- [69] Mark Ferriss, Alexander Rylyakov, José A. Tierno, Herschel Ainspan, Daniel J. Friedman "A 28 GHz Hybrid PLL in 32 nm SOI CMOS", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 49, NO. 4, APRIL 2014, pp. 1027-1035

- [70] Z. Zang, G. Zhu, C.P. Yue, HKUST- Qualcomm Lab "A 0.25-0.4V, Sub-0.11mW/GHz, 0.15-1.6GHz PLL Using an Offset Dual-Path Loop Architecture with Dynamic Charge Pumps" 2019 Symposium on VLSI Circuit Digest of Technical Papers

- [71] Andrea Baschirotto; Kofi A A Makinwa; Pieter Harpe: Frequency references, power management for SoC, and smart wireless interfaces: Advances in analog circuit design 2013. Springer, 2014

- [72] Kristofer S.J. Pister Berkeley, Sensor and Actuator: Introduction to MEMS Design and Fabrication Center. UC Berkeley

- [73] Emmanuel Onyema, Design and CMOS Technology Optimization of a Low Power MEMS Pierce Oscillator, Politecnico di Torino, Turin, Italy, 2012

- [74] Gabriel Iulian STROE, Modelarea dispozitivelor pasive de radiofrecvență, teza de doctorat, Universitatea Politehnica Bucuresti, 2012, conducator de doctorat, prof. Dr. Ing. Florin Constantinescu

- [75] Verdu Tirado, Jordi: Bulk AcousticWave Resonators and their Application to Microwave Devices. 2010

- [76] Stéphane Razafimandimby, ACCORD EN FRÉQUENCE DE RÉSONATEURS BAW APPLIQUÉ AU FILTRAGE ET À LA SYNTHÈSE DE FRÉQUENCE RF, Thèse docteur, l'Université des Sciences et Technologies de Lille 2007

- [77] Florin CONSTANTINESCU1, Alexandru Gabriel GHEORGHE1, Miruna NITESCU1, Aurelian FLOREA1, Olivier LLOPIS2, Petrica TARAS1, Parameter Identification for Nonlinear Circuit Models of Power BAW Resonators, Advances in Electrical and Computer Engineering Volume 11, Number 1, 2011

- [78] M. Maricaru, F. I. Hantila, F. Constantinescu, A. Stanciulescu, A. Buleandra, FEM SOLUTION OF THE COUPLED ELECTROMECHANICAL FIELD PROBLEM IN POWER BAW RESONATORS, POLITEHNICA UNIVERSITY BUCHAREST, MOBILIS 2006

- [79] Andreia Cathelin (1), Stéphane Razafimandimby (1), Andreas Kaiser (2) (1) STMicroelectronics, BAW-IC CO-INTEGRATION TUNABLE FILTERS AT GHz FREQUENCIES, France IEMN ISEN, Lille, France

- [80] Reza Abdolvand 1, Behraad Bahreyni 2, \*, Joshua E. -Y. Lee 3 and Frederic Nabki 4, Micromachined Resonators: A Review, Micromachines 2016, 7, 160; doi:10.3390/mi7090160

- [81] Spectrum Software "Creating Eye Diagrams" https://www.spectrum-soft.com/news/fall2002/eye.shtm

- [82] Leijun Xu, Chaoran Wang, LEIJUN X, A Novel Capacitor Bank for Linearized and Wide-band VCO, Wseas Tranzactions on Circuits and Systems, E-ISSN: 2224-266X, Volume 16, 2017

- [83] Kambiz Hadipour, Andrea Ghilioni, Junlei Zhao, and Andrea Mazzanti, A Wide Tuning Range mm-Wave LC VCO, International Journal of Electronics and Electrical Engineering Vol. 2, No. 1, March, 2014

- [84] Meng-Ting Hsu, Chien-Ta Chiu and Shiao-Hui Chen, Implementation of Low Phase Noise Wide-Band VCO with Digital Switching Capacitors, www.intechopen.com

- [85] Fan Xiangning, Zeng Jun, Li Bin, Zhu Weiwei, Chen Xiaoguang, A Fully Integrated Double Frequency Wide Tuning Range Differential CMOS LC VCO for 2.4GHz IEEE802.15.4/ZigBee, 978-1-4244-3709-2/10 ©2010 IEEE

- [86] Andreia Cathelin Nitescu-Henry, ADVANCED CIRCUITS AND SYSTEMS FOR RF, MMW AND THZ WIRELESS COMMUNICATIONS HDR THESIS, May, 2013

- [87] Fan He, Raymond Ribas, Cyril Lahuec, Michel Jézéquel, DISCUSSION ON THE GENERAL OSCILLATION STARTUP CONDITION AND THE BARKHAUSEN CRITERION, November 2008 Springer Science+Business Media, LLC 2008

- [88] Lindberg, E. (Author). (2012). The Barkhausen Criterion. Sound/Visual production

- [89] Zheng Wang, Huseyin S. Savci, Numan S. Dogan, 1-V Ultra-Low-Power CMOS LC VCO for UHF Quadrature Signal Generation, IEEE 2006, 4022-4025

- [90] Floyd M.Gardner, PHASELOCK TECHNIQUES-Third Edition, Published by John Wiley & Sons, Inc., Hoboken, New Jersey, 2005

- [91] Randall W. Rhea, Oscillator Design and Computer Simulation-Second Edition, 1995, ISBN 1-8849-32-30-4

- [92] R.L. Kubena, D.J. Kirby, Yook-Kong Yong, D.T. Chang, F.P. Stratton, H.D. Nguyen, R.J. Joyce, R. Perahia, H.P. Moyer, & R.G. Nagele, UHF Quartz MEMS Oscillators for Dynamics-Based System Enhancements, 2013 IEEE, Joint UFFC, EFTF and PFM Symposium, pp. 1-8,

- [93] Janak H. Patel, CMOS Process Variations: A Critical Operation Point Hypothesis, Computer Systems Colloquium (EE380)Stanford University, April 2, 2008

- [94] Jack Browne, What are the Filtering Differences Between SAWs and BAWs?, Feb. 2016 MICROWAVES & RF

- [95] Steven Mahon, Robert Aigner, Bulk Acoustic Wave Devices Why, How, and Where They are Going, CS MANTECH Conference, May 14-17, 2007, Austin, Texas, USA, pp. 15-18

- [96] Benes E., Groschl M., Seifert F., Pohl A., Comparison between BAW and SAW sensor principles, IEEE Trans Ultrason Ferroelectr Freq Control. 1998;45(5):1314-30. doi: 10.1109/58.726458.

- [97] Larry Miller, RF Filter Technologies For Dummies, Qorvo Special Edition, 2015 by John Wiley & Sons, Inc, Hoboken, New Jersey

- [98] Behzad Razavi, RF MICROELECtrONICS, 1998 Simon & Schuster Company, Prentice-Hall, Inc.

- [99] Dean Banerjee, PLL Performance, Simulation, and Design, 2003, Third Edition

- [100] Behzad Razavi, DESIGN OF ANALOG CMOS INTEGRATED CIRCUITS, 2001, McGRAW-Hill International Edition

- [101] Paul R. Gray, Paul J. Hurst, Stephen H. Lewis, Robert G. Meyer, ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITS, 2001 by John Wiley & Sons, Inc.

- [102] G. Bertotti, A. Laifi, E. Di Gioia, M. Masoumi, N. Dodel, E. F. Scarselli, R. Thewes, An 8 bit current steering DAC for offset compensation purposes in sensor arrays, 2012, Published by Copernicus Publications on behalf of the URSI Landesausschuss in der Bundesrepublik Deutschland e.V.

- [103] Tegze P. Haraszti, CMOS MEMORY CIRCUITS, 2002 Kluwer Academic Publishers

- [104] Tony R. Kuphaldt, Lessons In Electric Circuits, Volume IV -Digital, 2002 Design Science License, http://www.ibiblio.org/obp

- [105] Martin Schwerdtfeger, SPI Serial Peripheral Interface, 06/2000, mct.net: SPI Serial Peripheral Interface

- [106] Roubik Gregorian, INTRODUCTION TO CMOS OP-AMPS AND COMPARATORS

- [107] Walt Jung with the technical staff of Analog Devices, Op Amp Applications Handbook, 2005 by Analog Devices, Inc.

- [108] Rudy van de Plassche, CMOS INTEGRATED ANALOG-TO-DIGITAL AND DIGITAL-TO-ANALOG CONVERTERS 2nd Edition, 2003 Kluwer Academic Publishers, Boston

- [109] C.D. Motchenbacher, J.A. Connely, LOW-NOISE ELECTRONIC SYSTEM DEDIGN, 1993 by John Wiley & Sons, Inc.

- [110] Sung Tae Moon, Ari Yakov Valero-L´opez, Edgar S´anchez-Sinencio, FULLY INTEGRATED FREQUENCY SYNTHESIZERS:A TUTORIAL, International Journal of High Speed Electronics and Systems, World Scientific Publishing Company

- [111] Shailesh Rai, Ying Su, Wei Pang, Richard Ruby, Brian Otis, A Digitally Compensated 1.5 GHz CMOS/FBAR Frequency Reference, IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control, vol. 57, no. 3, March 2010 pp.552-561

- [112] Matteo Rinaldi, Chengjie Zuo, Jan Van der Spiegel and Gianluca Piazza, Reconfigurable 4-Frequency CMOS Oscillator Based on AlN Contour-Mode MEMS Resonators, 2010 IEEE International Ultrasonics Symposium Proceedings, pp1494-1497

- [113] Joydeep Basu, Tarun Kanti Bhattacharyya, Microelectromechanical Resonators for Radio Frequency Communication Applications, Microsystem Technologies, Oct 2011, vol. 17(10–11), pp. 1557–1580

- [114] DERYA DIKBAS, THIN FILM PIEZOELECTRIC ON SUBSTRATE RESONATORS ELECTRICAL CHARACTERIZATION AND OSCILLATOR CIRCUIT DESIGN, Istanbul Yildiz Technical University, Istanbul, Turkey 2009

- [115] EMMANUEL ONYEMA, Design and CMOS Technology Optimization of a Low Power MEMS Pierce Oscillator, University of Illinois at Chicago, 2014

- [116] Tektronix "Fundamentals of Signal Integrity" https://www.mouser.com/pdfDocs/Tektronix\_Fundamentals\_of\_Signal\_Integrity.pdf

- [117] GABRIELE MANGANARO, Advanced Data Converters, 2012 United States of America by Cambridge University Press, New York

- [118] Dean Nicholson, HeeSoo Lee, Characterization and modeling of bond wires for high-frequency applications, Microwave Engineering Europe, September 2006

- [119] Xiaoning Qi, HIGH FREQUENCY CHARACTERIZATION AND MODELING OF ON-CHIP INTERCONNECTS AND RF IC WIRE BONDS, Dissertation, Stanford University, June, 2001

- [120] Nozad Karim, Amit P. Agrawal, PLASTIC PACKAGES' ELECTRICAL PERFORMANCE: REDUCED BOND WIRE DIAMETER

- [121] Zuo C., Sinha N., der Spiegel J. V., Piazza G., Multi-frequency Pierce oscillators based on piezoelectric AlN contour-mode MEMS resonators, Proceedings of the 2008 International Frequency Symposium, pp. 402-407.

- [122] R. Tabrizian, M. Pardo, and F. Ayazi, A 27 MHZ Temperature compensated MEMS oscillator with sub-ppm instability, IEEE Int. Conf. on MEMS, 2012, pp. 23-26.

- [123] Discera Corporation, "DSC1121 Datasheet." http://www.audentia-gestion.fr/Microchip/DSC1101\_DSC1121\_Datasheet.pdf

- [124] Kinget P., Integrated GHz Voltage Controlled Oscillators, Bell Labs Lucent Technologies Murray Hill.

- [125] Cottier D., Oscillator Compensation Guide, Texas Instruments Application Report SPRAB84A—June 2010.

- [126] Zeji Chen, Xiao Kan, Quan Yuan, Tianyun Wang, Jinling Yang & Fuhua Yang, "A Switchable High-PerformanceRF-MEMS Resonator with Flexible Frequency Generations", Natureresearch Journal, https://www.nature.com/articles/s41598-020-61744-2 (March 2020)

- [127] Jacopo Iannacci "RF-MEMS for high-performance and widely reconfigurable passive components A review with focus on future telecommunications, Internet of Things (IoT) and 5G applications", Journal of King Saud University Science, Volume 29, Issue 4, Pages 436-443, https://doi.org/10.1016/j.jksus.2017.06.011 (October 2017)

- [128] Allan R. "RF MEMS switches are primed for mass-market applications" http://mwrf.com/active-components/rf-mems-switches-are-primed-mass-market-applications (May 2013)

- [129] Nilchi, J. N., Liu, R. & Nguyen "C. T.-C. High Cx/Co 13nm-capacitive-gap transduced disk resonator". In 2017 IEEE 30th International Conference on Micro Electro Mechanical Systems (MEMS). 924–927, https://doi.org/10.1109/memsys.2017.7863560 (IEEE, 2017)

- [130] Pourkamali, S., Hao, Z. & Ayazi, F. VHF single crystal silicon capacitive elliptic bulk-mode disk resonators-part II: implementation and characterization. J. Microelectromech. Syst. 13, 1054–1062, https://doi.org/10.1109/jmems.2004.838383 (2004).

- [131] Piazza, G., Stephanou, P. J. & Pisano, A. P. "Piezoelectric aluminum nitride vibrating contour-mode MEMS resonators". J.Microelectromech. Syst. 15, 1406–1418, https://doi.org/10.1109/jmems.2006.886012 (2006).

- [132] Piazza, G., Stephanou, P. J. & Pisano, A. P. "Single-chip multiple-frequency ALN MEMS filters based on contour-mode piezoelectric resonators" J. Microelectromech. Syst. 16, 319–328, https://doi.org/10.1109/jmems.2006.889503 (2007).

- [133] Chengjie Zuo, Nipun Sinha, Jan Van der Spiegel, and Gianluca Piazza, "Multi-Frequency Pierce Oscillators Based On Piezoelectric AlN Contour-Mode MEMS Resonators", IEEE International Frequency Control Symposium, 402-407. (September 2008)

- [134] Rinaldi, M., Zuo, C., Van der Spiegel, J. & Piazza G. "Reconfigurable CMOS oscillator based on multifrequency AlN contour-mode MEMS resonators" IEEE Trans. Electron Devices. 58, 1281–1286, https://doi.org/10.1109/ted.2011.2104961 (2011).

- [135] Gong, S. & Piazza G. "Monolithic Multi-Frequency Wideband RF Filters Using Two-Port Laterally Vibrating Lithium Niobate MEMS Resonators" J. Microelectromech. Syst. 23, 1188–1197, https://doi.org/10.1109/jmems.2014.2308259 (2014).