### Power Efficient RF/mm-wave Oscillators and Power Amplifiers for Wireless Applications

Babaie, Masoud

10.4233/uuid:456a2f0e-529d-4bd8-91e0-4dba4f623f0f

**Publication date**

**Document Version** Final published version

Citation (APA)

Babaie, M. (2016). Power Efficient RF/mm-wave Oscillators and Power Amplifiers for Wireless Applications. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:456a2f0e-529d-4bd8-

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Power Efficient RF/mm-wave Oscillators and Power Amplifiers for Wireless Applications

Masoud Babaie

## Power Efficient RF/mm-wave Oscillators and Power Amplifiers for Wireless Applications

### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben; voorzitter van het College voor Promoties, in het openbaar te verdedigen op

donderdag 9 juni 2016 om 12.30 uur

door

Masoud BABAIE

Master of Science in Electrical Engineering, Sharif University of Technology, Tehran, Iran geboren te Teheran, Iran This dissertation has been approved by the promotor: Prof. dr. R. B. Staszewski

Composition of the doctoral committee: Rector Magnificus chairman

Prof. dr. R. B. Staszewski Delft University of Technology

Independent members:

Prof. dr. E. Charbon Delft University of Technology

Prof. dr. ir. B. Nauta University of Twente

Prof. dr. ir. P. Reynaert University of Leuven, Belgium

Prof. dr. ing. S. Heinen RWTH Aachen University, Germany Prof. dr. P. Wambacq Vrije Universiteit Brussel, Belgium

Dr. J. Craninckx IMEC, Leuven, Belgium

Prof. dr. ir. W. A. Serdijn Delft University of Technology, reserve member

Masoud Babaie,

Power Efficient RF/mm-wave Oscillators and Power Amplifiers for Wireless Applications, Ph.D. Thesis Delft University of Technology, with summary in Dutch.

Keywords: RF, mm-wave, transmitter, oscillator, class-F, phase noise, impulse sensitivity function, switched-mode power amplifier, class-E/F, transformer, Bluetooth Low Energy, low voltage, low power, all-digital phase-locked loop (ADPLL).

ISBN 978-94-6233-305-5

Copyright © 2016 by Masoud Babaie Cover photo was taken from www.hdwpics.com.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written permission of the copyright owner.

Printed in the Netherlands.

To my lovely parents, Mahmoud and Shahin

To my lovely brothers, Saeed and Kasra

And last, but not least, to my lovely wife Mina and her respected family

"Insanity is doing the same thing over and over again and expecting different results."

Albert Einstein, 1879-1955

## Contents

| C | onter      | nts                                                                 | 1          |

|---|------------|---------------------------------------------------------------------|------------|

| 1 | Intr       | roduction                                                           | ]          |

|   | 1.1        | Technology Scaling                                                  | 3          |

|   |            | 1.1.1 Supply Voltage                                                | 3          |

|   |            | 1.1.2 Quality Factor of Passives                                    | 4          |

|   |            | 1.1.3 Noise of Active Devices                                       | 6          |

|   | 1.2        | Thesis Objectives                                                   | 6          |

|   | 1.3        | Thesis Outline                                                      | 7          |

|   | 1.4        | Original Contributions                                              | 8          |

| 2 | <b>A</b> ( | Class-F CMOS Oscillator                                             | 9          |

|   | 2.1        | Introduction                                                        | 9          |

|   | 2.2        | Evolution Towards Class-F Oscillator                                | 2          |

|   |            | 2.2.1 Realizing a Square-Wave across the LC Tank                    | 2          |

|   |            | 2.2.2 Proposed Tank                                                 | .4         |

|   |            | 2.2.3 Voltage Gain of the Tank                                      | . 7        |

|   |            | 2.2.4 Proposed Class-F Oscillator                                   | ç          |

|   | 2.3        | Class-F Phase Noise Performance                                     | 2          |

|   |            | 2.3.1 Quality Factor of Transformer-based Resonator                 | 22         |

|   |            | 2.3.2 Phase Noise Mechanism in Class-F Oscillator                   | 13         |

|   |            | 2.3.3 Class-F Operation Robustness                                  | 2 <u>C</u> |

|   | 2.4        | Experimental Results                                                | 2 <u>9</u> |

|   |            | 2.4.1 Implementation Details                                        | 2 <u>C</u> |

|   |            | 2.4.2 Measurement Results                                           | C          |

|   | 2.5        | Conclusion                                                          | 2          |

|   | 2.6        | Extension of class- $F_3$ operation to mm-wave frequency generation | 13         |

| 3 | An         | All-Digital PLL Based on Class-F DCO for 4G Phones 3                | 7          |

|   | 3.1        | Introduction                                                        | 37         |

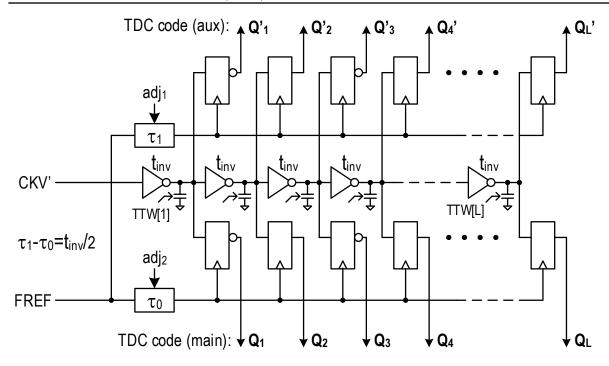

|   | 3.2        | Time-to-Digital Converter (TDC)                                     | 8          |

|   | 3.3        | ADPLL Architecture                                                  | F(         |

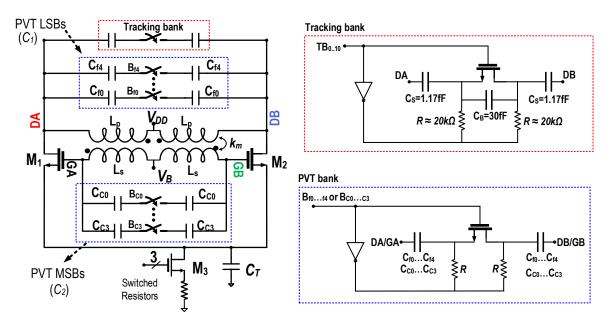

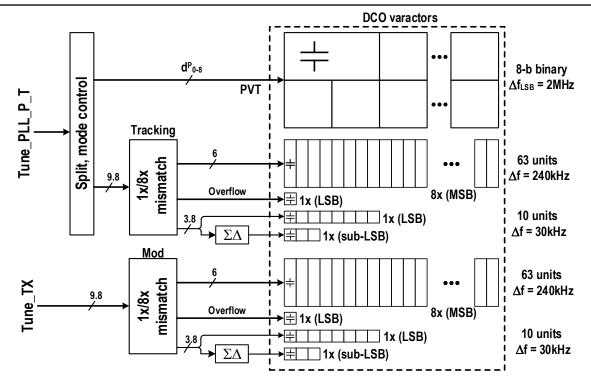

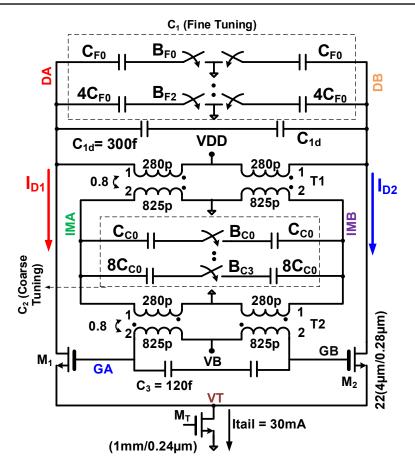

|   | 3.4        | Digitally Controlled Oscillator (DCO)                               | 2          |

ii Contents

|   | 3.5 | Measurement Results                                                            | 45  |  |  |  |  |

|---|-----|--------------------------------------------------------------------------------|-----|--|--|--|--|

|   | 3.6 | Conclusion                                                                     | 47  |  |  |  |  |

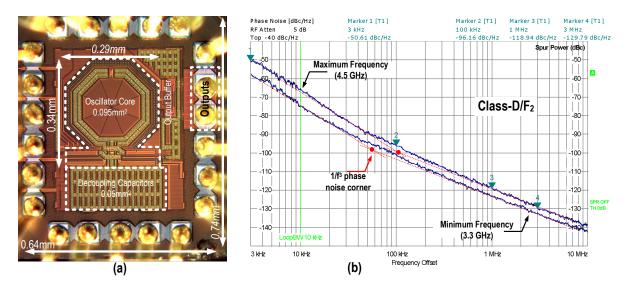

| 4 | An  | Ultra-Low Phase Noise Class- $F_2$ CMOS Oscillator with 191 dBc/Hz FoM         |     |  |  |  |  |

|   |     | Long-Term Reliability                                                          | 49  |  |  |  |  |

|   | 4.1 | Introduction                                                                   | 49  |  |  |  |  |

|   | 4.2 | Challenges in Ultra-Low Phase Noise Oscillators                                | 50  |  |  |  |  |

|   | 4.3 | Evolution Towards Class-F <sub>2</sub> Operation                               | 53  |  |  |  |  |

|   | 4.4 | Phase Noise Mechanism in Class-F $_2$ Oscillator                               | 59  |  |  |  |  |

|   | 4.5 | Experimental Results                                                           | 64  |  |  |  |  |

|   | 4.6 | Reliability of High-Swing RF Oscillators                                       | 68  |  |  |  |  |

|   | 4.7 | Conclusion                                                                     | 71  |  |  |  |  |

|   | 4.8 | Extension of class- $F_2$ operation for reducing flicker noise upconversion    | 72  |  |  |  |  |

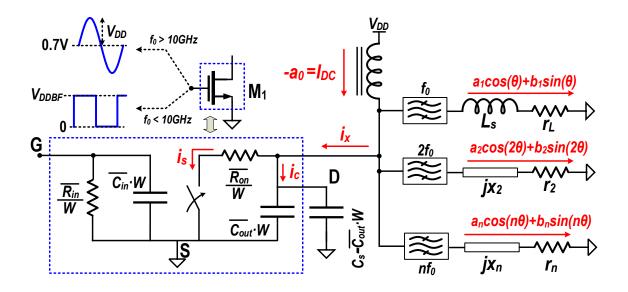

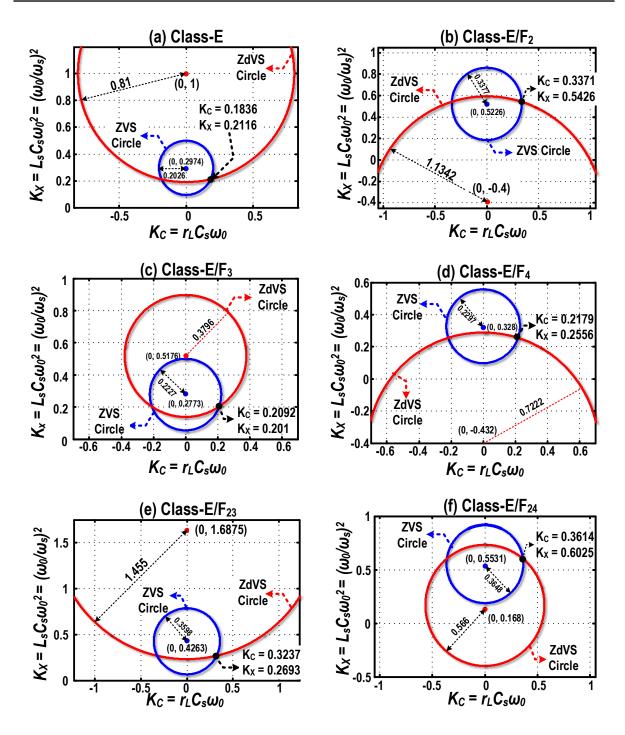

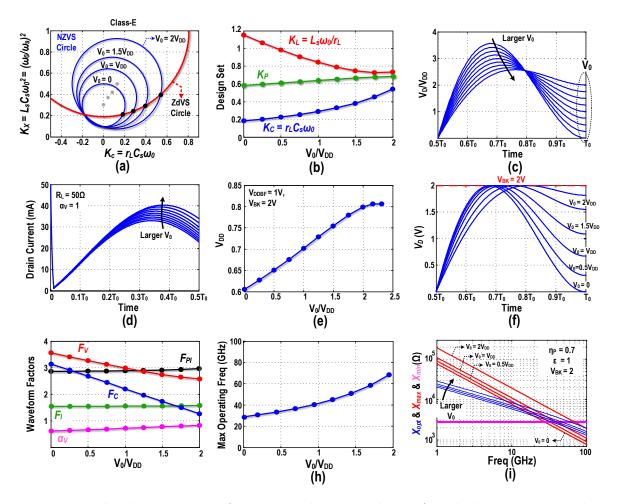

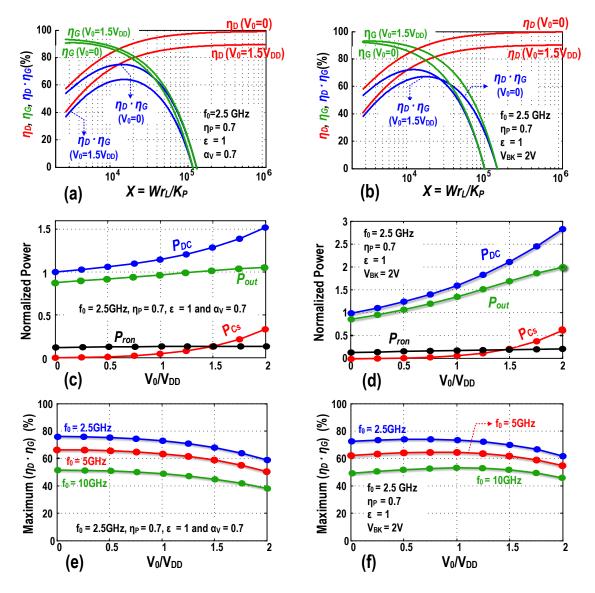

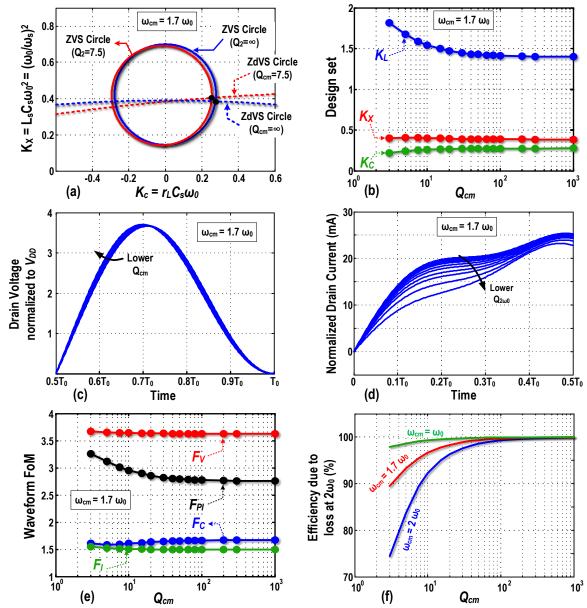

| 5 | Cor | mprehensive Analysis of Switch-mode PAs                                        | 77  |  |  |  |  |

|   | 5.1 | Predicting Switching Amplifier Waveforms                                       | 78  |  |  |  |  |

|   | 5.2 | Determining ZVS and ZdVS Tuning                                                | 81  |  |  |  |  |

|   | 5.3 | Waveform Figure of Merit                                                       | 82  |  |  |  |  |

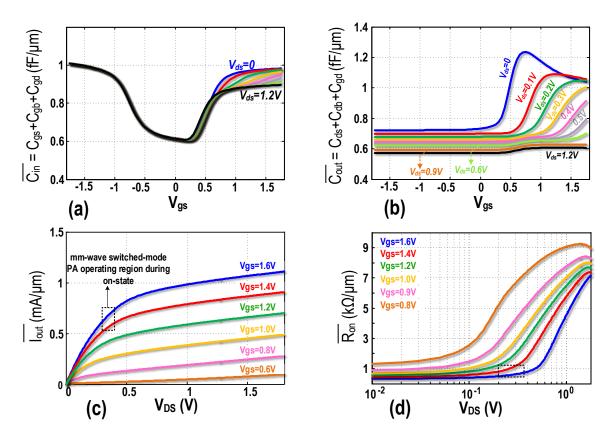

|   | 5.4 | Technology Dependent Parameters                                                |     |  |  |  |  |

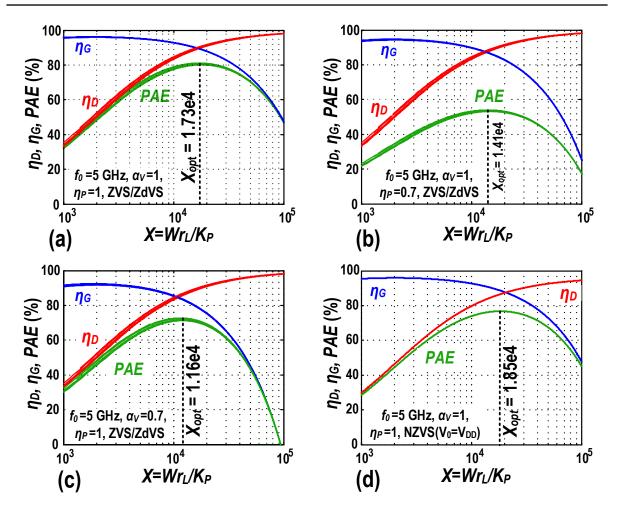

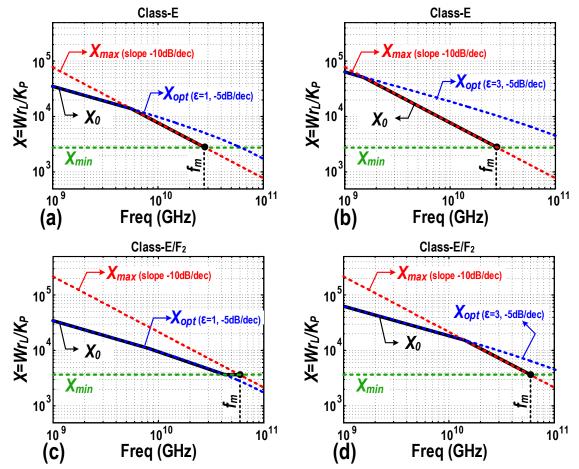

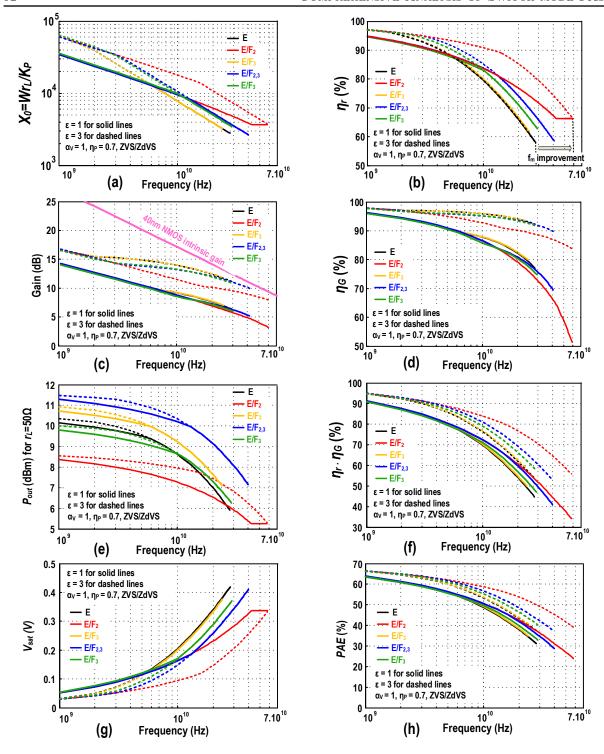

|   | 5.5 | Predicting Switching Amplifier Performance                                     |     |  |  |  |  |

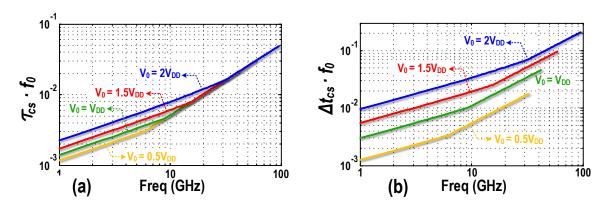

|   | 5.6 | Effects of Oxide Breakdown on PA Performance                                   |     |  |  |  |  |

|   | 5.7 | Single Device Versus Cascode Structure                                         | 97  |  |  |  |  |

|   | 5.8 | Benefits of Non-zero Voltage Switching                                         | 98  |  |  |  |  |

|   | 5.9 | Conclusion                                                                     | 103 |  |  |  |  |

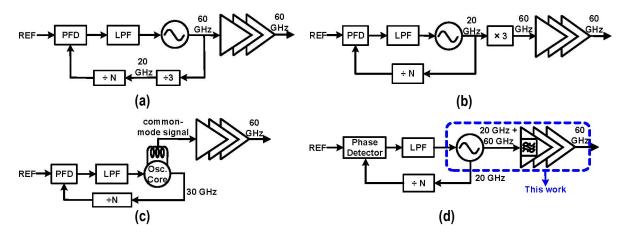

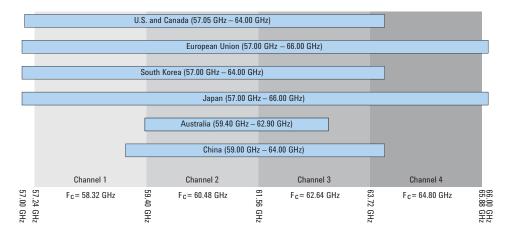

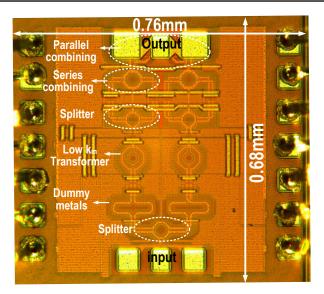

| 6 | A V | $oxed{	ext{Wideband 60GHz\ Class-E/F}_2 	ext{ Power Amplifier in 40nm\ CMOS}}$ | 105 |  |  |  |  |

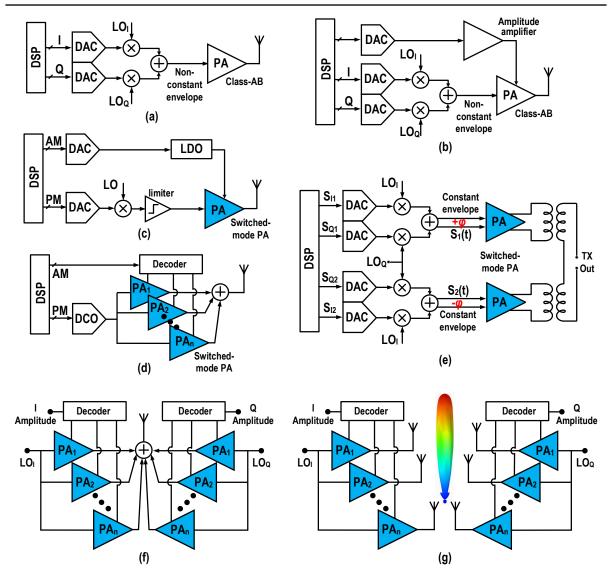

|   | 6.1 | Transmitter Architectures from mm-wave Viewpoint                               | 105 |  |  |  |  |

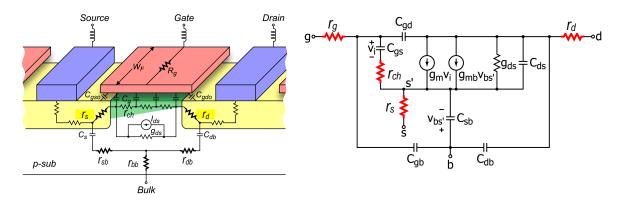

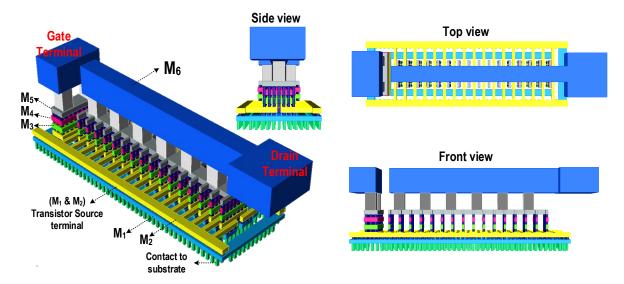

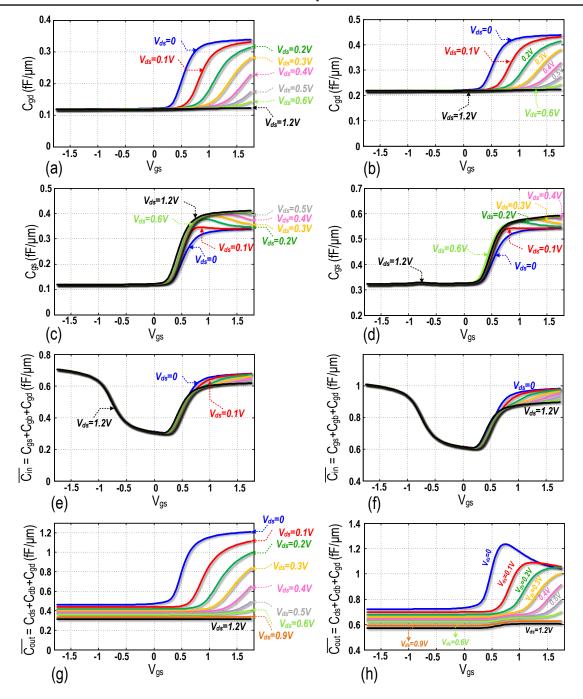

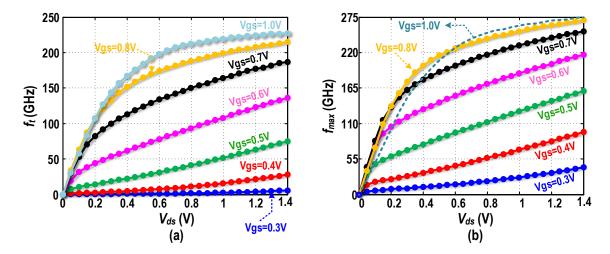

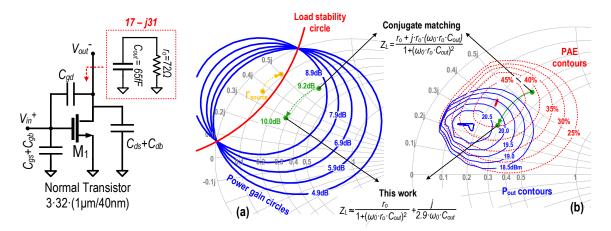

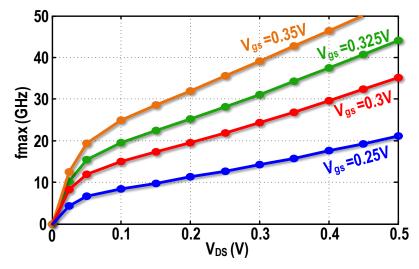

|   | 6.2 | Optimizing Active Devices at mm-wave Frequencies                               | 109 |  |  |  |  |

|   | 6.3 | Power Amplifier Design                                                         | 113 |  |  |  |  |

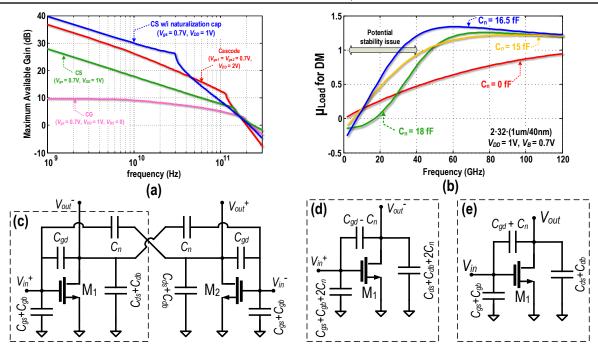

|   |     | 6.3.1 Amplifier Configuration                                                  | 114 |  |  |  |  |

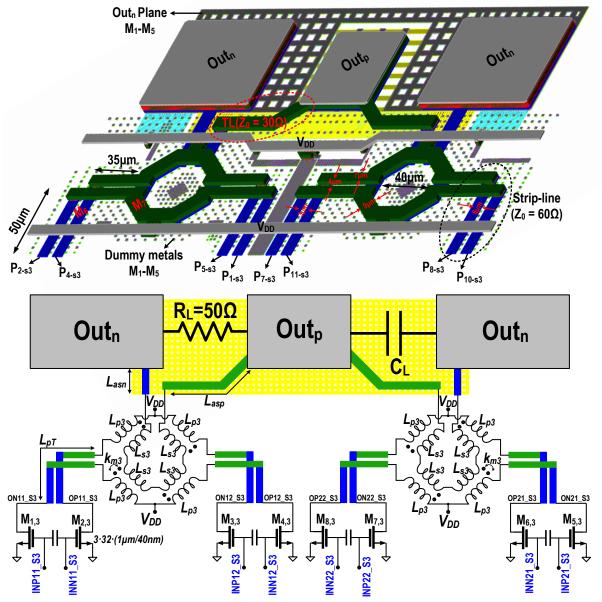

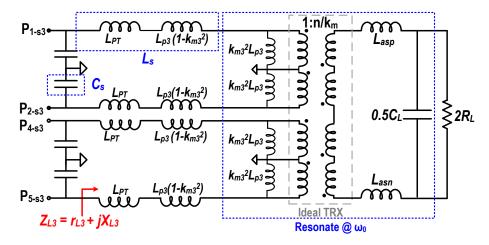

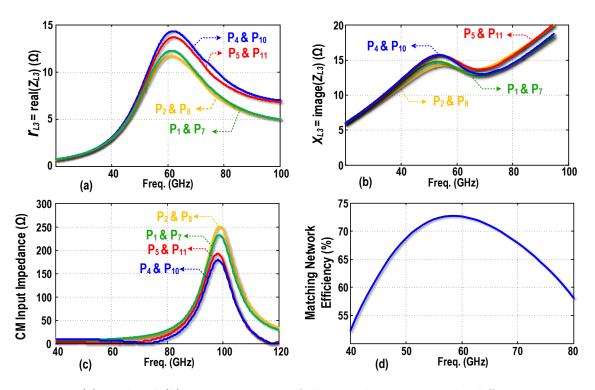

|   |     | 6.3.2 Output Matching Network                                                  | 116 |  |  |  |  |

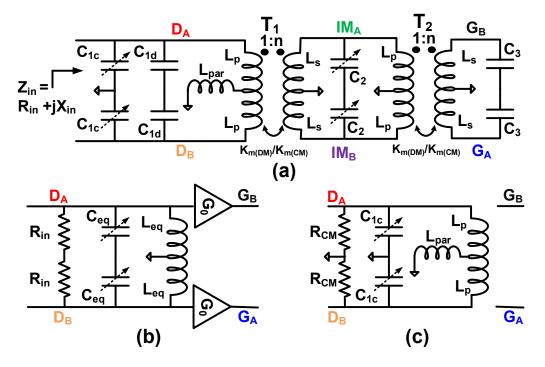

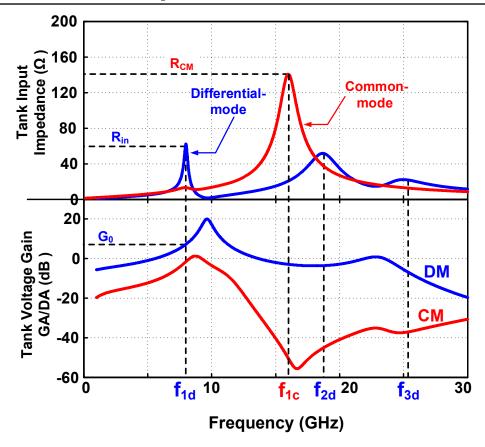

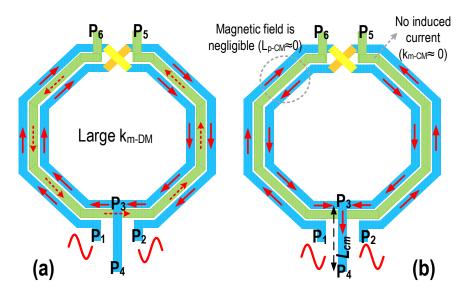

|   |     | 6.3.3 $$ Output Matching Network Behavior to DM and CM Input Signals $$        | 119 |  |  |  |  |

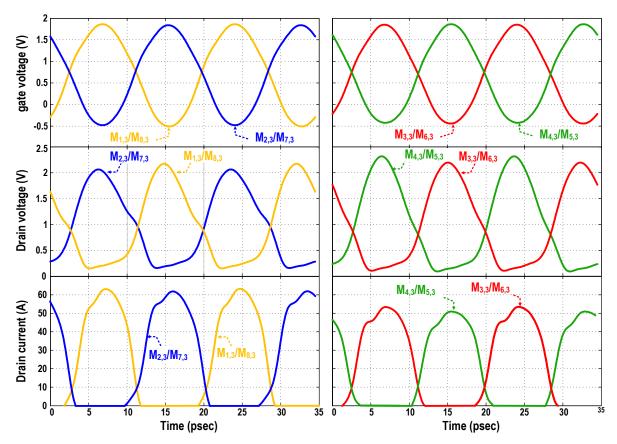

|   |     | 6.3.4 Extended Class-E/F <sub>2</sub> PA                                       | 122 |  |  |  |  |

|   |     | 6.3.5 Effects of CM Resistive Loss on PA's Performance                         | 124 |  |  |  |  |

|   |     | 6.3.6 Optimum Output Matching Network and Device Size                          | 124 |  |  |  |  |

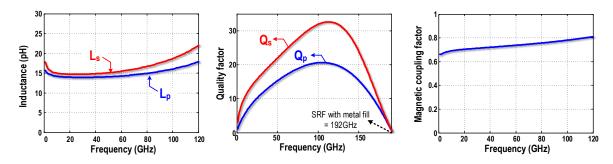

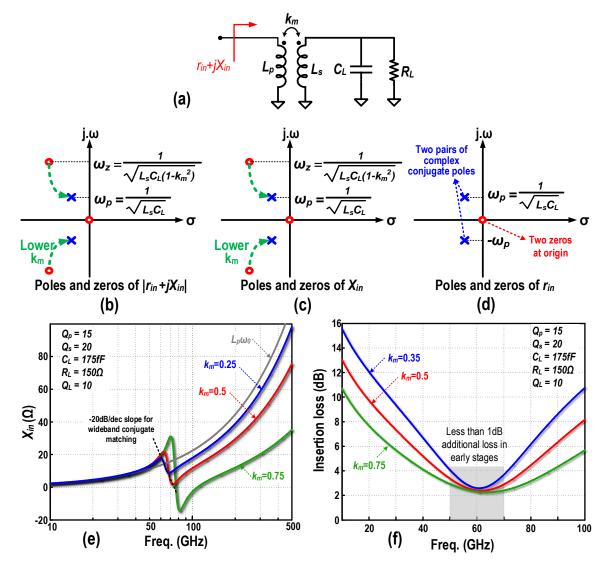

|   |     | 6.3.7 Low/Moderate Coupling-Factor Transformer for Wideband PAs                | 128 |  |  |  |  |

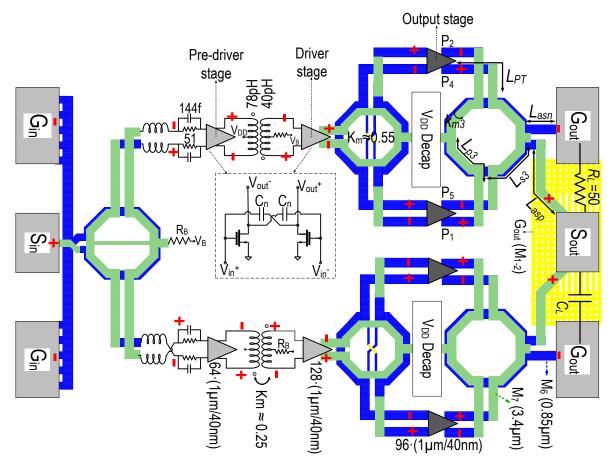

|   |     | 6.3.8 Driver Stage                                                             | 130 |  |  |  |  |

|   |     | 6.3.9 First Stage                                                              | 132 |  |  |  |  |

|   |     | 6.3.10 Effects of Dummy Metals on Transformer's Performance                    | 133 |  |  |  |  |

|   |     | 6.3.11 Power Amplifier Stability                                               | 134 |  |  |  |  |

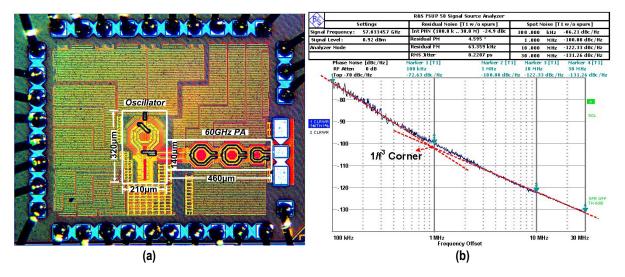

|   | 6.4 | Measurement Results                                                            |     |  |  |  |  |

|   | 6.5 | Conclusion                                                                     | 141 |  |  |  |  |

Contents

| 7             | Blu          | etooth-Low Energy Transmitter                                                   | 143  |

|---------------|--------------|---------------------------------------------------------------------------------|------|

|               | 7.1          | Introduction                                                                    | 143  |

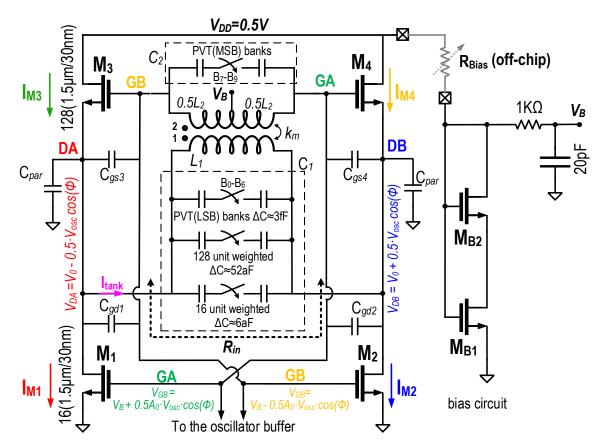

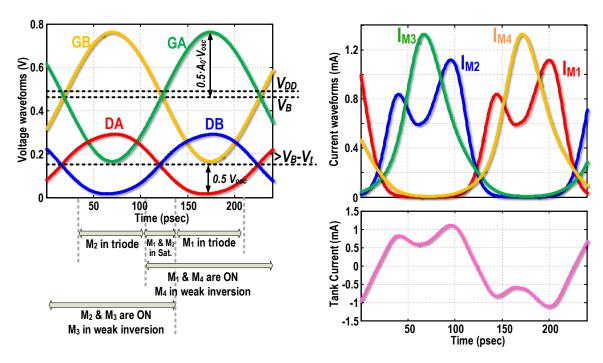

|               | 7.2          | Switching Current-Source DCO                                                    | 145  |

|               |              | 7.2.1 Oscillator Power Consumption Tradeoffs                                    | 146  |

|               |              | 7.2.2 Switching Current Source Oscillator                                       | 150  |

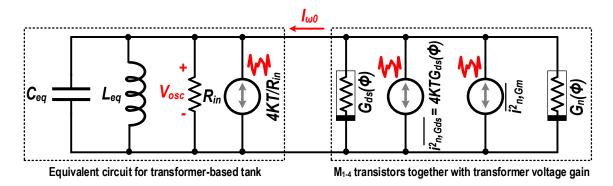

|               |              | 7.2.3 Thermal Noise Upconversion in The Proposed Oscillator                     | 153  |

|               |              | 7.2.4 1/f Noise Upconversion in The Proposed Oscillator                         | 156  |

|               |              | 7.2.5 Optimizing Transformer-based Tank                                         | 156  |

|               | 7.3          | $Class-E/F_2$ Switched-mode Power Amplifier                                     | 157  |

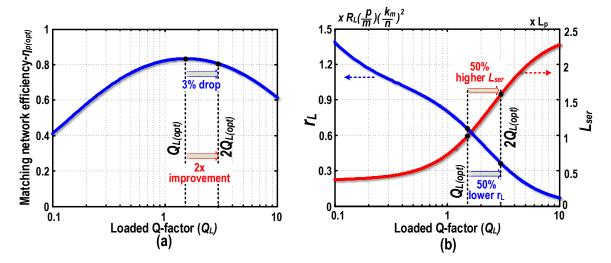

|               |              | 7.3.1 Efficiency and Selectivity Tradeoff in Transformer-based Matching Network | к158 |

|               |              | 7.3.2 Impedance Transformation                                                  |      |

|               |              | 7.3.3 Class-E/F <sub>2</sub> Operation                                          | 161  |

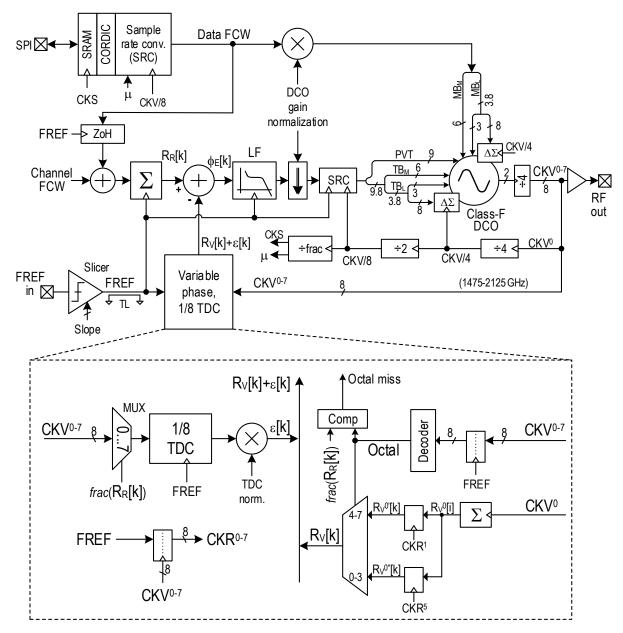

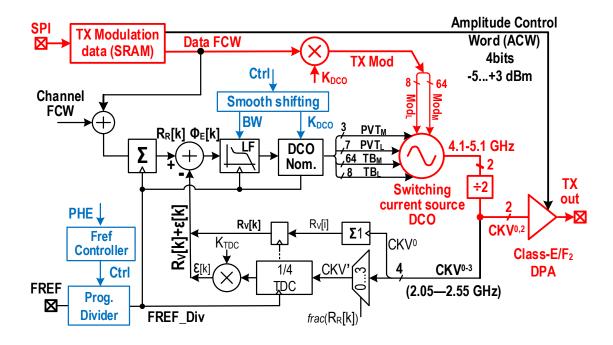

|               | 7.4          | All-Digital Phase-Locked Loop and Transmitter Architecture                      | 163  |

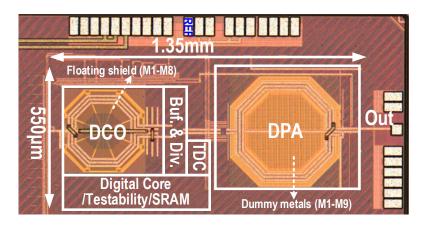

|               | 7.5          | Experimental Results                                                            |      |

|               | 7.6          | Conclusion                                                                      |      |

|               | 7.7          | Appendix A                                                                      | 169  |

|               | 7.8          | Appendix B                                                                      | 170  |

| 8             | Con          | nclusion                                                                        | 173  |

|               | 8.1          | The Thesis Outcome                                                              | 173  |

|               | 8.2          | Some Suggestions for Future Developments                                        | 174  |

| Bi            | bliog        | graphy                                                                          | 177  |

| $\mathbf{Li}$ | st of        | Publications                                                                    | 191  |

| Sι            | ımm          | ary                                                                             | 195  |

| Sa            | men          | vatting                                                                         | 197  |

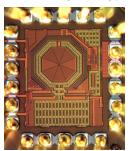

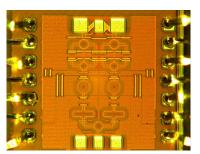

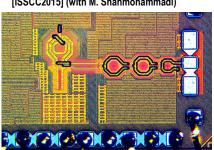

| $\mathbf{C}$  | hip N        | Aicrograph Gallery                                                              | 199  |

| Li            | ${ m st}$ of | Figures                                                                         | 200  |

| $\mathbf{Li}$ | ${ m st}$ of | Tables                                                                          | 209  |

| A             | cknov        | wledgments                                                                      | 211  |

| $\mathbf{A}$  | bout         | the Author                                                                      | 215  |

### CHAPTER

## 1

### Introduction

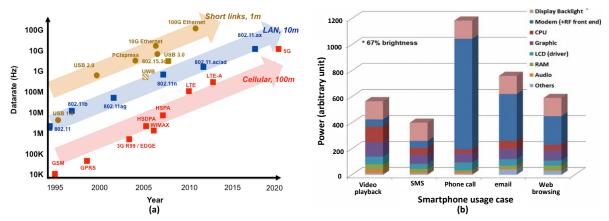

While mobile phones enjoy the largest production volume ever of any consumer electronics products, the demands they place on RF/mm-wave transceivers are particularly aggressive, especially on integration with digital processors, low area, low power consumption, while being robust against process-voltage-temperature (PVT) variations. Figure 1.1 (a) illustrates the evolution of data rates for wireless LAN, cellular, and wireline short links over time [1]. Interestingly, there is a constant  $\sim 10\times$  increase in bit rate every five years for both wireline and wireless links. Since mobile terminals inherently operate on batteries, their power budget is basically constant. Hence, an ever-decreasing power per bit is required to maintain the system lifetime. As shown in Fig. 1.1 (b), the RF front-end circuitry consumes significant power for typical use cases of mobile terminals such as voice call, web browsing and email [2]. Consequently, power efficiency of RF building blocks has become a major issue, especially when designing system-on-chips (SoC) for wireless communications.

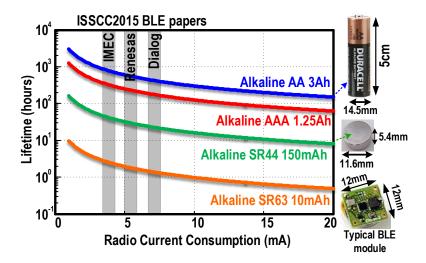

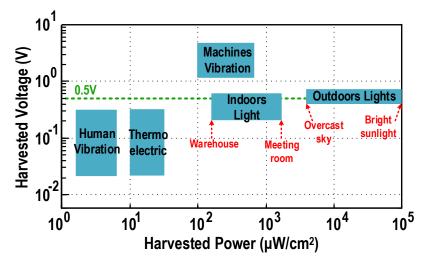

On the other hand, in the upcoming years, the wireless Internet-of-Things (IoT) will enable more objects to be sensed and controlled remotely, realizing more integration between the physical and digital worlds. According to the communications giant Cisco Systems [3], there are currently approximately 15 billion internet-connected objects (things) which is slated to reach 50 billion by 2020, just 2.7 percent of all the things that will be on the planet. However, the system lifetime still tends to be severely limited by its power consumption, available battery technology and efficiency of its energy harvester. Consequently, the key challenge of these wireless sensors is the ability to function at the lowest power possible while being robust to PVT variations. Similarly, the power consumption of RF building blocks should be reduced to satisfy the lifetime demands of IoT systems. Furthermore, RF circuitries such as oscillator and PLL should be able to turn on/off quickly to permit high energy-efficiency during intermittent operation.

It is well known that the power amplifier (PA) is the most power hungry building block of

2 Introduction

Figure 1.1: (a) evolution of data rates for wireless LAN, cellular, and wireline short links over time [1]; (b) power usage in a smartphone [2].

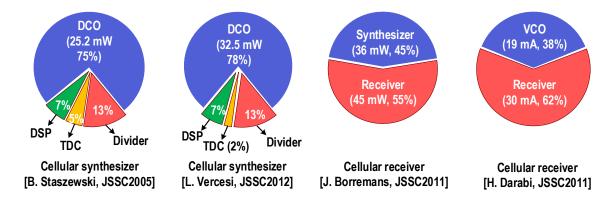

Figure 1.2: Contribution of RF oscillator to the power consumption of cellular frequency synthesizers and receivers.

any wireless radio and consequently any improvement on its power efficiency can significantly extend the battery lifetime of the entire radio. Furthermore, PAs need at least one matching network (including capacitors, inductors and transmission lines) in order to efficiently deliver power to the load. These passives usually occupy large surface on the chip thus making PA as the most area hungry and, consequently, most expensive block in any RF/mm-wave transceiver. This naturally leads to the conclusion that increasing the PA's power efficiency while reducing its size, can significantly improve the performance and cost of the entire wireless system.

The RF oscillator is the second most power hungry block of a wireless radio. As shown in Fig. 1.2, the RF oscillator consumes a disproportionate amounts of the power of a cellular frequency synthesizer [4,5] and burns more than 30% of the cellular receiver power [6,7]. Consequently, any power reduction in an RF oscillator will greatly benefit the overall power efficiency of the cellular transceiver. For IoT applications, the commercial perspective is now focusing on Bluetooth Low Energy (BLE). In the state-of-the-art BLE radios [8-10], the PLL power consumption is merely  $3-4\times$  lower than that of PA at the maximum BLE output power of 1 mW. However, the frequency synthesizer activity is much longer than that of a PA, making the PLL the most energy-hungry block in a BLE transceiver.

In this dissertation, the main goal is to innovate the RF/mm-wave oscillator and power amplifier structures that demonstrate better performance, lower cost, and higher power efficiency than traditional architectures.

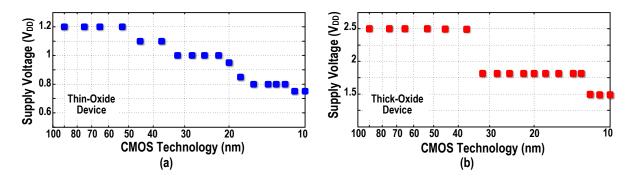

Figure 1.3: Nominal supply voltage versus CMOS technology node for (a) thin-oxide and (b) thick-oxide device.

### 1.1 Technology Scaling

The size, cost, and power consumption of digital circuits are reduced by technology scaling. However, the design of analog and RF circuits faces many difficulties using more advanced CMOS technologies. Consequently, in the semiconductor industry, there are two divergent trends for choosing a technology node for fabricating analog circuits. One trend is to implement analog circuits in older technology to exploit a higher voltage headroom. This approach is chiefly more in medical, automotive, and high-efficiency lighting applications [11]. Another trend is to implement analog and digital circuits together in the most advanced node such as a 16-nm FinFET. The approach is dictated by the market to achieve highest digital performance with lowest fabrication cost.

The vision for both wireless cellular communication and the Internet of Things keeps moving towards the second strategy [12]. For example, IMEC recently published the first integrated wireless sensor node in 40-nm CMOS including a microcontroller, digital baseband, power management, and BLE transceiver [8]. Furthermore, Intel and DMCE presented a SAW-less HSPA transceiver with on-chip integrated 3G power amplifiers in 65nm at ISSCC 2015 to enable real low-cost monolithic system integration [13]. Consequently, it is instructive to investigate the effects of technology scaling on the performance of an RF/mm-wave oscillator and power amplifiers.

### 1.1.1 Supply Voltage

To continue implementing increasingly complex functions while reducing the overall solution costs, scaling of CMOS transistors is inevitable. As circuits become denser, all of the physical dimensions of the transistors must be reduced correspondingly. The SiO<sub>2</sub> oxide-layer thickness reduction is accompanied by migrating to smaller supply voltages (see Fig. 1.3). This is to maintain the electric field strength across the oxide in order to prevent the device performance degradation due to the time dependent dielectric breakdown (TDDB) [14]. The supply voltage,  $V_{DD}$ , is reduced while RF and analog circuits must maintain their dynamic range, noise performance and output power. For example, the oscillator phase noise performance and power amplifier output power ( $P_{out}$ ) degrade by 6 dB/octave with the reduction of their supply voltage [15]. To compensate this phase noise penalty, the equivalent input parallel resistance of an LC tank should be proportionally decreased by reducing the tank's inductance. However, the

4 Introduction

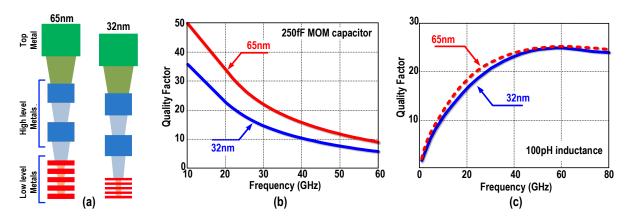

Figure 1.4: (a) Back-end-of-line (BEOL) metallization; quality factor of (b) a 250 fF capacitor, and (c) a 100 pH inductor in 65 nm and 32 nm CMOS technologies [16].

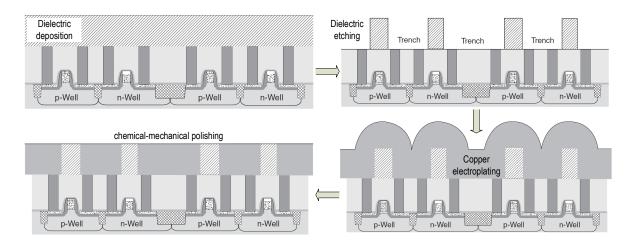

Figure 1.5: Damascene process steps [17].

resistance of the tank's interconnects will start dominating the resonator losses and, consequently, the effective Q-factor and oscillator power efficiency will dramatically drop. To compensate  $P_{out}$  penalty in the power amplifier, a smaller load must be seen by PA's transistors. Hence, the PA's matching network must provide a higher impedance transformation ratio. It leads to a larger insertion loss of the matching network and thus a lower efficiency of the PA.

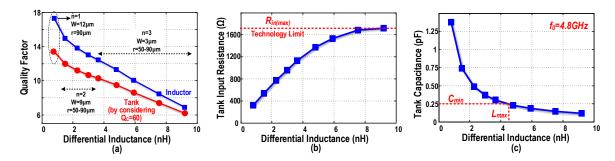

### 1.1.2 Quality Factor of Passives

Most RF/mm-wave CMOS oscillators and power amplifiers employ passive components such as integrated inductors, transformers, and capacitors to realize on-chip LC tanks and matching/biasing networks. Generally, top thick metal layers are used for the realization of inductive components while thinner lower-level metals are exploited in metal-oxide-metal (MoM) capacitors. Note that the  $0.18\,\mu\mathrm{m}$  node was the last generation of 8-inch wafer processes with aluminum metallization as almost all modern processes use copper metallization that improves the resistive loss and current handling capability of passive components. Consequently, the quality factor of passives was improved when RF products migrated from  $0.18\,\mu\mathrm{m}$  to  $0.13\,\mu\mathrm{m}$  technology.

By migrating to more advanced nano-scale CMOS technologies, however, the thickness of

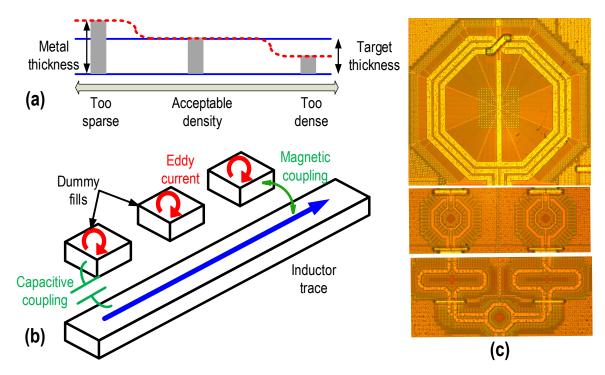

Figure 1.6: (a) Thickness variation by erosion in the CMP stage; (b) electromagnetic coupling between the wire and dummy fills; (c) inductor/transformer with lots of dummy metal fills.

lower level metals and interlayer dielectric layers reduce correspondingly as shown in Fig. 1.4 (a). As a consequence, the physical dimension of a given capacitance becomes smaller but with a worse quality factor (see Fig. 1.4 (b)). Fortunately, the thickness of top thick metal layers almost remains constant with scaling. However, the top-metal is closer to the lossy substrate. Hence, the capacitive parasitic, self-resonant frequency, and quality factor of inductor/transformer slightly degrade with scaling as shown in Fig. 1.4 (c).

As mentioned above, in most advanced CMOS technologies, copper is used for interconnections due to its low sheet resistance, high maximum current density, high thermal conductivity and resilience to electromigration failures. However, it is difficult to pattern copper using conventional etching techniques. Consequently, unlike traditional metallization of aluminum, copper metallization needs an additional damascene process as shown in Fig. 1.5 [17]. The inter-level dielectric is first deposited in the damascene process. Secondly, the dielectric is etched to define trenches where the metal lines will lie. Thirdly, copper is electroplated to fill the patterned oxide trenches. Finally, the surface is planarized and polished to remove surplus copper outside the desired metal lines using chemical-mechanical polishing (CMP). Unfortunately, CMP suffers from dishing and erosion phenomena. Since copper is much softer than the inter-level dielectric, areas with higher metal density are polished much faster than the others. Consequently, the metal thickness of the sparse areas become thicker than that of the dense places as shown in Fig. 1.6 (a) [18]. To resolve this issue, a minimum metal density must be satisfied for the entire chip. For example, the minimum metal density must be at least 25% in any  $100 \,\mu\text{m} \times 100 \,\mu\text{m}$ square in a 28-nm technology. Hence, inductors and transformers must include dummy metal pieces from the lowest to the highest metal layer (see Fig. 1.6 (c)). Metal dummies show negligible effects on the windings self-inductance and the coupling factor. However, as shown in Fig. 1.6 (b), eddy currents in dummy fills increase the loss and thus the inductor's/transformer's Q-factor

6 Introduction

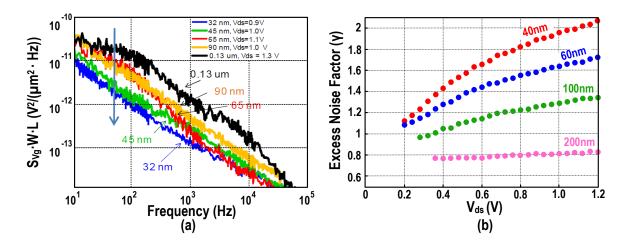

Figure 1.7: (a) Flicker noise scaling trend; (b) measured excess noise ( $\gamma$ ) factor versus drainsource voltage at 10 GHz and  $V_{gs} = 1.0 \,\mathrm{V}$  for different gate lengths of NMOS transistors in 40 nm LP technology [20].

could be degraded by 10% [19].

To conclude this section, the quality factor of passives degrades by migrating to more advanced nano-scale CMOS technologies. It leads to a worse phase noise performance for oscillators and a larger insertion loss for matching networks of power amplifiers.

### 1.1.3 Noise of Active Devices

Figure 1.7 (a) shows the normalized input referred 1/f noise,  $S_{vg}$ , versus frequency for different technology nodes. Due to oxide scaling enabled by high-k/metal gate technologies, the normalized  $S_{vg}$  is monotonically reduced with each successive technology node. For the same transistor area,  $S_{vg}$  decreases  $\sim 10 \times$  from the 0.13  $\mu$ m node to 32 nm node. However, as shown in Fig. 1.7 (b), the excess noise factor of CMOS transistors increases by migrating to finer CMOS technologies. Consequently, oscillator's core transistors inject more thermal noise to the tank, degrading its phase noise performance.

### 1.2 Thesis Objectives

Based on the aforementioned explanations in Section 1.1, the underlying objective of this dissertation is, therefore, to implement innovative RF/mm-wave oscillator and power amplifier structures to improve the power efficiency of the entire wireless transceiver. The first objective of this thesis is to introduce a new class of operation for RF oscillators to fill the performance/power gap in the ultra-high figure of merit (FoM) and ultra-low phase noise oscillator space currently not satisfied by state-of-the-art structures. The proposed oscillator is also implemented as the heart of an all-digital phase-locked loop to demonstrate its effectiveness on improving the power efficiency of a 4G frequency synthesizer. The second objective is to analyze and understand various design parameters and tradeoffs in the design space of switched-mode power amplifiers. These insights will lead to the design and implementation of two different power amplifiers operating at 2.4 GHz and 60 GHz. The third objective of this thesis is to improve the power

1.3 Thesis Outline 7

efficiency of a Bluetooth Low Energy transmitter by exploiting a novel digitally controlled oscillator and a class-E/F<sub>2</sub> switched-mode power amplifier.

### 1.3 Thesis Outline

This thesis is composed of three parts. The main focus of the first part is on the design and implementation of innovative RF oscillators for cellular applications. A comprehensive analysis of switched-mode amplifiers and the design and implementation of a wideband class-E/F<sub>2</sub> mm-wave PA are presented in the second part. Finally, a new transmitter architecture for ultra-low power radios is introduced in the third part of this dissertation.

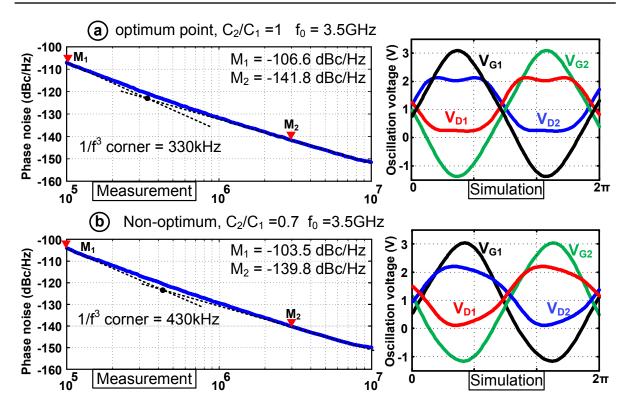

The first part starts with Chapter 2 by introducing an oscillator topology demonstrating an improved phase noise performance. The proposed oscillator operates in class-F by enforcing a pseudo-square voltage waveform around the LC tank by increasing the third harmonic of the fundamental oscillation voltage through an additional impedance peak. Measurement results of an implemented 65 nm prototype are presented and compared with state-of-the-art oscillators. Furthermore, a comprehensive study of circuit-to-phase-noise conversion mechanisms of different classes of RF oscillator is presented.

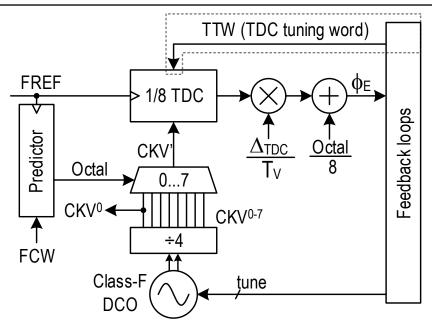

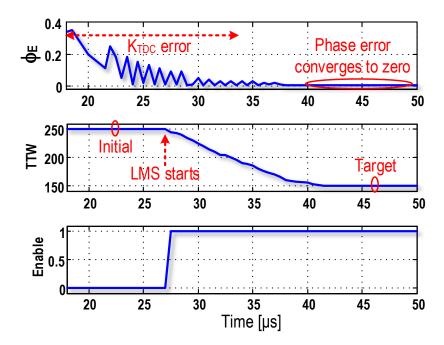

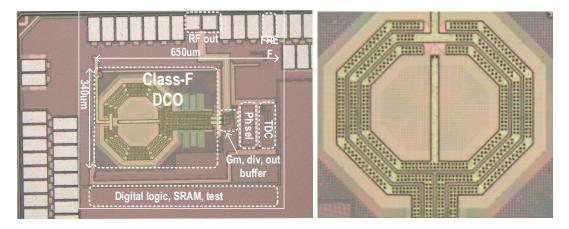

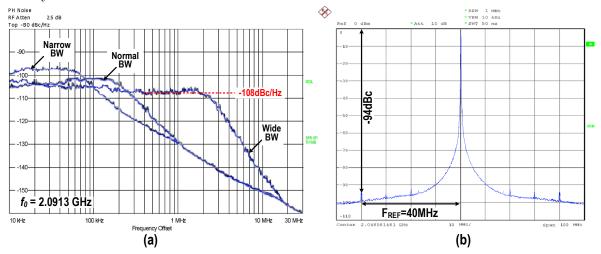

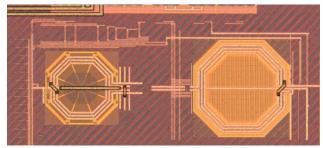

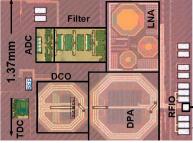

In Chapter 3, the proposed class-F oscillator is exploited in a 28 nm all-digital PLL (ADPLL) for 4G mobile phones. Functions of the different building blocks of this PLL are briefly explained. Due to the class-F operation of the digitally controlled oscillator (DCO), the ADPLL demonstrates a 72% power reduction over prior records.

In Chapter 4, a new class of operation for RF oscillators is introduced. The main idea is to enforce a clipped voltage waveform around the LC tank by increasing the second-harmonic of fundamental oscillation voltage through an additional impedance peak, thus giving rise to a class- $F_2$  operation. This oscillator specifically addresses the ultra-low phase noise design space while maintaining high power efficiency. Extensive experimental results and an insightful reliability analysis are also presented at the end of this chapter.

The second part of this thesis starts with Chapter 5 where a comprehensive analysis of switched-mode amplifiers is presented. Precise analytical voltage-current waveforms, zero-voltage, and zero-slope switching criteria and waveform-dependent parameters of any flavor of a switched-mode PA are quantified. Furthermore, closed-form equations are derived for the optimum size of the switch and different PA's characteristics such as maximum achievable power added efficiency, output power, and maximum operating frequency.

In Chapter 6, a fully integrated 60 GHz power amplifier is presented. The benefits, constraints, and trade-offs of different transmitter structures and extended class- $E/F_2$  PA are investigated from the mm-wave viewpoint. Implementation details and chip measurement results are also presented. This PA reaches the highest reported product of power-added efficiency and bandwidth. It is achieved through low/moderate coupling-factor transformers in the preliminary stages and a proper second harmonic termination of the output stage, such that it can operate as a class- $E/F_2$  switched-mode PA at the saturation point.

Chapter 7 is the last part of the dissertation. A novel digitally controlled oscillator with switching current sources is introduced to reduce supply voltage and power without sacrificing its phase noise and startup margins. A fully integrated differential class-E/F<sub>2</sub> switching PA is designed to improve system efficiency at a low output power of 0-3 dBm while fulfilling all

8 Introduction

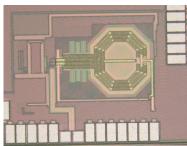

in-band and out of band emission masks. The required matching network is realized by exploiting different behaviors of a 2:1 step-down transformer in differential and common-mode excitations. Based on those innovations, an ultra-low power Bluetooth Low Energy transmitter is proposed that demonstrates the best ever reported system efficiency and phase purity while abiding by the strict 28 nm CMOS technology manufacturing rules.

Finally, Chapter 8 concludes this dissertation and presents suggestions for future developments.

### 1.4 Original Contributions

The original contributions to the body of knowledge of Solid-State Circuits Society are as follows:

- Introducing a new class of operation of an RF oscillator (Chapter 2, 4);

- Comprehensive analysis of circuit-to-phase-noise conversion mechanisms of different oscillators structures and dispelling common myths (Chapter 2, 4);

- Adapting the proposed class-F oscillator into a 28 nm all-digital phase-locked loop while abiding by strict metal density rules (Chapter 3);

- Applying the general knowledge of CMOS device reliability to high-performance RF oscillators (Chapter 4);

- Comprehensive analysis and systemization of different flavors of class-E/F power amplifiers (Chapter 5);

- Design, implementation, and test of a mm-wave power amplifier with the highest product of power-added efficiency and bandwidth. (Chapter 6);

- Proposing and verifying a switching current source oscillator for ultra-low voltage and power applications (Chapter 7);

- Design and implementation of a fully integrated differential class-E/F<sub>2</sub> switching PA for BLE transmitter (Chapter 7).

### CHAPTER

# 2

## A Class-F CMOS Oscillator

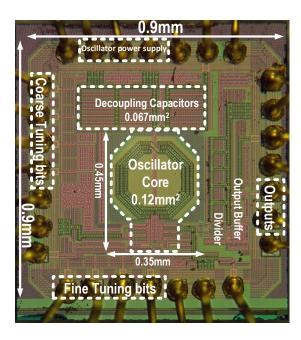

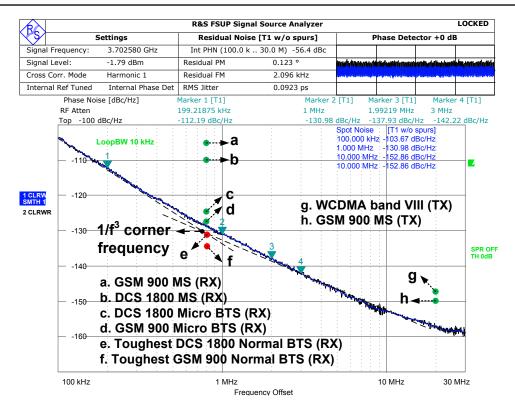

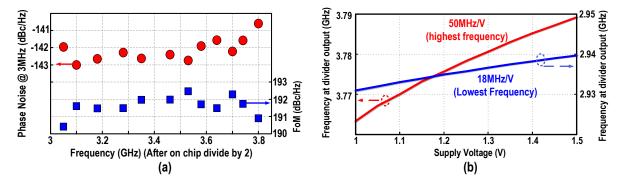

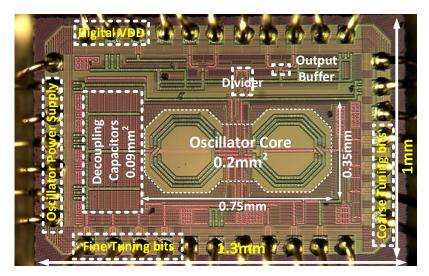

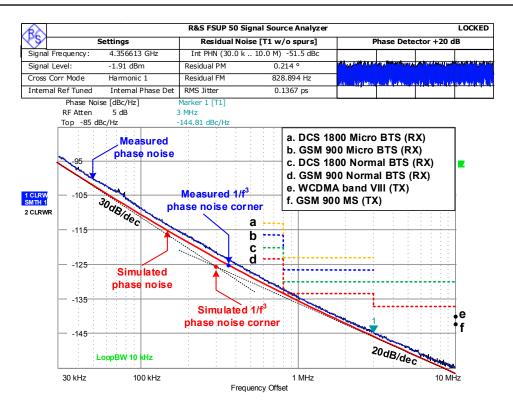

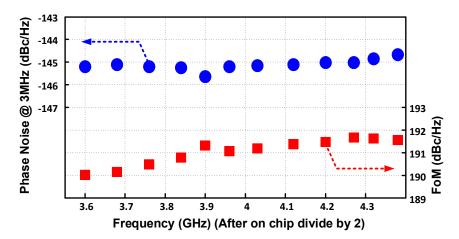

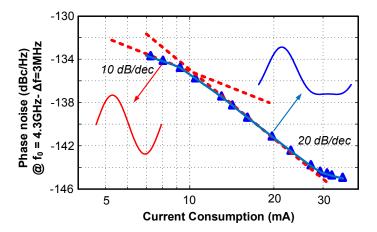

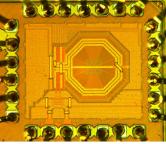

An oscillator topology demonstrating an improved phase noise performance is proposed in this Chapter<sup>1</sup>. It exploits a time-variant phase noise model with insights into the phase noise conversion mechanisms. The proposed oscillator is based on enforcing a pseudo-square voltage waveform around the LC tank by increasing the third-harmonic of the fundamental oscillation voltage through an additional impedance peak. This auxiliary impedance peak is realized by a transformer with moderately coupled resonating windings. As a result, the effective impulse sensitivity function (ISF) decreases thus reducing the oscillator's effective noise factor such that a significant improvement in the oscillator phase noise and power efficiency are achieved. A comprehensive study of circuit-to-phase-noise conversion mechanisms of different oscillators' structures shows the proposed class-F exhibits the lowest phase noise at the same tank's quality factor and supply voltage. The prototype of the class-F oscillator is implemented in TSMC 65-nm standard CMOS. It exhibits average phase noise of -142 dBc/Hz at 3 MHz offset from the carrier over 5.9—7.6 GHz tuning range with figure-of-merit of 192 dBc/Hz. The oscillator occupies 0.12 mm<sup>2</sup> while drawing 12 mA from 1.25 V supply.

### 2.1 Introduction

Designing voltage-controlled and digitally-controlled oscillators (VCO, DCO) of high spectral purity and low power consumption is quite challenging, especially for GSM transmitter (TX), where the oscillator phase noise must be less than -162 dBc/Hz at 20 MHz offset frequency from 915 MHz carrier [22]. At the same time, the RF oscillator consumes disproportionate amount of power of an RF frequency synthesizer [4], [5] and burns more than 30% of the cellular RX power [7], [23]. Consequently, any power reduction of RF oscillators will greatly benefit

<sup>&</sup>lt;sup>1</sup>This chapter has been published in the IEEE Journal of Solid-State Circuits [21].

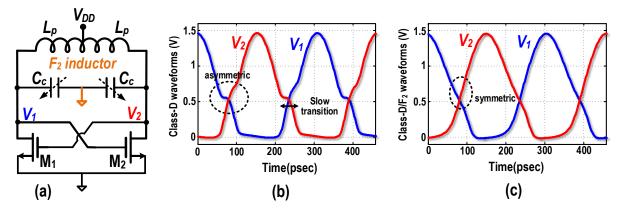

Figure 2.1: Oscillator schematic: (a) traditional class-B; (b) class-C.

the overall transceiver power efficiency and ultimately the battery lifetime. This motivation has encouraged an intensive research to improve the power efficiency of an RF oscillator while satisfying the strict phase noise requirements of the cellular standards.

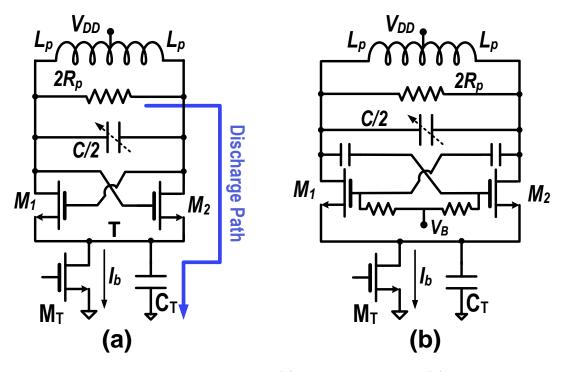

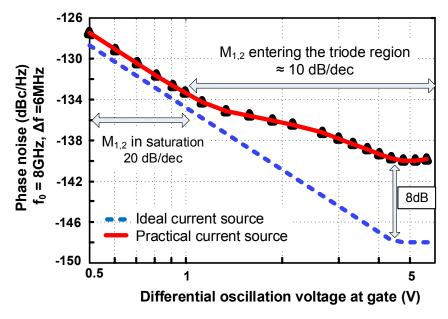

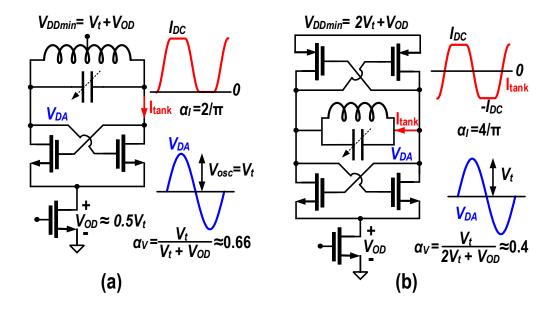

The traditional class-B oscillator (Fig.2.1(a)) is the most prevalent architecture due its simplicity and robustness. However, its phase noise and power efficiency performance drops dramatically just by replacing the ideal current source with a real one. Indeed, the traditional oscillator reaches its best performance for the oscillation amplitude of near supply voltage  $V_{DD}$  [24], [25]. Therefore, the gm-devices  $M_{1/2}$  enter deep triode for part of the oscillation period. They exhibit a few tens of ohms of channel resistance. In addition, the tail capacitor  $\mathcal{C}_T$  should be large enough to filter out thermal noise of  $\mathcal{M}_T$  around the even harmonics of the fundamental, thus making a low impedance path between node "T" and ground. Consequently, the tank output node finds a discharge path to the ground. It means that the equivalent Q-factor of the tank is degraded dramatically. This event happens alternatively between M<sub>1</sub> and M<sub>2</sub> transistors in each oscillation period. Hence, the phase noise improvement would be negligible by increasing the oscillation voltage swing when the gm-devices enter the triode region and thus, FoM drops dramatically. This degradation seems rather unavoidable in the simple structure of Fig. 2.1(a) since  $M_T$  must anyway be very large to reduce the  $1/f^3$  phase noise corner of the oscillator and thus its parasitic capacitor alone (i.e., even if  $C_T$  is zero) would be large enough to provide discharge path for the tank during the gm-device triode region operation.

The noise filtering technique [26] provides a relatively high impedance between the gm-devices and the current source. Hence, the structure maintains the intrinsic Q-factor of the tank during the entire oscillation period. However, it requires an extra resonator sensitive to parasitic capacitances, increasing the design complexity, area and cost.

Class-C oscillator (Fig.2.1(b)), prevents the gm-devices from entering the triode region [27], [28]. Hence, the tank Q-factor is preserved throughout the oscillation period. The oscillator

2.1 Introduction 11

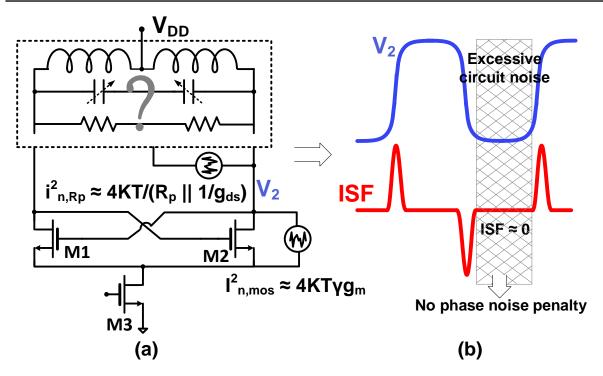

Figure 2.2: Oscillator: (a) noise sources; (b) targeted oscillation voltage (top) and its expected ISF (bottom).

also benefits with 36% power saving from changing the drain current shape from square-wave of the traditional oscillator to the "tall and narrow" form for the class-C operation. However, the constraint of avoiding entering the triode region limits the maximum oscillation amplitude of the class-C oscillator to around  $V_{DD}/2$ , for the case of bias voltage  $V_B$  as low as a threshold voltage of the active devices. It translates to 6 and 3 dB phase noise and FoM penalty, respectively. Consequently, class-C voltage swing constraint limits the lowest achievable phase noise performance.

Harmonic tuning oscillator enforces a pseudo-square voltage waveform around the LC tank through increasing the third-harmonic component of the fundamental oscillation voltage through an additional tank impedance peak at that frequency. Kim et al. [29] exploited this technique to improve the phase noise performance of the LC oscillator by increasing the oscillation zero-crossings' slope. However, that structure requires more than two separate LC resonators to make the desired tank input impedance. It increases die area and cost and decreases tuning range due to larger parasitics. Furthermore, the oscillator transconductance loop gain is the same for both resonant frequencies, thus raising the probability of undesired oscillation at the auxiliary tank input impedance. We have resolved the above mentioned concerns and quantified intuitively and theoretically the phase noise and power efficiency improvement of the class-F oscillator compared to other structures [30].

The Chapter is organized as follows: Section 2.2 establishes the environment to introduce the proposed class-F oscillator. The circuit-to-phase-noise conversion mechanisms are studied in Section 2.3. Section 2.4 presents extensive measurement results of the prototype, while Section 2.5 wraps up this Chapter with conclusions.

Figure 2.3: Traditional oscillator waveforms in time and frequency domains.

### 2.2 Evolution Towards Class-F Oscillator

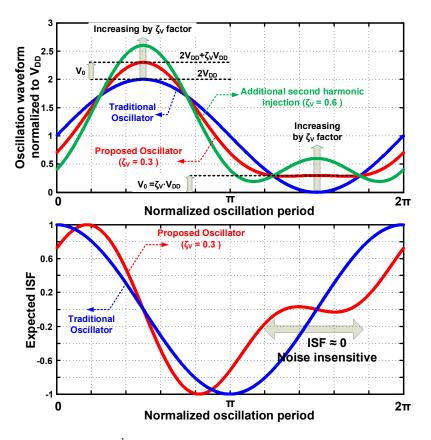

Suppose the oscillation voltage around the tank was a square-wave instead of a sinusoidal. As a consequence, the oscillator would exploit the special ISF [31] properties of the square-wave oscillation voltage to achieve a better phase noise and power efficiency. However, the gm-devices would work in the triode region (shaded area in Fig. 2.2(b)) even longer than in case of the sinusoidal oscillator. Hence, the loaded resonator and gm-device inject more noise to the tank. Nevertheless, ISF value is expected to be negligible in this time span due to the zero derivative of the oscillation voltage [31]. Although the circuit injects huge amount of noise to the tank, the noise cannot change the phase of the oscillation voltage and thus there is no phase noise degradation.

### 2.2.1 Realizing a Square-Wave across the LC Tank

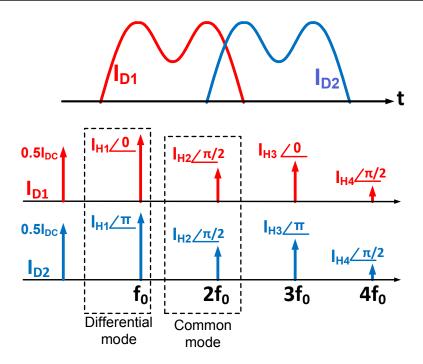

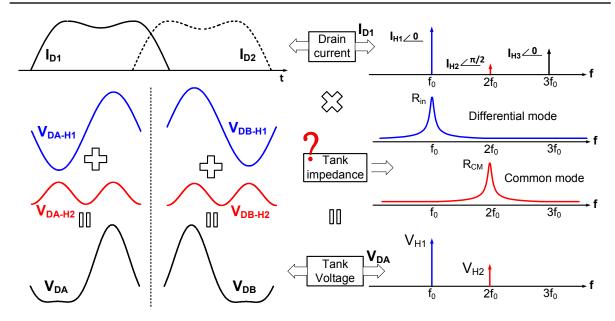

The above reasoning indicates that the square-wave oscillation voltage has special ISF properties that are beneficial for the oscillator phase noise performance. But how can a square-wave be realized across the tank? Let us take a closer look at the traditional oscillator in the frequency domain. As shown in Fig. 2.3, the drain current of a typical LC-tank oscillator is approximately a square-wave. Hence, it ideally has a fundamental and odd harmonic components. On the other hand, the tank input impedance has a magnitude peak only at the fundamental frequency. Therefore, the tank filters out the harmonic components of the drain current and finally a sinusoidal wave is seen across the tank.

Now, suppose the tank offers another input impedance magnitude peak around the third harmonic of the fundamental frequency (see Fig. 2.4). The tank would be prevented from filtering out the  $3^{rd}$  harmonic component of the drain current. Consequently, the oscillation voltage will contain a significant amount of the  $3^{rd}$  harmonic component in addition to the

Figure 2.4: Proposed oscillator waveforms in time and frequency domains.

fundamental:

$$V_{in} = V_{p1}\sin(\omega_0 t) + V_{p3}\sin(3\omega_0 t + \Delta\phi)$$

(2.1)

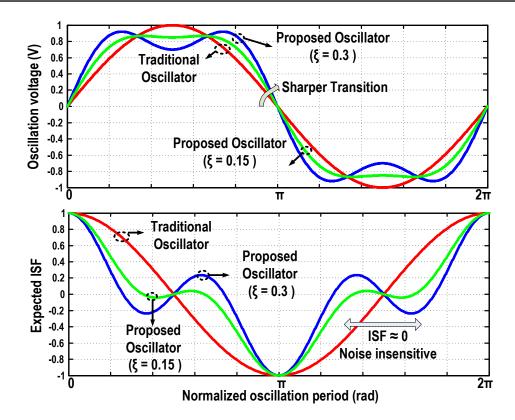

$\zeta$  is defined as the magnitude ratio of the third-to-first harmonic components of the oscillation voltage.

$$\zeta = \frac{V_{p3}}{V_{p1}} = \left(\frac{R_{p3}}{R_{p1}}\right) \left(\frac{I_{DH3}}{I_{DH1}}\right) \approx 0.33 \left(\frac{R_{p3}}{R_{p1}}\right)$$

(2.2)

where,  $R_{p1}$  and  $R_{p3}$  are the tank impedance magnitudes at the main resonant frequency  $\omega_1$  and  $3\omega_1$ , respectively. Figure 2.5 illustrates the oscillation voltage and its related expected ISF function (based on the closed-form equation in [31]) for different  $\zeta$  values. The ISF rms value of the proposed oscillation waveform can be estimated by the following expression for  $-\pi/8 < \Delta \phi < \pi/8$ .

$$\Gamma_{rms}^2 = \frac{1}{2} \frac{1 + 9\zeta^2}{(1 + 3\zeta)^2} \tag{2.3}$$

The waveform would become a sinusoidal for the extreme case of  $\zeta = 0$ ,  $\infty$  so (2.3) predicts  $\Gamma_{rms}^2 = 1/2$ , which is well-known for the traditional oscillators.  $\Gamma_{rms}^2$  reaches its lowest value of 1/4 for  $\zeta = 1/3$ , translated to a 3 dB phase noise and FoM improvement compared to the traditional oscillators. Furthermore, ISF of the proposed oscillator is negligible while the circuit injects significant amount of noise to the tank. Consequently, the oscillator FoM improvement could be larger than that predicted by just the ISF rms reduction.

Figure 2.5: The effect of adding  $3^{rd}$  harmonic in the oscillation waveform (top) and its expected ISF (bottom).

Figure 2.6: Transformer-based resonator (a); and its equivalent circuit (b).

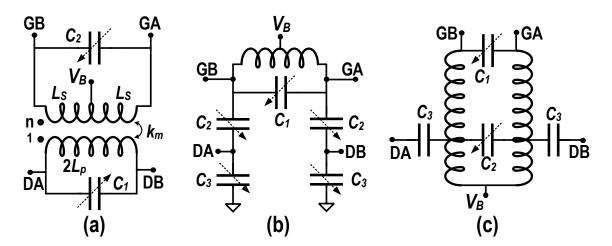

### 2.2.2 Proposed Tank

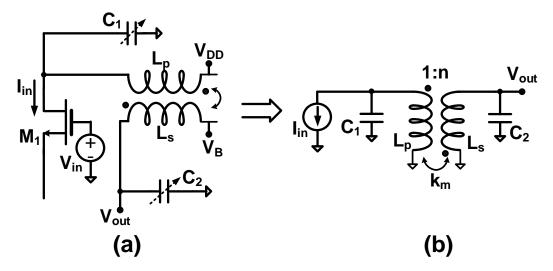

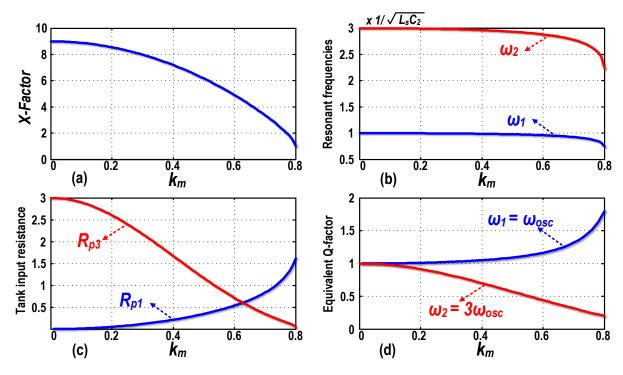

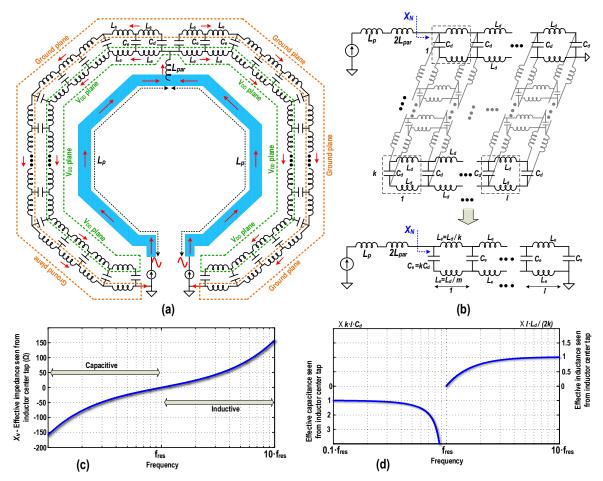

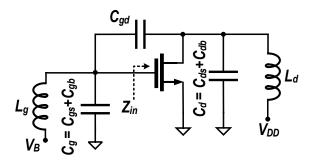

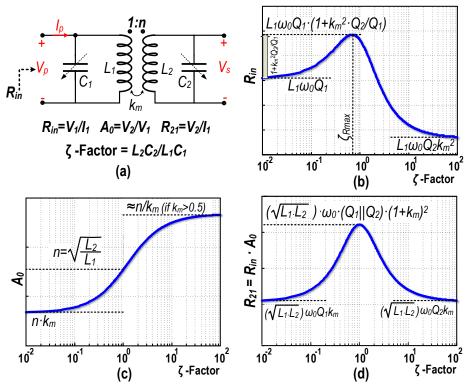

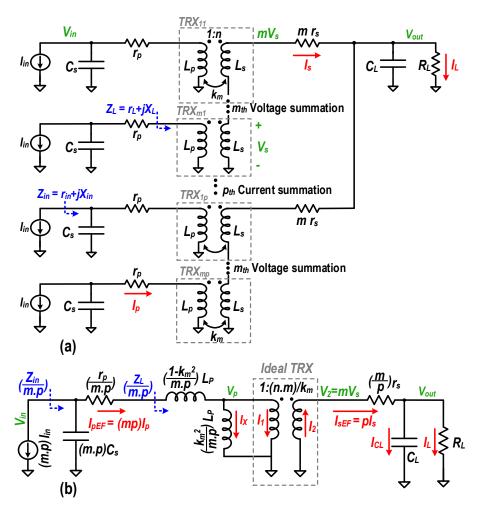

The argumentation related to Fig. 2.4 above advocates the use of two resonant frequencies with a ratio of 3. The simplest way of realizing that would be with two separate inductors [29], [32]. However this will be bulky and inefficient. The chosen option in this work is a transformer-based resonator. The preferred resonator consists of a transformer with turns ratio n and tuning capacitors  $C_1$  and  $C_2$  at the transformer's primary and secondary windings, respectively (see Fig. 2.6). Eq. (2.4) expresses the exact mathematical equation of the input impedance of the tank.

$$Z_{in} = \frac{s^{3}\left(L_{p}L_{s}C_{2}\left(1-k_{m}^{2}\right)\right) + s^{2}\left(C_{2}\left(L_{s}r_{p} + L_{p}r_{s}\right)\right) + s\left(L_{p} + r_{s}r_{p}C_{2}\right)\right) + r_{p}}{s^{4}\left(L_{p}L_{s}C_{1}C_{2}\left(1-k_{m}^{2}\right)\right) + s^{3}\left(C_{1}C_{2}\left(L_{s}r_{p} + L_{p}r_{s}\right)\right) + s^{2}\left(L_{p}C_{1} + L_{s}C_{2} + r_{p}r_{s}C_{1}C_{2}\right)\right) + s\left(r_{p}C_{1} + r_{s}C_{2}\right) + 1}$$

(2.4)

where,  $k_m$  is the magnetic coupling factor of the transformer,  $\mathbf{r}_p$  and  $\mathbf{r}_s$  model the equivalent series resistance of the primary  $\mathbf{L}_p$  and secondary  $\mathbf{L}_s$  inductances [33]. The denominator of

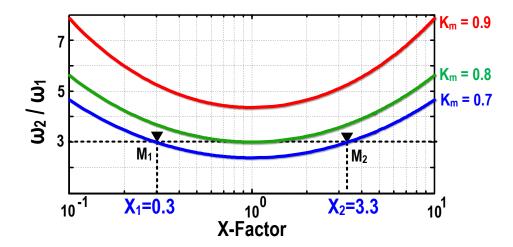

Figure 2.7: Ratio of the tank resonant frequencies versus X-factor for different  $k_m$ .

$Z_{in}$  is a fourth-order polynomial for the imperfect coupling factor (i.e.,  $k_m < 1$ ). Hence, the tank contains two different conjugate pole pairs, which realize two different resonant frequencies. Consequently, the input impedance has two magnitude peaks at these frequencies. Note that both resonant frequencies can satisfy the Barkhausen criterion with a sufficient loop gain [34]. However, the resulting multi-oscillation behavior is undesired and must be avoided [35]. In our case, it is preferred to see an oscillation at the lower resonant frequency  $\omega_1$  and the additional tank impedance at  $\omega_2$  is used to make a pseudo-square waveform across the tank. These two possible resonant frequencies can be expressed as

$$\omega_{1,2}^{2} = \frac{1 + \left(\frac{L_{s}C_{2}}{L_{p}C_{1}}\right) \pm \sqrt{1 + \left(\frac{L_{s}C_{2}}{L_{p}C_{1}}\right)^{2} + \left(\frac{L_{s}C_{2}}{L_{p}C_{1}}\right)(4k_{m}^{2} - 2)}}{2L_{s}C_{2}\left(1 - k_{m}^{2}\right)}$$

(2.5)

The following expression offers a good estimation of the main resonant frequency of the tank for  $0.5 \le k_m \le 1$ .

$$\omega_1^2 = \frac{1}{(L_p C_1 + L_s C_2)} \tag{2.6}$$

However, we are interested in the ratio of resonant frequencies as given by

$$\frac{\omega_2}{\omega_1} = \sqrt{\frac{1 + X + \sqrt{1 + X^2 + X(4k_m^2 - 2)}}{1 + X - \sqrt{1 + X^2 + X(4k_m^2 - 2)}}}$$

(2.7)

where, X-factor is defined as

$$X = \left(\frac{L_s}{L_p} \cdot \frac{C_2}{C_1}\right) \tag{2.8}$$

Eq. 2.7 indicates the resonant frequency ratio  $\omega_2/\omega_1$  is just a function of the transformer inductance ratio  $L_s/L_p$ , tuning capacitance ratio  $C_2/C_1$ , and transformer magnetic coupling factor  $k_m$ . The relative matching of capacitors (and inductors) in today's CMOS technology is expected to be much better than 1%, while the magnetic coupling is controlled through lithography that precisely sets the physical dimensions of the transformer. Consequently, the

relative position of the resonant frequencies is not sensitive to the process variation. The  $\omega_2/\omega_1$  ratio is illustrated versus X-factor for different  $k_m$  in Fig. 2.7. As expected, the ratio moves to higher values for larger  $k_m$  and finally the second resonance disappears for the perfect coupling factor. The ratio of  $\omega_2/\omega_1$  reaches the desired value of 3 at two points for the coupling factor of less than 0.8. Both points put  $\omega_2$  at the correct position of  $3\omega_1$ . However, the desired X-factor should be chosen based on the magnitude ratio  $R_{p2}/R_{p1}$  of the tank input impedance at resonance. The sum of the even orders of the denominator in (2.4) is zero at resonant frequencies. It can be shown that the first-order terms of the numerator and the denominator are dominant at  $\omega_1$ . By using (2.6), assuming  $Q_p = L_p \omega/r_p$ ,  $Q_s = L_s \omega/r_s$ , the tank input impedance at the fundamental frequency is expressed as

$$R_{p1} \approx \frac{L_p}{\omega_1 \left(\frac{L_p C_1}{Q_p} + \frac{L_s C_2}{Q_s}\right)} \stackrel{Q_p = Q_s = Q_0}{\Longrightarrow} R_{p1} \approx L_p \omega_1 Q_0 \tag{2.9}$$

On the other hand, it can be shown that the third-order terms of the numerator and the denominator are dominant in (2.4) at  $\omega_2 = 3\omega_1$ . It follows that

$$R_{p2} \approx \frac{(1 - k_m^2)}{C_1 \omega_2 \left(\frac{1}{Q_p} + \frac{1}{Q_s}\right)} \stackrel{Q_p = Q_s = Q_0}{\Longrightarrow} R_{p2} \approx \frac{Q_0 \left(1 - k_m^2\right)}{2 C_1 \omega_2}$$

(2.10)

$R_{p2}$  is a strong function of the coupling factor of the transformer and thus the resulting leakage inductance. Weaker magnetic coupling will result in higher impedance magnitude at  $\omega_2$  and, consequently, the second resonance needs a lower transconductance gain to excite. It could even become a dominant pole and the circuit would oscillate at  $\omega_2$  instead of  $\omega_1$ . This phenomenon has been used to extend the oscillator tuning range in [34], [36] and [37]. As explained before,  $R_{p2}/R_{p1}$  controls the amount of the  $3^{rd}$  harmonic component of the oscillation voltage. The impedance magnitude ratio is equal to

$$\frac{R_{p2}}{R_{v1}} \approx \frac{(1 - k_m^2)(1 + X)}{6} \tag{2.11}$$

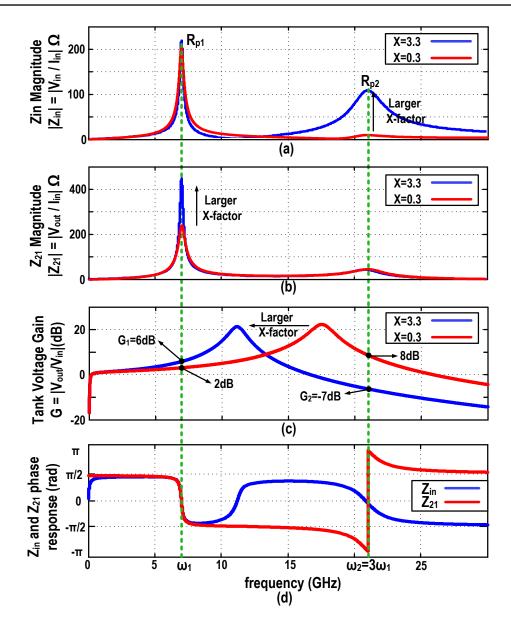

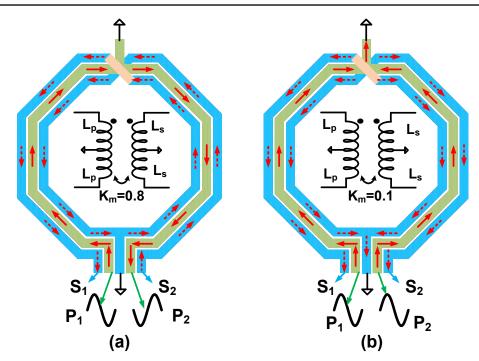

Hence, the smaller X-factor results in lower tank equivalent resistance at  $\omega_2 = 3\omega_1$ . Thus, the tank filters out more of the  $3^{rd}$  harmonic of the drain current and the oscillation voltage becomes more sinusoidal. Figure 2.8(a) illustrates Momentum simulation results of  $Z_{in}$  of the transformer-based tank versus frequency for both X-factors that satisfy the resonant frequency ratio of 3. The larger X-factor offers significantly higher tank impedance at  $\omega_2$ , which is entirely in agreement with the theoretical analysis.

The X-factor is defined as a product of the transformer inductance ratio  $L_s/L_p$  and tuning capacitance ratio  $C_2/C_1$ . This leads to a question of how best to divide X-factor between the inductance and capacitance ratios. In general, larger  $L_s/L_p$  results in higher inter-winding voltage gain, which translates to sharper transition at zero-crossings and larger oscillation amplitude at the secondary winding. Both of these effects have a direct consequence on the phase noise improvement. However, the transformer Q-factor drops by increasing the turns ratio. In addition, very large oscillation voltage swing brings up reliability issues due to the gate-oxide breakdown. It turns out that the turns ratio of 2 can satisfy the aforementioned constraints altogether.

Figure 2.8: The transformer-based tank characteristics: (a) the input impedance,  $Z_{in}$  magnitude; (b) the trans-impedance,  $Z_{21}$  magnitude; (C) transformer's secondary to primary voltage gain; (d) the phase of  $Z_{in}$  and  $Z_{21}$  (Momentum simulation).

### 2.2.3 Voltage Gain of the Tank

The transformer-based resonator, whose schematic was shown in Fig. 2.6, offers a filtering function on the signal path from the primary to the secondary windings. The tank voltage gain is derived as

$$G(s) = \frac{V_{out}}{V_{in}} = \frac{Ms}{s^3 (L_p L_s C_2 (1 - k_m^2)) + s^2 (C_2 (L_s r_p + L_p r_s)) + s (L_p + r_s r_p C_2)) + r_p}$$

(2.12)

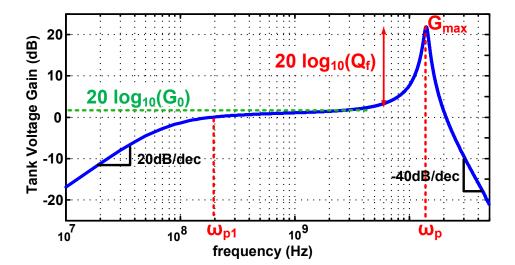

Bode diagram of the tank voltage gain transfer function is shown in Fig. 2.9. The tank exhibits a 20 dB/dec attenuation for frequencies lower than the first pole and offers a constant voltage gain at frequencies between the first pole and the complex conjugate pole pair at  $\omega_p$ .

Figure 2.9: Typical secondary-to-primary winding voltage gain of the transformer-based resonator versus frequency.

The gain plot reveals an interesting peak at frequencies around  $\omega_p$ , beyond which the filter gain drops at the -40 dB/dec slope. The low frequency pole is estimated by

$$\omega_{p1} = \frac{r_p}{L_p} \tag{2.13}$$

By substituting  $r_p = L_p \omega/Q_p$ ,  $r_s = L_s \omega/Q_s$  and assuming  $Q_p \cdot Q_s \gg 1$ , the tank gain transfer function can be simplified to the following equation for the frequencies beyond  $\omega_{p1}$ .

$$G(s) = \frac{\frac{M}{L_p}}{s^2 \left( L_s C_2 \left( 1 - k_m^2 \right) \right) + s \left( L_s C_2 \omega \left( \frac{1}{Q_p} + \frac{1}{Q_s} \right) \right) + 1}$$

(2.14)

The main characteristics of the tank voltage gain can be specified by considering it as a biquad filter.

$$G(s) = \frac{G_0}{\left(\frac{s}{\omega_p}\right)^2 + \left(\frac{s}{\omega_p Q_f}\right) + 1}$$

(2.15)

where,

$$G_0 = k_m n (2.16)$$

The peak frequency is estimated by

$$\omega_p = \sqrt{\frac{1}{L_s C_2 \left(1 - k_m^2\right)}} \tag{2.17}$$

$Q_f$  represents the amount of gain jump around  $\omega_p$  and expressed by

$$Q_f = \frac{(1 - k_m^2)}{\frac{1}{Q_p} + \frac{1}{Q_s}} \tag{2.18}$$

| Table 2.1. Itel manifed zero crossing slope of the proposed oscilla |                                                 |  |  |

|---------------------------------------------------------------------|-------------------------------------------------|--|--|

|                                                                     | Normalized zero-crossing slope                  |  |  |

| Traditional LC                                                      | 1                                               |  |  |

| Proposed tank (primary)                                             | $1+3\zeta = 1+3\cdot 1/6 = 1.5$                 |  |  |

| Proposed tank (secondary)                                           | $G_1-3G_2\zeta = 2.1 - 3\cdot0.4\cdot1/6 = 1.9$ |  |  |

Table 2.1: Normalized zero-crossing slope of the proposed oscillator.

Hence, the maximum voltage gain is calculated by

$$G_{max} = k_m n \times \frac{(1 - k_m^2)}{\frac{1}{Q_n} + \frac{1}{Q_s}}$$

(2.19)

Eqs. (2.19) and Fig. 2.9 demonstrate that the transformer-based resonator can offer the voltage gain above  $k_m n$  at the frequencies near  $\omega_p$  for  $k_m < 1$  and the peak magnitude is increased by improving Q-factor of the transformer individual inductors. Consequently,  $\omega_1$  should be close to  $\omega_p$  to have higher passive gain at the fundamental frequency and more attenuation at its harmonic components. Eqs. (2.6) and (2.17) indicate that  $\omega_p$  is always located at frequencies above  $\omega_1$  and the frequency gap between them decreases with greater X-factor. Figure 2.8(c) illustrates the voltage gain of the transformer-based tank for two different X-factors that exhibit the same resonant frequencies. The transformer peak gain happens at much higher frequencies for the smaller X-factor and, therefore, the gain is limited to only  $k_m n$  (2 dB in this case) at  $\omega_1$ . However, X-factor is around 3 for the proposed oscillator and, as a consequence,  $\omega_p$  moves lower and much closer to  $\omega_1$ . Now, the tank offers higher voltage gain (G<sub>1</sub>=6 dB in this case) at the main resonance and more attenuation (G<sub>2</sub>=-7 dB) at  $\omega_2$ . This former translates to larger oscillation voltage swing and thus better phase noise.

As can be seen in Fig. 2.8(d), the input impedance  $Z_{in}$  phase is zero at the first and second resonant frequencies. Hence, any injected  $3^{rd}$  harmonic current has a constructive effect resulting in sharper zero-crossings and flat peak for the transformer's primary winding voltage. However, the tank trans-impedance,  $Z_{21}$  phase shows a 180 degree phase difference at  $\omega_1$  and  $\omega_2 = 3\omega_1$ . Consequently, the  $3^{rd}$  harmonic current injection at the primary windings leads to a slower zero-crossings slope at the transformer's secondary, which has an adverse outcome on the phase noise performance of the oscillator. Figure 2.8(a-c) illustrates that the proposed transformer-based resonator effectively filters out the  $3^{rd}$  harmonic component of the drain current at the secondary winding in order to minimize these side effects and zero-crossings are sharpened by tank's voltage gain  $(G_1)$  at  $\omega_1$ . Table 2.1 shows that the zero-crossings slope of the proposed oscillator at both transformer's windings are improved compared to the traditional oscillator for the same  $V_{DD}$ , which is translated to shorter commutating time and lower active device noise factor.

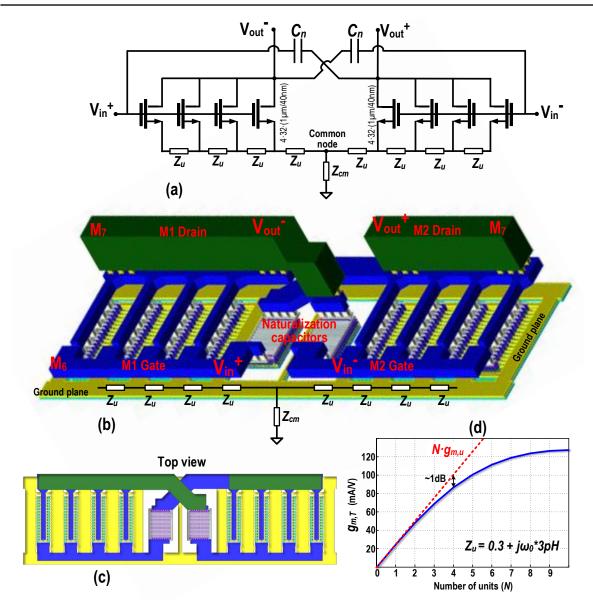

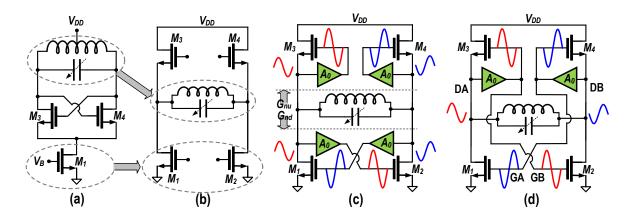

### 2.2.4 Proposed Class-F Oscillator

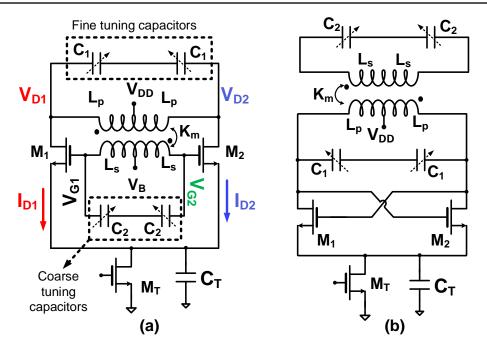

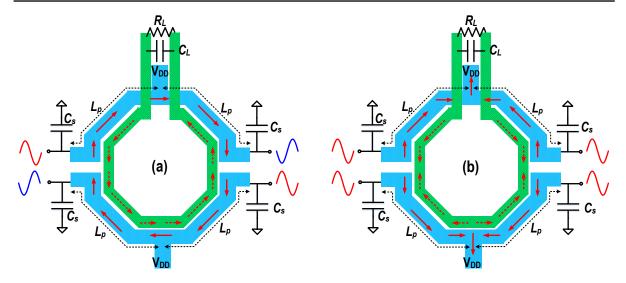

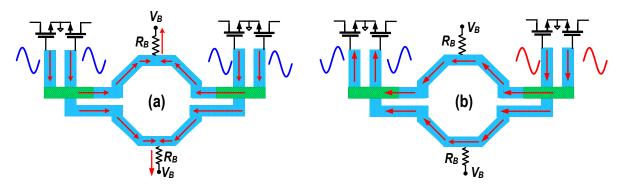

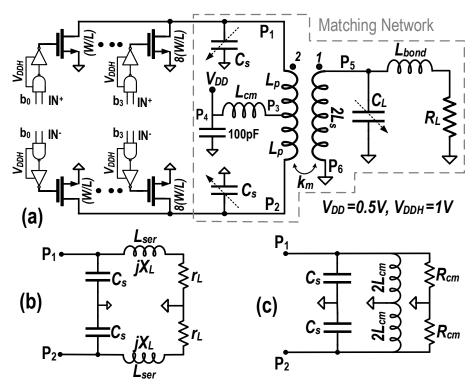

The desired tank impedance, inductance and capacitance ratios were determined above to enforce the pseudo-square-wave oscillation voltage around the tank. Now, two transistors should be customarily added to the transformer-based resonator to sustain the oscillation. There are two options, however, as shown in Fig. 2.10, for connecting the transformer to the active gm-devices. The first option is a transformer-coupled class-F oscillator in which the secondary

Figure 2.10: Two options of the transformer-based class-F oscillator: (a) transformer-coupled; and (b) cross-coupled. The first option was chosen as more advantageous in this work.

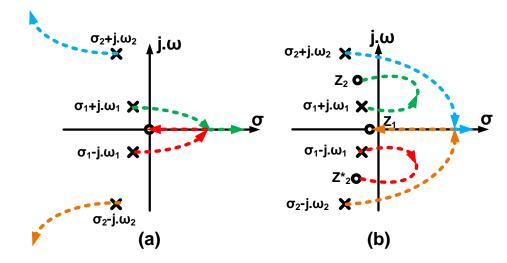

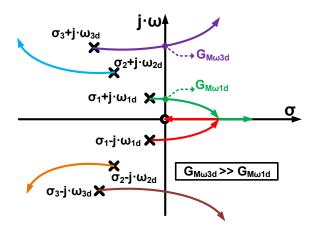

winding is connected to the gate of the gm-devices. The second option is a cross-coupled class-F oscillator with a floating secondary transformer winding, which only physically connects to tuning capacitors C<sub>2</sub>. The oscillation voltage swing, the equivalent resonator quality factor and tank input impedance are the same for both options. However, the gm-device sustains larger voltage swing in the first option. Consequently, its commutation time is shorter and the active device noise factor is lower. In addition, the gm-device generates higher amount of the  $3^{rd}$  harmonic, which results in sharper pseudo-square oscillation voltage with lower ISF rms value. The second major difference is about the possibility of oscillation at  $\omega_2$  instead of  $\omega_1$ . The root-locus plot in Fig. 2.11 illustrates the route of pole movements towards zeros for different values of the oscillator loop trans-conductance gain  $(G_m)$ . As can be seen in Fig. 2.11(b), both resonant frequencies  $(\omega_1, \omega_2)$  can be excited simultaneously with a relatively high value of  $G_m$  for the cross-coupled class-F oscillator of Fig. 2.10(b). It can increase the likelihood of the undesired oscillation at  $\omega_2$ . However, the transformer-coupled circuit of Fig. 2.10(a) demonstrates a different behavior. The lower frequency conjugate pole pair moves into the right-hand plane by increasing the absolute value of  $G_m$ , while the higher poles are pushed far away from imaginary axis (see Fig. 2.11(a)). This guarantees the oscillation can only happen at  $\omega_1$ . Consequently, it becomes clear that the transformer-coupled oscillator is a better option due to its phase noise performance and the guaranty of operation at the right resonant frequency. Nevertheless, the gate parasitic capacitance appears at the drain through a scaling factor of  $n^2$ , which reduces its tuning range somewhat as compared to the cross-coupled candidate.

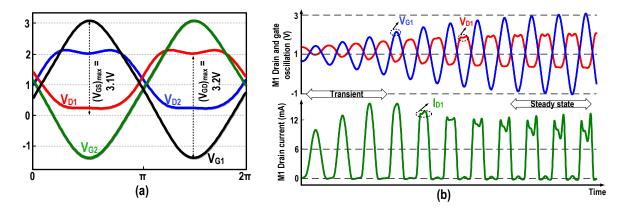

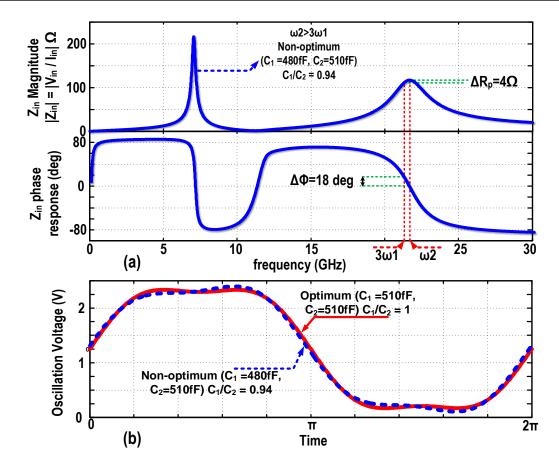

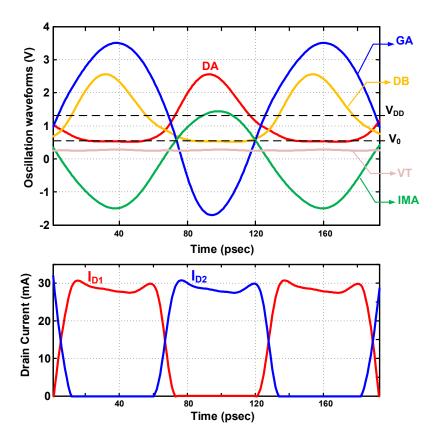

Figure 2.12 (a) illustrates the unconventional oscillation voltage waveforms of the proposed transformer-coupled class-F oscillator. As specified in Section 2.2.3, the  $3^{rd}$  harmonic component of the drain voltage attenuates at the gate and thus a sinusoidal wave is seen there. The gate-drain voltage swing goes as high as  $2.7 \cdot V_{DD}$  due to the significant voltage gain of the tank. Hence, using thick oxide gm-devices is a constraint to satisfy the time-dependent dielectric breakdown (TDDB) issue for less than 0.01% failure rate during ten years of the oscillator

Figure 2.11: Root-locus plot of the transformer-based class-F oscillator: (a) transformer-coupled structure of Fig. 2.10(a); and (b) cross-coupled structure of Fig. 2.10(b).

Figure 2.12: (a) Oscillation voltage waveforms and (b) transient response of the class-F oscillator.

operation [38], [39]. The costs are larger parasitics capacitance and slightly lower frequency tuning range.

The frequency tuning requires a bit different consideration in the class-F oscillator. Both  $C_1$  and  $C_2$  must, at a coarse level, be changed simultaneously to maintain  $L_sC_2/L_pC_1$  ratio such that  $\omega_2$  aligns with  $3\omega_1$ .

Figure 2.12(b) shows the transient response of the class-F oscillator. At power up, the oscillation voltage is very small and the drain current pulses have narrow and tall shape. Even though the tank has an additional impedance at  $3\omega_1$ , the  $3^{rd}$  harmonic component of the drain current is negligible and, consequently, the drain oscillation resembles a sinusoid. At steady state, gate oscillation voltage swing is large and the gm-device drain current is square-wave. Consequently, the combination of the tank input impedance with significant drain's  $3^{rd}$  harmonic component results in the pseudo-square wave for the drain oscillation voltage. This justifies its "class-F" designation.

Figure 2.13: Open-loop circuit for unloaded Q-factor calculation (a); its equivalent circuit (b).

### 2.3 Class-F Phase Noise Performance

### 2.3.1 Quality Factor of Transformer-based Resonator

The Q-factor of the complex tank, which comprises two coupled resonators, does not appear to be as straightforward in intuitive understanding as the Q-factor of the individual physical inductors. It is, therefore, imperative to understand the relationship between the open-loop Q-factor of the tank versus the Q-factor of the inductive and capacitive parts of the resonator.

First, suppose the tuning capacitance losses are negligible. Consequently, the oscillator equivalent Q-factor just includes the tank's inductive part losses. The open-loop Q-factor of the oscillator is defined as  $\omega_0/2 \cdot d\phi/d\omega$ , where  $\omega_0$  is the resonant frequency and  $d\phi/d\omega$  denotes the slope of the phase of the oscillator open-loop transfer function [40]. To determine the open-loop Q, we need to break the oscillator loop at the gate of  $M_1$ , as shown in Fig. 2.13. The open-loop transfer function is thus given by

$$H(s) = \frac{V_{out}}{I_{in}} = \frac{Ms}{As^4 + Bs^3 + Cs^2 + Ds + 1}$$

(2.20)

where,  $A = L_p L_s C_1 C_2 \left(1 - k_m^2\right)$ ,  $B = C_1 C_2 \left(L_s r_p + L_p r_s\right)$ ,  $C = L_p C_1 + L_s C_2 + r_p r_s C_1 C_2$ , and,  $D = r_p C_1 + r_s C_2$ . After carrying out lengthy algebra and considering  $(1 - C\omega^2 + A\omega^4 \approx 0)$  at the resonant frequencies,

$$Q_{i} = -\frac{\omega}{2} \frac{d\phi(\omega)}{d\omega} = \frac{(C\omega - 2A\omega^{3})}{(D - B\omega^{2})}$$

(2.21)

Substituting A, B, C and D into (2.21), then swapping  $r_p$  and  $r_s$  with  $L_p\omega/Q_p$  and  $L_s\omega/Q_s$ , respectively, and assuming  $Q_pQ_s\gg 1$ , we obtain

$$Q_{i} = \frac{\left(L_{p}C_{1} + L_{s}C_{2}\right) - 2\left(L_{p}L_{s}C_{1}C_{2}\left(1 - k_{m}^{2}\right)\right)\omega^{2}}{\left(\frac{L_{p}C_{1}}{Q_{p}} + \frac{L_{s}C_{2}}{Q_{s}}\right) - \left(C_{1}C_{2}L_{s}L_{p}\left(\frac{1}{Q_{p}} + \frac{1}{Q_{s}}\right)\right)\omega^{2}}$$

(2.22)

Substituting (2.5) as  $\omega$  into the above equation and carrying out the mathematics, the tank's

inductive part Q-factor at the main resonance is

$$Q_{i} = \frac{\left(1 + X^{2} + 2k_{m}X\right)}{\left(\frac{1}{Q_{p}} + \frac{X^{2}}{Q_{s}}\right)}$$

(2.23)

To help with an intuitive understanding, let us consider a boundary case. Suppose, that  $C_2$  is negligible. Therefore, X-factor is zero and (2.23) predicts that the  $Q_i$  equals to  $Q_p$ . This is not surprising, because no energy would be stored at the transformer's secondary winding and its Q-factor would not have any contribution to the equivalent Q-factor of the tank. In addition, (2.23) predicts that the equivalent Q-factor of the tank's inductive part can exceed Q-factors of the individual inductors. To the authors' best knowledge, this is the first ever report of quantifying the equivalent Q-factor of the transformer-based resonator at its resonant frequency in a general case that clearly proves Q-factor enhancement over that of the transformer's individual inductors. The maximum tank's inductive part Q-factor is obtained at the following X-factor for a given  $k_m$ ,  $Q_p$  and  $Q_s$ .

$$X_{Qmax} = \frac{Q_s}{Q_p} \tag{2.24}$$

For a typical case of  $Q_s = Q_p = Q_0$ , the maximum  $Q_i$  at  $\omega_1$  is calculated by

$$X_{Qi,max} = 1 \to Q_{i,max} = Q_0 (1 + k_m)$$

(2.25)

The above equation indicates that the equivalent Q-factor of the inductive part of the transformer-based resonator can be enhanced by a factor of  $1 + k_m$  at the optimum state. However, it does not necessarily mean the Q-factor of the transformer-based tank generally is superior to the simple LC resonator. The reason is that it is not possible to optimize the Q-factor of both windings of a 1:n transformer at a given frequency and one needs to use lower metal layers for the transformer cross connections, which results in more losses and lower Q-factor [41], [42]. For this prototype, the X-factor is around 3 with  $k_m$ =0.7 and the simulated  $Q_p$  and  $Q_s$  are 14 and 20 respectively. Based on (2.23), the equivalent Q-factor of the inductive part of the tank would be about 26, which is higher than that of the transformers' individual inductors. The Q-factor of the switched capacitance largely depends on the tuning range (TR) and operating frequency of the oscillator and is about 42 for the TR of 25% at 7 GHz resulting in an average Q-factor of 16 for the tank in this design.

### 2.3.2 Phase Noise Mechanism in Class-F Oscillator

According to the linear time-variant model [31], the phase noise of the oscillator at an offset frequency  $\Delta\omega$  from its fundamental frequency is expressed as,

$$L(\Delta\omega) = 10\log_{10}\left(\frac{\sum_{i} N_{L,i}}{2 q_{max}^{2} (\Delta\omega)^{2}}\right)$$

(2.26)

where,  $q_{max}$  is the maximum charge displacement across the tuning capacitor C, and  $N_{L,i}$  is the effective noise produced by  $i^{th}$  device given by

$$N_{L,i} = \frac{1}{2\pi N^2} \int_0^{2\pi} \Gamma_i^2(t) \ \overline{i_{n,i}^2(t)} dt$$

(2.27)

Figure 2.14: RF CMOS oscillator noise sources.

where  $\overline{i_{n,i}^2(t)}$  is the white current noise power density of the  $i^{th}$  noise source,  $\Gamma_i$  is its relevant ISF function from the corresponding  $i^{th}$  device noise, and N is the number of resonators in the oscillator. N is considered one for single-ended and two for differential oscillator topologies with a single LC tank [25].

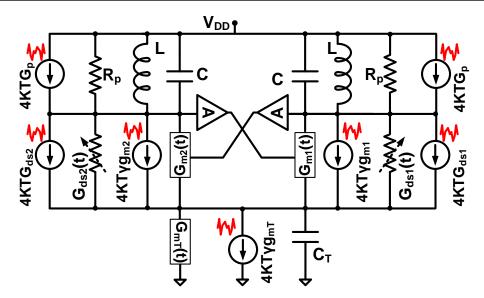

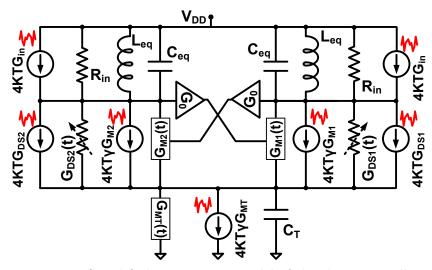

Figure 2.14 illustrates the major noise sources of CMOS class-B, C and F oscillators.  $R_p$  and  $G_{ds1,2}(t)$  represent the equivalent tank parallel resistance and channel conductance of the gm transistors, respectively. On the other hand,  $G_{m1,2}$  and  $G_{mT}$  model the noise due to transconductance gain of active core and current source transistors, respectively. By substituting (2.27) into (2.26) and carrying out algebra, the phase noise equation is simplified to

$$L(\Delta\omega) = 10\log_{10}\left(\frac{K_B T R_p}{2 Q_t^2 V_p^2} \cdot F \cdot \left(\frac{\omega_0}{\Delta\omega}\right)^2\right)$$

(2.28)

where  $Q_t$  is the tank's equivalent quality factor and  $V_p$  is the maximum oscillation voltage amplitude, derived by

$$V_{p} = \begin{cases} \left(\frac{1}{3} + \zeta\right) \sqrt{1 + \frac{1}{3\zeta}} \cdot \alpha_{I} \cdot R_{p} \cdot I_{B}, & \frac{1}{9} \leq \zeta \leq 1\\ (1 - \zeta) \cdot \alpha_{I} \cdot R_{p} \cdot I_{B}, & 0 \leq \zeta \leq \frac{1}{9} \end{cases}$$

$$(2.29)$$

where  $\alpha_I$  is the current conversion efficiency of the oscillator, expressed as the ratio of the fundamental component of gm-devices drain current to dc current  $I_B$  of the oscillator. F in (2.28) is the effective noise factor of the oscillator, expressed by

$$F = \sum_{i} \frac{1}{2\pi} \int_{0}^{2\pi} \Gamma_{i}^{2}(t) \frac{\overline{i_{n,i}^{2}(t)} R_{p}}{4K_{B}T} dt$$

(2.30)

Suppose that  $C_T$  is large enough to filter out the thermal noise of the tail transistor. Consequently, F consists of the noise factor of the tank  $(F_{tank})$ , transistor channel conductance  $(F_{GDS})$  and gm of core devices  $(F_{GM})$ . The expressions of  $F_{tank}$  and  $F_{GDS}$  are,

$$F_{Tank} = \frac{1}{\pi} \int_0^{2\pi} \Gamma_{tank}^2(t) dt = 2\Gamma_{rms}^2 \approx \frac{1 + 9\zeta^2}{(1 + 3\zeta)^2}$$

(2.31)

$$F_{GDS} = \frac{1}{\pi} \int_{0}^{2\pi} \Gamma_{MOS}^{2}(t) G_{DS1}(t) R_{P} dt \approx 2\Gamma_{rms}^{2} R_{P} \cdot G_{DS1EF}$$

(2.32)

where  $G_{DSEF1}$  is the effective drain-source conductance of one of the gm-devices expressed by

$$G_{DS1EF} = G_{DS1}[0] - G_{DS1}[2] (2.33)$$

where  $G_{DS1}[k]$  describes the  $k_{th}$  Fourier coefficient of the instantaneous conductance,  $G_{ds1}(t)$  [43].  $F_{GM}$  can be calculated by

$$F_{GM} = \frac{1}{\pi} \int_0^{2\pi} \Gamma_{MOS}^2(t) \gamma G_{m1}(t) R_P dt \approx 2\Gamma_{rms}^2 \cdot \gamma \cdot R_P \cdot G_{M1EF}$$

(2.34)

Now, the effective negative transconductance of the oscillator needs to overcome the tank and its own channel resistance losses and therefore the noise due to  $G_M$  also increases.

$$G_{M1EF} = \frac{1}{A} \left( \frac{1}{R_p} + G_{DS1EF} \right) \tag{2.35}$$

where A is the voltage gain of feedback path between the tank and MOS gate. By substituting (2.35) into (2.34)

$$F_{GM} = 2 \Gamma_{rms}^2 \cdot \frac{\gamma}{A} \cdot (1 + R_P G_{DS1EF})$$

(2.36)

Consequently, the effective noise factor of the oscillator is given by

$$F = 2 \Gamma_{rms}^2 \cdot \left(1 + \frac{\gamma}{A}\right) \cdot \left(1 + R_P G_{DS1EF}\right)$$

(2.37)

This is a general result and applicable to the class-B, C and F. The oscillator FoM normalizes the phase noise performance to the oscillation frequency and power consumption, yielding

$$FoM = -10 \cdot log_{10} \left( \frac{10^3 K_B T}{2 Q_t^2 \alpha_I \alpha_V} \cdot 2 \Gamma_{rms}^2 \cdot \left( 1 + \frac{\gamma}{A} \right) \cdot \left( 1 + R_P G_{DS1EF} \right) \right)$$

(2.38)

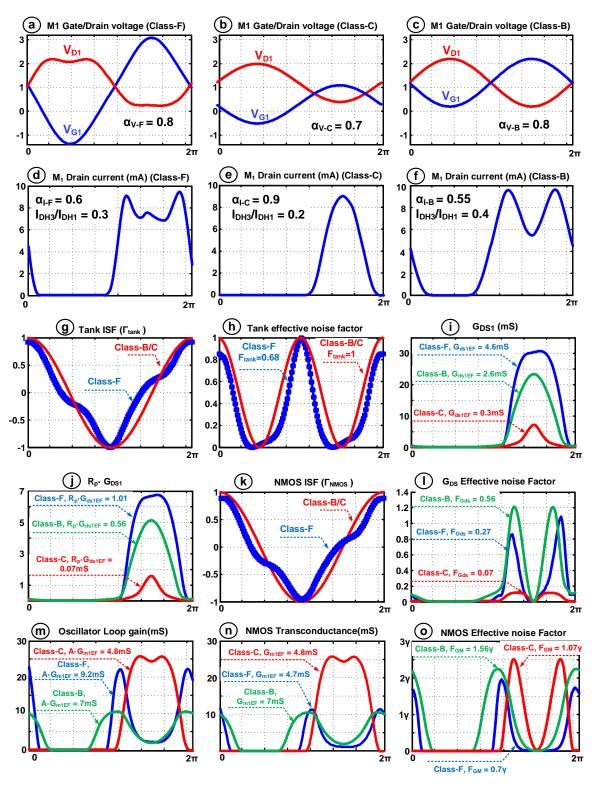

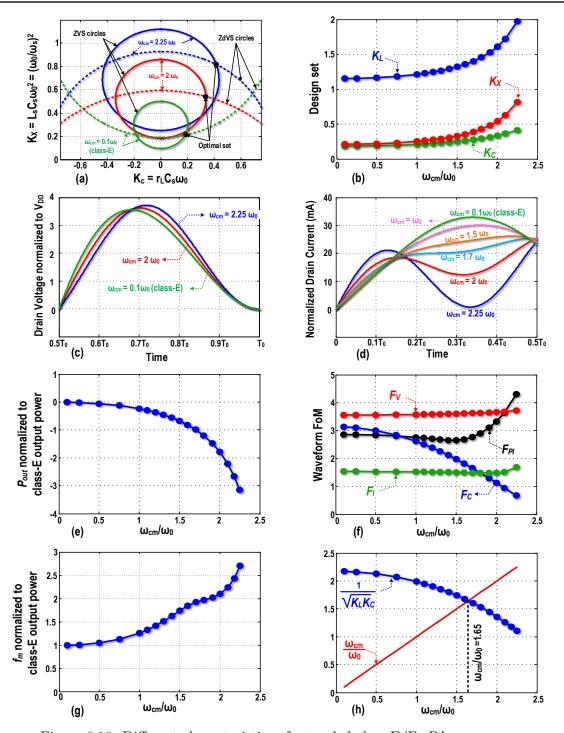

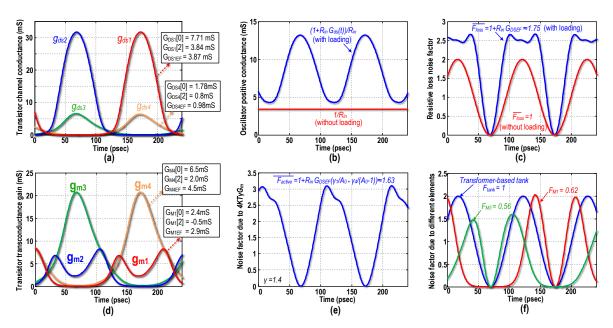

where  $\alpha_V$  is the voltage efficiency, defined as  $V_P/V_{DD}$ . To get a better insight, the circuit-tophase noise mechanism, relative phase noise and power efficiency of different oscillator classes are also investigated and compared together in this section. Figure 2.15 (a-f) shows the oscillation voltage and drain current for the traditional, class-C and the proposed class-F oscillators for the same  $V_{DD}$  (i.e., 1.2 V), tank Q-factor (i.e., 15) and  $R_P$  (i.e., 220  $\Omega$ ).

The  $\alpha_V$  must be around 0.8 for the class B and F oscillators due to the voltage drop  $V_{dsat}$  across tail transistor needed to keep it in saturation. The combination of the tail capacitance and entering the gm-devices into the linear region reduces  $\alpha_I$  of class-B from the theoretical value of  $2/\pi$  to around 0.55. Fortunately,  $\alpha_I$  is maintained around  $2/\pi$  for class-F due to the pseudo-square drain voltage and larger gate amplitude. The class-C oscillator with a dynamic bias of the active transistor offers significant improvements over the traditional class-C, and

|                         | Theoretical expression                                                                                                 | Class-B                      | Class-C                | Class-F                       |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------|-------------------------------|--|

| $F_{RP}$                | $2\Gamma_{rms}^2$                                                                                                      | 1 (average)                  | 1 (average)            | 0.7 (best)                    |  |

| $F_{GDS}$               | $2\Gamma_{rms}^2 R_P G_{DSEF1}$                                                                                        | 0.56 (worst)                 | 0.07 (best)            | 0.27 (average)                |  |

| $F_{GM}$                | $2\Gamma_{rms}^2 \frac{\gamma}{A} \left( 1 + R_P G_{DS1EF} \right)$                                                    | $1.56\gamma \text{ (worst)}$ | $1.07\gamma$ (average) | $0.7\gamma \text{ (best)}$    |  |

| F                       | $2 \Gamma_{rms}^2 \left(1 + \frac{\gamma}{A}\right) \left(1 + R_P G_{DS1EF}\right)$                                    | 5.5 dB (worst)               | 3.9 dB (average)       | 2.8 dB (best)                 |  |

| $\alpha_I$              | $I_{H1}/I_B$                                                                                                           | 0.55 (worst)                 | 0.9 (best)             | 0.63 (average)                |  |

| $\alpha_V$              | $V_p/V_{DD}$                                                                                                           | 0.8 (best)                   | 0.7 (average)          | 0.8 (best)                    |  |

| $PN\left(dBc/Hz\right)$ | $10\log_{10}\left(\frac{K_B\ T\ R_p}{2\ Q_0^2\ V_p^2}\cdot F\cdot \left(\frac{\omega_0}{\Delta\omega}\right)^2\right)$ | -133.5 (worst)               | -134 (average)         | -136 (best)                   |  |

| FoM(dB)                 | $-10log_{10}\left(\frac{1000K_BT}{2Q_0^2\alpha_I\alpha_V}F\right)$                                                     | 191.2 (worst)                | 194.5 (best)           | $194.2 (\approx \text{best})$ |  |

Table 2.2: Comparison of different oscillator's classes for the same  $V_{DD}$  (1.2 V), tank Q-factor (15),  $R_P$  (i.e. 220  $\Omega$ ), and carrier frequency (7 GHz) at 3 MHz offset frequency.

maximizes the oscillation amplitude without compromising the robustness of the oscillator start-up [44]. Nevertheless, its  $\alpha_V$  is around 0.7 to avoid gm-devices entering the triode region. Class-C drain current composed of tall and narrow pulses results in  $\alpha_I$  equal to 0.9 (ideally 1).

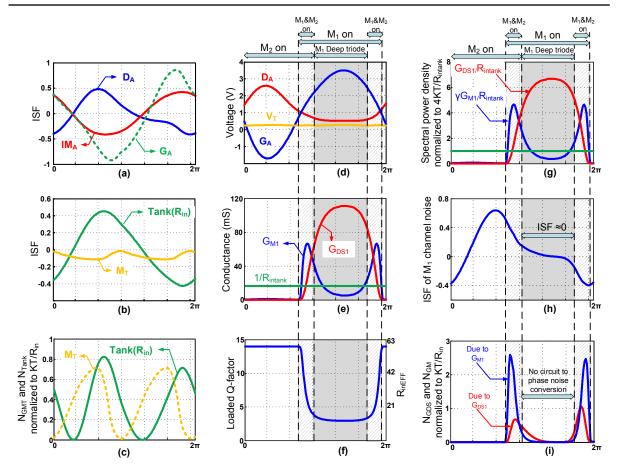

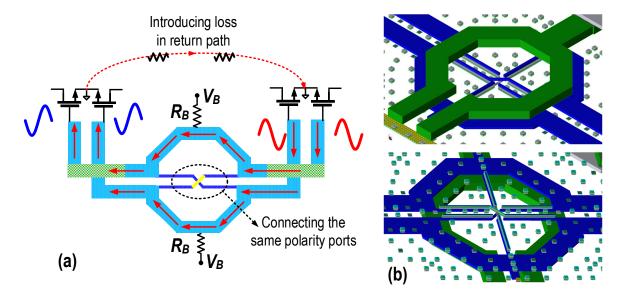

Obtaining the ISF function is the first step in the calculation of the oscillator's effective noise factor. The class-B/C ISF function is a sinusoid in quadrature with the tank voltage [25], [45]. However, finding the exact equation of class-F ISF is not possible, hence, we had to resort to painstakingly long Cadence<sup>TM</sup> simulations to obtain the ISF curves. Figure 2.15(g) shows the simulated class-F tank equivalent ISF function, which is smaller than the other classes for almost the entire oscillation period.

Figure 2.15(h) demonstrates the tank effective noise factor along the oscillation period for different oscillator classes. The  $F_{RP}$  is 32% lower for the proposed class-F due to its special ISF properties. The gm-device M<sub>1</sub> channel conductance across the oscillation period is shown in Fig. 2.15(i). As expected,  $G_{DS1}(t)$  of class-F exhibits the largest peak due to high oscillation swing at the gate and, consequently, injects more noise than other structures to the tank. On the other hand, class-C operates only in the saturation region and its effective transistor conductance is negligible. Figure 2.15(j) stronger emphasizes that the gm-device resistive channel noise could even be 7 times higher than the tank noise when the  $M_1$  operates in the linear region. To get a better insight, one need to simultaneously focus on Figs. 2.15(j) and (k). Although the class-F  $G_{DS1}$  generates lots of noise in the second half of the period, its relevant ISF value is very small there. Hence, the excessive transistor channel noise cannot convert to the phase noise and as shown in Fig. 2.15(l), the  $F_{GDS}$  of class-F is one half of the traditional oscillator. The transconductance loop gain of the different oscillator structures are shown in Fig. 2.15(m). Class-F needs to exhibit the highest effective transconductance loop gain to compensate its larger gm-devices channel resistance losses. However, half of the required loop gain is covered by the transformer-based tank voltage gain. Figure. 2.15(o) demonstrates the active device effective noise factor along the oscillation period. Class-F offers the lowest  $F_{GM}$  due to its special ISF

Figure 2.15: Mechanisms of circuit noise to phase noise conversion in different classes of RF CMOS oscillator.

nature and the passive voltage gain between the tank and gate of the gm-transistors.

Table 2.2 summarizes the performance of different oscillator classes of this example. It can be concluded that class-F oscillator achieves the lowest circuit-to-phase noise conversion along the best phase noise performance with almost the same power efficiency as the class-C oscillator.

Figure 2.16: Sensitivity of class-F oscillator to the position of the second resonant frequency: tank's input impedance magnitude and phase (top), oscillation waveform (bottom).

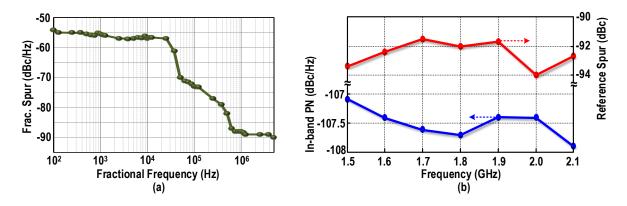

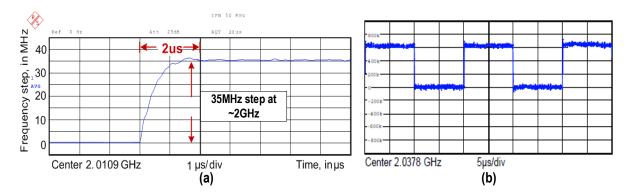

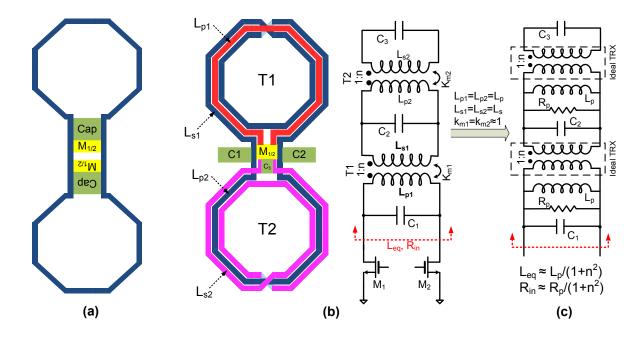

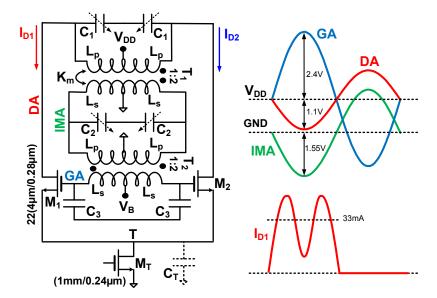

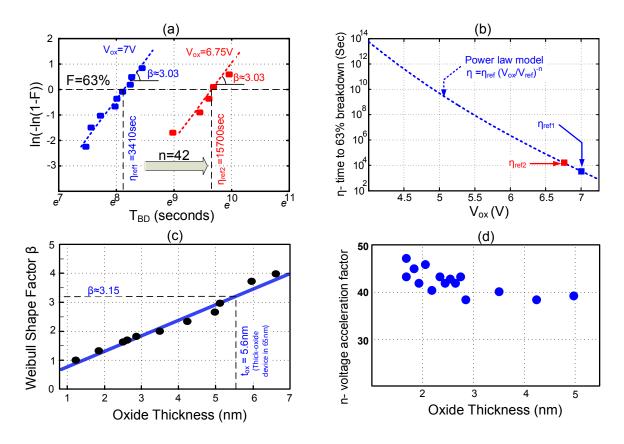

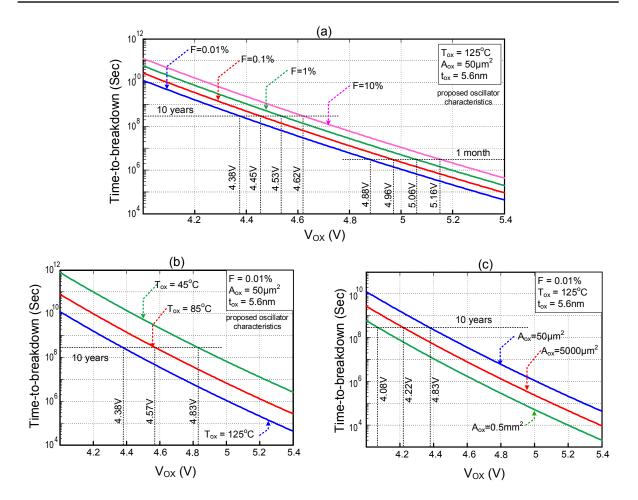

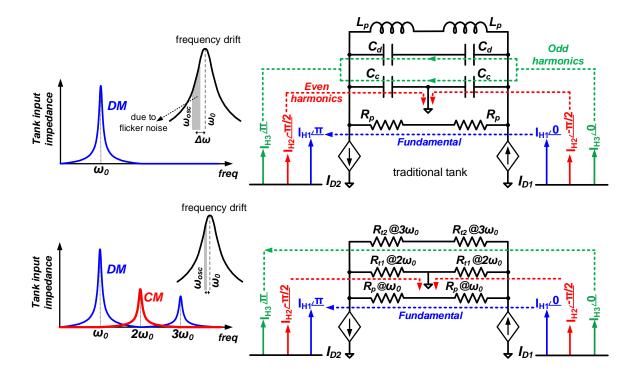

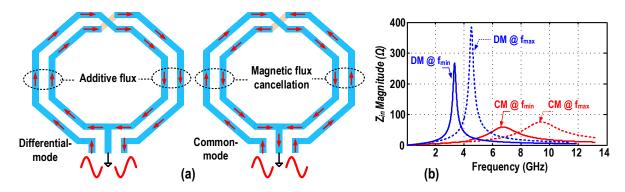

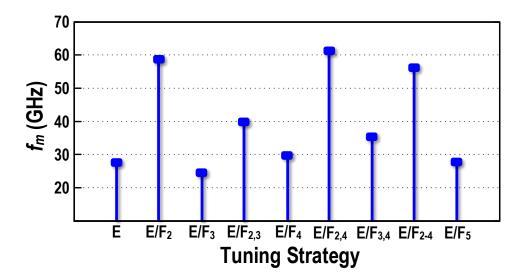

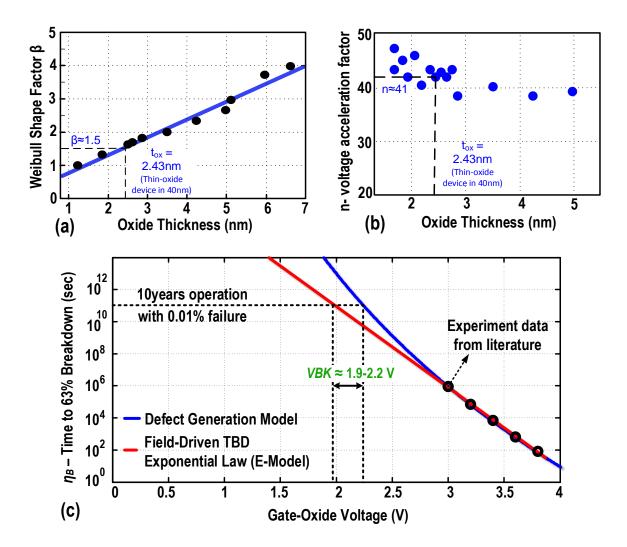

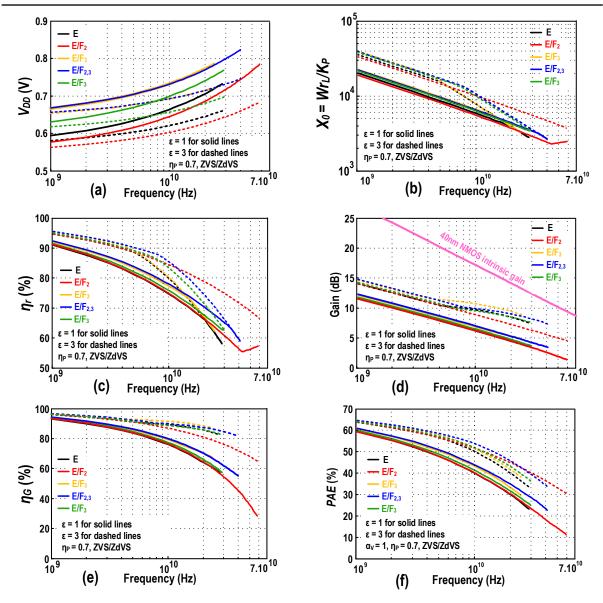

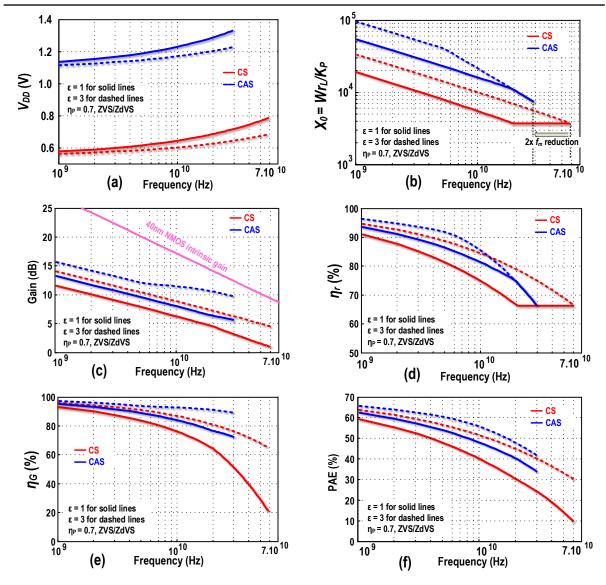

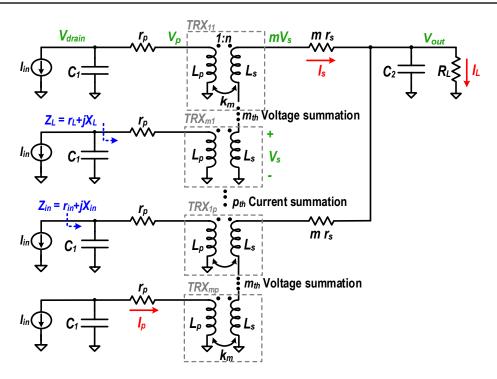

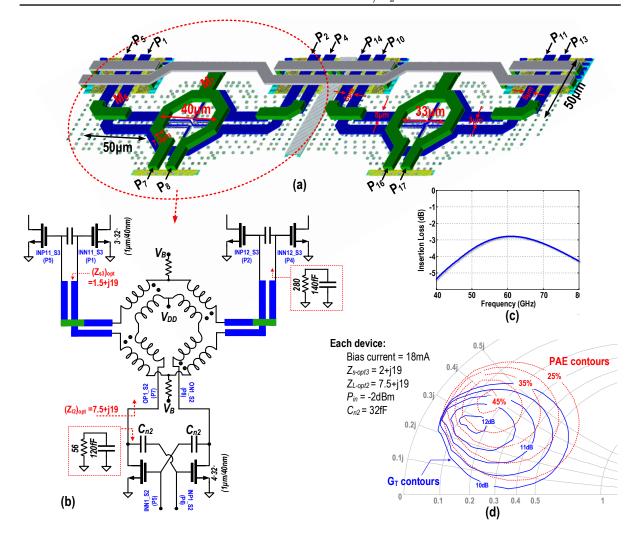

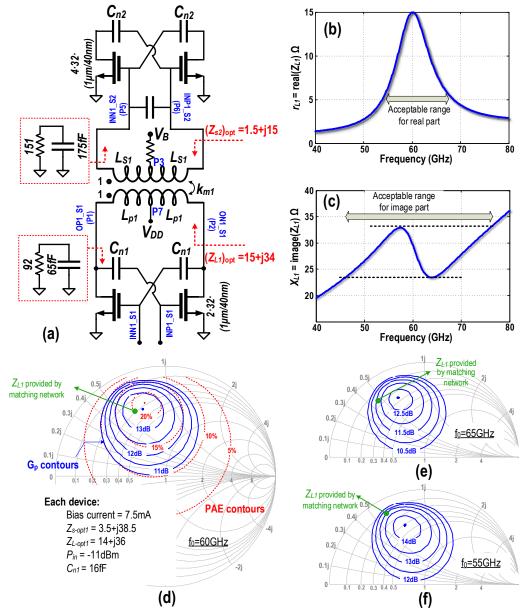

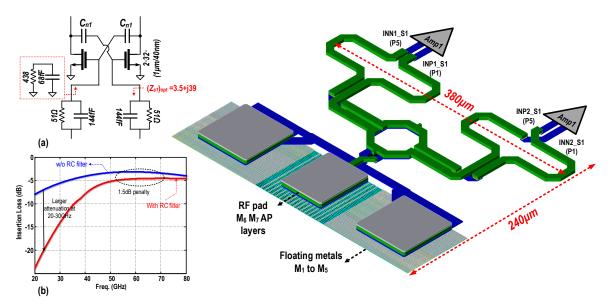

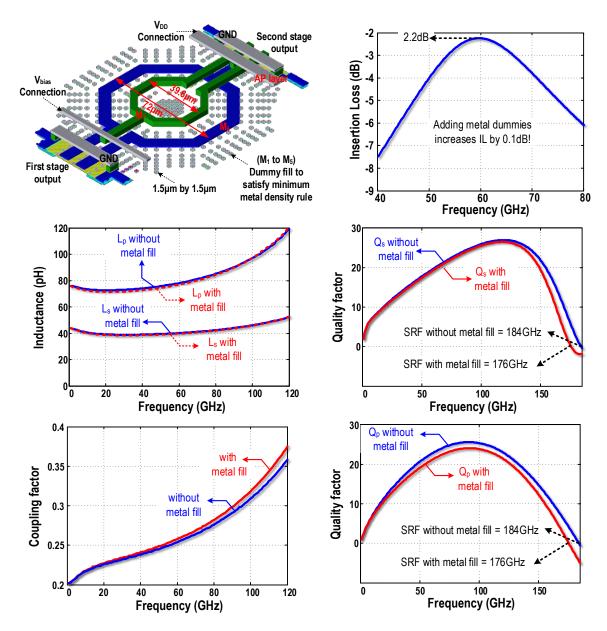

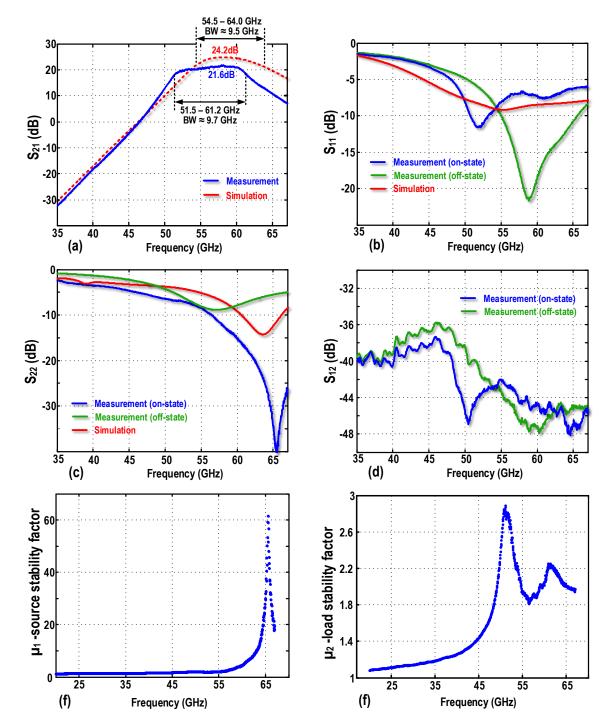

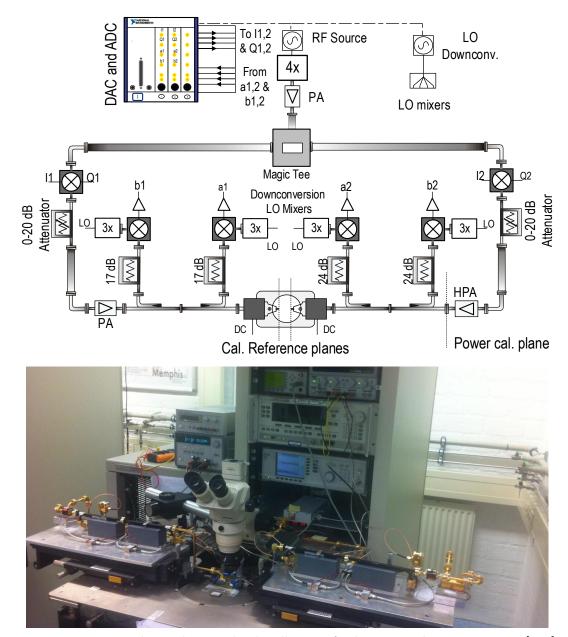

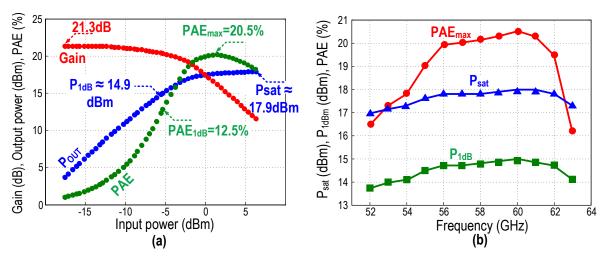

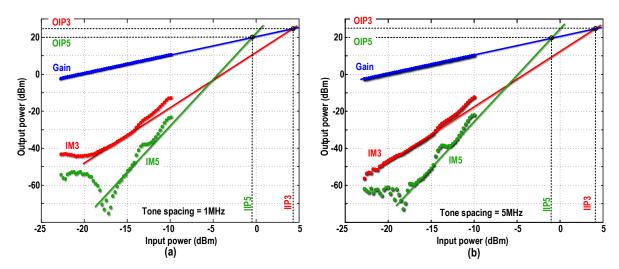

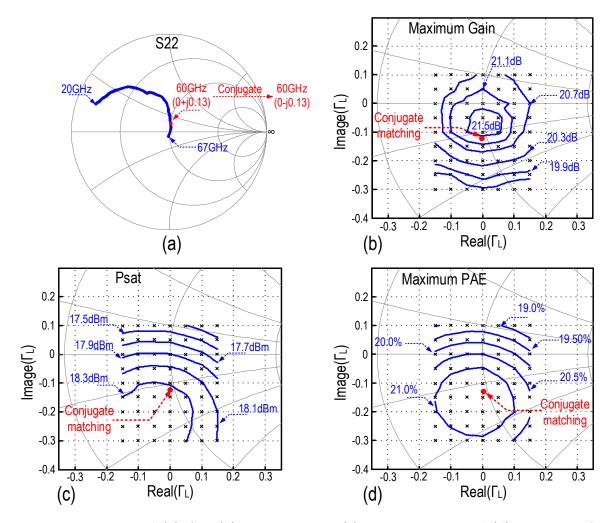

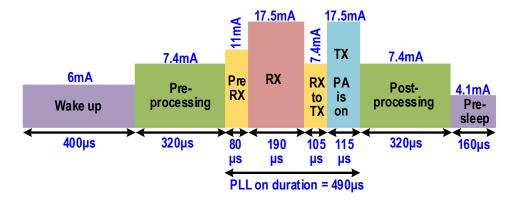

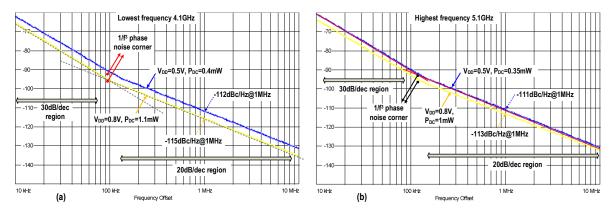

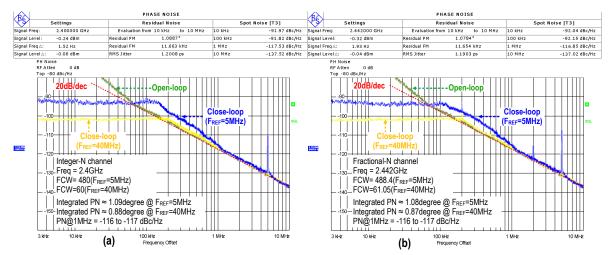

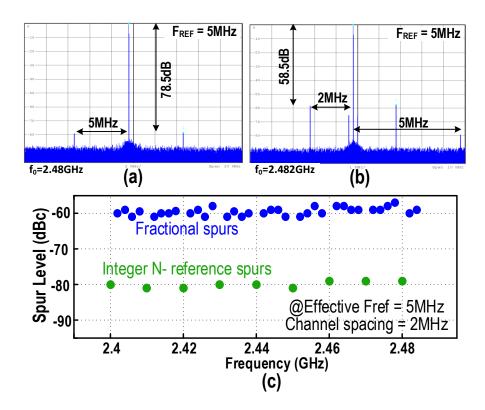

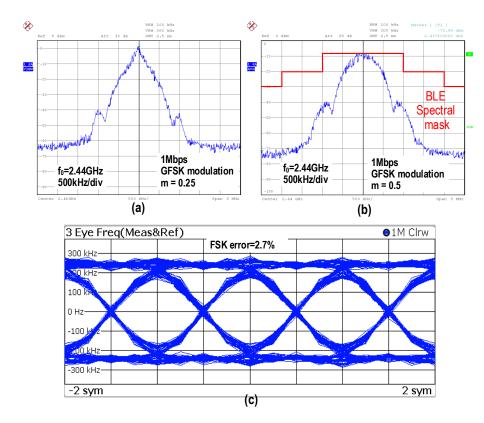

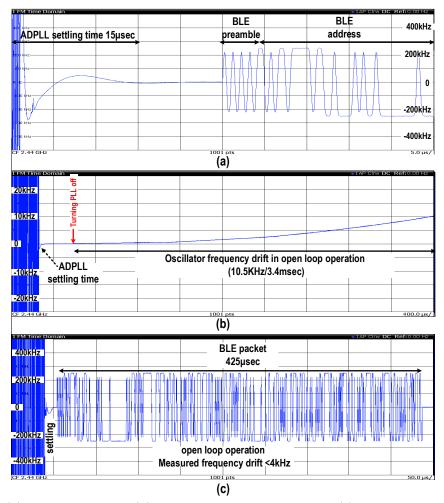

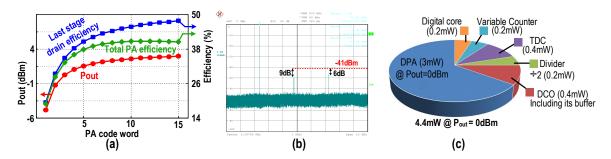

The use of transformer in the Class-F configuration offers an additional reduction of the  $1/f^3$  phase noise corner. The transformer inherently rejects the common-mode signals. Hence, the 1/f noise of the tail current source can appear at the transformer's primary but it will be effectively filtered out on the path to the secondary winding. Consequently, the AM-to-PM conversion at the  $C_2$  switched capacitors is entirely avoided.